## AVR 8ビット マイクロ コントローラ

# **Atmel**

# AVR1003: XMEGAのクロック システムの使い方

## 応用記述

## 要点

- ・32kHz, 2MHz, 32MHzの内部発振器

- ・外部クリスタル用発振器または外部クロック入力

- 1~31倍の倍率を持つ内部PLL

- ・安全なクロック元切り換え

- 外部発振器停止検出

- ・1~2048分周のシステム クロック前置分周器任意選択

- 内部発振器の走行時自動校正

- ・ドライバのソースコード内包

| 111 |

|-----|

|     |

|     |

| 要, | <u>اي</u> | •••••••1                                               |

|----|-----------|--------------------------------------------------------|

| 1. | 序説        |                                                        |

| 2. | クロック      | <b>シ</b> ステム概要 ····································    |

|    | 2.1.      | <b>内部クロック元</b> ····································    |

|    | 2.2.      | <b>外部クロック元</b> ····································    |

|    | 2.3.      | 高周波数PLL任意選択 ····································       |

|    | 2.4.      | ジステム クロック選択と前置分周器 ···································· |

|    | 2.5.      | クロック構成設定施錠 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・        |

|    | 2.6.      | 休止形態とクロック元 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・        |

|    |           | <b>外部発振器停止検出器</b> •••••••••• 6                         |

|    |           | 内部発振器の走行時自動校正・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・      |

|    | 16.4      | 7                                                      |

| 4. | 改訂關       | 覆歴 ••••••                                              |

# 1. 序説

Atmel<sup>®</sup> XMEGA<sup>®</sup>のクロックシステムは内部と外部のクロック元の大きな資源の組み合わせを提供する高い柔軟性を持つ単位部の組で す。内部の高周波数PLLと柔軟な前置分周器部がCPUと周辺機能の両方に対して広大な量の可能なクロック元を提供します。外部発 振器停止検出器と任意選択の内部発振器走行時自動校正は安全性と精度に関する設計を助けて外部部品数を削減します。

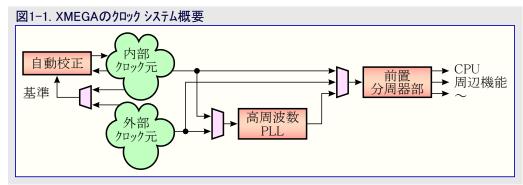

# 2. クロック システム概要

XMEGAのクロックシステムは内部と外部のクロック元の大きな資源の組み合わせを提供します。加えて内部PLLは選択したクロック元を1~31の範囲の係数での逓倍に使うことができます。

容易な実装ためにXMEGAに対する既定のクロック設定は工場校正された内部2MHz供給元からの走行での始動です。この方法では既定設定で充分なら、外部部品もコード実行を始めるためのソフトウェア構成設定も必要ありません。

後続項は様々なクロック元と主システム クロックとしてそれらの1つの使う利用可能な構成設定任意選択を記述します。

### 2.1. 内部クロック元

超低電力32kHz RC発振器から自動校正機能付きの工場校正された32MHz環状発振器までに渡って、(内部PLLを含めて)5つの内部クロック元があります。全て、けれどもその内の1つが主システム クロックに使うことができます。

内部供給元のいくつでもが、例え主システム クロックに使われていなくても、与えられたどの時にでも許可することができます。主システム クロックとしてと実時間計数器単位部用のクロック元として、同時に使うことができる32kHz RC発振器のように、いくつかのクロック元は複数の目的にさえも使われるかもしれません。

内部クロック元のいくつかは均一でより高い周波数を生成するために内部PLLへの基準として使うことができます。PLLは「高周波数PLL任意選択」項で網羅されます。

#### 超低電力32kHz RC発振器

超低電力(ULP)32kHz内部RC発振器は始動遅延、ウォッチドック、タイマ、様々な内部タイシングのような主にシステム目的に使われます。これ は実時間クロック単位部に使うことができますが、システム クロック元として利用できません。30%の周波数精度ではどちらにしてもそれとし て意図されていません。

ULP発振器は実時間計数器単位部に対する供給元として使うことができます。より多くの詳細については「AVR®1314:XMEGA実時間計数器の使い方」応用記述を参照してください。

ULP発振器はそれが必要とされる時にハードウェアによって自動的に許可されます。

#### 校正付き32kHz RC発振器

32.768kHz内部RC発振器(RC32K)は3V/25℃で1%の精度で32kHzに工場校正されています。校正値は校正(識票)列に格納され、リ セットで自動的に発振器の校正(RC32KCAL)レジスタ内へ設定されます。この値は使用者に対して読み書きアクセスが可能ですが、発振 器は推奨限度外に調節されるべきではりません。詳細についてはデバイスのデータシートの電気的特性を参照してください。

RC32K発振器は直接的にシステム クロック元として、また実時間計数器単位部に対する供給元(実際にはRC32Kが1.024kHzに分周されて)として使うことができます。より多くの詳細については「AVR1314:XMEGA実時間計数器の使い方」応用記述を参照してください。

RC32K発振器は内部PLLに対する供給元として使うことはできません。

システム クロック元の代替になることの他に、RC32Kは2MHzと32MHzの内部発振器の自動校正機能に対する基準としても使うことができます。この2つの発振器と自動校正機能は後の項で網羅されます。

発振器制御(OSC.CTRL)レジスタの内部32kHz RC発振器許可(RC32KEN)ビットがこの発振器を制御し、一方それがシステム クロック元とし ての使用準備が整って安定しているかを調べるために、発振器状態(OSC.STATUS)レジスタの内部32kHz RC発振器準備可(RC32KR DY)フラグをポーリングすることができます。

#### 校正付き2MHz RC発振器

2MHz内部RC発振器(RC2M)は3V/25℃で1%の精度で2MHzに工場校正されています。校正値は校正(識票)列に格納され、リセットで 自動的に発振器の校正レジスタ内へ設定されます。この発振器は更なる調節と後の項で網羅される自動校正機能を使って校正する ことができます。

RC2M発振器は直接的にまたは均一でより高いシステム周波数を生成するために内部PLLを通して、システム クロックとして使うことができます。PLL使用時、使用者にはCPUと周辺機能に対して推奨周波数限度を越えないようにする責任があることに注意してください。

発振器制御(OSC.CTRL)レシスタの内部2MHz RC発振器許可(RC2MEN)ビットがこの発振器を制御し、一方それがシステム クロック元としての使用準備が整って安定しているかを調べるために、発振器状態(OSC.STATUS)レシスタの内部2MHz RC発振器準備可(RC2MR DY)フラグをホーリングすることができます。

#### 校正付き32MHz環状発振器

32M内部環状発振器(R32M)は3V/25℃で1%の精度で32MHzに工場校正されています。校正値は校正(識票)列に格納され、リセットで 自動的に発振器の校正レジスタ内へ設定されます。この発振器は更なる調節と「内部発振器の走行時自動校正」項で網羅される自動 校正機能を使って校正することができます。

R32M発振器は直接的にまたは均一でより高いシステム周波数を生成するために内部PLLを通して、システム クロックとして使うことができます。PLL使用時、使用者にはCPUと周辺機能に対して推奨周波数限度を越えないようにする責任があることに注意してください。

発振器制御(OSC.CTRL)レジスタの内部32MHz環状発振器許可(R32MEN)ビットがこの発振器を制御し、一方それがシステム クロック元とし ての使用準備が整って安定しているかを調べるために、発振器状態(OSC.STATUS)レジスタの内部32MHz RC発振器準備可(R32MR DY)フラグをホーリングすることができます。

#### 2.2. 外部クロック元

全てがXTAL1とXTAL2のピンを共用する多くの可能な外部クロック元があります。勿論、これは与えられたどの時間でも1つの供給元だけを許可することができます。ハードウェアは2つの外部供給元が同時に許可されないことを保証します。故にこれを行う試みは無視されます。

これに対する例外は実時間クロック単位部への供給元として時計用外部クリスタルでTOSC1とTOSC2のピンを使う実時間計数器用発振器 です。実時間計数器用発振器はシステム クロック元として直接使うことができますが、前置分周された1kHz信号はRTCにだけ行くのでこ れを使うことはできません。RTCのより多くの詳細については「AVR1314:XMEGA実時間計数器の使い方」応用記述を参照してくださ い。

#### クリスタルと振動子

XTAL1とXTAL2のピンは0.4~16MHzの外部クリスタルまたは振動子を使うチップ上の発振器として働く反転増幅器の各々入力と出力です。このクリスタル用発振器(XOSC)は次の任意選択の1つに構成設定することができます。

- ・時計用32.768kHzクリスタル用低電力任意選択付き発振器

- ・0.4~2MHz低振幅クリスタルまたは振動子用発振器

- ・2~9MHz低振幅クリスタルまたは振動子用発振器

- ・9~12MHz低振幅クリスタルまたは振動子用発振器

- ・12~16MHz低振幅クリスタルまたは振動子用発振器

実際には、これが32.768kHzクリスタル用の1つと高周波数クリスタル用の1つの2つの発振器として実装されています。

時計用外部32kHzクリスタル使用時、外部発振器制御(OSC.XOSCCTRL)レジスタの32kHzクリスタル用発振器低電力動作(X32KLPM)ビットが低電力動作を許可します。これは時計用32kHzクリスタルだけに適用し、高品質クリスタルでだけ使われるべきです。

外部発振器制御(OSC.XOSCCTRL)レジスタの外部発振器選択(XOSCSEL)ビット領域がこの発振器を制御し、一方それがシステム クロック 元としての使用準備が整って安定しているかを調べるために、発振器状態(OSC.STATUS)レジスタの外部発振器準備可(XOSCRDY)フ ラグをポーリングすることができます。

この発振器はこれを許可する前に構成設定されなければならず、構成設定は先にこれを禁止することなしに変更することができません。ハードウェアはそれが許可されている間の如何なる構成設定変更も無視します。

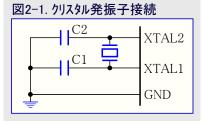

外部クリスタルの接続方法と推奨コンデンサ値は下の図と表で示されます。

注: クリスタル用発振器は低振幅型発振器で、他の装置へクロック信号を供給するためにXTALピンを使うことはできません。代わりにタイマ/カウンタ単位部の1つが外部装置用のクロック信号を生成するのに使うことができます。「AVR1306:XMEGAタイマ/カウンタの使い方」応用記述を参照してください。

| 表2-1. 推到 | 受コンデンサ値 |

|----------|---------|

|----------|---------|

|                           | ·                     |

|---------------------------|-----------------------|

| 周波数範囲                     | <b>コンデンサ値</b> (C1,C2) |

| $0.4 \sim 2 \mathrm{MHz}$ | 100pF                 |

| 2~9MHz                    | 15pF                  |

| 9∼12MHz                   | 15pF                  |

| 12~16MHz                  | 10pF                  |

# **Atmel**

#### 外部クロック

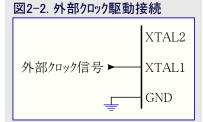

ハートウェア設計が外部クロック信号を供給する場合、それはXTAL1ピンに接続でき、チップ上のクリスタル用発振器は禁止されます。外部クロックは外部発振器制御(OSC.XOSCCTRL)レジスタの外部発振器選択(XOSCSEL)ビット領域での可能な選択の1つで、発振器状態(OSC.STATUS)レジスタの外部発振器準備可(XOSCRDY)フラクでの安定が報告される前に、6クロック周期の始動時間を常に費やします。

右図は外部クロック信号を接続方法を示します。正しい動作を保証するために、クロック周波数は或る周期から別の周期へ2%よりも大きく変わるべきではありません。クロック周波数がもっと急に変わる必要があるなら、XMEGAはその変化の間、リセット状態に保たれるべきです。

#### 2.3. 高周波数PLL任意選択

より高い周波数が必要とされるなら、1~31の係数でクロック元を逓倍する組み込みPLLを使うことができます。次のクロック元がPLLへの入力として使うことができます。

- ・内部2MHz RC発振器

- ・内部で4分周された内部32MHz環状発振器

- ・外部0.4~16MHzクリスタル用発振器

- ・外部クロック

ハートウェアは32kHz動作に構成設定された場合の外部発振器のPLL供給元としての使用を許しません。外部クロックが入力として使われる場合、それは0.4MHz以上でなければなりません。正確な最小値については電気的特性を参照してください。

PLLを許可する正しい手順は次のとおりです。

- 1. PLL制御(OSC.PLLCTRL)レジスタのクロック元(PLLSRC)ビット領域を使って入力クロック元を、倍率(PLLFAC)ビット領域を使って倍率を 選択してください。

- 2. 発振器制御(OSC.CTRL)レジスタのPLL許可(PLLEN)ビットを使ってPLLを許可してください。

3. 発振器状態(OSC.STATUS)レジスタのPLL準備可(PLLRDY)フラグを調べることによってPLLの安定を待ってください。

使用者はPLLの許可を試みる前に入力クロック元が安定であることを確認すべきです。許可時、代表的にPLLは安定化のために64基 準周期を必要とします。

PLL構成設定は先にそれを禁止することなしに変更することはできません。ハートウェアはそれが許可の間、構成設定変更の如何なる 試みも無視します。

使用者にはPLLへ最低入力クロック周波数供給し、出力が決して200MHzを越えないことを保証する責任があります。最低入力周波数 必要条件はPLLへの入力として外部信号を使う時に適用します。

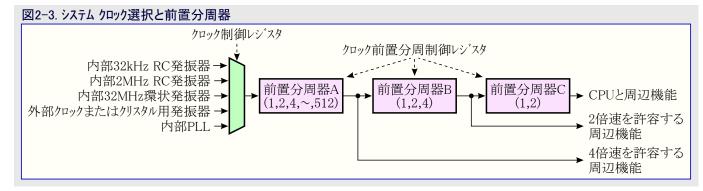

#### 2.4. システム クロック選択と前置分周器

主システム クロックに対して柔軟な任意選択を提供するために、XMEGAのクロックシステムはクロック元またはPLLの1つを選択する多重器(M UX)を含みます。それはCPUと周辺機能へ配給される前に1~2048の係数でクロック信号を分周できる高い構成設定能力の前置分周 器部を通して選択されたクロックを供給します。それはCPUより高い周波数で動作する周辺機能(例えばCPU周波数の2倍で動作する ことができるEBI単位部)に対してCPUクロック周波数の2または4倍のクロック信号を提供することもできます。

下図は多重器(MUX)と前置分周器を図解します。MUXからの出力は3つの前置分周器段を通って行きます。初段の前置分周器Aは 1~512の係数で分周することができます。次の前置分周器BとCは信号をそのまま通すか、または合同で最大4分周するかのどちら かに構成設定することができます。この制限にの詳細についてはデータシートをご覧ください。前置分周器Cの出力はCPUと周辺機能 へ送られます。

リセット後の既定設定は内部2MHz RC発振器で、クロック信号を3つ全ての前置分周器の分周なしで通します。前置分周器Aは消費電力削減のために大きな係数によってシステム周波数をより低くするのに使うことができ、一方前置分周器BとCは選択した周辺機能への CPU周波数の1、2、または4倍のクロック信号の提供を主に意図されています。

前置分周器設定は何時での安全に変更することができます。ハートウェアが周波数遷移間の不具合なしを保証します。クロック元変更時、ハートウェアは不安定なクロック元への如何なる試みも防止します。

# **Atmel**

システムクロックと前置分周器の変更手順は次のとおりです。

- 1. 構成設定変更保護(CCP)レジスタ内にI/Oレジスタ保護識票(バイト値\$D8)を設定してください。これは次からの4CPU命令周期間、割り込みを自動的に禁止します。

- 2. システム クロックまたは前置分周器に対して望む形態を設定してください。

- 注: CCPレジスタへの識票書き込みはシステム クロックまたは前置分周器のどちらかだけの再構成設定に対する許可時間です。両方の再 構成設定が必要な場合、CCP書き込みを繰り返してください。詳細については例のソフトウェアを学習してください。

#### 2.5. クロック構成設定施錠

安全の予防処置として次のリセットまで現在のクロック システム構成設定を施錠することが可能です。応用が1つのクロック構成設定での動作 を行っているなら、予期せぬ変更から構成設定を保護する方法を知ることができます。

構成設定の保護手順は次のとおりです。

- 1. XMEGAのクロック システムを望む構成設定に設定してください。

- 2. 構成設定変更保護(CCP)レジスタ内にI/Oレジスタ保護識票(バイト値\$D8)を設定してください。これは次からの4CPU命令周期間、割り込みを自動的に禁止します。

- 3. クロック システム施錠(CLK.LOCK)レジスタのクロック システム施錠(LOCK)ビットを設定(1)してください。

4. 今やクロック構成設定は次のシステムリセットまで施錠されています。

外部発振器停止検出器が許可されている場合、その停止はクロック システム構成設定を開錠にするでしょう。詳細については「<mark>外部発振</mark> 器停止検出器」項をご覧ください。

#### 2.6. 休止形態とクロック元

全ての発振器とクロック生成はパワーダウンとパワーセーブの休止形態で禁止されます。例外はパワーセーブ動作で実時間計数器(RTC)が許可されている場合で、これはRTCクロック元の走行をそのままにします。RTCが使われないなら、パワーセーブ動作の代わりにパワーダウン動作が推奨されます。これら2つの休止形態での始動遅延はまるで発振器が禁止されているように振舞います。

スタンバイと拡張スタンバイの休止形態では発振器が走行を維持し、大規模な遅延なしのCPU起動を可能にします。

アイドル動作では発振器が走行を維持し、CPUはどんな遅延もなしに休止形態から起動します。

休止形態と起動条件の詳細についてはデバイスのデータシートを参照してください。

#### 2.7. 外部発振器停止検出器

外部クリスタルまたは外部クロック元を使うとき、供給元停止の僅かな確率が常にあります。安全の予防処置として、XMEGAのクロックシステムは外部クロック元を監視してそれが停止した場合に反応する外部発振器停止検出器を持っています。

外部供給元が主システム クロック元として選択され、そしてそれが停止した場合、停止検出器は内部2MHz RC発振器に切り換えて、遮 蔽不可割り込み(NMI)を発行します。NMIの詳細に関しては「AVR1305:XMEGAの割り込みと設定可能な多段割り込み制御器」応用 記述を参照してください。

外部供給元が許可されていて、しかしそれが主システム クロック元として選択されていない場合、外部供給元が禁止されるだけですが、 未だNMIは発行されます。

停止検出器は外部供給元の監視にULP発振器を使い、周波数が32kHz以下へ下がる場合に反応します。ULP精度が30%で、故に 32kHz以下での走行の可能性がありますが、これは推奨されません。32kHz動作は停止検出を引き起こすために保証されません。

停止検出器は既定で許可されていません。偶然の許可を避けるために、それを許可するのに特別な手順が必要とされます。その手 順は次のとおりです。

- 1. 構成設定変更保護(CCP)レジスタ内にI/Oレジスタ保護識票(バイト値\$D8)を設定してください。これは次からの4 CPU命令周期間、 割り込みを自動的に禁止します。

- 2. 外部発振器停止検出(OSC.XOSCFAIL)レジスタの停止検出許可(XOSCFDEN)ビットを設定(1)してください。

- 3. 今や停止検出器は次のシステムリセットまで許可されています。

外部供給元が主システム クロック元として使われている時にそれが停止した場合に停止検出器が遮蔽不可割り込みを発行するので、この割り込みに対する割り込み処理の実装が重要です。遮蔽不可割り込みはどんな方法でも禁止することができず、従ってその名前が 『遮蔽不可"です。詳細については例のソフトウェアを学んでください。

## 2.8. 内部発振器の走行時自動校正

XMEGAのクロックシステムは、2MHz RC発振器に対する1つと32MHz環状発振器に対する1つの、2つのデジタル周波数固定化閉路(DF LL)を提供します。DFLLは校正処理に対する基準として内部32kHz RC発振器または外部の時計用32kHzクリスタルのどちらかの使用 へ個別に構成設定することができます。

ー旦許可されると、DFLLは基準クロックに基いてその発振器の継続的な校正を提供します。休止形態移行時、現在の状態で凍結され、休止形態を抜ける時に校正閉路はその場所から再び続けます。

DFLLが禁止される場合、発振器に対する現在の校正値はDFLLが再び許可されて校正処理が継続するまで、事実上そのまま留まります。

DFLL制御(OSC.DFLLCTRL)レジスタは、DFLL 32MHz校正基準選択(R32MCREF)とDFLL 2MHz校正基準選択(RC2MCREF)の2つの制御ビットを含み、これがDFLLに対する基準クロックを選択します。論理0が内部32kHz RC発振器を選択し、一方論理1が外部の時計用32kHzクリスタル用発振器を選択します。ハードウェアは不安定なクロック元使用の如何なる試みも無視します。

DFLLそられ自体が対応するDFLL計数(OSC.DFLLx.OSCCNTn)レジスタに3パイトの計数基準値を必要とします。正しい計数基準値が リセットで自動的に設定され、これは使用者によって変更されるべきではありません。

DFLLは2バイトの各々の校正(OSC.DFLLx.CALn)レジスタも持ち、これはリセットでハートウェアによって自動的に設定される許可ビットと校正 値を含んでいます。校正値は校正閉路に対する開始点として扱い、これは使用者によって変更されるべきではありません。 DFLL許可の正しい手順は次のとおりです。

1. DFLL制御(OSC.DFLLCTRL)レジスタのDFLL制御ビットで内部または外部の基準クロックを選択してください。

2. DFLLを許可するためにDFLLの制御(DFLLx.CTRL)レジスタのDFLL許可(ENABLE)ビットを論理1に設定してください。

3. 校正処理が直ちに始まります。

内部32KHz RC発振器に対する走行時校正任意選択はありませんが、必要なら、校正(RC32KCAL)レジスタを変更することによって微調整することができます。けれども、どの発振器も推奨動作限度外へ調節しないように最大限の注意が祓われるべきです。

# 3. 例

本応用記述はC言語で実装された基本的なクロック システム ドライハ での一括ソース コードを含みます。それはIAR Embedded Workbench® コンパイラで書かれています。

注: クロック システム ドライバは高性能コートでの使用に対して意図されていません。それはXMEGAのクロック システムで開始するためのラ イブラリとして設計されています。タイミングとコート 量が重要な応用開発については、クロック システムのレジスタに直接アクセスすべきです。 より多くの詳細についてはドライバのソース コード とデバイスのデータシートを参照してください。

#### ファイル

一括ソースコードは次の3つのファイルから成ります。

- ・ clksys\_driver.c : クロック システム ト・ライハ・ソース ファイル

- ・ clksys\_driver.h : クロック システム トライハ ヘッダ ファイル

- ・main.c : トライハを使うコート 例

利用可能なドライバインターフェース関数とそれらの使用の完全な概要についてはソース コードの資料を参照してください。

#### Doxygen資料化

全てのソースファイルはDoxygenを使う自動資料生成用に準備されています。Doxygenは特別なキーワードを使ってソースコードを分析することによって、ソースコードから資料を作成するツールです。Doxygenについてのより多くの詳細に関してはhttp://www.doxygen.orgを訪ねてください。予めコンハーイルされたDoxygen資料は本応用記述に伴うソースコードと共に供給され、ソースコードフォルダのreadme.htmlファイルから利用可能です。

# 4. 改訂履歴

| 文書改訂  | 日付       | 注釈  |

|-------|----------|-----|

| 8072E | 2009年11月 |     |

| 8072F | 2016年7月  | 新雛形 |

# Atnel | Enabling Unlimited Possibilities<sup>®</sup>

Atmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA TEL:(+1)(408) 441-0311 FAX: (+1)(408) 436-4200 | www.atmel.com

© 2016 Atmel Corporation. / 改訂:Atmel-8072F-Using-the-XMEGA-Clock-System\_AVR1003\_Application Note-07/2016

Atmel<sup>®</sup>、Atmelロンとそれらの組み合わせ、Enabling Unlimited Possibilities<sup>®</sup>、AVR<sup>®</sup>、XMEGA<sup>®</sup>とその他は米国及び他の国に於けるAtmel Corporati onの登録商標または商標です。他の用語と製品名は一般的に他の商標です。

お断り:本資料内の情報はAtmel製品と関連して提供されています。本資料またはAtmel製品の販売と関連して承諾される何れの知的所有権も禁 反言あるいはその逆によって明示的または暗示的に承諾されるものではありません。Atmelのウェブサイトに位置する販売の条件とAtmelの定義での 詳しい説明を除いて、商品性、特定目的に関する適合性、または適法性の暗黙保証に制限せず、Atmelはそれらを含むその製品に関連する暗示 的、明示的または法令による如何なる保証も否認し、何ら責任がないと認識します。たとえAtmelがそのような損害賠償の可能性を進言されたとし ても、本資料を使用できない、または使用以外で発生する(情報の損失、事業中断、または利益と損失に関する制限なしの損害賠償を含み)直 接、間接、必然、偶然、特別、または付随して起こる如何なる損害賠償に対しても決してAtmelに責任がないでしょう。Atmelは本資料の内容の正 確さまたは完全性に関して断言または保証を行わず、予告なしでいつでも製品内容と仕様の変更を行う権利を保留します。Atmelはここに含まれた 情報を更新することに対してどんな公約も行いません。特に別の方法で提供されなければ、Atmel製品は車載応用に対して適当ではなく、使用さ れるべきではありません。Atmel製品は延命または生命維持を意図した応用での部品としての使用に対して意図、認定、または保証されません。

安全重視、軍用、車載応用のお断り: Atmel製品はAtmelが提供する特別に書かれた承諾を除き、そのような製品の機能不全が著しく人に危害を 加えたり死に至らしめることがかなり予期されるどんな応用("安全重視応用")に対しても設計されず、またそれらとの接続にも使用されません。安全 重視応用は限定なしで、生命維持装置とシステム、核施設と武器システムの操作用の装置やシステムを含みます。Atmelによって軍用等級として特に明確 に示される以外、Atmel製品は軍用や航空宇宙の応用や環境のために設計も意図もされていません。Atmelによって車載等級として特に明確に示 される以外、Atmel製品は車載応用での使用のために設計も意図もされていません。

#### © HERO 2021.

本応用記述はAtmelのAVR1003応用記述(Rev.8072F-07/2016)の翻訳日本語版です。日本語では不自然となる重複する形容表現は省略されて いる場合があります。日本語では難解となる表現は大幅に意訳されている部分もあります。必要に応じて一部加筆されています。頁割の変更によ り、原本より頁数が少なくなっています。

必要と思われる部分には()内に英語表記や略称などを残す形で表記しています。

青字の部分はリンクとなっています。一般的に赤字の0,1は論理0,1を表します。その他の赤字は重要な部分を表します。