# AVR254 : ATtiny48でのQWheel<sup>®</sup>

# 要点

- チャネル数:4チャネル

- 感知器数:1感知器-1つの輪-全4チャネルで構成

- 輪設計:4チャネル

- 電極設計:2部電極形状(駆動-受信)、広い可能の多様性の配置

- 必要なPCB層:1層(ジャンパ有り)、2層(ジャンパなし)

- 電極材料: PCB、FPCB、フィルム上の銀または炭素、フィルム上のITO

- パネル材料: プラスティック、硝子、複合材、塗装面(低分子密度メタリック塗装可能)

- 隣接金属: キー真近の接地金属適合

- 輪感度:TWIインターフェース上の簡単な命令経由での個別設定可能

- インターフェース: 2線直列インターフェース(Philips<sup>®</sup> I<sup>2</sup>C適合、100kHzでの従装置動作)

- 許容湿度: クラス内最上

- 電力:1.8~5.5V

- 信号処理:自己校正

- 応用 : ラップトップ、車載、民生機器、PC周辺装置など

- 技術:特許スペクトラム拡散充電移転(横断形態)

- 特許と登録商標

- •QMatrix<sup>®</sup>(特許充電移転法)

- ・AKS<sup>®</sup>(特許隣接キー抑制<sup>®</sup>)技術

- ·QWheel(特許充電移転法)

# 1. 概要

この応用記述は(4チャネルから成る)輪用に設計されたATMEL®QTouch®ライブラリを用いで独自 化したファームウェア解決策を作ることに集中します。ファームウェアは輪上の接触を形態設定/感知し てPhilipsのI<sup>2</sup>Cインターフェースに適合するATMELのTWI(2線直列インターフェース)を使用してホストへ変 更を報告する能力を持ちます。ファームウェアは輪上の接触を感知して検出するためにQMatrix技 術を使用します。QMatrix技術は非常に簡潔に作られて容易に配線され得る横断充電転移感 知電極設計を使用します。充電は放射電極から横たわるパネル誘電体内に強制され、その後に 受信電極上で収集されます。これはその後に増幅器の使用なしで直接デジタル形式に変換さ れる採取コンデンサ内に充電を注ぎます。

チャネルは必要な走査線とデバイスのピンの数を最小にする配列形式で形態設定されます。キー電 極は銅箔模様またはプラスティック フィルム上の印刷導電インクとして、伝統的な印刷回路基板(PCB) またはフレキシブル印刷回路基板(FPCB)内に設計することができます。

# 2. ピン形態設定と説明

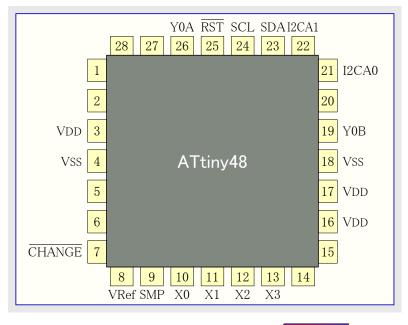

# 2.1. ピン形態設定

# 応用記述

# 暫定

本書は一般の方々の便宜のた め有志により作成されたもので、 ATMEL社とは無関係であること を御承知ください。しおりのはじ めにでの内容にご注意ください。

Rev. 8262A-10/09, 8262AJ1-12/13

# 2.2. ピン形態設定説明

| <u>表2-1. ピン-</u> | ·覧     |           |                               |              |

|------------------|--------|-----------|-------------------------------|--------------|

| ピン番号             | 機能名    | 入出力       | 注釈                            | 未使用時処理       |

| 3                | VDD    | 電源        | 供給電力                          | -            |

| 4                | VSS    | 電源        | 供給接地                          | -            |

| 7                | CHANGE | オープン ドレイン | 状態変更通知                        | 開放のまま        |

| 8                | VRef   | 電源        | 供給接地                          | -            |

| 9                | SMP    | 出力        | 採取出力                          | -            |

| 10               | X0     | 出力        | X配列駆動線                        | 開放のまま        |

| 11               | X1     | 出力        | X配列駆動線                        | 開放のまま        |

| 12               | X2     | 出力        | X配列駆動線                        | 開放のまま        |

| 13               | X3     | 出力        | X配列駆動線                        | 開放のまま        |

| 16               | VDD    | 電源        | 供給電力                          | -            |

| 17               | VDD    | 電源        | 供給電力                          | -            |

| 18               | VSS    | 電源        | 供給接地                          | -            |

| 19               | Y0B    | 入出力       | Y線接続                          | 開放のまま        |

| 21               | I2CA0  | 入力        | TWI(I2C適合)アドレス選択              | _            |

| 22               | I2CA1  | 入力        | TWI(I <sup>2</sup> C適合)アドレス選択 | -            |

| 23               | SDA    | オープン ドレイン | 直列インターフェース データ                | -            |

| 24               | SCL    | オープン ドレイン | 直列インターフェース クロック               | -            |

| 25               | RST    | 入力        | Lowリセット、内部30~60kΩのプルアップを持つ    | 開放のまま、またはVDD |

| 26               | Y0A    | 入出力       | Y線接続                          | 開放のまま        |

# <mark>3</mark>. 序説

独自化したファームウェアは充電条件の広い変化の元で安定した感知を提供するのに必要な全ての信号処理関数を含む、配列配置接触制御用に特別に設計されたデジタル集中動作充電移転感知器を容易にします。ほんの少しの外部部品だけが動作に必要とされます。完全な回路は数平方cmの片面PCB領域で構築することができます。可能な最低費用のためにCEM-1とFR1と打印された片面材を使用することができます。PCBの背面は3M VHB両面粘着アクリルフィルムのような伝統的な粘着物を用いて硝子またはプラステックのパネルの裏と同一面で装着することができます。

ファームウェアはパルス端によって2つの電極を渡って強制される電気的な充電での変化を感知する、横断充電移転感知技術を使用します。

ファームウェアは抽出されるべき感知器データと感知器パラメータの構成設定を許すためにPhilipsのI2Cインターフェースに適合するATMELの TWI(Two-wire Serial Interface:2線直列インターフェース)を使用します。命令構造はデータ転送量を最小にすると同時に伝達される情報 量を最大にするように設計されます。

# 3.1. QWheel

ATtiny48独自化されたファームウェアは輪を作るのに使用される4チャネルで構成されます。これらは4つのXと1つのYの走査線の電気的格子内のどの場所にも配置することができます。

追加処理は輪の形式に対するチャネルで行うことができます。輪はX0から始まらなければならず、Y0だけを使用します。輪は4つのチャネルを使用します。

# 3.2. QWheelの許可/禁止

輪は4つ全てのチャネルに対して非0の集中長を設定することによって許可することができます。 全チャネルに対する0の集中長は輪感知器を禁止します。

# 4. ハート・ウェアと機能

# <mark>4.1.</mark> 配列走査の流れ

回路はチャネル毎に各チャネルを連続的に走査することによって動きます。チャネル走査はX=0,Y=0 (チャネル0)の位置で始まります。例えこれが実際の配線を反映していなくても、X軸チャネルは行と して知られ、一方Y軸チャネルは列として参照されます。チャネルは行によって連続的に、例えば X0Y0,X1Y0,~X3Y0の流れで走査されます。チャネルは0~3でも番号付けされます。チャネル0は X0Y0に置かれます。表4-1.はチャネル番号付けを示します。

| 表4-1. チャネル番号付け |    |    |    |    |        |  |  |  |  |  |

|----------------|----|----|----|----|--------|--|--|--|--|--|

|                | Х3 | X2 | X1 | X0 |        |  |  |  |  |  |

| Y0             | 3  | 2  | 1  | 0  | チャネル番号 |  |  |  |  |  |

# AVR254

# AVR254

各チャネルは長さが構成設定パラメータのBL(表8-1.、これは輪に対して設定することができます。)によって決められる取得パルスの集中内 で採取されます。チャネルに対する集中は次のチャネルが採取される前に完了され、各集中の最後で結果の信号がデジタル形式に変換さ れて処理されます。集中長はチャネル利得に直接影響します。チャネル毎の基本的なチャネル感度の誂えを許すために、各チャネルは独自の 集中長を持つことができます。

### 4.2. 集中

接触検出のための測定が後続する全てのチャネルに対する集中が行われ、その後にデバイスは固定の16msの時間休止にされ、そして この周回が続きます。これは電池動作応用での消費電力低減に行われます。

# 4.3. Cs採取コンデンサの動作

Cs採取コンデンサ(Cs0)は各Xパルスの上昇端でチャネル電極からの充電を吸収します。Xの各下降端で、Y配列線は次のパルスの準備で中立への充電を電極と配線に許すためにGNDへ留め置きます。各Xパルスで充電がCsに累積し、その差電圧で階段状の増加を引き起こします。

集中完了後、デバイスはY線をGNDに留め置いて、逆端子を負に行かせます。0交差が達成されるまで負端子を上に向かって傾斜するため、Cs上の充電がその後に外部抵抗を用いて測定されます。0交差に必要とされる時間が測定結果になります。

これらのコンデンサの値は重要ではありませんが、殆どの場合で4.7μFが推奨されます。これらは10%のX7Rセラミックであるべきです。XからYへの横断容量性結合は利得を無効にして飽和することができるCsコンデンサで充分に大きな電圧です。このような場合、集中長は減少され、そして/またはCs値が増加されるべきです。4.4.項をご覧ください。

Y線が使用されない場合、それに対応するCsコンデンサは省略でき、そのピンは浮きのままにします。

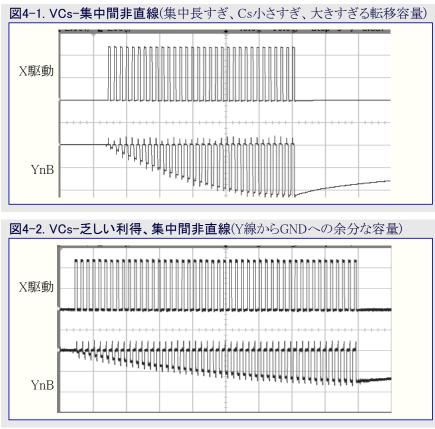

# 4.4. 採取コンデンサ飽和

YnBピンでのCs電圧飽和は図4-1.で示されます。飽和はYnBピンでの電圧が集中の最後で-0.25Vよりも負側になる時に発生を始めま す。この非直線性はピン保護ダイオート、での伝導を誘導してCsでの過度の電圧累積によって引き起こされます。この酷く飽和した信号 はチャネル利得を無効して錯覚の検出を引き起こし得る強い温度係数を持ち込みます。この場合は長すぎる集中長、小さすぎるCs値、 または大きすぎるX-Y伝達結合のどれかです。解決策にはキー構造差込を離す、PCB上のXとY線をもっと分離、Cs増加、そして集中 長減少を含みます。

Cs増加は或る程度より遅くし、集中長減少は感度を低くします。より良いPCB配置と(問題点に及ぶ)キー構造開放は負の影響を全く持ちません。Cs電圧はパネル材料に接する配列層とオシロスコープで観測されるべきで、どれかのCsのRs側がどれかの集中の間に(探針が加工してしまう行き過ぎスパイクを数えずに)-0.25Vよりももっと負に傾斜する場合、潜在的な飽和の問題があります。

図4-2.は図4-1.のそれと同様の欠点のある波形を示しますが、この場合はY線からAC接地へ過度の浮遊容量結合、例えば近すぎる 走行と遠すぎるGND側布線、GND面、または他の布線によって歪が引き起こされます。余分な結合は充電移転効果に受け取った充 電の重要部分をチャネルから浮遊容量内へ浪費させます。この現象はもっと微妙で、高い係数のようにBLを増加して波形が-0.25V以

下に向かって下がるようになるのを監視することに よって最良の検出にすることができます。波形は誤 魔化しで直線が現れますが、それは例え-0.25Vの レベルに達する前でも平坦へ緩やかに始まります。

正しい波形は図4-3.で示されます。下の軌跡の下端が(下方向スパイクを無効にする)実質上直線であることに注意してください。

他の充電移転回路と異なり、ATtiny487ァームウェアでのCsコンテンサ値は変換利得での影響を全く持ちません。けれども、それらは変換時間に影響を及ぼします。

未使用Y線は開放のままにすべきです。

注:滞在時間は最小約250nsです。4.7.項をご覧ください。

#### 4.5. 採取抵抗

各Csコンデンサで獲得した充電の単一傾斜A/D変換を実行するのに採取抵抗(Rs0)が使用されます。これらの抵抗は獲得利得を直接的に制御し、Rsのより大きな値は比例して信号利得を増加します。殆どの応用についてRsは1MΩであるべきです。 未使用Y線はRs抵抗が不要です。

#### 4.6. 信号レヘル

信号レベルは正しく設計されたキー形状とRsの値で通常200~750計数の範囲であるべきです。けれども、XからYの線の長い隣接走行 はまた信号値を不自然に増強し得て、信号飽和を引き起こし、これは避けられるべきです。XからYへの結合はXからYへの布線浮遊 結合からではなく、殆ど内部キー電極結合から来るでしょう。

最小の指接触からの信号の振れはむしろ8計数を超えて妥当な目標である12であるべきです。信号閾値設定(NTHR)は最小の接触 によって引き起こされる信号の振れ未満であることを保証される値に設定されるべきです。

集中長(BL)パラメータ増加は採取抵抗(Rs)値を増やすように、信号の強さを増すでしょう。

# 4.7. 配列直列抵抗

XからYへの配列走査線はEMC性能を改善するために直列抵抗(各々Rx0~Ex3とRy0)を使用することができます。

X駆動線はエッジ速度を減らし、従ってRF放射を減らすために殆どの場合でRxが必要です。値の範囲は1k $\Omega \sim 2k\Omega$ で、代表的に1k $\Omega$ です。

Y線はEMC感受性の問題といくつかの場合でESDを減らすのにRyが必要です。代表的にY値は約1kΩです。Y抵抗はCsコンデンサと で普通の低域通過濾波器を形成することによって雑音感受性の問題を減らすように働きます。

RxとRyの抵抗とCsコンデンサがチップの非常に近くへ配置されることが重要です。数mmよりも多く離れたこれらの部品配置は、部品とチップ間の布線長がRFアンテナとして働く原因になるため、回路に(20MHz以上の)高周波数妨害の問題を招きます。

RxとRyの上限は信号レヘール、従ってキーの感度が明らかに減らされた時に達します。RxとRyの限度はキー形状と浮遊容量に依存し、 従って両方の最適値を決めるのにオシロスコープが必要とされます。

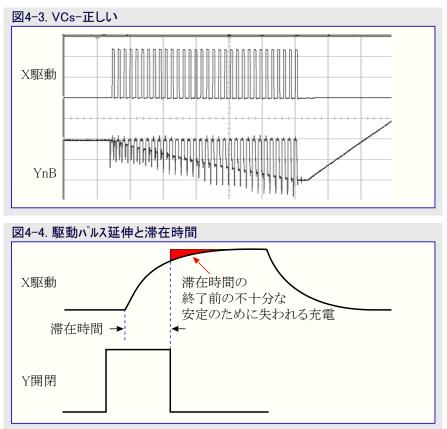

XからYへの充電結合の持続時間である滞在時間は図4-4.で示されるように捕らえられます。Rx値増加はXパルスの先行端に延伸増加を引き起こし、チャネルから捕らえられる充電の損失(従ってそれと信号強度の損失)を引き起こします。

滞在時間は最小250nsです。Xパルスが250ns内に安定されなかった場合、チャネル利得は減らされ、これが起きた場合、(配置変更、例 えばX線がGND面または布線の近くに晒されるのを減らすことによってX線での浮遊容量が減らされるべきか、またはRx抵抗が値を 減らされることが必要か(、または両方の策の組み合わせ)のどれかです。

# AVR254

4

X線安定時間を決める1つの方法はキー上で金属箔の破片または小さな硬貨を 用いて監視することです(図4-5.)。特定のX線に沿った1つのキーだけを観測す ることが必要で、250nsの滞在時間は25%以上のXパルスの安定で観測された 95%を超えるべきではありません。

殆ど全ての場合で、RyはRxに等しく設定されるべきで、そしてこれはY線での 充電がCsコンデンサ内へ完全に捕らえられることを保証します。

#### 図4-5. 硬貨でのX駆動波形探査

#### 4.8. QWheel設定

チャネルの群は輪(Wheel)として形態設定することができます。輪は配列のY0線を使用し、連続する番号順で配置されたチャネルでX0で 始まらなければなりません。輪はX0Y0として始まる最初のチャネル、X1Y0の2つ目のチャネル、3つ目のX2Y0と4つ目のX3Y0を持つY0線 上の4つのチャネルから成ります。

報告される位置の安定性は輪チャネル上の信号の量に依存します。厚いパネルを持つ、より高い分解能での動きは、変動する報告位置を生成するかもしれません。

#### 4.9. PCB配置、構造

#### 4.9.1. 概要

XとYの布線長を減らすようにして同じPCB上でキーをチップ近くに配置することが最良で、それによってEMCの問題に関する可能性を 減らします。長い接続布線はRFアンテナのように働きます。Y(受け取り)線はX(駆動)線よりもずっと多く雑音を拾う可能性があります。よ りずっと重要なことは、個別部品(抵抗とコンデンサ)に関係する全ての信号をチップ本体の非常に近くにすべきです。チップと様々な抵抗 とコンデンサ間の配線は雑音を拾うのを抑制するために可能な限り短く直進にすべきです。

使用される場合、GND面(層)はチップ。自体と回路内で提携する抵抗とコンデンサの下または周囲、電源の下または周囲、それとコネクタの 裏に配置されるべきです。GND面は輻射された雑音に対する防御に使用することができますが、先に記述されたように感度に於ける 減少を犠牲にしてです。

注: GND層/面使用時、Y線の寄生容量は充電移転効果減少になり得ます。雑音抑制のため、GND層/面は有益な周囲とPCBの接触側でのキー間にすることができます。けれども、寄生容量を減らすために層/面から最も離れるPCB層でY線を布線することが賢明です。網目GND面は効果的な防御として働き、同時に寄生容量低減を手助けします。チップ周辺のGND層/面はY線寄生と同じ考慮に注意して一般的に受け入れ可能です。

#### 4.9.2. LED布線と他の切り替え信号

Y線近くのデジタル切り替え信号は、デバイスのSNR性能を低下する、獲得した信号内への瞬間雑音を含みます。このような信号はY線から離して配置されるべき、または設計が信号獲得の進行(集中)中にそれらの線が切り換えられないようにすべきです。

浮き状態に多重化または切り換えられ、(例え近くの別のPCBでも)物理的にキー構造へ非常に近いLED電極は誤った信号移動を引き 起こし得る容量結合効果を抑制するために最低0.01μFでVSSまたはVDDのどちらかに迂回されるべきです。迂回コンデンサはLEDの傍 に必要ではなく、実際それはかなり遠くにすることができます。迂回コンデンサは重要ではなく、どの形式の物にもできます。

VSSまたはVDDへ定常的に接続されるLED電極は更なる迂回は必要ありません。

#### 4.9.3. 布線

チップの下側の中央パットはGNDに接続されるべきです。チップの本体の下近くはGNDだけで、どんな布線も走ってはいけません。

#

#### 4.9.4. PCBの綺麗さ

全ての容量性感知器は浮遊導電性漏れ経路によって影響を及ぼされ得る高感度の回路として扱われるべきです。充電移転デバイス はfF(フェムト ファラッド、フェムトは10<sup>-15</sup>、p(ピコ)の1/1000)範囲での基本分解能を持ち、この領域では、「綺麗な溶融促進剤(フラックス)」のような 物はありません。溶融促進剤は水分を吸収し、半田接続間の導電体になり、信号変動と結果として生じる誤った検出、感度の一時的 な損失や不安定性を引き起こします。絶縁保護被膜はその後に高い温度過敏になる既存水分量を防ぎます。

設計者は製造処理の一部として超音波洗浄を、そして高レベルの湿気が予期される場所の場合、湿気を締め出すための洗浄後に絶縁保護被膜の使用を指定すべきです。

#### 4.10. 電源の考慮

VDD範囲と短期的な電源変動については10.2.項をご覧ください。電源が温度で緩やかに変動する場合、デバイスは感度での微細な変更だけでそれらの変化に対して自動的に探査して補償するでしょう。供給電圧が素早く変動または移動する場合、移動補償機構が維持できなくなり、感度例外や誤った検出を引き起こします。

デバイスがアナログ基準として電源それ自体を使用するため、電力は非常に綺麗で独立した調整器から来るべきです。標準的な安価な 低損失(LDO)型調整器が使用されるべきで、またそれはLED、継電器、または他の高電流デバイスのような他の負荷の電力に使用さ れません。LDOの出力での負荷変動は誤った検出や感度移動をさせるのに充分な変動をVDDに引き起こします。

注意:他の論理デバイスと共用される調整器ICは突飛な動作に帰着し得て、これは推奨されません。

調整器は1つの基板上の複数の充電移転デバイスの間で共用することができます。短い布線で単一の0.1µFセラミック迂回コンデンサはIC の3番と4番の供給ピンの非常に近くに配置されるべきです。そうしないことはデバイス発振、高消費電流、突飛な動作などに帰着し得 ます。16番と17番のピンはそれらのピンと電力布線間が短絡していれば、迂回の必要がありません。

#### 4.11. 始動/校正時間

デバイスは概ね70msの初期化時間が必要です。この始動期間が終わった後、CHANGEがLowになり、校正が始まります(15配列走査かかります)。

#### 4.12. 校正

校正は周期的に起きません。輪は通電と以下の時にだけ校正されます。

- 許可

- そして

- 信号 / 値が基準値+負閾値の3/4として定義された正閾値よりも大きい

または

6

- 使用者が再校正命令を発行

### 4.13. リセット入力

デバイスとの通信が失われてデバイスを既知の状態に持ってくるために、パワーダウン動作形態をシミュレートするようにデバイスをリセットするの にRSTを使用することができます。このピンはLow活性で、リセットを起こすにはこのピンに最低10μs持続するパルスが印加されなければな りません。外部ハートウェアリセットが使用されない場合、リセット ピンはVDDに接続することができます。

# AVR254

**AVR254**

## 4.14. 検出積分部

デバイスは強健な流儀で検出を確定するために働く、検出積分機構が特徴です。キー毎の計数器はキーがそれの閾値を越える毎に増やされ、獲得数のためにそれらに留まります。この計数器が予め設定された限度に達する時にキーは最終的に接触を宣言されます。 例えば、限度の値が10の場合、デバイスはキーが接触を宣言されるのに先立って、閾値以下になることなく、連続で閾値を超えて10回の獲得のためにそれらへ留まらなければなりません。どの獲得でも信号が閾値レベルを超えたように見えない場合、計数器は解除されて処理は始めから開始されなければなりません。

#### 4.15. 休止

デバイスは電力を浪費しないように測定の組を実行してその後に16ms(既定値)間休止し、低電力(LP)動作形態がいくつかの他の値に 変更されない限り、この周回が繰り返しを維持されます。

低電力(LP)動作形態と休止動作形態の使用者定義可能な2つ休止形態があります。LP設定は7.9.項で示されるように電力を浪費しないために使用されます。これは変動補償を行うためにどれ位の頻度でデバイスが起き上がるかを決めます。それは不活性後の最初の接触に対する最大応用時間も決めます。

有効な接触が記録されると、デバイスは輪接触に対するより速い応答のために既定休止時間(16ms)に移行します。デバイスは輪が接触 と開放をされつつあるように見えることが続く場合に、この動作形態に留まります。0の低電力設定は測定が全く実行されない超低電 力動作形態(SLEEP)へ移行します。SLEEP動作形態は内部ウォッチトックゲタイマも停止し、故にデバイスは総合的に休止状態にあり、流出 電流は<3μAです。

TWIベス上でアドレス一致がある、RSTピンでのリセット、またはLP動作形態が設定される場合に、ATtiny48に独自化されたファームウェアが SLEEP動作形態から起き上がります。

#### 4.16. 配線

#### 提案される調整器製造業者は以下です。

• TOKO(XC6215系統)、SEIKO(S817系統)、BCD Semi(AP2121系統)

:3頁の4.3.項

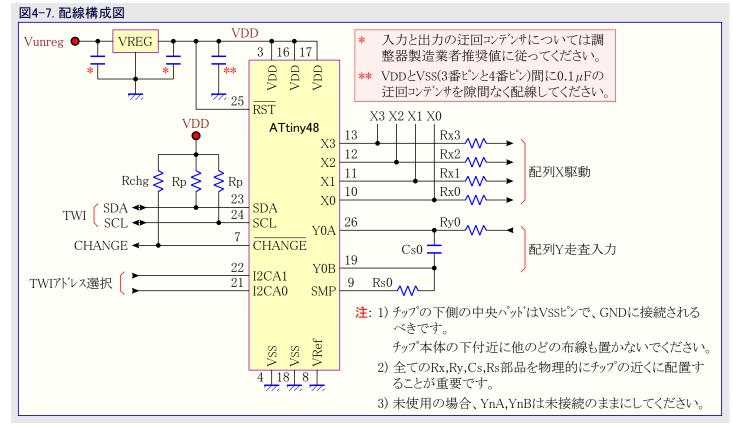

図4-7.での部品の値については以下の項を調べてください。

- ・Csコンデンサ(Cs0)

- ・採取抵抗(Rs0) : 4頁の4.5.項

- ・配列抵抗(Rx0~Rx3,Ry0) : 4頁の4.7.項

- ・電圧レベル : 6頁の4.10.項

- ・SDA,SLCプルアップ抵抗(Rp):10頁の6.4.項

- ・CHANGE抵抗(Rchg) : 10頁の6.5.項

- ・TWI一致アドレス : 9頁の6.2.項

# 5. TWI(Two-wire Serial Interface、2線直列インターフェース)バス動作

# 5.1. インターフェース バス

PhilipsのI<sup>2</sup>Cハズ/規約に適合するATMELのTWI(2線直列インターフェース)についてのより多くの詳細な情報は、ATMELの公式ウェブサイトの http://www.atmel.com/dyn/resources/prod\_documents/doc2565.pdf で入手可能です。

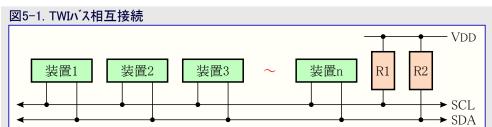

TWI規約はクロック(SCL)に対する1つとデータ(SDA)に対する1つで、2つの双方向ハス線だけを用いて128個までの異なる装置の相互接 続をシステム設計者に許します。ハスの実装に必要な外部部品はTWIハス線の各々に対する単一のプルアップ抵抗だけです。ハスに接続 された全ての装置は個別のアドレスを持ち、ハス競合を解決するための機構がTWI規約で本質的に備わっています。装置は図5-1.で 示されるようにハス上に接続されます。これは同時にハスを駆動することをどれにもそして全てに許すワイアードAND機能を実装します。 ハス上のLowレヘルは装置が0を出力する時に生成されます。

| 表5-1. TWIバス仕様        |         |  |  |  |  |  |  |

|----------------------|---------|--|--|--|--|--|--|

| n°ラメータ               | 単位      |  |  |  |  |  |  |

| アドレス空間               | 7ピット    |  |  |  |  |  |  |

| 最大バス速度(SCL)          | 100kHz  |  |  |  |  |  |  |

| 開始条件保持時間             | 最小4µs   |  |  |  |  |  |  |

| 停止条件構成時間             | 最小4µs   |  |  |  |  |  |  |

| 停止条件と停止条件間のバス空き間保持時間 | 最小4.7μs |  |  |  |  |  |  |

| SDAとSCLでの上昇時間        | 最大1µs   |  |  |  |  |  |  |

# 5.2. データビットの転送

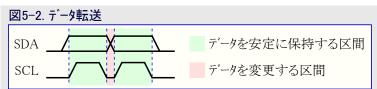

ヾス上で転送される各データビットはクロック線上のパルスと連携されます。データ線のレヘールはクロック線がHighの時に安定でなければなりません。この規則の唯一の例外は開始条件と停止条件を生成する時です。

# 5.3. 開始条件と停止条件

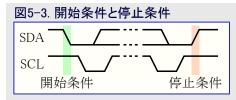

ホストはデータ送信を始めてそして終わります。送信はホストがハ、ス上で開始条件を発行する時に始められ、ホストが停止条件を発行することで終了されます。開始条件と停止条件の間、ハ、スは多忙と見做されます。右で示されるように、開始条件と停止条件はSCL線がHighの時のSDA線のレヘルを変更することによって合図されます。

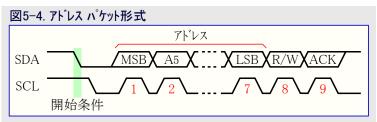

# 5.4. アドレス パケット形式

全てのアドレス パケットは7つのアドレス ビット、1つの読み/書き(R/W)ビット、それと応答ビットから成る9ビット長です。 読み/書き(R/W)ビットが 設定(1)されるなら、読み込み操作が実行され、さもなければ書き込み操作が実行されます。 装置がアドレス指定されつつあることを認 証すると、それは第9 SCL(ACK)周期でSDAをLowに引くことによって応答されます。 従装置アドレスと読みまたは書きのビットから成るア ドレス パケットは各々、SLA+RまたはSLA+Wと呼ばれます。

アト・レス ハ・イトの最上位ビット(MSB)が先に送信されます。ホストに よって送られたアト・レスは任意選択のシ・ャンハ。で選択されたものと 一致しなければなりません。

AVR254

8

AVR254

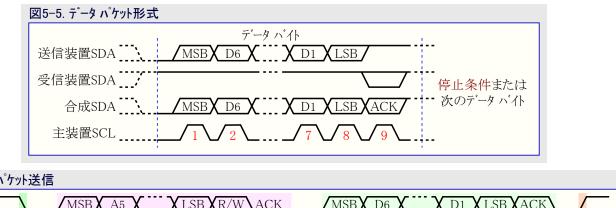

# 5.5. データ パケット形式

全てのデータパケットは1つのデータハイトと応答ビットから成る9ビット長です。データ転送中、ホストはクロック、そして開始条件と停止条件を生 成し、一方受信側にはその受信に応答する責任があります。応答(ACK)は第9 SCL周期中に受信側がSDA線をLowに引くことによっ て合図されます。受信側がSDA線をHighのままにする場合、否定応答(NACK)が合図されます。

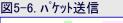

# 5.6. 送信でのアドレスとデータのパケットの結合

送信は開始条件、SLA+R/W、1つ以上のデータ パケット、停止条件から成ります。ホストと装置間のハント・シェークを実装するためにSCL線の ワイアードANDが使用されます。装置はデータ転送間での処理のために追加時間が必要な時に必ずSCL線をLowに引くことによって SCLのLow区間を延長します。

クロック伸長または他の何れかの目的のためにSCLまたはSDAのどちらかを保持することはATtinv48ファームウェアの動作を遅くします。 SCLまたはSDAが約12msよりも長く継続的にLowを保持される場合、これは異常状態として考えられ、TWI適合部がリセットします。

注:書き込みまたは読み込みの各周回は停止条件で終わらなければなりません。ATtiny48ファームウェアはその周回が新しい開始条件 によって終了される場合に正しく応答しないかもしれません。

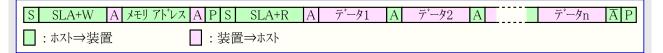

図5-6.は代表的なデータ送信を示します。SLA+R/Wと停止条件間で多数のデータハイトを送信できることに注意してください。

| SDA  | MSBX A5 X XLSBXR/W ACK | MSBX D6 X X D1 XLSB XACK |

|------|------------------------|--------------------------|

| SCL  |                        |                          |

| 開始条件 | SLA+R/W                | データバイト 停止条件              |

# 6. インターフェース

# 6.1. TWI(2線インターフェース)規約

TWI(2-wire interface)規約はアドレス表へのアクセスに基づき、複数バイトの読みと書きを支援します。

注:書き込みまたは読み込みの各周回は停止条件で終わらなければなりません。ATtiny48ファームウェアは周回が新しい開始条件で終 了される場合に正しく応答しないかもしれません。

# 6.2. TWI- 致アトレス

予め設定された4つのTWI(I<sup>2</sup>C-致)アドレスはI2CA1とI2CA0のピンを通して選択可能です(表6-1.)。

| <u>表6-1. TWI一致アドレス</u> |       |      |  |  |  |  |  |  |  |

|------------------------|-------|------|--|--|--|--|--|--|--|

| I2CA1                  | I2CA1 | アドレス |  |  |  |  |  |  |  |

| 0                      | 0     | \$0D |  |  |  |  |  |  |  |

| 0                      | 1     | \$17 |  |  |  |  |  |  |  |

| 1                      | 0     | \$44 |  |  |  |  |  |  |  |

| 1                      | 1     | \$6B |  |  |  |  |  |  |  |

# 6.3. データの読み/書き

#### 6.3.1. 装置へのデータ書き込み

装置へのデータ書き込みに必要とされる事象の流れが次に示されます。

| S SLA+W   | А | メモリ アト・レス | А | データ    | AP |

|-----------|---|-----------|---|--------|----|

| □: ホスト⇒装置 | Ē |           |   | :装置⇒ホン | ላኮ |

| 略語        | 意味              |

|-----------|-----------------|

| S         | 開始条件            |

| SLA+W     | 従装置アドレス+書き込みビット |

| А         | 応答ビット           |

| メモリ アト・レス | 装置内の目的対象メモリアドレス |

| データ       | 書かれるべきデータ       |

| Р         | 停止条件            |

ホストは開始条件を送ることによって転送を始め、書き込み(W)ビットと共に装置の従装置アトレスを送ることによってこれに後続します。装置は応答(ACK)を送ります。その後にホストはそこへ書こうとする装置内のメモリアトレスを送ります。装置はACKを送ります。

ホストは1つ以上のデータバイを送り、その各々は装置によって応答されます。

ホストが複数のデータ バイトを送る場合、それらは連続するメモリ アドレスに書かれます。装置は各データ バイト書き込み後に目的対象のメモリ アドレスを自動的に増加します。最後のデータ バイト書き込み後、ホストは停止条件を送るべきです。

装置は255を超えて内部メモリ アドレスを増加しないため、ホストはアドレス 255を超えて書こうとすべきではありません。

#### 6.3.2. 装置からのデータ読み込み

装置からのデータ読み込みに必要とされる事象の流れが次に示されます。

ホストは開始条件を送ることによって転送を始め、書き込み(W)ビットと共に装置の従装置アトレスを送ることによってこれに後続します。装置は応答(ACK)を送ります。その後にホストはそこへ書こうとする装置内のメモリアトレスを送ります。装置はACKを送ります。

ホストはその後に再び従装置アドレスが後続する停止条件と開始条件を送らなければなりませんが、この時は読み込み(R)ビットによって 伴われます。装置はデータハイトが後続するACKを返します。ホストはACKまたはNACKのどちらかを返さなければなりません。ホストが ACKを返す場合、装置は次のアドレスからのデータハイトを続けて送信します。データハイトが送信される毎に装置は内部的なアドレスを自 動的に増加します。装置はホストがNACKで応答するまでデータハイトを返し続けます。ホストは停止条件を発行することによって転送を 終了すべきです

#### 6.4. SDAŁSCL

TWI(I<sup>2</sup>C適合)バスはデータを転送し、SDAとSCLでクロック駆動されます。それらはオープンドレイン、即ちTWI主装置と従装置はそれらの線をLowまたはそれらを開放のままにすることだけができます。

終端抵抗(Rp)はTWI(I<sup>2</sup>C適合)装置がそれを(Lowに)引き下げない場合に線をVDDに引き上げます。

終端抵抗は一般的に1kΩ~10kΩの範囲で、SDAとSCLでの上昇時間がTWI仕様(最大1µs)に合うように選ばれるべきです。

### 6.5. CHANGEピン

CHANGEピンはホストの4つの状態ハイト(アトレス2~5)のどれかの何らかの変更の警告、従って無駄なTWI適合通信の必要性を減らすの に使用することができます。ATtiny48ファームウェア設定後、ホストはCHANGEピンが活性になる時を除いて、装置と通信することができま せん。

ホ자が変更された全ての状態バイトの読み込みを実行する時にだけ、CHANGEは再び不活性になります。

ポーリング速度:ホストは通信を始めるのにCHANGEビン出力を使用することができ、これは最適なポーリング速度を保証します。

ホストがCHANGEピンを使用することができない場合、ポーリング速度は配列走査毎に1度よりも速くならなくなるべきです(10.3.項をご覧く ださい)。より速い何もが新しい情報を提供せず、チップ動作を減速させるでしょう。

CHANGEピンは代表値約100kΩのプルアップ抵抗が必要です。

10

# 7. 通信規約

# 7.1. 始めに

装置はアドレス割り当てされます。全ての通信は8ビット アドレス割り 当て内の位置への書き込みと、そこからの読み込みから成りま す。表7-1.はATtiny48独自化ファームウェアのアドレス割り当てを示し ます。

| 表7-1. メモリ割り当て |

|---------------|

|---------------|

| 夜/~1. たり刮り当て |                |           |  |  |  |  |  |  |

|--------------|----------------|-----------|--|--|--|--|--|--|

| アト・レス        | 使用内容           | アクセス      |  |  |  |  |  |  |

| 0            | チップ『D          | 読み込み      |  |  |  |  |  |  |

| 1            | 主/副コード版番号      | 読み込み      |  |  |  |  |  |  |

| 2            | 全般状態           | 読み込み      |  |  |  |  |  |  |

| 3            | 輪接触状態          | 読み込み      |  |  |  |  |  |  |

| 4,5          | 輪接触位置          | 読み込み      |  |  |  |  |  |  |

| 6            | 校正             | 読み込み/書き込み |  |  |  |  |  |  |

| 7            | リセット           | 読み込み/書き込み |  |  |  |  |  |  |

| 8            | 低電力(LP)動作形態    | 読み込み/書き込み |  |  |  |  |  |  |

| 9            | 検出完全性 (DI)     | 読み込み/書き込み |  |  |  |  |  |  |

| 10           | 負閾値            | 読み込み/書き込み |  |  |  |  |  |  |

| 11~14        | チャネル0~3に対する集中長 | 読み込み/書き込み |  |  |  |  |  |  |

| $15 \sim 22$ | チャネル0~3信号      | 読み込み      |  |  |  |  |  |  |

| 23~30        | チャネル0~3基準      | 読み込み      |  |  |  |  |  |  |

| 31,32        | 輪差()           | 読み込み      |  |  |  |  |  |  |

## 7.2. アト・レス 0 : チッフ ID

\$0Bに設定される8ビットのチップIDがあ ります。

| 表7-2. チップID |      |                     |      |      |      |      |      |      |  |

|-------------|------|---------------------|------|------|------|------|------|------|--|

| アトレスヘビット    | ビット7 | ビット6                | ビット5 | ビット4 | ビット3 | ビット2 | ビット1 | ビットロ |  |

| 0           |      | チップ <sup>°</sup> ID |      |      |      |      |      |      |  |

### 7.3. アドレス 1 : コード版番号

ファームウェア コード改訂の8ビットの主と副の版番号があります。ファームウェア版レジスタの上位ニブルは主版番号(例えば、1.0)を含み、下位側 ニブルは副版番号(例えば、0.7)を含みます現在のファームウェア版番号は1.7です。 故に版番号を読む時にその値は版番号1.7として識 別される\$17でしょう。

| 表7-3. コード版番号 |      |      |      |      |                             |  |  |  |  |  |

|--------------|------|------|------|------|-----------------------------|--|--|--|--|--|

| アトレス、ビット     | ビット7 | ビット6 | ビット5 | ビット4 | <u> ビット3 ビット2 ビット1 ビット0</u> |  |  |  |  |  |

| 1            | 主版番号 |      |      |      | 副版番号                        |  |  |  |  |  |

# 7.4. アドレス 2: 全般状態

| これらのビットは装置の全般状態を示   |          |       |      |      |      |      |      |      |      |

|---------------------|----------|-------|------|------|------|------|------|------|------|

| します。このバイトの変更がCHANGE | アトレス、ビット | ビット7  | ビット6 | ビット5 | ビット4 | ビット3 | ビット2 | ビット1 | ビットロ |

| 線を起動させます。           | 2        | RESET | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

RESET: このビットはリセット後に設定(1)されます。このビットはこのハイトがホストによって読み戻された後に解除(0)されます。

# 7.5. アドレス 3: 輪接触状態

アトレス3:輪に対する検出接触状態

| 1 | 表7-5. 輪接触状態 |             |      |      |      |      |      |      |      |

|---|-------------|-------------|------|------|------|------|------|------|------|

|   | アドレス\ビット    | ビット7        | ビット6 | ビット5 | ビット4 | ビット3 | ビット2 | ビット1 | ビットロ |

|   | 3           | 接触状態(0または1) |      |      |      |      |      |      |      |

このアドレス位置は検出に於ける輪を示し、接触された輪は"1"として報告し、非接触または禁止された輪は"0"として報告します。この バイトの変化はCHANGE線を起動させます。

# 7.6. アドレス 4,5 : 輪接触位置

| 表7-6. 輪接触 | 長7−6. 輪接触位置 |  |  |  |  |  |  |

|-----------|-------------|--|--|--|--|--|--|

| アドレス∖項目   | 值           |  |  |  |  |  |  |

| 4,5       | 位置          |  |  |  |  |  |  |

#### 位置:輪での接触の最後の位置。

このバイトの変更はCHANGE線を起動させます。

#### 7.7. アドレス 6 : 校正

| 表 | 7-7. 校正 |      |      |      |      |      |      |      |      |

|---|---------|------|------|------|------|------|------|------|------|

| 7 | ドレス\ビット | ビット7 | ビット6 | ビット5 | ビット4 | ビット3 | ビット2 | ビット1 | ビットロ |

|   | 6       | 校正   |      |      |      |      |      |      |      |

このアドレスへの0以外の値の書き込みは輪上での再校正を開始するようにATtiny48ファームウェアを起動します。

### 7.8. アト・レス 7 : リセット

| 表7-8. リセット |       |      |      |      |      |      |      |      |

|------------|-------|------|------|------|------|------|------|------|

| アドレス\ビット   | ビット7  | ビット6 | ビット5 | ビット4 | ビット3 | ビット2 | ビット1 | ビットロ |

| 7          | IJセット |      |      |      |      |      |      |      |

1の値書き込みは装置のリセットを起動します。リセット後、装置は既定設定に復帰します。

リセット命令受信後、ATtiny48ファームウェアはTWI(I<sup>2</sup>C適合)通信に否定応答を開始し、16ms内でCHANGEを不活性にします。チップは別の約16ms後にリセットします。

## 7.9. アトレス 8: 低電力(LP)動作形態

| 表 | 表7-9. LP動作形態 |                   |      |      |      |      |      |      |      |

|---|--------------|-------------------|------|------|------|------|------|------|------|

| 7 | ドレス\ビット      | ビット7              | ビット6 | ビット5 | ビット4 | ビット3 | ビット2 | ビット1 | ビットロ |

|   | 8            | 低電力動作形態 (LP_MODE) |      |      |      |      |      |      |      |

LP動作形態は集中と集中の間の時間を休止に設定します。より大きな値はより低い電力消費に帰着する獲得間の間の時間でより多く休止にさせますが、より遅い応答時間にします。

値は次に与えられる或る値によって各々が休止時間を増す、0~7間です。例えば、1=16ms LP、2=32ms LP、3=64ms LP、4=125ms LP、5=250ms LP、6=500ms LP、7=1000ms LPなどです。

0の値はデバイスを測定が全く実行されない超低電力(SLEEP)動作形態にさせます。

ATtiny48独自化されたファームウェアが休止からの起き上がりにウォッチトックタイマを使用するので、故に休止タイミングはウォッチトックタイマ前 置分周器値に基づいてATtiny48デバイスに関して利用可能なウォッチトック時間経過周期によって決められます。ATtiny48ファームウェアは 電力を浪費しないように可能な限り多く休止するように設計されます。

注:より長いLP動作形態は最初の接触でのより長い応答時間です。最初の接触に対する応用時間はデジタル濾波器安定時間(数測 定周回)とDI処理を含みます。256ms以上のLP動作形態は例えより長いLP動作形態期間でも、消費電力がそれに応じて減りま せん。代表的な消費電力については表10-1.を参照してください。

**既定值**:1(16ms LP)

### 7.10. アドレス 9: 検出積分値

| 表7-10. 検出積分値 |      |      |      |      |      |      |      |      |

|--------------|------|------|------|------|------|------|------|------|

| アドレス\ビット     | ビット7 | ビット6 | ビット5 | ビット4 | ビット3 | ビット2 | ビット1 | ビットロ |

| 9            | 0    | 0    | 0    |      |      | NDIL |      |      |

#### NDILは信号濾波の提供に使用されます。

電気的な雑音のような偽の事象によって引き起こされる誤った検出を抑制するために、デバイスは'検出積分器'またはDI計数器機構 を組み入れます。検知器毎の計数器は感知器がそれの閾値を越える毎に増加され、閾値レヘル以下になることなく、連続での獲得数 をそこに止められます。この計数器は予め設定された限度に達すると、感知器は接触されたことを最終的に宣言されます。

何れかの獲得で信号が閾値レベルを超えるように見えない場合、計数器が解除されて処理が始めから開始されなければなりません。 ATtiny48ファームウェアはNDIL値に加えて最小1 DI計数を組み入れます。従って、3のNDIL値設定の場合、実際の連続する獲得数は4 です。

利用可能なNDIL値は1~31です。既定値:3(4 DI値)

## 7.11. アドレス 10 : 負閾値

| 表7-11. 負閾値    |          |      |      |      |      |      |      |      |      |

|---------------|----------|------|------|------|------|------|------|------|------|

|               | アトレスヘビット | ビット7 | ビット6 | ビット5 | ビット4 | ビット3 | ビット2 | ビット1 | ビットロ |

| 10 負閾値 (NTHR) |          |      |      |      |      |      |      |      |      |

負閾値はチャネルの信号基準値に比例して確定されます。この閾値は検出積分器によって濾波された後で負になる信号の振れによっ て横切られた時の感知器接触を決めるのに使用されます。 閾値のより大きな絶対値は、閾値レベルを横切るために信号が更に遠くへ 移らなければならないため、感知器の感度を減らします。

逆に、より低い閾値は感知器をより高感度にします。

CxとCsの変動のため、使用者設定可能な速度でこれらの変化に対して変動補償する基準点である閾値レベルは、基準点が動く時に 必ず再計算され、従ってそれも変動補償されます。

必要とされるNTHRの量は感知器が接触された時に起こる信号の振れる量に依存します。より厚いパネルやより小さなチャネル平面は「チャネル利得」、換言すると接触からの信号の振れを減らし、従って接触検出により小さなNTHR値が必要です。

負ヒステリシス:これは負閾値よりも2つ小さく固定され、変えることができません。これは検出内外での振るえからキーを止めるために実装されます。

NTHR代表值:5~12

NTHR既定值:10(閾値の10計数)

#### 7.12. アドレス 11~14:集中長

| 表7-12. 集中長 |          |      |      |      |      |      |      |      |

|------------|----------|------|------|------|------|------|------|------|

| アトレス、ビット   | ビット7     | ビット6 | ビット5 | ビット4 | ビット3 | ビット2 | ビット1 | ビットロ |

| 11~14      | 集中長 (BL) |      |      |      |      |      |      |      |

ATtiny487ァームウェアは集中動作形態で実行される固定のパルス数を使用します。この数値は4つの群で設定されます。従って、ATtiny 487ァームウェアへ送られる値は実際の集中パルス数を得るために4倍にされます。

集中長は与えられたチャネルで実行される充電移転処理の回数です。各充電移転処理はチャネルの容量Cxを通して渡された結果の充電を捕らえるための、対応する許可されたY線とでの単なる一度のX線のパルス出力です。

集中長の増加は直接的にチャネル感度に影響を及ぼします。これは充電積分器内の充電の累積が直接的に集中長へ繋げられるため に起きます。各チャネルの集中長は個別に設定できませんが、輪感知器によって使用される全てのチャネルに対して同じ集中長を順に設 定する全体として輪感知器に対して設定することができます(この場合の輪は4つのチャネルから成ります)。

見かけの接触感度は負閾値レベル(NTHR)によっても制御されます。集中長とNTHRの相互作用は、通常、走査時間を減らしてRF放射を制限するために集中長が可能な限り短く保たれるべきで、しかしNTHRは外部雑音のための誤った検出を減らすために6以上を保たれるべきです。検出積分器機構も誤った検出を防ぐのを助けます。

使用者はメモリ割り当てアドレスの11~14から始まる輪を構成する各チャネルの集中長を設定することができます。 チャネル0の集中長はアドレ ス 0、 チャネル1は12、 チャネル2は13、 チャネル4は14に割り当てられます。

代表値:8~32(32=128個の集中パルス)

既定値:16(64個の集中パルス)

#### 7.13. アドレス 15~30: 信号と基準

アドレス 15~22は各チャネルに対して読まれべき信号データを許します。各チャネルに対して2バイトのデータがあります。これらはLSBが先に格 納される2つの(8ビットの)バイトとしてアクセスされる、チャネルの16ビット信号です。 輪に対して4つのチャネルを持つので、故に信号値に対応し て8つのアドレスが割り当てられます。

アドレス 23~30は各チャネルに対して読まれるべき基準データを許します。各チャネルに対して2バイトのデータがあります。これらはLSBが先に 格納される2つの(8ビットの)バイトとしてアクセスされる、チャネルの16ビット基準です。輪に対して4つのチャネルを持つので、故に基準値に対応 して8つのアドレスが割り当てられます。

合計4チャネルとチャネル毎に4バイトのデータがあり、合計16個のアドレスを与えます。これらのアドレスは読み込み専用です。

| 夜/~13. 信方と本华 |        |              |              |        |              |  |  |  |

|--------------|--------|--------------|--------------|--------|--------------|--|--|--|

| アトレス         | チャネル番号 | 使用内容         | アトレス         | チャネル番号 | 使用内容         |  |  |  |

| 15           | 0      | 信号下位バイト(LSB) | 23           | 0      | 基準下位バイト(LSB) |  |  |  |

| 16           | 0      | 信号上位ハイト(MSB) | 24           | 0      | 基準上位バイト(MSB) |  |  |  |

| $17 \sim 22$ | 1~3    | チャネル1~3の信号   | $25 \sim 30$ | 1~3    | チャネル1~3の基準   |  |  |  |

表7-13. 信号と基準

# 7.14. アドレス 31,32 : 差(/)

アドレスの31,32は輪に対して読まれるべき⊿データを許します。輪の⊿に対して2ハイトのデータがあります。これらはLSBが先に格納される2つの(8ビットの)ハイトとしてアクセスされる、チャネルの16ビット(基準-信号)値です。ファームウェアでは全てのチャネルに対する⊿が計算され、その後の算術演算後に輪に対する⊿を与えます。

| 表7-14. 信号⊿ |     |        |  |  |  |  |  |

|------------|-----|--------|--|--|--|--|--|

| アト・レス      | 輪番号 | 使用内容   |  |  |  |  |  |

| 31,32      | 0   | 差(∠))値 |  |  |  |  |  |

# 8. 構成設定部

構成設定データはTWI(I<sup>2</sup>C適合)インターフェースを使用してホストからATtiny48独自化ファームウェアへ送られます。構成設定部はこのインターフェース上でメモリ割り当てされます。従って各構成設定は適切なアトレスの読み書きによってアクセスすることができます。構成設定は個別にまたは塊としてアクセスすることができます。

| 表8-1. 構成 | 表8-1. 構成設定表 |         |         |             |     |            |                                      |  |  |

|----------|-------------|---------|---------|-------------|-----|------------|--------------------------------------|--|--|

| アドレス     | バイト         | パラメータ   | シンホ゛ル   | 有効範囲        | ビット | 既定値        | 説明                                   |  |  |

| 8        | 1           | 低電力動作形態 | LP_MODE | 0~7         | 8   | 1          | 0:休止動作形態(容量性感知なし)<br>1~7:低電力動作形態     |  |  |

| 9        | 1           | 検出積分値   | DI      | $1 \sim 31$ | 8   | 4          |                                      |  |  |

| 10       | 1           | 負閾値     | NTHR    | $7 \sim 12$ | 8   | 10         |                                      |  |  |

| 11~14    | 4           | 集中長     | BL      | 0~32        | 32  | 16 (64パルス) | 全チャネルに対してBL=0なら、輪禁止<br>1~32:集中長=BL×4 |  |  |

アドレス 11~14の集中長は輪を構成する0~3の各チャネルに対してです。

# 8.1. EEPROMインターフェース

ATtiny48独自化ファームウェアは初期化時間中にEEPROM内の特定位置(アトレス \$0A) を読みます。そのアトレスの値が\$FFと等しくないことが分かった場合、EEPROMから 構成設定値を読みます。形態設定値は形態設定/構成設定の値で変更があった時 に更新されるかまたはEEPROMへ書かれます。ファームウェアはそれを調べて、次の接 触測定中に更新された値をEEPROMへ書きます。

ホストからリセット命令が来る時は必ず、装置がリセットを得てEEPROMから形態設定値を 読んで、メモリ割り当てアトレスレジスタをEEPROM値で更新します。

右表はEEPROM内に格納された全ての形態設定値と対応するEEPROMアドレスを記載します。

形態設定値は多数のEEPROMアドレスでEEPROMに格納されます。

低電力動作形態値は\$000のEEPROM位置に格納されます。DIは\$001のEEPROM 位置、負閾値は\$002、そして集中長形態設定値はチャネル0から始まりチャネル3までが \$003~\$006のEEPROMアドレス位置に格納されます。

# 8.2. 独自化されたファームウェアでのATtiny48プログラミング

ホストとの通信を持つためには、ATtiny48独自化ファームウェアがデベイス内にプログラミングされることが必要です。ファームウェアはISPを用いて、 またはJTAGコネクタを通してのどちらかでプログラミングすることができます。

# 9. ATtiny48独自化ファームウェアでの開始に際して

# 9.1. TWI(I2C適合)バスの使い方

ATtiny48独自化ファームウェアはアドレス割り当てされた部品です。全ての命令とデータの転送はメモリ位置に対する読み込みと書き込みから成ります。

# 9.2. 交信確立

装置が存在して動いていることを確定するには、そこへ0を書いてください(9.3.項をご覧ください)。そこで単一バイトを読んでください (9.4.項をご覧ください)。このバイトは装置ファームウェアのID(\$0B)であるべきです。これがそうならば装置が存在して動いてきます。

| 表8-2. | 表8−2. EEPROM内の形態設定値 |                     |  |  |  |  |  |  |  |

|-------|---------------------|---------------------|--|--|--|--|--|--|--|

| 通番    | 形態設定項目              | ΕΕΡ <b>ROM</b> アドレス |  |  |  |  |  |  |  |

| 1     | 低電力動作形態             | \$000               |  |  |  |  |  |  |  |

| 2     | 検出完全性 (DI)          | \$001               |  |  |  |  |  |  |  |

| 3     | 負閾値                 | \$002               |  |  |  |  |  |  |  |

| 4     | チャネル0の集中長           | \$003               |  |  |  |  |  |  |  |

| 5     | チャネル1の集中長           | \$004               |  |  |  |  |  |  |  |

| 6     | チャネル2の集中長           | \$005               |  |  |  |  |  |  |  |

| 7     | チャネル3の集中長           | \$006               |  |  |  |  |  |  |  |

# 14 AVR254

## 9.3. 装置への書き込み

装置への書き込み周回は装置のTWI(I<sup>2</sup>C一致)アドレスが後続する開始条件から成ります(6.1.項をご覧ください)。次のバイトは書き込み が始まる位置のアドレスです。このアドレスはその後にアドレス位置指示子として格納されます。

複数バイト転送に於けるその後のバイトはアドレス位置指示子の位置、アドレス位置指示子+1の位置、アドレス位置指示子+2の位置などに 書かれます。これはTWI(I<sup>2</sup>C適合)バス上での停止条件で終わります。新規の書き込み周回は別のアドレス位置指示子を送ることを意 味します。

装置にデータが全く書かれる必要がない場合にアドレス位置指示子を送った後で停止することが可能です。これはデータ読み込みのためにアドレス位置指示子を設定する時に行われます。

### 9.4. 装置からの読み込み

読み込み周回は装置のTWI(I<sup>2</sup>C一致)アドレスが後続する開始条件から成ります(6.1.項をご覧ください)。その後バイトは最後の書き込み 操作で設定されたアドレス位置指示子によって指示された位置から始まる読み込みを行うことができます。アドレスは複数バイト読み込み 中に各バイト読み込みに対して内部的に増加されます。

転送の最後での停止条件は内部アドレス位置指示子を最後の書き込み操作中に書かれた値へ復帰させます。これはデータ バイトの組 が(状態バイトように)複数回読むことが必要な場合にアドレス位置指示子を送り続けることが必要ないことを意味します。最初の位置に 設定して、複数バイト読み込みはその後に常にそこから始めることができます。

#### 9.5. 輪

Y線上の4チャネルの群は輪として働きます。これらはX0で始まって次々と欠損チャネルがなく番号順に配置されなければなりません。輪で 必要とされるチャネル数は4として固定化されます。

今や輪が許可されると、接触は輪接触位置バイトで報告されつつある輪の位置に帰着するでしょう。

輪の位置が滅茶苦茶なら、位置/角度に関してより大きな信号を得るために、ハ<sup>°</sup>ネルの厚みを減らす、または輪のチャネル/形状の感度 を増すことを試みてください。

### 9.6. 代表的な初期化と使い方

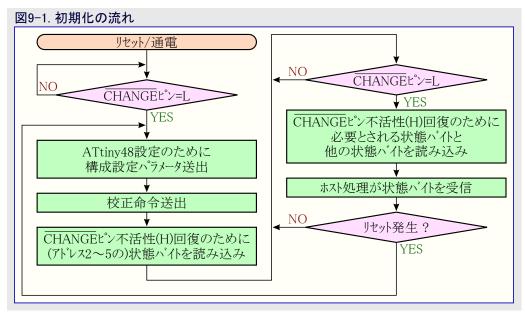

図9-1.はATtiny48ファームウェアとの代表的な通信例を示します。

- 1. リセット/通電後、ATtiny4877-ムウェアが初期化されて通信の準備が整ったことを示す、CHANGEがLowになるのを待ってください。

- 2. 始動既定値から変更されることが必要な全ての構成設定パラメータを送ってください。

- 3. ATtiny4877-ムウェア構成設定後、校正命令を送ってください。

- 4. CHANGE線を不活性状態に戻すために、全ての状態バイト(アトレス2~5)を一度読んでください。

- 5. CHANGE線がLowになったなら、必要とされる状態バイトの読み込みを実行してください。CHANGE線が再び不活性状態になることを保証するために、変更された全ての状態バイトを読むことが必要です。

- 6. それによって受信したバイトを処理してください。

- 7. (アドレス 2の)全般状態バイト内のRESETビットを調べてください。それが1に設定されていれば、リセットが起きたために全ての構成設定 パラメータを送るために手順2.へ行ってください。

- 8. 手順5.、6.、7.を繰り返してください。手順5.と6.は初期化後の通常動作繰り返し手順を続けます。

# 10. 仕様

# 10.1. 絶対最大仕様

| VDD                                                                                                                                                                       | -0.5~+6V                |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|

| 連続最大ピン電流、何れかの制御または駆動ピン                                                                                                                                                    | ±10mA                   |  |

| GNDに対する短絡回路持続時間、何れかのピン                                                                                                                                                    | 無限                      |  |

| VDDに対する短絡回路持続時間、何れかのピン                                                                                                                                                    | 無限                      |  |

| 何れかのピン上へ強制される電圧                                                                                                                                                           | $-0.6V \sim (VDD+0.6)V$ |  |

| 注意:「絶対最大仕様」下で一覧にされたこれらのを超える強制はデバイスに定常的な損傷を引き起こすかもしれません。これは<br>強制の評価だけで、それらまたはこの仕様の動作章で示されるそれらを超える他の条件でのデバイスの機能的な動作を意<br>味しません。長期に渡る期間、絶対最大仕様に晒すことはデバイスの信頼性に影響を及ぼすかもしれません。 |                         |  |

# 10.2. 推奨動作条件

| 動作温度            | -40∼85℃              |

|-----------------|----------------------|

| 保存温度            | -55∼125℃             |

| 供給波動+雑音 (<1MHz) | ±25mV                |

| 供給波動+雑音 (>1MHz) | $\pm 50 \mathrm{mV}$ |

| キー毎のCx横断負荷容量    | 2~20pF               |

# 10.3. 消費電力

| 表10-1. 平均消費電流 (試験条件:4チャネル輪許可、BL=16(4×16=64発の実際のパルス)) |                          |

|------------------------------------------------------|--------------------------|

| 低電力動作形態                                              | IDD ( $\mu$ A, VDD=3.3V) |

| 休止(SLEEP)                                            | <0.3                     |

| LP 16ms                                              | 363                      |

| LP 32ms                                              | 200                      |

| LP 64ms                                              | 107                      |

| LP 128ms                                             | 59                       |

| LP 256ms                                             | 32                       |

| LP 512ms                                             | 19                       |

| LP 1024ms                                            | 12                       |

# 10.4. 改訂履歴

| 改訂番号                   | 履歴    |

|------------------------|-------|

| ファームウェア改訂1.7 - 2009年7月 | ・初期公開 |

#### 本社

Atmel Corporation 2325 Orchard Parkway

San Jose, CA 95131 USA TEL 1(408) 441-0311 FAX 1(408) 487-2600

## 国外営業拠点

Atmel Asia

Unit 1–5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon Hong Kong TEL (852) 2245–6100 FAX (852) 2722–1369 Atmel Europe

Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France TEL (33) 1-30-60-70-00 FAX (33) 1-30-60-71-11 Atmel Japan

104-0033 東京都中央区 新川1-24-8 東熱新川ビル 9F アトメル ジャパン株式会社 TEL (81) 03-3523-3551 FAX (81) 03-3523-7581

# 製品窓口

### ウェブサイト

www.atmel.com

文献請求

www.atmel.com/literature

技術支援 avr@atmel.com 販売窓口 www.atmel.com/contacts

お断り:本資料内の情報はATMEL製品と関連して提供されています。本資料またはATMEL製品の販売と関連して承諾される何れ の知的所有権も禁反言あるいはその逆によって明示的または暗示的に承諾されるものではありません。ATMELのウェブサイトに位置す る販売の条件とATMELの定義での詳しい説明を除いて、商品性、特定目的に関する適合性、または適法性の暗黙保証に制限せ ず、ATMELはそれらを含むその製品に関連する暗示的、明示的または法令による如何なる保証も否認し、何ら責任がないと認識し ます。たとえATMELがそのような損害賠償の可能性を進言されたとしても、本資料を使用できない、または使用以外で発生する(情 報の損失、事業中断、または利益の損失に関する制限なしの損害賠償を含み)直接、間接、必然、偶然、特別、または付随して起こ る如何なる損害賠償に対しても決してATMELに責任がないでしょう。ATMELは本資料の内容の正確さまたは完全性に関して断言ま たは保証を行わず、予告なしでいつでも製品内容と仕様の変更を行う権利を保留します。ATMELはここに含まれた情報を更新する ことに対してどんな公約も行いません。特に別の方法で提供されなければ、ATMEL製品は車載応用に対して適当ではなく、使用さ れるべきではありません。ATMEL製品は延命または生命維持を意図した応用での部品としての使用に対して意図、認定、または保 証されません。

© Atmel Corporation 2009. 全権利予約済 ATMEL<sup>®</sup>、ATMEL<sup>®ロゴ</sup>とそれらの組み合わせ、AVR<sup>®</sup>、AVR<sup>®ロゴ</sup>、QWheel<sup>®</sup>、QTouch<sup>®</sup>、 QMtrix<sup>®</sup>、Adjacent Key suppression<sup>®</sup>、AKS<sup>®</sup>とその他はATMEL Corporationの登録商標または商標またはその付属物です。他の用 語と製品名は一般的に他の商標です。

#### © HERO 2013.

本応用記述はATMELのAVR254応用記述(doc8262.pdf Rev.8262A-10/09)の翻訳日本語版です。日本語では不自然となる重複す る形容表現は省略されている場合があります。日本語では難解となる表現は大幅に意訳されている部分もあります。必要に応じて一 部加筆されています。頁割の変更により、原本より頁数が少なくなっています。

必要と思われる部分には()内に英語表記や略称などを残す形で表記しています。

青字の部分はリンクとなっています。一般的に赤字の0,1は論理0,1を表します。その他の赤字は重要な部分を表します。