# AVR300: ソフトウェアTWI主装置インターフェース

# 要点

- 割り込み不使用

- 標準と高速の動作を支援

- 7ビットと10ビットの両アドレス指定を支援

- AVRマイクロ コントローラ系統全体を支援

## 序説

消費者、電気通信、電子工業での使用に関する簡単且つ費用効率的な内部ICバスの要求が TWIn゙スの開発へ導きました。今日、TWIn゙スは多数の周辺機能(IC)とマイクロ コントローラで実装され、それは低速応用に於いて良い選択にします。

AVRマイクロ コントローラ系統はTWI動作用の専用ハート・ウェアを持ちませんが(<mark>訳補</mark>:原書執筆時点に 於いてで、現在は多くのAVRがTWI専用ハート・ウェアを有しています)、柔軟な入出力と高い処理 速度のため、効率的なソフトウェア単一主装置インターフェースを容易に実装することができます。

# 動作の理屈

TWIバスは1つのデータ(SDA)線と1つのクロック(SCL)線から成る2線同期直列インターフェースです。オープンドレイン/コレクタ出力を使うことにより、TWIバスはどの製造製法(CMOS、バイポーラ、その他)も支援します。

TWIn、スはn、スの制御を行う能力がある1つ以上の装置を接続することができる複数主装置n、スです。n、スに接続された主装置が1つだけのとき、これはn、スの衝突と内部主装置アクセス(主装置の別の主装置アクセス)の処理を支援する必要がありません。主装置はSCLとSDAの両線を駆動することができ、一方従装置はSDA線でデータを出力することだけを許されます。

データ転送は常にハ、ス主装置によって始められます。SCLがHighの間のSDAでのHighからLowへの遷移が開始条件(または再送開始条件)に定義されています。開始条件は常に(固有の)7 ビット従装置アドレスとその後のデータ方向ビットが後続します。アドレス指定された従装置は1クロック周期の間、SDAをLowに保持することによって直ぐに応答します。主装置がどの応答も受信しなかった場合、その転送は終了されます。データ方向ビットに依存して、主装置または従装置は直ぐにSDA線へ8ビットのデータを送信します。そして受信する装置はデータに対して応答します。主装置よって再送開始条件と停止条件が発行される前に単一方向で複数バイを転送することができます。転送は主装置が停止条件を発行する時に終了されます。停止条件はSCLがHighの間のSDAでのLowからHighへの遷移によって定義されます。

いくつかの他の機能が実行されてしまうまで、従装置がやって来るデータを処理することができない場合、主装置に待ち状態を強制するためにSCLをLowに保持することができます。

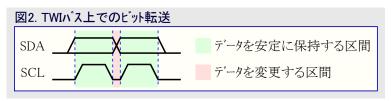

SDA線上のデータの変更は**図2**.で示されるようにSCLのLow区間の間でだけ許されます。これは開始条件と停止条件の定義の直接的な結果です。もっと詳細な説明とタイミング仕様は[1]で得られます(訳注:原書にて参照先なし)。

8ビット **AV**P® マイクロ コントローラ

応用記述

本書は一般の方々の便宜のため有志により作成されたもので、 Atmel社とは無関係であることを 御承知ください。しおりのはじめ にでの内容にご注意ください。

Rev. 0954B-05/02, 0954BJ3-04/21

# データ転送

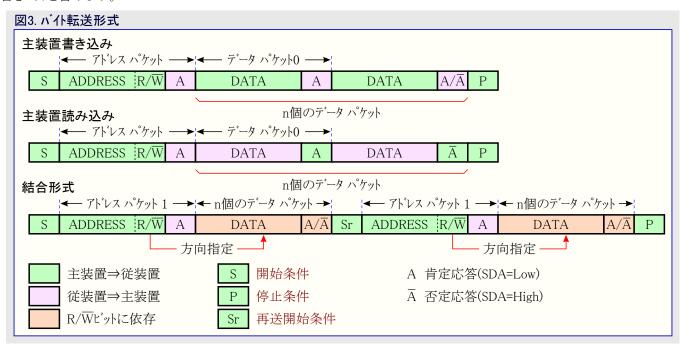

ハ、ス上の転送はハ・小単位です。各ハ・小は受信部によって設定される応答ビットが後続します。従装置アドレスバイトはアビットのアドレスと読み/書きビットを含みます。

図3.は有効なデータ転送形式を示します。結合形式に於いて、複数のデータを(同じ従装置へ)どの方向でも送ることができます。データ 方向の変更は<mark>再送開始条件</mark>を用いることによって行われます。主装置読み込み操作が最終バ・小読み込みに応答しないことによって 終了されなければならないことに注意してください。

# 接続

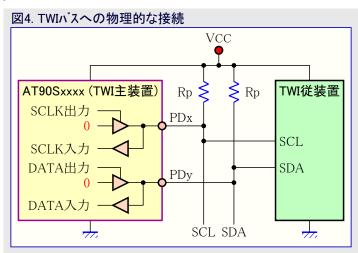

両TWI線(SDAとSCL)は従ってオープントレインまたはオープンコレクタ出力の双方向でなければなりません。各線はプルアップ抵抗経由で供給電圧へ接続されなければなりません。そして線を駆動する接続された装置が何もない時に線はHigh(論理1)で、1つ以上が線をLowに駆動する場合に論理0です。

図4.はTWIハスへAVRマイクロ コントローラを接続する方法を示します。Rpの値はVCCとハス容量に依存します(代表的には4.7 $k\Omega$ )。

# 実装

この応用記述で提供されるTWI主装置ルーチンによって使われる資源はポートD上のSCLとSDAに対する2つのピンだけです。TWIハスが同期なので、直列クロック線(SCL)に対するデューティサイクルと周期時間は重要でありません。従ってプログラム量の増加を引き起こすルーチンの"微調整"は必要ありません。

この実装で使われる2つの形式の遅延、1/4周期遅延と半周期遅延があります。標準(100kHz)動作のTWIに対してこれらの遅延はtquarter>2.5µsとthalf>5.0µsでなければなりません。高速(400kHz)動作に対するパラメータはtquarter>0.6µsとthalf>1.3µsです。

遅延ループには多くの可能な実装があります。全ての実装がMCUクロック周波数に依存します。全てのクロック速度に対して有効な版を生成することは不可能です。

以下の手順は最も効率的な遅延の実装を選ぶ方法を示します。

1. 両遅延で必要なクロック周期数を計算してください。

n = t×fosc ; t=tquarterとthalf, fosc=MCUクロック周波

2. 両遅延に関して以下の方法の1つを選ぶためにnを用いてください。

| n                                                                                                                                                                        | 遅延方法                                                                                                                                           |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| n<1                                                                                                                                                                      | 遅延ルーチンへの全ての呼び出しを取り去ってください。                                                                                                                     |  |

| 1 <n<2< th=""><th>遅延ルーチンへの全ての呼び出しを1つの"NOP"命令に置き換えてください。</th></n<2<>                                                                                                      | 遅延ルーチンへの全ての呼び出しを1つの"NOP"命令に置き換えてください。                                                                                                          |  |

| 2 <n<3< th=""><th>遅延ルーチンへの全ての呼び出しを1つの"RJMP 1"命令に置き換えてください。</th></n<3<>                                                                                                   | 遅延ルーチンへの全ての呼び出しを1つの"RJMP 1"命令に置き換えてください。                                                                                                       |  |

| 3 <n<7< th=""><th>遅延ルーチンは1つの"RET"命令だけから成るべきです。</th></n<7<>                                                                                                               | 遅延ルーチンは1つの"RET"命令だけから成るべきです。                                                                                                                   |  |

| 7 <n< th=""><th>以下のルーチンを使ってください。 LDI TWIdelay, 1+(n-7)/3;遅延計数器初期化 LOOP: DEC TWIdelay ;遅延計数器減数(-1) BRNE LOOP ;計数完了まで継続 ; RET ;呼び出し元へ復帰 (このルーチンはプログラムコードで使われます。)</th></n<> | 以下のルーチンを使ってください。 LDI TWIdelay, 1+(n-7)/3;遅延計数器初期化 LOOP: DEC TWIdelay ;遅延計数器減数(-1) BRNE LOOP ;計数完了まで継続 ; RET ;呼び出し元へ復帰 (このルーチンはプログラムコードで使われます。) |  |

# TWIサブルーチン

### "TWI init"

SCL線とSDA線を初期化します。プログラムコートの先頭に配置されているSCLPとSDAPの定数はポートDのピン番号を選びます。必要ならば、プログラムコートを変更することによってどのポートのどのピンも使うことが可能です。

コート`量を減らすためにポートD全ての初期化をこのサブルーチンに置くことができます。

### "TWI start"

開始条件を生成して従装置アトレスを送ります。全ての転送はこのサブルーチンで始めなければなりません。転送が終了した時に"TWI\_end"が呼び出されなければなりません。ハ、スが開放されると("TWI\_end"が呼び出された後)、全てのレシ、スタは他の使用に関して自由にできます。

| 項目       | 値                                    |

|----------|--------------------------------------|

| コート・量(語) | 3                                    |

| 実行周期数    | N/A                                  |

| 使用レジスタ   | 下位レジスタ=0,<br>上位レジスタ=3,<br>全体レジスタ変数=1 |

| レジスタ | 入力                        | 内部             | 出力 |

|------|---------------------------|----------------|----|

| R16  | 1                         | TWIdelay:遅延計数器 | _  |

| R17  | 1                         | TWIdata:送信緩衝部  | _  |

| R18  | TWIadr:従装置アドレスと転送方法(全体変数) | _              | _  |

### "TWI\_rep\_start"

再送開始条件を生成して従装置アドレスを送ります。再送開始条件はバイトが読み書きされてしまった後にだけ生成できます。

| 項目       | 値                                    |

|----------|--------------------------------------|

| コート・量(語) | 5                                    |

| 実行周期数    | N/A                                  |

| 使用レジスタ   | 下位レジスタ=0,<br>上位レジスタ=3,<br>全体レジスタ変数=1 |

| レジスタ | 入力                        | 内部             | 出力 |

|------|---------------------------|----------------|----|

| R16  | 1                         | TWIdelay:遅延計数器 | -  |

| R17  | -                         | TWIdata:送信緩衝部  | ı  |

| R18  | TWIadr:従装置アドレスと転送方法(全体変数) | _              | ı  |

## "TWI\_write"

TWIバスにデータ(1バイト)を書き(送信し)ます。この関数はアドレスを送るのにも使われます。

| 項目       | 値                                    |

|----------|--------------------------------------|

| コート・量(語) | 16                                   |

| 実行周期数    | N/A                                  |

| 使用レジスタ   | 下位レジスタ=0,<br>上位レジスタ=2,<br>全体レジスタ変数=0 |

| レジスタ | 入力            | 内部             | 出力 |

|------|---------------|----------------|----|

| R16  | -             | TWIdelay:遅延計数器 | _  |

| R17  | TWIdata:送信緩衝部 | _              | _  |

## "TWI\_get\_ack"

従装置の応答を得ます。このサブルーチンが"TWI\_write"ルーチンから独立している理由はもっと読み易いプログラムコートにするためです。

| 項目      | 值                                    |

|---------|--------------------------------------|

| コード量(語) | 11                                   |

| 実行周期数   | N/A                                  |

| 使用レシブスタ | 下位レジスタ=0,<br>上位レジスタ=1,<br>全体レジスタ変数=0 |

| レジスタ | 入力 | 内部             | 出力 |

|------|----|----------------|----|

| R16  | -  | TWIdelay:遅延計数器 | _  |

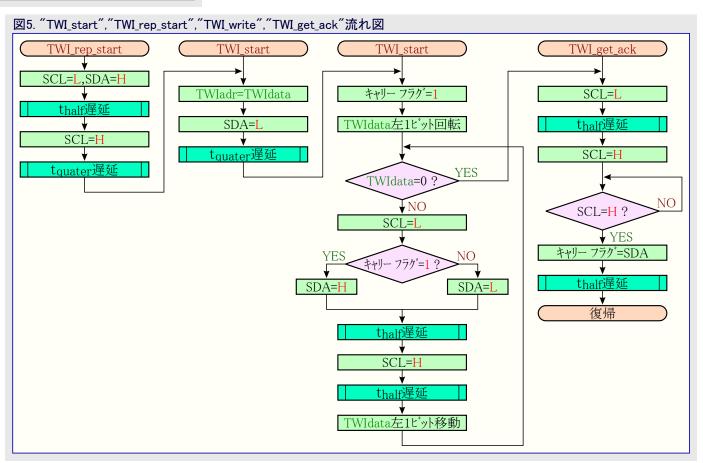

**図5**.は"TWI\_start","TWI\_rep\_start","TWI\_write","TWI\_get\_ack"に関する流れ図を示します。これらのサブルーチンは量を減らすためにプログラム コート・を共用します。

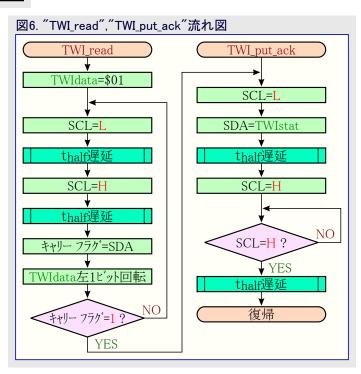

## $^{\prime\prime}$ TWI\_read $^{\prime\prime}$

TWIバスからデータ(1バイト)読み(受信し)ます。

| 項目       | 値                                    |

|----------|--------------------------------------|

| コート・量(語) | 11                                   |

| 実行周期数    | N/A                                  |

| 使用レジスタ   | 下位レジスタ=0,<br>上位レジスタ=3,<br>全体レジスタ変数=1 |

| レジスタ | 入力 | 内部                   | 出力            |

|------|----|----------------------|---------------|

| R16  | -  | TWIdelay:遅延計数器       | _             |

| R17  | -  | _                    | TWIdata:受信データ |

| R19  | _  | TWI stat:応答ビット(全体変数) | _             |

## "TWI\_put\_ack"

キャリー フラグが設定(1)されているか否かに依存して応答ビットを出力します。"TWI\_read"ルーチンからこのルーチンが独立していることは、応答が読み込み操作の結果に基く場合、使用者にとって便利です。

| 項目       | 値                                    |

|----------|--------------------------------------|

| コート・量(語) | 12                                   |

| 実行周期数    | N/A                                  |

| 使用レジスタ   | 下位レジスタ=0,<br>上位レジスタ=2,<br>全体レジスタ変数=1 |

| レジスタ | 入力 | 内部                   | 出力 |

|------|----|----------------------|----|

| R16  | -  | TWIdelay:遅延計数器       | _  |

| R19  | ı  | TWI stat:応答ビット(全体変数) | _  |

図6.は"TWI\_read","TWI\_put\_ack"に関する流れ図を示します。これらのサブルーチンは量を減らすためにプログラムコートを共用します。

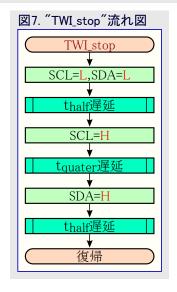

## "TWI\_stop"

停止条件を生成します。転送が終了した時に"TWI\_end"が呼び出されなければなりません。 バスが開放になると("TWI\_end"が呼び出された後)、全てのレジスタは使用が自由です。

| 項目       | 値                                    |  |

|----------|--------------------------------------|--|

| コート・量(語) | 8                                    |  |

| 実行周期数    | N/A                                  |  |

| 使用レジスタ   | 下位レジスタ=0,<br>上位レジスタ=1,<br>全体レジスタ変数=0 |  |

| レジスタ | 入力 | 内部             | 出力 |

|------|----|----------------|----|

| R16  | -  | TWIdelay:遅延計数器 | _  |

| R17  | -  | -              | _  |

図7.は"TWI\_stop"に関する流れ図を示します。

### "TWI do tansfer"

"TWI\_do\_transfer"ルーチンは便宜のためだけに実装されています。"TWI\_read"と"TWI\_write"のどちらのルーチンを呼び出すかを決めるのに最後に送られたアドレス ビットの方向を使います。

# 心得と警告

プログラム内の主繰り返しは256パイトのSRAMへのデータの読み書きの例を示します。これはTWIルーチン使用法の簡単な実演です。代表的にSRAMの読み書きは関数呼び出しとして実装されますが、従装置実装とそれらのアクセス方法の広い多様性のため、この関数呼び出しの形式は使用者に任せます。

警告! TWIルーチンの順番を変更しないでください。 殆どのルーチンは正しく動作するために他の特定のTWIルーチンが後続することを予定しています。

# 結び

この応用記述はどのAVRマイクロコントローラデバイスに於いても主装置TWIインターフェースを実装する方法を示します。そしてこれは資源の最小使用でです。実装に於いて割り込みが使われないため、それらは他の応用に対して自由にできます。割り込み内でTWIインターフェースを使うことも可能です。

### 本社

### Atmel Corporation

2325 Orchard Parkway San Jose, CA 95131, USA TEL 1(408) 441-0311 FAX 1(408) 487-2600

### 国外営業拠点

#### Atmel Asia

Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon Hong Kong TEL (852) 2245-6100 FAX (852) 2722-1369

### Atmel Europe

Le Krebs

8, Rue Jean-Pierre Timbaud

BP 309

78054 Saint-Quentin-en-Yvelines

Cedex

France

TEL (33) 1-30-60-70-00

FAX (33) 1-30-60-71-11

### Atmel Japan

104-0033 東京都中央区 新川1-24-8 東熱新川ビル 9F アトメル ジャパン株式会社 TEL (81) 03-3523-3551 FAX (81) 03-3523-7581

### 製造拠点

#### Memory

2325 Orchard Parkway San Jose, CA 95131, USA TEL 1(408) 441-0311 FAX 1(408) 436-4314

### Microcontrollers

La Chantrerie

2325 Orchard Parkway San Jose, CA 95131, USA TEL 1(408) 441-0311 FAX 1(408) 436-4314

BP 70602 44306 Nantes Cedex 3 France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA TEL 1(719) 576-3300 FAX 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR Scotland TEL (44) 1355–803–000

FAX (44) 1355-242-743

#### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA TEL 1(719) 576–3300 FAX 1(719) 540–1759

#### **Biometrics**

BP 123 38521 Saint-Egreve Cedex France TEL (33) 4-76-58-47-50 FAX (33) 4-76-58-47-60

Avenue de Rochepleine

### 文献請求

www.atmel.com/literature

#### © Atmel Corporation 2002.

Atmel製品は、ウェブサ仆上にあるAtmelの定義、条件による標準保証で明示された内容以外の保証はありません。本製品は改良のため予告なく変更される場合があります。いかなる場合も、特許や知的技術のライセンスを与えるものではありません。Atmel製品は、生命維持装置の重要部品などのような使用を認めておりません。

本書中の<sup>®</sup>、™はAtmelの登録商標、商標です。 本書中の製品名などは、一般的に商標です。

### © HERO 2021.

本応用記述はAtmelのAVR300応用記述(doc0954.pdf Rev.0954B-05/02)の翻訳日本語版です。日本語では不自然となる重複する 形容表現は省略されている場合があります。日本語では難解となる表現は大幅に意訳されている部分もあります。必要に応じて一部 加筆されています。 頁割の変更により、原本より頁数が少なくなっています。

必要と思われる部分には()内に英語表記や略称などを残す形で表記しています。

青字の部分はリンクとなっています。一般的に赤字の0,1は論理0,1を表します。その他の赤字は重要な部分を表します。