# 序説

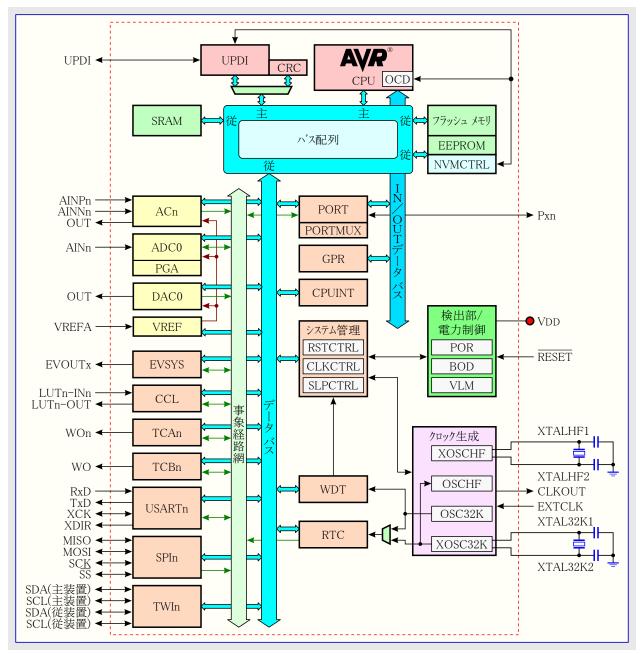

AVR® EA系統のAVR16EA28/32/48マイクロコントローラは20MHzまでのクロック速度で動くハートウェア乗算器を持つAVR® CPUを使っていま す。これらは16Kパイトのフラッシュメモリ、2KパイトのSRAM、512パイトのEEPROMを備えています。このマイクロコントローラは28、32、48ピン外囲 器で利用可能です。AVR® EA系統は事象システム、正確なアナログ部分系、進化したデジタル周辺機能を含む柔軟で低電力な基本設計 を持つMicrochipの最新技術を使います。

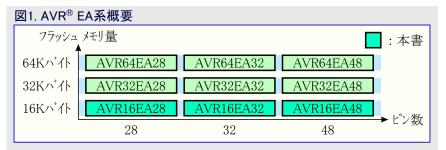

# 系統概要

下図はピン数変種とメモリ量で並べてAVR® EAデバイスを示します。

- ・これらのデバイスが完全なピンと機能の互換のため、垂直方向移植はコード変更なしで可能です。

- ・左への水平方向移植はピン数、従って利用可能な機能を減らします。

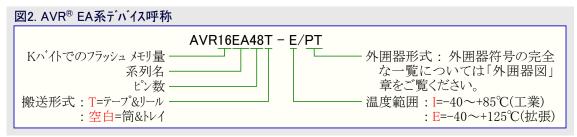

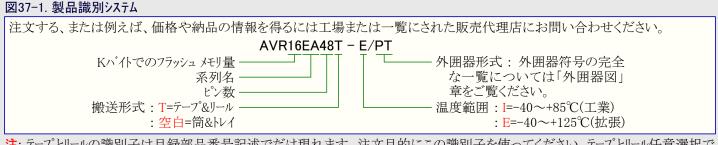

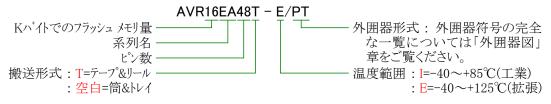

異なるフラッシュメモリ量を持つデバイスは一般的に異なるSRAMの量も持ちます。 AVR® EA系のデバイスの名前は次のように復号されます。

(訳注)・本書はAVR16EA28/32/48シリコン障害とデータシート説明(DS80001089D)の内容を含みます。

・原書に対して断りなく最新情報に更新している場合があります。

本書は一般の方々の便宜のため有志により作成されたもので、Microchip社とは無関係であることを御承知ください。しおりの[はじめに]での内容にご注意ください。

# メモリ概要

下表は系統全体のメモリ概要を示しますが、この先の文書はAVR16EA28/32/48デバイスだけを記述します。

# 表1. メモリ概要

| パモリ形式                    | AVR16EA28/32/48 | AVR32EA28/32/48     | AVR64EA28/32/48     |

|--------------------------|-----------------|---------------------|---------------------|

| フラッシュ メモリ (書き中読み(RWW)領域) | 16Kバイト (12Kバイト) | 32Kバイト (28Kバイト)     | 64Kバイト (56Kバイト)     |

| SRAM                     | 2Kバイト           | 4Kハ <sup>*</sup> イト | 6Kハ <sup>*</sup> イト |

| EEPROM                   |                 | 512/ 기사             |                     |

| 使用者列                     |                 | 64시 イト              |                     |

# 周辺機能概要

下表はAVR® AE系統全体の周辺機能概要を示しますが、この先の文書はAVR16EA28/32/48デバイスだけを記述します。

| 表2. 周辺機能概要                   |               |                                      |                                     |                                                    |  |

|------------------------------|---------------|--------------------------------------|-------------------------------------|----------------------------------------------------|--|

| 機能項目                         | 型番            | AVR64EA28<br>AVR32EA28<br>AVR16EA28  | AVR64EA32<br>AVR32EA32<br>AVR16EA32 | AVR64EA48<br>AVR32EA48<br>AVR16EA48                |  |

| ピン数                          |               | 28                                   | 32                                  | 48                                                 |  |

| 最大動作周波数 (MHz)                |               |                                      | 20                                  |                                                    |  |

| 16ビット タイマ/カウンタA型 (TCA)       |               |                                      | 2                                   |                                                    |  |

| 16ビット タイマ/カウンタB型 (TCB)       |               |                                      | 4                                   |                                                    |  |

| 実時間計数器 (RTC)                 |               |                                      | 1                                   |                                                    |  |

| USART/SPI主装置                 |               |                                      | 3                                   |                                                    |  |

| SPI主装置/従装置                   |               |                                      | 1                                   |                                                    |  |

| TWI/I <sup>2</sup> C         | (注1)          |                                      | 1                                   | r                                                  |  |

| 12ビット差動ADC (チャネル数)           |               | 1 (20)                               | 1 (24)                              | 1 (28)                                             |  |

| 10t <sup>*</sup> yFDAC       |               | 1                                    |                                     |                                                    |  |

| アナログ比較器 (AC)                 |               |                                      | 2                                   |                                                    |  |

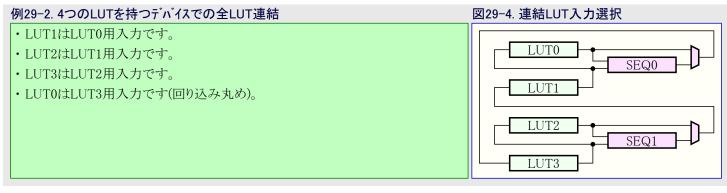

| 構成設定可能な注文論理回路 (CCL) (LUT数)   |               |                                      | 4                                   |                                                    |  |

| ウォッチドック゛タイマ(WDT)             |               |                                      | 1                                   |                                                    |  |

| 事象システムチャネル数                  |               |                                      | 6                                   | 1                                                  |  |

| 汎用入出力 (GPIO) (入力数/出力数)       | ( <b>注2</b> ) | 24/23                                | 28/27                               | 42/41                                              |  |

| ホ <sup>°</sup> ート            |               | PA7~0<br>PC3~0<br>PD7~0<br>PF7,6,1,0 | PA7~0<br>PC3~0<br>PD7~0<br>PF7~0    | PA7~0<br>PB5~0<br>PC7~0<br>PD7~0<br>PE3~0<br>PF7~0 |  |

| 外部割り込み                       |               | 24                                   | 28                                  | 42                                                 |  |

| CRC走査 (CRCSCAN)              |               | 1                                    |                                     |                                                    |  |

| 統一プログラム/デバッグ インターフェース (UPDI) |               |                                      | 1                                   |                                                    |  |

注1: TWI/I<sup>2</sup>Cは異なるピンで主装置と従装置として同時に動かすことができます。

注2: PF6/RESETピンは入力専用です。

# 特徴

- AVR® CPU

- 最大20MHzで走行

- 単一周期I/Oレシ`スタ アクセス

- -2段階の割り込み制御器

- 2周期ハートウェア乗算器

- 供給電圧範囲:1.8~5.5V

- XEI

- 真の書き込み中の読み込み動作を持つ実装書き換え可能な16Kバイト(8K語)のフラッシュメモリ

- 2KバイトのSRAM

- 512バイトのEEPROM

- チップ消去間もデータを保持してデバイスが施錠中でも書くことができる不揮発性メモリ内の64バイトの使用者列

- 書き込み/消去耐久性

- ・フラッシュ:メモリ 10,000回

- EEPROM: 100,000回

- データ保持力:55℃で40年

- ・システム

- 電源ONリセット(POR)回路

- 使用者設定可能な基準を持つ低電圧検出器 (BOD)

- BOD基準越えで設定可能な基準での割り込みを持ち使用者設定可能な基準を持つ電圧水準監視部 (VLM)

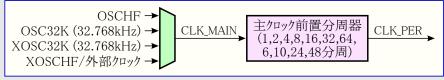

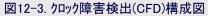

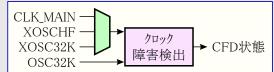

- クロック障害検出 (CFD)

- クロック任意選択

- ・20MHzまで選択可能な周波数を持つ高精度内部高周波数発振器(OSCHF)

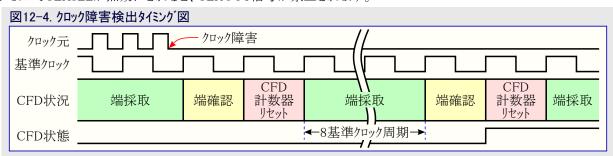

内部発振器精度を改善する自動調整

- 内部超低電力32.768kHz発振器 (OSC32K)

- ・外部32.768kHzクリスタル用発振器 (XOSC32K)

- ・外部クロック入力

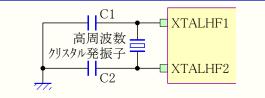

- ・ クロック障害検出を持つ外部高周波数クリスタル用発振器 (XOSCHF)

- 単一ピンの統一プログラム/デバッグ インターフェース (UPDI)

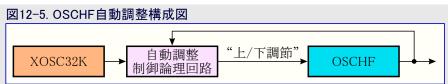

- 3つの休止動作形態

- ・即時起き上がりのために全ての周辺機能が走行しているアイドル

- ・選んだ周辺機能の構成設定可能な動作を持つスタンバイ

- ・完全なデータ保持力を持つパワータウン

- 周辺機能

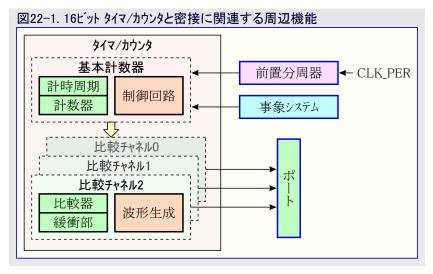

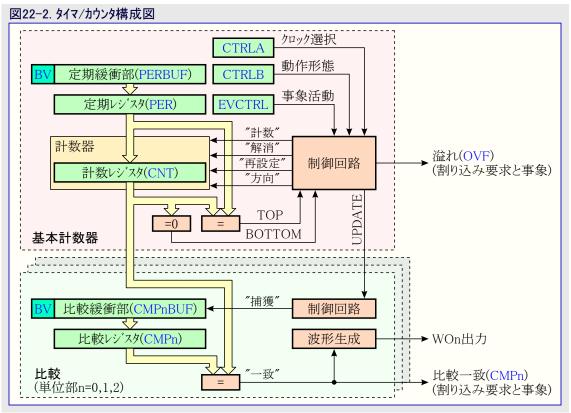

- PWMと波形生成用に3つの比較チャネルを持つ2つの16ビットタイマ/カウンタA型 (TCA)

- 捕獲と信号測定用に捕獲入力を持つ4つの16ビットタイマ/カウンタB型 (TCB)

- 外部クリスタルまたは内部発振器で走行することができる1つの16ビット実時間計数器(RTC)

- 分数ボーレート生成器、自動ボーレート、フレーム開始検出を持つ3つのUSART

- -1つの主装置/従装置直列周辺インターフェース (SPI)

- 2重アドレス一致を持つ1つの2線インターフェース (TWI)

- ・独立した主装置と従装置の動作(2元動作)

- Philips I2C互換

- ・標準動作(Sm, 100kHz)

- ・高速動作(Fm, 400kHz)

- ・高速動作プラス (Fm+, 1MHz)

- CPUから独立して予測可能な周辺機能相互合図用の事象システム

- 最大4つの設定可能な参照表(LUT)を持つ構成設定可能な注文論理回路(CCL)

- 12ビット、375kspsの1つの差動A/D変換器 (ADC)

- ・入力信号で1~16倍の利得の設定可能な利得増幅器(PGA)を内包

- 1つの10ビットD/A変換器 (DAC)

- 窓比較機能を持つ2つのアナログ比較器 (AC)

- 多数の電圧参照基準

- 1.024V

- 2.048V

- 2.500V

- 4.096V

- VREFA

- VDD

- 自動化された巡回冗長検査(CRC)フラッシュプログラム メモリ走査

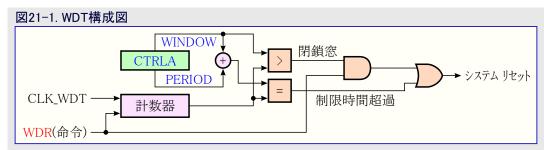

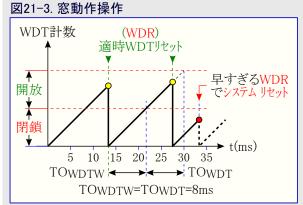

- 窓動作と独立したチップ上発振器を持つウォッチト、ック、タイマ (WDT)

- 全ての汎用ピンでの外部割り込み

#### ・I/Oと外囲器

- 24~42本の設定可能なI/Oピン

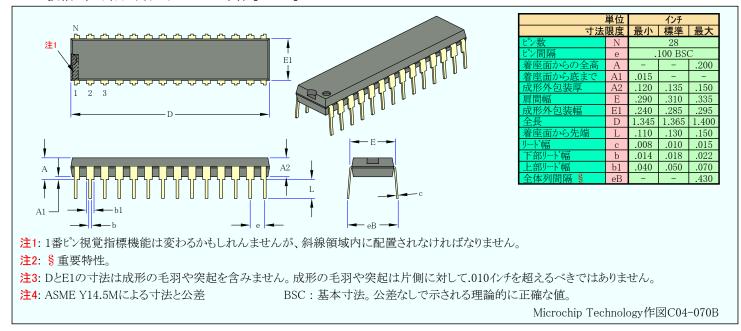

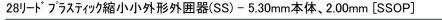

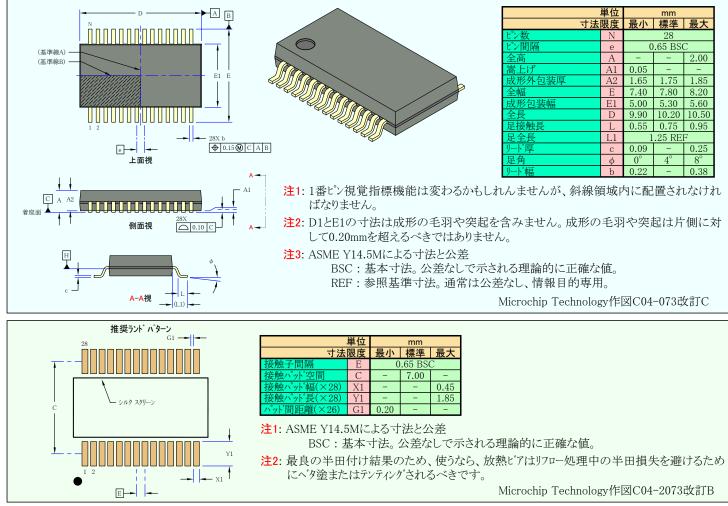

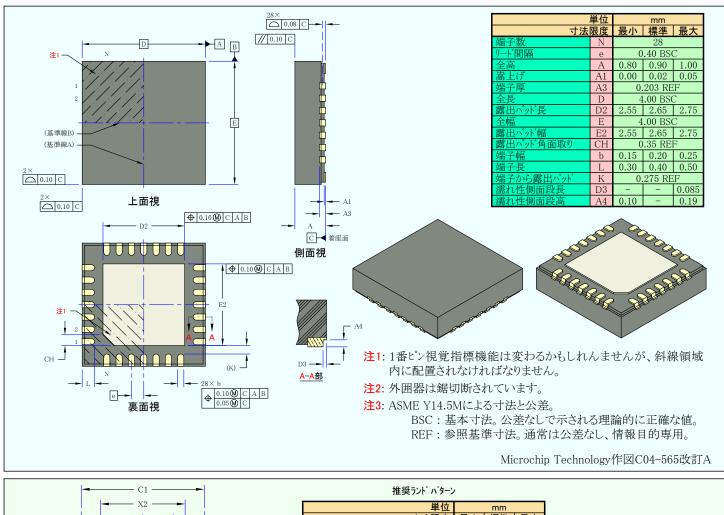

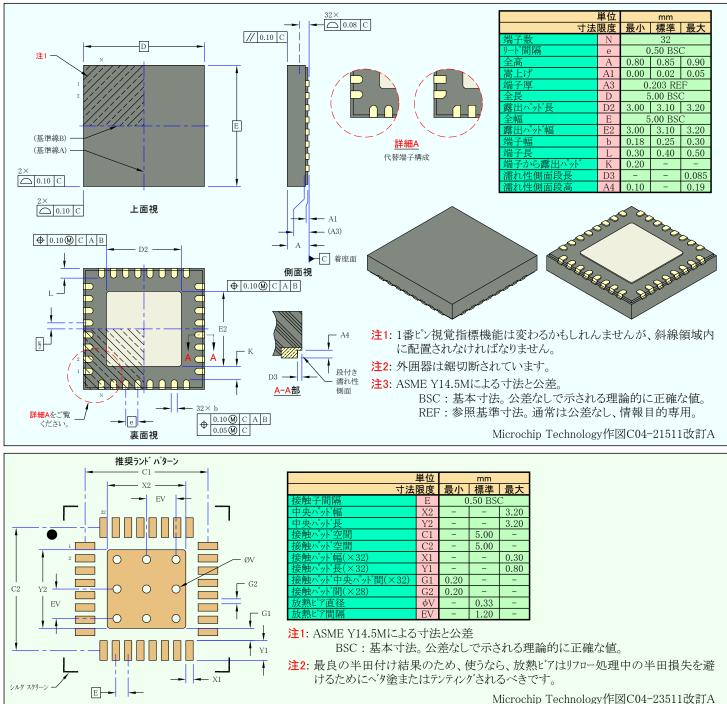

- 28ピンのSPDIP、28リードのSSOP、28パッドのVQFN 4×4mm

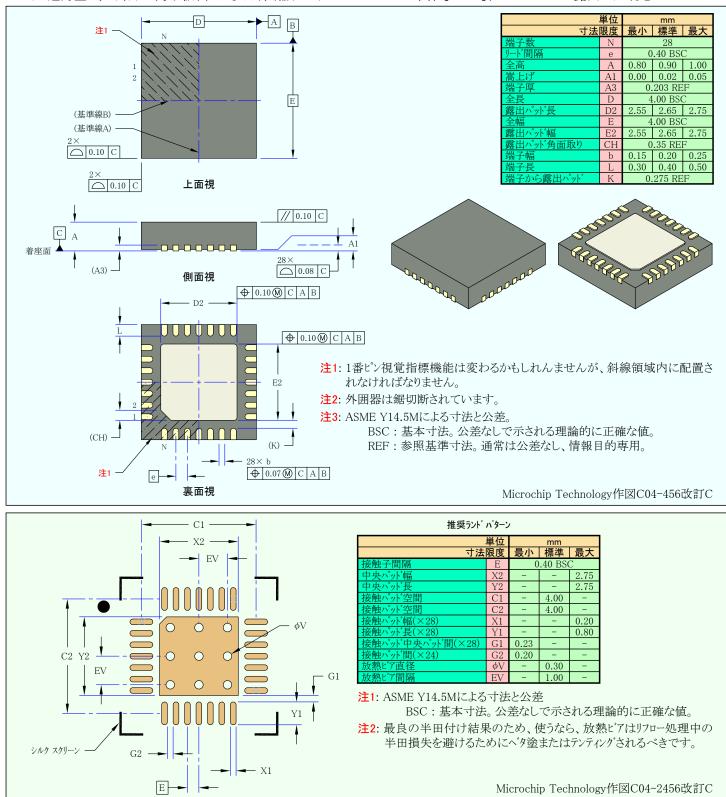

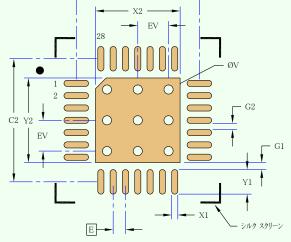

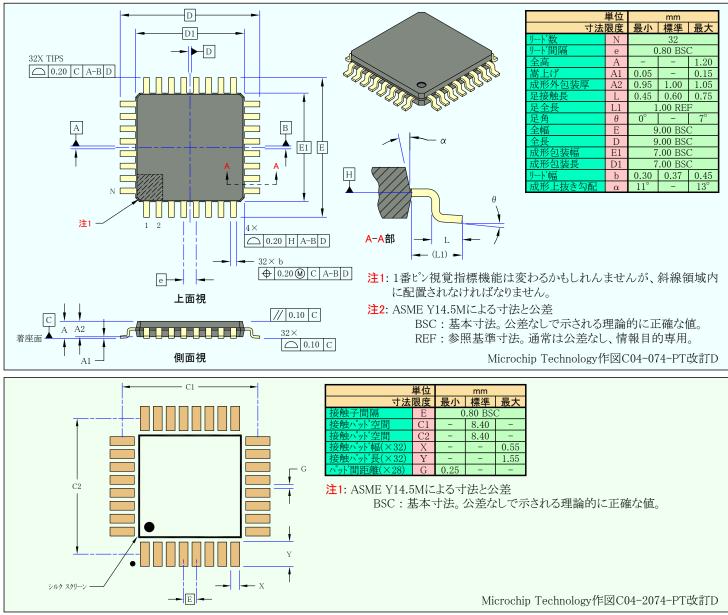

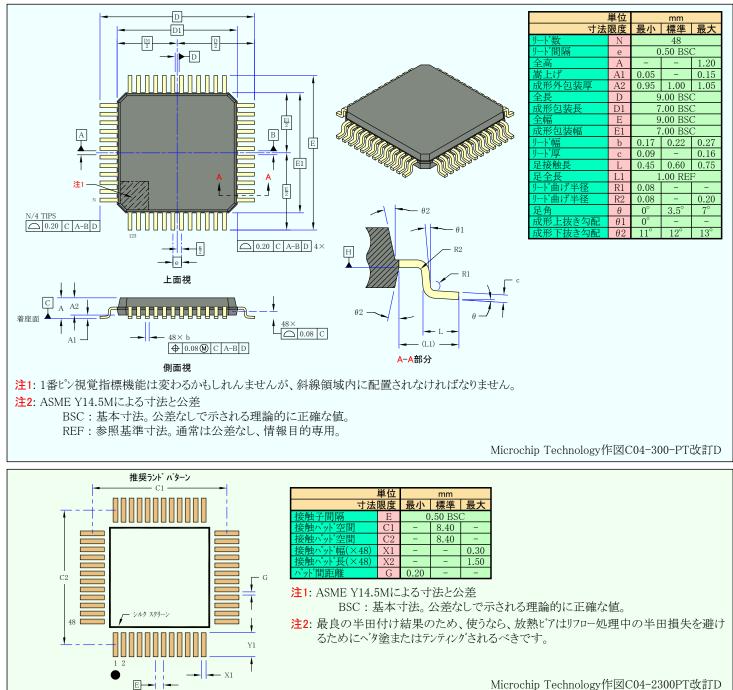

- 32パッドのVQFN 5×5mmと32リードのTQFP 7×7mm

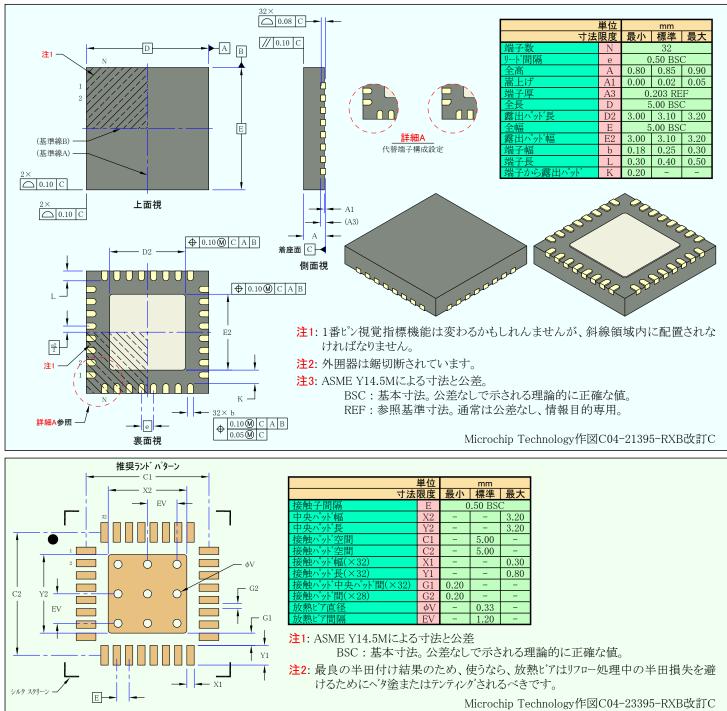

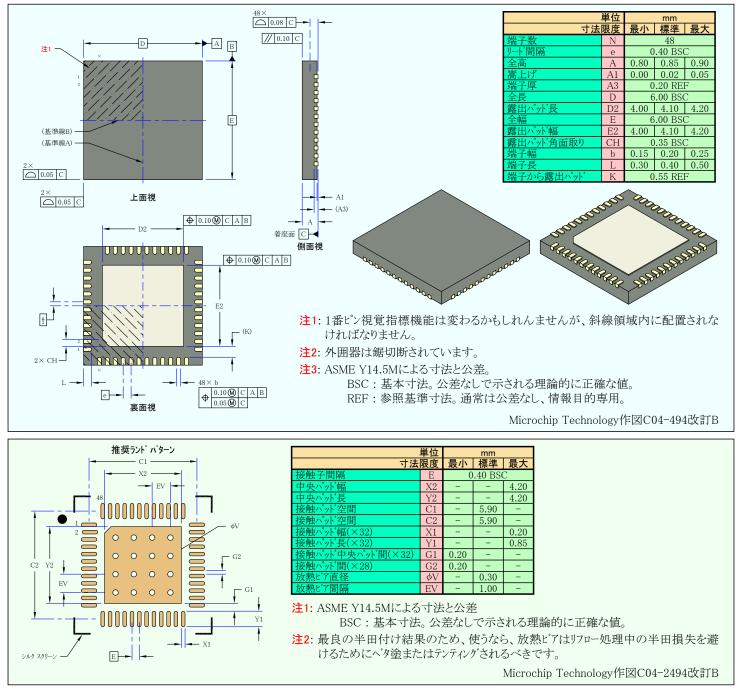

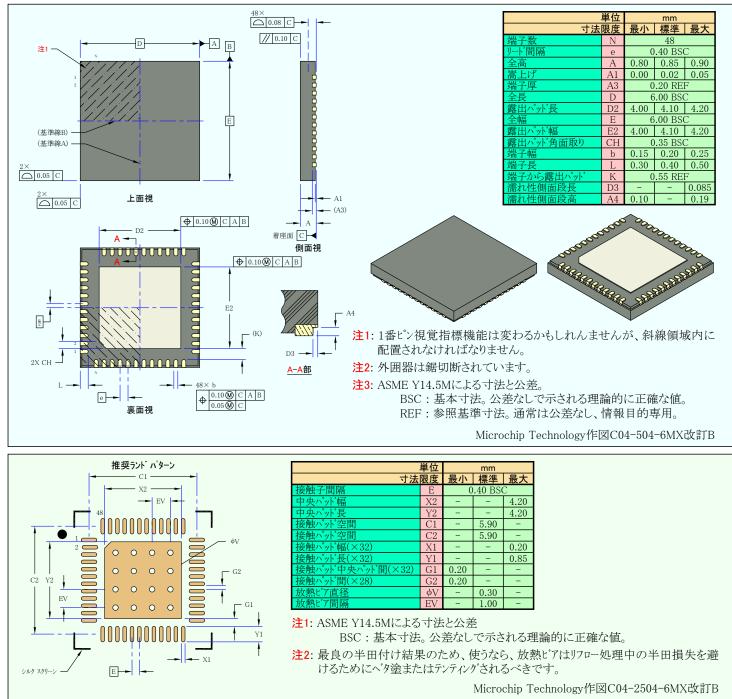

- 48パッドのVQFN 6×6mmと48リードのTQFP 7×7mm

- ・温度範囲

- 工業:周囲 -40~85℃

- 拡張:周囲 -40~125℃

# 目次

|     | 序説                |                                                                         |

|-----|-------------------|-------------------------------------------------------------------------|

|     | 系統                | ·····································                                   |

|     |                   | メモリ概要 ······2                                                           |

|     |                   | <b>周辺機能概要</b> ······2                                                   |

|     | 特徴                | →→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→                                   |

| 1.  | 構成                | <b>×</b> •••••• 8                                                       |

| 2.  | ヒン面               | 置置 ••••••• 9                                                            |

|     | 2.1.              | 28L°ンSPDIP・28リート、SSOP · · · · · · · · 9                                 |

|     | 2.2.              | <b>28</b> א <sup>°</sup> ילעקדא                                         |

|     | 2.3.              | <b>32ו\^יyh`VQFN•32IJ_h`TQFP</b> ••••••• 10                             |

|     | 2.4.              | <b>48א יין VQFN • 48 א דער דער דער 1</b> 0                              |

| 3.  | 入出                | <b>力多重化と考察 ・・・・・・・・・・・</b> 11                                           |

|     | 3.1.              | 入出力多重化       11         ウェアの指針       12                                 |

| 4.  | ハート               | <b>ウェアの指針 ・・・・・・・・・・・・・・・</b> 12                                        |

|     | 4.1.              | <b>一般的な指針</b> · · · · · · · · · · · · · · · · · · ·                     |

|     | 4.2.              | <b>電源用接続</b> · · · · · · · · · · · · · · · · · · ·                      |

|     | 4.3.              | RESET用接続 ····································                           |

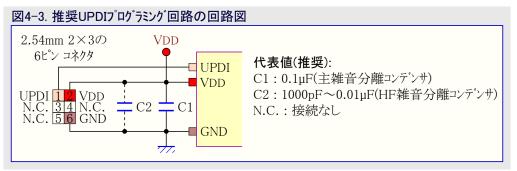

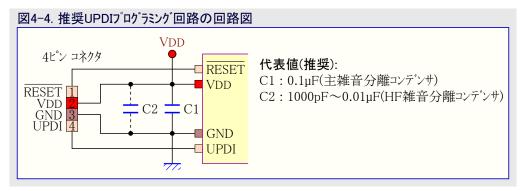

|     | 4.4.              | <b>UPDI7<sup>°</sup>ログラミング用接続</b> ・・・・・・・・13                            |

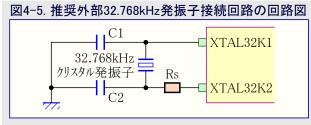

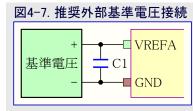

|     | 4.5.<br>4.6.      | <b>外部クリスタル発振子接続・・・・・・・・・・・</b> 14<br><b>外部基準電圧接続・・・・・・・・・・・・・・・・</b> 15 |

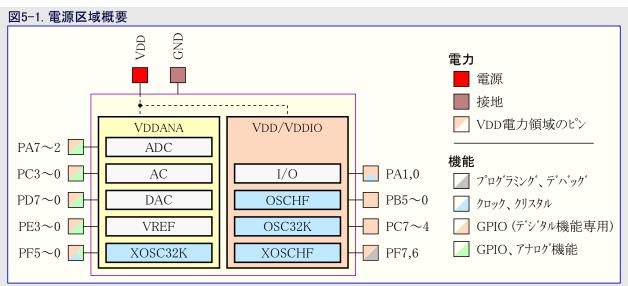

| 5.  | 4.0.<br>電力        | 区域 ······16                                                             |

| 5.  | <b>电ノ</b><br>5.1. | □□□□□□□□□□□□□□□□□□□□□□□□□□□□□□□□□□□□                                    |

| 6.  | 見定                | 电源投入 10 10 17                                                           |

| 0.  | 死足                | 数字表記法       17                                                          |

|     | 6.2.              | 数子衣記法<br>メモリの大きさと形式 ・・・・・・・・・・・・・・・・・・・・・・・17                           |

|     | 6.3.              | 周波数と時間・・・・・・・・・・・・・・・・・・・・・・17                                          |

|     | 6.4.              | レジスタとビット 18                                                             |

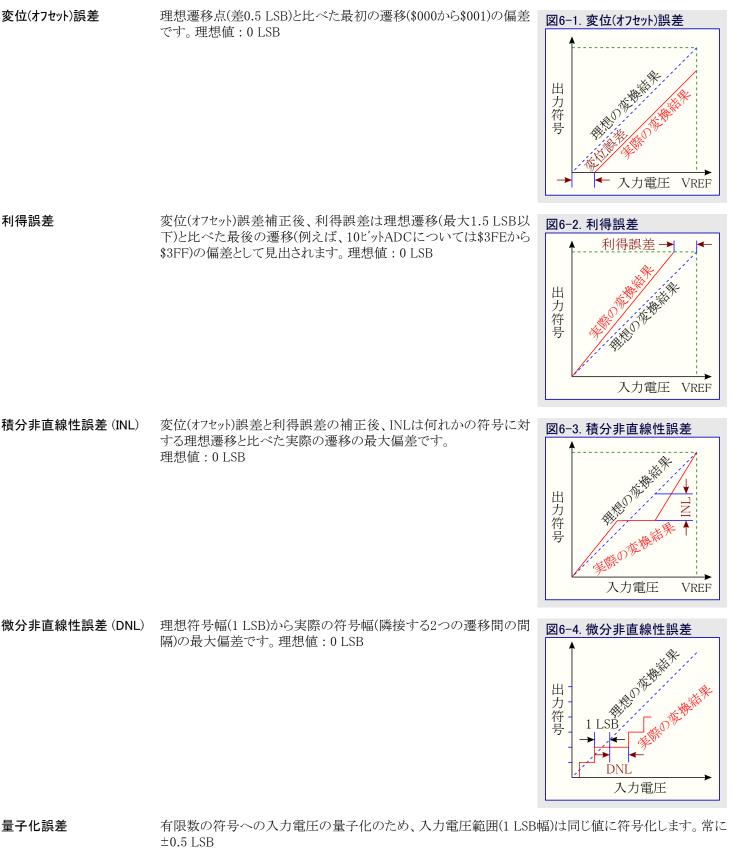

|     | 6.5.              | ADCパラメータ定義 ・・・・・ 19                                                     |

| 7.  | AVR               | <sup>®</sup> CPU ····· 20                                               |

|     | 7.1.              | 特徴                                                                      |

|     | 7.2.              | 概要 · · · · · · · · 20                                                   |

|     | 7.3.              | 基本構成                                                                    |

|     | 7.4.<br>7.5.      | <b>機能的な説明</b> ······ 21<br>レジスタ要約 ····· 24                              |

|     | 7.6.              | レジスタ説明 ····································                             |

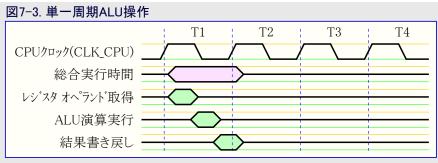

| 8.  | メモリ               |                                                                         |

| 0.  | 8.1.              | 27<br>概要・・・・・27<br>パリ配置・・・・・27<br>27                                    |

|     | 8.2.              | 火川配置 ・・・・・ 27                                                           |

|     | 8.3.              | 実装書き換え可能なフラッシュ プログラム メモリ・・・・・27                                         |

|     | 8.4.              | SRAMデータ メモリ         28           EEPROMデータ メモリ         28               |

|     | 8.5.              | <b>EEPROM</b> ד <sup>-</sup> -א לדון 28                                 |

|     |                   | USERROW - 使用者列                                                          |

|     | 8.7.              | LOCK - メモリ領域アクセス保護 ······ 28                                            |

|     | 8.8.              | FUSE - 構成設定と使用者のヒュース <sup>*</sup> ******** 30                           |

|     | 8.9.<br>0 10      | SIGROW - 識票列 35<br>I/Oメモリ 37                                            |

| 0   |                   | - 汎用レジスタ・・・・・・・・・・・・・・・・・38                                             |

| 9.  | 9.1.              | - <u>パロレクスター 30</u><br>し、「74 亜約                                         |

|     | 9.1.<br>9.2.      | レジスタ要約 ····································                             |

| 10. |                   | 機能と基本構造 ・・・・・・・・・・・・・・・・ 41                                             |

| 10. | 10.1              | 1成化こ本や1年2 年1 日辺機能でしていた。 41                                              |

|     | 10.1.             | 周辺機能アドレス配置 ······ 41<br>割り込みへ、クタ配置 ····· 42                             |

|     | 10.3.             | SYSCFG - システム構成設定・・・・・・・・・・・・・・・・・43                                    |

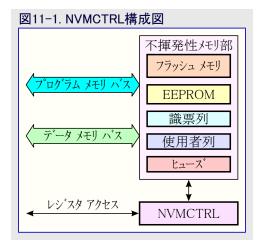

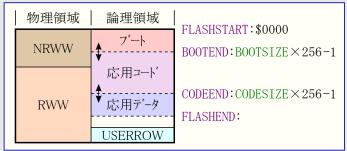

| 11. |                   | CTRL - 不揮発性メモリ制御器・・・・・・ 44                                              |

|     | 11.1.             |                                                                         |

|     | 11.2.             | 概要 •••••• 44                                                            |

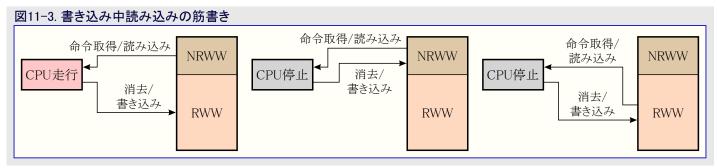

|     | 11.3.             | <b>機能的な説明・・・・・・・・・・・・・・・</b> 44                                         |

|     | 11.4.         | レジスタ要約                                                     |                     |                 |                 | ••••• 51  |

|-----|---------------|------------------------------------------------------------|---------------------|-----------------|-----------------|-----------|

|     | 11.5.         | レジスタ説明                                                     |                     |                 |                 | ••••• 52  |

| 12  | CLK           | CTRL –                                                     | り制御器                |                 |                 | •••• 56   |

|     | 12.1.         | 特徴・・・・                                                     |                     | •               |                 | 56        |

|     | 12.2.         | 概要・・・・                                                     |                     |                 |                 | ••••• 56  |

|     | 12.2.         | 機能的な説                                                      | <b>AA</b>           |                 |                 |           |

|     |               | しがスタ要約                                                     | EPH 1               |                 |                 | 62        |

|     | 12.4.         |                                                            |                     | •••••           |                 | ····· 62  |

|     | 12.5.         | レジスタ説明                                                     |                     |                 |                 |           |

| 13. |               | CTRL - 休」                                                  | 上制御器                |                 | • • • • •       | •••• 70   |

|     | 13.1.         |                                                            |                     |                 |                 | ••••• 70  |

|     | 13.2.         | 概要 ••••                                                    | • • • • • • • • • • | • • • • • • • • | • • • • • • •   | ····· 70  |

|     | 13.3.         | 機能的な説                                                      | 明 ••••              | • • • • • • • • |                 | ••••• 70  |

|     | 13.4.         | レジスタ要約<br>レジスタ説明                                           |                     |                 |                 | ••••• 73  |

|     | 13.5.         | レジスタ説明                                                     |                     |                 |                 | ••••• 74  |

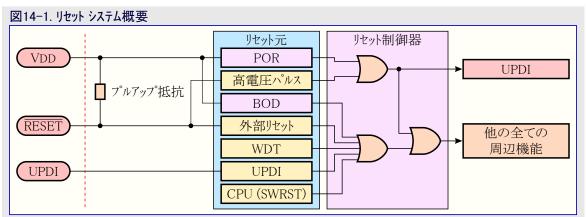

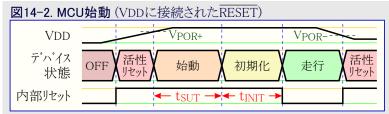

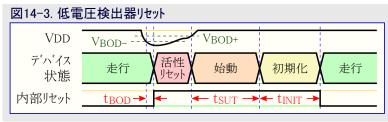

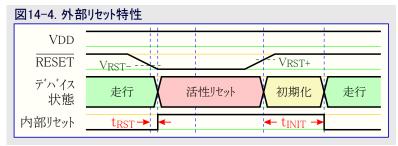

| 14. | PSTO          | CTRL - リセ                                                  | 小制御哭                |                 |                 | 75        |

| 14. | 14.1.         | 特徵                                                         | זהריושיו נייוי די   | r<br>           |                 | 15        |

|     | 14.1.         | 概要                                                         |                     |                 |                 | ····· 75  |

|     |               | 城安<br>機能的な説                                                |                     |                 |                 | 75        |

|     | 14.3.         | 機能的な説                                                      | <b>9</b>            |                 |                 |           |

|     | 14.4.         | レジスタ要約レジスタ朝                                                |                     | •••••           |                 |           |

|     | 14.5.         | レシス外記明                                                     |                     |                 | • • • • • • • • |           |

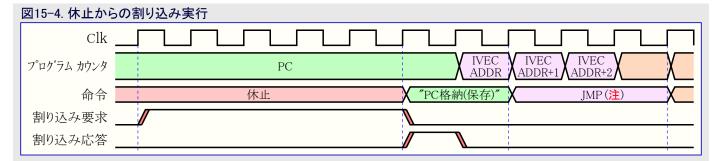

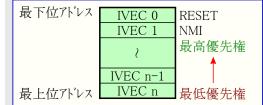

| 15. | CPUI          | NT – CPU                                                   | 割り込み                | 制御器             | • • • • •       | ••••• 80  |

|     | 15.1.         | 特徴 ••••                                                    | • • • • • • • • • • | • • • • • • • • |                 | ····· 80  |

|     | 15.2.         | 概要 ••••                                                    |                     | • • • • • • • • |                 | ••••• 80  |

|     | 15.3.         | 機能的な説                                                      | 明 •••••             |                 |                 | ••••• 80  |

|     | 15.4.         | レジスタ要約                                                     |                     |                 |                 | ••••• 84  |

|     | 15.5.         | 機能的な説<br>レジスタ要約<br>レジスタ説明                                  |                     |                 |                 | ••••• 85  |

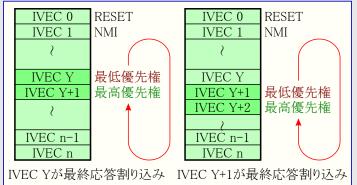

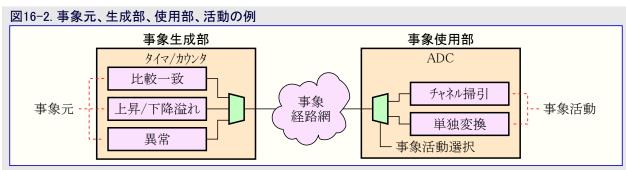

| 16. | FVSV          | ′S - 事象シ                                                   | 771                 |                 |                 |           |

| 10. | 16.1.         | 5 手家/                                                      | ~/4                 |                 |                 | ••••• 87  |

|     | 16.2.         | 概要                                                         |                     |                 |                 | ••••• 87  |

|     | 16.3.         | 城安<br>機能的な説                                                | <b>00</b>           |                 |                 | 01        |

|     |               | し し え え 見 か し ジ ス 身 要 約                                    | . чн                |                 |                 | 00        |

|     | 16.4.         |                                                            |                     | •••••           |                 | ····· 91  |

|     | 16.5.         | レジスタ説明                                                     |                     |                 |                 |           |

| 17. |               | ΓMUX – ホ <sup>°</sup> ·                                    | -卜多里1               | い話              | • • • • •       | •••• 95   |

|     | 17.1.         | 概要 ••••                                                    |                     | • • • • • • • • | • • • • • • •   | ••••• 95  |

|     | 17.2.         | レジスタ要約                                                     |                     |                 |                 | ••••• 96  |

|     | 17.3.         | レジスタ説明                                                     | •••••               | • • • • • • • • | • • • • • • •   | ••••• 97  |

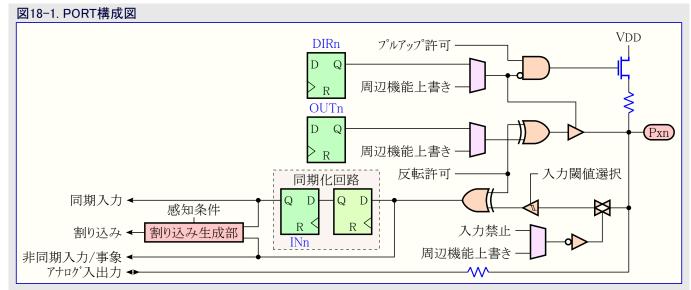

| 18. | POR           | 「 - I/Oピン<br>特徴<br>概要<br>機能的な説                             | 構成設定                |                 |                 | •••• 100  |

|     | 18 1          | 特徴                                                         |                     |                 |                 | •••• 100  |

|     | 18.2          | 概要 ••••                                                    |                     |                 |                 | ••••• 100 |

|     | 18.3          | 機能的な説                                                      | 88                  |                 |                 | ••••• 101 |

|     | 18.4.         |                                                            |                     |                 |                 | 104       |

|     | 18.5.         | レジスタ要約レジスタ説明                                               |                     |                 |                 | 104       |

|     | 18.6.         | レンス加切                                                      |                     |                 |                 | 103       |

|     |               | レジスタ要約<br>レジスタ説明                                           |                     |                 |                 | 112       |

|     | 18.7.         |                                                            |                     | <b>(</b>        |                 | 113       |

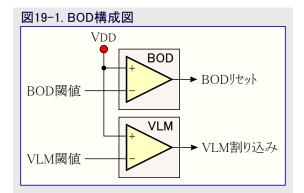

| 19. |               | - 低電圧構                                                     | 利用 いっちょう            | • • • • • •     |                 | •••• 115  |

|     | 19.1.         | 特徴                                                         | •••••               | •••••           | • • • • • • • • | ••••• 115 |

|     | 19.2.         | 概要 ••••                                                    | •••••               | • • • • • • • • | • • • • • • •   | ••••• 115 |

|     | 19.3.         | 機能的な説                                                      | 明 ••••              | • • • • • • • • |                 | ••••• 115 |

|     | 19.4.         | レジスタ要約                                                     | •••••               | • • • • • • • • | • • • • • • •   | ••••• 117 |

|     | 20.5.         | レジスタ要約<br>レジスタ<br>ジスタ<br>説明                                | •••••               |                 |                 | ••••• 118 |

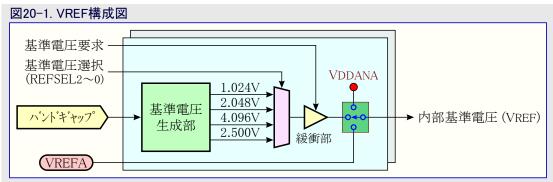

| 20  | VREF          | - ++ 24                                                    | -                   |                 |                 | 101       |

| _0. | 20.1          | —————————————————————————————————————                      | <u> </u>            |                 |                 | 191       |

|     | 20.1.         |                                                            |                     |                 |                 | 101       |

|     | 20.2.         | 燃生的たき                                                      | RB                  |                 |                 | 141       |

|     | 20.3.<br>20.4 | 1及日ヒロゾよ 武                                                  | רשי                 |                 |                 | 121       |

|     | 20.4.<br>20 F | レントン安心                                                     |                     |                 |                 | 122       |

| •   | 20.5.         | レンスツ記明                                                     | L* L /_             |                 |                 | 123       |

| 21. | WDT           | - 基準<br>特徴<br>概要<br>機能的な説<br>レジスタ要約<br>レジスタ説明<br>- ウォッチト・ッ | 7 917 •             | • • • • • •     | • • • • •       | •••• 124  |

|                   | 011                                                                                                                                                                                                                                              | H+ (H) 104                                                                                                                                                                                                                                                                                                                                                |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | 21.1.                                                                                                                                                                                                                                            | 特徴 124                                                                                                                                                                                                                                                                                                                                                    |

|                   | 21.2.                                                                                                                                                                                                                                            | 概要 ••••••124                                                                                                                                                                                                                                                                                                                                              |

|                   | 21.3.                                                                                                                                                                                                                                            | <b>機能的な説明</b> ······124                                                                                                                                                                                                                                                                                                                                   |

|                   | 21.4.                                                                                                                                                                                                                                            | <b>レジネタ要約・・・・・・・・・・・・・・・・</b> 127                                                                                                                                                                                                                                                                                                                         |

|                   | 21.5.                                                                                                                                                                                                                                            | レジスタ要約・・・・・・127<br>レジスタ説明・・・・・128                                                                                                                                                                                                                                                                                                                         |

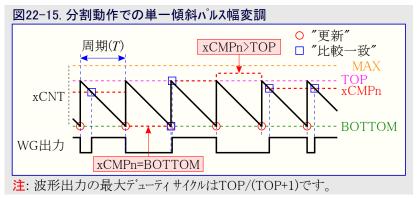

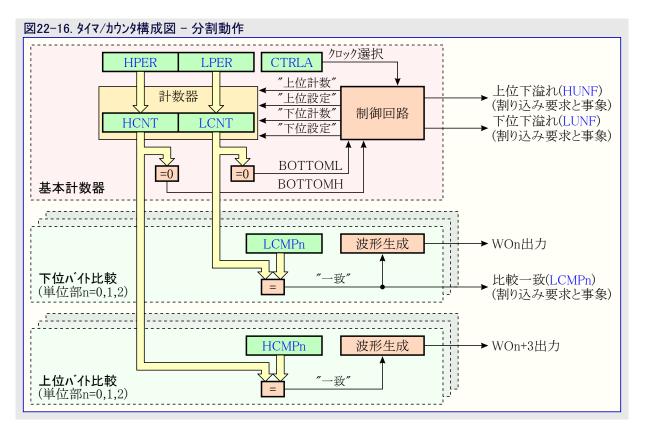

| 22                |                                                                                                                                                                                                                                                  | - <b>16ビット タイマ/カウンタA型</b> ····· 129                                                                                                                                                                                                                                                                                                                       |

| 22.               |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                           |

|                   | 22.1.                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                           |

|                   | 22.2.                                                                                                                                                                                                                                            | 概要 129                                                                                                                                                                                                                                                                                                                                                    |

|                   | 22.3.                                                                                                                                                                                                                                            | <b>機能的な説明</b> ······ 131                                                                                                                                                                                                                                                                                                                                  |

|                   | 22.4.                                                                                                                                                                                                                                            | <b>レジスタ要約 - 標準動作 ・・・・・・ 138</b>                                                                                                                                                                                                                                                                                                                           |

|                   | <b>22</b> .5.                                                                                                                                                                                                                                    | レジスタ説明 - 標準動作 ・・・・・・・・・・139                                                                                                                                                                                                                                                                                                                               |

|                   | 22.6.                                                                                                                                                                                                                                            | <b>レジスタ要約 - 分割動作 ・・・・・・・・・・</b> 148                                                                                                                                                                                                                                                                                                                       |

|                   | 22.7.                                                                                                                                                                                                                                            | <b>レジスタ説明 - 分割動作 ・・・・・・・・・・・・</b> 149                                                                                                                                                                                                                                                                                                                     |

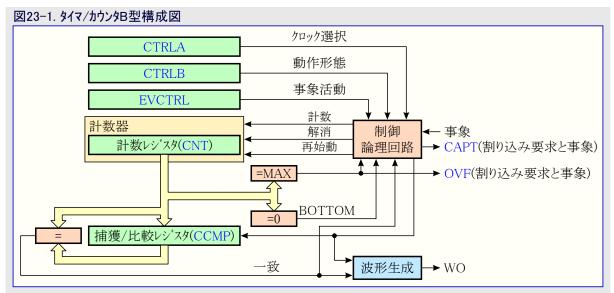

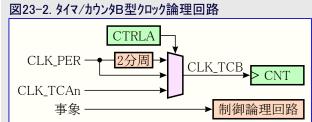

| 23                | TCB -                                                                                                                                                                                                                                            | - <b>16ビット タイマ/カウンタB型 ・・・・・・・・</b> 155                                                                                                                                                                                                                                                                                                                    |

| 20.               | 23.1.                                                                                                                                                                                                                                            | 特徴                                                                                                                                                                                                                                                                                                                                                        |

|                   | 23.2.                                                                                                                                                                                                                                            | 概要                                                                                                                                                                                                                                                                                                                                                        |

|                   | 23.2.                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                           |

|                   |                                                                                                                                                                                                                                                  | (成肥町)4武明 100                                                                                                                                                                                                                                                                                                                                              |

|                   | 23.4.                                                                                                                                                                                                                                            | レン A9安約 101                                                                                                                                                                                                                                                                                                                                               |

|                   | 23.5.                                                                                                                                                                                                                                            | <ul><li>機能的な説明</li><li>レジスタ要約</li><li>レジスタ説明</li><li>161</li></ul>                                                                                                                                                                                                                                                                                        |

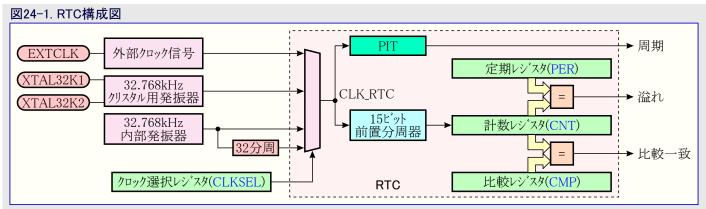

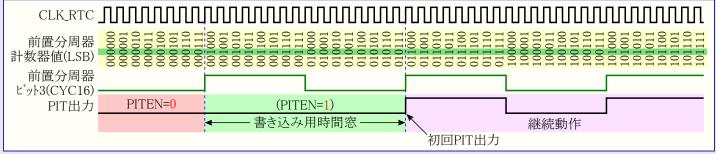

| 24.               | RTC -                                                                                                                                                                                                                                            | - 実時間計数器 ・・・・・ 167                                                                                                                                                                                                                                                                                                                                        |

|                   | 24.1.                                                                                                                                                                                                                                            | 特徴 ・・・・・・167                                                                                                                                                                                                                                                                                                                                              |

|                   | 24.2.                                                                                                                                                                                                                                            | 概要 •••••• 167                                                                                                                                                                                                                                                                                                                                             |

|                   | 24.3                                                                                                                                                                                                                                             | <u>/፲</u>                                                                                                                                                                                                                                                                                                                                                 |

|                   | 24.4.                                                                                                                                                                                                                                            | RTCの機能的な説明 ······ 168                                                                                                                                                                                                                                                                                                                                     |

|                   | 24.5.                                                                                                                                                                                                                                            | <b>PITの機能的な説明</b> ・・・・・・・・・・・・・・・・168                                                                                                                                                                                                                                                                                                                     |

|                   | 24.6.                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                           |

|                   |                                                                                                                                                                                                                                                  | <b>クリスタル誤差修正</b> ・・・・・・・・・・・・・・・・169<br>事象・・・・・・・・・・・・・・・・・・・・・・・・169                                                                                                                                                                                                                                                                                     |

|                   | 24.7.                                                                                                                                                                                                                                            | 事象 ····· 169                                                                                                                                                                                                                                                                                                                                              |

|                   | 24.8.                                                                                                                                                                                                                                            | 割り込み・・・・・・・170                                                                                                                                                                                                                                                                                                                                            |

|                   | 24.9.                                                                                                                                                                                                                                            | 休止形態動作                                                                                                                                                                                                                                                                                                                                                    |

|                   | 24.10.                                                                                                                                                                                                                                           | 同期                                                                                                                                                                                                                                                                                                                                                        |

|                   | 21.10.                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                           |

|                   | 24.11.                                                                                                                                                                                                                                           | <b>デバック</b> 操作 ······ 170                                                                                                                                                                                                                                                                                                                                 |

|                   | 24.11.<br>24.12.                                                                                                                                                                                                                                 | <b>デバッグ操作</b> 170<br>レジスタ要約 171                                                                                                                                                                                                                                                                                                                           |

|                   | 24.11.<br>24.12.                                                                                                                                                                                                                                 | <b>デバック</b> 操作 ······ 170                                                                                                                                                                                                                                                                                                                                 |

| 25                | 24.11.<br>24.12.<br>24.13.                                                                                                                                                                                                                       | デ <sup>*</sup>                                                                                                                                                                                                                       |

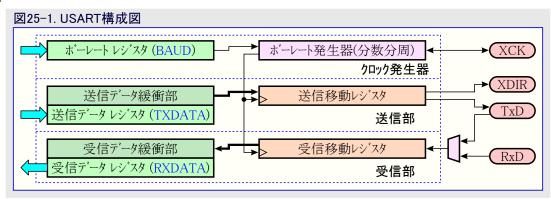

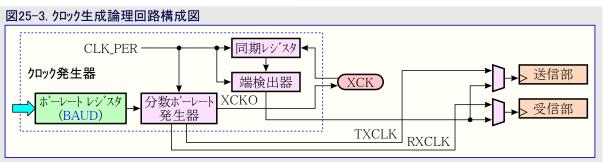

| 25.               | 24.11.<br>24.12.<br>24.13.<br>USAF                                                                                                                                                                                                               | デバッグ操作 170<br>レジスタ要約 171<br>レジスタ説明 172<br>RT - 万能同期非同期送受信器・・・・・ 179                                                                                                                                                                                                                                                                                       |

| 25.               | 24.11.<br>24.12.<br>24.13.<br>USAF<br>25.1.                                                                                                                                                                                                      | デバッグ操作 170<br>レジスタ要約 171<br>レジスタ説明 172<br>RT - 万能同期非同期送受信器・・・・ 179<br>特徴 179                                                                                                                                                                                                                                                                              |

| 25.               | 24.11.<br>24.12.<br>24.13.<br><b>USAR</b><br>25.1.<br>25.2.                                                                                                                                                                                      | デバッグ操作 170<br>レジスタ要約 171<br>レジスタ説明 172<br>RT - 万能同期非同期送受信器・・・・ 179<br>特徴 179<br>概要 179                                                                                                                                                                                                                                                                    |

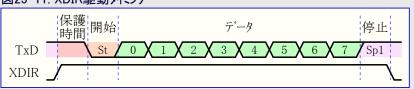

| 25.               | 24.11.<br>24.12.<br>24.13.<br><b>USAF</b><br>25.1.<br>25.2.<br>25.3.                                                                                                                                                                             | デバッグ操作       170         レジスタ要約       171         レジスタ説明       172         RT - 万能同期非同期送受信器・・・・       179         特徴       179         概要       179         機能的な説明       180                                                                                                                                                                              |

| 25.               | 24.11.<br>24.12.<br>24.13.<br><b>USAF</b><br>25.1.<br>25.2.<br>25.3.<br>25.4.                                                                                                                                                                    | デバッグ操作       170         レジスタ要約       171         レジスタ説明       172         RT - 万能同期非同期送受信器・・・・       179         特徴       179         概要       179         機能的な説明       180                                                                                                                                                                              |

|                   | 24.11.<br>24.12.<br>24.13.<br><b>USAF</b><br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.                                                                                                                                                           | デハッグ操作       170         レジスタ要約       171         レジス9説明       172         RT - 万能同期非同期送受信器・179         特徴       179         概要       179         機能的な説明       180         レジス9要約       189         レジス9規明       190                                                                                                                                      |

|                   | 24.11.<br>24.12.<br>24.13.<br><b>USAF</b><br>25.1.<br>25.2.<br>25.3.<br>25.4.                                                                                                                                                                    | デバッグ操作170レジスタ要約171レジスタ説明172RT - 万能同期非同期送受信器・179特徴179機能的な説明179機能的な説明180レジスタ要約189レジスタ説明190直列周辺インターフェース199                                                                                                                                                                                                                                                   |

|                   | 24.11.<br>24.12.<br>24.13.<br><b>USAF</b><br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.                                                                                                                                                           | デバッグ操作170レジスタ要約171レジスタ説明172RT - 万能同期非同期送受信器・179特徴179機能的な説明179機能的な説明180レジスタ要約189レジスタ説明190直列周辺インターフェース199                                                                                                                                                                                                                                                   |

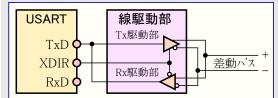

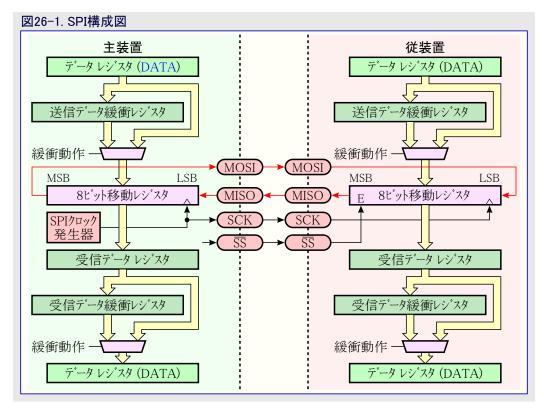

|                   | 24.11.<br>24.12.<br>24.13.<br><b>USAR</b><br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br><b>SPI</b> –                                                                                                                                           | デハッグ操作       170         レジスタ要約       171         レジスタ説明       172         RT - 万能同期非同期送受信器       179         概要       179         機能的な説明       180         レジスタ要約       189         レジスタ要約       190         直列周辺インターフェース       199         概要       199         概要       199                                                                            |

|                   | 24.11.<br>24.12.<br>24.13.<br><b>USAF</b><br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br><b>SPI –</b><br>26.1.                                                                                                                                  | デバッグ操作       170         レジスタ要約       171         レジス9説明       172         RT - 万能同期非同期送受信器       179         構要       179         機能的な説明       180         レジスタ要約       180         レジスタ要約       180         レジスタ要約       189         レジスタ要約       190         菌列周辺インターフェース       199         概要       199         概要       199         機能的な説明       200 |

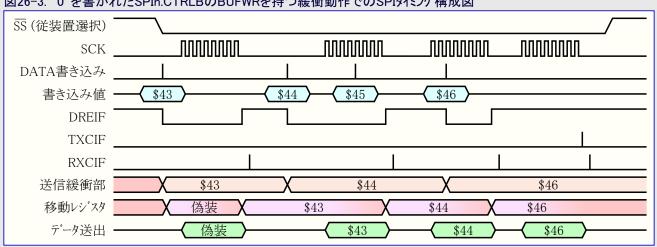

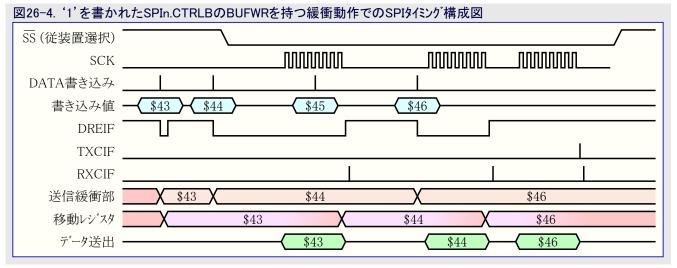

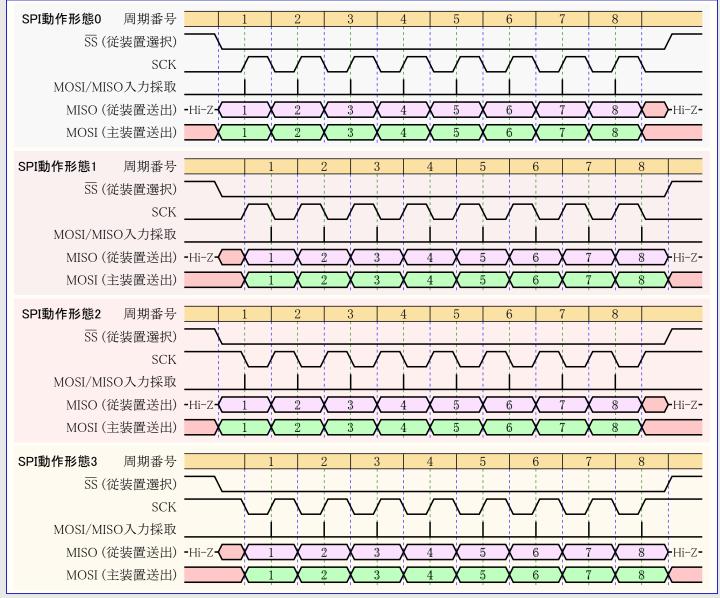

|                   | 24.11.<br>24.12.<br>24.13.<br><b>USAF</b><br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br><b>SPI –</b><br>26.1.<br>26.2.<br>26.3.                                                                                                                | デバッグ操作       170         レジスタ要約       171         レジス9説明       172         RT - 万能同期非同期送受信器       179         構要       179         機能的な説明       180         レジスタ要約       180         レジスタ要約       180         レジスタ要約       189         レジスタ要約       190         菌列周辺インターフェース       199         概要       199         概要       199         機能的な説明       200 |

|                   | 24.11.<br>24.12.<br>24.13.<br><b>USAF</b><br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br><b>SPI –</b><br>26.1.<br>26.2.<br>26.3.<br>26.3.<br>26.4.                                                                                              | デバッグ操作       170         レジスタ要約       171         レジス9説明       172         RT - 万能同期非同期送受信器       179         構要       179         機能的な説明       180         レジスタ要約       180         レジスタ要約       180         レジスタ要約       189         レジスタ要約       190         菌列周辺インターフェース       199         概要       199         概要       199         機能的な説明       200 |

| 26.               | 24.11.<br>24.12.<br>24.13.<br><b>USAF</b><br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br><b>SPI –</b><br>26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.                                                                                              | デハッグ操作170レジスタ要約171レジスタ要約172レジスタ説明172RT - 万能同期非同期送受信器・179概要179機能的な説明180レジスタ要約189レジスタ説明190直列周辺インターフェース199機能的な説明200レジスタ要約200レジスタ要約200レジスタ要約200レジスタ期200レジスタ期200レジスタ期200レジスタ説明200レジスタ期200レジスタ説明201                                                                                                                                                             |

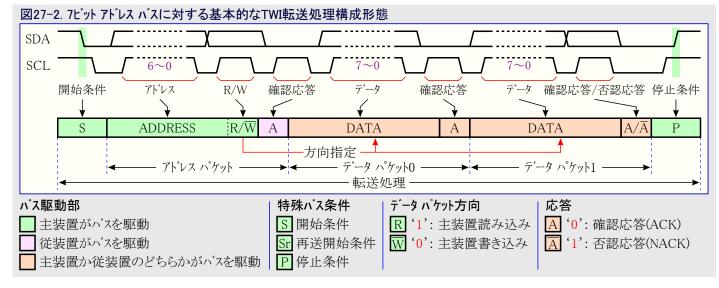

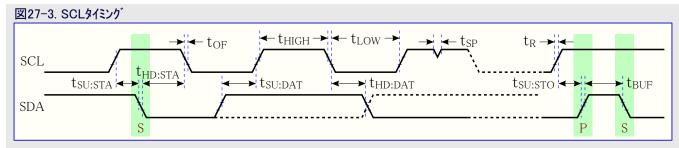

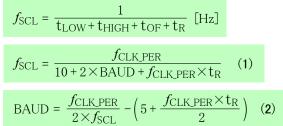

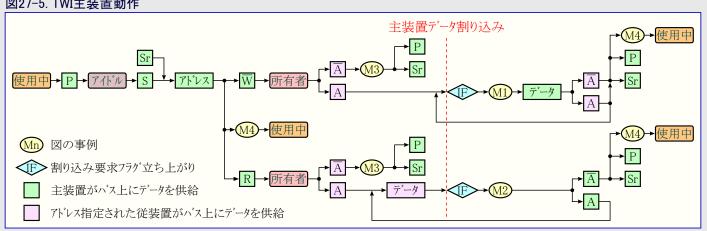

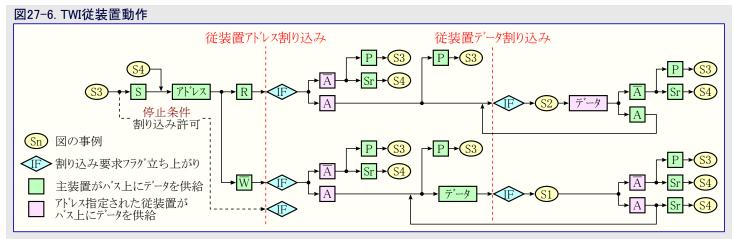

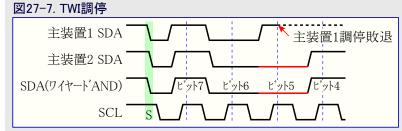

| 26.               | 24.11.<br>24.12.<br>24.13.<br>USAF<br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br>SPI -<br>26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>TWI -                                                                                                   | デハッグ操作170レジスタ要約171レジスタ要約172RT - 万能同期非同期送受信器179特徴179概要179機能的な説明180レジスタ要約189レジスタ説明190直列周辺インターフェース199機能的な説明200レジスタ要約200レジスタ要約200レジスタ要約200レジスタ要約200レジスタ要約200レジスタ要約201ビジスタ説明2072線インターフェース211                                                                                                                                                                   |

| 26.               | 24.11.<br>24.12.<br>24.13.<br><b>USAF</b><br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br><b>SPI –</b><br>26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br><b>TWI –</b><br>27.1.                                                                     | デハッグ操作170レジスタ要約171レジスタ説明172RT - 万能同期非同期送受信器179特徴179概要179機能的な説明180レジスタ要約189レジスタ要約190直列周辺インターフェース199機能的な説明200レジスタ要約200レジスタ要約206レジスタ規明2072線インターフェース211                                                                                                                                                                                                       |

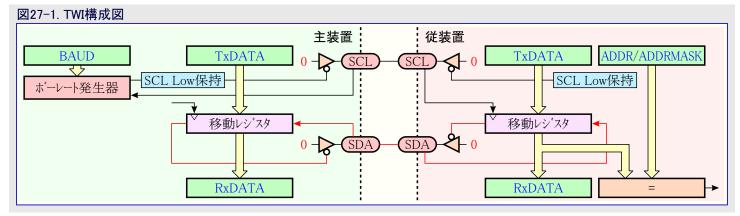

| 26.               | 24.11.<br>24.12.<br>24.13.<br><b>USAF</b><br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br><b>SPI –</b><br>26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br><b>TWI –</b><br>27.1.<br>27.2.                                                            | デハッグ操作170レジスタ要約171レジスタ説明172RT - 万能同期非同期送受信器179特徴179概要179機能的な説明180レジスタ要約189レジスタ要約190直列周辺インターフェース199機能的な説明200レジスタ要約200レジスタ要約200レジスタ要約201大家教説明202レジスタ説明201ビジスタ説明201レジスタ説明201レジスタ説明201レジスタ説明201ビジスタ説明201シスタ説明201シスタ説明201シスタ説明201シスタ説明201シスタ説明201大学会201大学会201大学会201レジスタ201レジスタ201レジスタ201レジスタ201レジスタ201レジスタ201レジスタ201                                           |

| 26.               | 24.11.<br>24.12.<br>24.13.<br>USAF<br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br>SPI -<br>26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>TWI -<br>27.1.<br>27.2.<br>27.3.                                                                        | デハッグ操作170レジスタ要約171レジスタ説明172RT - 万能同期非同期送受信器179特徴179概要179機能的な説明180レジスタ要約189レジスタ説明190直列周辺インターフェース199機能的な説明200レジスタ要約200レジスタ要約200レジスタ説明200レジスタ説明201学スタ説明201大教要約201レジスタ期201レジスタ期201レジスタ期201大教201レジスタ201レジスタ201レジスタ201レジスタ201レジスタ201大会説明2012線211機能的な説明211機能的な説明212                                                                                              |

| 26.               | 24.11.<br>24.12.<br>24.13.<br>USAF<br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br>SPI -<br>26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>TWI -<br>27.1.<br>27.2.<br>27.3.                                                                        | デハッグ操作170レジスタ要約171レジスタ説明172RT - 万能同期非同期送受信器179特徴179概要179機能的な説明180レジスタ要約189レジスタ説明190直列周辺インターフェース199機能的な説明200レジスタ要約200レジスタ要約200レジスタ説明200レジスタ説明201学スタ説明201大教要約201レジスタ期201レジスタ期201レジスタ期201大教201レジスタ201レジスタ201レジスタ201レジスタ201レジスタ201大会説明2012線211機能的な説明211機能的な説明212                                                                                              |

| 26.<br>27.        | 24.11.<br>24.12.<br>24.13.<br>USAF<br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br>SPI –<br>26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>TWI –<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.                                                      | デハッグ操作170レジスタ要約171レジスタ要約172RT - 万能同期非同期送受信器179特徴179概要179機能的な説明180レジスタ要約189レジスタ要約190直列周辺インターフェース199機能的な説明200レジスタ要約200レジスタ要約200レジスタ要約201大家設明202レジスタ要約201ビジスタ要約202レジスタ要約201大家設明202レジスタ要約202レジスタ要約203レジスタ要約201機能的な説明212レジスタ要約220レジスタ説明220レジスタ説明220レジスタ説明221                                                                                                   |

| 26.<br>27.        | 24.11.<br>24.12.<br>24.13.<br>USAF<br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br>SPI –<br>26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>TWI –<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.                                                      | デハッグ操作170レジスタ要約171レジスタ要約172RT - 万能同期非同期送受信器179特徴179概要179機能的な説明180レジスタ要約189レジスタ要約190直列周辺インターフェース199機能的な説明200レジスタ要約200レジスタ要約200レジスタ要約201大家設明202レジスタ要約201ビジスタ要約202レジスタ要約201大家設明202レジスタ要約202レジスタ要約203レジスタ要約201機能的な説明212レジスタ要約220レジスタ説明220レジスタ説明220レジスタ説明221                                                                                                   |

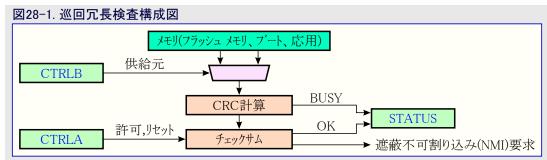

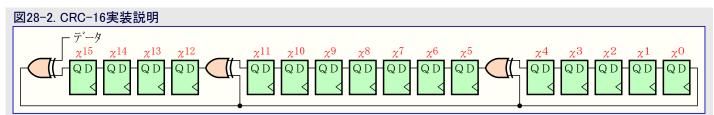

| 26.<br>27.        | 24.11.<br>24.12.<br>24.13.<br>USAF<br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br>SPI –<br>26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>TWI –<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>CRCS                                              | デハッグ操作170レジスタ要約171レジスタ要約171レジスタ説明172RT - 万能同期非同期送受信器179概要179概要179機能的な説明180レジスタ要約189レジスタ要約190直列周辺インターフェース199機能的な説明200レジスタ要約206レジスタ説明2072線インターフェース211特徴211機能的な説明212レジスタ要約220レジスタ要約220レジスタ要約221どスタ説明221どスタ要約221どスタ要約221どスタ要約221ンズス9説明221どスタ要約221どスタ要約221どスタ要約221ジスタ要約221ジスタ要約221どろの221どろの221どろの221                                                           |

| 26.<br>27.        | 24.11.<br>24.12.<br>24.13.<br>USAF<br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br>SPI –<br>26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>TWI –<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>CRCS<br>28.1.                                     | デハッグ操作170レジスタ要約171レジスタ要約171レジスタ説明172RT - 万能同期非同期送受信器179概要179概要179機能的な説明180レジスタ要約189レジスタ要約190直列周辺インターフェース199機能的な説明200レジスタ要約206レジスタ説明2072線インターフェース211特徴211機能的な説明212レジスタ要約220レジスタ要約220レジスタ要約221どスタ説明221どスタ要約221どスタ要約221どスタ要約221ンズス9説明221どスタ要約221どスタ要約221どスタ要約221ジスタ要約221ジスタ要約221どろの221どろの221どろの221                                                           |

| 26.<br>27.        | 24.11.<br>24.12.<br>24.13.<br>USAF<br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br>SPI -<br>26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>TWI -<br>27.1.<br>27.2.<br>27.4.<br>27.5.<br>CRCS<br>28.1.<br>28.2                                      | デハッグ操作170レジスタ要約171レジスタ要約172RT - 万能同期非同期送受信器179構要179概要179機能的な説明180レジスタ要約189レジスタ要約190直列周辺インターフェース199機要199機要199機要199機要200レジスタ要約200レジスタ要約200レジスタ要約201レジスタ要約202レジスタ朝明202レジスタ説明201特徴211機能的な説明212レジスタ要約220レジスタ説明221SCAN - 巡回冗長検査メモリ走査231構要231概要231                                                                                                               |

| 26.<br>27.        | 24.11.<br>24.12.<br>24.13.<br>USAF<br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br>SPI -<br>26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>TWI -<br>27.1.<br>27.2.<br>27.4.<br>27.5.<br>CRCS<br>28.1.<br>28.2                                      | デハッグ操作170レジスタ要約171レジスタ要約172RT - 万能同期非同期送受信器179構要179概要179機能的な説明180レジスタ要約189レジスタ要約190直列周辺インターフェース199機要199機要199機要199機要200レジスタ要約200レジスタ要約200レジスタ要約201レジスタ要約202レジスタ朝明202レジスタ説明201特徴211機能的な説明212レジスタ要約220レジスタ説明221SCAN - 巡回冗長検査メモリ走査231構要231概要231                                                                                                               |

| 26.<br>27.        | 24.11.<br>24.12.<br>24.13.<br>USAF<br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br>SPI -<br>26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>TWI -<br>27.1.<br>27.2.<br>27.4.<br>27.5.<br>CRCS<br>28.1.<br>28.2                                      | デハッグ操作170レジスタ要約171レジスタ要約172RT - 万能同期非同期送受信器179構要179概要179機能的な説明180レジスタ要約189レジスタ要約190直列周辺インターフェース199機要199機要199機要199機要200レジスタ要約200レジスタ要約200レジスタ要約201レジスタ要約202レジスタ朝明202レジスタ説明201特徴211機能的な説明212レジスタ要約220レジスタ説明221SCAN - 巡回冗長検査メモリ走査231構要231概要231                                                                                                               |

| 26.<br>27.<br>28. | 24.11.<br>24.12.<br>24.13.<br>USAF<br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br>SPI -<br>26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>TWI -<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>CRCS<br>28.1.<br>28.2.<br>28.3.<br>28.4.<br>28.5. | デハッグ操作170レジスタ要約171レジスタ説明172RT - 万能同期非同期送受信器179概要179概要179機能的な説明180レジスタ要約189レジスタ要約190直列周辺インターフェース199機要199機要199機要199機要200レジスタ要約200レジスタ要約201ビジスタ要約202レジスタ要約201ジスタ要約202レジスタ要約211機能的な説明212レジスタ要約220レジスタ要約221SCAN - 巡回冗長検査メモリ走査231機能的な説明231機能的な説明231レジスタ要約231レジスタ要約231レジスタ要約231レジスタ要約231レジスタ要約231レジスタ要約231レジスタ現約231レジスタ現約231レジスタ説明231                            |

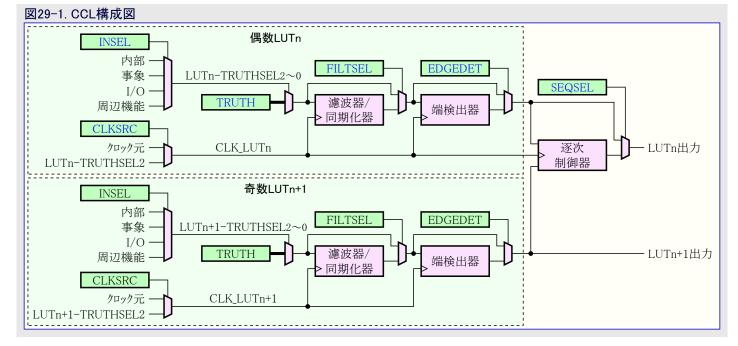

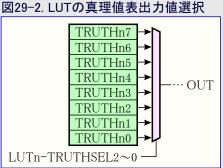

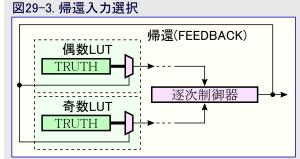

| 26.<br>27.<br>28. | 24.11.<br>24.12.<br>24.13.<br>USAF<br>25.1.<br>25.2.<br>25.3.<br>25.4.<br>25.5.<br>SPI -<br>26.1.<br>26.2.<br>26.3.<br>26.4.<br>26.5.<br>TWI -<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>CRCS<br>28.1.<br>28.2.<br>28.3.<br>28.4.<br>28.5. | デハッグ操作170レジスタ要約171レジスタ要約172RT - 万能同期非同期送受信器179特徴179概要179機能的な説明180レジスタ要約189レジスタ要約190直列周辺インターフェース199機能的な説明200レジスタ要約200レジスタ要約200レジスタ要約201レジスタ要約201レジスタ要約202レジスタ要約201レジスタ要約202レジスタ要約203特徴211概要211機能的な説明212レジスタ要約220レジスタ要約221SCAN - 巡回冗長検査メモリ走査231特徴231レジスタ要約231レジスタ要約231レジスタ要約231横能的な説明231レジスタ説明235-構成設定可能な注文論理回路237                                          |

|     | 29.2.          | 概要 •••••• 237                                                                                                                        |

|-----|----------------|--------------------------------------------------------------------------------------------------------------------------------------|

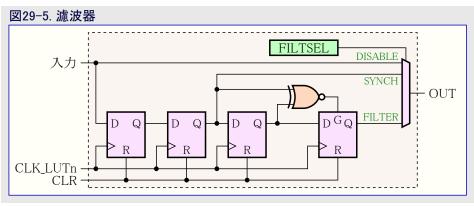

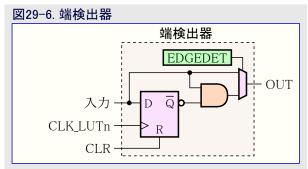

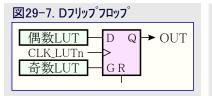

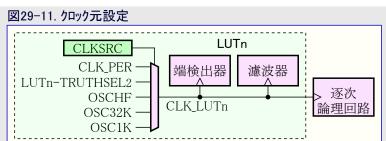

|     | 29.3.          | <b>機能的な説明</b> ······ 238                                                                                                             |

|     | 29.4.          | レジスタ要約 ······243<br>レジスタ説明 ·····244                                                                                                  |

|     | 29.5.          | <b>レジスタ説明</b> ・・・・・・・・・・・・・・・・・・・・・・244                                                                                              |

| 30. | <b>AC</b> –    | <b>アナログ比較器 ・・・・・</b> 248                                                                                                             |

|     | 30.1.          | 特徴                                                                                                                                   |

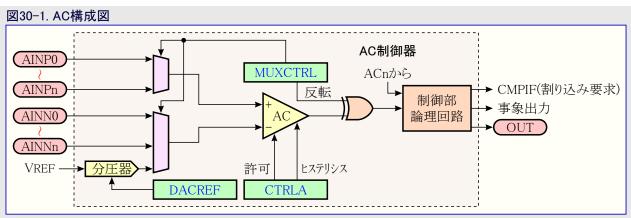

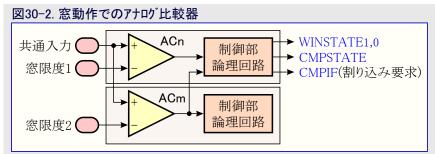

|     | 30.2.          | 概要 •••••• 248                                                                                                                        |

|     | 30.3.          | <b>機能的な説明</b> ······ 249                                                                                                             |

|     | 30.4.          | <b>レジスタ要約</b> ······ 251                                                                                                             |

|     | 30.5.          | レジスタ説明                                                                                                                               |

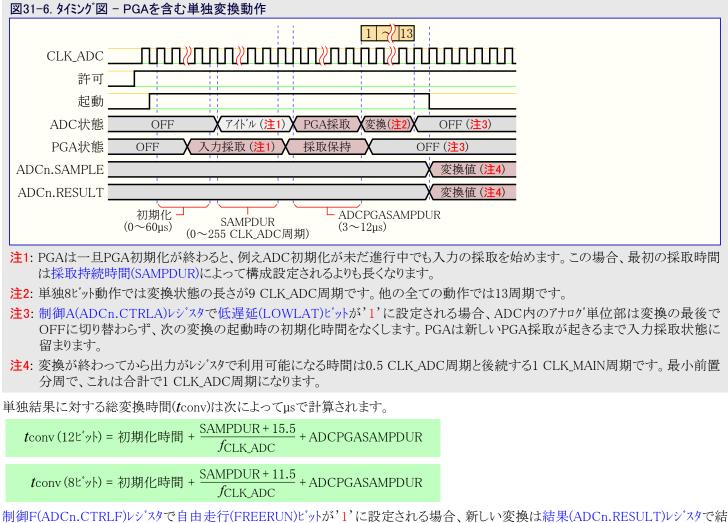

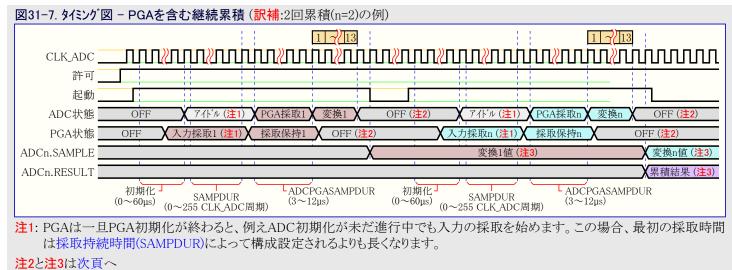

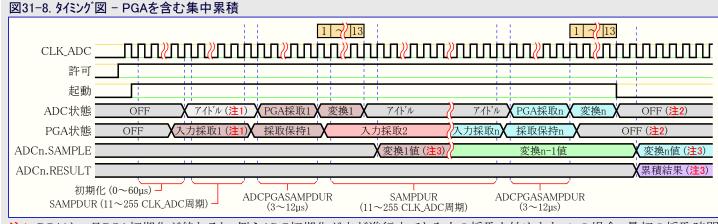

| 31. |                | - A/D変換器 ····· 255                                                                                                                   |

|     | 31.1.          | 特徴 255                                                                                                                               |

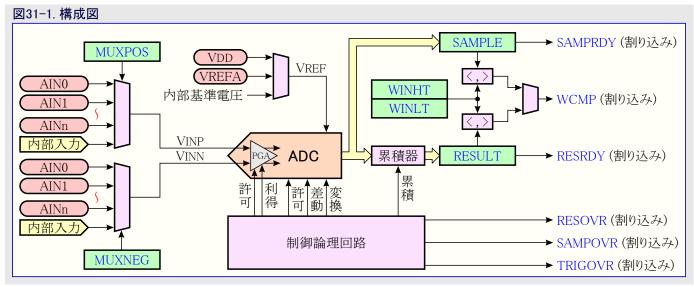

|     | 31.2.          | 概要 ······ 255<br>機能的な説明 ····· 256                                                                                                    |

|     | 31.3.          | 機能的な説明 256                                                                                                                           |

|     | 31.4.<br>31.5. | レジスタ要約 ····································                                                                                          |

| 20  | 31.5.          | レッス学説明 207                                                                                                                           |

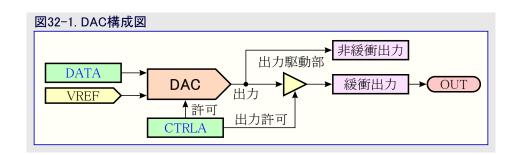

| 32. | DAC · 32 1     | - D/A変換器 ····· 277<br>特徴 ····· 277                                                                                                   |

|     | 32.1.          | 将倒 ····· 277<br>概要 ···· 277                                                                                                          |

|     | 32.2.<br>32.3. | (祝安) 211<br>機能的た説明 977                                                                                                               |

|     | 32.3.<br>32.4  | 機<br>機能的な説明 ······277<br>レジスタ要約 ·····279                                                                                             |

|     | 32.5.          | レジスタ説明 ····································                                                                                          |

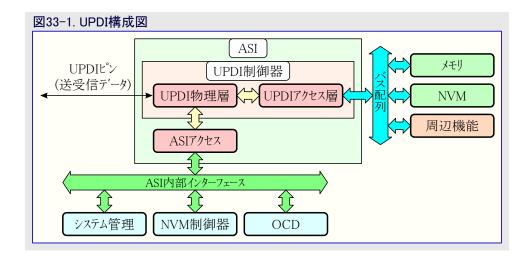

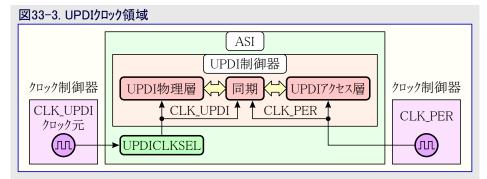

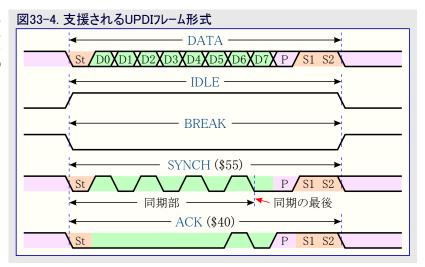

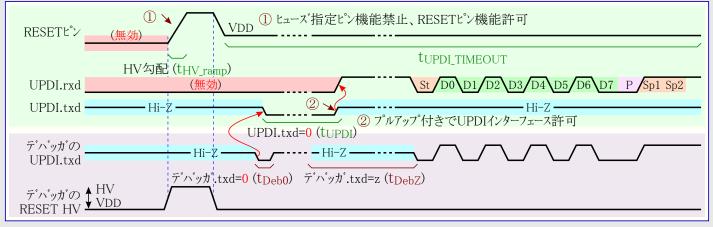

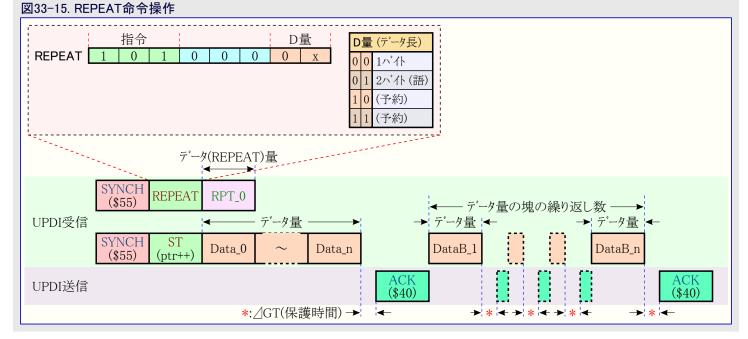

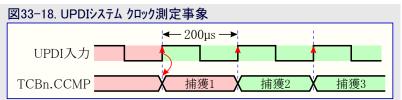

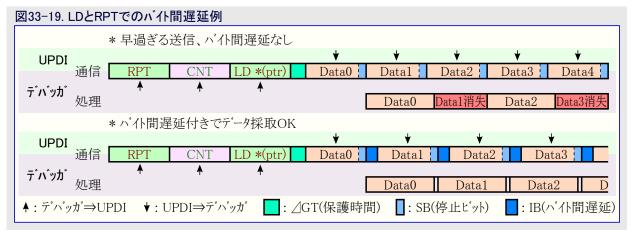

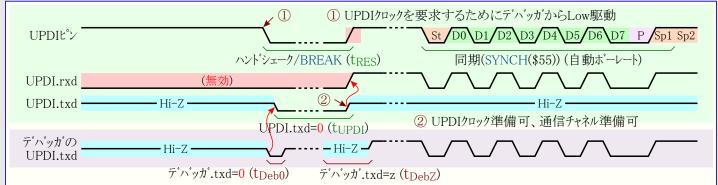

| 33. |                | - 統一フ <sup>°</sup> ログ <sup>*</sup> ラム/デバック <sup>*</sup> インターフェース • 281                                                               |

| 00. | 33.1.          | 特徴                                                                                                                                   |

|     | 33.2.          | 概要 ······ 281                                                                                                                        |

|     | 33.3.          | <b>機能的な説明</b> ······ 283                                                                                                             |

|     | 33.4.          | <b>レジスタ要約</b> ····································                                                                                   |

|     | 33.5.          | <b>レジスタ説明</b> ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                   |

| 34. | 命令-            | <b>- 式要約 ・・・・・ 30</b> 2                                                                                                              |

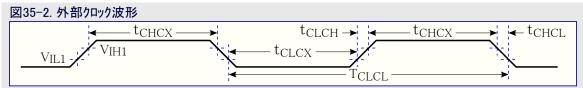

| 35. | 雷気的            | 内特性 •••••• 303                                                                                                                       |

|     | 35.1.          | お断り・・・・・・・・・・・・・・・・・・303                                                                                                             |

|     | 35.2.          | 絶対最大定格 ************************ 303                                                                                                  |

|     | 35.3.          | 標準動作条件 ******************** 303                                                                                                      |

|     | 35.4.          | 供給電圧 ····· 304                                                                                                                       |

|     | 35.5.          | 消費電力                                                                                                                                 |

|     | 35.6.          | 周辺機能消費電力 ····· 306                                                                                                                   |

|     | 35.7.          | 入出力ピン・・・・・・・・・・・・・・・・・・・・・・・・307                                                                                                     |

|     | 35.8.          | メモリ ノロク フェンク 仕様 ・・・・・・・・・・・・・・・・・・・・・・・・308                                                                                          |

|     | 30.9.          | メモリ プログラミング 仕様・・・・・・・308         温度仕様・・・・・・308         CLKCTRL・・・・・309                                                               |

|     | 35.10.         |                                                                                                                                      |

|     | 35.12          | VRFF                                                                                                                                 |

|     | 35.13.         | RSTCTRL&BOD                                                                                                                          |

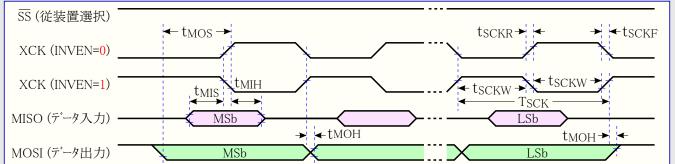

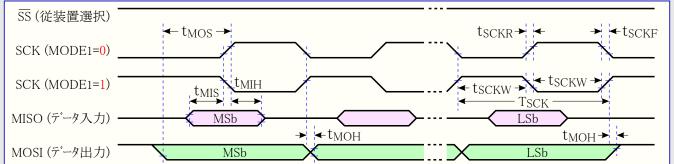

|     | 35 14          | <b>SPI</b>                                                                                                                           |

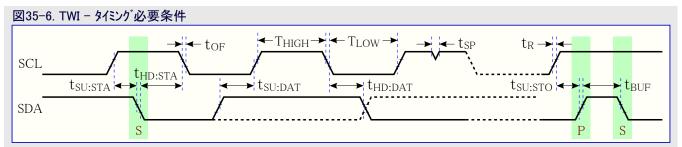

|     | 35.15.         | TWI                                                                                                                                  |

|     | 35.16.         | DAC                                                                                                                                  |

|     | 35.17.         | ADC                                                                                                                                  |

|     | 35.18.         | AC                                                                                                                                   |

|     | 35.19.         | <b>UPDI</b>                                                                                                                          |

| 36. | 特性國            | <b>X</b> •••••• 318                                                                                                                  |

| 37. | 注文             | <b>青報 ······</b> 319                                                                                                                 |

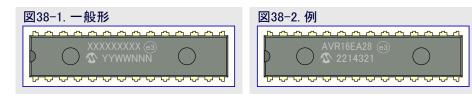

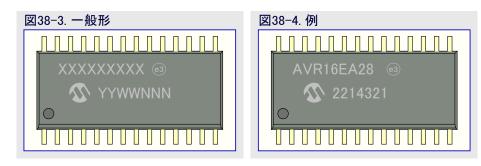

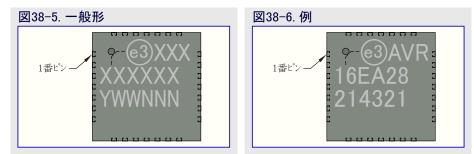

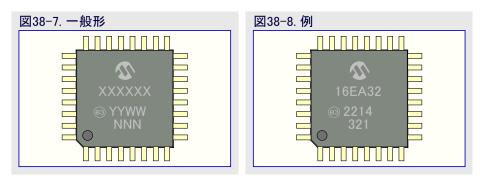

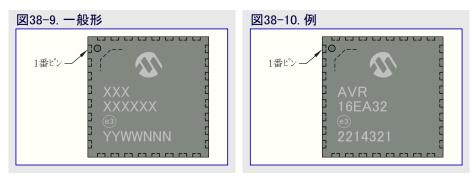

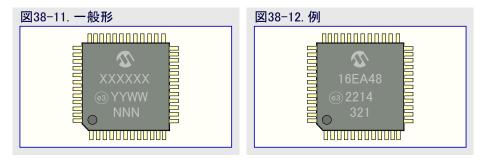

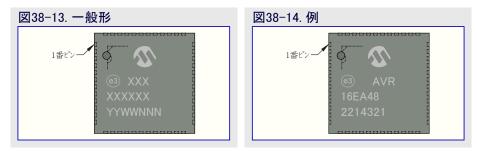

| 38. | 外囲             | 器図 ····· 320                                                                                                                         |

|     | 38.1.          | オンライン外囲器図 ······ 320                                                                                                                 |

|     | 38.2.          | <b>外囲器表示情報</b> ······ 320                                                                                                            |

|     | 38.3.          | <b>28Ľ&gt;SPDIP</b>                                                                                                                  |

|     | 38.4.          | オリフィレクト団盗図       320         外囲器表示情報       320         28ビンSPDIP       322         28リート*SSOP       323         28パット*VQFN       324 |

|     | 38.5.          | 28/1 ット VQFN 324                                                                                                                     |

|     | 38.6.          | <b>28</b> パット*VQFN 濡れ性側面 ······ 325<br>32リート*TQFP ····· 326                                                                          |

|     | 38.7.          | 329-r IQFP 326                                                                                                                       |

|     | 38.7.  | <b>32</b> ∧ <sup>°</sup> yh <sup>*</sup> VQFN       |

|-----|--------|-----------------------------------------------------|

|     | 38.8.  | <b>32</b> パット VQFN 濡れ性側面 ······ 328                 |

|     | 38.9.  | <b>48'J-h</b> <sup>*</sup> <b>TQFP</b>              |

|     |        | <b>48パット VQFN</b>                                   |

|     | 38.11. | <b>48</b> パット VQFN 濡れ性側面 ······ 331                 |

| 39. | 障害     | <b>青報 ······</b> 332                                |

| 40. | デーダン   | <b>/</b>                                            |

|     | 40.1.  | <b>改訂A - 2023年5月</b> ······ 336                     |

| Mic | rochip |                                                     |

|     | Micro  | <b>chipウェブ サイト</b> ····· 337                        |

|     | 製品     | <b>変更通知サービス ·····</b> 337                           |

|     |        | <b>美支援・・・・・・・・・・・・・・・・・・・・・</b> 337                 |

|     | 製品     | <b>哉別システム</b> · · · · · · · · · · · · · · · · · · · |

|     | Micro  | <b>chipデバイス コード保護機能 ・・・・・・・・・</b> 337               |

|     | 法的i    |                                                     |

|     | 商標     | 338                                                 |

|     | 品質管    | <b>管理システム ・・・・・</b> 338                             |

|     | 世界的    | <b>内な販売とサービス ・・・・・・・・・・・・・・・・</b> 339               |

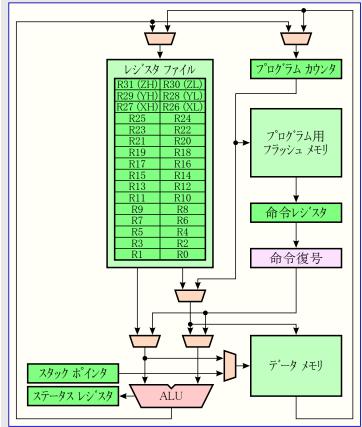

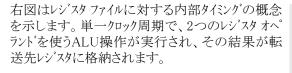

# 1. 構成図

# 2. ピン配置

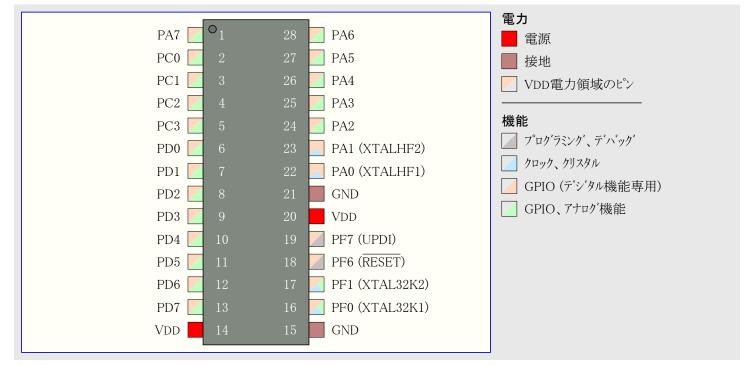

# 2.1. 28ピンSPDIP・28リート SSOP

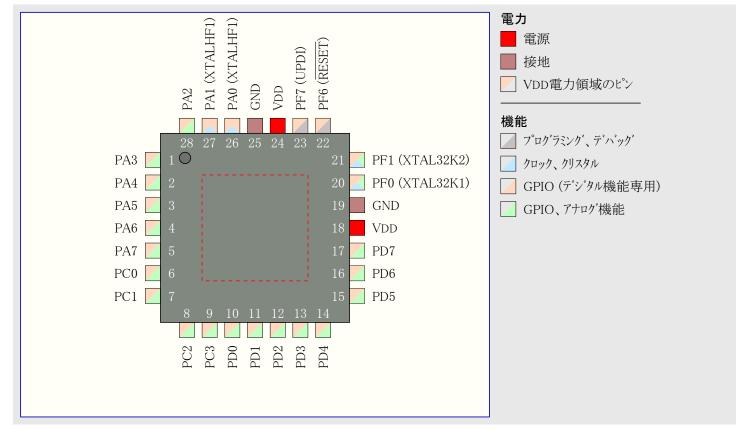

# 2.2. 28パット VQFN

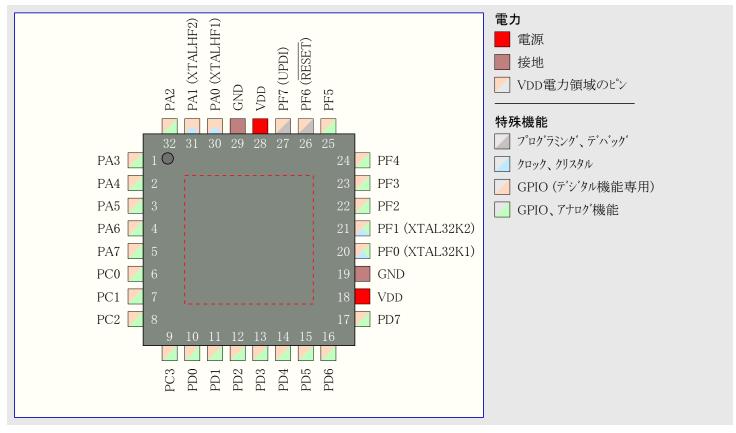

# 2.3. 32パッドVQFN・32リードTQFP

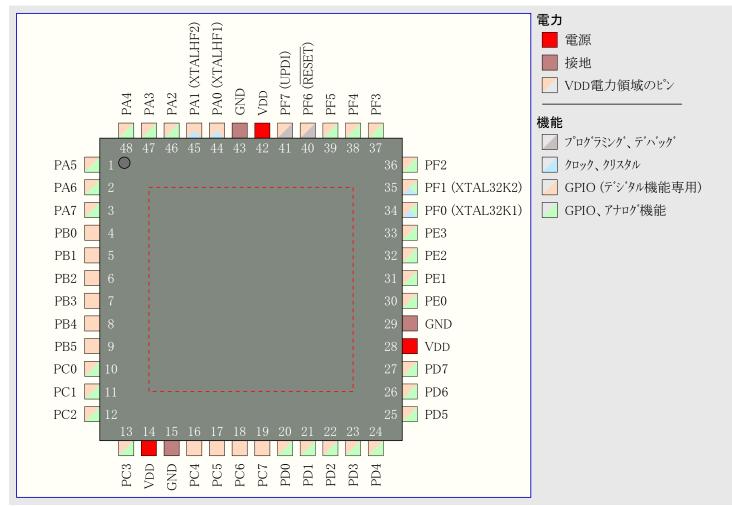

# 2.4. 48パッドVQFN・48リードTQFP

# 3. 入出力多重化と考察

# 3.1. 入出力多重化

表3-1. ポート機能多重化 (<u>注2</u>)

| 1                 |                   |          |                    |                            |                   |              |                         |      |                  |                      |                  |               |      |                |         |

|-------------------|-------------------|----------|--------------------|----------------------------|-------------------|--------------|-------------------------|------|------------------|----------------------|------------------|---------------|------|----------------|---------|

| VQFN48/<br>TQFP48 | VQFN32/<br>TQFP32 | VQFN28   | SPDIP28/<br>SSOP28 | ピン名<br>( <mark>注1</mark> ) | 特殊                | ADC0         | ACn                     | DAC0 | UARTn            | SPIO                 | TWI0<br>(注3)     | TCAn          | TCBn | CCL-<br>LUTn   | EVSYS   |

| 44                | 30                | 26       | 22                 | PA0                        | XTALHF1<br>EXTCLK |              |                         |      | 0,TxD            | MOSI                 | SDA(MS)          | 0,WO0         |      | 0,IN0          |         |

| 45                | 31                | 27       | 23                 | PA1                        | XTALHF2           |              |                         |      | 0,RxD            | MISO                 | SCL(MS)          | 0,WO1         |      | 0,IN1          |         |

| 46                | 32                | 28       | 24                 | PA2                        |                   | AIN22        |                         |      | 0,XCK•0,TxD      |                      | SDA(MS)          | 0,WO2         | 0,WO | 0,IN2          | EVOUTA  |

| 47                | 1                 | 1        | 25                 | PA3                        |                   | AIN23        |                         |      | 0,XDIR•0,RxD     |                      | SCL(MS)          | 0,WO3         | 1,WO | 0,OUT          |         |

| 48                | 2                 | 2        | 26                 | PA4                        |                   | AIN24        |                         |      | 0,TxD            | MOSI                 |                  | 0,WO4·1,WO0   |      |                |         |

| 1                 | 3                 | 3        | 27                 | PA5                        |                   | AIN25        |                         |      | 0,RxD            | MISO                 |                  | 0,WO5·1,WO1   |      |                |         |

| 2                 | 4                 | 4        | 28                 | PA6                        |                   | AIN26        |                         |      | 0,XCK            | SCK                  |                  | 1,WO2         |      | 0,OUT          |         |

| 3                 | 5                 | 5        | 1                  | PA7                        | CLKOUT            | AIN27        | 0,OUT · 1,OUT           |      | 0,XDIR           | SS                   |                  |               |      |                | EVOUTA  |

| 4                 | -                 | -        | -                  | PB0                        |                   |              |                         |      |                  |                      |                  | 0,WO0·1,WO0   |      |                |         |