## 特徴

- AVR® RISC構造

- AVR -高性能、低消費RISC構造

- 強力な118命令(多くは1周期で実行)

- 32個の1バイト長汎用レジスタ

- 1.5MHz時、1.5MIPSに達する高速動作

- 不揮発性プログラム用メモリとデータ用メモリ

- 8Kバイ(4K語)フラッシュメモリ内蔵 1000回の書き換えが可能

- 256バイトの内蔵SRAM

- 512バイトのEEPROM

100,000回の書き換えが可能

- ソフトウェア保護用の設定可能な施錠機能

#### • 内蔵周辺機能

- 独立した前置分周器付き8ビットタイマ/カウンタ

- 独立した前置分周器付き16ビットタイマ/カウンタ

- 6チャネル 10ビット A/D変換器

- 特殊マイクロ コントローラ機能

- アイドルとパワーダウンの2つの低消費動作

- 外部及び内部の割り込み

- 2つの外部割り込み

- 電気的特長

- 高速、低消費なCMOS製法

- 完全なスタティック動作

- 消費電流 (条件: 1.5MHz,3.6V,25℃)

- 活動動作 ••••• 1.2mA

- アイドル動作 ・・・・・・ 0.2mA

- パワーダウン動作 ・・・・ 10μA未満

#### • I/Oと外囲器

- 7ビットの標準出力

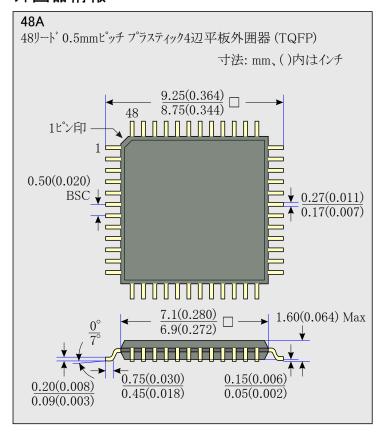

- 48"-FLQFP/VQFP

- 動作電圧

- -3.3~6.0V

- 動作速度

- $-0\sim1.5 MHz$

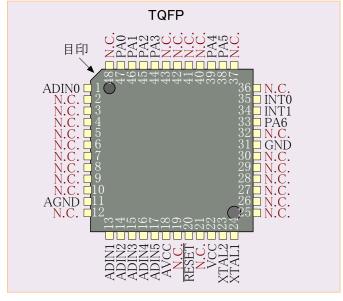

## ピン配置

#### (訳注)

原書に於いて、フラッシュメモリ やEEPROM書き込みを行う 並列プログラミングで使うPENピ ンが未定義です(記載されて いません)。

8ビット **AV** <sup>®</sup> マイクロ コントローラ 書き換え可能な 8 K ハ ´ イト フラッシュ メモリ内蔵

AT90C8534

暫定

本書は一般の方々の便宜のため有志によって作成されたもので、Atmel社とは無関係であることを御承知ください。しおりの[はじめに]での内容にご注意ください。

Rev. 1229B-11/00, 1229BJ18-07/22

## 概要

AT90C8534はAVR RISC構造の低消費CMOS 8ビット マイクロコントローラです。1周期で実行する強力な命令はMHzあたり1 MIPSに達し、実行速度対電力消費の最適化が容易に行えます。

AVRは32個の汎用レジスタと豊富な命令群を兼ね備えています。32個の全レジスタは、ALU(Arithmetic Logic Unit)に直結され、レジスタ間命令は1クロック周期で実行されます。AVR構造は現状のCISC型マイクロコントローラに対して、最大10倍の単位処理量向上効果があります。

AT90C8534は、8Kバイトの書き換え可能なフラッシュメモリ、512バイトのEEPROM、256バイトのSRAM、7ビットの汎用出力、2本の外部割り込み線、32個の汎用レジスタ、柔軟性のある2つのタイマ/カウンタ、内部及び外部割り込み、6チャネル 10ビット A/D変換器、ソフトウェアで選べる2つの低消費動作機能を提供します。アイドル動作では動作を停止しますが、A/D変換器、タイマ/カウンタ、割り込み機能は有効で動作を継続します。パワーダウン動作ではSRAMとレジスタの内容は保護されますが、発振器が停止するため、以降のハードウェアリセットか外部割り込みまで、他の全機能を無効にします。

本デバイスはAtmelの高密度不揮発性メモリ技術を使って製造されています。内蔵の書き換え可能なフラッシュ メモリはプログラム メモリに使え、規定の不揮発性メモリ書き込み器により、再書き込みができます。モノリシック チップ 上の実装書き換え可能なフラッシュ メモリと拡張された8ビットRISC型CPUの組み合わせによるAT90C8534は、多くの組み込み制御の応用に対して高度な柔軟性と対費用効果をもたらす強力なマイクロコントローラです。

AT90C8534 AVRはCコンパイラ、マクロ アセンブラ、デバッガ、シミュレータ、インサーキット エミューレータ、評価キットを含む完全なプログラム及びシステム開発ツールで支援されます。

### ピン概要

#### VCC

デジタル電源ピン。

#### **GND**

デジタル接地ピン。

#### PA6~PA0 (π°-\A)

ポートAは7ビットの3状態付き出力ポートです。ポートAの出力緩衝部は吸い込み電流が20mAで、LED表示器を直接駆動できます。リセット 条件が有効になると、クロックが動作していなくても、ポートAピンはHi-Zにされます。

#### INT1,0

外部割り込み入力ピンです。これらのピンの上昇端か下降端のどちらかが割り込み要求を発生します。クロックが動作していなくても、40nsより長いパルスは割り込みを発生します。

#### ADIN5~ADIN0

A/D変換器のアナログ入力ピンで、これらのピンの何れかがA/D変換器の入力として選ばれます。

#### RESET

リセット入力。外部リセットはRESETピンのLowレヘールにより生成されます。クロックが動作していなくても、100nsより長いリセット パルスはリセットを生成します。短すぎるパルスはリセットの生成が保証されません。

#### XTAL<sub>1</sub>

発振増幅器の反転入力。または外部発振入力。

#### XTAL2

発振増幅器の出力。

#### **AVCC**

A/D変換用アナログ電源ピンです。A/D変換を使われない場合、このピンはVCCに接続されなければなりません。A/D変換が使われる場合、このピンは低域通過濾波器を経由してVCCに接続されるべきです。A/D変換操作の詳細については、22頁を参照してください。

#### **AGND**

アナログ接地ピンです。分離したアナログGND面がある基板の場合、このピンはアナログGND面に接続されるべきです。その他の場合はGN D(ピン)に接続します。

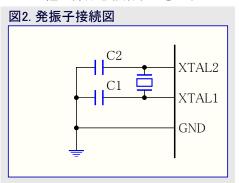

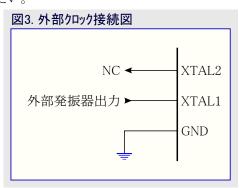

#### クロック発振器

XTAL1とXTAL2は、**図2**.に示される内蔵発振器に於ける反転増幅器の各々入力と出力です。クリスタル発振子かセラミック振動子のどちらかを使うことができます。外部クロック元から駆動するには、**図3**.で示されるようにXTAL1が駆動され、一方XTAL2は未接続のままにされるべきです。XTAL2が他の部品を駆動すべきでないことに注意してください。

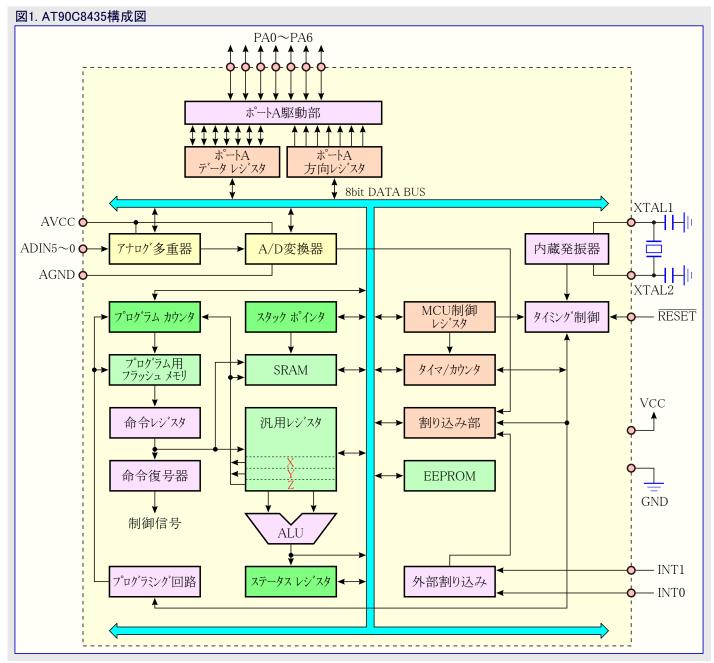

## 構造概要

高速レジスタファイルの概念は、1クロック周期アクセス時間の32個の8ビット長汎用レジスタを含みます。これは1クロック周期中に1つのALU(Arith metic Logic Unit)命令が実行されることを意味します。1クロック周期で、2つのオペランドはレジスタファイルから出力され、命令が実行され、その結果がレジスタファイルに書き戻されます。

32個中の6つのレジ、スタはデータ空間についてアト・レス計算が効率的に行える、3つの16ビット長間接アト・レス ポインタとして使うことができます。3つのアト・レス ポインタの1つは定数表参照用アト・レス ポインタとしても使われます。これらの付加機能レジ、スタは、16ビット長のXレジ、スタ、Yレジ、スタ、Zレジ、スタです。

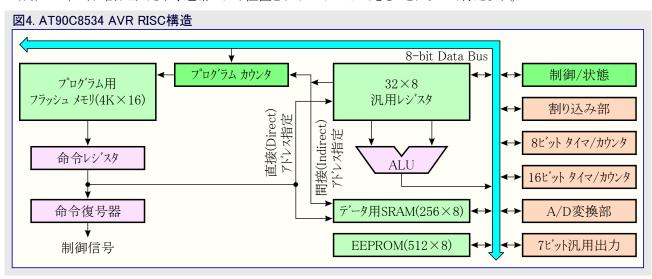

ALUはレジスタ間、レジスタと定数間の算術及び論理操作を行います。単一レジスタ操作も同様にALUで実行されます。**図4**.はAT90C 8534 AVR RISCマイクロ コントローラの構造を示します。

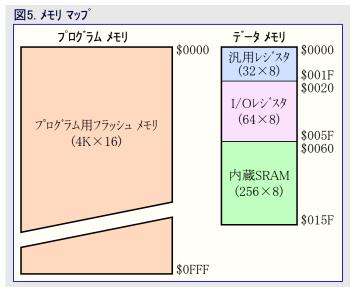

付加的なレジスタ操作として、通常のメモリアト・レス指定をレジスタファイルにも使うことができます。実際にはレジスタファイルがデータ空間の最下位32バイト(\$00~\$1F)に割り当てられ、通常のメモリ位置としてのアクセスができることによって行えます。

I/Oメモリ空間には、タイマ/カウンタ、A/D変換、その他I/O機能など、CPU周辺機能用の制御レジスタとして64アドレスがあります。I/Oメモリは直接またはレジスタ ファイルに後続するデータ空間位置\$20~\$5Fとしてアクセスできます。

AVRのメモリとバスは、プログラム用とデータ用に各々分離されたハーバード構造で構成されています。プログラム メモリは2段のパイプ ラインでアクセスされます。1命令の実行中に、次の命令をプログラム メモリから事前取得します。この概念は全てのクロック周期で命令が実行されるのを可能にします。プログラム メモリは書き換え可能なフラッシュ メモリです。

プログラム カウンタ(PC)相対の無条件分岐(RJMP)命令と呼び出し(RCALL)命令で、4K語(8Kバイト)アドレス空間全てがアクセスされます。AVRの多くの命令は16ビット1語の形式です。全てのプログラム メモリのアドレスに16または32ビット命令を配置できます。

割り込みやサブルーチン呼び出しでの戻りアドレスを示すプログラム カウンタ(PC)はスタックに保存されます。スタックは一般的なデータ用SRAMに配置され、スタック容量はSRAM容量とSRAM使用量でのみ制限されます。プログラムでは、リセット時の初期化ルーチンで(サブルーチンや割り込みが実行される前に)、スタック ポインタ(SP)を初期化しなければなりません。9ビットのスタック ポインタはI/O空間で読み書きできます。

256バイトのデータSRAMとレジスタ ファイルやI/Oレジスタは、AVR構造で支援される5つの異なるアドレス指定種別で容易にアクセスできます。

AVR構造に於けるメモリ空間は、全て直線的な普通のメモリ配置です。 柔軟な割り込み部には、I/O空間の各制御レジスタとステータス レジスタ (SREG)の全割り込み許可(I)ビットがあります。全ての割り込み要因はプログラム メモリの先頭に割り込みベクタ表として個別の割り込みベクタがあります。各割り込みは、この割り込みベクタ表の位置に従った優先順です。下位側割り込みベクタ アドレスが高い優先順位です。

#### 汎用レジスタファイル

図6.は32個の汎用レジスタの構成を示します。

全てのレジスタに対するレジスタ操作命令はレジスタ直接指定ができ、1周期でアクセスします。SBCI,SUBI,CPI,ANDI,ORIの5つの算術、論理定数演算命令と、定数をレジスタに設定するLDI命令だけ例外です。これらの命令はレジスタファイル後半のR16~R31に対して適用されます。通常のSBC,SUB,CP,AND,ORや他の全てのレジスタ間、単一レジスタ操作命令はレジスタファイルの全レジスタに適用されます。

図6.で示されるように、各レシ、スタはデータメモリ領域の先頭からの32アトレスに配置されています。レシ、スタファイルは物理的にSRAMのような配置構成ではなく、この特別な構成のため、X,Y,Zレジ、スタを指標とする任意のレシ、スタ指定のような、非常に柔軟なアクセスができます。

#### 図6. AVR CPU 汎用レジスタ構成図 0 アドレス R0 \$00 7 R15 \$0F R16 \$10 汎用 レジスタ 7 ファイル R26 \$1A Xレジスタ R27 上位バイ \$1B 下位バイト R28 \$1C Yレシブスタ R29 上位バイ \$1D 下位バイト R30 \$1E Zレジスタ R31 \$1F 上位バイト

#### Xレシ、スタ、Yレシ、スタ、Zレシ、スタ

レジスタR26~R31には、通常の汎用用途以外に、いくつかの付加機能があります。これらのレジスタは、データ空間の間接アトレス指定用ポインタにもなります。この3つの間接アトレス用レジスタX,Y,Zは図7.で定義されます。

これらのアドレスレシ、スタは定数変位付き、自動増加/減少付きのアドレス指定が行えます。(これらの概要は個別命令を参照してください。)

| 図7. X,Y,Zl           | <i>ジ</i> ス: | <b>対構成図</b> |     |            |   |

|----------------------|-------------|-------------|-----|------------|---|

|                      | 15          | (上位)        |     | (下位)       | 0 |

| X レシ <sup>*</sup> スタ | 7           | R27 (\$1B)  | 0 7 | R26 (\$1A) | 0 |

| Yレジスタ                | 7           | R29 (\$1D)  | 0 7 | R28 (\$1C) | 0 |

| Z レジスタ               | 7           | R31 (\$1F)  | 0 7 | R30 (\$1E) | 0 |

### ALU (Arithmetic Logic Unit)

高性能なAVRのALUは、32個全ての汎用レシ、スタに直接接続で動作します。レシ、スタファイル内のレシ、スタ間ALU操作は、1クロック周期内で実行されます。ALU操作は、算術演算、論理演算、ビット操作の3つの分野に分けられます。

#### 書き換え可能なプログラム用フラッシュ メモリ

AT90C8534には、プログラム用に書き換え可能な8Kバイトのフラッシュ メモリが内蔵されています。全ての命令が16または32ビット語のため、フラッシュ メモリは4K×16ビットとして構成されています。フラッシュ メモリは最低1000回再書き込みの耐久性があります。AT90C8534のプログラム カウンタ(PC)は12ビットで、プログラム メモリ内の4096アトレスを指定します。

定数表はアドレス0~4K内に割り当てられなければなりません。(LPM命令の説明参照)

プログラム メモリの各アドレス指定種別については6頁を参照してください。

#### データ用EEPROMメモリ

AT90C8534には、512バイトのデータ用EEPROMがあります。これは1バイト単位で読み書きできる独立データ空間として構成されます。 EEPROMは少なくても100,000回書き換えの耐久性があります。EEPROMとCPU間のアクセスは、20頁のEEPROMアドレス レジスタ、EEPROMデータ レジスタ、EEPROM制御レジスタで詳細に説明されます。

#### 内蔵SRAM

図8.はAT90C8534のデータメモリの構成を示します。

下位側352のデータメモリ位置はレジスタファイル、I/Oレジスタ、データ用内蔵SRAMを指定します。最初の96位置はレジスタファイルとI/Oレジスタを、次の256位置がデータ用内蔵SRAMを指定します。直接、間接、変位付き間接、事前減少付き間接、事後増加付き間接の5つのアドレス指定種別がデータメモリ空間を網羅します。レジスタファイル内のレジスタR26~R31が間接アドレス指定時のポインタレジスタです。

直接アドレス指定は全てのデータ アドレス空間に届きます。

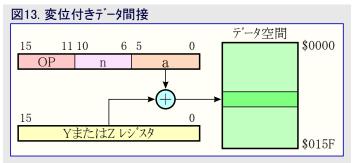

変位付き間接アドレス指定はYまたはZレジスタで与えられる基準アドレスから届く63アドレス位置が特徴です。

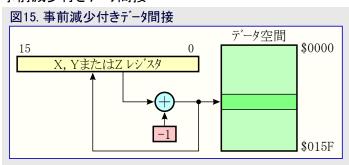

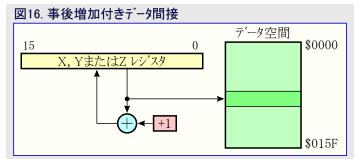

事前減少付き間接、事後増加付き間接アトンス指定を使う時にアトンスレジスタX,YまたはZが使われ、自動的に減少(-1)または増加(+1)されます。

AT90C8534の32個の汎用レジスタ、64個のI/Oレジスタ、256バイトのデータ用内蔵SRAMは、これら全てのアドレス指定種別を通して、全て直接的にアクセス可能です。

各アドレス指定種別の詳細説明については次章を参照してください。

|                            |        | アト・レス  |

|----------------------------|--------|--------|

|                            | R0     | \$0000 |

|                            | R1     | \$0001 |

| レシ <sup>・</sup> スタ<br>ファイル | }      |        |

| 7 / 1/1/                   | R30    | \$001E |

|                            | R31    | \$001F |

| I/O                        | \$00   | \$0020 |

| レジスタ                       | \$01   | \$0021 |

|                            | >      |        |

| (赤字は<br>I/O                | \$3E   | \$005E |

| I/O<br>アドレス)               | \$3F   | \$005F |

|                            | \$0060 | \$0060 |

|                            | \$0061 | \$0061 |

| 内蔵<br>SRAM                 | ~      |        |

| SIVAMI                     | \$015E | \$015E |

|                            | \$015F | \$015F |

## プログラム及びデータ空間に対するアドレス指定種別

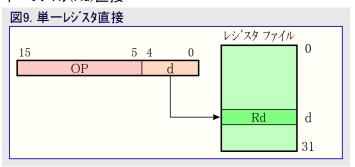

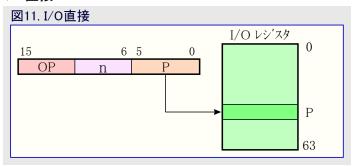

AT90C8534 AVR RISCマイクロコントローラは、プログラム(フラッシュ)メモリとデータ(SRAM,レシ、スタファイル,I/O)メモリのアクセス用に強力で効率的なアトレス指定種別を支援します。本項はAVR構造によって支援される各アトレス指定種別を記述します。図内のOPは命令語の動作符号部を意味します。単純化のため、全ての図がアトレス指定ビットの正確な位置を示すとは限りません。

#### 単一レジスタ(Rd)直接

オペラント、はレシ、スタd(Rd)を示します。

#### I/O直接

オヘ<sup>°</sup>ラント゛はI/Oアト゛レスPと、転送元または転送先となるレシ、スタn(Rn)を示します。

#### 変位付きデータ間接

オペラント、アトレスは、YまたはZレジスタの内容と命令語内の6ビット値aを加算した値となり、他方が転送元または転送先となるレジスタn(Rn)を示します。

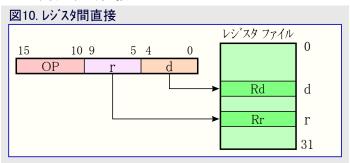

#### レジスタ間(Rd, Rr)直接

オペラント、はレジスタr(Rr)とd(Rd)を示し、結果はレジスタd(Rd)に格納されます。

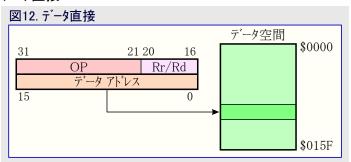

#### データ直接

オペラント、は2語命令の下位16ビットでデータ空間のアトレス位置を示し、Rr/Rdは転送元または転送先となるレジスタを示します。

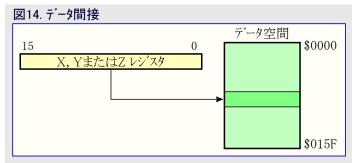

#### データ間接

オペラント、アトンスは、X, YまたはZレジスタの内容となります。

#### 事前減少付きデータ間接

X,YまたはZレシ、スタはアクセス動作前に内容が減少されます。オヘ。 ラント、アト・レスは減少されたX,YまたはZレシ、スタの内容となります。

#### 事後増加付きデータ間接

X,YまたはZレシ、スタはアクセス動作後に内容が増加されます。オペ。 ラント、アト、レスは増加される前のX,YまたはZレシ、スタの内容となります。

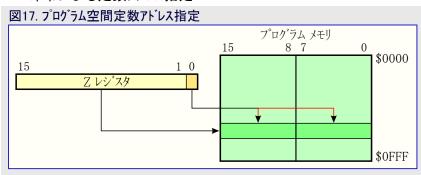

#### LPM命令による定数アドレス指定

ハイト定数のアトレスはZレジスタの内容で示されます。上位15ビットが0~4Kの語(ワート)アトレスを指示し、最下位ビットがハイト位置を表し、LSB=0で下位ハイト、LSB=1で上位ハイトを示します。

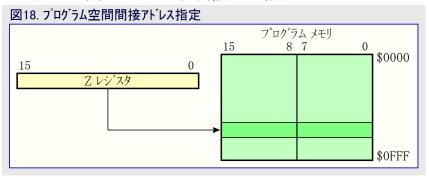

#### IJMP. ICALL命令によるプログラム間接アトレス指定

プログラムはZレシ、スタの内容のアト・レスから実行が継続されます。(PCにZレシ、スタの内容を設定します。)

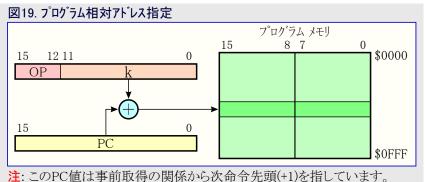

#### RJMP, RCALL命令によるプログラム相対アドレス指定

プログラムはPC+k+1のアドレスから継続実行されます。相対値kは符号付きで、-2048~2047です。

#### メモリ アクセスと命令実行タイミング

本項は命令実行と内部メモリ アクセスについての一般的なアクセス タイミングの概念を記述します。

AVR CPUは外部クロック クリスタルから直接的に生成されるシステム クロックゅによって駆動されます。内部クロック分周は使われません。

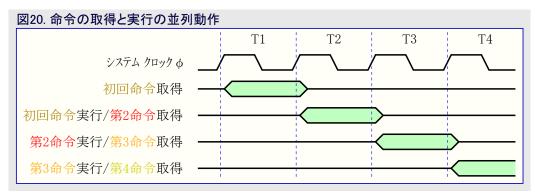

図20.はハーハート・構造と高速アクセスレシ、スタファイルの概念によって可能となる命令取得と命令実行の並列動作を示します。これは機能対費用、機能対クロック、機能対電源部での好結果に相当するMHzあたり1 MIPSまでを得る基本的なパイプラインの概念です。

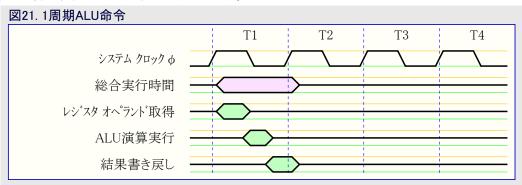

図21.はレシ、スタファイルに対する内部タイミングの概念を示します。2つのレジ、スタオペ・ラント、を使うALU操作は、転送先レジ、スタへの結果書き戻しを含め、単一クロック周期で実行されます。

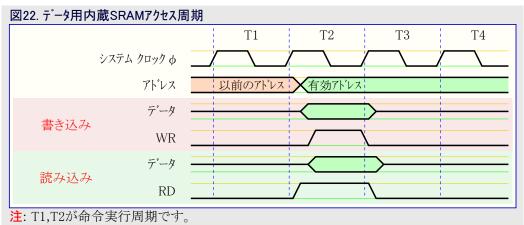

データ用内蔵SRAMのアクセスは、図22.で示されるように、2システム クロック周期実行されます。

#### I/O レジスタ

AT90C8534のI/O領域定義は表1.に示されます。

#### 表1. AT90C8534 I/Oレジスタ

| アト・レス       | レジスタ名  |                        | 機能                                    |

|-------------|--------|------------------------|---------------------------------------|

| \$3F (\$5F) | SREG   | ステータス レジスタ             | Status Register                       |

| \$3E (\$5E) | SPH    | スタック ポインタ上位            | Stack Pointer High                    |

| \$3D (\$5D) | SPL    | スタック ポインタ下位            | Stack Pointer Low                     |

| \$3B (\$5B) | GIMSK  | 一般割り込み許可レジスタ           | General Interrupt MaSK register       |

| \$3A (\$5A) | GIFR   | 一般割り込みフラグレジブスタ         | General Interrupt Flag register       |

| \$39 (\$59) | TIMSK  | タイマ/カウンタ割り込み許可レジブスタ    | Timer/Counter Interrupt MaSK register |

| \$38 (\$58) | TIFR   | タイマ/カウンタ割り込み要求フラグ レジスタ | Timer/Counter Interrupt Flag register |

| \$35 (\$55) | MCUCR  | MCU制御レシ、スタ             | MCU general Control Register          |

| \$33 (\$53) | TCCR0  | タイマ/カウンタ0 制御レシブスタ      | Timer/Counter 0 Control Register      |

| \$32 (\$52) | TCNT0  | タイマ/カウンタ0 カウンタ         | Timer/CouNTer 0 (8bit)                |

| \$2E (\$4E) | TCCR1  | タイマ/カウンタ1 制御レシブスタ      | Timer/Counter 1 Control Register      |

| \$2D (\$4D) | TCNT1H | タイマ/カウンタ1 カウンタ上位       | Timer/CouNTer 1 High byte             |

| \$2C (\$4C) | TCNT1L | タイマ/カウンタ1 カウンタ下位       | Timer/CouNTer 1 Low byte              |

| \$1F (\$3F) | EEARH  | EEPROMアドレス上位 レジスタ      | EEPROM Address Register high byte     |

| \$1E (\$3E) | EEARL  | EEPROMアドレス下位 レジスタ      | EEPROM Address Register low byte      |

| \$1D (\$3D) | EEDR   | EEPROMテータ レシ、スタ        | EEPROM Data Register                  |

| \$1C (\$3C) | EECR   | EEPROM制御レシブスタ          | EEPROM Control Register               |

| \$1B (\$3B) | PORTA  | ポートA出力データ レジスタ         | Data Register, Port A                 |

| \$1A (\$3A) | DDRA   | ポートA方向レシ、スタ            | Data Direction Register, Port A       |

| \$10 (\$30) | GIPR   | 外部割り込み入力レジブスタ          | General Interrupt Pin Register        |

| \$07 (\$27) | ADMUX  | A/D多重器選択レジスタ           | ADC Multiplexer Select Register       |

| \$06 (\$26) | ADCSR  | A/D変換制御/状態レジスタ         | ADC Control and Status Register       |

| \$05 (\$25) | ADCH   | A/Dデータ レジスタ上位          | ADC Data Register High                |

| \$04 (\$24) | ADCL   | A/Dデータ レジスタ下位          | ADC Data Register Low                 |

**注**: 予約と未使用の位置は、この表で示されていません。()内のアドレスはデータ空間の一部としてアクセスする場合のアドレスです。

AT90C8534の全てのI/Oと周辺部はI/O空間に配置されています。各I/O位置は、I/O空間と32個の汎用レジスタ間のデータ移動を行うIN命令とOUT命令によりアクセスされます。アドレス\$00~\$1F範囲内のI/Oレジスタは、SBIとCBI命令を使う直接ビットアクセスが可能です。これらのレジスタでは、SBISとSBIC命令の使用により、単一ビット値の検査ができます。より詳細な内容は命令要約を参照してください。I/O指定命令INとOUTを使う時にI/Oアドレス\$00~\$3Fが使われなければなりません。I/OレジスタをSRAMとしてアクセスする時に\$20がこのアドレスに加算されなければなりません。本文書を通して、全てのI/Oレジスタアドレスは、()内でデータ空間アドレスが示されます。

将来のデバイスとの共通性を保つため、予約ビットに書く場合は0を書くべきです。予約済みI/Oアドレスは決して書かれるべきではありません。

状態フラグのいくつかは、論理1を書くことで解除(0)されます。CBIとSBI命令はI/Oレジスタ内の全ビットを操作し、設定(1)として読むフラグは1が書き戻され、従ってフラグを解除(0)することに注意してください。CBIとSBI命令は、レジスタ\$00~\$1Fでのみ動作します。

I/Oと周辺制御レジスタは次章で説明されます。

#### ステータス レジスタ (Status Register) SREG

AVRのステータス レシ、スタ(SREG)は、I/O領域の\$3F(\$5F)で、次のように定義されています。

| ピット         | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _    |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$3F (\$5F) | I   | Т   | Н   | S   | V   | N   | Z   | С   | SREG |

| Read/Write  | R/W |      |

| 初期値         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

#### • ビット7 - I: 全割り込み許可 (Global Interrupt Enable)

この全割り込み許可ビットは、割り込みを許可する場合、設定(1)しなければなりません。各割り込みの許可は各制御レジスタで個別に行います。全割り込み許可ビットが解除(0)されると、個別に割り込みが許可されていても割り込みは発生しません。このIビットは割り込み発生後、自動的に解除(0)され、後続の割り込みを許可するため、割り込み処理のRETI命令によって設定(1)されます。

#### • ビット6 - T: ビット変数 (Bit Copy Storage)

このTビットは、BLD(Bit LoaD)命令とBST(Bit STore)命令の転送元または転送先として使われます。BLD命令はTをレジスタ ファイルのレ ジスタのビットに複写し、BST命令はレジスタ ファイルのレジスタからビットをTに複写します。

#### • ビット5 - H : ハーフキャリー フラク (Half Carry Flag)

このHフラグはいくつかの算術演算命令でのハーフキャリーを示します。ハーフキャリーはBCD演算に有用です。詳細情報については命令要約を参照してください。

#### • ビット4 - S: 符号 (Sign Bit, S= N Ex-OR V)

このSフラグは常に負(N)フラグと2の補数溢れ(V)フラグの排他的論理和です。詳細情報については命令要約を参照してください。

#### • ビット3 - V: 2の補数溢れフラグ(2's Complement Overflow Flag)

この2の補数溢れ(V)フラグは2の補数算術演算を補助します。詳細情報については命令要約を参照してください。

### • t "y h 2 - N: 負フラグ (Negative Flag)

このNフラグは算術及び論理演算の結果が負であること(MSB=1)を示します。詳細情報については命令要約を参照してください。

#### • L'yh1 - Z : t'D 750 (Zero Flag)

このZフラグは算術及び論理演算の結果がゼロ(0)であることを示します。 詳細情報については命令要約を参照してください。

#### • Ľット0 – C: キャリー フラク (Carry Flag)

このCフラグは算術及び論理演算でキャリーが発生したことを示します。詳細情報については命令要約を参照してください。

ステータス レシ スタは割り込み処理ルーチン移行時の保存と、割り込み処理ルーチンから復帰時の再設定が、自動的に行われないことに注意してください。これはソフトウェアにより操作しなければなりません。

#### スタック ホーインタ (Stack Pointer) SPH.SPL (SP)

I/Oアドレス\$3D(\$5D)と\$3E(\$5E)の2つの8ビット レジスタがAT90C8534のスタック ポインタを形成します。この9ビットが領域\$60~\$15F内の256 バイトSRAMを指し示すのに使われます。

| ピット         | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |     |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| \$3E (\$5E) | -   | -   | -   | -   | -   | -   | -   | SP8 | SPH |

| Read/Write  | R   | R   | R   | R   | R   | R   | R   | R/W |     |

| 初期値         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |     |

| ピット         | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _   |

| \$3D (\$5D) | SP7 | SP6 | SP5 | SP4 | SP3 | SP2 | SP1 | SP0 | SPL |

| Read/Write  | R/W |     |

| 初期値         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |     |

スタック ポインタはサブルーチンと割り込みのスタックが配置されるデータSRAMのスタック領域を指し示します。データSRAM内のスタック領域は、割り込みの許可や、何れかのサブルーチン呼び出しが実行される前にプログラムによって定義されなければなりません。スタック ポインタは \$60以上を指示するために設定されなければなりません。スタック ポインタは、PUSH命令でデータがスタック上に格納されるときー1され、サブルーチン呼び出しや割り込みでアドレスがスタック上に格納されるときー2されます。POP命令でデータをスタックから引き出すとき+1され、サブルーチンからの復帰(RET命令)や割り込みからの復帰(RETI命令)でアドレスをスタックから引き出すとき+2されます。

### リセットと割り込みの扱い

AT90C8534には6種類の割り込みがあります。これらの割り込みとリセットのベクタは、プログラム メモリ空間内に各々個別のベクタを持っています。全ての割り込みは、割り込みを許可するために、個別の許可ビットとステータス レジスタ(SREG)の全割り込み許可(I)ビットを設定(1)しなければなりません。

プログラム メモリ空間の最下位アドレスは、リセットと割り込みのヘブクタとして自動的に定義されています。このヘブクタの全一覧は**表2**.に示されます。この一覧が各割り込みの優先順位も決めます。下位アドレスがより高い優先順位です。リセットが最高優先順位で、以下、外部割り込み要求の(INTO)の順です。

表2. リセットと割り込みのベクタ

| ベクタ番号 | プログラム アトレス | 発生元            | 備考              |

|-------|------------|----------------|-----------------|

| 1     | \$000      | リセット           | 電源ONまたは外部等のリセット |

| 2     | \$001      | INT0           | 外部割り込み要求0       |

| 3     | \$002      | INT1           | 外部割り込み要求1       |

| 4     | \$003      | タイマ/カウンタ1 OVF1 | タイマ/カウンタ1溢れ     |

| 5     | \$004      | タイマ/カウンタ0 OVF0 | タイマ/カウンタ0溢れ     |

| 6     | \$005      | A/D変換器 ADC     | A/D変換完了         |

| 7     | \$006      | EEPROM EE_RDY  | EEPROM操作可       |

リセットと割り込みのベクタの最も代表的な設定例を次に示します。

| アト・レス | ラヘ゛ル   | 命令   |                    | 注釈               |

|-------|--------|------|--------------------|------------------|

| \$000 |        | RJMP | RESET              | ;各種リセット          |

| \$001 |        | RJMP | EXT_INTO           | ;外部割り込み要求0       |

| \$002 |        | RJMP | EXT_INT1           | ;外部割り込み要求1       |

| \$003 |        | RJMP | TIM1_OVF           | ;タイマ/カウンタ1溢れ     |

| \$004 |        | RJMP | TIMO_OVF           | ;タイマ/カウンタ0溢れ     |

| \$005 |        | RJMP | ADC                | ;A/D変換完了         |

| \$006 |        | RJMP | EE_RDY             | ;EEPROM操作可       |

| ;     |        |      |                    |                  |

| \$007 | RESET: | LDI  | R16, HIGH (RAMEND) | ;RAM最終アドレス上位を取得  |

| \$008 |        | OUT  | SPH, R16           | ;スタック ポインタ上位を初期化 |

| \$009 |        | LDI  | R16, LOW (RAMEND)  | ;RAM最終アドレス下位を取得  |

| \$00A |        | OUT  | SPL, R16           | ;スタック ポインタ下位を初期化 |

|       |        | >    |                    | ;以下、I/O初期化など     |

#### リセット

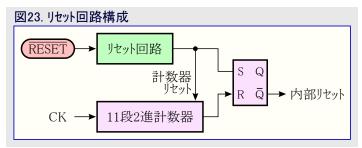

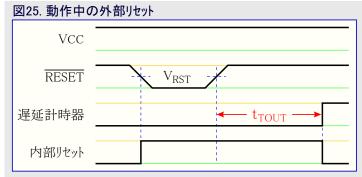

リセットによって全I/Oレシ、スタは初期値になり、アトレス\$000からプログラムが開始されます。アトレス\$000はリセット処理ルーチンに対する無条件相対分岐(RJMP)命令でなければなりません。プログラムで割り込みを禁止する場合、割り込みへ、クタがこれらの領域を使わないので、この領域に通常のプログラムを記述することができます。図23.にリセット部の回路構成を示します。表3.と図24、図25.にはリセット回路の電気的特性とタイミングを示します。

#### 表3. リセット電気的特性 (VCC=5.0V)

| シンホ゛ル            | 項目          | 最小 | 代表     | 最大 | 単位 |

|------------------|-------------|----|--------|----|----|

| V <sub>RST</sub> | RESETピン閾値電圧 |    | 0.6VCC |    | V  |

| ${ m t_{TOUT}}$  | リセット遅延時間    | I  | 1026   | -  | CK |

#### 外部リセット

AT90C8534には、外部リセット ピンがあり、次の3つの目的で使われます。

- ・電源ONリセット・・・・・・・・・・・・・・・・電源投入中、外部リセットはVCCが最低動作電圧に到達後100nsまで有効(Low)レベルが保持されなければなりません。

- ・ブラウンアウト(低電圧)リセット・・・動作中にVCCが最低動作電圧以下に下がる場合、外部リセットは直ちに有効にしなければならず、 VCCが最低動作電圧へ復帰後100nsまで有効レヘルが保持されなければなりません。

- ・通常リセット・・・・・・・・・・・・通常動作中、外部リセットを最低100ns有効に保持することによりリセットが生成されます。

外部リセットが開放されると、外部クロック入力から駆動される内部計数器(計時器)が起動され、外部クロックが表3.に示される回数を確実にH/L交互変移されるまで、内部リセットは有効を保持します。これは図24.と図25.に示されます。

#### 割り込み

AT90C8534には、一般割り込み許可レジスタ(GIMSK)とタイマ/カウンタ割り込み許可レジスタ(TIMSK)の2つの8ビット割り込み許可レジスタがあります。

割り込みが起こると、ステータス レジスタ(SREG)の全割り込み許可(I)ビットが解除(0)され、全ての割り込みが禁止されます。ソフトウェアは多重割り込みを許可するために、全割り込み許可(I)ビットを設定(1)できます。この全割り込み許可(I)ビットは、割り込みからの復帰(RETI)命令が実行される時に設定(1)されます。

割り込み処理ルーチンを実行するために、プログラム カウンタが実際の割り込みへ、クタを指示するとき、割り込みを起こした対応する割り込み要求フラグを自動的に解除(0)します。いくつかの割り込み要求フラグは、そのフラグのビット位置に論理1を書くことによっても解除(0)できます。

対応する割り込み許可ビットが解除(0)されている時に割り込み条件が発生すると、対応する割り込み要求フラグが設定(1)され、その割り込みが許可または、ソフトウェアで解除(0)されるまで保持されます。

全割り込み許可(I)ビットが解除(0)されている時に1つまたは多くの割り込み条件が発生すると、対応する割り込み要求フラグが設定(1)され、全割り込み許可(I)ビットが設定(1)されるまで保持されます。許可後、それらは優先順に実行されます。

ステータス レジ スタ(SREG)は割り込み処理ルーチンへの移行時の保存と割り込み処理ルーチンからの復帰時の再設定が自動的に行われないことに注意してください。これはソフトウェアにより操作しなければなりません。

#### 一般割り込み許可レジスタ (General Interrupt Mask Register) GIMSK

| ピット         | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 | _     |

|-------------|------|------|---|---|---|---|---|---|-------|

| \$3B (\$5B) | INT1 | INT0 | - | - | - | - | - | - | GIMSK |

| Read/Write  | R/W  | R/W  | R | R | R | R | R | R |       |

| 初期値         | 0    | 0    | 0 | 0 | 0 | 0 | 0 | 0 |       |

#### • ビットフ - INT1:外部割り込み1許可 (External Interrupt Request 1 Enable)

ステータス レシ、スタ(SREG)の全割り込み許可(I)ビットとINT1ビットが共に設定(1)されると、外部(INT1)ピン割り込みが許可されます。この外部割り込みはMCU制御レシ、スタ(MCUCR)の割り込み条件制御1(ISC1)ビットの指定により、INT1ピンの上昇端または下降端で起動されます。外部割り込み要求1に対応するプログラムはプログラム メモリ アト・レス\$002から実行されます。「外部割り込み」も参照してください。

#### • ビット6 - INTO:外部割り込み0許可 (External Interrupt Request 0 Enable)

ステータス レシ、スタ(SREG)の全割り込み許可(I)ビットとINTOビットが共に設定(1)されると、外部(INTO)ピン割り込みが許可されます。この外部割り込みはMCU制御レシ、スタ(MCUCR)の割り込み条件制御の(ISCO)ビットの指定により、INTOピンの上昇端または下降端で起動されます。外部割り込み要求のに対応するプログラムはプログラムメモリアドレス\$001から実行されます。「外部割り込み」も参照してください。

#### • ビット5~0 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

#### 一般割り込み要求フラグレジスタ (General Interrupt Flag Register) GIFR

| ピット         | 7     | 6     | 5 | 4 | 3 | 2 | 1 | 0 | _    |

|-------------|-------|-------|---|---|---|---|---|---|------|

| \$3A (\$5A) | INTF1 | INTF0 | - | - | - | - | - | - | GIFR |

| Read/Write  | R/W   | R/W   | R | R | R | R | R | R |      |

| 初期値         | 0     | 0     | 0 | 0 | 0 | 0 | 0 | 0 |      |

#### • ビット7 - INTF1:外部割り込み1要求フラグ(External Interrupt Flag1)

INT1ピン上の出来事が割り込み要求を起こすと、INTF1が設定(1)になります。このとき、ステータスレシ、スタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レシ、スタ(GIMSK)の外部割り込み1許可(INT1)ピットが共に設定(1)されていれば、MCUはアドレス\$002の割り込みへクタへ飛びます。このフラグは割り込みヘクタを取得する時に解除(0)されます。代わりに論理1を書くことによっても解除(0)できます。

#### • ビット6 - INTFO:外部割り込み0要求フラグ(External Interrupt Flag0)

INTOピン上の出来事が割り込み要求を起こすと、INTFOが設定(1)になります。このとき、ステータスレン、スタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レン、スタ(GIMSK)の外部割り込み0許可(INTO)ビットが共に設定(1)されていれば、MCUはアドレス\$001の割り込みへ、クタへ飛びます。このフラグは割り込みへ、クタを取得する時に解除(0)されます。代わりに論理1を書くことによっても解除(0)できます。

## • ビット5~0 - Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

#### 外部割り込み入力レジスタ (General Interrupt Pin Register) GIPR

| ピット         | 7 | 6 | 5 | 4 | 3     | 2     | 1 | 0 | _    |

|-------------|---|---|---|---|-------|-------|---|---|------|

| \$10 (\$30) | _ | - | - | - | IPIN1 | IPIN0 | - | - | GIPR |

| Read/Write  | R | R | R | R | R     | R     | R | R |      |

| 初期値         | 0 | 0 | 0 | 0 | 不定    | 不定    | 0 | 0 |      |

• ビット7~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

• ビット3 - IPIN1:外部割り込み1入力(External Interrupt Pin 1)

このビットの読み込みはINT1ピン入力上に存在する(同期ラッチ後の)論理値が戻ります。

• ビット2 - IPIN0:外部割り込み0入力(External Interrupt Pin 0)

このビットの読み込みはINT0ピン入力上に存在する(同期ラッチ後の)論理値が戻ります。

• ビット1,0 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

#### タイマ/カウンタ割り込み許可レジスタ (Timer/Counter Interrupt Mask Register) TIMSK

| ピット         | 7 | 6 | 5 | 4 | 3 | 2     | 1 | 0     |       |

|-------------|---|---|---|---|---|-------|---|-------|-------|

| \$39 (\$59) | _ | _ | _ | _ | - | TOIE1 | - | TOIE0 | TIMSK |

| Read/Write  | R | R | R | R | R | R/W   | R | R/W   |       |

| 初期値         | 0 | 0 | 0 | 0 | 0 | 0     | 0 | 0     |       |

• ビット7~3 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

• ピット2 - TOIE1: タイマ/カウンタ1溢れ割り込み許可 (Timer/Counter1 Overflow Interrupt Enable)

ステータス レジスタ(SREG)の全割り込み許可(I)ビットとTOIE1ビットが共に設定(1)されると、タイマ/カウンタ1溢れ割り込みが許可されます。タイマ/カウンタ1溢れが起こる、換言すると、タイマ/カウンタ割り込み要求フラグ レジスタ(TIFR)のタイマ/カウンタ1溢れ割り込み要求フラグ (TOV1)が設定(1)されると、対応する割り込み(ベクタ \$003)が実行されます。

• ビット1 - Res: 予約 (Reserved)

このビットは予約されており、常に0として読みます。

• ビット0 - TOIE0: タイマ/カウンタ0溢れ割り込み許可 (Timer/Counter0 Overflow Interrupt Enable)

ステータス レジ スタ(SREG)の全割り込み許可(I)ビットとTOIE0ビットが共に設定(1)されると、タイマ/カウンタ0溢れ割り込みが許可されます。タイマ/カウンタ0溢れが起こる、換言すると、タイマ/カウンタ割り込み要求フラケ レジ スタ(TIFR)のタイマ/カウンタ0溢れ割り込み要求フラケ (TOV0)が設定(1)されると、対応する割り込み(ベクタ \$004)が実行されます。

#### タイマ/カウンタ割り込み要求フラグ レジスタ (Timer/Counter Interrupt Flag Register) TIFR

| ピット         | 7 | 6 | 5 | 4 | 3 | 2    | 1 | 0    | _    |

|-------------|---|---|---|---|---|------|---|------|------|

| \$38 (\$58) | - | - | - | - | - | TOV1 | - | TOV0 | TIFR |

| Read/Write  | R | R | R | R | R | R/W  | R | R/W  |      |

| 初期値         | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0    |      |

• ビット7~3 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

• ビット2 - TOV1 : タイマ/カウンタ1溢れ割り込み要求フラヴ(Timer/Counterl Overflow Interrupt Flag)

タイマ/カウンタ1溢れが起きる時にTOV1が設定(1)されます。TOV1は割り込みへ、クタを取得する時に解除(0)されます。代わりに、このフラク、へ論理1を書くことによっても、TOV1は解除(0)されます。ステータスレジ、スタ(SREG)の全割り込み許可(I)ビットとタイマ/カウンタ割り込み許可レジスタ(TIMSK)のタイマ/カウンタ1溢れ割り込み許可(TOIE1)ビットとTOV1が設定(1)されれば、タイマ/カウンタ1溢れ割り込みが実行されます。

• **ビット1 - Res**: 予約 (Reserved)

このビットは予約されており、常に0として読みます。

• ビット0 - TOV0: タイマ/カウンタ0溢れ割り込み要求フラグ(Timer/Counter0 Overflow Interrupt Flag)

タイマ/カウンタ0溢れが起きる時にTOV0が設定(1)されます。TOV0は割り込みへ、クタを取得する時に解除(0)されます。代わりに、このフラケーへ論理1を書くことによっても、TOV0は解除(0)されます。ステータスレジ、スタ(SREG)の全割り込み許可(I)ビットとタイマ/カウンタ割り込み許可レジスタ(TIMSK)のタイマ/カウンタ0溢れ割り込み許可(TOIE0)ビットとTOV0が設定(1)されれば、タイマ/カウンタ0溢れ割り込みが実行されます。

#### 外部割り込み

外部割り込みはINT0またはINT1ピンによって起動されます。外部割り込みは上昇端または下降端で起動できます。これはMCU制御レジスタ(MCUCR)についての詳細で説明されるように設定します。

#### 割り込み応答時間

全ての許可された割り込みについての割り込み実行応答時間は最小4クロックです。割り込み要求フラグが設定(1)されてしまった後の4ク ロック周期で実際の割り込み処理ルーチン用の割り込みへ、クタアトレスが実行されます。この4クロック周期期間中、プログラム カウンタ(2バイト)がスタック上に保存(プッシュ)され、スタック ポインタが減少(-2)されます。通常、このヘブクタは割り込み処理ルーチンに対する無条件相対分岐(RJMP)命令で、この分岐に2クロック周期かかります。複数周期の命令実行中に割り込みが起こると、割り込みが扱われる前にその命令が完了されます。

割り込み処理ルーチンからの復帰は4クロック周期要します。この4クロック周期中にスタックからプログラム カウンタ(2バイト)が回復(ポップ)され、スタック ポインタが増加(+2)されて、ステータス レジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されます。割り込みを抜ける 時は常に主(元の) プログラムへ復帰し、保留されている割り込みが扱われる前に1つ以上の命令を実行します。

#### MCU制御レシ、スタ (MCU Control Register) MCUCR

このMCU制御レジスタは、一般的なMCU機能の制御ビットで構成されます。

| ピット         | 7 | 6   | 5   | 4 | 3 | 2    | 1 | 0    | _     |

|-------------|---|-----|-----|---|---|------|---|------|-------|

| \$35 (\$55) | - | SE  | SM  | - | - | ISC1 | - | ISC0 | MCUCR |

| Read/Write  | R | R/W | R/W | R | R | R/W  | R | R/W  |       |

| 初期値         | 0 | 0   | 0   | 0 | 0 | 0    | 0 | 0    |       |

• ビット7 - Res: 予約 (Reserved)

このビットは予約されており、常に0として読みます。

• ビット6 - SE: 休止許可 (Sleep Enable)

SLEEP命令が実行される時にMCUを休止形態へ移行させるには、休止許可(SE)ビットが設定(1)されなければなりません。MCUの目的外休止形態移行をなくすため、SLEEP命令実行直前に休止許可(SE)ビットを設定(1)することが推奨されます。

• ビット5 - SM: 休止種別 (Sleep Mode Select)

このピットは利用可能な2つの休止形態種別を選びます。SMが解除(0)されると休止形態としてアイドル動作が選ばれます。SMが設定(1)されると休止形態としてパワーダウン動作が選ばれます。詳細については、「休止形態」章を参照してください。

• ビット4.3 - Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

• ビット2 - ISC1:外部割り込み1条件制御 (Interrupt Sense Control 1)

外部割り込み1はステータス レジスタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レジスタ(GIMSK)の対応する割り込み許可、外部割り込み1許可(INT1)ピットが設定(1)されている場合の外部(INT1)ピンにより起動されます。ISC1が解除(0)されると、INT1の下降端が割り込みを起こします。ISC1が設定(1)されると、INT1の上昇端が割り込みを起こします。INT1の端(エッジ)は非同期に検出されます。40nsより広いINT1のパルスは割り込みを生成します。短すぎるパルスは割り込みの発生が保証されません。

ISC1ビット変更時、割り込みが起き得ます。従って一般割り込み許可レジスタ(GIMSK)の割り込み許可(INT1)ビットを解除(0)することによって、最初にINT1を禁止することが推奨されます。その後、ISC1ビットは変更できます。最後は、割り込みが再許可される前に一般割り込み要求フラグレジスタ(GIFR)の外部割り込み1要求フラグ(INTF1)に論理1を書くことにより、INT1割り込み要求フラグが解除(0)されるべきです。

• **ビット1 - Res**: 予約 (Reserved)

このビットは予約されており、常に0として読みます。

• ビット0 - ISCO: 外部割り込み0条件制御 (Interrupt Sense Control 0)

外部割り込み0はステータスレジスタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レジスタ(GIMSK)の対応する割り込み許可、外部割り込み0許可(INTO)ビットが設定(1)されている場合の外部(INTO)ピットとします。ISCOが解除(0)されると、INTOの下降端が割り込みを起こします。ISCOが設定(1)されると、INTOの上昇端が割り込みを起こします。INTOの端(エッジ)は非同期に検出されます。40nsより広いINT1のパルスは割り込みを生成します。短すぎるパルスは割り込みの発生が保証されません。

ISCOビット変更時、割り込みが起き得ます。従って一般割り込み許可レジスタ(GIMSK)の割り込み許可(INT0)ビットを解除(0)することによって、最初にINT0を禁止することが推奨されます。その後、ISCOビットは変更できます。最後は、割り込みが再許可される前に一般割り込み要求フラグレジスタ(GIFR)の外部割り込み0要求フラグ(INTF0)に論理1を書くことにより、INT0割り込み要求フラグが解除(0)されるべきです。

#### 休止形態

2つの休止形態の何れかへ移行するには、MCU制御レジ、スタ(MCUCR)の休止許可(SE)ビットを設定(1)し、SLEEP命令が実行されなければなりません。MCU制御レジ、スタ(MCUCR)のSMビットはどちらの休止形態かを選びます。アイドル動作とパワーーダウン動作はSLEEP命令によって有効にされます。

MCUが休止形態中に許可されている割り込みが発生すると、MCUは起動復帰します。その後CPUは4周期停止され、対応する割り込み処理ルーチンを実行し、そしてSLEEP命令の次から実行を再開します。レジスタファイル、SRAM、I/Oレジスタの内容は変化しません。休止形態中にリセットが起こると、MCUは起動復帰し、リセットへクタから実行します。

#### アイドル動作

休止種別(SM)ビットが解除(0)されていると、SLEEP命令でMCUがアイドル動作へ移行し、CPUは停止しますが、タイマ/カウンタ、A/D変換器、割り込み機構は継続して動作します。これはタイマ/カウンタ溢れやA/D変換の割り込みなどのような内部の割り込みだけでなく、外部で起動される割り込みでもMCUの起動復帰を可能にします。

#### パリーダウン動作

休止種別(SM)ビットが設定(1)されていると、SLEEP命令でMCUがパワーダウン動作へ移行します。この動作では、外部発振器が停止され、一方、外部割り込みは動作を継続します。外部リセットまたはINT0, INT1の外部割り込みだけがMCUを起動復帰できます。 パワーダウン動作からの復帰にINT0またはINT1が使われる場合、その端(エッジ)情報が復帰まで記憶されることに注意してください。 パワーダウン動作から復帰するとき、起動復帰条件発生から起動復帰の効果が現れるまで遅延を伴います。これは停止されてしまっている後に、再開のためのクロックが許可され、安定状態になるためです。この起動時間はリセット遅延時間(trout)と同じです。

## タイマ/カウンタ

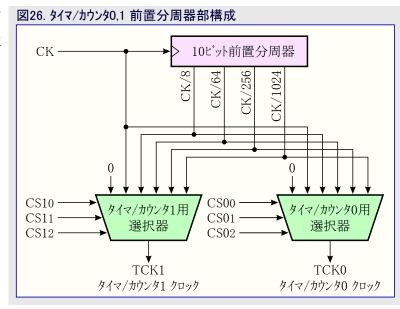

AT90C8534には2つ(8ビット×1と16ビット×1)の一般目的用タイマ/カウンタがあります。タイマ/カウンタ0と1には、同じ10ビット前置分周器用タイマから選ぶ個別の前置分周器があります。

#### タイマ/カウンタ前置分周器部

タイマ/カウンタ0と1に対する前置分周器で分周された5つの異なる選択はCKを発振器クロックとする、CK, CK/8, CK/64, CK/256, CK/1024です。加えてタイマ/カウンタは停止もできます。

#### 8ビット タイマ/カウンタ0

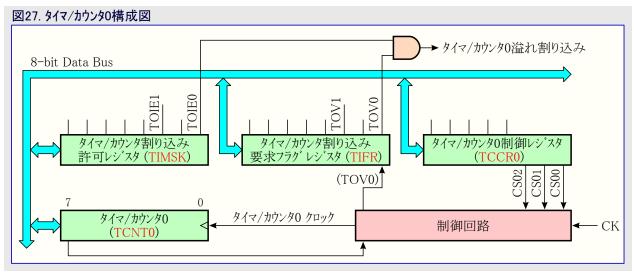

図27.はタイマ/カウンタ0の構成図を示します。

8ビットのタイマ/カウンタ0は、CKまたは分周されたCKからのクロック元を選べます。更に、タイマ/カウンタ0制御レジスタ(TCCR0)の詳細で説明されるように停止もできます。溢れ状態フラグ(TOV0)はタイマ/カウンタ割り込み要求フラグレジスタ(TIFR)にあります。制御ビットはタイマ/カウンタ0制御レジスタ(TCCR0)にあります。タイマ/カウンタ0についての割り込みの許可/禁止設定はタイマ/カウンタ割り込み許可レジスタ(TIMSK)内にあります。

8ビットのタイマ/カウンタ0は低前置分周(使用)機会での高分解能及び高精度の使用が特徴です。同様に高前置分周(使用)機会は低速な目的や稀に動く正確なタイミングの目的についてタイマ/カウンタ0を有効にします。

#### タイマ/カウンタ0制御レシ、スタ (Timer/Counter O Control Register) TCCRO

| ピット         | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    | _     |

|-------------|---|---|---|---|---|------|------|------|-------|

| \$33 (\$53) | _ | - | _ | - | - | CS02 | CS01 | CS00 | TCCR0 |

| Read/Write  | R | R | R | R | R | R/W  | R/W  | R/W  |       |

| 初期値         | 0 | 0 | 0 | 0 | 0 | 0    | 0    | 0    |       |

#### • ビット7~3 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

#### • ビット2~0 - CS02~0: クロック選択0 (Clock Select0, bit 2,1 and 0)

クロック選択0ビット2~0はタイマ/カウンタ0に供給するクロック元を 定義します。

停止状態はタイマ/カウンタの許可/禁止機能を提供します。 CKの分周出力動作では、発振器クロック(CK)から直接的 に分周されます。

| 表4. タイマ | マ/カウンタ( | )入力加 | ック選択                           |

|---------|---------|------|--------------------------------|

| CS02    | CS01    | CS00 | 意味                             |

| 0       | 0       | 0    | 停止(タイマ/カウンタ0は動作を停止します。)        |

| 0       | 0       | 1    | CK                             |

| 0       | 1       | 0    | CK/8 (CPUクロックを8分周したクロック)       |

| 0       | 1       | 1    | CK/64 (CPUクロックを64分周したクロック)     |

| 1       | 0       | 0    | CK/256 (CPUクロックを256分周したクロック)   |

| 1       | 0       | 1    | CK/1024 (CPUクロックを1024分周したクロック) |

| 1       | 1       | 0    | (予約)                           |

| 1       | 1       | 1    | (予約)                           |

#### タイマ/カウンタ0 (Timer/Counter0) TCNT0

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |       |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|-------|

| \$32 (\$52) | (MSB) |     |     |     |     |     |     | (LSB) | TCNT0 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |       |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |       |

このタイマ/カウンタ0は、読み書きできる上昇カウンタとして実現されます。タイマ/カウンタ0が書かれ、クロック元が存在すると、タイマ/カウンタ0は書き込み動作の次に来るタイマ/カウンタ クロック周期で計数を開始/継続します。

#### 16ビット タイマ/カウンタ1

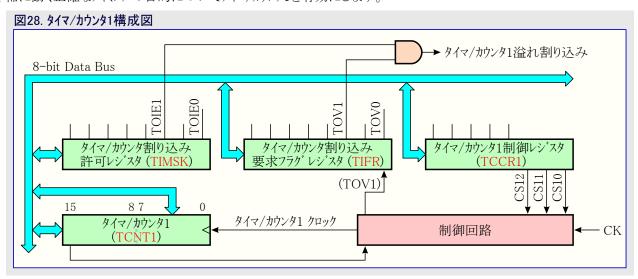

図28.はタイマ/カウンタ1の構成図を示します。

16ビットのタイマ/カウンタ1は、CKまたは分周されたCKからのクロック元を選べます。更に、タイマ/カウンタ1制御レジスタ(TCCR1)の詳細で説明されるように停止もできます。溢れ状態フラグ(TOV1)はタイマ/カウンタ割り込み要求フラグレジスタ(TIFR)にあります。制御ビットはタイマ/カウンタ1制御レジスタ(TCCR1)にあります。タイマ/カウンタ1についての割り込みの許可/禁止設定はタイマ/カウンタ割り込み許可レジスタ(TIMSK)内にあります。

16ビットのタイマ/カウンタ1は低前置分周(使用)機会での高分解能及び高精度の使用が特徴です。同様に高前置分周(使用)機会は低速な目的や稀に動く正確なタイミングの目的についてタイマ/カウンタ1を有効にします。

#### タイマ/カウンタ1制御レシ、スタ (Timer/Counter1 Control Register) TCCR1

| ピット         | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |       |

|-------------|---|---|---|---|---|------|------|------|-------|

| \$2E (\$4E) | _ | - | _ | - | - | CS12 | CS11 | CS10 | TCCR1 |

| Read/Write  | R | R | R | R | R | R/W  | R/W  | R/W  |       |

| 初期値         | 0 | 0 | 0 | 0 | 0 | 0    | 0    | 0    |       |

#### • ビット7~3 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

#### • ビット2~0 - CS12~0: クロック選択1 (Clock Select1, bit 2,1 and 0)

このクロック選択1ビット2~0はタイマ/カウンタ1(TCNT1)に供給 表5. タイマ/カウンタ1入力クロック選択 するクロックを定義します。

停止状態はタイマ/カウンクの動作許可/禁止機能を提供します。CKが分周される動作では、発振器クロックCKから直接的に分周されます。

| 120. 71 | (//3/2/ | 1/(/)/ | 77. 运1八                    |

|---------|---------|--------|----------------------------|

| CS12    | CS11    | CS10   | 意味                         |

| 0       | 0       | 0      | 停止(タイマ/カウンタ1は動作停止)         |

| 0       | 0       | 1      | CK                         |

| 0       | 1       | 0      | CK/8 (CPUクロックを8分周したクロック)   |

| 0       | 1       | 1      | CK/64 (CPUクロックを64分周したクロック) |

# 0 1 1 CK/64 (CPUクロックを64分周したクロック) 1 0 0 CK/256 (CPUクロックを256分周したクロック) 1 0 1 CK/1024 (CPUクロックを1024分周したクロック) 1 1 0 (予約)

(予約)

#### タイマ/カウンタ1 (Timer/Counter1) TCNT1H.TCNT1L (TCNT1)

| • |             | •     | ,   | ,   | `   | •   |     |     |       |        |

|---|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

|   | ピット         | 15    | 14  | 13  | 12  | 11  | 10  | 9   | 8     |        |

|   | \$2D (\$4D) | (MSB) |     |     |     |     |     |     |       | TCNT1H |

|   | Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

|   | 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

|   | ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |        |

|   | \$2C (\$4C) |       |     |     |     |     |     |     | (LSB) | TCNT1L |

|   | Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

|   | 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

|   |             |       |     |     |     |     |     |     |       |        |

この16ビット レジスタは16ビットのタイマ/カウンタ1の前置分周された値を含みます。CPUがこれらのレジスタをアクセスするとき、上位と下位のバイトの両方が同時に読み書きされることを保証するため、このアクセスは8ビットの一時レジスタ(TEMP)を使って実行されます。主プログラムと割り込みルーチンがTEMPを使うレジスタにアクセスする場合、割り込みが(再度)許可されるならば、主プログラムや割り込みルーチンからのアクセス中、割り込みは禁止されなければなりません。

#### タイマ/カウンタ1(TCNT1)書き込み (Timer/Counter1 Write)

CPUが上位バイト(TCNT1H)に書くとき、書かれたデータは一時レジスタ(TEMP)に置かれます。次にCPUが下位バイト(TCNT1L)に書くとき、TEMP内のバイト データと組み合わされ、16ビット全てがタイマ/カウンタ1(TCNT1)へ同時に書かれます。従って、完全な16ビット レジスタ書き込み操作では、上位バイト(TCNT1H)が先にアクセスされなければなりません。

#### タイマ/カウンタ1(TCNT1)読み込み (Timer/Counter1 Read)

CPUが下位バイト(TCNT1L)を読むとき、下位バイト(TCNT1L)のデータがCPUへ送られ、上位バイト(TCNT1H)のデータが一時レジスタ(TEMP)に置かれます。CPUが上位バイト(TCNT1H)を読むとき、CPUはTEMP内のデータを受け取ります。従って、完全な16ビット レジスタ読み込み操作では、下位バイト(TCNT1L)が先にアクセスされなければなりません。

タイマ/カウンタ1は読み書き可能な上昇カウンタとして実現されます。クロック供給元が選ばれ、タイマ/カウンタ1が書かれると、タイマ/カウンタ1は書かれた値を設定後、次のタイマ/カウンタ1 クロック周期で計数を開始/継続します。

## **EEPROMアクセス**

EEPROMをアクセスするレシ、スタはI/O空間でアクセスできます。

書き込み時間はVCC電圧に依存し、2.5~35msの範囲です。(書き込みは)自己タイミング機能ですが、使用者ソフトウェアは次バイトが書ける時を検知してください。EEPROMが新規データを受け入れる準備ができているときに起動するために、特別なEEPROM操作可割り込みが設定できます。

不測のEEPROM書き込みを防ぐため、特別な書き込み手順に従わなければなりません。この詳細については「EEPROM制御レジスタ (EECR)」の説明を参照してください。

EEPROMが書かれるとき、CPUは次の命令が実行される前に2クロック周期停止されます。EEPROMが読まれるとき、CPUは次の命令が実行される前に4クロック周期停止されます。

#### EEPROM7トレス レジスタ (EEPROM Address Register) EEARH, EEARL (EEAR)

|             |       |       | O     | ,     | ,     | ` ,   |       |       |       |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| ピット         | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     | _     |

| \$1F (\$3F) | -     | -     | -     | -     | -     | -     | -     | EEAR8 | EEARH |

| Read/Write  | R     | R     | R     | R     | R     | R     | R     | R/W   |       |

| 初期値         | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 不定    |       |

| ピット         | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |       |

| \$1E (\$3E) | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEARL |

| Read/Write  | R/W   |       |

| 初期値         | 不定    |       |

|             |       |       |       |       |       |       |       |       |       |

#### • ビット8~0 - EEAR8~0: EEPROMアトレス (EEPROM Address)

EEPROMアドレスレジ、スタ(EEARHとEEARL)は512バイトのEEPROM空間のEEPROMアドレスを指定します。EEPROMデータのバイトは0~511間で直線的に配置されています。

#### EEPROMデータレジスタ (EEPROM Data Register) EEDR

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     | _    |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|------|

| \$1D (\$3D) | (MSB) |     |     |     |     |     |     | (LSB) | EEDR |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |      |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |      |

#### • ビット7~0 - EEDR7~0: EEPROMデータ (EEPROM Data)

EEPROM書き込み操作について、EEDRはEEPROMアドレス レジスタ(EEAR)で与えられるアドレスのEEPROMに書かれるデータです。EEP ROM読み込み操作では、EEDRがEEARで与えられるアドレスのEEPROMから読み出されたデータです。

#### EEPROM制御レジスタ (EEPROM Control Register) EECR

| ピット         | 7 | 6 | 5 | 4 | 3     | 2     | 1    | 0    | _    |

|-------------|---|---|---|---|-------|-------|------|------|------|

| \$1C (\$3C) | _ | - | - | - | EERIE | EEMWE | EEWE | EERE | EECR |

| Read/Write  | R | R | R | R | R/W   | R/W   | R/W  | R/W  |      |

| 初期値         | 0 | 0 | 0 | 0 | 0     | 0     | 不定   | 0    |      |

#### • ビット7~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

#### • ビット3 - EERIE: EEPROM操作可割り込み許可(EEPROM Ready Interrupt Enable)

ステータス レシ 、スタ(SREG)の全割り込み許可(I)ビットとこのEERIEが設定(1)されると、EEPROM操作可割り込みが許可されます。解除(0)されると、この割り込みは禁止されます。EEWEが解除(0)されていると、EEPROM操作可割り込みは継続する割り込みを発生します。

#### • ビット2 - EEMWE : EEPROM主書き込み許可 (EEPROM Master Write Enable)

このEEMWEビットは、EEPROM書き込み許可(EEWE)ビットの1設定がEEPROM書き込みの原因となるかどうかを決めます。EEMWEが設定(1)されると、EEWEの1設定は選ばれたアドレスのEEPROMにデータを書きます。EEMWEが0なら、EEWEの1設定は無効です。EEMWEがソフトウェアによって設定(1)されてしまうと、4クロック周期後、自動的に解除(0)されます。EEPROM書き込み手順については、次の「書き込み許可(EEWE)ビット」の説明を参照してください。

#### • ビット1 - EEWE: EEPROM書き込み許可(EEPROM Write Enable)

このEEPROM書き込み許可信号(EEWE)はEEPROMへの書き込みストローブです。アドレスとデータが適切に設定されると、EEPROMへこの値を書き込むために、このEEWEビットを設定(1)しなければなりません。論理1がEEWEに書かれるとき、EEPROM主書き込み許可(EEMWE)ビットは設定(1)されなければならず、そうしないと、EEPROM書き込みは行われません。EEPROMを書く時は次の手順に従うべきです(手順2.と3.の順番は重要ではありません)。

- 1. EEPROM書き込み許可(EEWE)ビットがのになるまで待機します。

- 2. 今回のEEPROMアトレスをEEPROMアトレス レシブスタ(EEARHとEEARL)に書きます。(任意、省略可)

- 3. 今回のEEPROMデータをEEPROMデータレジスタ(EEDR)に書きます。(任意、省略可)

- **4.** EEPROM制御レジスタ(EECR)のEEPROM主書き込み許可(EEMWE)ビットに論理1を書きます。(EEMWEビットに論理1が書けるためには、同一周期内でEEWEビットは0が書かれなければなりません。)

- 5. EEMWE設定後4クロック周期内に、EEPROM書き込み許可(EEWE)ビットへ論理1を書きます。

警告: 手順4.と5.間の割り込みは、EEPROM主書き込み許可が時間超過となるため、書き込み周期失敗になります。EEPROMをアクセスする割り込み処理ルーチンが他のEEPROMアクセスで割り込み、EEARまたはEEDRを変更すると、割り込まれたEEPROMアクセスが失敗する原因になります。これらの問題を防ぐため、手順2.~5.の間中、ステータスレジスタ(SREG)の全割り込み許可(I)ビットは解除(0)されていることが推奨されます。

書き込み時間(代表値で、2.5ms/VCC=5V, 4ms/VCC=2.7V)が経過してしまうと、EEWEビットは自動的に解除(0)されます。次のバイトを書く前に、このビットをポーリングして0まで待機できます。EEWEが設定(1)されてしまうと、次の命令が実行される前に、CPUは2周期停止されます。

#### • ビット0 - EERE: EEPROM読み込み許可 (EEPROM Read Enable)

このEEPROM読み込み許可信号(EERE)はEEPROMへの読み込みストローブです。EEARに適切なアドレスが設定されると、このEEREビッ トを設定(1)しなければなりません。EEREビットが自動的に解除(0)されると、求められたデータがEEDR内にあります。EEPROM読み込み アクセスは1命令で行われるので、EEREビットのポーリングは必要ありません。EEREが設定(1)されてしまうと、次の命令が実行される前に CPUは4周期停止されます。

読み込み操作を始める前にEEWEビットをポーリングすべきです。書き込み動作が実行中のとき、どのEEPROM I/Oレジスタの書き込みも 阻止されます(EERIEビットを除く、これは書けます)。従って、書き込みアクセス中に読み出しアクセスが試みられると、アドレスが変更されず、 読み出しアクセスは実行されません。書き込み動作は邪魔されずに完了します。

#### EEPROMデータ化けの防止

電源電圧が低すぎる時のCPUやEEPROMの動作特性により、低VCCの期間中、EEPROMデータが化けてしまいます。これらはEEPR OMを使った基板段階の問題と同じで、同じ設計上の解決法が適用されるべきです。

EEPROMデータ化けが発生する低電源電圧は、2つの場合が想定できます。1つ目は、EEPROM書き込み動作に必要な最低電圧以下の場合で、2つ目は、CPUが命令を実行するのに必要な最低電圧以下の場合です。

次の推奨設計(内の1つで充分)により、EEPROMのデータ化けは容易に避けることができます。

- ・電源の供給電圧が不足する時間中、AVRのRESETを有効(Low)に保ちます。これは外部低VCCリセット保護回路による実現が最善で、これはブラウンアウト検出器(BOD)として度々参照されます。電源ONリセットと低電圧検出に関する設計上の考慮については、応用記述のAVR180を参照してください。

- ・低VCCの時間中、AVRコアをパワーダウン休止動作に保ちます。これはCPUを命令の復号と実行を試みないように防ぎ、不測の書き込みからEEPROMレジスタを保護する効果があります。

- ・ソフトウェアからメモリ内容を変更できることが必要とされない場合、フラッシュ メモリに定数を格納します。フラッシュ メモリはCPUにより更新されることができないので、データ化けの問題はありません。

## A/D変換器

A/D変換器の主な機能を次に示します。

- 10ビット分解能

- 精度±2 LSB (AVCC=3.3~6.0V)

- 変換時間76~175µs

- 13k採取/sまでの採取速度

- 6チャネルの多重器内蔵

- 全電圧範囲(AGND~AVCC)入力可能

- 連続と単独の変換動作

- A/D変換完了割り込み

- 休止形態時の雑音低減機能

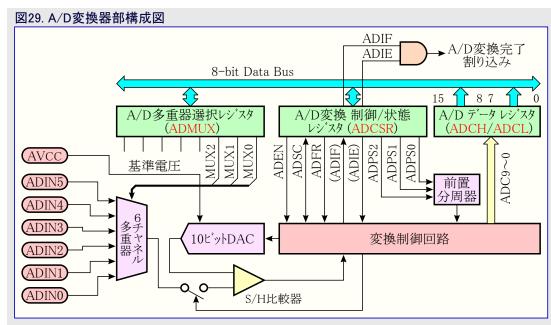

AT90C8534は10ビットの逐次比較A/D変換部が特徴です。このA/D変換部は、A/D変換器の入力として使われるADIN5~0の各ピンが供される6チャネルの多重器に接続されます。A/D変換部は、A/D変換器が変換中の一定水準を保持するための入力電圧を保証する採取&保持(S/H)を含みます。A/D変換部の構成図は図29.に示されます。

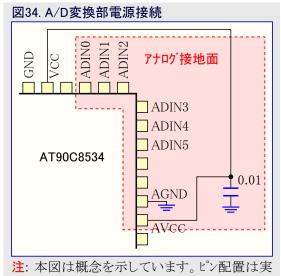

A/D変換部には分離された2つの電源(AVCC, AGND)  $\ell^{\circ}$ ンがあります。AGNDはGNDに接続されなければならず、AVCCの電圧は VCC±0.3 V以内でなければなりません。これらの $\ell^{\circ}$ ンの接続方法は、25頁の「**雑音低減技術**」を参照してください。

#### (訳注)

原書の図29.に於いて、基準電圧が外部基準電圧と記述されていますが、具体的ピン名の説明が存在しませんので、ここではAVCCを基準電圧として使うものと推定して記載します。

#### 操作

A/D変換は単独と連続の2つの動作ができます。単独変換動作では、変換毎に使用者により開始されなければなりません。連続変換動作では、常に採取とA/Dデータレシ、スタ(ADCH/ADCL)の更新が行われます。A/D制御/状態レシ、スタ(ADCSR)のA/D動作選択(ADFR)と、かは、この2つの利用可能な動作を選びます。

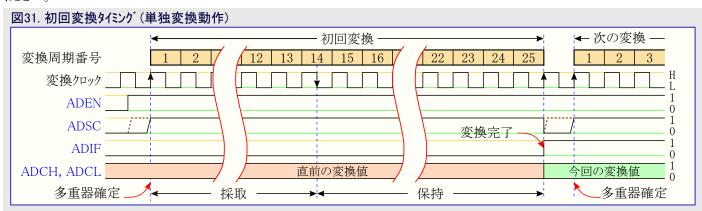

A/D変換部はADCSRのA/D許可(ADEN)ビットへの論理1書き込みによって許可されます。A/D変換部許可後の最初の変換は、A/D変換部を初期化するために擬似変換が先行して行われます。違いは、この変換が標準変換より12変換クロック余計にかかることだけです。

ADINO~5アナログ入力チャネルはA/D多重器選択レジスタ(ADMUX)のチャネル選択(MUX)ビットの書き込みによって選びます。

変換はADCSRの変換開始(ADSC)ビットに論理1を書くことによって開始されます。このビットは変換が実行中である限り1に留まり、変換が完了されるとき、ハードウェアによって0に設定されます。変換実行中に違うデータ チャネルが選ばれると、チャネル変更を行う前に現在の変換を完了します。

A/D変換は10ビットの結果を2つのデータレジスタ(ADCH,ADCL)に生成し、変換完了時に結果を得るため読まなければなりません。それらが読まれるとき、データレジスタの内容が同じ変換からであるのを保証するため、特別なデータ保護回路が使われます。この機構は次のように動作します。

データを読むとき、ADCLが最初に読まれなければなりません。一度ADCLが読まれると、データレジスタへのA/D変換器アクセスは防止されます。これはADCLが読まれてしまい、ADCHが読まれる前に変換が完了すると、どちらのレジスタも更新されず、その変換からの結果が失われることを意味します。ADCHが読まれると、ADCHとADCLへのA/D変換器アクセスが許可されます。

A/D変換部には、変換完了時に起動できる自身の割り込み(ADIF)があります。データレジスタへのA/D変換器アクセスがADCLとADCHの読み込み間で禁止されていると、結果は失われてしまいますが、割り込みは起動します。

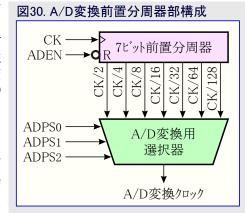

#### 前置分周と変換タイミング

A/D変換部はシステム クロックを受け入れ可能なA/D変換クロック周波数に分周する前置分周器を含みます。A/D変換器は80~170kHz範囲の入力クロック周波数を受け入れます。

A/D制御/状態レジスタ(ADCSR)のA/Dクロック選択(ADPS2~0)ビットは、160kHz以上の何れかのシステムクロック周波数から適切なA/D変換クロック周波数を生成するために使われます。この前置分周器はADCSRのA/D許可(ADEN)ビットを設定(1)することによってA/D変換部がONに切り替えられる時から計数を始めます。前置分周器はADENビットが設定(1)である限り動作し続け、ADENが解除(0)のときは継続的にリセットされます。

ADCSRのA/D変換開始(ADSC)ビットを設定(1)することにより変換を開始するとき、直後の変換クロック周期の上昇端で変換が始まります。

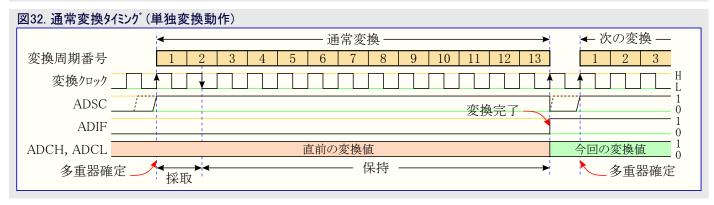

実際の採取&保持は変換開始後1.5変換クロック周期の位置で行われます。13変換クロック周期後に結果が用意でき、A/Dデータ レジスタ(ADCH, ADCL)に書かれます。単独変換動作(ADFR=0)では、次の変換開始前に1変換クロック周期以上が必要(図32.参照)です。この期間にA/D変換開始(ADSC)ビットが1に設定されると、直ちに新しい変換が始まりま

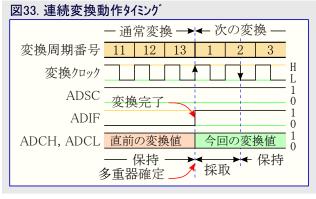

す。連続変換動作(ADFR=1)では、結果がA/Dデータレジスタ(ADCH, ADCL)に書かれた後、直ぐに新規変換が開始されます。変換クロックが170kHzで連続変換動作を使うと、最小変換時間76µs(約13k採取/s)が得られます。変換時間の概要については表6.を参照してください。

| 表6. A/D変換時間 |      |      |       |          |  |  |  |  |  |  |  |

|-------------|------|------|-------|----------|--|--|--|--|--|--|--|

| 変換種別        | 保持点  | 変換終了 | 総変換時間 | 変換時間(µs) |  |  |  |  |  |  |  |

| 連続(初回)      | 13.5 | 25   | 25    | 147~313  |  |  |  |  |  |  |  |

| 単独(初回)      | 13.5 | 25   | 26    | 153~325  |  |  |  |  |  |  |  |

| 連続(通常)      | 1.5  | 13   | 13    | 76~163   |  |  |  |  |  |  |  |

| 単独(通常)      | 1.5  | 13   | 14    | 82~175   |  |  |  |  |  |  |  |

注:変換時間を除く各番号は変換開始からの変換クロック数です。

#### 雑音低減機能

A/D変換部は、CPUコアから誘導される雑音を低減するため、アイドル動作中にA/D変換を可能にする雑音低減機能が特徴です。この機能の使用を行うには、次の手順が使われるべきです。

- 1. A/D変換が許可(ADEN=1)され、変換中でない(ADSC=0)ことを確認します。単独変換動作が選択(ADFR=0)され、A/D変換完了 割り込みが許可(ADIE=1)されなければなりません。

- 2. アイドル動作に移行します。一旦CPUが停止されてしまうと、A/D変換部は変換を開始します。

- 3. A/D変換完了前に他の割り込みが起きなければ、A/D変換完了割り込みがMCUを起動復帰し、A/D変換完了割り込み処理ルーチンを実行します。

#### A/D多重器選択レジスタ (ADC Multiplexer Select Register) ADMUX

| ピット         | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |       |

|-------------|---|---|---|---|---|------|------|------|-------|

| \$07 (\$27) | _ | _ | - | _ | _ | MUX2 | MUX1 | MUX0 | ADMUX |

| Read/Write  | R | R | R | R | R | R/W  | R/W  | R/W  |       |

| 初期値         | 0 | 0 | 0 | 0 | 0 | 0    | 0    | 0    |       |

#### • ビット7~3 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

• ビット2~0 - MUX2~0: A/Dチャネル選択 (Analog Channel Select Bits 2~0)

これらの3ビットの値はA/D変換器に接続されるアナログ入力5~0を選びます。設定値\$07と\$06は予約されており、使われるべきではありません。

#### 表7 アナログ入力チャネル選択

| 2017/11/70/70 | 17722373 |       |       |       |       |       |       |      |

|---------------|----------|-------|-------|-------|-------|-------|-------|------|

| MUX2~0        | 0 0 0    | 0 0 1 | 0 1 0 | 0 1 1 | 100   | 101   | 1 1 0 | 111  |

| アナログ入力チャネル    | ADIN0    | ADIN1 | ADIN2 | ADIN3 | ADIN4 | ADIN5 | (予約)  | (予約) |

#### A/D変換 制御/状態レジスタ (ADC Control and Status Register) ADCSR

| ピット         | 7    | 6    | 5    | 4    | 3    | 2     | 1     | 0     |       |

|-------------|------|------|------|------|------|-------|-------|-------|-------|

| \$06 (\$26) | ADEN | ADSC | ADFR | ADIF | ADIE | ADPS2 | ADPS1 | ADPS0 | ADCSR |

| Read/Write  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W   | R/W   | R/W   |       |

| 初期値         | 0    | 0    | 0    | 0    | 0    | 0     | 0     | 0     |       |

#### • ビットフ – ADEN: A/D許可(ADC Enable)

このビットへの論理1書き込みがA/D動作を可能にします。このビットを0に解除することにより、A/D変換部はOFFに切り替えられます。 A/D変換中のOFFへの切り替えは、その変換を終了します。

#### • ビット6 - ADSC: A/D変換開始 (ADC Start Conversion)

単独変換動作では、変換毎に変換を開始するため、このビットに論理1が書かれなければなりません。連続変換動作では、最初の変換を開始するため、このビットに論理1が書かれなければなりません。A/D許可(ADEN=1)後の最初のADSCの設定(1)か、A/D許可時の同時設定(1)で、擬似変換が実際の変換開始に先行します。この擬似変換はA/D変換部の初期化を行います。

A/D変換中、ADSCは1に留まります。ADSCは実際の変換が終了された後、Oになりますが、その前に結果がA/Dデータレシブスタ(ADC H,ADCL)に書かれます。これは現在の変換が完了する前に新規変換が開始されることを許します。 擬似変換が実際の変換に先行するとき、ADSCは実際の変換が終了されるまで1に留まります。

このビットへの0書き込みは無効です。

#### • ビット5 - ADFR: 連続/単独変換動作選択 (ADC Free Running Select)

このビットが設定(1)されるとA/D変換は連続変換動作で動きます。この動作では採取とA/Dデータ レジスタの更新を連続的に行います。このビットの解除(0)は連続変換を終了し、単独変換動作になります。

#### • ビット4 - ADIF: A/D変換完了割り込み要求フラグ(ADC Interrupt Flag)

A/D変換が完了し、A/Dデータレジスタが更新されるとき、このビットが設定(1)されます。ステータスレジスタ(SREG)の全割り込み許可(I)ビットとA/D変換完了割り込み許可(ADIE)ビットが設定(1)されていると、A/D変換完了割り込みが実行されます。ADIFは対応する割り込み へクタ実行時、自動的に解除(0)されます。代わりに、このフラグへの論理1書き込みによっても解除(0)されます。ADCSRで読み-変更-書き(リード・モデファイライト)を行う場合、保留割り込みが禁止されることに注意してください。これはSBI、CBI命令が使われる場合にも適用されます。

#### • ビット3 - ADIE: A/D変換完了割り込み許可(ADC Interrupt Enable)

このビットとステータス レジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されると、A/D変換完了割り込みが有効にされます。

• ビット2~0 - ADPS2~0: A/D変換クロック選択 (ADC Prescaler Select Bits)

これらのビットは、システム クロック周波数とA./D変換器への入力クロック間の分周比を決めます。

| 表8 △ | /D変換クロック選択 | (CK=システム クロック) |

|------|------------|----------------|

|      |            |                |

| ADPS2     | 0    | 0    | 0    | 0    | 1     | 1     | 1     | 1      |

|-----------|------|------|------|------|-------|-------|-------|--------|

| ADPS1     | 0    | 0    | 1    | 1    | 0     | 0     | 1     | 1      |

| ADPS0     | 0    | 1    | 0    | 1    | 0     | 1     | 0     | 1      |

| A/D変換クロック | CK/2 | CK/2 | CK/4 | CK/8 | CK/16 | CK/32 | CK/64 | CK/128 |

#### A/Dデータレジスタ (ADC Data Register) ADCH.ADCL

| ピット         | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |      |

|-------------|------|------|------|------|------|------|------|------|------|

| \$05 (\$25) | _    | -    | -    | -    | -    | -    | ADC9 | ADC8 | ADCH |

| Read/Write  | R    | R    | R    | R    | R    | R    | R    | R    |      |

| 初期値         | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

| ピット         | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    | _    |

| \$04 (\$24) | ADC7 | ADC6 | ADC5 | ADC4 | ADC3 | ADC2 | ADC1 | ADC0 | ADCL |

| Read/Write  | R    | R    | R    | R    | R    | R    | R    | R    |      |

| 初期値         | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

|             |      |      |      |      |      |      |      |      |      |

A/D変換完了時、その結果がこれら2つのレジスタ内にあります。連続変換動作では、2つのレジスタが読まれることと、ADCHの前に ADCLが読まれることが重要です。

#### 複数チャネル走査

アナログ入力チャネルの変更は常に変換完了まで遅らされるため、連続変換動作はA/D変換部の割り込みなしでの複数チャネル走査に使 うことができます。通常、A/D変換完了割り込みがチャネル移動を行うために使われます。しかし、次の要素が考慮されるべきです。

一旦読まれるべき結果が用意されると、割り込みが起動します。連続変換動作では、割り込みが起動するとき、次の変換が直ちに始 まります。割り込み起動後にA/D多重器選択レジスタ(ADMUX)が変更される場合、次の変換は既に開始されており、これには変更前 の設定が使われます。

#### 雑音低減技術

AT90C8534内外のデジタル回路は、アナログ測定の精度に影響を及ぼすかもしれないEMIを発生します。変換精度が重要な場合、次 の技法を適用することによって雑音水準を減少できます。

- 1. AT90C8534のアナログ部と応用回路内の全てのアナログ部品は、基板上で分離 したアナログGND面を持つべきです。このアナログGND面は基板上の1点でデジ タルGND面に接続されます。

- 2. アナログ信号経路は可能な限り最短を維持します。アナログ信号線がアナログ GND面上走っているか確認し、高速切り替えのデジタル信号線から充分離す ことを厳守します。

- 3. AT90C8534のAVCCピンは**図34**.で示されるように、VCC(デジタル供給電圧)に 接続されるべきです。

- 4. CPUからの誘導雑音を低減するため、A/D変換雑音低減機能を使います。

際のデバイスと異なります。

## A/D変換器特性

TA= $-40^{\circ}$ C $\sim$ 85 $^{\circ}$ C 条件 単位 シンボル 項目 最小 代表 最大 10 ピット 分解能 絶対精度 2 積分非直線性誤差 1 INL LSB AVCC=3.3∼6.0V 微分非直線性誤差 2 DNL 変位(オフセット)/ゼロ誤差 0.5 変換時間 76 175 μs 変換クロック周波数 80 170 kHz AVCC アナログ供給電圧 VCC-0.3 VCC+0.3 (注1) V RREF 基準電圧入力インピーダンス 6 10 13  $k\Omega$ RAIN アナログ入力インピーダンス 100  $M\Omega$

**注1**: AVCCは3.3~6.0Vの範囲です。

## 出力ポートA

ポートAは7ビットのトライステート付き標準出力ポートです。

このポートは真の読みー変更ー書き(リード モデファイ ライト)機能を持ちます。これはCBIやSBI命令で、他の何れのピンのトライステート状態をも不測の変化なしに、ポート ピンの1つのトライステート状態が変更できることを意味します。これは駆動(出力)値の変更にも適用されます。

ポートAについては2つのI/Oメモリ位置が各々、出力データレジスタ(PORTA),\$1B(\$3B)、データ方向レジスタ(DDRA),\$1A(\$3A)に割り当てられます。 両位置とも読み書き可能です。

ポートA出力緩衝部は20mAの吸い込み電流を流すことができますので、LED表示器を直接駆動できます。

#### ホ°ートA出力レジスタ (Port A Data Register) PORTA

| ピット         | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|-------------|---|--------|--------|--------|--------|--------|--------|--------|-------|

| \$1B (\$3B) | _ | PORTA6 | PORTA5 | PORTA4 | PORTA3 | PORTA2 | PORTA1 | PORTA0 | PORTA |

| Read/Write  | R | R/W    |       |

| 初期値         | 0 | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

#### ポートA方向レジスタ (Port A Data Direction Register) DDRA

| ピット         | 7 | 6    | 5    | 4    | 3    | 2    | 1    | 0    | _    |

|-------------|---|------|------|------|------|------|------|------|------|

| \$1A (\$3A) | _ | DDA6 | DDA5 | DDA4 | DDA3 | DDA2 | DDA1 | DDA0 | DDRA |

| Read/Write  | R | R/W  |      |

| 初期値         | 0 | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

ポートAの7ピン全ては同じ機能です。

標準出力ピンPAnではポートA方向レジスタ(DDRA)のDDAnビットがそのピンのHi-Z 状態を選びます。DDAnが設定(1)されると、PAnはポート出力レジスタ(PORTA)の PORTAnの値で駆動(出力)するために設定されます。DDAnが解除(0)されると、 PAnはトライステート(Hi-Z)ピンとして設定されます。

| 表9. ポートAピンに対するDDAnの関係 |        |      |          |  |  |  |  |  |

|-----------------------|--------|------|----------|--|--|--|--|--|

| DDAn                  | PORTAn | 出力   | 備考       |  |  |  |  |  |

| 0                     | 0      | Hi-Z | 高インピーダンス |  |  |  |  |  |

| 0                     | 1      | пг   | 同年では一クマス |  |  |  |  |  |

| 1                     | 0      | 出力   | Low出力    |  |  |  |  |  |

| 1                     | 1      | 出力   | High出力   |  |  |  |  |  |

注: nは6~0でビット番号を示します。

## メモリ プロク゛ラミンク゛

#### プログラム メモリとデータ メモリ用施錠ビット

AT90C8534は、非プログラム(1)のままか、表10.で示される付加機能を得るためにプログラム(0)できる2つの施錠ビットを提供します。

#### 表10. 施錠ビットの保護種別

| 保護番号 | メモリ施 | 錠ビット | 保護種別                           |

|------|------|------|--------------------------------|

| 体设备与 | LB1  | LB2  | 不設性の                           |

| 1    | 1    | 1    | メモリ施錠機能は許可されません。               |

| 2    | 0    | 1    | フラッシュとEEPROMのプログラミング機能が禁止されます。 |

| 3    | 0    | 0    | 保護種別2と同様、更に照合も禁止されます。          |

注: この施錠ビットは、チップ消去操作によってのみ、消去(非プログラム)可能です。

#### 識票バイ

全てのAtmelマイクロコントローラには、デバイス識別用に3バイトの識票符号があります。この3バイトは他から分離された空間に存在します。AT90C8534の識票符号を次に示します。

① \$000:\$1E 製造業者Atmelを示します。

② \$001:\$93 フラッシュ メモリ容量8Kバイを示します。

**③** \$002: \$04 **②**値\$93と合せ、AT90C8534を示します。

### フラッシュ メモリとEEPROMのプログラミング

AT90C8534は、再書き込み可能な8Kバイトのプログラム用フラッシュメモリと、512バイトのデータ用EEPROMメモリを提供します。

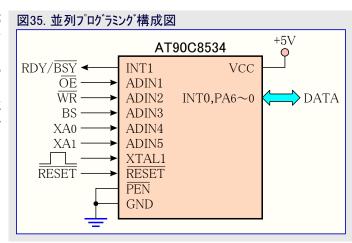

AT90C8534には、プログラム用内蔵フラッシュ メモリとデータ用EEPROMメモリが、消去(全ビット=1)され、プログラムされる準備が整った状態で搭載されています。このデバイスは、PENピンにより許可される並列プログラミング動作を支援します。

AT90C8534のプログラム(フラッシュメモリ)とデータ(EEPROM)用メモリはバイト単位で書かれます。

#### 並列プログラミング

この章ではAT90C8534でのプログラム用フラッシュメモリ、データ用EEPROM、施錠ビットの並列プログラミングと照合の方法を記述します。

#### 信号名

この章ではAT90C8534のいくつかのピンが並列プログラミング中の機能を示す信号名によって参照されます。 図35.と表11.を参照してください。表11.で示されないピンはピン名で参照されます。

XA0とXA1ピンは、XTAL1ピンに正パルスが与えられる時に実行される動作を決めます。この規約は**表12**.で示されます。

WRまたはOEパルスで、取得された指令は実行される動作を決定します。この指令は**表13**.で示されるように各ビットで機能が示されるバイトです。

#### 表11. 信号名とピン名の関係

| 信号名     | ピン名        | 入出力 | 機能                           |

|---------|------------|-----|------------------------------|

| RDY/BSY | INT1       | 出力  | 0: プログラミング 多忙 1: 準備可 (指令受付可) |

| ŌĒ      | ADIN1      | 入力  | 出力許可(負論理)                    |

| WR      | ADIN2      | 入力  | 書き込み(負論理)                    |

| BS      | ADIN3      | 入力  | 上位/下位バイト選択 (0:下位, 1:上位)      |

| XA0     | ADIN4      | 入力  | XTAL動作ビット0                   |

| XA1     | ADIN5      | 入力  | XTAL動作ビット1                   |

| DATA    | INT0,PA6∼0 | 入出力 | データ (OE=L時出力)                |

#### 表12. XA0とXA1の機能

| XA1 | XA0 | XTAL1パルス時の動作                       |

|-----|-----|------------------------------------|

| 0   | 0   | フラッシュまたはEEPROMのアドレス取得(上位/下位はBSで指示) |

| 0   | 1   | データ取得 (フラッシュ時の上位/下位はBSで指示)         |

| 1   | 0   | 指令取得                               |

| 1   | 1   | アイドル(動作なし)                         |

#### 表13. ビット規約による指令バイト

| 指令バイト            | 指令の機能         |

|------------------|---------------|

| \$80 (1000 0000) | fップ消去         |

| \$20 (0010 0000) | 施錠ビット書き込み     |

| \$10 (0001 0000) | フラッシュ メモリ書き込み |

| \$11 (0001 0001) | EEPROM書き込み    |

| \$08 (0000 1000) | 識票バイト読み出し     |

| \$04 (0000 0100) | 施錠ビット読み出し     |

| \$02 (0000 0010) | フラッシュ メモリ読み出し |

| \$03 (0000 0011) | EEPROM読み出し    |

#### プログラミング動作への移行

デバイスは次に示す方法で並列プログラミング動作になります。

- ① VCCとGND間に5Vを供給します。

- ② PEN、RESETとBSピンをLow(0)にし、最低100ns待機します。

- ③ RESETをHigh(1)にします。RESETをHigh(1)に変更後100ns以内の如何なるBSの動き(値)も、デバイスのプログラミング動作移行失敗の原因になります。

#### チップ消去

チップ消去指令はフラッシュ メモリ、EEPROM、施錠ビットを消去します。施錠ビットはフラッシュ メモリとEEPROMが完全に消去されてしまうまで消去されません。フラッシュ メモリまたはEEPROMの再書き込み前には、チップ消去が実行されなければなりません。

チップ。消去の手順を次に示します。

- ① XA1をHigh(1)、XA0をLow(0)にします。これで指令取得が有効になります。

- ② BSをLow(0)にします。

- ③ DATAを\$80(1000 0000)にします。これはチップ消去指令です。

- ④ XTAL1に正パルスを与えます。これで指令を設定します。

- ⑤ チップ消去を実行するため、WRにtwlwh\_ce幅(表14.参照)の負パルスを与えます。チップ消去はRDY/BSYピンにどんな動きも生成しません。

#### フラッシュ メモリ書き込み (図36.タイミングを参照)

#### A.フラッシュ メモリ書き込み指令設定

- ① XA1をHigh(1)、XA0をLow(0)にします。これで指令取得が有効になります。

- ② BSをLow(0)にします。

- ③ DATAを\$10(0001 0000)にします。これはフラッシュ メモリ書き込み指令です。

- ④ XTAL1に正パルスを与えます。これでフラッシュ メモリ書き込み指令を設定します。

#### B.上位アドレス バイト設定

- ① XA1をLow(0)、XA0をLow(0)にします。これでアドレス取得が有効になります。

- ② BSをHigh(1)にします。これは上位バイ選択です。

- ③ DATAにアトレス上位バイト(\$00~\$0F)を設定します。

- ④ XTAL1に正パルスを与えます。これでアドレス上位バイトを設定します。

#### C. 下位アドレス バイト設定

- ① XA1をLow(0)、XA0をLow(0)にします。これでアドレス取得が有効になります。

- ② BSをLow(0)にします。これは下位バイ選択です。

- ③ DATAにアドレス下位ハイト(\$00~\$FF)を設定します。

- ④ XTAL1に正パルスを与えます。これでアトレス下位バイトを設定します。

#### D. データ下位バイト設定

- ① XA1をLow(0)、XA0をHigh(1)にします。これでデータ取得が有効になります。

- ② DATAにデータ下位ハイト(\$00~\$FF)を設定します。

- ③ XTAL1に正パルスを与えます。これでデータ下位バイトを設定します。

#### E.データ下位バイト書き込み

- ① BSをLow(0)にします。これは下位バイ選択です。

- ② WRに負パルスを与えます。これでバイトデータの書き込みが開始され、RDY/BSYがLow(0)になります。

- ③ 次バ小書き込みのため、RDY/BSYがHigh(1)になるまで待機します。

#### F. データ上位バイト設定

- ① XA1をLow(0)、XA0をHigh(1)にします。これでデータ取得が有効になります。

- ② DATAにデータ上位ハイト(\$00~\$FF)を設定します。

- ③ XTAL1に正パルスを与えます。これでデータ上位バイを設定します。

#### G.データ上位バイト書き込み

図36. フラッシュ メモリの書き込みタイミング

- ① BSをHigh(1)にします。これは上位バイ選択です。

- ② WRに負パルスを与えます。これでバイト データの書き込みが開始され、RDY/BSYがLow(0)になります。

- ③ 次バト書き込みのため、RDY/BSYがHigh(1)になるまで待機します。

設定された指令とアドレスはプログラム中、保持されます。効率的なプログラミングを行うには、次の点が考慮されるべきです。

- 複数のメモリ位置を読み書きするとき、指令は一度の設定だけ必要です。

- アドレス上位バイトは、フラッシュ メモリの新規256語ページのプログラミング前に設定されることだけが必要です。

- チップ。消去後のフラッシュ メモリとEEPROMの全ての内容は\$FFですので、値\$FFのデータ書き込みは行わないようにします。 これらの考慮は、EEPROM書き込みと、フラッシュ メモリ、EEPROM、識票バートの読み出しでも適用されます。

##

(訳注) 図36.と図37.は図36.として結合しました。

RDY/BSY

RESET

OE.

#### フラッシュ メモリ読み出し

フラッシュ メモリの読み出し方法を次に示します。(指令とアドレス設定の詳細については、「**フラッシュ メモリ書き込み** |を参照。)

- 1. フラッシュ メモリ読み出し指令\$02(0000 0010)を設定します。(「フラッシュ メモリ書き込み」のA.を参照)

- 2. アト・レス上位ハ・イト(\$00~\$0F)を設定します。(「フラッシュ メモリ書き込み」のB.を参照)

- 3. アドレス下位ハイト(\$00~\$FF)を設定します。(「フラッシュ メモリ書き込み」のC.を参照)

- ① BSをLow(0)、OEをLow(0)にします。これでフラッシュ メモリの語(ワート)の下位バイがDATAに読み出されます。

- ② BSをHigh(1)にします。これでフラッシュ メモリの語(ワート)の上位バイトがDATAに読み出されます。

- ③ OEをHigh(1)にします。これでDATAはHi-Zになります。

#### EEPROM書き込み

データ用EEPROMメモリの書き込み方法を次に示します。(指令、アトレス、データ設定の詳細は、「フラッシュメモリ書き込み」を参照。)

- 1. EEPROM書き込み指令\$11(0001 0001)を設定します。(「フラッシュ メモリ書き込み | のA.を参照)

- 2. アトンス上位バイト(\$00~\$01)を設定します。(「フラッシュ メモリ書き込み」のB.を参照)

- 3. アトンス下位ハイト(\$00~\$FF)を設定します。(「**フラッシュ メモリ書き込み**」の**C**.を参照)

- 4. データ下位バイト(\$00~\$FF)を設定します。(「フラッシュ メモリ書き込み」のD.を参照)

- 5. データ下位バイを書き込みます。(「フラッシュ メモリ書き込み」のE.を参照)

#### EEPROM読み出し

EEPROMメモリの読み出し方法を次に示します。(指令とアトンス設定の詳細については、「フラッシュ メモリ書き込み」を参照。)

- 1. EEPROM読み出し指令\$03(0000 0011)を設定します。(「フラッシュ メモリ書き込み」のA.を参照)

- 2. アトンス上位ハイト(\$00~\$01)を設定します。(「フラッシュ メモリ書き込み」のB.を参照)

- 3. アドレス下位ハイト(\$00~\$FF)を設定します。(「フラッシュ メモリ書き込み」のC.を参照)

- ① BSをLow(0)、OEをLow(0)にします。これでEEPROMメモリのハイト データがDATAに読み出されます。

- ② OEをHigh(1)にします。これでDATAはHi-Zになります。

#### 施錠ビット書き込み

施錠ビットの書き込み方法を次に示します。(指令とデータ設定の詳細については、「フラッシュ メモリ書き込み」を参照。)

- 1. 施錠ビット書き込み指令\$20(0010 0000)を設定します。(「フラッシュ メモリ書き込み」のA.を参照)

- 2. データ下位バイトを設定します。 0=プログラム,1=無変化(状態維持)です。(「フラッシュ メモリ書き込み」のD.を参照)

| <b>ビット2</b>     | 施錠ビット2 (LB2) |                                     |

|-----------------|--------------|-------------------------------------|

| ピット1            | 施錠ビット1 (LB1) |                                     |

| <b>ビット7~3,0</b> | 1            | これらのビットは予約されており、非プログラム(1)のままとすべきです。 |

① データ下位ハーイトを書き込みます。(「フラッシュ メモリ書き込み」のE.を参照)

施錠ビットはチップ消去の実行によってのみ消去(1)できます。

#### 施錠ビットの読み出し

施錠ビットの読み出し方法を次に示します。(指令設定の詳細については、「フラッシュ メモリ書き込み」を参照。)

- 1. 施錠ビットの読み出し指令\$04(0000 0100)を設定します。(「フラッシュ メモリ書き込み」のA.を参照)

- ① BSをHigh(1)、OEをLow(0)にします。これで施錠ビットの状態がDATAに読み出されます。

| ヒ゛ット7 | 施錠ビット1 (LB1) |  |

|-------|--------------|--|

| ヒ゛ット6 | 施錠ビット2 (LB2) |  |

② OEをHigh(1)にします。これでDATAはHi-Zになります。

BSがHigh(1)に設定されなければならないことに注意してください。

#### 識票バイ読み出し

識票バイトの読み出し方法を次に示します。(指令とデータ設定の詳細については、「**フラッシュ メモリ書き込み**」を参照。)

- 1. 識票バイ読み出し指令\$08(0000 1000)を設定します。(「フラッシュ メモリ書き込み」のA.を参照)

- 2. アトレス下位ハーイト(\$00~\$02)を設定します。(「フラッシュ メモリ書き込み」のC.を参照)

- ① BSをLow(0)、OEをLow(0)にします。これで認承バイがDATAに読み出されます。

- ② OEをHigh(1)にします。これでDATAはHi-Zになります。

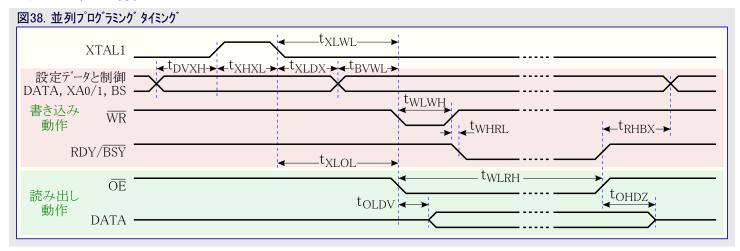

### 並列プログラミング特性

表14. 並列プログラミング特性 (TA=25℃±10%, VCC=5V±10%)

| シンホ゛ル             | 項目                                   | 最小  | 代表  | 最大  | 単位 |

|-------------------|--------------------------------------|-----|-----|-----|----|

| $t_{DVXH}$        | XTAL1に対するデータと制御の準備時間                 | 67  |     |     |    |

| t <sub>XHXL</sub> | XTAL1パルス幅                            | 67  |     |     |    |

| t <sub>XLDX</sub> | XTAL1に対するデータと制御の保持時間                 | 67  |     |     |    |

| t <sub>XLWL</sub> | XTAL1パルスの↓に対するWR↓待機時間                | 67  |     |     | na |

| tbvwl             | BS(有効から)に対するWR↓待機時間                  | 67  |     |     | ns |

| trhbx             | RDY/BSY↑後のBS保持時間                     | 67  |     |     |    |

| twLwH             | WRハ°ルス幅 (注1)                         | 67  |     |     |    |

| twhrl             | WRパルス後(↑)のRDY/BSY↓遅延時間 ( <b>注2</b> ) |     | 20  |     |    |

| twlrh             | 書き込み時間 (WR↓からRDY/BSY↑) (注2)          | 0.5 | 0.7 | 0.9 | ms |

| txLoL             | XTAL1パルスの↓に対するOE↓待機時間                | 67  |     |     |    |

| toldv             | OE↓に対するデータ出力遅延時間                     |     | 20  |     | ns |

| toHDZ             | OE↑に対する浮き遅延時間                        |     |     | 20  |    |

| twlwh_ce          | チップ消去時のWRハプルス幅                       | 5   | 10  | 15  | ms |

注1: チップ消去時はtWLWH\_CEを使います。

注2: twLwHがtwLRHより長い場合、RDY/BSYの負パルスは現れません。

## 電気的特性

### 絶対最大定格 (警告)

| 動作温度 ・・・・・・・・・・・・・・・・・・・・・・・・・ -40℃ ~ +105℃ |

|---------------------------------------------|

| 保存温度 ・・・・・・・・・・・ −65℃ ~ +150℃               |

| ピン許容電圧 ・・・・・・・・・-1.0V ~ VCC+0.5V            |

| 最大動作電圧 ····· 6.6V                           |

| 入出力ピン出力電流 ・・・・・・・・・・・・・・ 20.0mA             |

| 消費電流 ······ 100.0mA                         |

#### (警告)

絶対最大定格を超える負担はデバイスに定常的な損傷を与えます。 絶対最大定格は負担の定格を示すためだけのもので、この値また は、この仕様書の動作特性で示された値を超える条件で動作する ことを示すものではありません。長時間の最大定格での使用はデバイスの信頼性を損なう場合があります。

#### DC特性

TA=-40°C~85°C, VCC=3.3V~6.0V (特に指示された条件を除く)

| シンホ゛ル            | 項目                            | 条              | 件        | 最小                   | 代表   | 最大                   | 単位     |

|------------------|-------------------------------|----------------|----------|----------------------|------|----------------------|--------|

| VIL              | Lowレベル入力電圧                    | XTAL1を除        | :<       | -0.5                 |      | 0.3VCC ( <b>注1</b> ) |        |

| V <sub>IL1</sub> | Lowレベル入力電圧                    | XTAL1          |          | -0.5                 |      | 0.2VCC ( <b>注1</b> ) |        |

| VIH              | Highレヘブル入力電圧                  | XTAL1,RESETを除く |          | 0.6VCC ( <b>注2</b> ) |      | VCC+0.5              |        |

| VIH1             | Highレヘブル入力電圧                  | XTAL1          |          | 0.8VCC ( <b>注2</b> ) |      | VCC+0.5              | V      |

| V <sub>IH2</sub> | Highレヘブル入力電圧                  | RESET          | RESET    |                      |      | VCC+0.5              |        |

| Vol              | Lレヘ・ル出力電圧(ポートA) (注3)          | IOL=1mA, V     | /CC=2.5V |                      |      | 0.1                  |        |

| Voh              | Hレヘブル出力電圧(ポートA) ( <b>注4</b> ) | IOH=-1mA,      | VCC=2.5V | 1.44                 |      |                      |        |

| IIL              | I/OビンLowレベル入力漏れ電流             | VCC=6V         |          |                      |      | 8.0                  | 11 Λ   |

| IIH              | I/OビンHighレベル入力漏れ電流            | (確実なH/L        | 上範囲)     |                      |      | 8.0                  | μA     |

| RRST             | RESETピン プルアップ抵抗               |                |          | 100                  |      | 500                  | kΩ     |

| RPEN             | PENピン プルアップ抵抗                 |                |          | 30                   |      | 250                  | K 22   |

|                  | <br> 活動動作消費電流                 | VCC=3.6V       | ADC禁止    |                      | 1.5  | 2.0                  |        |

|                  |                               | 1MHz           | ADC許可    |                      | 1.9  | 2.7                  | mA     |

| ICC              | アパル動作消費電流                     | VCC=3.6V       | ADC禁止    |                      | 0.25 | 1.0                  | 111/-1 |

|                  |                               | 1MHz           | ADC許可    |                      | 0.7  | 1.7                  |        |

|                  | パワーダウン動作消費電流                  | VCC=3.6V       |          |                      | 1    | 10                   | μA     |

注1: Lowレベルの認識が保証される最高電圧です。

注2: Highレベルの認識が保証される最低電圧です。

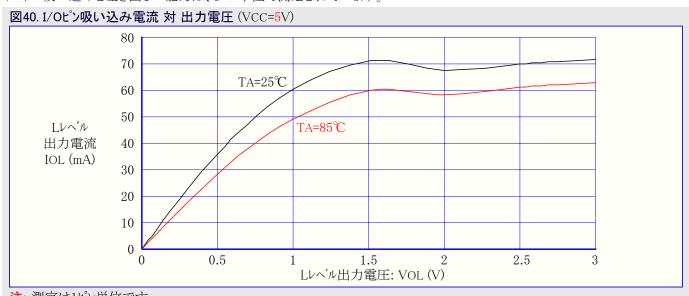

注3: 各I/Oポートは安定状態(非過渡時)に於いては、検査条件(VCC=2.5Vで1mA)より多くの吸い込み電流を流すことができますが、次の条件を厳守してください。

① 全ポートのIOLの合計が80mAを超えるべきではありません。

IOLが検査条件を超える場合、VOLも仕様書での値を超えます。表の検査条件より大きな吸い込み電流を流すことは保証されません。

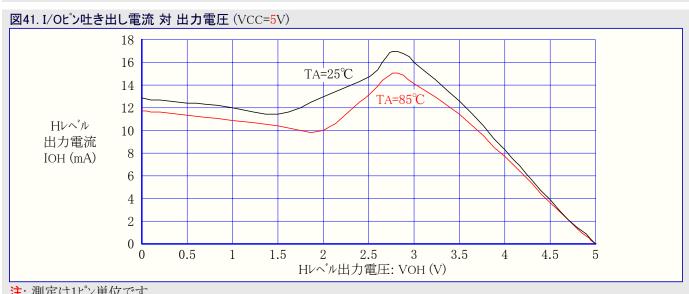

**注4**: 各I/Oポートは安定状態(非過渡時)に於いては、検査条件(VCC=2.5Vで1mA)より多くの吐き出し電流を流すことができますが、次の条件を厳守してください。

① 全ポートのIOHの合計が80mAを超えるべきではありません。

IOHが検査条件を超える場合、VOHも仕様書での値を超えます。表の検査条件より大きな吐き出し電流を流すことは保証されません。

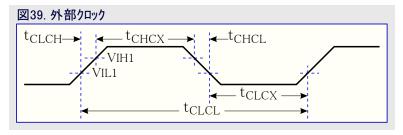

### 外部クロック特性

| > . I * | 1          | VCC=3.3 | .,,,,, |     |  |

|---------|------------|---------|--------|-----|--|

| シンホ゛ル   | 項目         | 最小      | 最大     | 単位  |  |

| 1/tclcl | クロック周波数    | 0       | 1.5    | MHz |  |

| tclcl   | クロック周期     | 667     |        |     |  |

| tchcx   | Highレヘブル時間 | 267     |        | ns  |  |

| tclcx   | Lowレヘブル時間  | 267     |        |     |  |

| tclch   | 上昇時間       |         | 0.5    | 110 |  |

| tchcl   | 下降時間       |         | 0.5    | μs  |  |

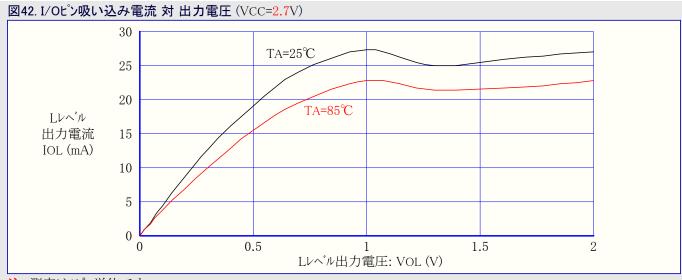

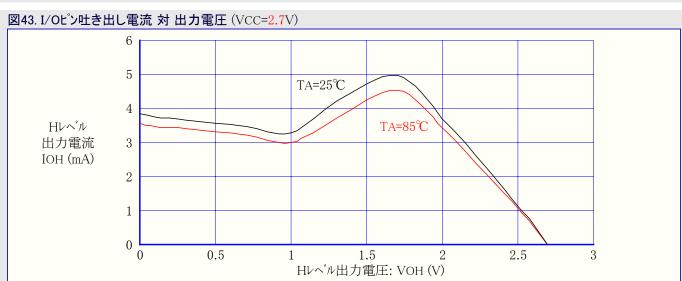

## 代表特性

以下の図で代表的な特性を示します。これらの図は特性を表していますが、製造時の検査は行っていません。 I/Oポートの吸い込みと吐き出しの能力は、1ピン単位で測定されています。

注: 測定は1ピン単位です。

注: 測定は1ピン単位です。

注: 測定は1ピン単位です。

## レジスタ要約

| アト・レス                      | レジスタ略称        | ヒ゛ットフ | ヒ゛ット6  | ヒ゛ット5  | ヒ゛ット4              | ヒ゛ット3     | <b>ビット2</b>     | ヒット1   | ビット0   | 頁        |

|----------------------------|---------------|-------|--------|--------|--------------------|-----------|-----------------|--------|--------|----------|

| \$3F (\$5F)                | SREG          | I     | T      | Н      | S                  | V         | N               | Z      | C      | 10       |

| \$3E (\$5E)                | SPH           | -     | _      | -      | -                  | -         | -               | -      | SP8    | 10       |

| \$3D (\$5D)                | SPL           | SP7   | SP6    | SP5    | SP4                | SP3       | SP2             | SP1    | SP0    | 10       |

| \$3C (\$5C)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$3B (\$5B)                | GIMSK         | INT1  | INT0   | -      | -                  | -         | -               | -      | -      | 13       |

| \$3A (\$5A)                | GIFR          | INTF1 | INTF0  | -      | -                  | _         | -               | -      | -      | 13       |

| \$39 (\$59)                | TIMSK         | _     | _      | _      | _                  | -         | TOIE1           | -      | TOIE0  | 14       |

| \$38 (\$58)<br>\$37 (\$57) | TIFR<br>予約    | -     | -      | -      | -                  | -         | TOV1            | _      | TOV0   | 14       |

| \$36 (\$56)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$35 (\$55)                | MCUCR         | -     | SE     | SM     | -                  | -         | ISC1            | _      | ISC0   | 15       |

| \$34 (\$54)                | 予約            |       | OL     | DIVI   |                    |           | 1501            |        | 1500   | 10       |

| \$33 (\$53)                | TCCR0         | -     | _      | -      | -                  | -         | CS02            | CS01   | CS00   | 18       |

| \$32 (\$52)                | TCNT0         |       |        |        | タイマ/>              | カウンタ0     |                 |        |        | 18       |

| \$31 (\$51)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$30 (\$50)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$2F (\$4F)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$2E (\$4E)                | TCCR1         | _     | -      | -      | -                  | -         | CS12            | CS11   | CS10   | 19       |

| \$2D (\$4D)                | TCNT1H        |       | 1      | +      | タイマ/カウンタ           |           |                 |        |        | 19       |

| \$2C (\$4C)                | TCNT1L        |       |        |        | タイマ/カウンタ           | 1 ト位ハイト   |                 |        |        |          |

| \$2B (\$4B)                |               |       |        |        |                    |           |                 |        |        |          |

| \$2A (\$4A)<br>\$29 (\$49) | 予約<br>予約      |       |        |        |                    |           |                 |        |        |          |

| \$29 (\$49)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$27 (\$47)                | 予約            |       |        |        |                    |           |                 |        |        | $\vdash$ |

| \$26 (\$46)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$25 (\$45)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$24 (\$44)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$23 (\$43)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$22 (\$42)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$21 (\$41)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$20 (\$40)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$1F (\$3F)                | EEARH         | -     | -      | -      | -                  | -         | -               | -      | EEAR8  | 20       |

| \$1E (\$3E)                | EEARL         |       | 1      | EEPRON | <b>Mアドレス レシ スタ</b> |           | £AR7∼0)         |        |        |          |

| \$1D (\$3D)<br>\$1C (\$3C) | EEDR          |       |        |        | EEPROMF            | EERIE     | EEMWE           | EEWE   | EERE   | 20 20    |

| \$1B (\$3B)                | EECR<br>PORTA |       | PORTA6 | PORTA5 | PORTA4             | PORTA3    | EEMWE<br>PORTA2 | PORTA1 | PORTA0 | 27       |

| \$1A (\$3A)                | DDRA          | _     | DDA6   | DDA5   | DDA4               | DDA3      | DDA2            | DDA1   | DDA0   | 27       |

| \$19 (\$39)                | 予約            |       | DD110  | DDN    | DD/14              | DDN       | DDNZ            | DDM    | DDN    | 1        |

| \$18 (\$38)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$17 (\$37)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$16 (\$36)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$15 (\$35)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$14 (\$34)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$13 (\$33)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$12 (\$32)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$11 (\$31)                | 予約<br>CIDD    | _     | _      |        | _                  | IDINI1    | IDINO           | _      | _      | 1.4      |

| \$10 (\$30)<br>\$0F (\$2F) | GIPR<br>予約    | _     | _      | -      | _                  | IPIN1     | IPIN0           | _      | _      | 14       |

| \$0F (\$2F)<br>\$0E (\$2E) | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$0D (\$2D)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$0C (\$2C)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$0B (\$2B)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$0A (\$2A)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$09 (\$29)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$08 (\$28)                | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$07 (\$27)                | ADMUX         | -     | -      | -      | -                  | -         | MUX2            | MUX1   | MUX0   | 24       |

| \$06 (\$26)                | ADCSR         | ADEN  | ADSC   | ADFR   | ADIF               | ADIE      | ADPS2           | ADPS1  | ADPS0  | 24       |

| \$05 (\$25)                | ADCH          | -     | -      | -      | -                  | -         | -               | ADC9   | ADC8   | 25       |

| \$04 (\$24)                | ADCL          |       |        | A/D    | データ レジスタ下          | 位ハイト (ADC | 7~0)            |        |        |          |

| \$01~\$03                  | 予約            |       |        |        |                    |           |                 |        |        |          |

| \$00 (\$20)                | 予約            |       |        |        |                    |           |                 |        |        | ш        |

注: 将来のデバイスとの共通性のため、予約ビットへ書く場合は0を書くべきです。予約されたI/Oメモリ アドレスへは決して書くべきではありません。

# 命令要約

| ニーモニック       | オペラント゛        | 意味                                      | 動作                                                   | フラク゛                                 | クロック              |

|--------------|---------------|-----------------------------------------|------------------------------------------------------|--------------------------------------|-------------------|

|              |               |                                         | <b>国演算命令</b>                                         |                                      |                   |

| ADD          | Rd,Rr         | 汎用レシブスタ間の加算                             | Rd ← Rd + Rr                                         | I,T,H,S,V,N,Z,C                      | 1                 |

| ADC          | Rd,Rr         | キャリーを含めた汎用レジスタ間の加算                      | $Rd \leftarrow Rd + Rr + C$                          | I,T,H,S,V,N,Z,C                      | 1                 |

| ADIW         | Rd,K6         | 即値のワード長加算                               | RdH:RdL ← RdH:RdL + K6                               | I,T,H,S,V,N,Z,C                      | 2                 |

| SUB          | Rd,Rr         | 汎用レジスタ間の減算                              | Rd ← Rd − Rr                                         | I,T,H,S,V,N,Z,C                      | 1                 |

| SUBI         | Rd,K          | 汎用レジスタから即値の減算                           | Rd ← Rd − K                                          | I,T,H,S,V,N,Z,C                      | 1                 |

| SBIW         | Rd,K6         | 即値のワート・長減算                              | RdH:RdL ← RdH:RdL - K6                               | I,T,H,S,V,N,Z,C                      | 2                 |

| SBC          | Rd,Rr         | キャリーを含めた汎用レジスタ間の減算                      | $Rd \leftarrow Rd - Rr - C$                          | I,T,H,S,V,N,Z,C                      | 1                 |

| SBCI         | Rd,K          | 汎用レジスタからキャリーと即値の減算                      | $Rd \leftarrow Rd - K - C$                           | I,T,H,S,V,N,Z,C                      | 1                 |

| AND          | Rd,Rr         | 汎用レジスタ間の論理積(AND)                        | Rd ← Rd AND Rr                                       | I,T,H,S,0,N,Z,C                      | 1                 |

| ANDI         | Rd,K          | 汎用レジスタと即値の論理積(AND)                      | $Rd \leftarrow Rd \ AND \ K$                         | I,T,H,S,0,N,Z,C                      | 1                 |

| OR<br>ORI    | Rd,Rr<br>Rd,K | 汎用レジスタ間の論理和(OR)<br>汎用レジスタと即値の論理和(OR)    | Rd ← Rd OR Rr<br>Rd ← Rd OR K                        | I,T,H,S,0',N,Z,C<br>I,T,H,S,0',N,Z,C | 1                 |

| EOR          | Rd,Rr         | 汎用レジスタと即個の調理和(OR) 汎用レジスタ間の排他的論理和(Ex-OR) | Rd ← Rd OR K<br>Rd ← Rd EOR Rr                       | I,T,H,S,0,N,Z,C                      | 1                 |

| COM          | Rd, Rf        | 1の補数(論理反転)                              | $Rd \leftarrow \$FF - Rd$                            | I,T,H,S,0,N,Z,C                      | 1                 |

| NEG          | Rd            | 2の補数                                    | Rd ← \$00 - Rd                                       | I,T,H,S,V,N,Z,C                      | 1                 |

| SBR          | Rd,K          | 汎用レジスタの(複数)ビット設定(1)                     | Rd ← Rd OR K                                         | I,T,H,S,V,N,Z,C                      | 1                 |

| CBR          | Rd,K          | 汎用レジスタの(複数)ビット解除(0)                     | $Rd \leftarrow Rd \ AND \ (\$FF - K)$                | I,T,H,S,V,N,Z,C                      | 1                 |

| INC          | Rd            | 汎用レジスタの増加(+1)                           | Rd ← Rd + 1                                          | I,T,H,S,V,N,Z,C                      | 1                 |

| DEC          | Rd            | 汎用レジスタの減少(-1)                           | $Rd \leftarrow Rd - 1$                               | I,T,H,S,V,N,Z,C                      | 1                 |

| TST          | Rd            | 汎用レジスタのゼロとマイナス検査                        | Rd ← Rd AND Rd                                       | I,T,H,S,V,N,Z,C                      | 1                 |

| CLR          | Rd            | 汎用レジスタの全 <mark>0</mark> 設定(=\$00)       | Rd ← Rd EOR Rd                                       | I,T,H,0,0,0,1,C                      | 1                 |

| SER          | Rd            | 汎用レジスタの全1設定(=\$FF)                      | Rd ← \$FF                                            | I,T,H,S,V,N,Z,C                      | 1                 |

|              |               |                                         | 命令                                                   | -, -, -, -, -, -, -, -, -, -, -      |                   |

| RJMP         | k             | 相対分岐                                    | $PC \leftarrow PC + k + 1$                           | I,T,H,S,V,N,Z,C                      | 2                 |