# AT90PWM2. AT90PWM2B. AT90PWM3. AT90PWM3B

# 8Kバイト実装書き込み可能フラッシュ メモリ付き Atmel 8ビット マイクロ コントローラ

データシート

#### 特徴

- 高性能、低消費AVR® 8ビット マイクロ コントローラ

- 進化したRISC構造

- 強力な129命令(多くは1周期で実行)

- 32個の1バイト長汎用レジスタ

- 完全なスタティック動作

- 1MHz当たり、1MIPSに達する高速動作

- 2周期実行の乗算命令

- データ メモリと不揮発性プログラム メモリ

- 実装書き換え可能な8Kバイト(4K語)フラッシュ メモリ内蔵(10,000回の書き換えが可能)

- 個別施錠ビットを持つ任意のブート コード領域

- ・チップウンートプログラムによる自己書き換え

- ・真の書き込み中の読み出し動作

- 実装書き換え可能な512 が 小のEEPROM (100,000回の書き換えが可能)

- 512バイトの内蔵SRAM

- ソフトウェア保護用の設定可能な施錠機能

- デバッグWIRE内蔵デバッグ機能

- 内蔵周辺機能

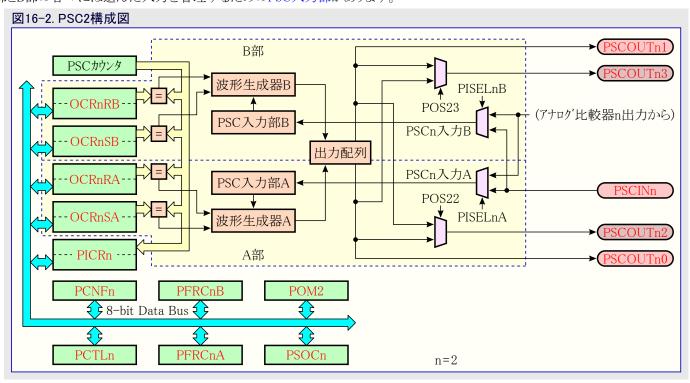

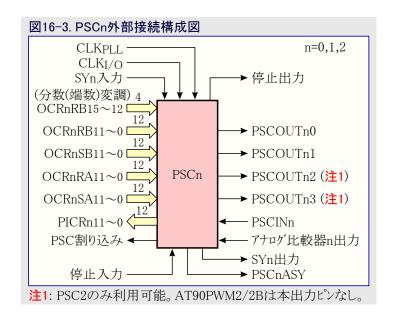

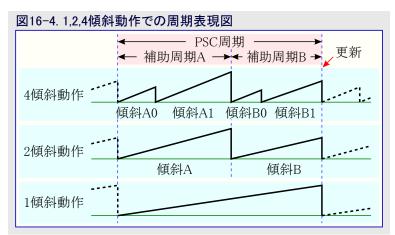

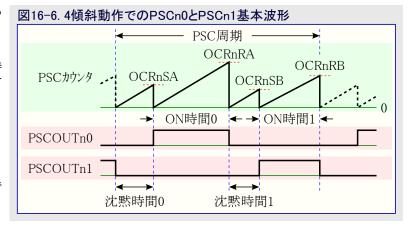

- 4ビット分解能増強付き、2または3つの12ビット高速電力段制御器(PSC)

- ・柔軟な沈黙時間付き非重複反転PWM出力ピン

- ・可変PWMデューティ比と可変PWM周波数

- ・全PWMレジスタの同期更新

- ・事象駆動力率改善(PFC)実装用、自動停止機能

- ・150kHzで25Hz未満幅の段階

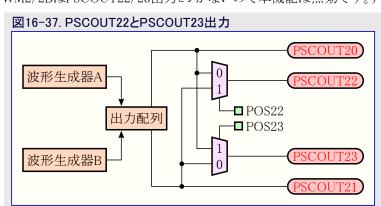

- ・4つの出力ピンと出力配列の電力段制御器2(PSC2)

- 独立した前置分周器、比較機能付き、1つの汎用8ビットタイマ/カウンタ

- 独立した前置分周器、比較、捕獲機能付き、1つの汎用16ビットタイマ/カウンタ

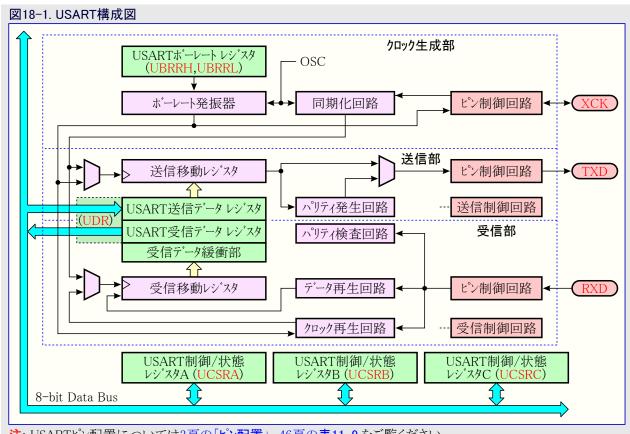

- 設定可能な直列USART

- ・標準UART動作

- ・DALI (Digital Addressable Lighting Interface) 通信用16/17ビット両位相(Biphase)動作

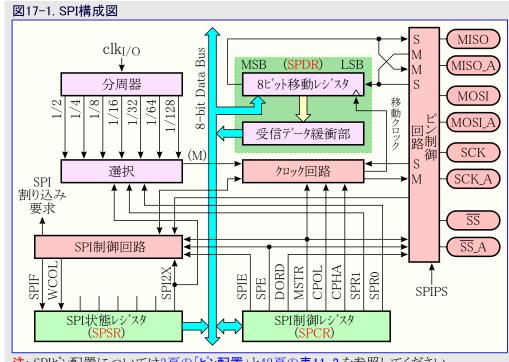

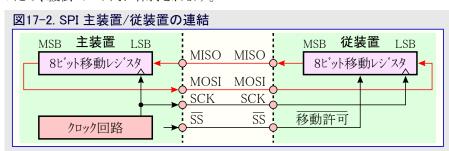

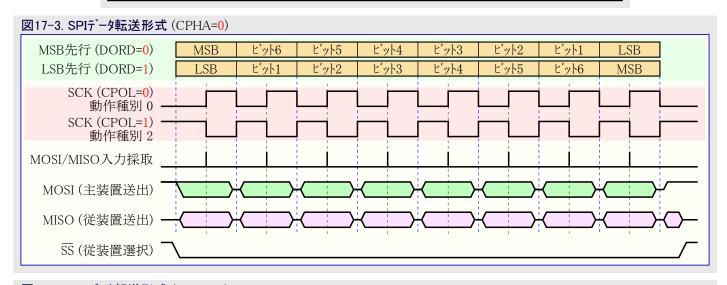

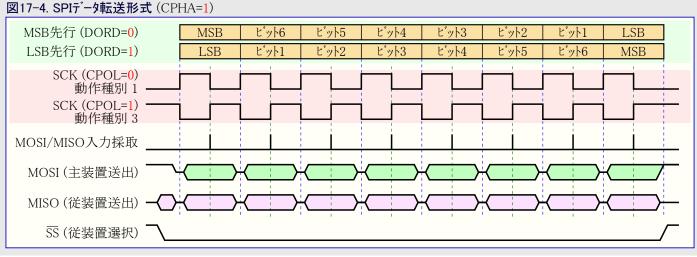

- 主装置/従装置動作SPI直列インターフェース

- 10ビット A/D変換器

- ・8または11までのシングルェント、入力チャネルと、1または2つの完全な差動チャネル対

- ・設定可能な利得(差動チャネルでの $\times$ 5, $\times$ 10, $\times$ 20, $\times$ 40)

- · 内部基準電圧

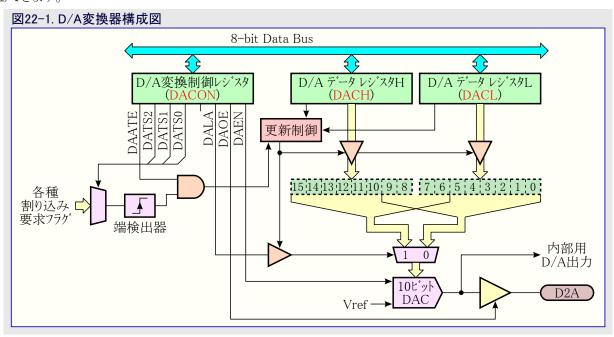

- 10t'ット D/A変換器 (AT90PWM2/2Bは出力ピンなし)

- 比較電圧調整用抵抗列付き、2/3つのアナログ比較器

- 3または4つの外部割り込み

- 設定可能な専用発振器付きウォッチト、ッグ・タイマ

- 特殊マイクロ コントローラ機能

- アイドル、A/D変換雑音低減、パワーダウン、スタンバイの4つの低消費動作

- 電源ONリセット回路と設定可能な低電圧検出器(BOD)

- ビット設定可能なI/O空間内のフラグ列(4バイト)

- SPIポート経由での実装書き込み

- 校正可能な内蔵RC発振器 (8MHz)

- 高速PWM(32MHz, 64MHz)とCPU(16MHz)用のチップ上PLL

- 動作電圧: 2.7~5.5V

- 拡張された温度範囲: -40~105℃

本書は一般の方々の便宜のため有志により作成されたもので、Atmel社とは無関係であることを御承知ください。しおりの[はじめに]での内容にご注意ください。

| 製品名         | 外囲器          | 沈黙時間付き     | A/D | 変換器    | アナロク゛ | 応用例               |

|-------------|--------------|------------|-----|--------|-------|-------------------|

| <b>老</b> 四位 | 77四份         | 12ビットPWM数  | 入力数 | 差動増幅器数 | 比較器数  | 까가게행              |

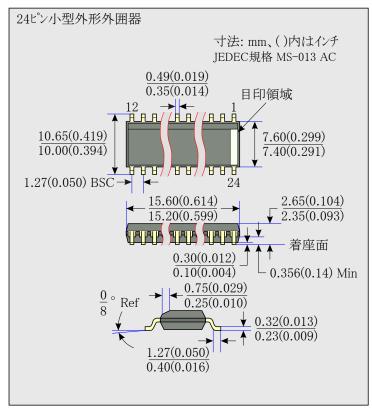

| AT90PWM2/2B | SOIC24       | $2\times2$ | 8   | 1      | 2     | 単一調光安定器           |

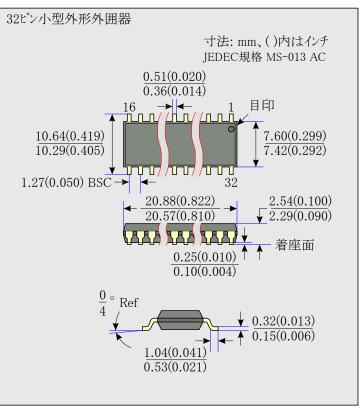

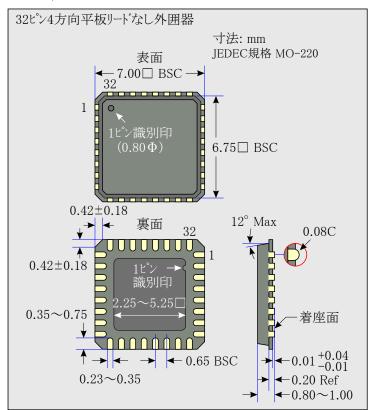

| AT90PWM3/3B | SOIC32,QFN32 | 3×2        | 11  | 2      | 3     | HID安定器,調光安定,電動機制御 |

# 1. 履歴

| 製品           | 版                                                                                                                                                                                                                                                                                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AT90PWM2/3   | デバイスの(マスク)初版、継続中製品用のみ。                                                                                                                                                                                                                                                                                                                                    |

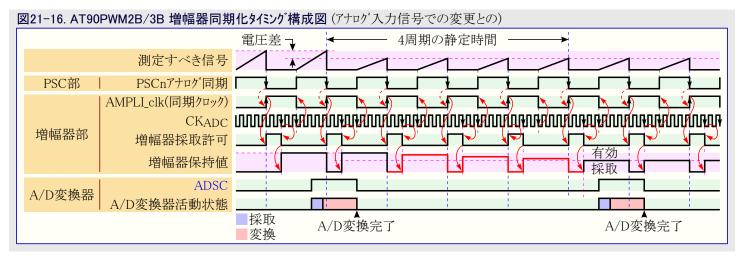

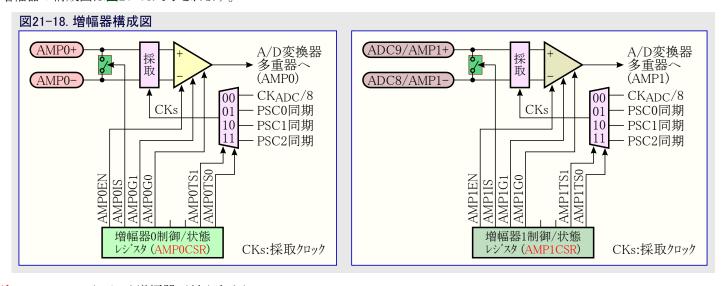

| AT90PWM2B/3B | デバイスの(マスケ)第2版、全ての新規開発用。主変更点: ・中央整列動作でのPSCOUT01,PSCOUT11,PSCOUT21極性補足(逆相) - 90頁の「中央整列動作」をご覧ください。 ・電力段制御器(PSC)捕獲ソフトウェア起動を追加 - 108頁の「PICRnH,PICRnL - PSCn捕獲レジスタ」をご覧ください。 ・電力段制御器(PSC)出力活動読み取りビットを追加 - 109頁の「PIFRn - PSCn割り込み要求フラケ レジスタ」をご覧ください。 ・いくつかのクロック(選択)設定を追加 - 18頁の表7-2.をご覧ください。 ・増幅器同期化変更 - 154頁の「増幅器」と図21-16.をご覧ください。 ・障害情報修正 - 213頁の「障害情報」をご覧ください。 |

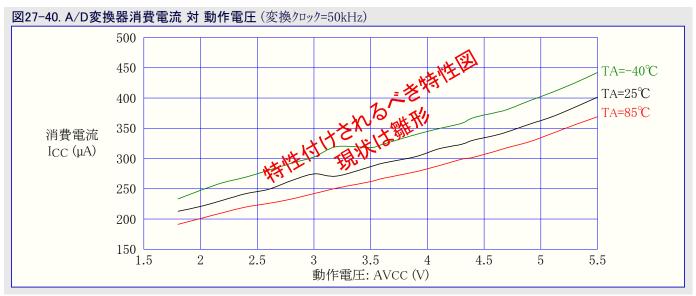

このデータシートはAT90PWM2とAT90PWM3の製品特性を取り扱います。これは特性付けが行われると直ぐに更新されるでしょう。

# 2. お断り

本データシート内で示された代表値はシミュレーションと同じ製法技術で製造された他のAVRマイクロコントローラの特性を基にしています。最小と最大の値はデバイスの特性が記載された後に利用可能になります。

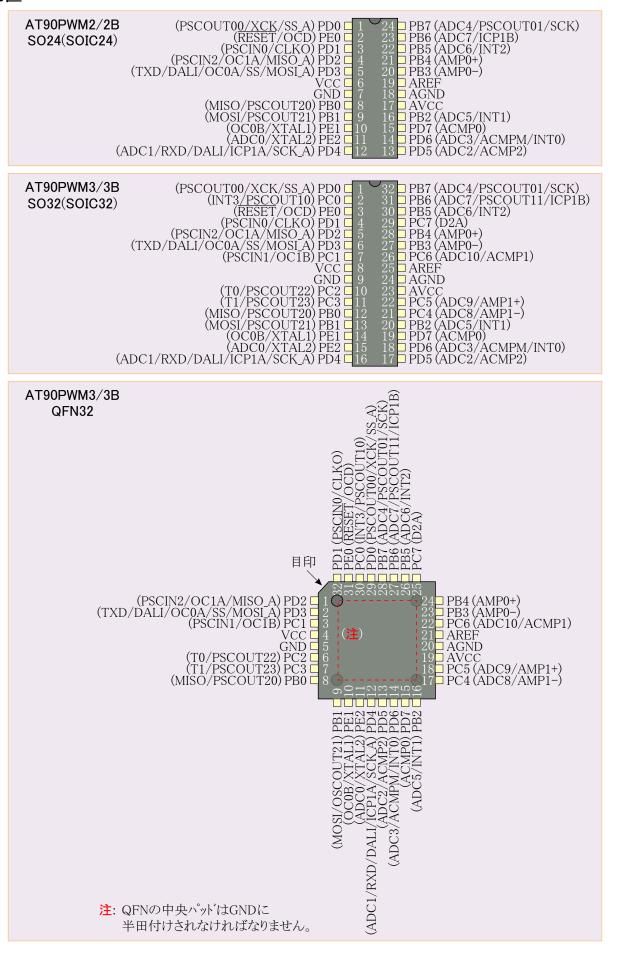

#### 3. ピン配置

# 3.1. ピン概要

表3-1. ピン割り当て説明

|        | ピン番号   |       | L°V. Æ | 形式    | □                                                                                                  |

|--------|--------|-------|--------|-------|----------------------------------------------------------------------------------------------------|

| SO24   | SO32   | QFN32 | ピン名    | 分類    | <b>名称、機能、代替機能</b>                                                                                  |

| 7      | 9      | 5     | GND    | 電源    | 接地: 0V基準                                                                                           |

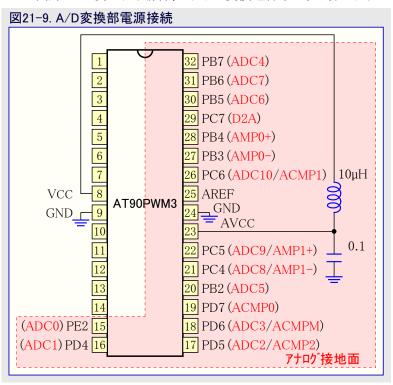

| 18     | 24     | 20    | AGND   | 電源    | アナログ接地: アナログ部用0V基準                                                                                 |

| 6      | 8      | 4     | VCC    | 電源    | 電力供給:                                                                                              |

| 17     | 23     | 19    | AVCC   | 電源    | アナログ電力供給:これはアナログ部用の供給電力電圧です。                                                                       |

| 19     | 25     | 21    | AREF   | 電源    | アナログ基準電圧: これはA/D変換器用基準電圧です。<br>通常使用で本ピンは接続されなければなりません。                                             |

| 8      | 12     | 8     | PB0    | I/O   | MISO (SPI 主側入力/従側出力) PSCOUT20 出力                                                                   |

| 9      | 13     | 9     | PB1    | I/O   | MOSI (SPI 主側出力/従側入力) PSCOUT21 出力                                                                   |

| 16     | 20     | 16    | PB2    | I/O   | ADC5 (アナログ) 入力チャネル5) INT1 (外部割り込み1入力)                                                              |

| 20     | 27     | 23    | PB3    | I/O   | AMP0- (アナロケ・差動増幅器0 反転入力チャネル)                                                                       |

| 21     | 28     | 24    | PB4    | I/O   | AMP0+ (アナロケ 差動増幅器0 非反転入力チャネル)                                                                      |

| 22     | 30     | 26    | PB5    | I/O   | ADC6 (アナログ) 入力チャネル6) INT2 (外部割り込み2入力)                                                              |

| 23     | 31     | 27    | PB6    | I/O   | ADC7 (アナログ入力チャネル7) ICP1B (タイマ/カウンタ1捕獲起動代替入力) PSCOUT11 出力(注1参照)                                     |

| 24     | 32     | 28    | PB7    | I/O   | SCK (SPI クロック入出力) ADC4 (アナロケ、入力チャネル4) PSCOUT01 出力                                                  |

|        | 2      | 30    | PC0    | I/O   | INT3 (外部割り込み3入力) PSCOUT10 出力(注1参照)                                                                 |

|        | 7      | 3     | PC1    | I/O   | OC1B (タイマ/カウンタ1比較B出力) PSCIN1 (電力段制御器(PSC)1 デジタル入力)                                                 |

| 利      | 10     | 6     | PC2    | I/O   | T0 (タイマ/カウンタ0外部クロック入力) PSCOUT22 出力                                                                 |

| 用      | 11     | 7     | PC3    | I/O   | T1 (タイマ/カウンタ1外部クロック入力) PSCOUT23 出力                                                                 |

| 不      | 21     | 17    | PC4    | I/O   | ADC8 (アナログ)入力チャネル8)AMP1- (アナログ)差動増幅器1 反転入力チャネル)                                                    |

| 可      | 22     | 18    | PC5    | I/O   | ADC9 (アナログ) 入力チャネル9) AMP1+ (アナログ) 差動増幅器1 非反転入力チャネル)                                                |

|        | 26     | 22    | PC6    | I/O   | ADC10 (アナロケ`入力チャネル10) ACMP1 (アナロケ`比較器1 非反転入力)                                                      |

|        | 29     | 25    | PC7    | I/O   | D2A (D/A変換器出力) ( <b>注2</b> 参照)                                                                     |

| 1      | 1      | 29    | PD0    | I/O   | XCK (USART 転送クロック入出力) SS_A (代替SPI 従装置選択入力) PSCOUT00 出力                                             |

| 3      | 4      | 32    | PD1    | I/O   | CLKO (システム クロック出力) PSCINO (電力段制御器(PSC)O デ・シ・タル入力)                                                  |

| 4      | 5      | 1     | PD2    | I/O   | OC1A (タイマ/カウンタ1比較A出力) MISO_A (プログラミングと代替SPI 主側入力/従側出力) PSCIN2 (電力段制御器(PSC)2 デジ゙タル入力)               |

| 5      | 6      | 2     | PD3    | I/O   | TXD (USART/DALI 送信データ出力) OC0A (タイマ/カウンタ0比較A出力) SS (SPI 従装置選択入力) MOSI_A (プログラミングと代替SPI 主側出力/従側入力)   |

| 12     | 16     | 12    | PD4    | I/O   | RXD (USART/DALI 受信データ入力) ICP1A (タイマ/カウンタ1捕獲起動入力) ADC1 (アナログ・入力チャネル1) SCK_A (プログラミングと代替SPI クロック入出力) |

| 13     | 17     | 13    | PD5    | I/O   | ADC2 (アナログ)入力チャネル2) ACMP2 (アナログ)比較器2 非反転入力)                                                        |

| 14     | 18     | 14    | PD6    | I/O   | ADC3 (アナログ) 入力チャネル3) ACMPM (アナログ) 比較器基準反転入力) INTO (外部割り込み0入力)                                      |

| 15     | 19     | 15    | PD7    | I/O   | ACMP0 (アナログ) 比較器0 非反転入力)                                                                           |

| 2      | 3      | 31    | PE0    | I/O   | RESET (外部リセット入力) OCD (内蔵デバックWIRE機能入出力)                                                             |

| 10     | 14     | 10    | PE1    | I/O   | XTAL1 (発振増幅器入力) OC0B (タイマ/カウンタ0比較B出力)                                                              |

| 11     | 15     | 11    | PE2    | I/O   | XTAL2 (発振増幅器出力) ADCO (アナログ) 入力チャネルの)                                                               |

| 1: PS0 | COUT10 | トPSCO | UT11は  | 24ピンタ | ・<br>・囲器にはありません。                                                                                   |

注1: PSCOUT10とPSCOUT11は24ピン外囲器にはありません。

**注2**: D2A(D/A変換器出力)はAT90PWM216(24t°ンSOIC)で利用できません。

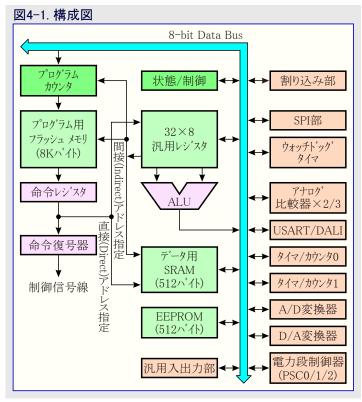

#### 4. 概要

AT90PWM2/2B/3/3BはAVR強化RISC構造の低消費CMOS 8ビット マイクロ コントローラです。1周期で実行する強力な命令はMHzあたり 1 MIPSにも達し、実行速度対電力消費の最適化が容易に行えます。

#### 4.1. 構成図

AVRコアは32個の汎用作業レジスタと豊富な命令群を兼ね備えています。32個の全レジスタはALU(Arithmetic Logic Unit)に直結され、レジスタ間命令は1クロック周期で実行されます。AVR構造は現状のCISC型マイクロコントローラに対して10倍以上の単位処理量向上効果があります。

AT90PWM2/2B/3/3Bは次の特徴、書き込み中読める能力を持 つ8Kバイトの実装書き換え可能なフラッシュメモリと512バイトのEEPRO M、512小小のSRAM、19/27本の汎用入出力線、32個の汎用作業 レジブスタ、2/3つの電力段制御器(PSC)、比較動作やPWMを含む柔 軟性のある2つのタイマ/カウンタ、DALI動作付きの1つのUSART、設 定可能な増幅器を持つ1/2つの差動入力段付きの任意選択差動 入力付き8/11チャネルの10ビット A/D変換器、10ビット D/A変換器、 設定可能な内部発振器付きウォッチドッグタイマ、SPI直列ポート、内蔵 デバッグ システム、ソフトウェアで選べる4つの低消費動作機能を提供し ます。アイドル動作では動作を停止しますが、SRAM、タイマ/カウンタ、 SPIポート、割り込み機能は有効で、動作を継続します。パワーダウン 動作ではレジスタの内容は保護されますが、発振器が停止するた め、以降のハートウェアリセットか外部割り込みまで他の全機能を禁止 (無効に)します。A/D変換雑音低減動作ではA/D変換中の切り替 え雑音を最小とするために、A/D変換器を除く全ての周辺機能と CPUが停止します。スタンバイ動作ではクリスタル発振子/セラミック振動 子用発振器が動作し、一方デバイスのその他は休止します。これ は低消費電力と非常に速い起動の組み合わせを許します。

本デバイスはAtmelの高密度不揮発性メモリ技術を使って製造されています。内蔵の実装書き換え(ISP)可能なプログラム用フラッシュメモリは規定の不揮発性メモリ書き込み器、SPI直列インターフェース経由、AVRコア上プートプログラムの実行によって再書き込みができます。プートプログラムは応用領域フラッシュメモリ内の応用プログラムの読み込みにどのインターフェースでも使えます。プート領域フラッシュメモリ内のプログラムは真の「書き込み中の読み出し可」動作により、応用領域フラッシュメモリ更新中も実行を継続します。モノリシックチップ上の実装書き換え可能なフラッシュメモリと、8ビットRISC型CPUの組み合わせによるAtmel AT90PWM2/2B/3/3Bは多くの組み込み制御の応用に対して高度な柔軟性と対費用効果をもたらす強力なマイクロコントローラです。

AT90PWM2/2B/3/3B AVRはCコンパイラ、マクロ アセンブラ、デバッカ、シミュレータ、インサーキット エミューレータ、評価キットを含む専用のプログラム及びシステム開発ツールで支援されます。

注: AT90PWM2/2Bデバイスは24ピンSOIC外囲器で利用可能ですが、I/OピンへのD2A(D/A変換器出力)出力を持ちません。

#### 4.2. ピン説明

#### 421 VCC

デジタル電源ピン。

#### 4.2.2. GND

接地ピン。

#### **4.2.3.** PB7~PB0 (ホートB)

ポートBは(ビット毎に選ばれる)内蔵プルアップ抵抗付きの8ビットの双方向入出力ポートです。ポートB出力緩衝部は共に高い吐き出し/吸い込み能力の対称駆動特性です。入力の時にプルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートBピンには吐き出し電流が流れます。リセット条件が有効になるとき、クロックが動作していなくても、ポートBピンはHi-Zになります。

ポートBは42頁で一覧されるAT90PWM2/2B/3/3Bの様々な特殊機能も扱います。

#### **4.2.4.** PC7~PC0 (ホートC)

ポートCは(ビット毎に選ばれる)内蔵プルアップ抵抗付きの8ビットの双方向入出力ポートです。ポートC出力緩衝部は共に高い吐き出し/吸い込み能力の対称駆動特性です。入力の時にプルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートCピンには吐き出し電流が流れます。リセット条件が有効になるとき、クロックが動作していなくても、ポートCピンはHi-Zになります。

ポートCは24ピン外囲器で利用できません。

ポートCは44頁で一覧されるAT90PWM3/3Bの様々な特殊機能も扱います。

#### **4.2.5**. PD7~PD0 (ホートロ)

ポートDは(ビット毎に選ばれる)内蔵プルアップ抵抗付きの8ビットの双方向入出力ポートです。ポートD出力緩衝部は共に高い吐き出し/吸い込み能力の対称駆動特性です。入力の時にプルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートDピンには吐き出し電流が流れます。リセット条件が有効になるとき、クロックが動作していなくても、ポートDピンはHi-Zになります。

ポートDは46頁で一覧されるAT90PWM2/2B/3/3Bの様々な特殊機能も扱います。

#### 4.2.6. PE2~PE0 (ポートE). RESET/XTAL1/XTAL2

ポートEは(ビット毎に選ばれる)内蔵プルアップ抵抗付きの3ビットの双方向入出力ポートです。ポートE出力緩衝部は共に高い吐き出し/吸い込み能力の対称駆動特性です。入力の時にプルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートEピンには吐き出し電流が流れます。リセット条件が有効になるとき、クロックが動作していなくても、ポートEピンはHi-Zになります。

RSTDISBLヒューズがプログラム(0)されると、PE0はI/Oピンとして使われます。PE0の電気的特性がポートEの他のピンのそれらと異なることに注意してください。

RSTDISBLヒューズが非プログラム(1)の場合、PE0はリセット入力として使われます。クロックが動作していなくても、最小パルス幅より長いこのピンのLowレヘルはリセットを生成します。最小パルス幅は28頁の表9-1.で与えられます。より短いパルスはリセットの生成が保証されません。

クロック選択ヒューズ設定に依存して、PE1は発振器反転増幅器への入力と内部クロック操作回路への入力として使えます。

クロック選択ヒューズ設定に依存して、PE2は発振器反転増幅器からの出力として使えます。

ポートEの様々な特殊機能は48頁の「ホートEの交換機能」と17頁の「クロック系統とその配給」で詳しく述べられます。

#### 4.2.7. AVCC

AVCCはADC入力とA/D変換器用供給電圧(電源)ピンです。例えA/D変換が使われなくても、外部的にVCCへ接続されるべきです。 A/D変換が使われる場合、低域通過濾波器を通してVCCに接続されるべきです。

#### 4.2.8. AREF

AREFはA/D変換器用アナログ基準(電圧)ピンです。

#### 4.3. コード例について

この文書はデバイスの様々な部分の使用法を手短に示す簡単なコート・例を含みます。これらのコート・例はアセンブルまたはコンパイルに先立ってデバイス定義へッタ・ファイルがインクルートされると仮定します。全てのCコンパイラ製造業者がヘッタ・ファイル内にビット定義を含めるとは限らず、またCでの割り込みの扱いがコンパイラに依存することに注意してください。より多くの詳細についてはCコンパイラの資料で確認してください。

これらのコート 例はアセンブルまたはコンハ イルに先立ってデバイス定義ファイルがインクルート されることが前提です。拡張I/O領域に配置した I/Oレジ スタに対し、IN, OUT, SBIS, SBIC, CBI, SBI命令は拡張I/O領域へのアクセスを許す命令に置き換えられなければなりません。 代表的にはSBRS, SBRC, SBR, CBR命令と組み合わせたLDS, STS命令です。

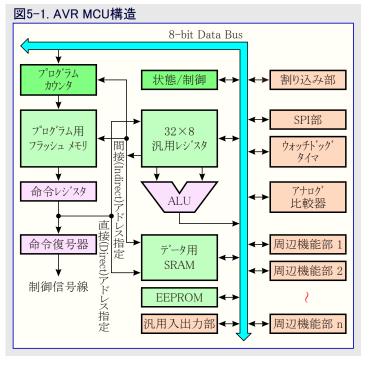

#### 5. AVR CPU コア

#### 5.1. 序説

ここでは一般的なAVRコア構造について説明します。このCPUコアの主な機能は正しいプログラム実行を保証することです。従ってCPU はメモリ アクセス、計算実行、周辺制御、割り込み操作ができなければなりません。

#### 5.2. 構造概要

最大効率と平行処理のため、AVRはプログラムとデータに対してメモリ とハスを分離するハーハート、構造を使います。プログラムメモリ内の命令 は、単一段のハーイプラインで実行されます。1命令の実行中に次の命 令がプログラムメモリから事前取得されます。この概念は全部のクロック 周期で命令実行を可能にします。プログラムメモリは実装書き換え可 能なフラッシュメモリです。

高速レジスタファイルは1クロック周期アクセスの32個の8ビット長汎用レジスタを含みます。これは1クロックALU(Arithmetic Logic Unit)操作を許します。代表的なALU操作では2つのオペラントがレジスタファイルからの出力で、1クロック内でその操作が実行され、その結果がレジスタファイルに書き戻されます。

32個中の6つのレシ、スタは効率的なアト・レス計算ができるデータ空間アト・レス指定用の3つの16ビット長間接アト・レスポーインタ用レシ、スタとして使われます。これらアト・レスポーインタの1つはプログラム用フラッシュメモリ内の定数表参照用アト・レスポーインタとしても使えます。これら16ビット長付加機能レシ、スタはX,Y,Zレシ、スタで、本章内で後述されます。

ALUはレジスタ間またはレジスタと定数間の算術及び論理操作を支援します。単一レジスタ操作もALUで実行できます。算術演算操作後、操作結果についての情報を反映するために、ステータスレジスタ(SREG)が更新されます。

プログラムの流れは条件/無条件分岐や呼び出し命令によって提供され、全アドレス空間を直接アドレス指定できます。AVR命令の多くは

16ビット語(ワード)形式です。全てのプログラム メモリのアドレスは(<mark>訳注</mark>:定数のみを除き)16または32ビット長命令を含みます。

プログラム用フラッシュ メモリ空間はブート プログラム領域と応用プログラム領域の2つに分けられます。 どちらの領域にも書き込み禁止や読み書き防止用の専用施錠ビットがあります。 応用フラッシュ メモリ領域内に書き込むSPM命令はブート プログラム領域内に属さ(存在し)なければなりません。

割り込みやサブルーチン呼び出し中、戻りアトレスを示すプログラム カウンタ(PC)はスタックに保存されます。スタックは一般的なデータ用SRAM上に実際には割り当てられ、従ってスタック容量は全SRAM容量とSRAM使用量でのみ制限されます。全ての使用者プログラムはリセット処理ルーチンで(サブルーチン呼び出しや割り込みが実行される前に)、スタック ホーインタ(SP)を初期化しなければなりません。SPはI/O空間で読み書きアクセスが可能です。データ用SRAMはAVR構造で支援される5つの異なるアトレス指定種別を通して容易にアクセスできます。

AVR構造に於けるメモリ空間は全て直線的な普通のメモリ配置です。

柔軟な割り込み部にはI/O空間の各制御レシ、スタとステータスレシ、スタ(SREG)の特別な全割り込み許可(I)ビットがあります。全ての割り込みは割り込みへ、クタ表に個別の割り込みへ、クタを持ちます。割り込みには割り込みへ、クタ表の位置に従う優先順があります。下位側割り込みへ、クタアドレスが高い優先順位です。

I/Oメモリ空間は制御レジスタ、SPI、他のI/O機能としてCPU周辺機能用の64アドレスを含みます。I/Oメモリは直接またはレジスタ ファイルの次のデータ空間位置\$20~\$5Fとしてアクセスできます。加えてAT90PWM2/2B/3/3BにはST/STS/STDとLD/LDS/LDD命令だけ使えるSRAM内の\$60~\$FFに拡張I/O空間があります。

#### **5.3. ALU** (Arithmetic Logic Unit)

高性能なAVRのALUは32個の全汎用レジスタに直接接続され動作します。汎用レジスタ間または汎用レジスタと即値間の演算操作は単一クロック周期内で実行されます。ALU操作は算術演算、論理演算、ビット操作の3つの主な種類に大別されます。符号付きと符号なし両方の乗算と固定小数点形式を支援する、乗算器(乗算命令)も提供する構造の実装(製品)もあります。詳細記述については「命令要約」章をご覧ください。

#### 5.4. SREG - ステータス レジスタ (Status Register)

ステータス レジスタは最も直前に実行した演算命令の結果についての情報を含みます。この情報は条件処理を行うためのプログラムの流れ変更に使えます。ステータス レジスタは「命令一式手引書」で詳述したように、全てのALU操作後、更新されることに注目してください。これは多くの場合でそれ用の比較命令使用の必要をなくし、高速でより少ないコードに帰着します。

ステータス レジ スタは割り込み処理ルーチン移行時の保存と割り込みからの復帰時の回復(復帰)が自動的に行われません。これはソフトウェアによって扱われなければなりません。

AVRのステータスレジ、スタ(SREG)は次のように定義されます。

| ピット         | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |      |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$3F (\$5F) | I   | Т   | Н   | S   | V   | N   | Z   | С   | SREG |

| Read/Write  | R/W |      |

| 初期値         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

#### • ビット7 - I: 全割り込み許可 (Global Interrupt Enable)

全割り込み許可ビットは割り込みが許可されるために設定(1)されなければなりません。その時の個別割り込み許可制御は独立した制御レジスタで行われます。全割り込み許可ビットが解除(0)されると、個別割り込み許可設定に拘らず、どの割り込みも許可されません。I ビットは割り込みが起こった後にハードウェアによって解除(0)され、後続の割り込みを許可するために、RETI命令によって設定(1)されます。Iビットは「命令一式手引書」で記述されるようにSEIやCLI命令で応用(プログラム)によって設定(1)や解除(0)もできます。

#### • ビット6 - T: ビット変数 (Bit Copy Storage)

ビット複写命令、BLD(Bit LoaD)とBST(Bit STore)は操作したビットの転送元または転送先として、このTビットを使います。レジスタ ファイルのレジスタからのビットはBST命令によってTに複写でき、TのビットはBLD命令によってレジスタ ファイルのレジスタ内のビットに複写できます。

#### • ビット5 - H: **ハーフキャリー フラク** (Half Carry Flag)

ハーフキャリー(H)フラグはいくつかの算術操作でのハーフキャリーを示します。ハーフキャリーはBCD演算に有用です。詳細情報については「命令要約」記述をご覧ください。

#### • ビット4 - S: 符号 (Sign Bit, S= N Ex-OR V)

Sフラグは常に負(N)フラグと2の補数溢れ(V)フラグの排他的論理和です。詳細情報については「命令要約」記述をご覧ください。

#### • ビット3 - V: 2の補数溢れフラグ(2's Complement Overflow Flag)

2の補数溢れ(V)フラグは2の補数算術演算を支援します。詳細情報については「命令要約」記述をご覧ください。

#### • **ビット2** - **N** : **負フラク** (Negative Flag)

負(N)フラグは算術及び論理操作での負の結果(MSB=1)を示します。詳細情報については「命令要約」記述をご覧ください。

#### • t "yh1 - Z : t "D 750" (Zero Flag)

ゼロ(Z)フラグは算術及び論理操作でのゼロ(0)の結果を示します。詳細情報については「**命令要約**」記述をご覧ください。

#### • ビット0 - C: キャリー フラク (Carry Flag)

キャリー(C)フラグは算術及び論理操作でのキャリー(またはボロー)を示します。詳細情報については「**命令要約**」記述をご覧ください。

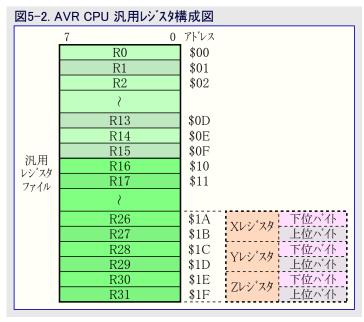

#### 5.5. 汎用レジスタファイル

このレジスタ ファイルはAVRの増強したRISC命令群用に最適化されています。必要な効率と柔軟性を達成するために、次の入出力機構がレジスタ ファイルによって支援されます。

- 1つの8ビット出力オペランドと1つの8ビットの結果入力

- 2つの8ビット出力オペラントと1つの8ビットの結果入力

- 2つの8ビット出力オペランドと1つの16ビットの結果入力

- 1つの16ビット出力オペランドと1つの16ビットの結果入力

図5-2.はCPU内の32個の汎用作業レジスタの構造を示します。

レジスタファイルを操作する殆どの命令は全てのレジスタに直接アクセスし、それらの殆どは単一周期命令です。

図5-2.で示されるように各レジスタは使用者データ空間の最初の32位置へ直接的に配置することで、それらはデータメモリアトレスも割り当てられます。例え物理的にSRAM位置として実装されていなくてもX,Y,Zレジスタ(ポインタ)がレジスタファイル内のどのレジスタの指示にも設定できるように、このメモリ構成は非常に柔軟なレジスタのアクセスを提供します。

#### 5.5.1. Xレシ、スタ、Yレシ、スタ、Zレシ、スタ

R26~R31レジスタには通常用途の使用にいくつかの追加機能があります。これらのレジスタはデータ空間の間接アトレス指定用の16ビットアドレスポーインタです。3つのX,Y,Z間接アトレスレジスタは図5-3.で記載したように定義されます。

種々のアドレス指定種別で、これらのアドレス レジスタは固定変位、 自動増加、自動減少としての機能を持ちます(詳細については 「命令一式手引書」をご覧ください)。

| 図5-3. X,Y,Z          | 図5-3. X,Y,Zレシ、スタ構成図 |            |     |            |    |  |  |  |  |

|----------------------|---------------------|------------|-----|------------|----|--|--|--|--|

|                      | 15                  | XH (上位)    |     | XL (下位)    | 0_ |  |  |  |  |

| X レシ <sup>*</sup> スタ | 7                   | R27 (\$1B) | 0 7 | R26 (\$1A) | 0  |  |  |  |  |

|                      | 15                  | YH (上位)    |     | YL (下位)    | 0  |  |  |  |  |

| Y レジスタ               | 7                   | R29 (\$1D) | 0 7 | R28 (\$1C) | 0  |  |  |  |  |

|                      | 15                  | ZH (上位)    |     | ZL (下位)    | 0  |  |  |  |  |

| Z レシ <sup>・</sup> スタ | 7                   | R31 (\$1F) | 0 7 | R30 (\$1E) | 0  |  |  |  |  |

#### 5.6. SPH.SPL (SP) - スタック ホーインタ (Stack Pointer)

スタックは主に一時データの保存、局所変数の保存、割り込みとサブルーチン呼び出し後の戻りアドレスの保存に使われます。スタック ポインタ レジスタは常にこのスタックの先頭(<mark>訳注</mark>:次に使われるべき位置)を指し示します。スタックが高位メモリから低位メモリへ伸長するように実行されることに注意してください。これはスタックへのPUSH命令はスタック ポインタを減少するという意味です。

スタック ポインタはサブルーチンや割り込みのスタックが配置されるデータSRAMのスタック領域を指し示します。データSRAM内のスタック空間はサブルーチン呼び出しの実行や割り込みの許可の何れにも先立ってプログラムによって定義されなければなりません。スタック ポインタは \$100以上を指示するように設定されなければなりません。スタック ポインタは PUSH命令でデータがスタックに格納されるとー1され、サブルーチン呼び出しや割り込みで戻りアト・レスがスタックに格納されると-2されます。スタック ポインタは POP命令でデータがスタックから引き出されると+1され、サブルーチンからの復帰(RET)命令や割り込みからの復帰(RETI)命令でアト・レスがスタックから引き出されると+2されます。

AVRのスタック ポインタはI/O空間内の2つの8ビット レジスタとして実装されます。実際に使われるビット数は(そのデバイス)実装に依存します。SPLだけが必要とされる程に小さいAVR構造の実装(デバイス)のデータ空間もあることに注意してください。その場合、SPHレジスタは存在しません。

| ピット         | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | _   |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| \$3E (\$5E) | -   | -   | -   | -   | -   | -   | SP9 | SP8 | SPH |

| Read/Write  | R   | R   | R   | R   | R   | R   | R/W | R/W |     |

| 初期値         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |     |

| ピット         | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |     |

| \$3D (\$5D) | SP7 | SP6 | SP5 | SP4 | SP3 | SP2 | SP1 | SP0 | SPL |

| Read/Write  | R/W |     |

| 初期値         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |     |

#### 5.7. 命令実行タイミング

本項は命令実行の一般的なアクセスタイミングの概念を記述します。AVR CPUはチップ(デバイス)用に選んだクロック元から直接的に生成したCPUクロック(clkcpu)によって駆動されます。内部クロック分周は使われません。

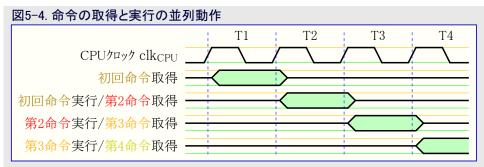

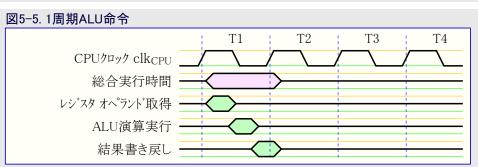

図5-4.はハーハート・構造と高速アクセスレジスタファイルの概念によって可能とされる並列の命令取得と命令実行を示します。これは機能対費用、機能対クロック、機能対電源部に関する好結果と対応するMHzあたり1 MIPSを達成するための基本的なパイプラインの概念です。

図5-5.はレシ、スタファイルに対する内部タイミングの概念を示します。単一クロック周期で2つのレシ、スタオペラント、を使うALU操作が実行され、その結果が転送先レシ、スタへ書き戻されます。

#### 5.8. リセットと割り込みの扱い

AVRは多くの異なる割り込み元を提供します。これらの割り込みと独立したリセット へうタ各々はプログラム メモリ空間内に独立したプログラム へうタを持ちます。全ての割り込みは割り込みを許可するために、ステータス レジスタ(SREG)の全割り込み許可(I)ビットと共に論理1が書かれなければならない個別の許可ビットを割り当てられます。BLB02またはBLB12 ブート施錠ビットがプログラム(0)されると、プログラム カウンタ値によっては割り込みが自動的に禁止されるかもしれません。この特質はソフトウェア保護を改善します。詳細については170頁の「メモリプログラミング」章をご覧ください。

既定でのプログラム メモリ空間の最下位アトレスはリセットと割り込みへブクタとして定義されます。へブクタの完全な一覧は34頁の「割り込み」で示されます。この一覧は各種割り込みの優先順位も決めます。下位側アトレスがより高い優先順位です。リセットが最高優先順位で次が電力段制御器2捕獲発生(PSC2 CAPT)です。割り込みへブクタはMCU制御レシブスタ(MCUCR)の割り込みへブクタ選択(IVSEL)ビットの設定(1)によってブート フラッシュ領域先頭へ移動できます。より多くの情報については34頁の「割り込み」を参照してください。リセットへブクタもBOOT RSTヒューズのプログラム(0)によってブート フラッシュ領域先頭へ移動できます。161頁の「ブートローダ支援 - (書き込み中読み出し可能な自己プログラミング」をご覧ください。

#### 5.8.1. 割り込みの動き

割り込みが起こると全割り込み許可(I)ビットが解除(0)され、全ての割り込みは禁止されます。使用者ソフトウェアは多重割り込みを許可するため、全割り込み許可(I)ビットへ論理1を書けます。その後全ての許可した割り込みが現在の割り込みルーチンで割り込めます。全割り込み許可(I)ビットは割り込みからの復帰(RETI)命令が実行されると、自動的に設定(1)されます。

根本的に2つの割り込み形式があります。1つ目の形式は割り込み要求フラグを設定(I)する事象によって起動されます。これらの割り込みでは割り込み処理ルーチンを実行するために、プログラム カウンタは対応する現実の割り込みへ、クタを指示し、ハートウェアが対応する割り込み要求フラグを解除(0)します。割り込み要求フラグは解除(0)されるべきフラグのビット位置へ論理1を書くことによってもかいじょ(0)できます。対応する割り込み許可ビットが解除(0)されている間に割り込み条件が起こると、割り込み要求フラグが設定(1)され、割り込みが許可されるか、またはこのフラグがソフトウェアによって解除(0)されるまで記憶(保持)されます。同様に、全割り込み許可(I)ビットが解除(0)されている間に1つまたはより多くの割り込み条件が起こると、対応する割り込み要求フラグが設定(1)されて全割り込み許可(I)ビットが設定(1)されるまで記憶され、その(I=1)後で優先順に従って実行されます。

2つ目の割り込み形式は割り込み条件が存在する限り起動し(続け)ます。これらの割り込みは必ずしも割り込み要求フラグを持っているとは限りません。割り込みが許可される前に割り込み条件が消滅すると、この割り込みは起動されません。

AVRが割り込みから抜け出すと常に主プログラムへ戻り、何れかの保留割り込みが扱われる前に1つ以上の命令を実行します。

ステータス レジスタ(SREG)は割り込みルーチンへ移行時の保存も、復帰時の回復も自動的に行われないことに注意してください。これはソフトウェアによって扱われなければなりません。

割り込みを禁止するためにCLI命令を使うと、割り込みは直ちに禁止されます。CLI命令と同時に割り込みが起こっても、CLI命令後に割り込みは実行されません。次例は時間制限EEPROM書き込み手順中に割り込みを無効とするために、これがどう使えるかを示します。

```

アセンブリ言語プログラム例

;ステータスレジスタを保存

IN

R16, SREG

;EEPROM書き込み手順中割り込み禁止

CLI

EECR, EEMPE

;EEPROM主書き込み許可

SBI

EECR, EEPE

;EEPROM書き込み開始

SBI

OUT

SREG, R16

;ステータスレジ、スタを復帰

C言語プログラム例

/* ステータス レジスタ保存変数定義 */

char cSREG;

/* ステータス レジ スタを保存 */

cSREG = SREG;

_CLI();

/* EEPROM書き込み手順中割り込み禁止 */

EECR \mid = (1 << EEMPE);

/* EEPROM主書き込み許可*/

/* EEPROM書き込み開始 */

EECR = (1 << EEPE);

/* ステータス レジ スタを復帰 */

SREG = cSREG:

```

割り込みを許可するためにSEI命令を使うと、次例で示されるようにどの保留割り込みにも先立ってSEI命令の次の命令が実行されます。

| アセンフ・リ言語フ゜ロク・ラム例     |                                        |

|----------------------|----------------------------------------|

| SEI<br>SLEEP         | ;全割り込み許可;休止形態移行(割り込み待ち)                |

| C言語プログラム例            |                                        |

| _SEI();<br>_SLEEP(); | /* 全割り込み許可 */<br>/* 休止形態移行 (割り込み待ち) */ |

注: SLEEP命令までは割り込み禁止、保留割り込み実行前に休止形態へ移行します。

#### 5.8.2. 割り込み応答時間

許可した全てのAVR割り込みに対する割り込み実行応答は最小4クロック周期です。4クロック周期後、実際の割り込み処理ルーチンに対するプログラム ヘブタ アドレスが実行されます。この4クロック周期時間中にプログラム カウンタ(PC)がスタック上に保存(プッシュ)されます。このヘブタは標準的に割り込み処理ルーチンへの無条件分岐で、この分岐は2クロック周期(<mark>訳注</mark>:原文は3(JMP命令=3を想定、実際はRJMP命令=2))要します。複数周期命令実行中に割り込みが起こると、その割り込みが扱われる前に、この命令が完了されます。MCUが休止形態の時に割り込みが起こると、割り込み実行応答時間は4クロック周期増やされます。この増加は選んだ休止形態からの起動時間に加えてです。

割り込み処理ルーチンからの復帰は4クロック周期要します。これらの4クロック周期中、プログラム カウンタ(PC:2バイト)がスタックから取り戻され(ポップ)、スタック ポインタは増加され(+2)、ステータス レジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されます。

#### 6. メモリ

この項はAT90PWM2/2B/3/3Bの各種メモリを記述します。 AVR構造にはプログラム メモリ空間とデータ メモリ空間の2つの主なメモリ空間があ ります。加えてAT90PWM2/2B/3/3Bはデータ保存用EEPROMメモリが特徴です。3つのメモリ空間全ては一般的な直線的アドレスです。

#### 6.1. 実装書き換え可能なプログラム用フラッシュ メモリ

AT90PWM2/2B/3/3Bはプログラム保存用に実装書き換え可能な8Kバイトのフラッシュ メモリをチップ 上に含みます。全てのAVR命令が16または32ビット幅のため、このフラッシュ メモリは4K×16ビット として構成されます。ソフトウェア保護のため、フラッシュプログラムメモリ空間はブートプログラム領域と 応用プログラム領域の2つに分けられます。

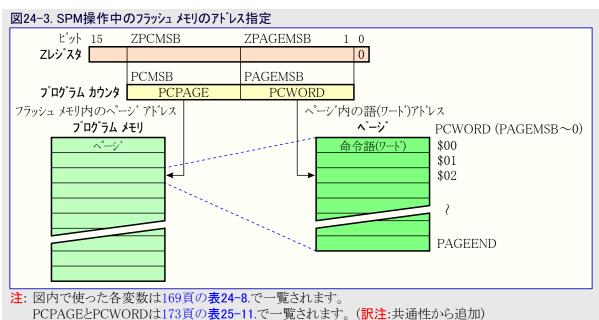

フラッシュ メモリは最低10,000回の消去/書き込み数の耐久性があります。AT90PWM2/2B/3/ 3Bのプログラム カウンタ(PC)は12ビット幅、故に4Kプログラム メモリ位置のアトンス指定です。 ブート プロ グラム領域の操作とソフトウュア保護用関連ブート施錠ビットは161頁の「**ブート ローダ支援 - 書き込み** 中読み出し可能な自己プログラミング」の詳細で記述されます。170頁の「メモリ プログラミング」はSPI (直列)または並列プログラミング動作でのフラッシュ メモリ プログラミングの詳細な記述を含みます。

定数表は全てのプログラム メモリ アトレス空間に配置できます。(LPM命令記述参照)

命令の取得と実行のタイミング図は10頁の「命令実行タイミング」で示されます。

# 図6-1. プログラム メモリ配置図 \$0000 応用プログラム用 フラッシュ メモリ $(3K\sim3.875K)\times16$ ブートプログラム用 フラッシュ メモリ $(128 \sim 1 \text{K}) \times 16$ \$0FFF

#### 6.2. データ用SRAM メモリ

図6-2.はAT90PWM2/2B/3/3BのSRAMメモリ構成方法を示します。

AT90PWM2/2B/3/3BはINやOUT命令で予約した64位置で支援されるより多くの周 辺機能部を持つ複合マイクロコントローラです。SRAM(データ空間)内\$60~\$FFの拡張I/O 空間に対してLD/LDS/LDDとST/STS/STD命令だけが使えます。

下位768データメモリ位置はレシ、スタファイル、I/Oメモリ、拡張I/Oメモリ、データ用内蔵SRAMに 充てます。先頭の32位置はレシ、スタファイル、次の64位置は標準I/Oメモリ、その次の160 位置は拡張I/Oメモリ、そして次の512位置はデータ用内蔵SRAMに充てます。

直接、間接、変位付き間接、事前減少付き間接、事後増加付き間接の5つの異なるア ト゛レス指定種別でデータ メモリ(空間)を網羅します。 レシ゛スタ ファイル内のレシ゛スタR26~R31は 間接アドレス指定ポインタ用レジスタが特徴です。

直接アドレス指定はデータ空間全体に届きます。

変位付き間接動作はYまたはZレジスタで与えられる基準アドレスからの63アドレス位置に 届きます。

図6-2. データ メモリ配置図 アドレス R0 \$0000 レシブスタ ファイル  $(32 \times 8)$ \$001F R31 \$0020 \$00 I/Oレシ スタ  $(64 \times 8)$ \$3F \$005F \$0060 \$0060 拡張[/()レジブスタ  $(160 \times 8)$ \$00FF \$00FF \$0100 \$0100 内蔵SRAM  $(512 \times 8)$ \$02FF \$02FF

注: 赤字はI/Oアドレス

自動の事前減少付きと事後増加付きのレジスタ間接アドレス指定動作を使う時に(使われる)X,Y,Zアドレス レジスタは減少(ー1)または増加 (+1)されます。

AT90PWM2/2B/3/3Bの32個の汎用レジスタ、64個のI/Oレジスタ、160個の拡張I/Oレジスタ、512バイトのデータ用内蔵SRAMはこれら全て のアト・レス指定種別を通して全部アクセスできます。レシ、スタファイルは9頁の「汎用レジ、スタファイル」で記述されます。

#### 6.2.1. データ用SRAMメモリ アクセス タイミング

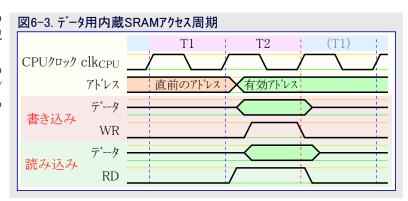

この項は内部メモリ アクセスに対する一般的なアクセス タイミングの 概念を記述します。データ用内蔵SRAMアクセスは図6-3.で記 載されるように2 clkcpu周期で実行されます。

(訳注) 内蔵SRAMのアクセスを含む代表的な命令はT1,T2の 2周期で実行され、T1で対象アドレスを取得/(算出)/ 確定し、T2で実際のアクセスが行われます。後続する (T1)は次の命令のT1です。

#### 6.3. データ用EEPROMメモリ

AT90PWM2/2B/3/3Bは512バイトのデータEEPROMを含みます。それは単一バイトが読み書きできる分離したデータ空間として構成されます。EEPROMは最低100,000回の消去/書き込み回数の耐久性があります。CPUとEEPROM間のアクセスは以降のEEPROMアドレス レ ジスタ、EEPROMデータ レジスタ、EEPROM制御レジスタで詳細に記述されます。

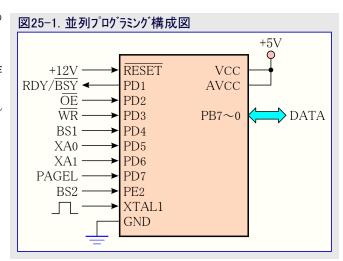

SPI(直列)と並列でのEEPROMプログラミングの詳細については181頁の「**直列プログラミング**」と173頁の「**並列プログラミング**」をご覧ください。

#### 6.3.1. EEPROMアクセス

EEPROMアクセスレジスタはI/O空間でアクセス可能です。

EEPROMの書き込み(<mark>訳注</mark>:原文はアクセス)時間は14頁の表6-1.で与えられます。(書き込みは)自己タイシンが機能ですが、使用者ソフトウェアは次パイトが書ける時を検知してください。使用者コートがEEPROMに書く命令を含む場合、いくつかの予防処置が取られなければなりません。厳重に濾波した電源では電源投入/切断でVCCが緩やかに上昇または下降しそうです。これはデバイスが何周期かの時間、使われるクロック周波数に於いて最小として示されるより低い電圧で走行する原因になります。これらの状態で問題を避ける方法の詳細については15頁の「EEPROMデータ化けの防止」をご覧ください。

予期せぬEEPROM書き込みを防止するため、特別な書き込み手順に従わなければなりません。この詳細については「EEPROM制御 レジスタ」の記述を参照してください。

EEPROMが読まれると、CPUは次の命令が実行される前に4クロック周期停止されます。EEPROMが書かれると、CPUは次の命令が実行される前に2クロック周期停止されます。

#### 6.3.2. EEARH.EEARL (EEAR) - EEPROMプトレス レジスタ (EEPROM Address Register)

| *           | ,     | •     |       |       |       |       | ,     |       |       |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| ピット         | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     |       |

| \$22 (\$42) | _     | -     | -     | -     | -     | -     | -     | EEAR8 | EEARH |

| Read/Write  | R     | R     | R     | R     | R     | R     | R     | R/W   |       |

| 初期値         | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 不定    |       |

| ピット         | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |       |

| \$21 (\$41) | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEARL |

| Read/Write  | R/W   |       |

| 初期値         | 不定    |       |

|             |       |       |       |       |       |       |       |       |       |

#### • ビット15~9 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

#### • ビット8~0 - EEAR8~0: EEPROMアトレス (EEPROM Address)

EEPROMアドレス レジスタ(EEARHとEEARL)は512バイトEEPROM空間のEEPROMアドレスを指定します。EEPROMデータ バイトは0~511間で直線的に配されます。EEARの初期値は不定です。EEPROMがアクセスされるであろう前に適切な値が書かれねばなりません。

#### 6.3.3. EEDR - EEPROMデータレジスタ (EEPROM Data Register)

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     | _    |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|------|

| \$20 (\$40) | (MSB) |     |     |     |     |     |     | (LSB) | EEDR |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |      |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |      |

#### • ビット7~0 - EEDR7~0: EEPROMデータ (EEPROM Data)

EEPROM書き込み操作に対してEEDRはEEPROMアドレスレジスタ(EEAR)で与えたアドレスのEEPROMへ書かれるべきデータを含みます。 EEPROM読み込み操作に対してEEDRはEEARで与えたアドレスのEEPROMから読み出したデータを含みます。

#### 6.3.4. EECR - EEPROM制御レジスタ (EEPROM Control Register)

| ピット         | 7 | 6 | 5     | 4     | 3     | 2     | 1    | 0    | _    |

|-------------|---|---|-------|-------|-------|-------|------|------|------|

| \$1F (\$3F) | - | - | EEPM1 | EEPM0 | EERIE | EEMPE | EEPE | EERE | EECR |

| Read/Write  | R | R | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  |      |

| 初期値         | 0 | 0 | 不定    | 不定    | 0     | 0     | 不定   | 0    |      |

#### • ビット7~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

#### • ビット5,4 - EEPM1,0: EEPROMプログラミング種別 (EEPROM Programing Mode Bits)

EEPROMプログラミング種別ヒット設定はEEPROMプログラミング・

がラミング・許可(EEPE)書き込み時にどのプログラミング

動作が起動されるかを定義します。1つの非分離

操作(旧値消去と新値書き込み)、または2つの異なる操作として消去と書き込み操作を分離してデータをプログラムする(書く)ことが可能です。各動作に対するプログラミング・時間は表6-1.で示されます。EEPEが設定(1)されている間はEEPMnへのどの書き込

| 表6-1. E | 表6-1. EEPROM7 ロクラミンク 種別 |           |                     |  |  |  |  |  |  |  |

|---------|-------------------------|-----------|---------------------|--|--|--|--|--|--|--|

| EEPM1   | EEPM0                   | プログラミング時間 | 動作                  |  |  |  |  |  |  |  |

| 0       | 0                       | 3.4ms     | 1操作での消去と書き込み(非分離操作) |  |  |  |  |  |  |  |

| 0       | 1                       | 1.8ms     | 消去のみ                |  |  |  |  |  |  |  |

| 1       | 0                       | 1.8ms     | 書き込みのみ              |  |  |  |  |  |  |  |

| 1       | 1                       | -         | 将来使用に予約             |  |  |  |  |  |  |  |

みも無視されます。リセット中、EEPMnビットはEEPROMがプログラミング作業中を除いて'00'にリセットされます。

#### ● ビット3 - EERIE: EEPROM操作可割り込み許可(EEPROM Ready Interrupt Enable)

EERIEの1書き込みはステータス レジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されているなら、EEPROM操作可割り込みを許可します。EERIEの0書き込みは、この割り込みを禁止します。EEPROM操作可割り込みは不揮発性メモリ(フラッシュ メモリとEEPROM)がプログラミングの準備可ならば継続する割り込みを発生します。

#### • ヒット2 - EEMPE: EEPROM主プログラム許可 (EEPROM Master Program Enable)

EEMPEL'ットはEEPROMプログラム許可(EEPE)L'ットの1書き込みが有効か無効かどちらかを決めます。EEMPEが設定(1)されると、4クロック周期内のEEPE設定(1)は選んだアトレスのEEPROMをプログラムします。EEMPEが0なら、EEPE設定(1)は無効です。EEMPEがソフトウェアによって設定(1)されてしまうと、4クロック周期後にハートウェアがこのビットを0に解除します。EEPROM書き込み手順については次のEEPE記述をご覧ください。

#### • ビット1 - EEPE : EEPROMプログラム許可 (EEPROM Program Enable)

EEPROMプログラム(書き込み)許可信号(EEPE)はEEPROMへの書き込みストローブです。アトレスとデータが正しく事前設定されると、EEPROMへその値を書くためにEEPEビットは1を書かれなければなりません。論理1がEEPEへ書かれる前にEEPROM主プログラム許可(EEMPE)ビットは1を書かれなければならず、さもなければEEPROM書き込みは行われません。EEPROMを書くとき、次の手順に従うべきです(手順3.と4.の順番は重要ではありません)。

- 1. EEPROMプログラム許可(EEPE)ビットがOになるまで待ちます。

- 2. SPM制御/状態レジスタ(SPMCSR)のSPM操作許可(SPMEN)ビットがOになるまで待ちます。

- 3. 今回のEEPROMアドレスをEEPROMアドレスレジスタ(EEAR)に書きます。(任意、省略可)

- 4. 今回のEEPROMデータをEEPROMデータ レジスタ(EEDR)に書きます。(任意、省略可)

- 5. EEPROM制御レジスタ(EECR)のEEPROM主プログラム許可(EEMPE)ビットに1を、EEPROMプログラム許可(EEPE)ビットに0を同時に書きます。

- 6. EEMPEL'ット設定後4クロック周期内にEEPROMプログラム許可(EEPE)L'ットへ論理1を書きます。

CPUがフラッシュ メモリ書き込み中、EEPROMはプログラム(書き込みが)できません。ソフトウェアは新規EEPROM書き込みを始める前にフラッシュ メモリのプログラミングが完了されていることを検査しなければなりません。2.はソフトウェアがフラッシュ メモリをプログラム(書き込みを)することをCPUに許すフート ローダを含む場合だけ関係します。フラッシュ メモリが決してCPUによって更新されないなら、2.は省略できます。フート プログラミングについての詳細に関しては161頁の「ブート ローダ支援 - 書き込み中読み出し可能な自己プログラミング」をご覧ください。

警告: 手順5.と6.間の割り込みはEEPROM主プログラム許可が時間超過するため、書き込み周期失敗になります。EEPROMをアクセスする割り込みルーチンが他のEEPROMアクセスを中断し、EEARかEEDRが変更されると、中断したEEPROMアクセスを失敗させます。これらの問題を避けるため、全ての手順中、ステータスレジスタ(SREG)の全割り込み許可(I)ビットは解除(0)されていることが推奨されます。

書き込み(プログラミング)アクセス時間が経過されると、EEPROMプログラム許可(EEPE)ビットはハードウェアによって解除(①)されます。使用者ソフトウェアは次ハイトを書く前にこのビットをホーリングし、Oを待つことができます。EEPEが設定(1)されてしまうと、次の命令が実行される前にCPUは2周期停止されます。

#### • ビット0 - EERE: EEPROM読み込み許可 (EEPROM Read Enable)

EEPROM読み込み許可信号(EERE)はEEPROMへの読み込みストローブです。EEARに正しいアトレスが設定されると、EEPROM読み出しを起動するためにEEREt ットは1を書かれなければなりません。EEPROM読み出しアクセスは(その)1命令で行われ、要求したデータは直ちに利用できます。EEPROMが読まれるとき、次の命令が実行される前にCPUは4周期停止されます。

使用者は読み込み操作を始める前にEEPEビットをポーリングすべきです。書き込み(プログラム)操作実行中の場合、EEPROMアドレス レジスタ(EEAR)の変更もEEPROM読み込みもできません。

EEPROMアクセスの時間に校正済み内蔵RC発振器が使われます。表6-2.はCPUからのEEPROMアクセスに対する代表的な書き込み時間を示します。

| 表6-2. EEPROM書き込み時間                           |                    |    |  |  |  |  |  |

|----------------------------------------------|--------------------|----|--|--|--|--|--|

| 項目                                           | 校正付き内蔵RC<br>発振器周期数 | 代表 |  |  |  |  |  |

| EEPROM書き込み(CPU)         26,368         3.3ms |                    |    |  |  |  |  |  |

次のコート・例はアセンブリ言語とC言語でのEEPROM消去、書き込み、または非分離書き込み関数を示します。本例は(例えば全割り込み禁止によって)割り込みが制御され、これらの関数実行中に割り込みが起きない前提です。本例はソフトウェア内にフラッシュ ブート ロータ・が無い前提でもあります。そのようなコートが存在する場合、EEPROM書き込み関数は何れかが実行するSPM命令の完了も待たねばなりません。(訳注:共通性から次例は補足修正しています。)

```

アセンブリ言語プログラム例

EEPROM_WR:

;EEPROMプログラミング完了ならばスキップ

SBIC

EECR, EEPE

EEPROM WR

;以前のEEPROMプログラミング完了まで待機

RJMP

LDI

R19, (0<<EEPM1) | (0<<EEPM0)

;プログラミング種別値取得(本例は非分離)

;対応プログラミング種別設定

OUT

EECR, R19

OUT

EEARH, R18

;EEPROMアドレス上位バイ設定

OUT

EEARL, R17

;EEPROMアドレス下位バイト設定

OUT

EEDR, R16

;EEPROM書き込み値を設定

;EEPROM主プログラム許可ビット設定

SBI

EECR, EEMPE

;EEPROMプログラミング開始(プログラム許可ビット設定)

SBI

EECR, EEPE

RET

;呼び出し元へ復帰

C言語プログラム例

void EEPROM_write(unsigned int uiAddress, unsigned char ucData)

while (EECR & (1<<EPE));

/* 以前のEEPROMプログラミング完了まで待機 */

EECR = (0 << EEPM1) \mid (0 << EEPM0);

/* 対応プログラミング種別設定 */

/* EEPROMアドレス設定 */

EEAR = uiAddress;

EEDR = ucData;

/* EEPROM書き込み値を設定 */

EECR = (1 < EEMPE);

/* EEPROM主プログラム許可*/

EECR = (1 < EEPE);

/* EEPROMプログラミング開始*/

}

```

次のコート・例はアセンブリ言語とC言語でのEEPROM読み込み関数を示します。本例は割り込みが制御され、これらの関数実行中に割り込みが起きない前提です。

```

アセンブリ言語プログラム例

SBIC

;EEPROMプログラミング完了ならばスキップ

EEPROM RD:

EECR, EEPE

;以前のEEPROMプログラミング完了まで待機

RJMP

EEPROM_RD

OUT

EEARH, R18

;EEPROMアドレス上位バイト設定

OUT

EEARL, R17

;EEPROMアドレス下位バイト設定

;EEPROM読み出し開始(読み込み許可ビット設定)

SBI

EECR, EERE

IN

R16, EEDR

;EEPROM読み出し値を取得

RET

;呼び出し元へ復帰

C言語プログラム例

unsigned char EEPROM read(unsigned int uiAddress)

/* 以前のEEPROMプログラミング完了まで待機 */

while (EECR & (1<<EPE));

EEAR = uiAddress;

/* EEPROMアドレス設定*/

EECR = (1 \le EERE);

/* EEPROM読み出し開始 */

/* EEPROM読み出し値を取得,復帰 */

return EEDR;

}

```

#### 6.3.5. EEPROMデータ化けの防止

低VCCの期間中、正しく動作するための供給電圧がCPUとEEPROMに対して低すぎるためにEEPROMデータが化け得ます。これらの問題はEEPROMを使う基板段階の装置と同じで、同じ設計上の解決策が適用されるべきです。

EEPROMデータ化けは電圧が低すぎる時の2つの状態によって起こされ得ます。1つ目として、EEPROMへの通常の書き込み手順は正しく動作するための最低電圧が必要です。2つ目として、供給電圧が低すぎると、CPU自身が命令を間違って実行し得ます。

EEPROMデータ化けは次の推奨設計によって容易に避けられます。

不充分な供給電源電圧の期間中、AVRのRESETを活性(Low)に保ってください。これは内蔵低電圧検出器(BOD)を許可することによって行えます。内蔵BODの検出電圧が必要とした検出電圧と一致しない場合、外部低VCCリセット保護回路が使えます。書き込み動作実行中にリセットが起こると、この書き込み操作は供給電源電圧が充分ならば(継続)完了されます。

#### 6.4. I/O メモリ (レシ スタ)

AT90PWM2/2B/3/3BのI/O空間定義は205頁の「レジスタ要約」で示されます。

AT90PWM2/2B/3/3Bの全てのI/Oと周辺機能はI/O空間に配置されます。全てのI/O位置はI/O空間と32個の汎用作業レシ、スタ間のデータ転送を行うLD/LDS/LDD命令とST/STS/STD命令によってアクセスされます。アドレス範囲\$00~\$1F内のI/Oレシ、スタはSBI命令とCBI命令の使用で直接的にビットアクセス可能です。これらのレシ、スタではSBISとSBIC命令の使用によって単一ビット値が検査できます。より多くの詳細については「命令要約」章を参照してください。I/O指定命令INとOUTを使う時にI/Oアドレス\$00~\$3Fが使われなければなりません。LD命令とST命令を使い、データ空間としてI/Oレシ、スタをアクセスする時はこれらのアドレスに\$20が加算されなければなりません。AT90PWM2/2B/3/3BはINやOUT命令で予約した64位置で支援されるより多くの周辺機能部を持つ複合マイクロコントローラです。SRAM(データ空間)内\$60~\$FFの拡張I/O領域に対してはLD/LDS/LDDとST/STS/STD命令だけが使えます。

将来のデバイスとの共通性を保つため、アクセスされる場合、予約ビットはのが書かれるべきです。予約済みI/Oメモリ アドレスは決して書かれるべきではありません。

状態フラグのいくつかはそれらへ論理1を書くことによって解除(0)されます。CBIとSBI命令は他の多くのAVRの様ではなく、指定ビットだけを操作し、従って状態フラグのようなものを含むレジスタに使えることに注意してください。CBIとSBI命令は(I/Oアドレス)\$00~\$1Fのレジスタでのみ動作します。

I/Oと周辺制御レジスタは以降の項で説明されます。

#### 6.5. 汎用I/Oレジスタ

AT90PWM2/2B/3/3Bは4つの汎用I/Oレジスタを含みます。これらのレジスタはどの情報の格納にも使え、特に全体変数や状態フラグの格納に有用です。(I/O)アドレス範囲\$00~\$1Fの汎用I/OレジスタはSBI,CBI,SBIS,SBIC命令の使用で直接ビット アクセスが可能です。

#### 6.5.1. GPIOR3 - 汎用I/Oレジスタ3 (General Purpose I/O Register 3)

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |        |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$1B (\$3B) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR3 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

#### 6.5.2. GPIOR2 - 汎用I/Oレジスタ2 (General Purpose I/O Register 2)

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     | _      |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$1A (\$3A) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR2 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

#### 6.5.3. GPIOR1 - 汎用I/Oレジスタ1 (General Purpose I/O Register 1)

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     | _      |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$19 (\$39) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR1 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

#### 6.5.4. GPIORO - 汎用I/OレジスタO (General Purpose I/O Register 0)

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     | _      |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$1E (\$3E) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR0 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

#### 7. システム クロック

#### 7.1. クロック系統とその配給

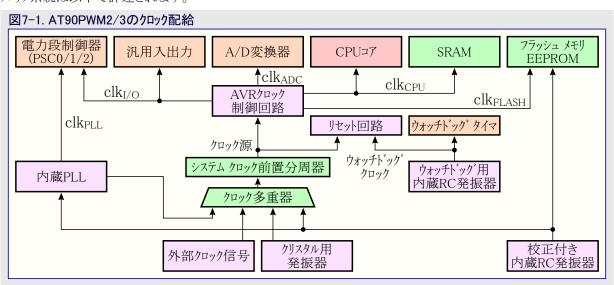

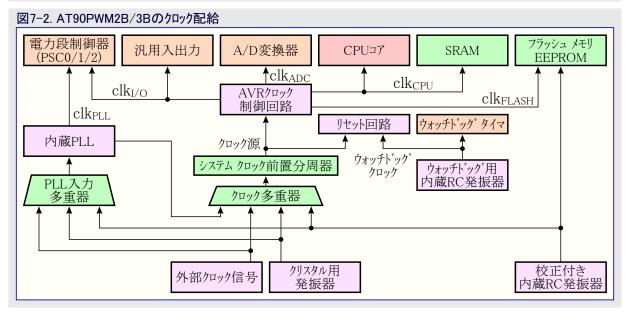

図7-1.,図7-2.はAVR内の主要なクロック系統とその配給を示します。全てのクロックが与えられた時間有効である必要はありません。消費電力低減のため、24頁の「電力管理と休止形態」で記述される各種休止形態の使用によって、使われていない部分のクロックが停止できます。クロック系統は以下で詳述されます。

#### 7.1.1. CPU クロック – clk<sub>CPU</sub>

CPUクロックはAVRコアの動作と関係する系統部分に配給されます。このような部分の例は汎用レジスタ ファイル、ステータス レジスタ、スタック ポイ ンタを保持するデータ メモリです。CPUクロックの停止はコアが一般的な操作や計算を実行することを禁止します。

#### 7.1.2. I/O クロック - clk<sub>I/O</sub>

I/Oクロックはタイマ/カウンタ、SPI、USARTのようなI/O部の大部分で使われます。I/Oクロックは外部割り込み部でも使われますが、いくつかの外部割り込みは例えI/Oクロックが停止されても検出されることを、このような割り込みに許す非同期論理回路によって検出されることに注意してください。

#### **7.1.3**. フラッシュ クロック - clk<sub>FLASH</sub>

フラッシュ クロックはフラッシュ メモリ インターフェースの動作を制御します。このフラッシュ クロックは常にCPUクロックと同時に活動します。

#### **7.1.4. PLLクロック** – clk<sub>PLL</sub>

PLLクロックは64/32MHzから直接的にクロック駆動されるのを電力段制御器(PSC)に許します。16MHzクロックもCPU用に分周されます。

#### 7.1.5. A/D変換クロック - clk<sub>ADC</sub>

A/D変換器には専用のクロック範囲が提供されます。これはデジタル回路によって生成される雑音を低減するためにCPUとI/Oクロックの停止を許します。これはより正確なA/D変換結果を与えます。

#### 7.2. クロック元

このデバイスには表7-1.または表7-2.で示されるようにフラッシュ ヒュース ビットによって選択可能な後続のクロック元選択があります。選んだク ロック元からのクロックはAVRクロック発生器への入力で、適切な単位部へ配給されます。

| クロック種別           | CKSEL3~0  |

|------------------|-----------|

| 外部クリスタル/セラミック発振子 | 1111~1000 |

| 4分周PLL出力 (16MHz) | 0011      |

| 校正付き内蔵RC発振器      | 0010      |

| 外部クロック信号         | 0000      |

| (予約)             | 01xx,0001 |

注: 1=非プログラム、0=プログラム

各クロック選択に対する様々な選択は次項で得られま す。CPUがパワーダウンから起動するとき、選んだクロック 元は命令実行開始前に安定な発振器動作を保証 注: 1=非プログラム、0=プログラム する起動時間に使われます。CPUがリセットから始まる

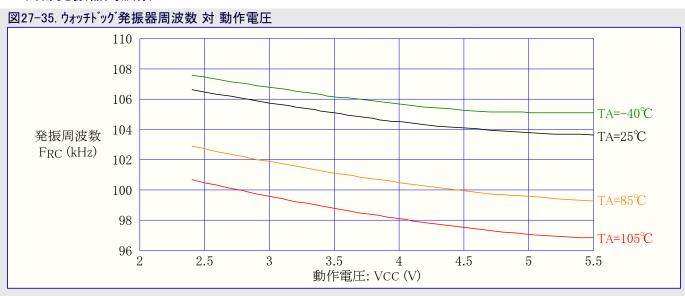

とき、これらは通常動作開始前に安定電圧へ達するのを電源に許す付加遅延 です。ウォッチドック、発振器はこの起動時間の実時間部のタイミングに使われます。 各計時完了に使われるウォッチドッゲ(WDT)発振器の周期数は表7-3.で示されま す。200頁の「ウォッチト、ック・発振器周波数対電源電圧」で示されるようにウォッチ トックで発振器の周波数は電圧に依存します。

表7-1. AT90PWM2/3のクロック種別選択 表7-2. AT90PWM2B/3Bのクロック種別選択

| システム クロック        | PLL入力            | CKSEL3~0  |

|------------------|------------------|-----------|

| 外部クリスタル/セラミック発振子 | 校正付き内蔵RC発振器      | 1111~1000 |

| (予約)             | (予約)             | 011x      |

| 4分周PLL出力         | 外部クリスタル/セラミック発振子 | 0101      |

| 外部クリスタル/セラミック発振子 | 外部クリスタル/セラミック発振子 | 0100      |

| 4分周PLL出力 (16MHz) | 校正付き内蔵RC発振器      | 0011      |

| 校正付き内蔵RC発振器      | 校正付き内蔵RC発振器      | 0010      |

| 4分周PLL出力         | 外部クロック信号         | 0001      |

| 外部クロック信号         | 校正付き内蔵RC発振器      | 0000      |

# 表7-3. WDT発振器の代表計時完了値、周期数

| VCC=3.0V | VCC=5.0V | 周期数       |

|----------|----------|-----------|

| 4.3ms    | 4.1ms    | 512       |

| 69ms     | 65ms     | 8K (8192) |

#### 7.3. 既定のクロック元

本デバイスはCKSEL=0010, SUT=10, CKDIV8=プログラム(0)で出荷されます。既定のクロック元設定は最長起動時間の(8.0MHzの)校正 付き内蔵RC発振器で、8分周の初期システム クロックです。この既定設定は全ての使用者が実装または並列書き込み器を使い、それら を希望したクロック元設定にできることを保証します。

#### 7.4. クリスタル用低電力発振器

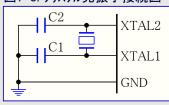

XTAL1とXTAL2は**図7-3**.で示されるように、チップ上の発振器としての使用に設定できる反転増幅器の各々、入力と出力です。 クリスタル発振子またはセラミック振動子のどちらでも使えます。

この発振器はXTAL2出力上の電圧振幅を減少した低電力発振器です。これは最低消費電力を与えますが、他のクロック入力を駆動する能力はありません。

C1とC2はクリスタル発振子とセラミック振動子の両方について常に等しくすべきです。このコンデンサの最適値は使うクリスタル発振子やセラミック振動子、浮遊容量の量、その環境の電磁雑音に依存します。クリスタル発振子使用に対するコンデンサ選択について初期の指針のいくつかは表7-4.で与えられます。セラミック振動子については製造業者によって与えられたコンデンサ値が使われるべきです。

低電力発振器は示された周波数範囲で各々最適化された3つの異なる種別で動作できます。この動作種別は表7-4.で示されるようにCKSEL3~1ヒュース によって選ばれます。

CKSEL0ヒュースiはSUT1,0ヒュースiと共に表7-5.で示されるように起動時間を選びます。

#### 図7-3. クリスタル発振子接続図

#### 表7-4. クリスタル用低電力発振器動作種別

|          | 710120000000000000000000000000000000000 | HH -93 11 12273 |

|----------|-----------------------------------------|-----------------|

| CKSEL3~1 | 周波数範囲                                   | 推奨C1,2容量        |

| 100 (注1) | 0.4~0.9MHz                              | _               |

| 101      | 0.9~3.0MHz                              | 12∼22pF         |

| 110      | 3.0~8.0MHz                              | 12∼22pF         |

| 111      | 8.0~16MHz                               | 12~22pF         |

注: 周波数範囲は暫定値で実際の値はTBDで す。

**注1**: 本選択はクリスタル発振子ではなく、セラミック振動子でのみ使われるべきです。

#### 表7-5. クリスタル発振子/セラミック振動子用低電力発振器起動遅延時間選択表

| CKSEL0 | SUT1,0 | パワーダウンからの<br>起動遅延時間  | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法                       |

|--------|--------|----------------------|------------------------------|-----------------------------|

|        | 0 0    | 258×CK ( <b>注1</b> ) | $14 \times \text{CK+4.1ms}$  | 外部セラミック振動子、高速上昇電源           |

| 0      | 0 1    | 258×CK ( <b>注1</b> ) | $14 \times \text{CK+65ms}$   | 外部セラミック振動子、低速上昇電源           |

| U      | 1 0    | 1K×CK ( <b>注2</b> )  | 14×CK                        | 外部セラミック振動子、低電圧検出(BOD)リセット許可 |

|        | 1 1    | 1K×CK ( <b>注2</b> )  | 14×CK+4.1ms                  | 外部セラミック振動子、高速上昇電源           |

|        | 0 0    | 1K×CK ( <b>注2</b> )  | 14×CK+65ms                   | 外部セラミック振動子、低速上昇電源           |

| 1      | 0 1    | 16K×CK               | 14×CK                        | 外部クリスタル発振子、低電圧検出(BOD)リセット許可 |

| 1      | 1 0    | 16K×CK               | $14 \times \text{CK+4.1ms}$  | 外部クリスタル発振子、高速上昇電源           |

|        | 1 1    | 16K×CK               | 14×CK+65ms                   | 外部クリスタル発振子、低速上昇電源           |

**注1**: これらの選択はデバイスの最高周波数付近での動作でないとき、応用にとって起動での周波数安定性が重要でない場合だけ使われるべきです。これらの選択はクリスタル発振子用ではありません。

**注2**: これらの選択はセラミック振動子での使用を意図され、起動での周波数安定性を保証します。デバイスの最高周波数付近での動作でないとき、応用にとって起動での周波数安定性が重要でない場合はクリスタル発振子も使えます。

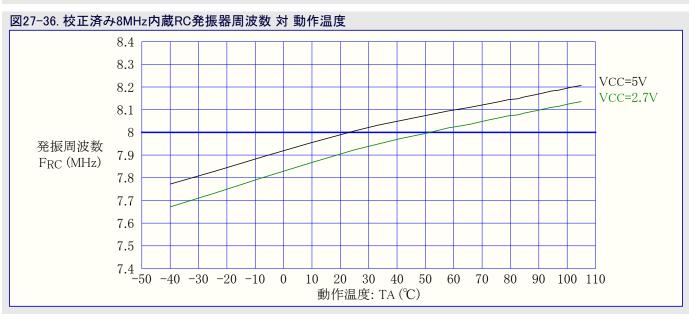

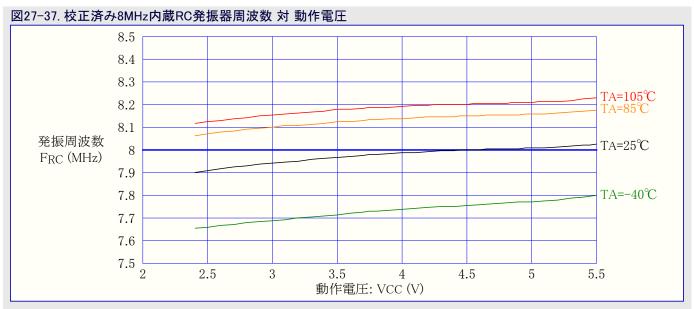

#### 7.5. 校正付き内蔵RC発振器

既定による校正された内蔵RC発振器は概ね8.0MHzのクロックを供給します。電圧と温度に依存しますが、このクロックは使用者によって 高精度な校正ができます。より多くの詳細については184頁の表26-1.と200頁の「内部発振器周波数」をご覧ください。このデバイスは CKDIV8ヒュースがプログラム(0)で出荷されます。より多くの詳細については23頁の「システム クロック前置分周器」をご覧ください。

このクロックは表アー6.で示されるようにCKSELヒューズのプログラミングによってシステム クロックとして選べます。 選んだなら、外部部品なしで動 作します。リセット中、ハート・ウェアが発振校正(OSCCAL)レシブスタに予めプログラムされた校正値バイトを設定し、これによってRC発振器を自動 的に校正します。この校正の精度は表26-1.で工場校正として示されます。

ソフトウェアからOSCCALレシ、スタを変更することによって(発振校正レシ、スタ(OSCCAL)参照)、工場校正を使うよりも高い精度を得ることがで きます。この校正の精度は表26-1.で使用者校正として示されます。

この発振器がチップ(システム)クロックとして使われる時にウォッチドッグ発振器は未だウォッチドッグタイマとリセット付加遅延タイマに使われます。 予 め設定された校正値のより多くの情報については172頁の「校正n'仆」項をご覧ください。

この発振器が選択されると、起動時間は**表7-7**.で示されるようにSUTヒューズによって決定されます。PE1(XTAL1/OC0B)とPE2(XTAL2 /ADC0)は標準I/Oピンまたは交換機能ピンのどちらかとして使えます(訳補:共通性から本行追加)。

表7-6. 校正付き内蔵RC発振器動作種別 注: デバイスはこの選択で出荷されます。

| CKSEL3~0 | 周波数範囲 (MHz) |

|----------|-------------|

| 0 0 1 0  | 7.3~8.1     |

注: この8MHz周波数がデバイス仕様(VCCに依存)を越える場合、内部周波数を8分 周するためにCKDIV8ヒュース、をプログラム(0)にできます。

#### 表7-7. 校正付き内蔵RC発振器用起動遅延時間選択表

| SUT1,0  | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法            |

|---------|---------------------|------------------------------|------------------|

| 0 0     | 6×CK                | 14×CK ( <b>注2</b> )          | 低電圧検出リセット(BOD)許可 |

| 0 1     | 6×CK                | 14×CK+4.1ms                  | 高速上昇電源           |

| 10 (注1) | 6×CK                | 14×CK+65ms                   | 低速上昇電源           |

| 1 1     |                     |                              | (予約)             |

注1: デバイスはこの選択で出荷されます。

注2: RSTDISBLヒューズがプログラム(0)されると、プログラミング動作への移行可を保証するため、付加遅延時間は14×CK+4.1msに増 やされます。

#### 7.5.1. OSCCAL - 発振校正レジスタ (Oscillator Calibration Register)

| Read/Write R/W R/W R/W R/W R/W R/W R/W | ピット        | 7    | 6    | 5    | 4      | 3     | 2    | 1    | 0    |        |

|----------------------------------------|------------|------|------|------|--------|-------|------|------|------|--------|

|                                        | (\$66)     | CAL7 | CAL6 | CAL5 | CAL4   | CAL3  | CAL2 | CAL1 | CAL0 | OSCCAL |

| 知期値 デッジス国右の松正値                         | Read/Write | R/W  | R/W  | R/W  | R/W    | R/W   | R/W  | R/W  | R/W  |        |

| 777700月927亿工匠                          | 初期値        |      |      |      | デバイス固ィ | 有の校正値 |      |      |      |        |

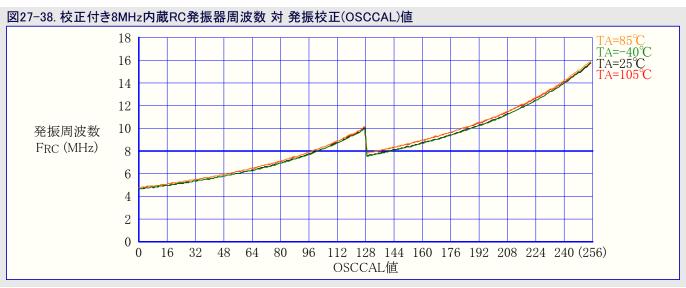

#### • ビット7~0 - CAL7~0:発振校正値 (Oscillator Calibration Value) (訳注: 内容を新版対応に変更)

発振校正レシ、スタは発振器周波数の偏差処理を省くための内蔵発振器の調整に使われます。チップのリセット中、184頁の表26-1.で指 定されるように工場で校正された周波数を与える、予めプログラムされた値が本レジスタへ自動的に書かれます。応用ソフトウェアは発振器 周波数を変更するために、このレジスタに書くことができます。この発振器は表26-5.で指定される周波数に校正できます。この範囲外 への校正は推奨されません。

この発振器はフラッシューメモリとEEPROMの書き込みアクセス時間に使われ、これらの書き込み時間はそれに応じて影響されることに注意し てください。フラッシュ メモリまたはEEPROMが書かれる場合、8.8MHzより高く校正してはいけません。そうでなければ、フラッシュ メモリまた はEEPROM書き込みは失敗するかもしれません。

CAL7ビットは発振器に関する操作範囲を決めます。このビットの(0)設定は低周波数範囲になり、(1)設定は高周波数範囲になります。 この2つの周波数範囲は重複し、別の言葉では、OSCCAL=\$7F設定はOSCCAL=\$80設定より高い周波数になります。

CAL6~0ピットは選んだ範囲内の周波数調整に使われます。\$00設定はその範囲の最低周波数になり、\$7F設定はその範囲の最高 周波数になります。

#### 7.6. PLL

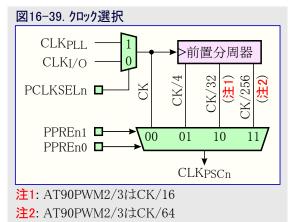

高い精度と周波数のPWM波形を生成するために、電力段制御器(PSC)は高周波数クロック入力が必要です。このクロックはPLLによって生成されます。全てのPWM精度を維持するため、PLLの周波数係数はソフトウェアによって設定されなければなりません。8MHzのシステムクロックでのPLL出力は32MHzまたは64MHzです。

#### 7.6.1. 電力段制御器(PSC)用内部PLL

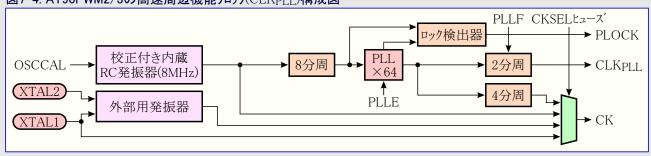

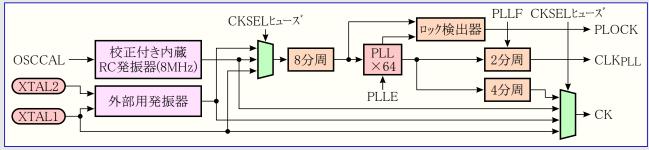

AT90PWM2/2B/3/3Bの内部PLLは公称1MHzから64倍されたクロック周波数を生成します。この1MHzのPLL入力クロック元は1MHzに分周された内蔵RC発振器の出力です。図7-4.または図7-5.をご覧ください。

PLLはこのRC発振器に固定化し、発振校正レジスタ(OSCCAL)経由のRC発振器調整は同時に高速周辺機能クロックも調整します。けれども分周したRC発振器が1MHzより高い周波数にされるのが可能でも、高速周辺機能クロックは(最悪の場合)70MHzで飽和し、最高周波数での発振に留まります。この場合のPLLがRC発振器クロックのどれにも固定化されないことに注意されるべきです。

従ってPLLを正しい動作範囲に保持するため、1MHzより高い周波数にOSCCAL補正を行わないことが推奨されます。内部PLLはPLL制御/状態レジスタ(PLLCSR)のPLL許可(PLLE)ビットが設定(1)される時だけ許可されます。PLLCSRのPLL固定化(PLOCK)ビットはPLLが固定化されている時に設定(1)されます。

内部1MHz RC発振器とPLLはパワーダウンとスタンバイの休止形態でOFFへ切り替えられます。

#### 表7-8. PLLシステム クロック用起動遅延時間選択表

| CKSEL3~0           | SUT1,0 | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=5.0V) |

|--------------------|--------|---------------------|------------------------------|

|                    | 0 0    | 1K×CK               | 14×CK                        |

| 0 1 0 1            | 0 1    | 1K×CK               | 14×CK+4ms                    |

| (外部クリスタル/セラミック発振子) | 1 0    | 16K×CK              | 14×CK+4ms                    |

|                    | 1 1    | 16K×CK              | 14×CK+64ms                   |

|                    | 0 0    | 1K×CK               | 14×CK                        |

| 0 0 1 1            | 0 1    | 1K×CK               | 14×CK+4ms                    |

| (校正付き内蔵RC発振器)      | 1 0    | 1K×CK               | 14×CK+64ms                   |

|                    | 1 1    | 16K×CK              | 14×CK                        |

|                    | 0 0    | 6×CK ( <b>注</b> )   | 14×CK                        |

| 0 0 0 1            | 0 1    | 6×CK ( <b>注</b> )   | 14×CK+4ms                    |

| (外部クロック信号)         | 1 0    | 6×CK ( <b>注</b> )   | 14×CK+64ms                   |

|                    | 11     | (予                  | 約)                           |

注: この値は正しい再起動を提供せず、このクロック機構でパワーダウン動作を使ってはいけません。

#### 図7-4. AT90PWM2/3の高速周辺機能クロック(CLKPLL)構成図

# 図7-5. AT90PWM2B/3Bの高速周辺機能クロック(CLKPLL)構成図

#### 7.6.2. PLLCSR - PLL制御/状態レジスタ (PLL Control and Status Register)

| ピット         | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0     |        |

|-------------|---|---|---|---|---|------|------|-------|--------|

| \$29 (\$49) | - | - | - | _ | _ | PLLF | PLLE | PLOCK | PLLCSR |

| Read/Write  | R | R | R | R | R | R/W  | R/W  | R     |        |

| 初期値         | 0 | 0 | 0 | 0 | 0 | 0    | 0/1  | 0     |        |

#### • ビット7~3 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

#### • ビット2 - PLLF: PLL周波数係数 (PLL Factor)

PLLFt'ットはPLLの分周係数選択に使われます。PLLFが設定(1)されると、PLL出力は64MHzです。PLLFが解除(0)されると、PLL出力は32MHzです。

#### • ビット1 - PLLE: PLL許可 (PLL Enable)

PLLEが設定(1)されると、PLLが起動され、必要とされるなら、PLL基準クロックとして内蔵RC発振器が起動されます。システム クロック元としてPLLが選ばれると、このビットに対する値は常に1です。

#### • ビット0 - PLOCK : PLL固定化検出 (PLL Lock Detector)

PLOCKビットが設定(1)されると、PLLが基準クロックに固定化され、電力段制御器(PSC)に対するCLKPLLの許可は安全です。PLLが許可された後、PLLが固定化するのに約100μsかかります。

### 7.7. 128kHz内部発振器

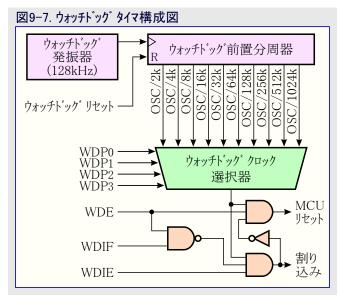

128kHz内部発振器は128kHzのクロックを供給する低電力発振器です。この周波数は3V,25℃での公称値です。このクロックはウォッチドッ グ発振器によって使われます。

#### 7.8. 外部クロック信号

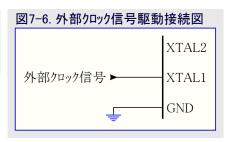

外部クロック元からデバイスを駆動するには、XTAL1が 図7-6.で示されるように駆動されるべきです。外部クロックでデバイスを走行するためには、CKSELヒュースが '0000'にプログラム(設定)されなければなりません。

| 表7-9. 外部クロック信号動作種別 |         |  |  |  |  |  |

|--------------------|---------|--|--|--|--|--|

| CKSEL3~0 周波数範囲     |         |  |  |  |  |  |

| 0 0 0 0            | 0∼16MHz |  |  |  |  |  |

このクロック元が選ばれると、起動時間は**表7-10**.で示されるようにSUTヒューズによって決定されます。

#### 表7-10. 外部クロック信号駆動用起動遅延時間選択表

| SUT1,0 | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法            |  |  |  |  |  |

|--------|---------------------|------------------------------|------------------|--|--|--|--|--|

| 0 0    | 6×CK                | 14×CK                        | 低電圧検出(BOD)リセット許可 |  |  |  |  |  |

| 0 1    | 6×CK                | 14×CK+4.1ms                  | 高速上昇電源           |  |  |  |  |  |

| 1 0    | 6×CK                | 14×CK+65ms                   | 低速上昇電源           |  |  |  |  |  |

| 1 1    | (予約)                |                              |                  |  |  |  |  |  |

外部クロックを供給するとき、MCUの安定な動作を保証するために供給したクロック周波数の急な変化を避けることが必要とされます。或るクロック周期から次への2%より大きな周波数変化は予測されない事態を引き起こします。このようなクロック周波数での変化中、MCUはリセットに保たれるのを保証することが必要とされます。

システム クロック前置分周器が安定な動作を保証しながら、内部クロック周波数の実行時変更の実現に使えることに注意してください。詳細については23頁の「システム クロック前置分周器」を参照してください。

#### 7.9. クロック出力緩衝部(外部クロック出力)

CKOUTヒューズがプログラム(0)されると、システム クロックがCLKOピンに出力されます。この動作はチップのクロックがシステム上の他の回路を駆動する時用です。このヒュースがプログラム(0)されると、I/Oピンの標準動作は無視され、このクロックはリセット中も出力されます。CLKOがクロック出力を扱うとき、校正付き内蔵RC発振器を含むどのクロック元も選べます。システム クロック前置分周器が使われると、CKOUTヒュース、がプログラム(0)された時の出力は分周したシステム クロックです。

#### 7.10. システム クロック前置分周器

AT90PWM2/2B/3/3Bはシステム クロック前置分周器を持ち、システム クロックはクロック前置分周レシ、スタ(CLKPR)の設定により分周できます。この特徴(機能)は必要とされる処理能力が低い時の消費電力削減に使えます。これは全クロック種別で使え、CPUと全同期周辺機能のクロック周波数に影響を及ぼします。clk<sub>CPU</sub>、clk<sub>FLASH</sub>、clk<sub>I/O</sub>、clk<sub>ADC</sub>は表7-11.で示された値によって分周されます。

前置分周器設定間を切り替えるとき、システム クロック前置分周器は中間(経過途中)の周波数が直前の設定に対応するクロック周波数または新規設定に対応するクロック周波数のどちらよりも高くなく、クロック系で不具合が起きないことを保証します。前置分周器として実行するリプル カウンタは分周されない クロック周波数で走行し、CPUのクロック周波数より速いかもしれません。従って例え(カウンタ値が)読めるとしても、前置分周器の状態を決めることはできず、1から他へのクロック分周値切り替えを行う正確な時間は必ずしも予測できません。CLKPS値が書かれる時から新規クロック周波数が活性(有効)になる前にT1+T2~T1+2×T2間かかります。この間で2つの有効なクロック端が生成されます。ここでのT1は直前のクロック周期、T2は新規前置分周器設定に対応する周期です。

予期せぬクロック周波数の変更を防ぐため、CLKPSビットの変更は次の特別な書き込み手順に従わなければなりません。

- 1. クロック分周値変更許可(CLKPCE)ビットに1、CLKPR内の他の全ビットに0を書きます。

- 2. (次からの)4設定以内にCLKPCEビットをOとする欲したCLKPS値を書きます。

前置分周器設定変更時、書き込み手続きが割り込まれないことを保証するため、割り込みは禁止されなければなりません。

#### 7.10.1. CLKPR - クロック前置分周レジスタ (Clock Prescale Register)

| ピット        | 7      | 6 | 5 | 4 | 3      | 2      | 1      | 0      |       |

|------------|--------|---|---|---|--------|--------|--------|--------|-------|

| (\$61)     | CLKPCE | - | - | - | CLKPS3 | CLKPS2 | CLKPS1 | CLKPS0 | CLKPR |

| Read/Write | R/W    | R | R | R | R/W    | R/W    | R/W    | R/W    |       |

| 初期値        | 0      | 0 | 0 | 0 | 内容参照   | 内容参照   | 内容参照   | 内容参照   |       |

#### • ビット7 - CLKPCE: クロック分周値変更許可 (Clock Prescaler Change Enable)

CLKPSビットの変更を許可するためにCLKPCEビットは論理1を書かれなければなりません。CLKPCEビットは同時にCLKPRの他の全 ビットが0を書かれる時だけ更新されます。CLKPCEは書き込み後4クロック設定またはCLKPSビット書き込み時、ハードウェアによって解除(0)されます。この制限時間(4クロック設定)内のCLKPCEビット再書き込みは制限時間の延長もCLKPCEビットの解除(0)も行いません。

#### • ビット3~0 - CLKPS3~0: クロック分周値選択 (Clock Prescaler Select Bits 3~0)

これらのビットは選んだクロック元と内部システム クロック間の分周値を定義します。これらのビットは応用の必要条件に合わせた各種クロック周波数を実行時に書けます。分周値が使われると、分周器はMCUへの主クロックを分周し、全ての同期周辺機能の速度が減じられます。分周値は表7-11.で与えられます。

CKDIV8ヒュース、がCLKPSビットの初期値を決めます。CKDIV8が非プログラム(1)にされると、CLKPSビットは'0000'にリセットされます。CKDI V8がプログラム(0)されると、CLKPSビットは起動時に8分周を与える'0011'にリセットされます。現在の動作条件でデバイスの最高周波数より高い周波数のクロック元を選んだ場合、この機能が使われるべきです。CKDIV8ヒュース、設定に拘らず、どの値もCLKPSビットへ書けることに注意してください。応用ソフトウェアは現在の動作条件でデバイスの最高周波数より高い周波数のクロック元を選んだ場合、充分な分周値が選ばれることを保証しなければなりません。本デバイスはCKDIV8ヒュースがプログラム(0)で出荷されます。

表7-11. クロック前置分周器選択 CLKPS3 0 0 0 CLKPS2 CLKPS<sub>1</sub>  $\cap$ 0 0 0 0 0 0 0 0 0 0 0 CLKPS0 分周値(数) (予約) 64 128 256 4 8 16 32

### 8. 電力管理と休止形態

休止形態は応用でMCU内の未使用部を一時停止することを可能にし、それによって節電します。AVRは応用で必要な消費電力に 仕立てることを使用者に許す様々な休止形態を提供します。

4つの休止形態の何れかへ移行するには休止形態制御レシ、スタ(SMCR)の休止許可(SE)ヒットが論理1を書かれ、SLEEP命令が実行されなければなりません。SMCRの休止種別選択(SM2~0)ヒットはSLEEP命令によって活性(有効)にされる休止形態(アイ・ル、A/D変換雑音低減、パワータ・ウン、スタンハイ)のどれかを選びます。一覧については表8-1.をご覧ください。MCUが休止形態中に許可した割り込みが起こると、MCUは起動します。その時にMCUは起動時間に加えて4周期停止され、割り込みルーチンを実行し、そしてSLEEP命令の次の命令から実行を再開します。デハイスが休止から起動するとき、レジ、スタファイルとSRAMの内容は変えられません。休止形態中にリセットが起こると、MCUは起動し、リセット ヘンクタから実行します。

17頁の図7-1.と図7-2.はAT90PWM2/2B/3/3Bの各種クロック系統とその配給を示します。この図は適切な休止形態選択の助けになります。

#### 8.0.1. SMCR - 休止形態制御レジスタ (Sleep Mode Control Register)

この休止形態制御レジスタは電力管理用の制御ビットを含みます。

| ピット         | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   | -    |

|-------------|---|---|---|---|-----|-----|-----|-----|------|

| \$33 (\$53) | _ | - | _ | _ | SM2 | SM1 | SM0 | SE  | SMCR |

| Read/Write  | R | R | R | R | R/W | R/W | R/W | R/W |      |

| 初期値         | 0 | 0 | 0 | 0 | 0   | 0   | 0   | 0   |      |

• ビット7~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

• ビット3~1 - SM2~0: 休止種別選択 (Sleep Mode Select Bit 2, 1 and 0)

これらのビットは表8-1.で示される利用可能な5つの休止形態の1つを選びます。

• ビット0 - SE: 休止許可 (Sleep Enable)

SLEEP命令が実行される時にMCUを休止形態へ移行させるには、休止許可(SE)ビットが論理1を書かれなければなりません。MCUの目的外休止形態移行を避けるため、SLEEP命令実行直前に休止許可(SE)ビットを設定(1)し、起動後直ちに解除(0)することが推奨されます。

| 表8-1. 休止形態種別選択 |                                             |                                                                                                                                                     |  |  |  |  |  |  |  |  |

|----------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| SM1            | SM0                                         | 休止形態種別                                                                                                                                              |  |  |  |  |  |  |  |  |

| 0              | 0                                           | アイドル動作                                                                                                                                              |  |  |  |  |  |  |  |  |

| 0              | 1                                           | A/D変換雑音低減動作                                                                                                                                         |  |  |  |  |  |  |  |  |

| 1              | 0                                           | パプーダウン動作                                                                                                                                            |  |  |  |  |  |  |  |  |

| 1              | 1                                           | (予約)                                                                                                                                                |  |  |  |  |  |  |  |  |

| 0              | 0                                           | (予約)                                                                                                                                                |  |  |  |  |  |  |  |  |

| 0              | 1                                           | (予約)                                                                                                                                                |  |  |  |  |  |  |  |  |

| 1              | 0                                           | スタンバイ動作 (注)                                                                                                                                         |  |  |  |  |  |  |  |  |

| 1              | 1                                           | (予約)                                                                                                                                                |  |  |  |  |  |  |  |  |

|                | SM1<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>1 | SM1         SM0           0         0           0         1           1         0           1         1           0         0           0         1 |  |  |  |  |  |  |  |  |

**注**: スタンバイ動作は外部クリスタル発振子またはセラミック 振動子でだけ利用できます。

#### 8.1. アイドル動作

休止種別選択( $SM2\sim0$ )ビットが'000'を書かれるとき、SLEEP命令はMCUをア仆ル動作へ移行させ、CPUを停止しますが、SPI、USAR T、アナログ比較器、A/D変換器、94マ/カウンタ、ウォッチトック、割り込み機構の継続動作を許します。この休止形態は基本的に $Clk_{CPU}$ と $clk_{FLASH}$ を停止する一方、他のクロックに走行を許します。

アイドル動作はMCUにタイマ溢れやUSARTの送信完了などの内部割り込みだけでなく、外部で起動された割り込みからの起動も可能にします。A/D変換が許可されるなら、この動作に移行すると変換が自動的に始まります。

#### 8.2. A/D変換雑音低減動作

SM2~0ビットが'001'を書かれるとき、SLEEP命令はMCUをA/D変換雑音低減動作へ移行させ、CPUを停止しますが、A/D変換器、外部割り込み、(クロック元が外部(T0またはT1)ならば)タイマ/カウンタ、ウォッチドッグの(許可されていれば)継続動作を許します。この休止形態は基本的にclkɪ/O, clkcpu, clkpt.ashを停止する一方、他のクロックに走行を許します。

これはA/D変換に対する雑音環境を改善し、より高い分解能の測定を可能にします。A/D変換器が許可されている場合、この動作に移行すると、変換が自動的に始まります。A/D変換完了割り込みからの他、外部リセット、ウォッチトック・リセット、低電圧検出(BOD)リセット、タイマ/カウンタの割り込み、電力段制御器(PSC)割り込み、SPM/EEPROM操作可割り込み、INTO~3の外部レベル割り込みだけが、A/D変換雑音低減動作からMCUを起動できます。

#### 8.3. パワーダウン動作

休止種別選択(SM2~0)ビットが、'010'を書かれると、SLEEP命令はMCUをパワーダウン動作へ移行させます。この動作では外部発振器が停止される一方、外部割り込み、ウォッチドッグ機能は(許可されていれば)継続して動作します。外部リセット、ウォッチドッグリセット、低電圧検出(BOD)リセット、INT0~3の外部レベル割り込みだけがMCUを起動できます。この休止形態は基本的に生成した全てのクロックを停止して、非同期部の動作だけを許します。

レヘールで起動した割り込みがハプワーダウン動作からの復帰に使われる場合、MCUを起動するためには変更したレヘールが一定時間保持されなければならないことに注意してください。詳細については51頁の「外部割り込み」を参照してください。

ハプワーダウン動作から起動するとき、起動条件が起きてから起動の効果が現れるまで遅延があります。これは停止されてしまっている後の再始動と安定になることをクロックに許します。この起動(遅延)時間は18頁の「クロック元」で記述されるように、リセット付加遅延時間を定義するのと同じCKSELヒュース、によって定義されます。

#### 8.4. スタンバイ動作

外部クリスタル発振子/セラミック振動子クロック種別が選ばれ、SM2~0ビットが'110'のとき、SLEEP命令はMCUをスタンバイ動作へ移行させます。この動作は(外部クリスタル用)発振器が走行(動作)を保たれる例外を除いてパワーダウン動作と同じです。デバイスはスタンバイ動作から6クロック周期で起動します。

表8-2. 各休止形態に於ける動作クロック範囲と復帰起動要因

|                                    |            | 動作           | クロック範     | 囲          |            | 発振器          | 復帰起動要因(割り込み・リセット) |                     |                      |                 |               |            |  |

|------------------------------------|------------|--------------|-----------|------------|------------|--------------|-------------------|---------------------|----------------------|-----------------|---------------|------------|--|

| 休止種別                               | clk<br>CPU | clk<br>FLASH | clk<br>10 | clk<br>ADC | clk<br>PLL | 主クロック<br>供給元 | INT<br>0~3        | 電力段<br>制御器<br>(PSC) | SPM<br>EEPROM<br>操作可 | A/D<br>変換<br>完了 | ウォッチ<br>ト゛ック゛ | その他<br>I/O |  |

| アイドル                               |            |              | 0         | 0          | 0          | 0            | 0                 | 0                   | 0                    | 0               | 0             | 0          |  |

| A/D変換雑音低減                          |            |              |           | 0          | 0          | 0            | 2                 | 0                   | 0                    | 0               | 0             |            |  |

| ハ <sup>°</sup> ワータ <sup>*</sup> ウン |            |              |           |            |            |              | 2                 | 0                   |                      |                 | 0             |            |  |

| スタンバイ(注1)                          |            |              |           |            |            | 0            | 2                 |                     |                      |                 | 0             |            |  |

注1: クロック元として外部クリスタル発振子またはセラミック振動子が選ばれた場合です。

② INTO~3のレベル割り込みだけです。

#### 8.5. 電力削減

電力削減レシ、スタ(PRR)は消費電力を削減するために個別周辺機能へのクロックを停止する方法を提供します。周辺機能は現状で固定化され、I/Oレシ、スタは読み込みも書き込みもできません。クロックを停止している時に周辺機能によって使われていた資源は占有されたままなので、その周辺機能は殆どの場合、クロックを停止する前に禁止されるべきです。周辺機能部の起動は電力削減レシ、スタ(PRR)のビットを解除(0)することによって行い、その周辺機能部を停止前と同じ状態にします。

クロック停止中や停止後、クロック開始中の周辺機能の予測可能な全動作は保証されません。故に電力削減レジスタ(PRR)でクロックを停止前に周辺機能を停止することが推奨されます。

周辺機能部の停止は全体に亘る重要な消費電力の削減のために活動動作とアイドル動作で使えます。その他の休止形態ではクロックが予め停止されます。

#### 8.5.1. PRR - 電力削減レジスタ (Power Reduction Register)

| ピット        | 7                            | 6         | 5      | 4      | 3      | 2     | 1        | 0     |  |  |  |  |

|------------|------------------------------|-----------|--------|--------|--------|-------|----------|-------|--|--|--|--|

| (\$64)     | PRPSC2                       | PRPSC1(注) | PRPSC0 | PRTIM1 | PRTIM0 | PRSPI | PRUSART0 | PRADC |  |  |  |  |

| Read/Write | R/W                          | R/W       | R/W    | R/W    | R/W    | R/W   | R/W      | R/W   |  |  |  |  |

| 初期値        | 0                            | 0         | 0      | 0      | 0      | 0     | 0        | 0     |  |  |  |  |

|            | 注: PRPSC1はAT90PWM2/2Bで使えません。 |           |        |        |        |       |          |       |  |  |  |  |

• ビット7 - PRPSC2:電力段制御器(PSC)2電力削減 (Power Reduction PSC2)

このビットへの1書き込みはその部分へのクロック停止によって電力段制御器(PSC)2の消費を削減します。PSC2の再起動時、PSC2は正しい動作を保証するために再初期化されるべきです。

• ビット6 - PRPSC1:電力段制御器(PSC)1電力削減 (Power Reduction PSC1)

このビットへの1書き込みはその部分へのクロック停止によって電力段制御器(PSC)1の消費を削減します。PSC1の再起動時、PSC1は正しい動作を保証するために再初期化されるべきです。

• ビット5 - PRPSC0:電力段制御器(PSC)0電力削減 (Power Reduction PSC0)

このビットへの1書き込みはその部分へのクロック停止によって電力段制御器(PSC)0の消費を削減します。PSC0の再起動時、PSC0は正しい動作を保証するために再初期化されるべきです。

• ビット4 - PRTIM1 : タイマ/カウンタ1電力削減 (Power Reduction Timer/Counter1)

このビットへの1書き込みはタイマ/カウンタ1部の消費を削減します。 タイマ/カウンタ1が許可されると、本ビット設定(=1)前のように動作は継続します。

• ビット3 - PRTIMO: タイマ/カウンタ0電力削減 (Power Reduction Timer/Counter0)

このビットへの1書き込みはタイマ/カウンタ0部の消費を削減します。 タイマ/カウンタ1が許可されると、本ビット設定(=1)前のように動作は継続します。

• ビット2 - PRSPI: 直列周辺インターフェース電力削減 (Power Reduction Serial Peripheral Interface)

このビットへの1書き込みはその部分へのクロック停止によって直列周辺インターフェース(SPI)の消費を削減します。SPIの再起動時、SPIは正しい動作を保証するために再初期化されるべきです。

• ビット1 - PRUSARTO: USART電力削減 (Power Reduction USART)

このビットへの1書き込みはその部分へのクロック停止によってUSARTの消費を削減します。USARTの再起動時、USARTは正しい動作を保証するために再初期化されるべきです。

• ビット0 - PRADC : A/D変換器電力削減 (Power Reduction ADC)

このビットへの1書き込みはその部分へのクロック停止によってA/D変換器(ADC)の消費を削減します。A/D変換器は本機能使用前に禁止されなければなりません。

#### 8.6. 消費電力の最小化

これらはAVRが制御するシステムで消費電力の最小化を試みる時に考慮するためのそれぞれの検討点です。一般的に休止形態は可能な限り多く使われるべきで、休止種別は動作するデバイスの機能が可能な限り少なくなるように選ばれるべきです。必要とされない全ての機能は禁止されるべきです。特に次の機能部は最低可能消費電力の達成を試みるとき、特別な考慮を必要とするでしょう。

#### 8.6.1. A/D変換器 (ADC)

許可したなら、A/D変換器は全休止形態で許可されます。節電するため、休止形態の何れかへ移行する前にA/D変換器は禁止されるべきです。A/D変換器がOFFそして再びONに切り替えられると、次の(最初の)変換は延長された(初回)変換になります。A/D変換器操作の詳細については144頁の「A/D変換器」を参照してください。

#### 8.6.2. アナログ比較器

アイドル動作へ移行するとき、アナロゲ比較器は使われないなら、禁止されるべきです。A/D変換雑音削減動作へ移行するとき、アナロゲ比較器は禁止されるべきです。その他の休止形態でのアナロゲ比較器は自動的に禁止されます。しかしアナロゲ比較器が入力として内部基準電圧を使う設定の場合、全休止形態でアナロゲ比較器は禁止されるべきです。さもなければ内部基準電圧は休止形態と無関係に許可されます。アナロゲ比較器設定法の詳細については140頁の「アナロゲ比較器」を参照してください。

#### 8.6.3. 低電圧検出器 (BOD)

低電圧検出器(BOD)が応用で必要とされないなら、この単位部はOFFにされるべきです。低電圧検出器がBODLEVELヒューズによって許可されていると全休止形態で許可され、故に常時電力を消費します。これはより深い休止形態での総消費電流にとって重要な一因になります。低電圧検出器(BOD)設定法の詳細については29頁の「低電圧検出 (BOD)」を参照してください。

#### 8.6.4. 内部基準電圧

内部基準電圧は低電圧検出器(BOD)、アナログ比較器、A/D変換器によって必要とされる時に許可されます。これら単位部が上の項目で記述されたように禁止されると、内部基準電圧は禁止され、電力を消費しません。再び許可する場合、この出力が使われる前に使用者は基準電圧へ起動(安定時間)を与えなければなりません。基準電圧が休止形態でON保持される場合、この出力は直ちに使えます。起動時間の詳細については30頁の「内部基準電圧」を参照してください。

#### 8.6.5. ウォッチト ック タイマ

ウォッチト、ック、タイマが応用で必要とされないなら、この単位部はOFFにされるべきです。ウォッチト、ック、タイマが許可されていると全休止形態で許可され、故に常時電力を消費します。これはより深い休止形態での総消費電流にとって重要な一因になります。ウォッチト、ック、タイマ 設定法の詳細については31頁の「ウォッチト、ック、タイマ」を参照してください。

#### 8.6.6. ホート ピン

休止形態へ移行するとき、全てのポート ピンは最小電力使用に設定されるべきです。最も重要なことはその時にピンが抵抗性負荷を駆動しないのを保証することです。I/Oクロック(clkɪ/O)とA/D変換クロック(clkADC)の両方が停止される休止形態ではデバイスの入力緩衝部が禁止されます。これは必要とされない時に入力論理回路によって電力が消費されないことを保証します。いくつかの場合で入力論理回路は起動条件を検出するために必要とされ、その時は許可されます。どのピンが許可されるかの詳細については40頁の「デジタル入力許可と休止形態」を参照してください。入力緩衝部が許可され、入力信号が浮いている状態のままか、またはアナログ信号電圧がVCC/2付近の場合、入力緩衝部は過大な電力を消費するでしょう。

アナログ、入力ピンに対するデジタル入力緩衝部は常に禁止されるべきです。入力ピンでのVCC/2付近のアナログ信号入力は通常動作でも 重要な電流を引き起こし得ます。デジタル入力緩衝部はデジタル入力禁止レジスタ(DIDR0とDIDR1)の書き込みによって禁止できます。 詳細については143頁と153頁の「DIDR0 - デジタル入力禁止レジスタ0」、「DIDR1 - デジタル入力禁止レジスタ1」を参照してください。

#### 8.6.7. 内蔵デバッグ機能(dW)

内蔵デバックが機能がDWENヒューズによって許可され、チップが休止形態へ移行すると、主クロック元は許可に留まり、従って常に電力を消費します。これはより深い休止形態での総消費電流にとって重要な一因になります。

# 9. システム制御とリセット

#### 9.0.1. AVRのリセット

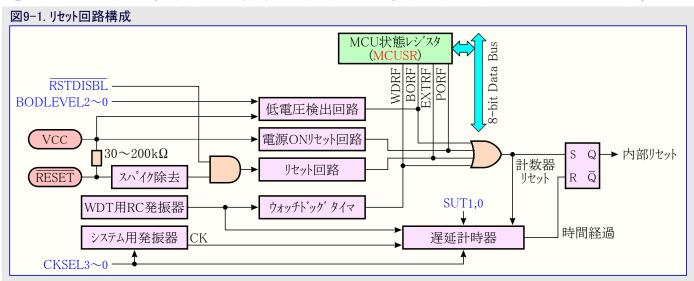

リセット中、全てのI/Oレジスタはそれらの初期値に設定され、プログラムはリセット ベクタから実行を開始します。リセット ベクタに配置される命令は、きっとリセット処理ルーチンへのRJMP(相対分岐)命令でしょう。プログラムが決して割り込み元を許可しないなら、割り込みベクタは使われず、これらの位置に通常のプログラムコートが配置できます。これはリセット ベクタが応用領域の一方、割り込みベクタがブート領域の場合やその逆も同様です。図9-1.の回路構成図はリセット論理回路を示します。表9-1.はリセット回路の電気的特性を定義します。

AVRのI/Oポートはリセット元が有効になると直ちにそれらの初期状態にリセットされます。これはどのクロック元の走行も必要ありません。

全てのリセット元が無効にされてしまった後、遅延計数器(タイマ)が始動され、内部リセットを引き伸ばします。これは通常動作開始前に安定電圧へ達することを電源に許します。遅延タイマの遅延時間はSUTヒューズとCKSELヒューズを通して使用者によって定義されます。この遅延時間についての各種選択は18頁の「クロック元」で示されます。

#### 9.0.2. リセット元

AT90PWM2/2B/3/3Bには次の4つのリセット元があります。

- 電源ONリセット・・・・・ 供給電圧が電源ONリセット閾値電圧(VPOT)以下でMCUがリセットされます。

- 外部リセット・・・・・・・ RESET ピンが最小パルス幅以上Lowレヘブルに保たれると、MCUがリセットされます。

- ウォッチト、ック、リセット・・・ ウォッチト、ック、システム リセット動作が許可され、ウォッチト、ック、タイマが終了すると、MCUがリセットされます。

- 低電圧リセット・・・・・ 低電圧検出が許可され、供給電圧(VCC)が低電圧検出電圧(VBOT)以下でMCUがリセットされます。

#### 表9-1. リセット電気的特性

| シンホ゛ル             | 項目                    | 条件      | 最小     | 代表    | 最大      | 単位    |      |

|-------------------|-----------------------|---------|--------|-------|---------|-------|------|

| $V_{ m POT}$      | 上昇時電源ONリセット閾値電        |         | -      | 1.4   | 2.3     |       |      |

| V POT             | 下降時電源ONリセット閾値電        |         | 1      | 1.3   | 2.3     | V     |      |

| $V_{RST}$         | RESETt°ン閾値電圧          |         | 0.2VCC |       | 0.85VCC |       |      |

| ${ m t_{RST}}$    | RESETピンでの最小パルス幅       |         |        | 400   |         |       | ns   |

| $V_{POR}$         | 内部電源ONリセット信号を VCC開始電圧 |         |        | -0.05 | GND     | +0.05 | V    |

| V <sub>CCRR</sub> | 保証するための               | VCC上昇速度 |        | 0.3   |         |       | V/ms |

注1: 供給電圧がこの電圧以下にならないと、上昇時の電源ONリセットは動作しません。

注: 値は指針の意味だけです。

#### 9.0.3. 電源ONリセット

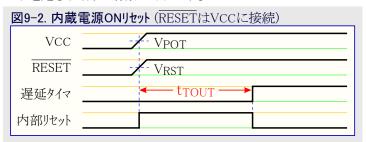

電源ONリセット(POR)パルスはチップ上の検出回路によって生成されます。検出電圧は表9-1.で定義されます。POR信号はVCCが検出電圧以下の時は必ず活性(有効)にされます。POR回路は供給電圧異常検出は勿論、始動リセットの起動にも使えます。

電源ONJセット回路はデバイスが電源投入でリセットされることを保証します。電源ONJセット閾値電圧(VPOT)への到達はVCCの上昇後にデバイスがどのくらいリセットを保つかを決める遅延計数器(タイマ)を起動します。VCCがこの検出電圧以下に低下すると、リセット信号はどんな遅延もなく再び有効にされます。

#### 9.0.4. 外部リセット

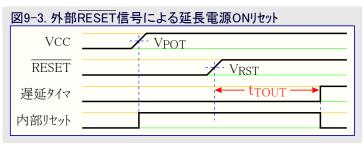

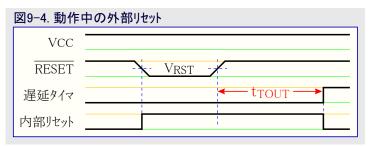

外部リセットはRESETt°ンのLowレヘルによって生成されます。クロックが動いていなくても、最小ハペルス幅(表9-1.参照)以上のリセット パルスはリセットを生成します。短すぎるパルスはリセット生成が保証されません。印加された信号の上昇がリセット閾値電圧(VRST)に達すると(遅延タイマを起動し)、遅延タイマは遅延時間(t<sub>TOUT</sub>)経過後にMCUを始動します。

#### 9.0.5. 低電圧(ブラウンアウト)検出リセット

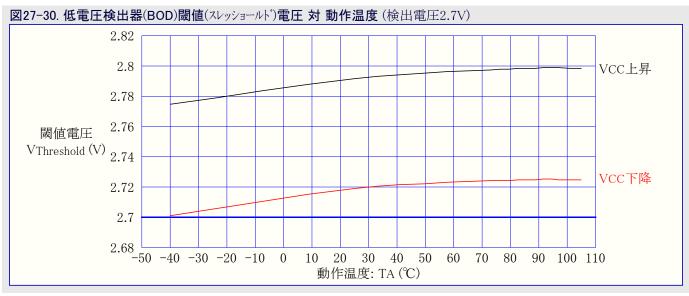

本デバイスには固定化された起動(検出)電圧と比較することによって動作中のVCCを監視するチップ。上の低電圧検出(BOD)回路があります。BODの起動電圧はBODLEVELヒュース。によって選べます。この起動電圧はスパイク対策BODを保証するため、ヒステリシスを持ちます。検出電圧のヒステリシスはVBOT+=VBOT+VHYST/2、VBOT-=VBOT-VHYST/2と解釈されるべきです。

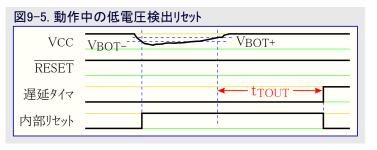

BODが許可され、VCCが起動電圧以下に下降すると(**図9-5**.の VBOT-)、低電圧リセットが直ちに有効とされます。VCCが起動電圧以上に上昇すると(**図9-5**.のVBOT+)、(遅延タイマが起動され)遅延タイマは遅延時間(t<sub>TOUT</sub>)経過後にMCUを始動します。

BOD回路は電圧が表9-3.で与えられるtBOD時間より長く起動電圧以下に留まる場合のみ、VCCでの低下を検出します。

#### 表9-3. 低電圧検出(BOD)特性

| シンホ゛ル             | 項目            | 最小 | 代表 | 最大 | 単位 |

|-------------------|---------------|----|----|----|----|

| V <sub>HYST</sub> | 低電圧検出ヒステリシス電圧 |    | 70 |    | mV |

| $t_{ m BOD}$      | 最小低電圧検出時間     |    | 2  |    | μs |

#### 表9-2. BODLEVELヒューズ(VBOT) 設定(注1)

| BODLEVEL2~0 | 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111    |

|-------------|-----|-----|-----|-----|-----|-----|-----|--------|

| 最大          |     |     |     |     |     |     |     | 低電圧検出  |

| 代表          | 2.6 | 2.8 | 4.2 | 4.4 | 4.3 | 2.7 | 4.5 | (BOD)  |

| 最小          |     |     |     |     |     |     |     | リセット禁止 |

| 単位          |     |     |     |     |     |     |     |        |

注: 値は指針の意味だけです。

注1: いくつかのデバイスでVBOTが公称最低動作電圧以下の可能性があります。この状態のデバイスについては製造検査中、VCC=VBOTに落として検査されています。これはマイクロコントローラの正しい動作がもはや保証されない電圧になる前に、低電圧検出(BOD)リセットが起きることを保証します。この検査は高動作電圧に対してBODLEVEL =010、低動作電圧に対してBODLEVEL =010、低動作電圧に対してBODLEVEL =010、低動作電圧に対して

#### 9.0.6. ウォッチト・ック・リセット

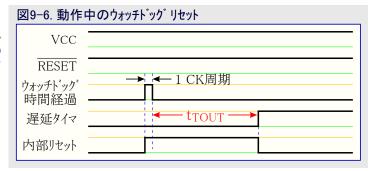

ウォッチト・ック・時間経過時、(内部的に)1CK周期幅の短いリセット パルスを生成します。このパルスの下降端で遅延タイマは遅延時間(t<sub>TOUT</sub>)の計時を始めます。ウォッチト・ック・タイマ操作の詳細については31頁を参照してください。

#### 9.0.7. MCUSR - MCU状態レジスタ (MCU Status Register)

MCU状態レジスタはどのリセット元がMCUリセットを起こしたかの情報を提供します。

| ピット         | 7 | 6 | 5 | 4 | 3    | 2    | 1     | 0    | _     |

|-------------|---|---|---|---|------|------|-------|------|-------|

| \$34 (\$54) | - | - | - | - | WDRF | BORF | EXTRF | PORF | MCUSR |

| Read/Write  | R | R | R | R | R/W  | R/W  | R/W   | R/W  |       |

| 初期値         | 0 | 0 | 0 | 0 | 内容参照 | 内容参照 | 内容参照  | 内容参照 |       |

#### • ビット7~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

• ヒット3 - WDRF: ウォッチトック リセット フラク (Watchdog Reset Flag)

このビットはウォッチドッグ リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

• ビット2 - BORF: 低電圧リセット フラク (Brown-Out Reset Flag)

このビットは低電圧リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

• ビット1 - EXTRF:外部リセット フラク (External Reset Flag)

このビットは外部リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

• ビット0 - PORF: 電源ONリセット フラク (Power-on Reset Flag)

このビットは電源ONリセットが起こると設定(1)されます。このビットはこのフラグへの論理0書き込みによってのみリセット(0)されます。

リセット条件の確認にリセット フラグを使うため、使用者はプログラム内で可能な限り早くMCUSRを読み、そして解除(0)すべきです。別のリセットが起こる前にこのレジスタが解除(0)されると、そのリセット元はリセットフラグを調べることによって得られます。

#### 9.1. 内部基準電圧

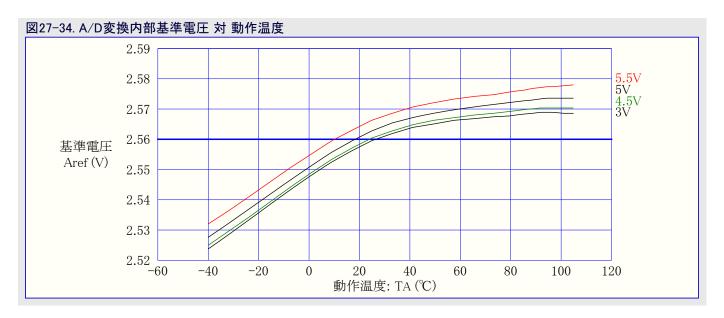

AT90PWM2/2B/3/3Bは内部(1.1Vバンドギャップ)基準電圧が特徴です。この基準電圧は低電圧検出(BOD)に使われます。2.56V基準電圧はこのバンドギャップによって生成されます。D/A変換器やA/D変換器の基準電圧としても、アナログ比較器のアナログ入力としても使えます。内部Vrefを使うにはA/D変換多重器選択(ADMUX)レジスタの基準電圧選択(REFS1,0)ビットを設定し、必要とするアナログ機能を設定する必要があります。

#### 9.1.1. 基準電圧許可信号と起動時間

基準電圧には使われるべき方法に影響を及ぼすかもしれない起動時間があります。この起動時間は表9-4.で与えられます。節電のために、この基準電圧は常にONではありません。この基準電圧は次の状態中ONです。

- 1. 低電圧検出リセット許可時 (BODLEVELヒュース、のプログラム(0)により)

- 2. A/D変換部動作許可時 (A/D変換制御/状態レジスタA(ADCSRA)のA/D動作許可(ADEN)=1)

- 3. D/A変換部動作許可時 (D/A変換制御(DACON)レジスタのD/A動作許可(DAEN)=1)

従って低電圧検出(BOD)が許可されていないと、A/D変換部許可(ADEN=1)またはD/A変換部許可(DAEN=1)後、使用者はアナログ比較器またはA/D変換器またはD/A変換器出力が使われる前に、基準電圧へ起動時間を与えなければなりません。パワーダウン動作での消費電力を減らすため、使用者はパワーダウン動作へ移行する前に基準電圧がOFFされるのを保証することで上の3つの状態を避けられます。

#### 9.1.2. 内部基準電圧特性

#### 表9-4 内部其進雷圧特性

| シンホ゛ル             | 項目   | 条件 | 最小 | 代表  | 最大 | 単位 |

|-------------------|------|----|----|-----|----|----|

| $V_{BG}$          | 基準電圧 |    | -  | 1.1 | -  | V  |

| $t_{\mathrm{BG}}$ | 起動時間 | -  |    | 40  | -  | μs |

| $I_{\mathrm{BG}}$ | 消費電流 |    |    | 15  |    | μA |

注: 値は目安だけです。

#### 9.2. ウォッチトック タイマ

AT90PWM2/2B/3/3Bには強化されたウォッチト、ッグ タイマ(WDT)があります。主な機能を次に示します。

- 独立した内蔵発振器からのクロック駆動

- 3つの動作種別

- 割り込み

- システム リセット

- 割り込みとシステム リセット

- 選択可能な16ms~8sの計時完了時間

- 安全動作用のウォッチトック 常時ONハートウェア ヒュース

ウォッチドック、タイマ(WDT)はチップ上の独立した128kHz発振器の間隔で計時するタイマです。WDTは計数器が与えられた計時完了値に達した時に割り込みまたはシステムリセットを与えます。通常動作では計時完了値へ達する前に計数器を再始動するために、システムがウォッチドック、リセット(WDR)命令を使う必要があります。システムが計数器を再始動しなければ、割り込みまたはシステムリセットが起こるでしょう。

割り込み動作種別では、タイマ計時完了時にWDTが割り込みを生じます。この割り込みは休止形態からデバイスを起動するためや、一般的なシステムタイマとしても使えます。1つの例は或る動作に対して許された最

大時間を制限することで、その動作が予測されたより長く走行する時に割り込みを生じます。システム リセット動作種別ではタイマ計時完了時にWDTがリセットを生じます。これは一般的にコート・外走行の場合の中断を防止するのに使われます。3つ目の動作種別は先に割り込みを生じ、その後にシステム リセット動作種別に切り替えることで、他の2つの動作種別の組み合わせとなる、割り込み及びシステム リセット動作種別です。この動作種別は例えばシステム リセットに先立って重要なパラメータを保存することによって安全な停止を許します。

ウォッチト、ック、常時ON(WDTON)ヒュース、のプログラム(0)はウォッチト、ック、タイマをシステム リセット動作種別に強制します。このヒュース、のプログラム(0)でシステム リセット動作(WDE)ヒ、ットと割り込み動作(WDIE)ヒ、ットは各々、'1'と'0'に固定されます。

更にプログラム保護を保証するためにウォッチドッグ設定の変更は時間制限手順に従わなければなりません。システム リセット許可(WDE)の解除と計時完了時間設定の変更についての手順は次のとおりです。

- 1. 同じ操作(命令)でウォッチト、ッグ変更許可(WDCE)とWDEに論理1を書きます。WDEビットの直前の値に拘らず、論理1がWDEに書かれなければなりません。

- 2. 次からの4クロック周期内に同じ操作(命令)で欲したWDEとウォッチドッグタイマ前置分周選択(WDP3~0)ビットを書きますが、WDCEビットは解除(0)されてです。これは1操作(命令)で行わなければなりません。

次のコート・例はウォッチト・ッグ・タイマをOFFに切り替えるアセンブリ言語とC言語の関数を示します。本例は(例えば全割り込み禁止によって)割り込みが制御され、それ故これらの関数実行中に割り込みが起きない前提です。

```

アセンブリ言語プログラム例

WDT_OFF:

;全割り込み禁止

CLI

WDR

;ウォッチト`ック` タイマ リセット

IN

R16, MCUSR

;MCUSR値を取得

ANDI

R16, ~ (1<<WDRF)

;WDRF論理0値を取得

;ウォッチト、ック、リセットフラク、(WDRF)解除

OUT

MCUSR, R16

LDS

R16, WDTCSR

;現WDTCSR値を取得(他ビット保護用)

R16, (1<<WDCE) | (1<<WDE)

;WDCEとWDE論理1値を設定

ORI

STS

WDTCSR, R16

;WDCEとWDEに論理1書き込み

LDI

R16, (0<<WDE)

;WDE論理0値を取得

STS

WDTCSR, R16

;ウォッチト・ック・禁止

;全割り込み許可

SEI

;呼び出し元へ復帰

RET

C言語プログラム例

void WDT_off(void)

__disable_interrupt();

/* 全割り込み禁止 */

/* ウォッチト゛ック゛ タイマ リセット */

__watchdog_reset();

MCUSR &= ^{\sim} (1<<WDRF);

/* ウォッチト`ック` リセット フラク`(WDRF)解除 */

WDTCSR \mid = (1 << WDCE) \mid (1 << WDE);

/* WDCEとWDEに論理1書き込み */

WDTCSR = 0x00;

/* ウォッチト・ック 禁止 */

/* 全割り込み許可 */

__enable_interrupt();

```

**注**: 6頁の「**コート** 例について」をご覧ください。

注: ウォッチドッゲが偶然に許可されると(例えばポインタの逸脱や低電圧(プラウンアウト)状態)、デバイスはリセットし、ウォッチドッゲは許可に留まります。コードがウォッチドッゲ操作の初期設定をしなければ、これは計時完了の無限繰り返しを引き起こすかもしれません。この状態を避けるため、応用ソフトウェアは例えウォッチドッゲが使われなくても、初期化ルーチンでWDRFフラケ、とWDE制御ビットを常に解除(0)すべきです。

次のコートが例はウォッチトックがタイマの計時完了値変更用のアセンブリ言語とC言語の関数を示します。

```

アセンブリ言語プログラム例

WDT PRS:

CLI

;全割り込み禁止

;ウォッチトック タイマ リセット

WDR

LDS

R16, WDTCSR

;現WDTCSR値を取得(他ビット保護用)

R16, (1<<WDCE) | (1<<WDE)

ORI

;WDCEとWDE論理1値を設定

;WDCEとWDEに論理1書き込み

STS

WDTCSR, R16

R16, (1<<WDE) | (1<<WDP2) | (1<<WDP0)

;WDE=1,計時間隔=0.5s値を取得

LDI

STS

WDTCSR, R16

;0.5s監視間隔リセット動作開始

SEI

;全割り込み許可

;呼び出し元へ復帰

RET

C言語プログラム例

void WDT off(void)

__disable_interrupt();

/* 全割り込み禁止 */

/* ウォッチト・ック・タイマ リセット */

_watchdog_reset();

WDTCSR \mid = (1 << WDCE) \mid (1 << WDE);

/* WDCEとWDEに論理1書き込み */

WDTCSR = (1 << WDE) \mid (1 << WDP2) \mid (1 << WDP0);

/* 0.5s 監視間隔リセット動作開始 */

__enable_interrupt();

/* 全割り込み許可 */

```

注: 6頁の「コート・例について」をご覧ください。

注: ウォッチト・ッグ タイマ前置分周選択(WDP3~0)ビットの変更がより短い計時完了周期に変わってしまう結果になり得るため、ウォッチト・ッグ タイマはWDPビットのどんな変更にも先立ってリセット(WDR命令)されるべきです。

#### 9.2.1. WDTCSR - ウォッチトック、タイマ制御レシ、スタ (Watchdog Timer Control Register)

| ピット        | 7    | 6    | 5    | 4    | 3   | 2    | 1    | 0    |        |

|------------|------|------|------|------|-----|------|------|------|--------|

| (\$60)     | WDIF | WDIE | WDP3 | WDCE | WDE | WDP2 | WDP1 | WDP0 | WDTCSR |

| Read/Write | R/W  | R/W  | R/W  | R/W  | R/W | R/W  | R/W  | R/W  |        |

| 初期値        | 0    | 0    | 0    | 0    | 不定  | 0    | 0    | 0    |        |

#### • ビット7 - WDIF : ウォッチドッグ割り込み要求フラグ (Watchdog Interrupt Flag)

ウォッチト、ック、タイマが割り込みに設定され、ウォッチト、ック、タイマで計時完了が起こると、本ヒ、ットが設定(1)されます。対応する割り込み処理へクタを実行すると、WDIFはハート・ウェアによって解除(0)されます。代わりにWDIFはこのフラグへの論理1書き込みによっても解除(0)されます。ステータスレシ、スタ(SREG)の全割り込み許可(I)ビットとウォッチト、ック・割り込み許可(WDIE)が設定(1)されていれば、ウォッチト、ック・計時完了割り込みが実行されます。

#### • ビット6 - WDIE : ウォッチドッグ割り込み許可 (Watchdog Interrupt Enable)

このビットが1を書かれ、ステータス レジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されると、ウォッチドッグ割り込みが許可されます。この設定(1)との組み合わせでウォッチドッグリセット許可(WDE)ビットが解除(0)されると、割り込み動作種別になり、ウォッチドッグタイマで計時完了が起こると、対応する割り込みが実行されます。

WDEが設定(1)されると、ウォッチドッグ タイマは割り込み及びシステム リセット動作種別になります。ウォッチドッグ タイマでの最初の計時完了がウォッチドッグ割り込み要求(WDIF)フラグを設定(1)します。対応する割り込みへ、クタの実行はハート・ウェアによってWDIEとWDIFを自動的に解除(0)します。これは割り込みを使う間のウォッチト、ッグ リセット保護を維持するのに有用です。割り込み及びシステム リセット動作種別に留まるには、各割り込み後にWDIEが設定(1)されなければなりません。然しながら、ウォッチト、ッグ・システム リセット動作種別の安全機能に危険を及ぼすかもしれないため、これは割り込み処理ルーチン自身内で行われるべきではありません。次の計時完了に先立って割り込みが実行されない場合、システム リセットが適用(実行)されます。

| 表9-5. ウォ | 表9-5. ウォッチドッグ タイマ設定 |      |                |                      |  |  |  |  |

|----------|---------------------|------|----------------|----------------------|--|--|--|--|

| WDTON    | WDE                 | WDIE | 動作種別           | 計時完了での動作             |  |  |  |  |

| 1        | 0                   | 0    | 停止             | なし                   |  |  |  |  |

| 1        | 0                   | 1    | 割り込み           | 割り込み                 |  |  |  |  |

| 1        | 1                   | 0    | システム リセット      | リセット                 |  |  |  |  |

| 1        | 1                   | 1    | 割り込み及びシステムリセット | 割り込み、その後システムリセット動作種別 |  |  |  |  |

| 0        | Х                   | X    | システム リセット      | リセット                 |  |  |  |  |

注: WDTONヒュース は0=プログラム、1=非プログラムです。

#### • ビット4 - WDCE : ウォッチドッグ変更許可 (Watchdog Change Enable)

このビットはウォッチドッグ リセット許可(WDE)と前置分周器ビットの変更用の時間制限手順で使われます。WDEビットの解除(0)や前置分周器ビット変更のため、WDCEは設定(1)されなければなりません。

一旦1を書かれると、4クロック周期後にハードウェアがWDCEを解除(0)します。

#### • ビット3 - WDE: ウオッチドッグ リセット許可 (Watchdog System Reset Enable)

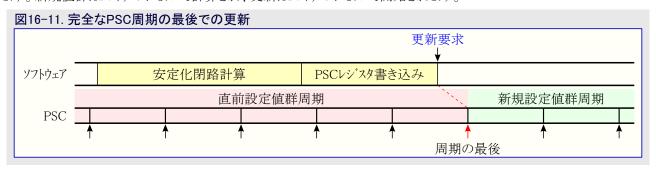

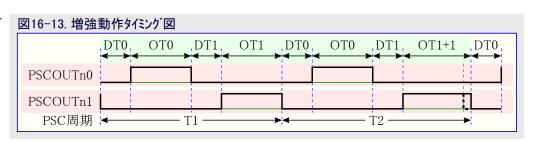

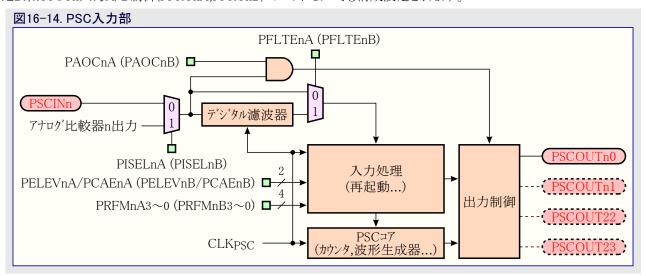

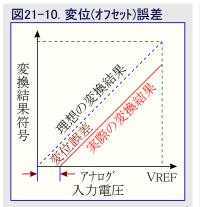

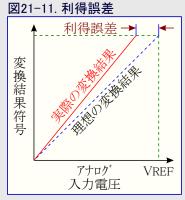

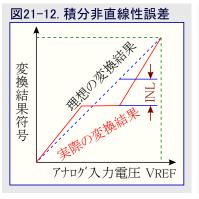

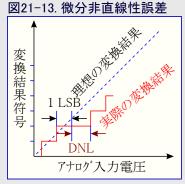

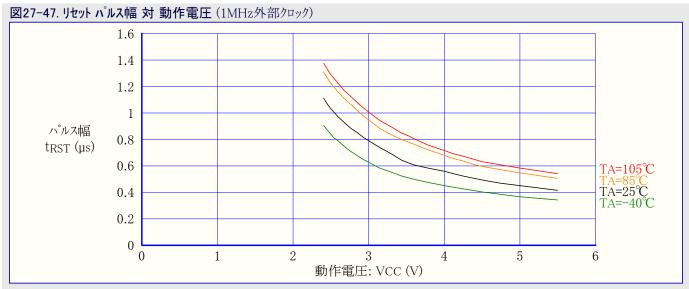

WDEはMCU状態レシ、スタ(MCUSR)のウォッチト、ック、リセット フラク(WDRF)によって無効にされます。これはWDRFが設定(1)されると、WDEが常に設定(1)されることを意味します。WDEを解除(0)するにはWDRFが先に解除(0)されなければなりません。この特徴は失敗を引き起こす状態中の複数リセットと失敗後の安全な起動を保証します。