## 特徴

- AVR® RISC構造

- AVR -高性能、低消費RISC構造

- 強力な118命令(多くは1周期で実行)

- 32個の1バイト汎用レジスタ

- 8MHz時、8MIPSに達する高速動作

- 不揮発性プログラム用メモリとデータ用メモリ

- 実装書き換え(ISP: In-System Program)可能な4K/8Kバイト(2K/4K語)フラッシュメモリ内蔵

1000回の書き換えが可能

- 256/512バイトのSRAM

- 実装書き換え(ISP)可能な256/512バイトのEEPROM

100,000回の書き換えが可能

- 64Kバイトまでの任意外部SRAM(メモリ)空間

- ソフトウェア保護用の設定可能な施錠機能

- 内蔵周辺機能

- 分離された前置分周器付き1つの8ビットタイマ/カウンタ

- 分離された前置分周器付き1つの16ビットタイマ/カウンタ

比較、捕獲、2つの8,9または10ビットPWM

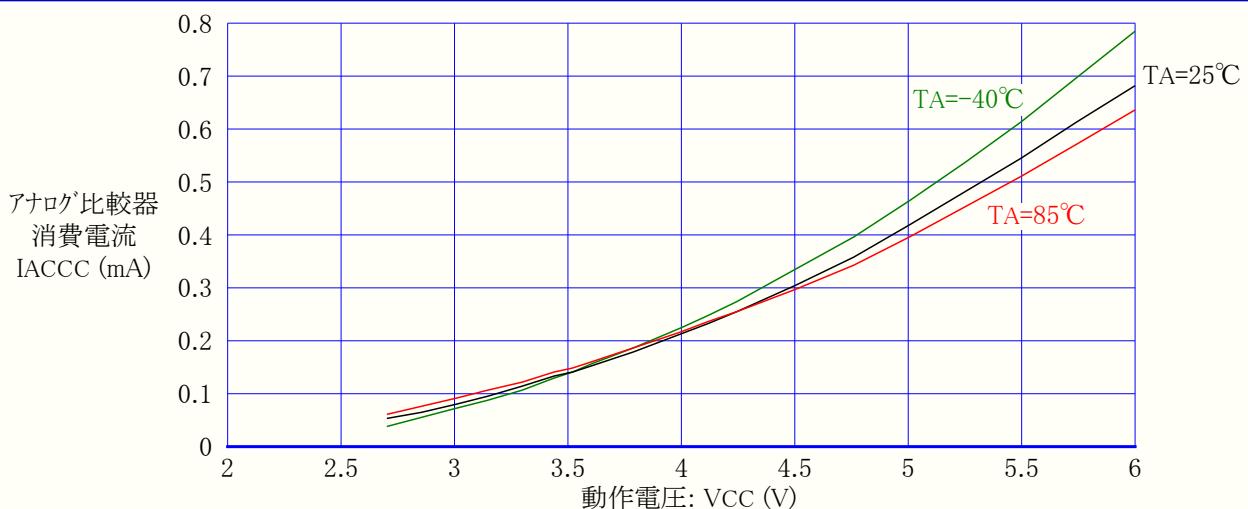

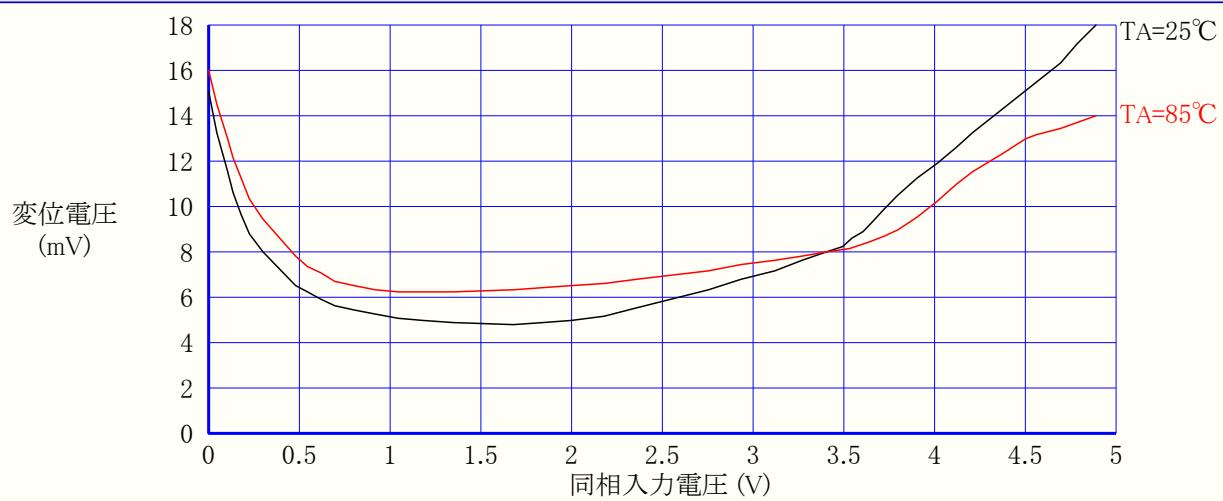

- アナログ比較器

- 設定可能な専用発振器付きウォッチドッグタイマ

- 設定可能なUART

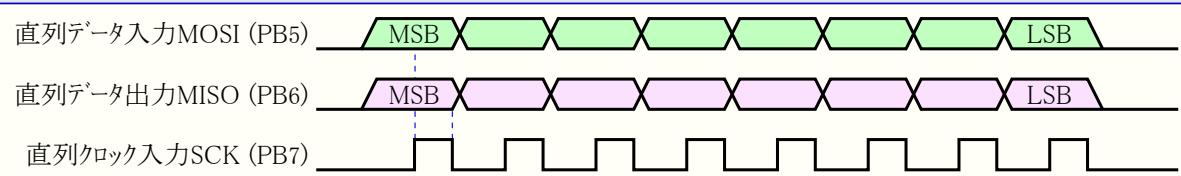

- 主装置/従装置動作SPI直列インターフェース

- 特殊マイクロコントローラ機能

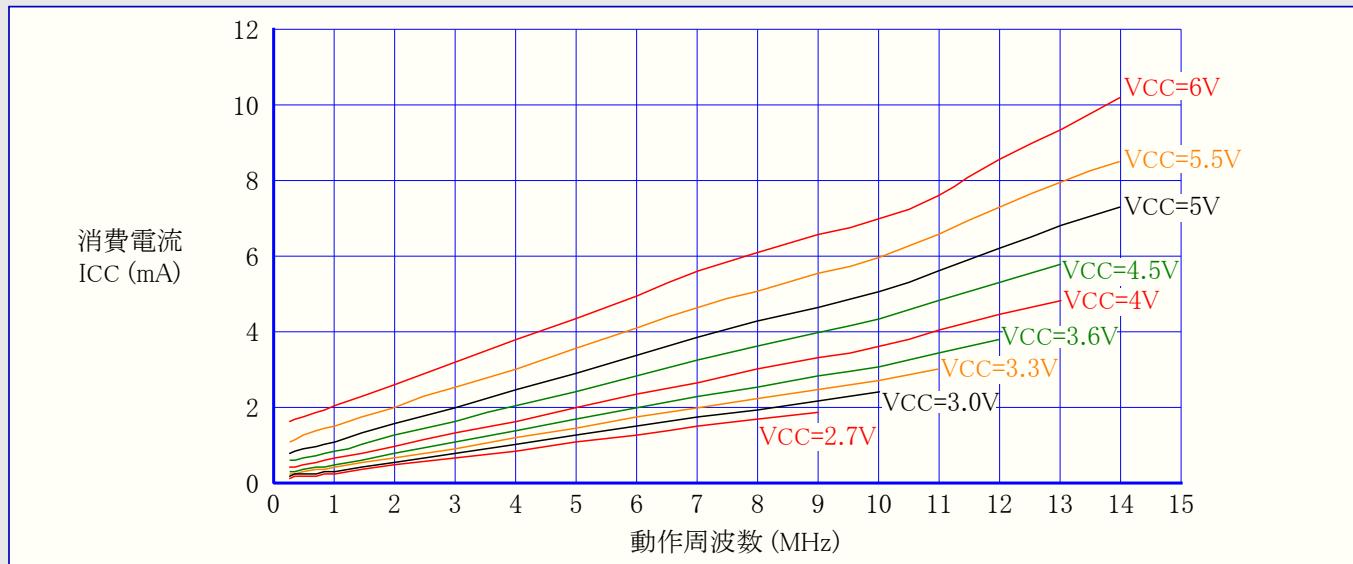

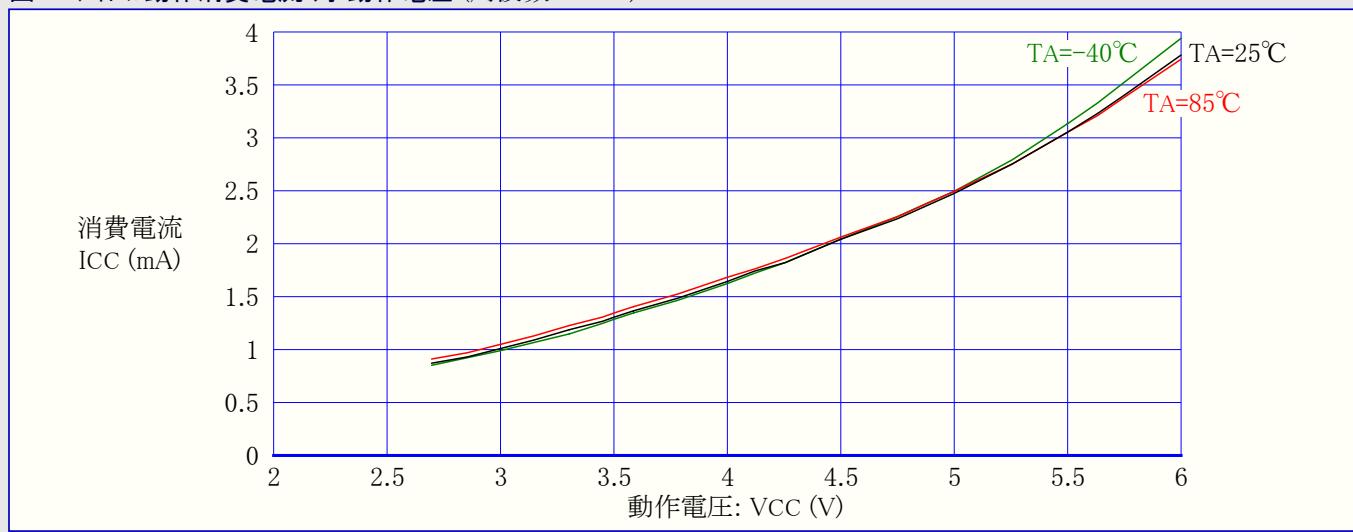

- アイドルとパワーダウンの2つの低消費動作

- 外部及び内部の割り込み

- 電気的特長

- 高速、低消費なCMOS製法

- 完全なスタティック動作

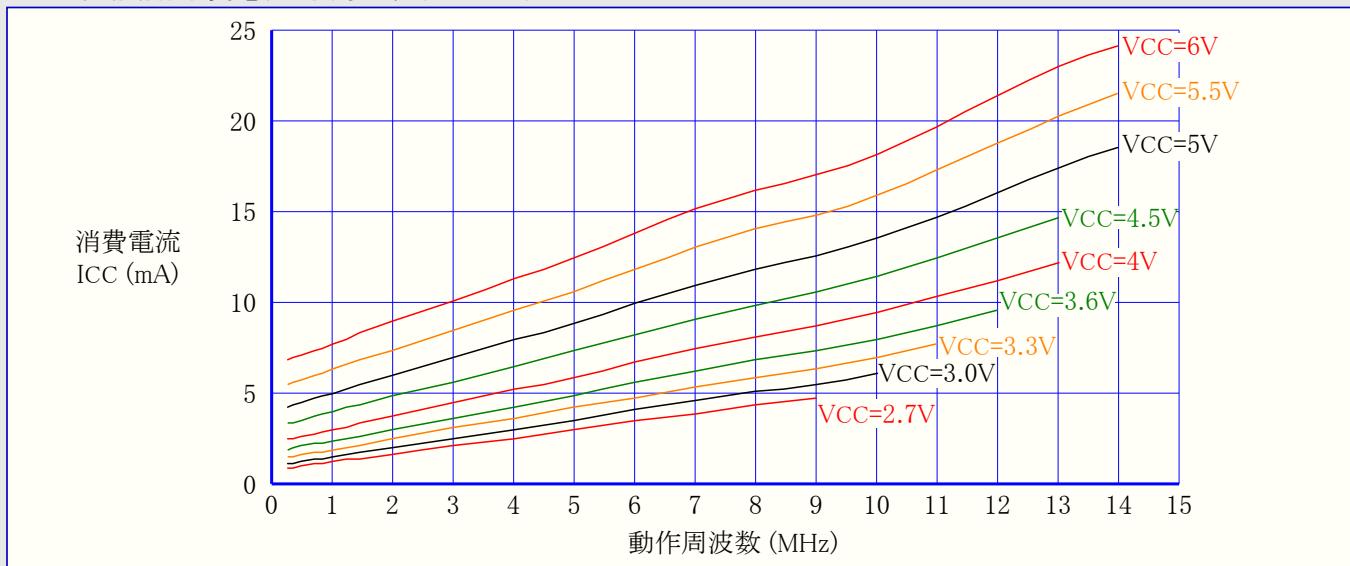

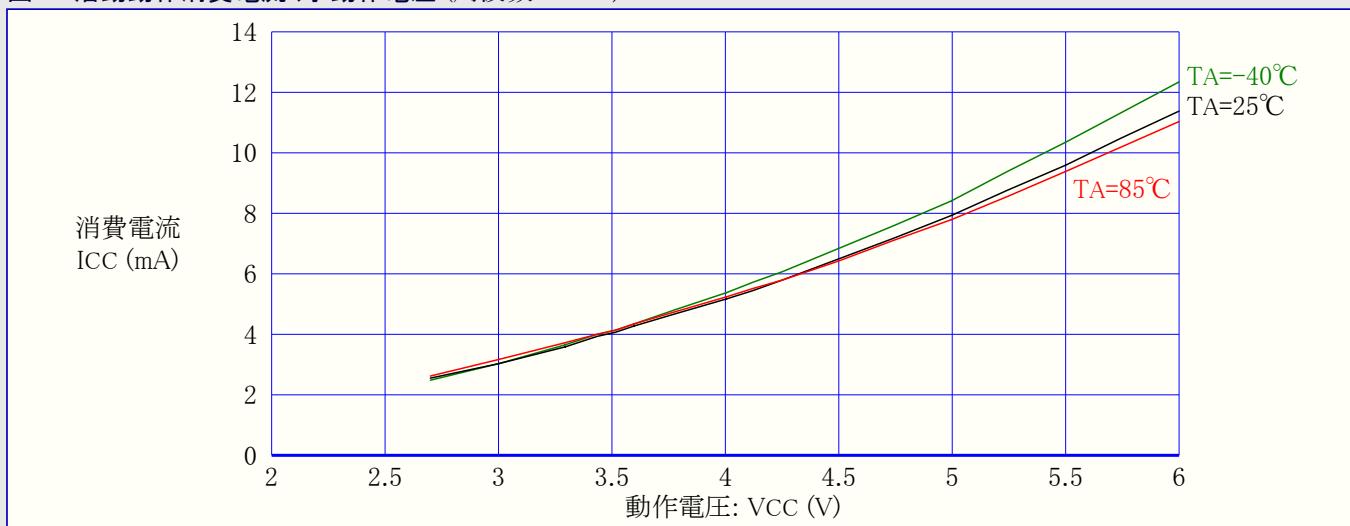

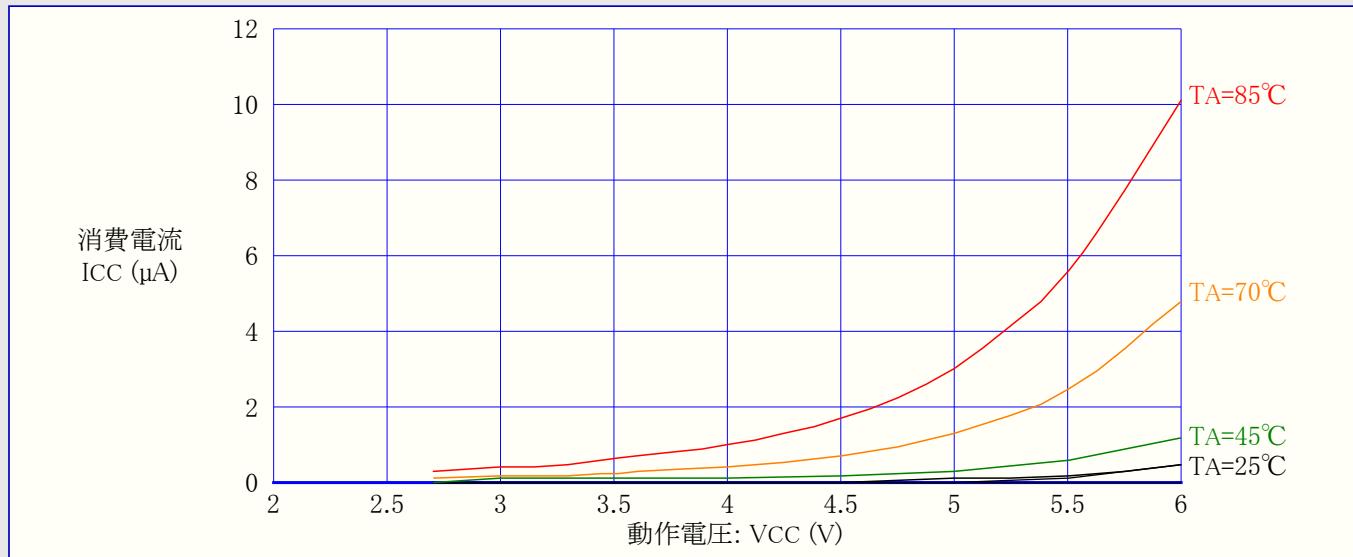

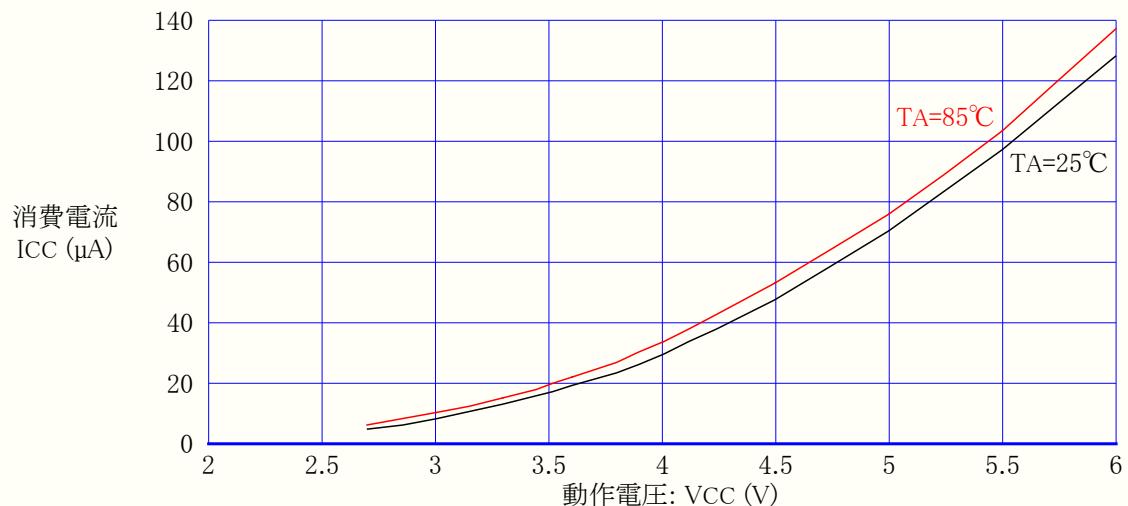

- 消費電流 (条件: 4MHz, 3V, 25°C)

- 活動動作 ..... 3.0mA

- アイドル動作 ..... 1.0mA

- パワーダウン動作 ..... 1μA未満

- I/Oと外囲器

- 32ビットの設定可能なI/O

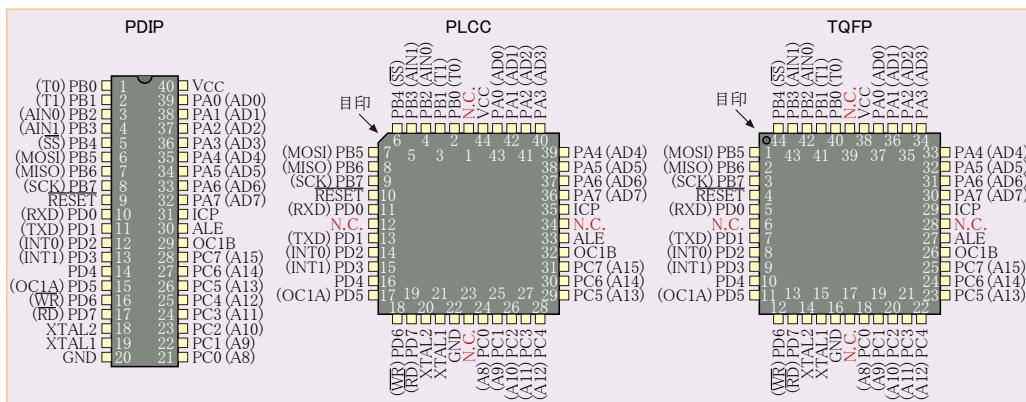

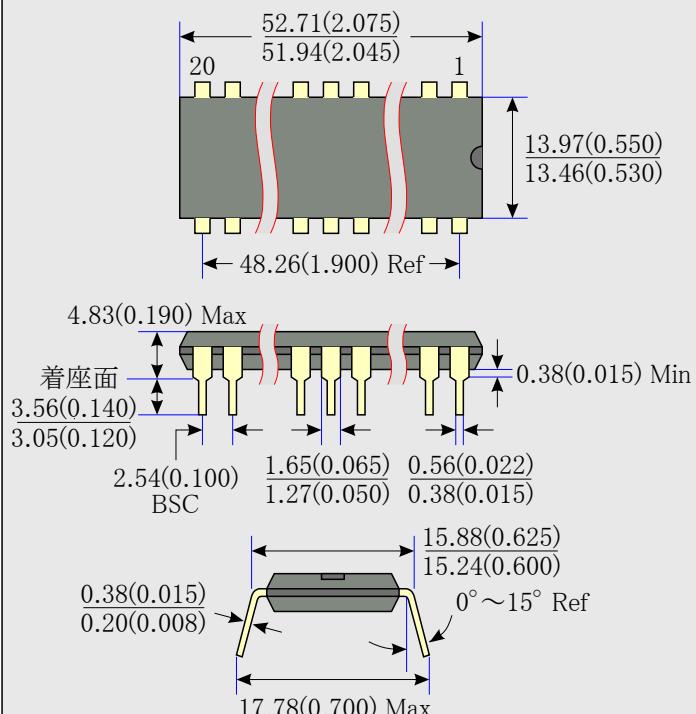

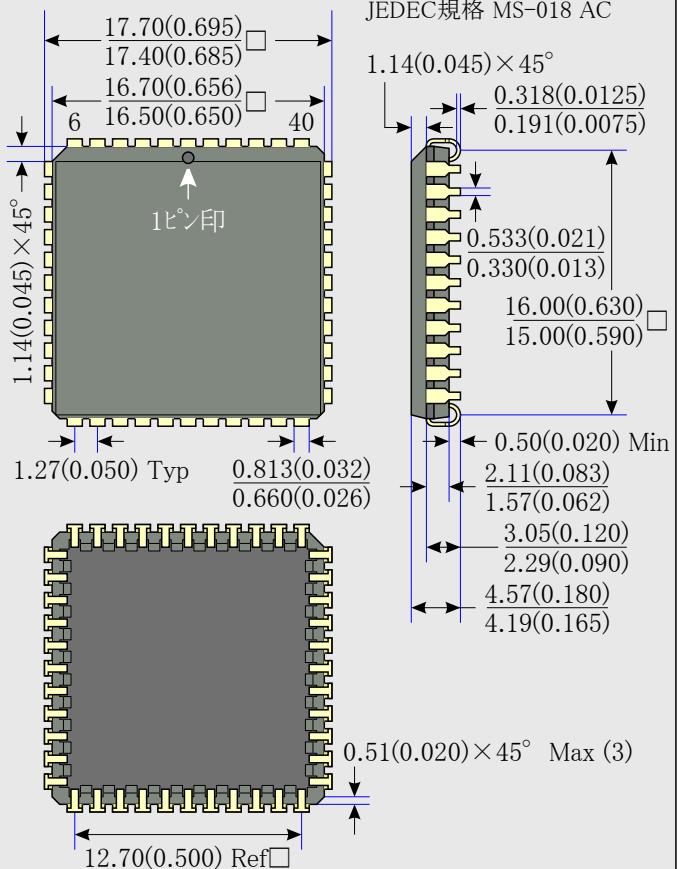

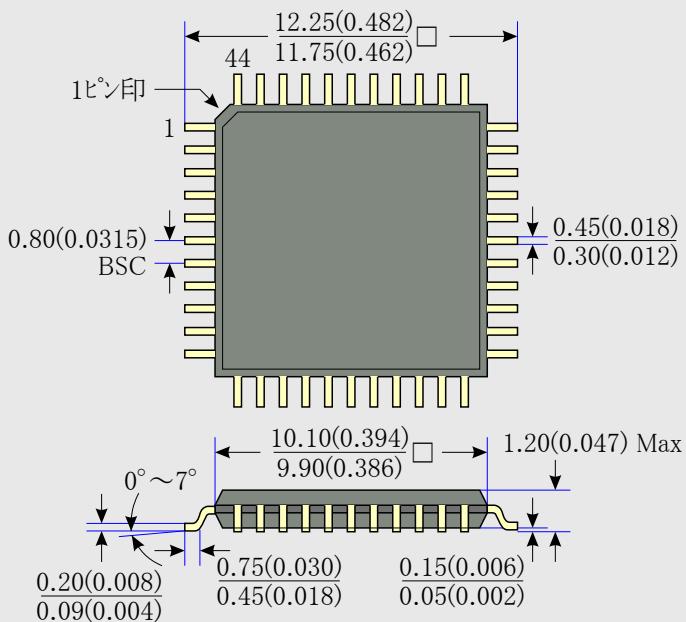

- 40ピンPDIP、44ピンPLCC, TQFP

- 動作電圧

- 2.7~6.0V (AT90S4414-4, AT90S8515-4)

- 4.0~6.0V (AT90S4414-8, AT90S8515-8)

- 動作速度

- 0~4MHz (AT90S4414-4, AT90S8515-4)

- 0~8MHz (AT90S4414-8, AT90S8515-8)

## ピン配置

8ビット AVR®

マイクロコントローラ

実装書き換え可能な

4K/8Kバイト

フラッシュメモリ内蔵

AT90S4414

AT90S8515

本製品での新規設計は推奨されません。

ATmega8515をお使いください。

本書は一般の方々の便宜のため有志によって作成されたもので、Atmel社とは無関係であることを御承知ください。しおりの[はじめに]での内容にご注意ください。

Rev. 0841E-04/99, 0841EJ15-08/22

Rev. 0841G-09/01, 0841GJ19-08/22

## 概要

AT90S4414/8515はAVR RISC構造の低消費CMOS 8ビットマイクロコントローラです。1周期で実行する強力な命令はMHzあたり1 MIPSにも達し、実行速度対電力消費の最適化が容易に行えます。

AVRは32個の汎用レジスタと豊富な命令群を兼ね備えます。32個の全レジスタはALU(Arithmetic Logic Unit)に直結され、レジスタ間命令は1クロック周期で実行されます。AVR構造は現状のCISC型マイクロコントローラに対して最大10倍の単位処理量向上効果があります。

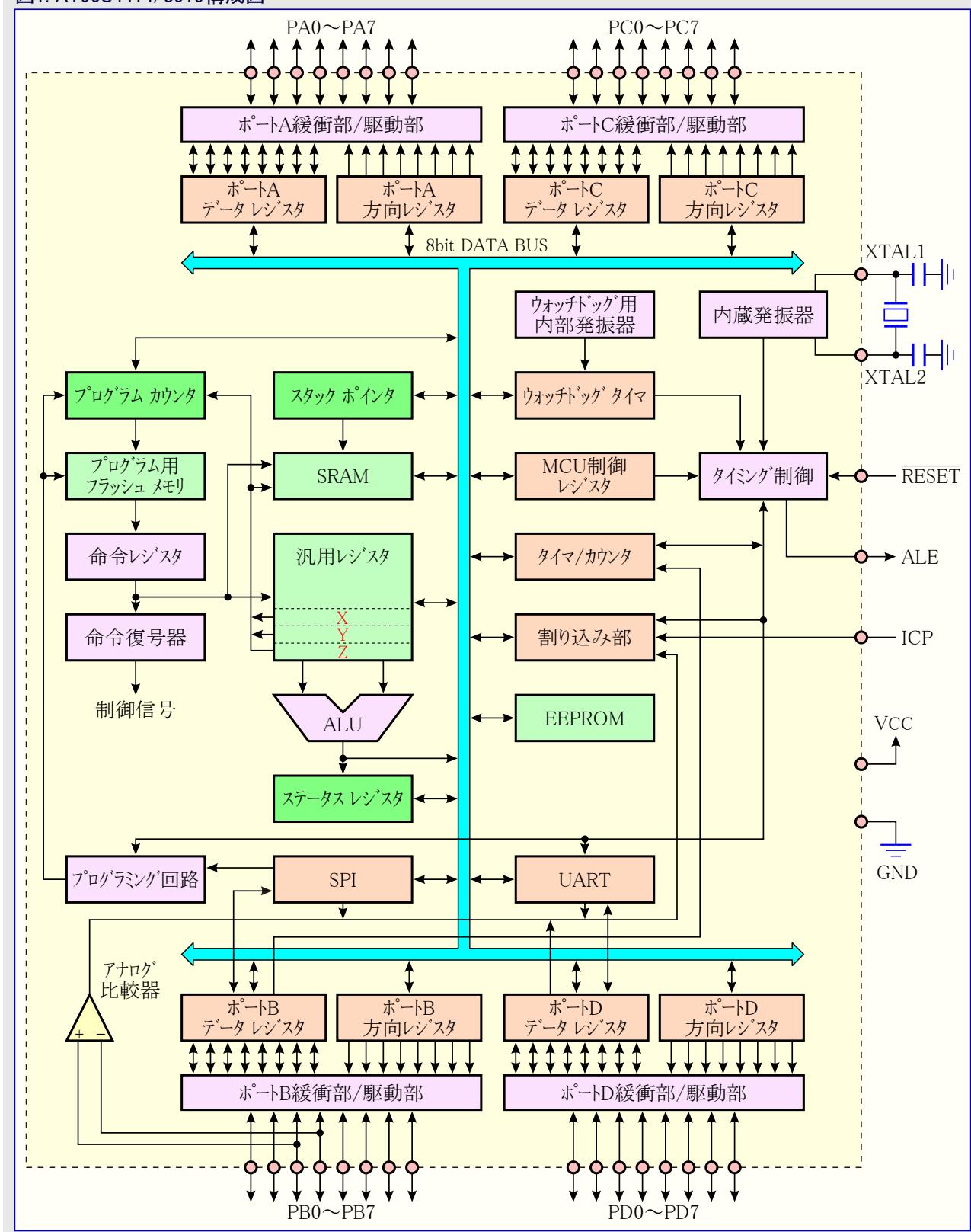

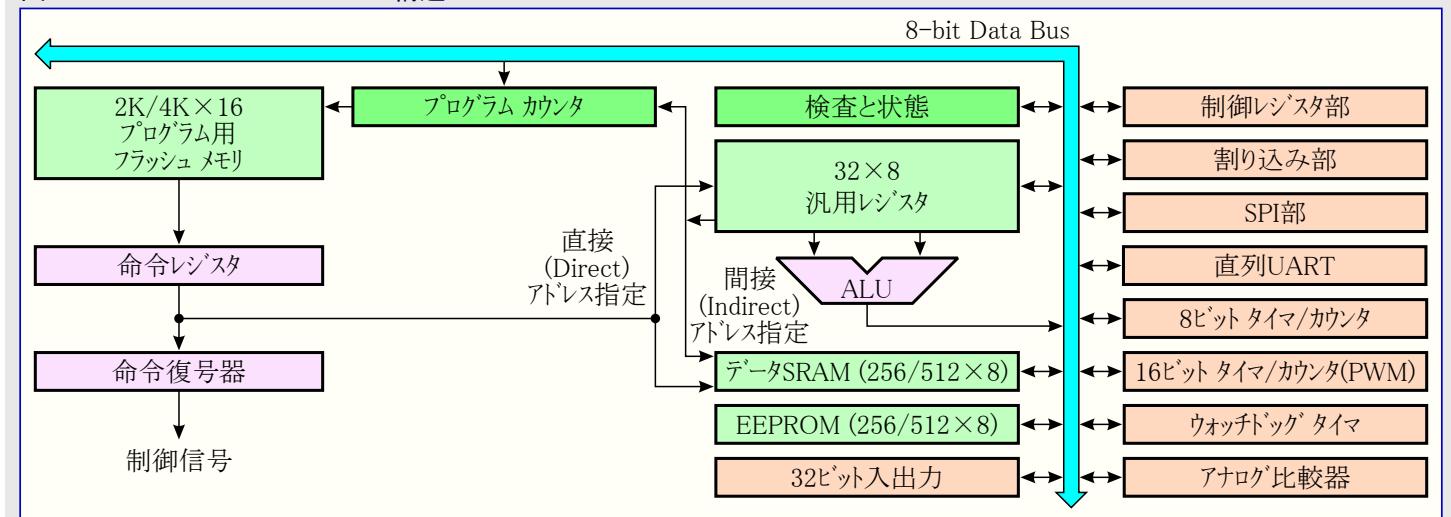

図1. AT90S4414/8515構成図

AT90S4414/8515は、4K/8Kバイトの実装書き換え可能なフラッシュメモリ、256/512バイトのEEPROM、256/512バイトのSRAM、32ビットの汎用入出力、32個の汎用レジスタ、比較動作を含む柔軟なタイマ/カウンタ、内部及び外部割り込み、設定変更可能な直列UART、設定変更可能な内部発振器付きウォッチドッグタイマ、SPI直列ポート、ソフトウェアで選べる2つの低消費動作機能を提供します。アイドル動作では動作を停止しますが、SRAM、タイマ/カウンタ、SPIポート、割り込み機能は有効で、動作を継続します。パワーダウン動作ではレジスタの内容は保護されますが、発振器が停止するため、以降のハードウェアリセットか外部割り込みまで他の全機能を無効にします。

本デバイスはAtmelの高密度不揮発性メモリ技術を使って製造されています。内蔵の実装書き換え(ISP)可能なフラッシュメモリはプログラムメモリに使え、規定の不揮発性メモリ書き込み器かSPI直列インターフェース経由によって再書き込みができます。モリシックチップ上の実装書き換え可能なフラッシュメモリと拡張された8ビットRISC型CPUの組み合わせによるAT90S4414/8515は、多くの組み込み制御の応用に対して高度な柔軟性と対費用効果をもたらす強力なマイクロコントローラです。

AT90S4414/8515 AVRはCコンパイラ、マクロアセンブラー、デバッガ、シミュレータ、インサーキットエミュレータ、評価キットを含む完全なプログラム及びシステム開発ツールで支援されます。

## AT90S4414とAT90S8515の違い

AT90S4414は実装書き換え可能なフラッシュメモリが4Kバイト、EEPROMが256バイト、内蔵SRAMが256バイトです。AT90S8515は実装書き換え可能なフラッシュメモリが8Kバイト、EEPROMが512バイト、内蔵SRAMが512バイトです。

表1. メモリ容量対比表

| デバイス名     | フラッシュメモリ | EEPROM | SRAM   |

|-----------|----------|--------|--------|

| AT90S4414 | 4Kバイト    | 256バイト | 256バイト |

| AT90S8515 | 8Kバイト    | 512バイト | 512バイト |

## ピン概要

### VCC

電源ピン。

### GND

接地ピン。

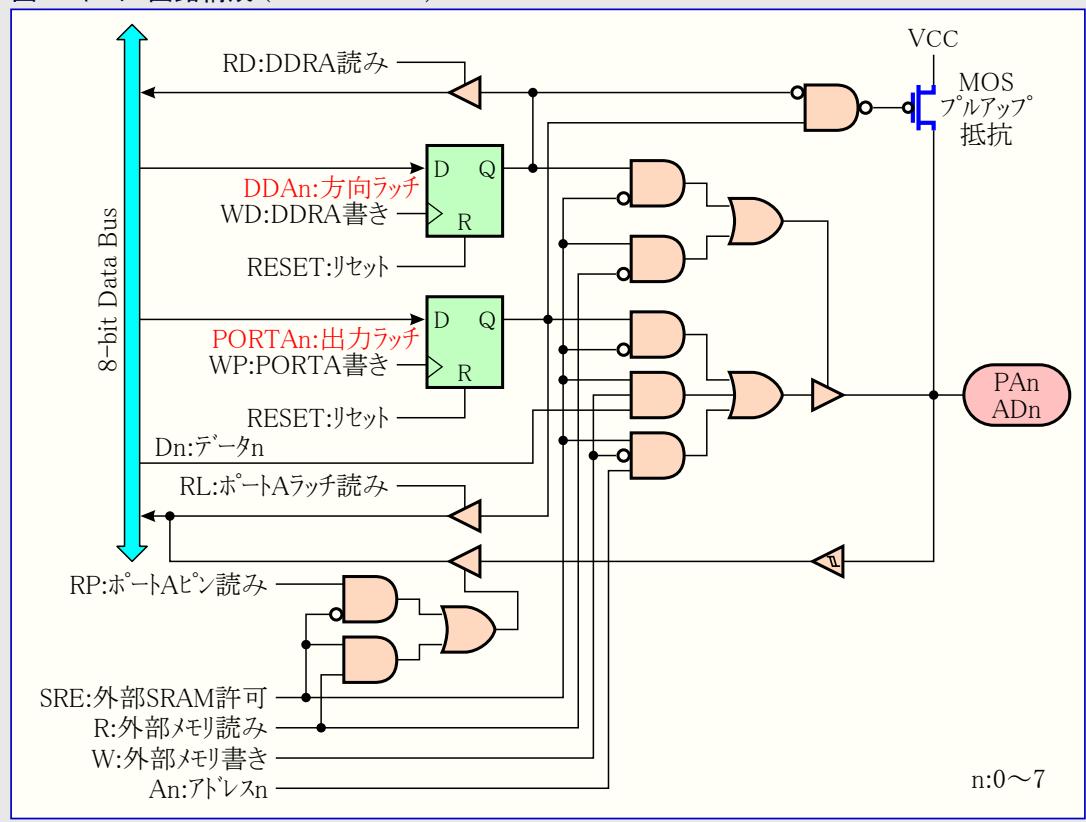

### PA7～PA0 (ポートA)

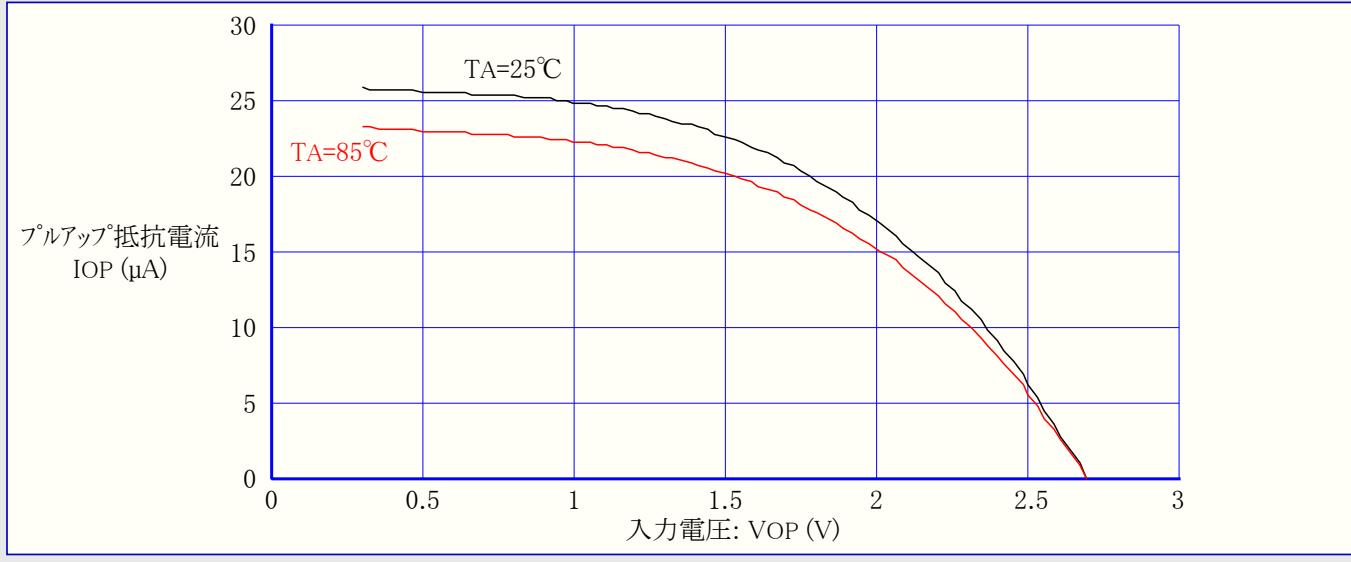

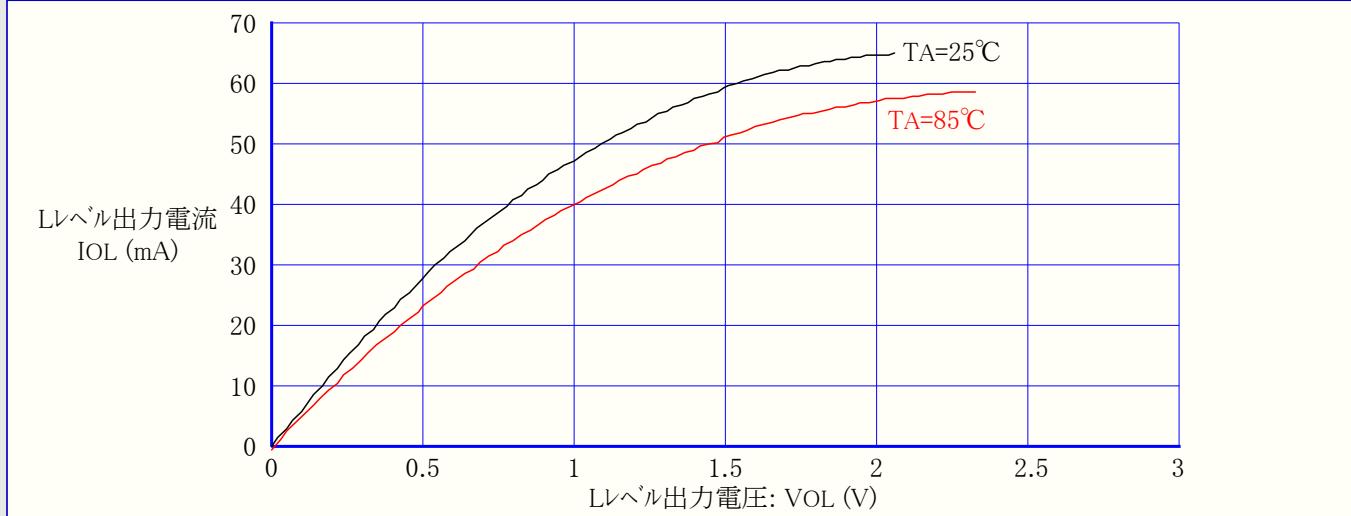

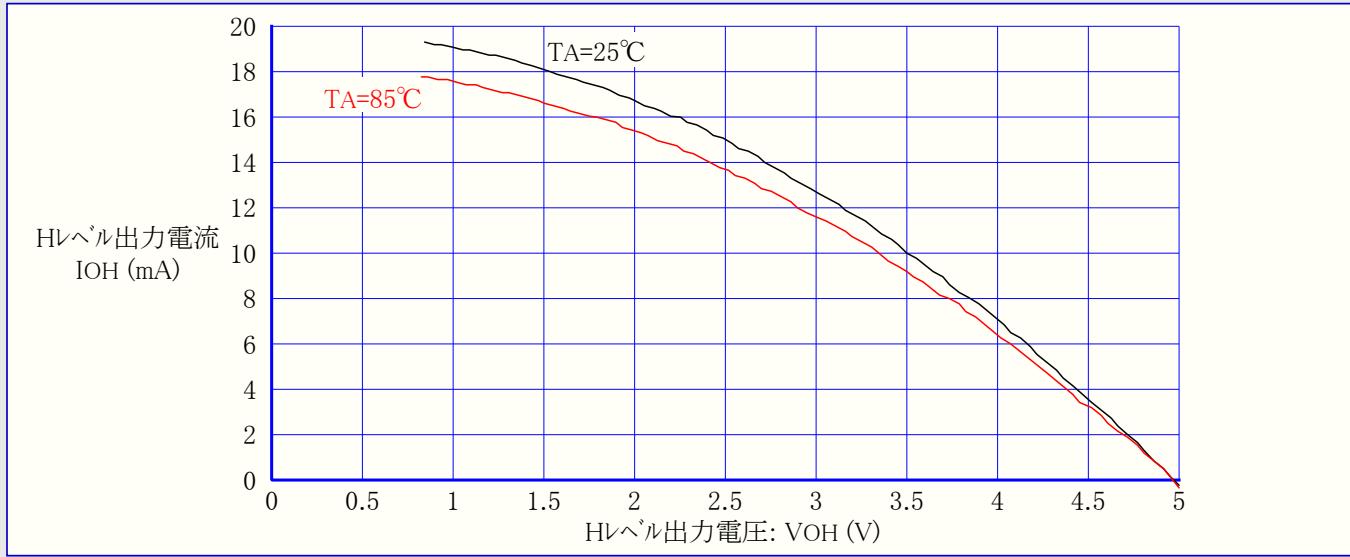

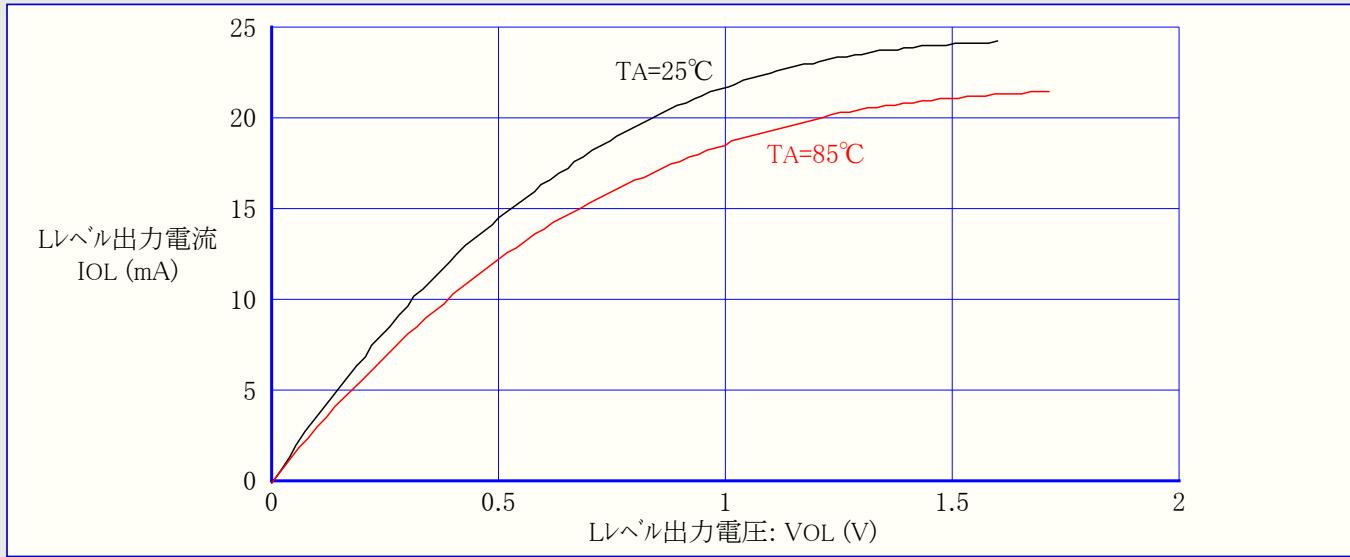

ポートAは8ビットの双方向入出力ポートです。ポートピンは(ピット毎に選ばれる)内蔵プルアップ抵抗を提供できます。ポートA出力緩衝部は20mAの吸い込み電流を流せ、LED表示器を直接駆動できます。PA0～7ピンが入力として使われ、外部的にLowへ引き込まれるとき、内蔵プルアップ抵抗が有効の場合、吐き出し電流が流れます。リセット条件が有効になるとき、クロックが動作していなくても、ポートAピンはHi-Zになります。

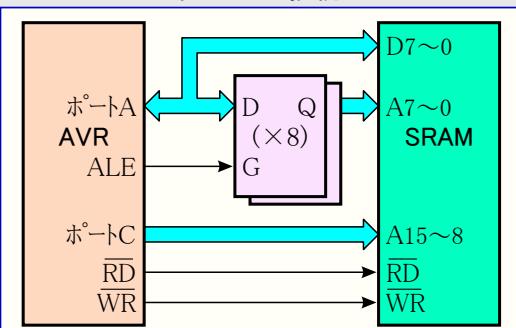

外部SRAM使用時、ポートAは切り替え使用されるアドレス/データの入出力として取り扱います。

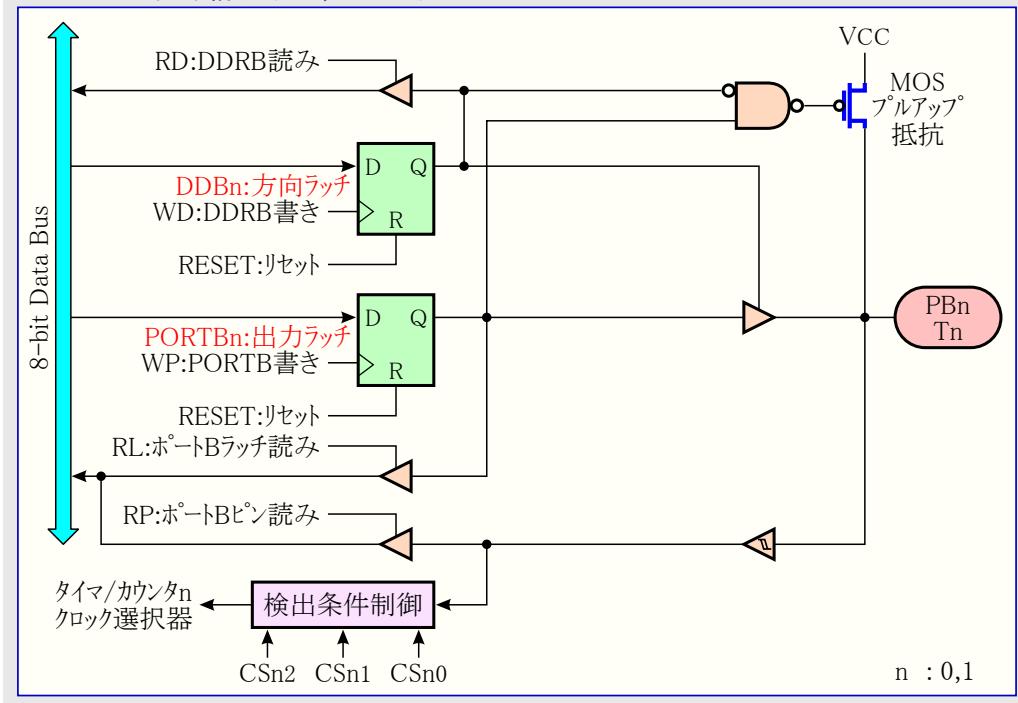

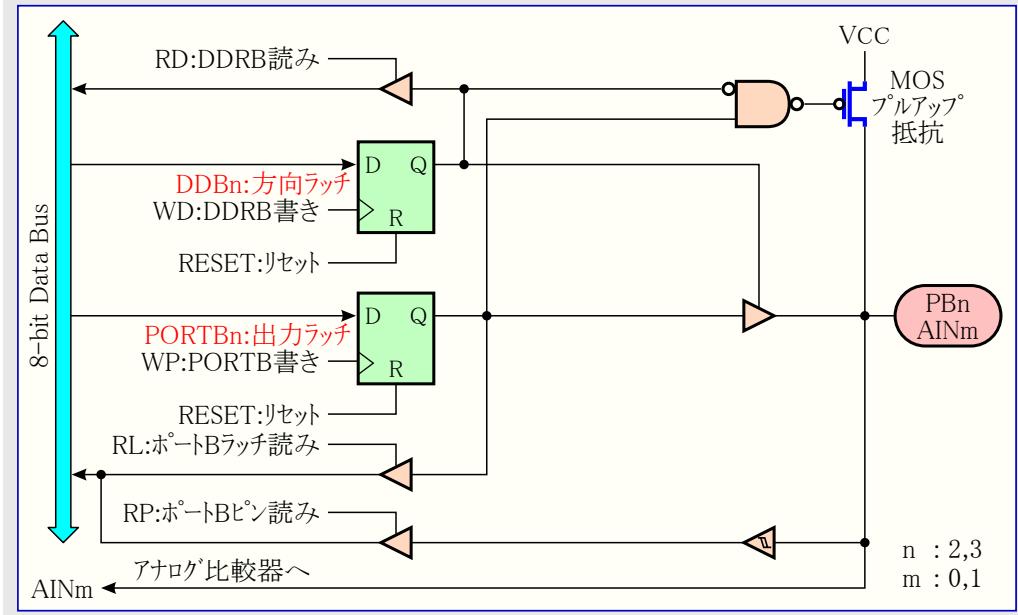

### PB7～PB0 (ポートB)

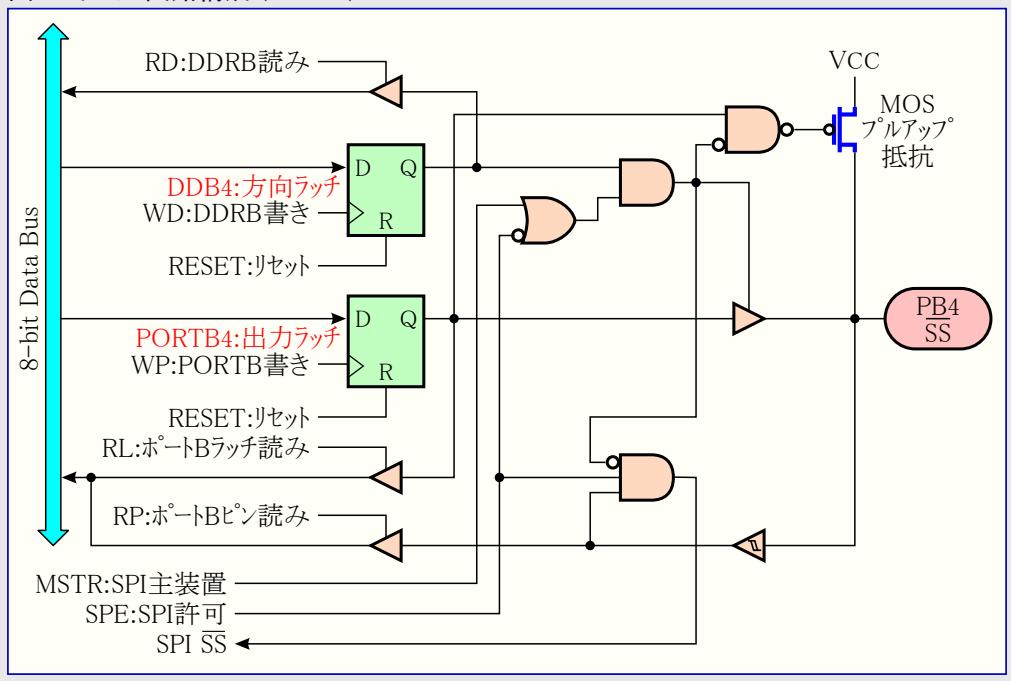

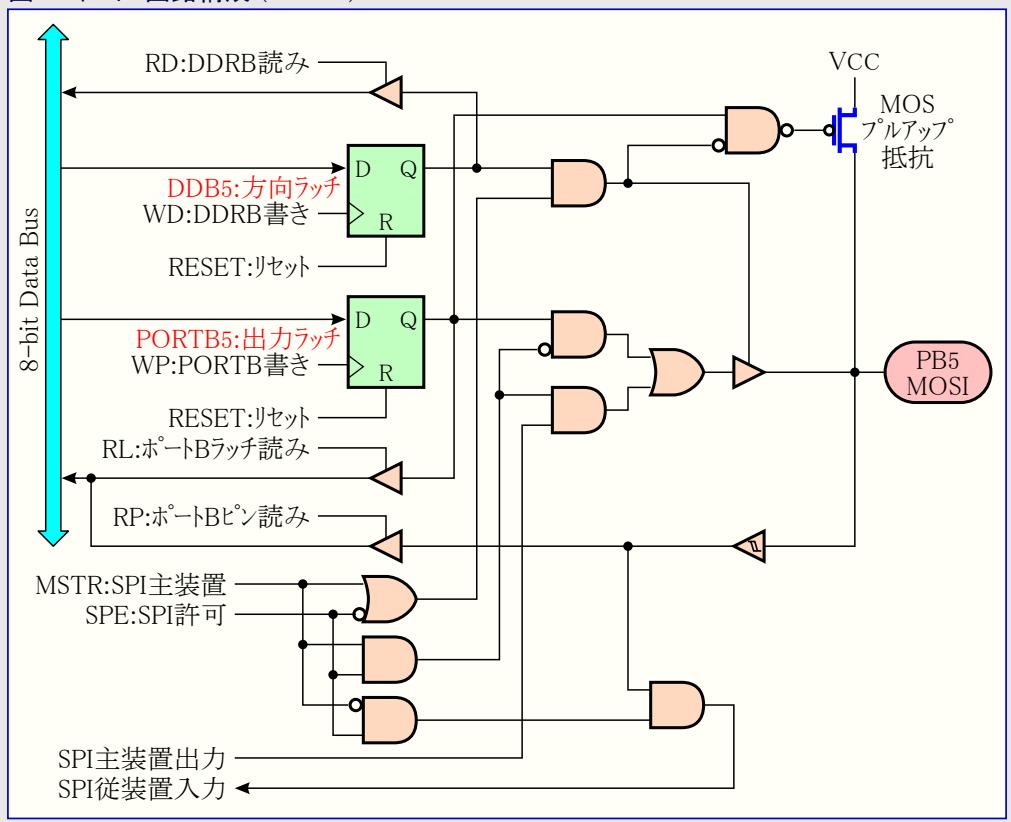

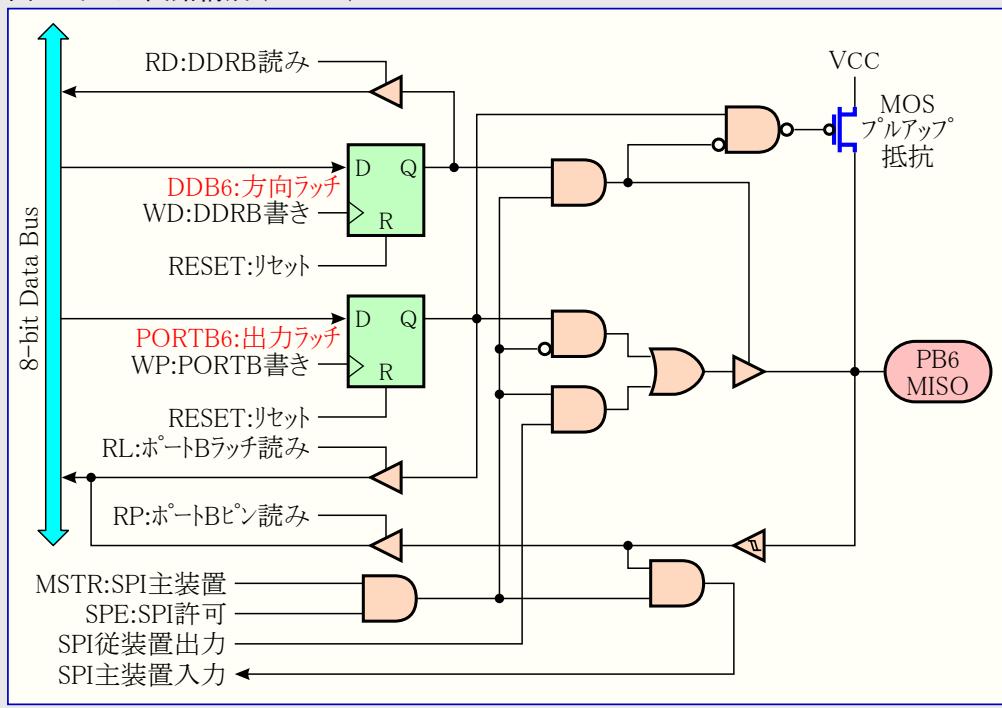

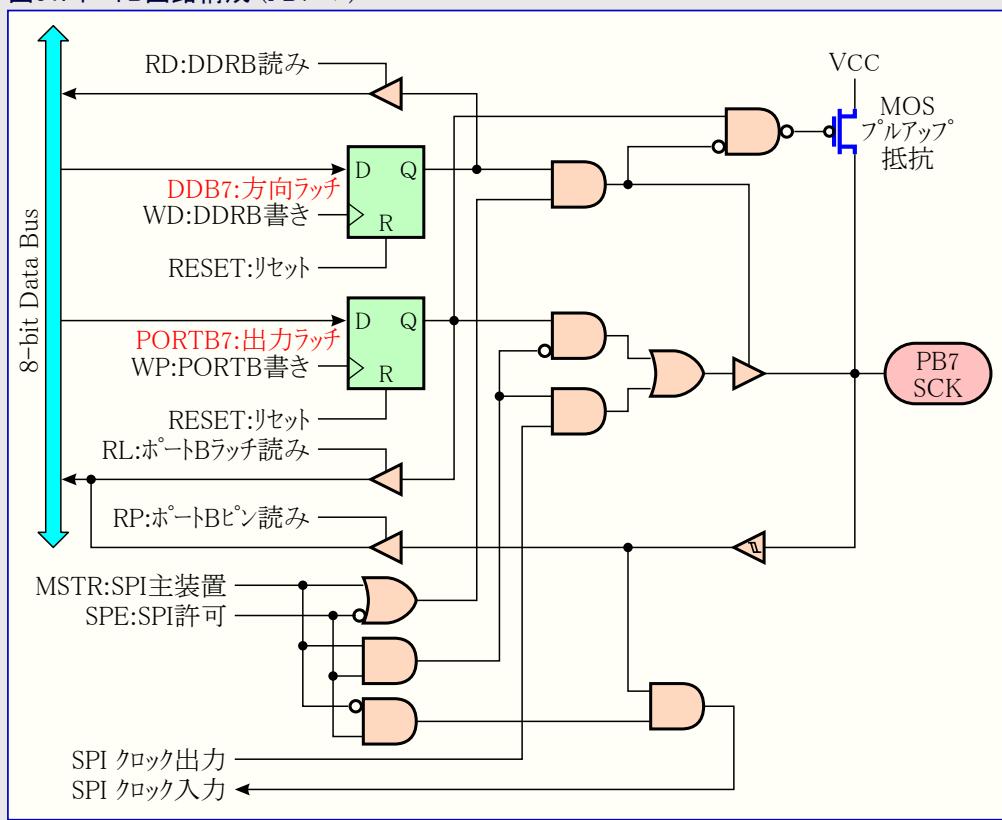

ポートBは内蔵プルアップ抵抗付き8ビット双方向入出力ポートです。ポートBの出力緩衝部は20mAの吸い込み電流を流せます。入力のとき、プルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートBピンには吐き出し電流が流れます。リセット条件が有効になるとき、クロックが動作していなくても、ポートBピンはHi-Zになります。

ポートBは44頁で示されるAT90S4414/8515の各特殊機能としても扱います。

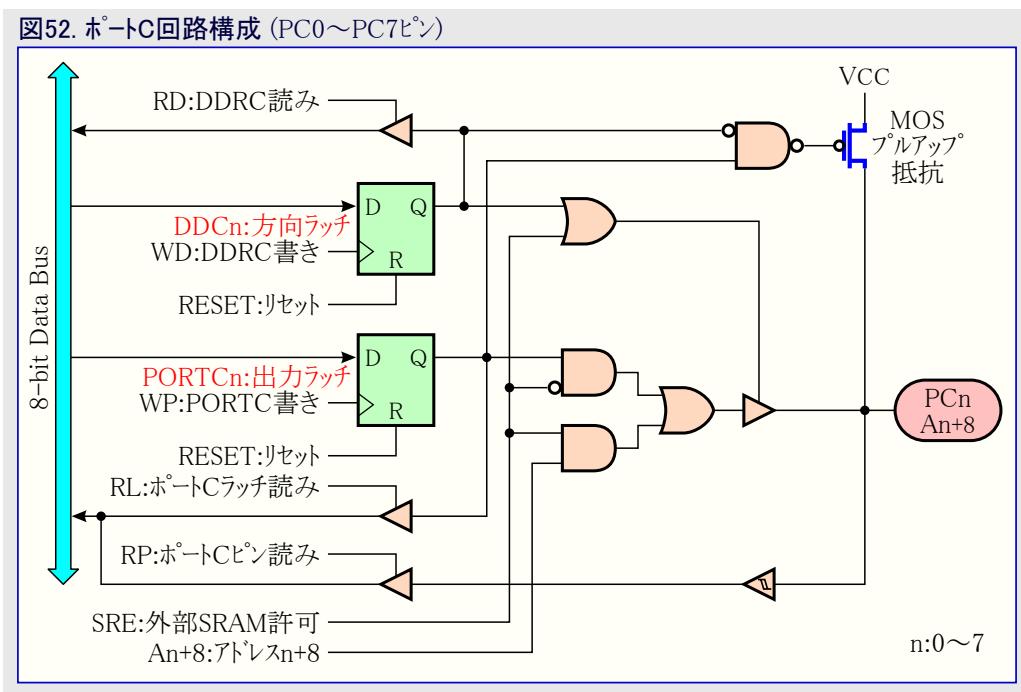

### PC7～PC0 (ポートC)

ポートCは内蔵プルアップ抵抗付きの8ビットの双方向入出力ポートです。ポートCの出力緩衝部は20mAの吸い込み電流を流せます。入力のとき、プルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートCピンには吐き出し電流が流れます。リセット条件が有効になるとき、クロックが動作していなくても、ポートCピンはHi-Zになります。

外部SRAM使用時、ポートCはアドレス出力としても扱います。

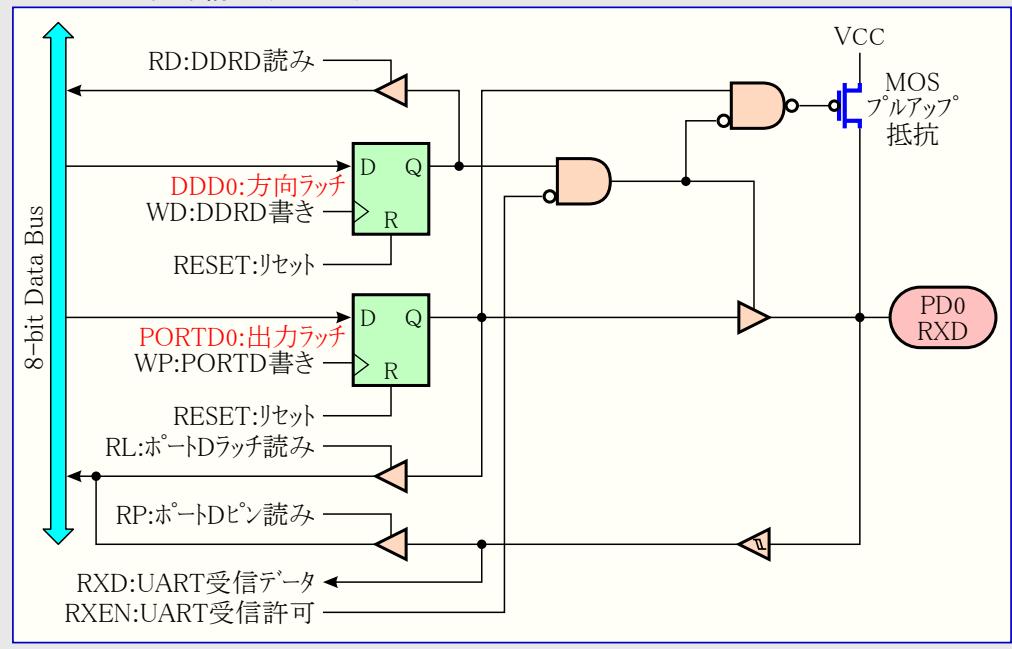

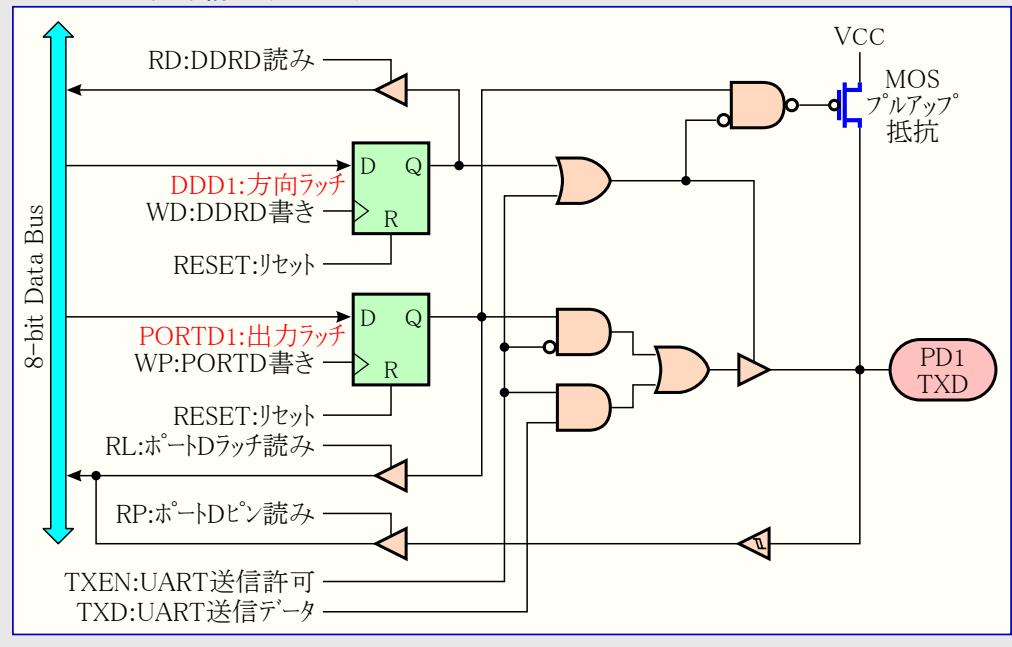

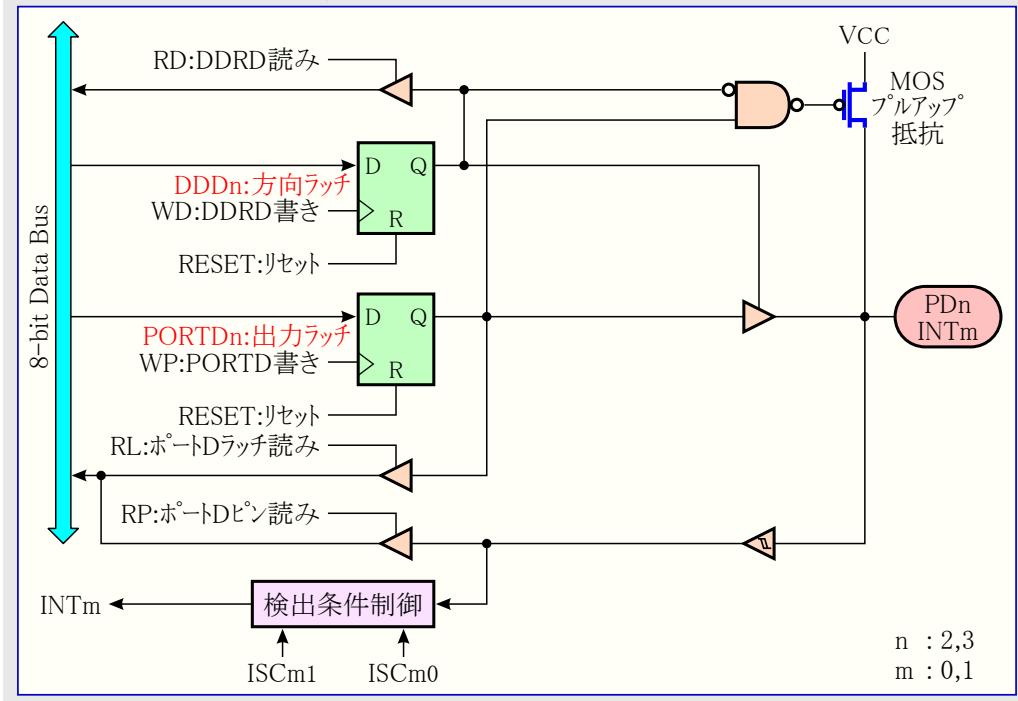

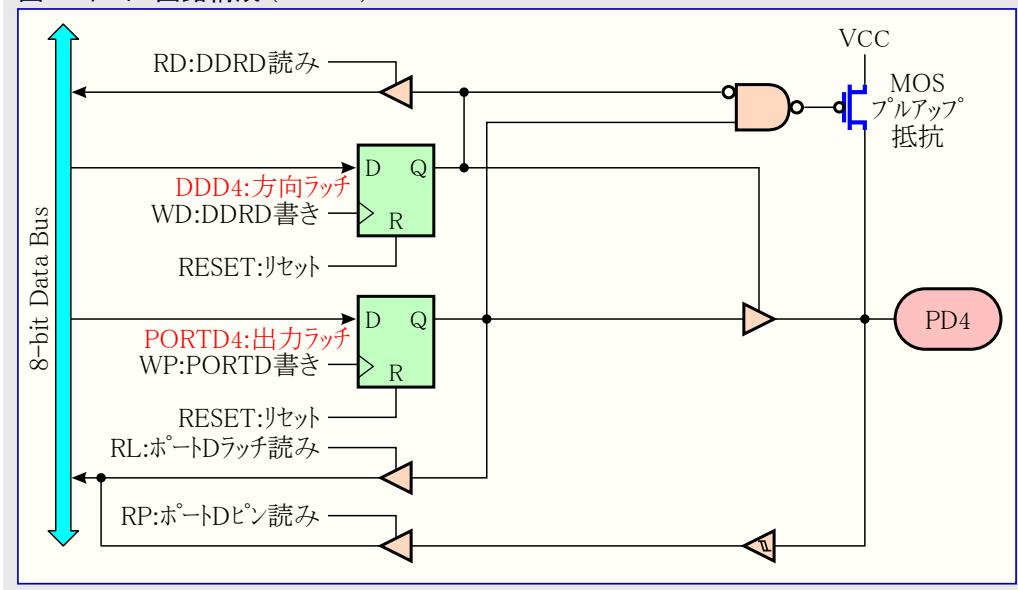

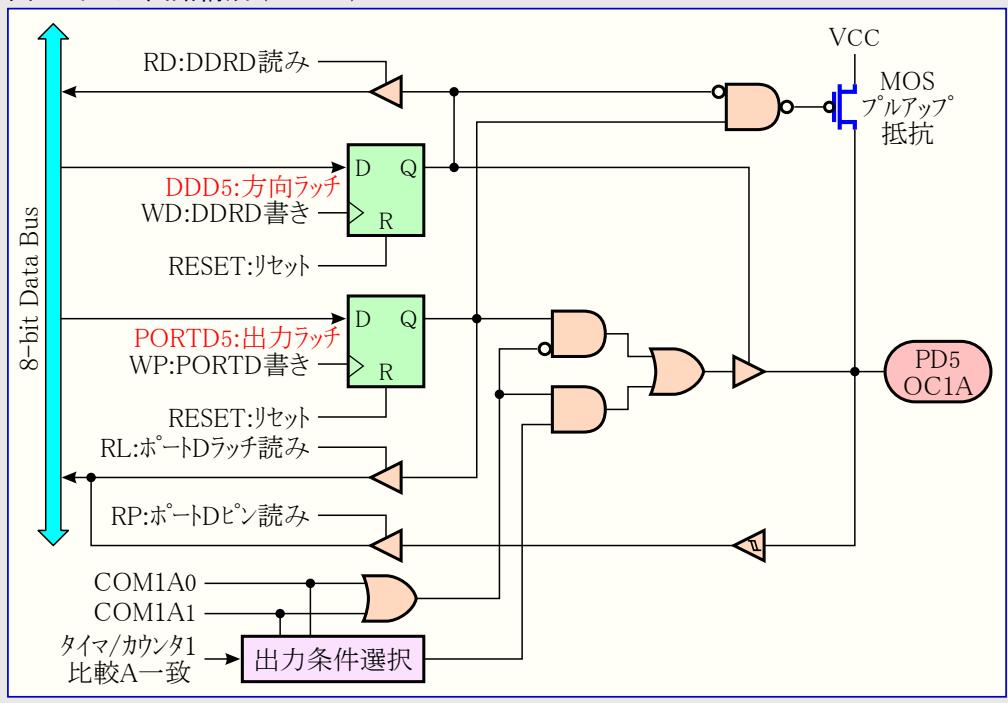

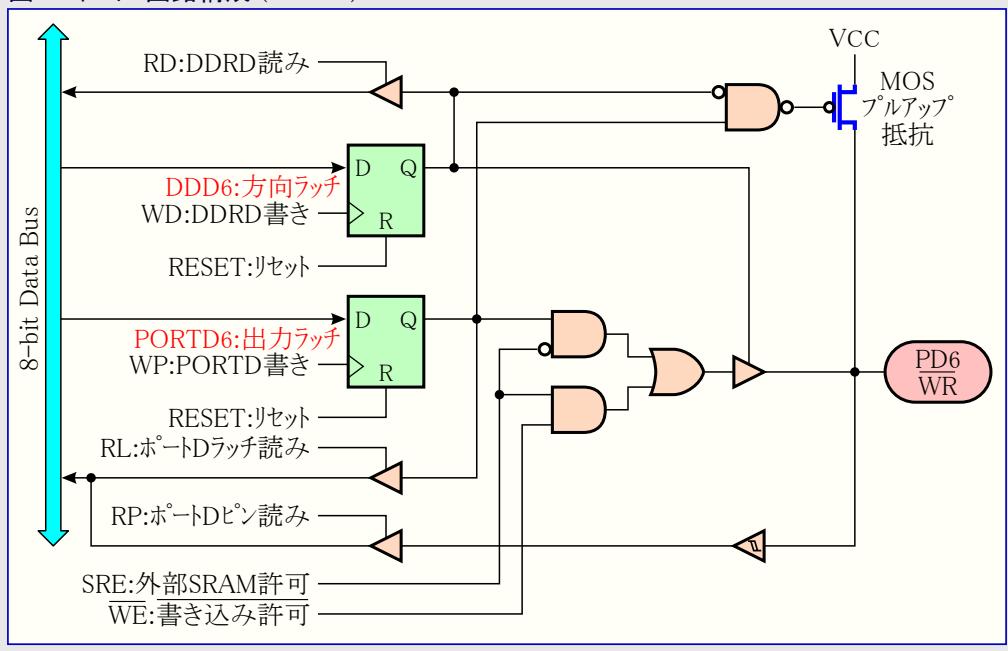

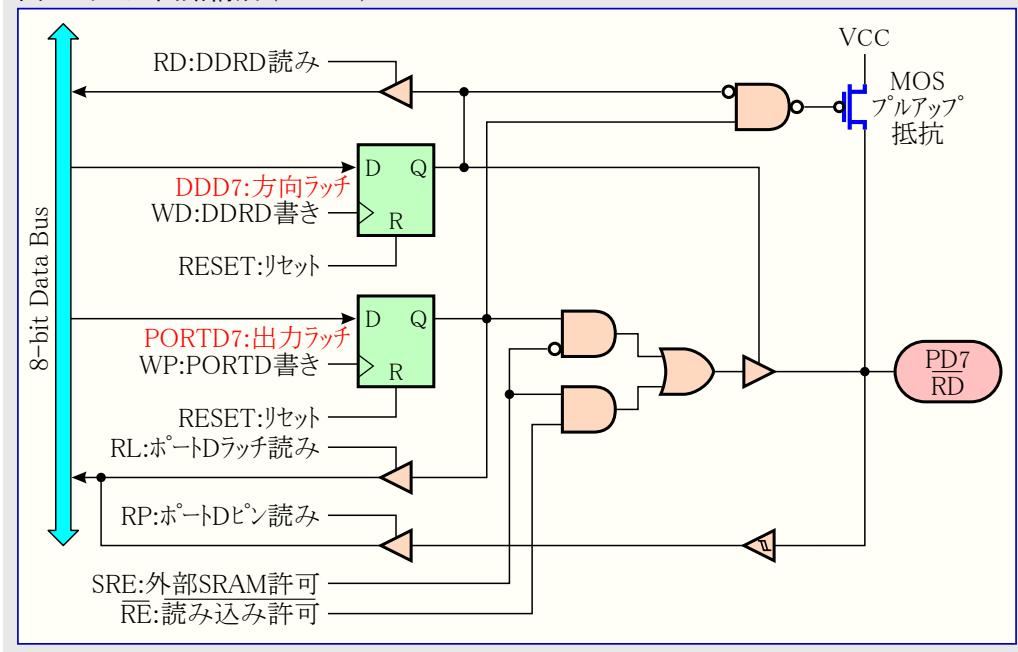

### PD7～PD0 (ポートD)

ポートDは内蔵プルアップ抵抗付きの8ビットの双方向入出力ポートです。ポートDの出力緩衝部は20mAの吸い込み電流を流せます。入力のとき、プルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートDピンには吐き出し電流が流れます。リセット条件が有効になるとき、クロックが動作していなくても、ポートDピンはHi-Zになります。

ポートDは51頁で示されるAT90S4414/8515の各特殊機能としても扱います。

### RESET

リセット入力。このピンの50nsより長いLowレベルは、例えクロックが動作していなくてもリセットを発生します。短すぎるパルスはリセットの生成が保証されません。

## XTAL1

発振器用反転増幅器の入力、内部クロック動作回路の入力。

## XTAL2

発振器用反転増幅器の出力。

## ICP

ICPはタイマ/カウンタ1捕獲機能用(起動)入力ピンです。

## OC1B

OC1Bはタイマ/カウンタ1比較B出力機能用出力ピンです。

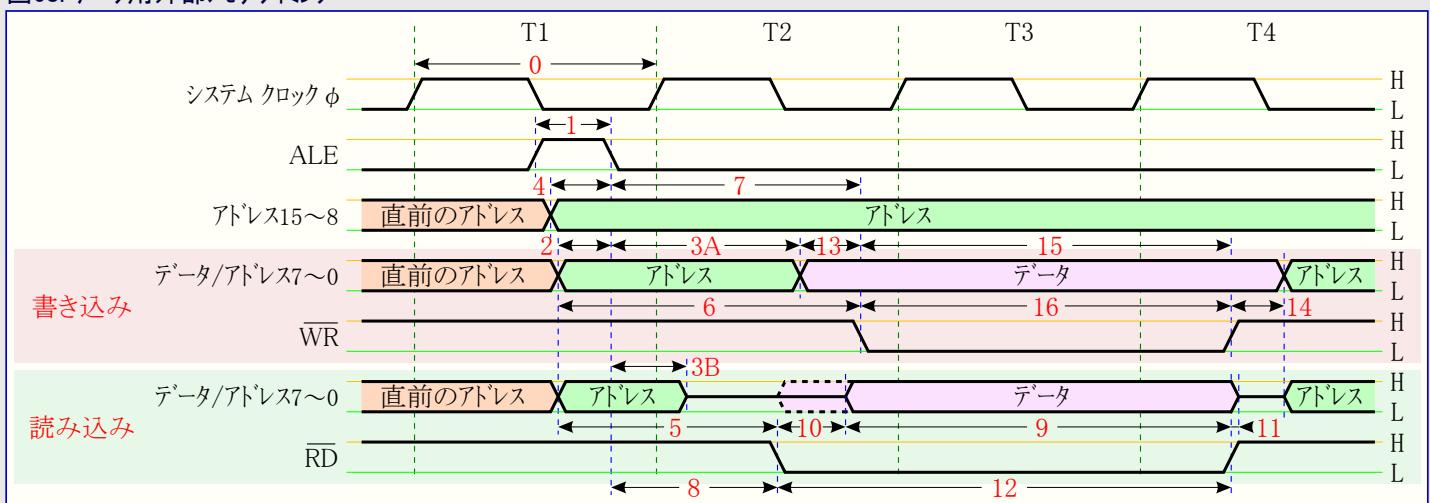

## ALE

ALEは外部メモリが許可されるときに使われるアドレス ラッチ許可信号です。このALEストローブは第1アクセス周期(High)間にアドレス ラッチ内へ下位側アドレス(8ビット)をラッチするために使われ、第2アクセス周期(Low)間、AD7～0ピンはデータ用に使われます。

## クロック発振器

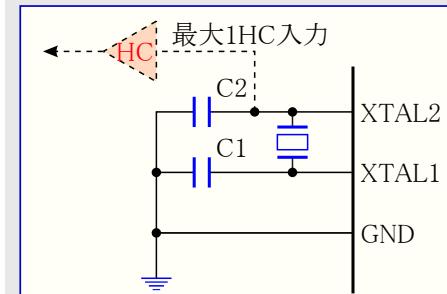

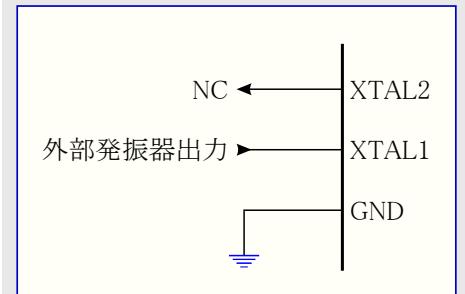

### クリスタル用発振器

XTAL1とXTAL2は、図2.に示される内蔵発振器として使える反転増幅器の各々入力と出力です。クリスタル発振子、セラミック振動子のどちらでも使えます。外部クロック信号でデバイスを駆動するには、図3.で示されるようにXTAL1が駆動され、XTAL2は未接続のままですべきです。

**注:** 内蔵発振器の出力で外部デバイスを駆動する場合、図で示されるようにHC緩衝器が接続されるべきです。

図2. 発振子接続図

図3. 外部クロック接続図

## 構造概要

高速レジスタ ファイルの概念は、1クロック周期アクセス時間の32個の8ビット長汎用レジスタを含みます。これは1クロック周期中に1つのALU(Arithmetic Logic Unit)命令が実行されることを意味します。1クロック周期で2つのオペラントはレジスタ ファイルから出力され、命令が実行され、その結果がレジスタ ファイルに書き戻されます。

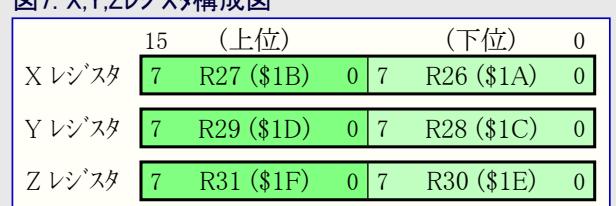

32個中の6つのレジスタはデータ空間についてアドレス計算が効率的に行える、3つの16ビット長間接アドレス ポインタとして使えます。3つのアドレス ポインタの1つは定数表参照用アドレス ポインタとしても使われます。これらの付加機能レジスタは16ビット長のXレジスタ、Yレジスタ、Zレジスタです。

ALUはレジスタ間、レジスタと定数間の算術及び論理操作を行います。単一レジスタ操作も同様にALUで実行されます。図4.はAT90S 4414/8515 AVR RISC構造を示します。

図4. AT90S4414/8515 AVR RISC構造

付加的なレジスタ操作として、通常のメモリアドレス指定をレジスタファイルにも使えます。実際にはレジスタファイルがデータ空間の最下位32バイト(\$00～\$1F)に割り当てられ、通常のメモリ位置としてのアクセスができます。実際にはレジスタファイルがデータ空間の最下位32バイト(\$00～\$1F)に割り当てられ、通常のメモリ位置としてのアクセスができます。

I/Oメモリ空間は、制御レジスタ、タイマ/カウンタ、その他I/O機能など、CPU周辺機能用の64アドレスを含みます。I/Oメモリは直接またはレジスタファイルに後続するデータ空間位置\$20～\$5Fとしてアクセスできます。

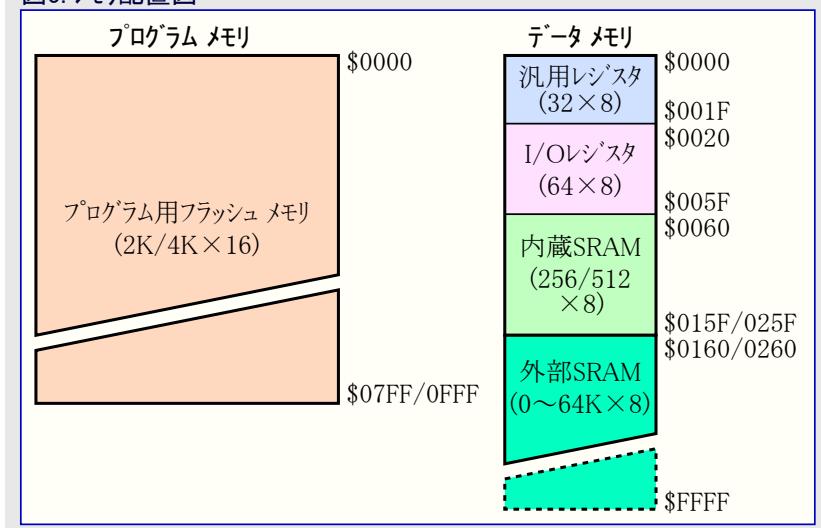

AVRのメモリとバスはプログラム用とデータ用に各々分離されたハーバード構造で構成されています。プログラムメモリは2段のパイプラインでアクセスされます。1命令の実行中に、次の命令をプログラムメモリから事前取得します。この概念は全てのクロック周期で命令が実行されるのを可能にします。プログラムメモリは実装書き換え可能なフラッシュメモリです。

プログラムカウンタ(PC)相対の無条件分岐(RJMP)命令と呼び出し(RCALL)命令で2K/4Kアドレス空間全てがアクセスされます。AVRの多くの命令は16ビット1語の形式です。全てのプログラムメモリのアドレスに16または32ビット命令を配置できます。

割り込みやサブルーチン呼び出しでの戻りアドレスを示すプログラムカウンタ(PC)はスタックに保存されます。スタックは一般的なデータ用SRAMに配置され、スタック容量はSRAM容量とSRAM使用量でのみ制限されます。プログラムではリセット時の初期化ルーチンで(サブルーチンや割り込みが実行される前に)、スタックポインタ(SP)を初期化しなければなりません。16ビットのSPはI/O空間にあり、読み書き可能です。

256/512バイトのデータSRAMとレジスタファイルやI/OレジスタはAVR構造で支援される5つの異なるアドレス指定種別で容易にアクセスできます。

AVR構造に於けるメモリ空間は全て直線的な普通のメモリ配置です。

柔軟な割り込み部にはI/O空間の各制御レジスタとステータスレジスタ(SREG)の全割り込み許可(I)ビットがあります。全ての割り込み要因はプログラムメモリの先頭に割り込みベクタ表として、個別の割り込みベクタがあります。各割り込みは、この割り込みベクタ表の位置に従った優先順です。下位側割り込みベクタアドレスが高い優先順位です。

図5. メモリ配置図

## 汎用レジスタファイル

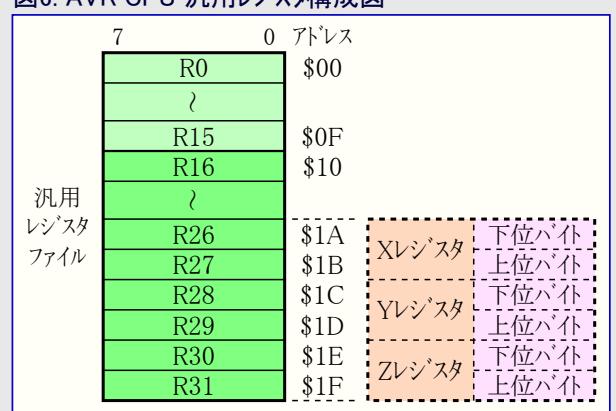

図6.は32個の汎用レジスタの構成を示します。

全てのレジスタに対するレジスタ操作命令はレジスタ直接指定ができ、1周期でアクセスします。SBCI, SUBI, CPI, ANDI, ORIの5つの算術、論理定数演算命令と、定数をレジスタに設定するLDI命令だけは例外です。これらの命令はレジスタファイル後半のR16～R31に対してだけ適用されます。通常のSBC, SUB, CP, AND, ORや他の全てのレジスタ間、単一レジスタ操作命令はレジスタファイルの全レジスタに適用されます。

図6.で示されるように、各レジスタはデータメモリ領域の先頭からの32アドレスに配置されています。レジスタファイルは物理的にSRAMのような配置構成ではなく、この特別な構成のため、X, Y, Zレジスタを指標とする任意のレジスタ指定のような、非常に柔軟なアクセスができます。

図6. AVR CPU 汎用レジスタ構成図

## Xレジスタ, Yレジスタ, Zレジスタ

レジスタR26～R31には通常の汎用用途以外にいくつかの付加機能があります。これらのレジスタはデータ空間の間接アドレス指定ポインタにもなります。この3つの間接アドレス用レジスタX, Y, Zは図7.で定義されます。

これらのアドレスレジスタは定数変位付き、自動増加/減少付きのアドレス指定が行えます(これらの概要は個別命令を参照してください)。

図7. X, Y, Zレジスタ構成図

## ALU (Arithmetic Logic Unit)

高性能なAVRのALUは、32個全ての汎用レジスタに直接接続され、動作します。レジスタファイル内のレジスタ間ALU操作は、1クロック周期内で実行されます。ALU操作は、算術演算、論理演算、ビット操作の3つの主な種類に大別されます。

## 実装書き換え(ISP: In-System Program)可能なプログラム用フラッシュメモリ

AT90S4414/8515にはプログラム用に実装書き換え可能な4K/8Kバイトのフラッシュメモリが内蔵されています。全ての命令が16または32ビット語のため、フラッシュメモリは2K/4K×16ビットとして構成されています。フラッシュメモリは少なくとも1000回再書き込みの耐久性があります。AT90S4414/8515のプログラムカウンタ(PC)は11/12ビットで、プログラムメモリ内の2048/4096アドレスを指定します。

フラッシュメモリ書き込みの詳細説明については[56頁](#)を参照してください。

各アドレス指定種別については[7頁](#)を参照してください。

## データ用EEPROMメモリ

AT90S4414/8515には256/512バイトのデータ用EEPROMがあります。これは1バイト単位で読み書きできる独立データ空間として構成されます。EEPROMは少なくとも100,000回書き換えの耐久性があります。EEPROMとCPU間のアクセスは[29頁](#)のEEPROMアドレスレジスタ、EEPROMデータレジスタ、EEPROM制御レジスタで詳細に説明されます。

SPI書き込み(直列プログラミング)の詳細説明については[62頁](#)を参照してください。

## 内蔵SRAMと外部SRAM

図8はAT90S4414/8515のデータメモリ構成を示します。

下位側352/608のデータメモリ位置は汎用レジスタファイル、I/Oレジスタ、データ用内蔵SRAMを指定します。最初の96位置はレジスタファイルとI/Oレジスタ、次の256/512位置がデータ用内蔵SRAMを指定します。任意の外部データ用SRAMが同じSRAMメモリ空間内に配置できます。このSRAMはSRAM容量に依存し、64K-1までの内蔵SRAMに続く位置を占有します。

アドレスが内蔵データSRAMを越えるデータメモリ空間をアクセスするとき、外部データSRAMは内蔵データSRAMアクセス時と同じ命令を使ってアクセスされます。内部データ空間がアクセスされるとき、読み書きストローブピン(RDとWR)はそのアクセス周期中全てで無効(High)です。外部SRAM動作はMCU制御レジスタ(MCUCR)の外部SRAM許可(SRE)ビットの設定(1)によって許可されます。詳細については[18頁](#)を参照してください。

外部SRAMのアクセスは内蔵SRAMのアクセスに比べてバイト毎に1つの付加クロック周期を必要とします。これはLD, ST, LDS, STS, PUSH, POP命令が1つの付加クロック周期を必要とする意味します。スタックが外部SRAMに配置されると、割り込み、サブルーチン呼び出し、その復帰は2バイトのプログラムカウンタがpush/popされるため、2クロック周期の追加が必要になります。外部SRAMインターフェースが待ち状態付きで使われると、バイト毎に2つの付加クロック周期が使われます。これは次の影響があります。データ転送命令は2つの追加クロック周期が必要になり、然るに、割り込み、サブルーチン呼び出し、その復帰は命令一式手引書で示されるより4クロック周期多く必要です。

[直接、間接、変位付き間接、事前減少付き間接、事後増加付き間接](#)の5つのアドレス指定種別が、データメモリ空間を網羅します。レジスタファイル内のレジスタR26～R31が間接アドレス指定時のポインタレジスタです。

直接アドレス指定は全てのデータアドレス空間に届きます。

変位付き間接アドレス指定はYまたはZレジスタで与えられる基準アドレスから届く63アドレス位置が特徴です。

事前減少付き間接、事後増加付き間接アドレス指定を使う時はアドレスレジスタX,YまたはZが使われ、自動的に減少または増加されます。

AT90S4414/8515の32個の汎用レジスタ、64個のI/Oレジスタ、256/512バイトのデータ用内蔵SRAM、任意のデータ用外部SRAMの64Kバイトは、これら全てのアドレス指定種別を通して、全て直接的にアクセス可能です。

各アドレス指定種別の詳細な説明については[次章](#)を参照してください。

図8. データ空間とSRAMの配置

|              |             | アドレス        |

|--------------|-------------|-------------|

| レジスタファイル     | R0          | \$0000      |

|              | R1          | \$0001      |

|              | (           |             |

|              | R30         | \$001E      |

|              | R31         | \$001F      |

| I/Oレジスタ      | \$00        | \$0020      |

| (赤字はI/Oアドレス) | \$01        | \$0021      |

|              | (           |             |

|              | \$3E        | \$005E      |

|              | \$3F        | \$005F      |

| 内蔵SRAM       | \$0060      | \$0060      |

|              | \$0061      | \$0061      |

|              | (           |             |

|              | \$015E/025E | \$015E/025E |

|              | \$015F/025F | \$015F/025F |

| 外部SRAM       | \$0160/0260 | \$0160/0260 |

|              | \$0161/0261 | \$0161/0261 |

|              | (           |             |

|              | \$FFFFE     | \$FFFFE     |

|              | \$FFFFF     | \$FFFFF     |

## プログラム及びデータ空間に対するアドレス指定種別

AT90S4414/8515 AVR RISCマイクロコントローラはプログラムメモリ(フラッシュメモリ)とデータメモリ(SRAM、レジスタファイル、I/Oメモリ)アクセス用に強力で効率的なアドレス指定種別を支援します。本項はAVR構造によって支援される各アドレス指定種別を記述します。図内のOPは命令語の動作符号部を意味します。単純化のため、全ての図がアドレス指定ビットの正確な位置を示すとは限りません。

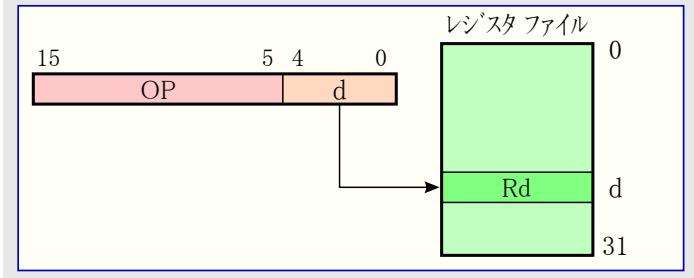

### 単一レジスタ(Rd)直接

図9. 単一レジスタ直接

オペランドはレジスタd(Rd)を示します。

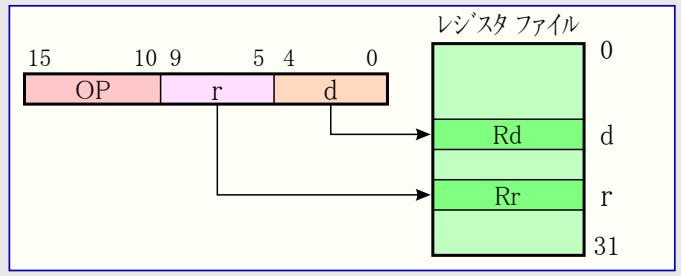

### レジスタ間(Rd, Rr)直接

図10. レジスタ間直接

オペランドはレジスタr(Rr)とd(Rd)を示し、結果はレジスタd(Rd)に格納されます。

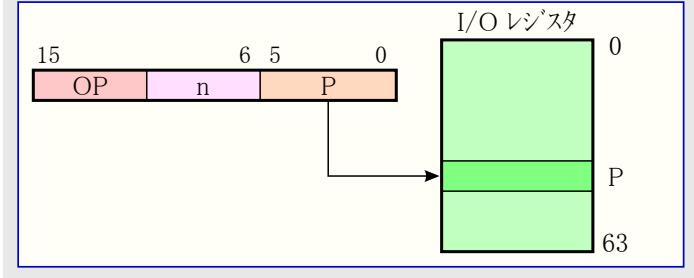

### I/O直接

図11. I/O直接

オペランドはI/OアドレスPと、転送元または転送先となるレジスタn(Rn)を示します。

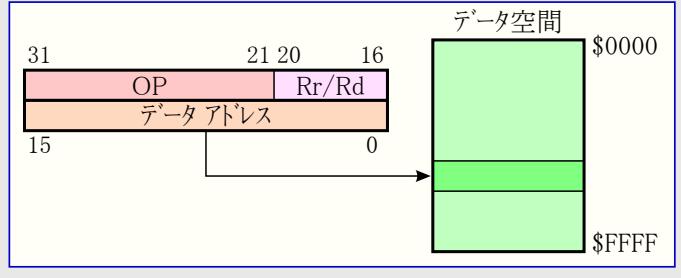

### データ直接

図12. データ直接

オペランドは2語命令の下位16ビットでデータ空間のアドレス位置を示し、Rr/Rdは転送元または転送先となるレジスタを示します。

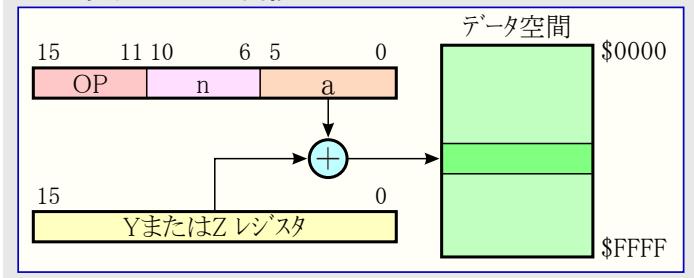

### 変位付きデータ間接

図13. 変位付きデータ間接

オペランドアドレスは、YまたはZレジスタの内容と命令語内の6ビット値aを加算した値となり、他方が転送元または転送先となるレジスタn(Rn)を示します。

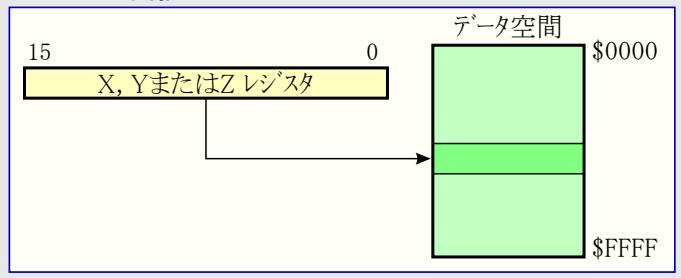

### データ間接

図14. データ間接

オペランドアドレスは、X, YまたはZレジスタの内容となります。

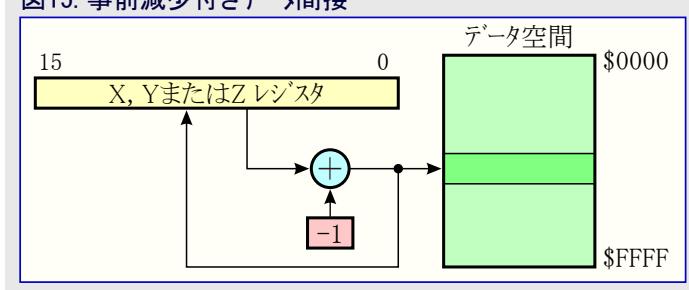

## 事前減少付きデータ間接

図15. 事前減少付きデータ間接

X, YまたはZレジスタはアクセス動作前に内容が減少されます。オペランドアドレスは減少されたX, YまたはZレジスタの内容となります。

## 事後増加付きデータ間接

図16. 事後増加付きデータ間接

X, YまたはZレジスタはアクセス動作後に内容が増加されます。オペランドアドレスは増加される前のX, YまたはZレジスタの内容となります。

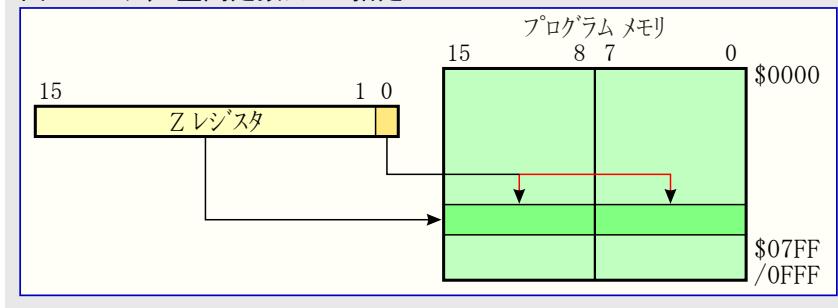

## LPM命令による定数アドレス指定

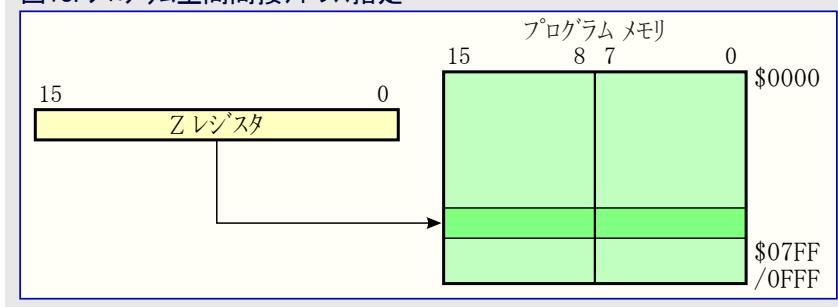

図17. プログラム空間定数アドレス指定

バイト定数のアドレスはZレジスタの内容で示されます。上位15ビットが0～2K/4Kの語(ワード)アドレスを指示し、最下位ビットがバイト位置を表し、LSB=0で下位バイト、LSB=1で上位バイトを示します。

## IJMP, ICALL命令によるプログラム間接アドレス指定

図18. プログラム空間間接アドレス指定

プログラムはZレジスタの内容のアドレスから実行が継続されます。(PCにZレジスタの内容を設定します。)

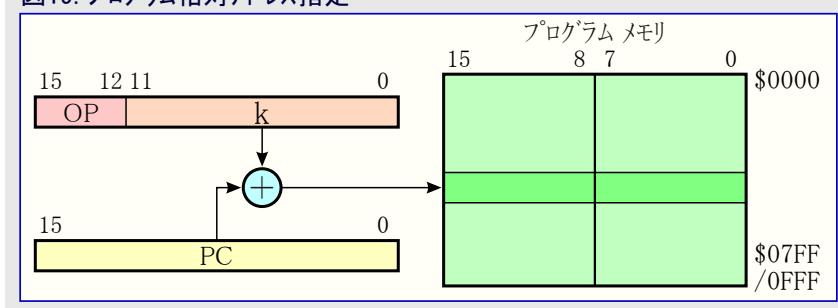

## RJMP, RCALL命令によるプログラム相対アドレス指定

図19. プログラム相対アドレス指定

プログラムはPC+k+1のアドレスから継続実行されます。相対値kは符号付きで、-2048～2047です。

注: このPC値は事前取得の関係から次命令先頭(+1)を指しています。

## メモリアクセスと命令実行タイミング

本項は命令実行と内部メモリアクセスについての一般的なアクセスタイミングの概念を記述します。

AVR CPUは外部クロッククリスタルから直接的に生成されるシステムクロック $\phi$ により駆動されます。内部クロック分周は使われません。

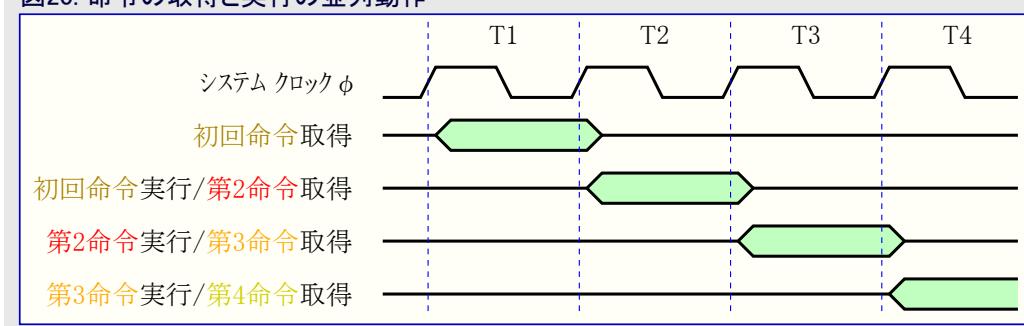

図20.はハード構造と高速アクセスレジスタファイルの概念により可能となる命令取得と命令実行の並列動作を示します。これは機能対費用、機能対クロック、機能対電源部での好結果に相当するMHzあたり1 MIPSまでを得る基本的なパイプラインの概念です。

図20. 命令の取得と実行の並列動作

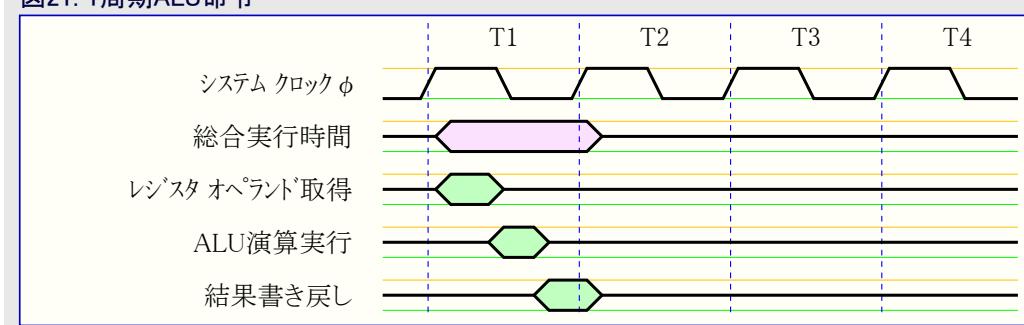

図21.はレジスタファイルに対する内部タイミングの概念を示します。2つのレジスタオペラントを使うALU操作は、転送先レジスタへの結果書き戻しを含め、单一クロック周期で実行されます。

図21. 1周期ALU命令

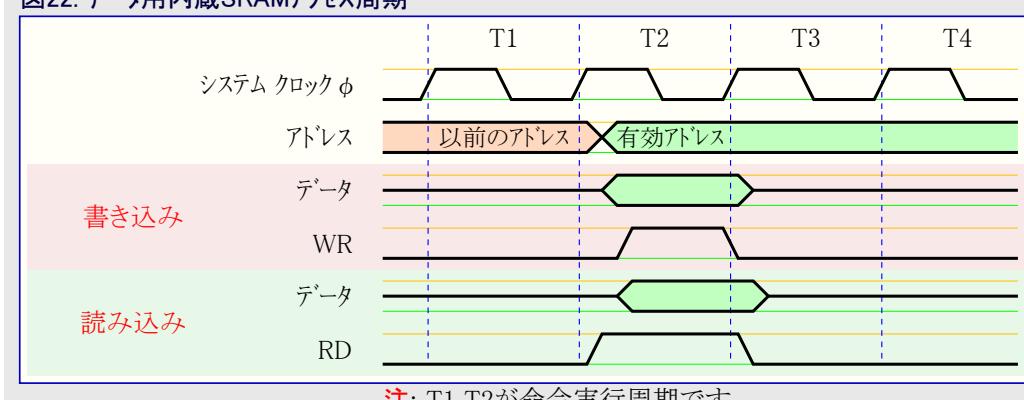

データ用内蔵SRAMのアクセスは、図22.で示されるように、2システムクロック周期で実行されます。

図22. データ用内蔵SRAMアクセス周期

外部SRAMアクセスの説明については、40頁の「外部SRAM(メモリ)インターフェース」を参照してください。

## I/O レジスタ

AT90S4414/8515のI/O領域定義は表2に示されます。

表2. AT90S4414/8515 I/Oレジスタ

| アドレス        | レジスタ略名 | レジスタ名                  |                                                      |

|-------------|--------|------------------------|------------------------------------------------------|

| \$3F (\$5F) | SREG   | ステータス レジスタ             | Status Register                                      |

| \$3E (\$5E) | SPH    | スタック ポインタ上位            | Stack Pointer High                                   |

| \$3D (\$5D) | SPL    | スタック ポインタ下位            | Stack Pointer Low                                    |

| \$3B (\$5B) | GIMSK  | 一般割り込み許可レジスタ           | General Interrupt MaSK register                      |

| \$3A (\$5A) | GIFR   | 一般割り込み要求フラグ レジスタ       | General Interrupt Flag register                      |

| \$39 (\$59) | TIMSK  | タイマ/カウンタ割り込み許可レジスタ     | Timer/Counter Interrupt MaSK register                |

| \$38 (\$58) | TIFR   | タイマ/カウンタ割り込み要求フラグ レジスタ | Timer/Counter Interrupt Flag register                |

| \$35 (\$55) | MCUCR  | MCU制御レジスタ              | MCU general Control Register                         |

| \$33 (\$53) | TCCR0  | タイマ/カウンタ0 制御レジスタ       | Timer/Counter 0 Control Register                     |

| \$32 (\$52) | TCNT0  | タイマ/カウンタ0 カウンタ         | Timer/CouNTer 0 (8bit)                               |

| \$2F (\$4F) | TCCR1A | タイマ/カウンタ1 制御レジスタ A     | Timer/Counter 1 Control Register A                   |

| \$2E (\$4E) | TCCR1B | タイマ/カウンタ1 制御レジスタ B     | Timer/Counter 1 Control Register B                   |

| \$2D (\$4D) | TCNT1H | タイマ/カウンタ1 カウンタ上位       | Timer/CouNTer 1 High byte                            |

| \$2C (\$4C) | TCNT1L | タイマ/カウンタ1 カウンタ下位       | Timer/CouNTer 1 Low byte                             |

| \$2B (\$4B) | OCR1AH | タイマ/カウンタ1 比較Aレジスタ上位    | Timer/Counter 1 Output Compare Register 1A High byte |

| \$2A (\$4A) | OCR1AL | タイマ/カウンタ1 比較Aレジスタ下位    | Timer/Counter 1 Output Compare Register 1A Low byte  |

| \$29 (\$49) | OCR1BH | タイマ/カウンタ1 比較Bレジスタ上位    | Timer/Counter 1 Output Compare Register 1B High byte |

| \$28 (\$48) | OCR1BL | タイマ/カウンタ1 比較Bレジスタ下位    | Timer/Counter 1 Output Compare Register 1B Low byte  |

| \$25 (\$45) | ICR1H  | タイマ/カウンタ1 捕獲レジスタ上位     | Timer/Counter 1 Input Capture Register High byte     |

| \$24 (\$44) | ICR1L  | タイマ/カウンタ1 捕獲レジスタ下位     | Timer/Counter 1 Input Capture Register Low byte      |

| \$21 (\$41) | WDTCR  | ウォッチドッグ タイマ制御レジスタ      | WatchDog Timer Control Register                      |

| \$1F (\$3F) | EEARH  | EEPROM アドレス上位 レジスタ     | EEPROM Address Register high byte (AT90S8515のみ)      |

| \$1E (\$3E) | EEARL  | EEPROM アドレス下位 レジスタ     | EEPROM Address Register low byte                     |

| \$1D (\$3D) | EEDR   | EEPROM データレジスタ         | EEPROM Data Register                                 |

| \$1C (\$3C) | EECR   | EEPROM 制御レジスタ          | EEPROM Control Register                              |

| \$1B (\$3B) | PORTA  | ポートA 出力データレジスタ         | Data Register, Port A                                |

| \$1A (\$3A) | DDRA   | ポートA 方向レジスタ            | Data Direction Register, Port A                      |

| \$19 (\$39) | PINA   | ポートA 入力データレジスタ         | Input Pins, Port A                                   |

| \$18 (\$38) | PORTB  | ポートB 出力データレジスタ         | Data Register, Port B                                |

| \$17 (\$37) | DDRB   | ポートB 方向レジスタ            | Data Direction Register, Port B                      |

| \$16 (\$36) | PINB   | ポートB 入力データレジスタ         | Input Pins, Port B                                   |

| \$15 (\$35) | PORTC  | ポートC 出力データレジスタ         | Data Register, Port C                                |

| \$14 (\$34) | DDRC   | ポートC 方向レジスタ            | Data Direction Register, Port C                      |

| \$13 (\$33) | PINC   | ポートC 入力データレジスタ         | Input Pins, Port C                                   |

| \$12 (\$32) | PORTD  | ポートD 出力データレジスタ         | Data Register, Port D                                |

| \$11 (\$31) | DDRD   | ポートD 方向レジスタ            | Data Direction Register, Port D                      |

| \$10 (\$30) | PIND   | ポートD 入力データレジスタ         | Input Pins, Port D                                   |

| \$0F (\$2F) | SPDR   | SPI データレジスタ            | SPI I/O Data Register                                |

| \$0E (\$2E) | SPSR   | SPI 状態レジスタ             | SPI Status Register                                  |

| \$0D (\$2D) | SPCR   | SPI 制御レジスタ             | SPI Control Register                                 |

| \$0C (\$2C) | UDR    | UART データレジスタ           | UART Data Register                                   |

| \$0B (\$2B) | USR    | UART 状態レジスタ            | UART Status Register                                 |

| \$0A (\$2A) | UCR    | UART 制御レジスタ            | UART Control Register                                |

| \$09 (\$29) | UBRR   | UART ポーレートレジスタ         | UART Baud Rate Register                              |

| \$08 (\$28) | ACSR   | アナログ比較器 制御/状態レジスタ      | Analog Comparator Control and Status Register        |

注: 預約と未使用の位置は、この表で示されていません。()内のアドレスはデータ空間の一部としてアクセスする場合のアドレスです。

AT90S4414/8515の全てのI/Oと周辺部はI/O空間に配置されています。各I/O位置は、I/O空間と32個の汎用レジスタ間のデータ移動を行うIN命令とOUT命令によりアクセスされます。アドレス\$00～\$1F範囲内のI/Oレジスタは、SBIとCBI命令を使う直接ビットアクセスが可能です。これらのレジスタでは、SBISとSBIC命令の使用により、单一ビット値の検査ができます。より詳細な内容は命令要約を参照してください。I/O指定命令INとOUTを使う時はI/Oアドレス\$00～\$3Fが使われなければなりません。I/OレジスタをSRAMとしてアクセスする時はこのアドレスに\$20が加算されなければなりません。本文書を通して、全てのI/Oレジスタアドレスは、()内でデータ空間アドレスが示されます。

将来のデバイスとの共通性を保つため、予約ビットに書く場合は0を書くべきです。予約済みI/Oアドレスは決して書かれるべきではありません。

状態フラグのいくつかは、論理1を書くことで解除(0)されます。CBIとSBI命令はI/Oレジスタ内の全ビットを操作し、設定(1)として読むフラグは1が書き戻され、従ってフラグを解除(0)することに注意してください。CBIとSBI命令は、レジスタ\$00～\$1Fでのみ動作します。

I/Oと周辺制御レジスタは次章で説明されます。

## ステータス レジスタ (Status Register) SREG

AVRのステータス レジスタ(SREG)は、I/O領域の\$3F(\$5F)で、次のように定義されています。

| ビット         | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |      |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$3F (\$5F) | I   | T   | H   | S   | V   | N   | Z   | C   | SREG |

| Read/Write  | R/W |      |

| 初期値         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

### • ビット7 – I : 全割り込み許可 (Global Interrupt Enable)

この全割り込み許可ビットは割り込みを許可する場合に設定(1)しなければなりません。各割り込みの許可は各制御レジスタで個別に行います。全割り込み許可ビットが解除(0)されると、個別に割り込みが許可されていても割り込みは発生しません。このビットは割り込み発生後、自動的に解除(0)され、後続の割り込みを許可するため、割り込み処理のRETI命令によって設定(1)されます。

### • ビット6 – T : ビット変数 (Bit Copy Storage)

このTビットはBLD(Bit LoaD)命令とBST(Bit STore)命令の転送元または転送先として使われます。BLD命令はTをレジスタ ファイルのレジスタのビットに複写し、BST命令はレジスタ ファイルのレジスタからビットをTに複写します。

### • ビット5 – H : ハーフキャリー フラグ (Half Carry Flag)

このHフラグはいくつかの算術演算命令でのハーフキャリーを示します。ハーフキャリーはBCD演算に有用です。詳細情報については[命令要約](#)を参照してください。

### • ビット4 – S : 符号 (Sign Bit, S= N Ex-OR V)

このSフラグは常に負(N)フラグと2の補数溢れ(V)フラグの排他的論理和です。詳細情報については命令要約を参照してください。

### • ビット3 – V : 2の補数溢れフラグ (2's Complement Overflow Flag)

この2の補数溢れ(V)フラグは、2の補数算術演算を補助します。詳細情報については命令要約を参照してください。

### • ビット2 – N : 負フラグ (Negative Flag)

このNフラグは算術及び論理演算の結果が負であること(MSB=1)を示します。詳細情報については命令要約を参照してください。

### • ビット1 – Z : ゼロ フラグ (Zero Flag)

このZフラグは算術及び論理演算の結果がゼロ(0)であることを示します。詳細情報については命令要約を参照してください。

### • ビット0 – C : キャリー フラグ (Carry Flag)

このCフラグは算術及び論理演算でキャリーが発生したことを示します。詳細情報については命令要約を参照してください。

ステータス レジスタは割り込み処理ルーチン移行時の保存と、割り込み処理ルーチンから復帰時の再設定が、自動的に行われないことに注意してください。これはソフトウェアにより操作しなければなりません。

## スタック ポインタ (Stack Pointer) SPH,SPL (SP)

AVRの一般16ビット スタック ポインタは、実際にはI/O空間位置\$3E(\$5E)と\$3D(\$5D)の2つの8ビット レジスタの構造です。AT90S4414/8515は64Kバイトまでの外部SRAMを支援するため、16ビット全てが使われます。

| ビット         | 15   | 14   | 13   | 12   | 11   | 10   | 9   | 8   |     |

|-------------|------|------|------|------|------|------|-----|-----|-----|

| \$3E (\$5E) | SP15 | SP14 | SP13 | SP12 | SP11 | SP10 | SP9 | SP8 | SPH |

| Read/Write  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W | R/W |     |

| 初期値         | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   |     |

| ビット         | 7    | 6    | 5    | 4    | 3    | 2    | 1   | 0   |     |

| \$3D (\$5D) | SP7  | SP6  | SP5  | SP4  | SP3  | SP2  | SP1 | SP0 | SPL |

| Read/Write  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W | R/W |     |

| 初期値         | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   |     |

スタック ポインタはサブルーチンと割り込みのスタックが配置されるデータSRAMのスタック領域を指し示します。データSRAM内のスタック領域は、割り込みの許可や、何れかのサブルーチン呼び出しが実行される前にプログラムによって定義されなければなりません。スタック ポインタは\$60以上を指示するために設定されなければなりません。スタック ポインタは、PUSH命令でデータがスタック上に格納されるとき-1され、サブルーチン呼び出しや割り込みでアドレスがスタック上に格納されるとき-2されます。POP命令でデータをスタックから引き出すとき+1され、サブルーチンからの復帰(RET命令)や割り込みからの復帰(RETI命令)でアドレスをスタックから引き出すとき+2されます。

## リセットと割り込みの扱い

AT90S4414/8515には12種類の割り込みがあります。これらの割り込みとリセットのベクタは、プログラムメモリ空間内に各々個別のベクタを持っています。全ての割り込みは、割り込みを許可するために、個別の許可ビットとステータスレジスタ(SREG)の全割り込み許可(I)ビットと共に設定(1)しなければなりません。

プログラムメモリ空間の最下位アドレスは、リセットと割り込みのベクタとして自動的に定義されています。このベクタの全一覧は表3に示されます。この一覧が各割り込みの優先順位も決めます。下位アドレスがより高い優先順位です。リセットが最高優先順位で、以下、外部割り込み要求0(INT0)の順です。

表3. リセットと割り込みのベクタ

| ベクタ番号 | プログラムアドレス | 発生元              | 備考                   |

|-------|-----------|------------------|----------------------|

| 1     | \$000     | リセット             | 電源ONまたはウォッチドッグ等のリセット |

| 2     | \$001     | INT0             | 外部割り込み要求0            |

| 3     | \$002     | INT1             | 外部割り込み要求1            |

| 4     | \$003     | タイマ/カウンタ1 CAPT   | タイマ/カウンタ1捕獲発生        |

| 5     | \$004     | タイマ/カウンタ1 COMPA  | タイマ/カウンタ1比較A一致       |

| 6     | \$005     | タイマ/カウンタ1 COMPB  | タイマ/カウンタ1比較B一致       |

| 7     | \$006     | タイマ/カウンタ1 OVF1   | タイマ/カウンタ1溢れ          |

| 8     | \$007     | タイマ/カウンタ0 OVF0   | タイマ/カウンタ0溢れ          |

| 9     | \$008     | SPI STC          | SPI転送完了              |

| 10    | \$009     | UART RX          | UART受信完了             |

| 11    | \$00A     | UART UDRE        | UART送信緩衝部空き          |

| 12    | \$00B     | UART TX          | UART送信完了             |

| 13    | \$00C     | アナログ比較器 ANA_COMP | アナログ比較器出力遷移          |

リセットと割り込みのベクタの最も代表的な設定例を次に示します。

| アドレス  | ラベル    | 命令                    | 注釈              |

|-------|--------|-----------------------|-----------------|

| \$000 |        | RJMP RESET            | ;各種リセット         |

| \$001 |        | RJMP EXT_INT0         | ;外部割り込み要求0      |

| \$002 |        | RJMP EXT_INT1         | ;外部割り込み要求1      |

| \$003 |        | RJMP TIM1_CAPT        | ;タイマ/カウンタ1捕獲発生  |

| \$004 |        | RJMP TIM1_COMPA       | ;タイマ/カウンタ1比較A一致 |

| \$005 |        | RJMP TIM1_COMPB       | ;タイマ/カウンタ1比較B一致 |

| \$006 |        | RJMP TIM1_OVF         | ;タイマ/カウンタ1溢れ    |

| \$007 |        | RJMP TIM0_OVF         | ;タイマ/カウンタ0溢れ    |

| \$008 |        | RJMP SPI_STC          | ;SPI転送完了        |

| \$009 |        | RJMP UART_RXC         | ;UART受信完了       |

| \$00A |        | RJMP UART_DRE         | ;UART送信緩衝部空     |

| \$00B |        | RJMP UART_TXC         | ;UART送信完了       |

| \$00C |        | RJMP ANA_COMP         | ;アナログ比較器出力遷移    |

| ;     |        |                       |                 |

| \$00D | RESET: | LDI R16, HIGH(RAMEND) | ;RAM最終アドレス上位を取得 |

| \$00E |        | OUT SPH, R16          | ;スタックポインタ上位を初期化 |

| \$00F |        | LDI R16, LOW(RAMEND)  | ;RAM最終アドレス下位を取得 |

| \$010 |        | OUT SPL, R16          | ;スタックポインタ下位を初期化 |

|       |        |                       | ;以下、I/O初期化など    |

## リセット発生元

AT90S4414/8515には、次の3つのリセット発生元があります。

- **電源ONリセット** …… 電源電圧が電源ONリセット閾値電圧(VPOT)以下でリセットになります。

- **外部リセット** …… RESETピンが50ns以上Lowレベルに保たれるとリセットになります。

- **ウォッチドッグリセット** …… ウォッチドッグが許可され、ウォッチドッグ タイマ周期が経過するとリセットになります。

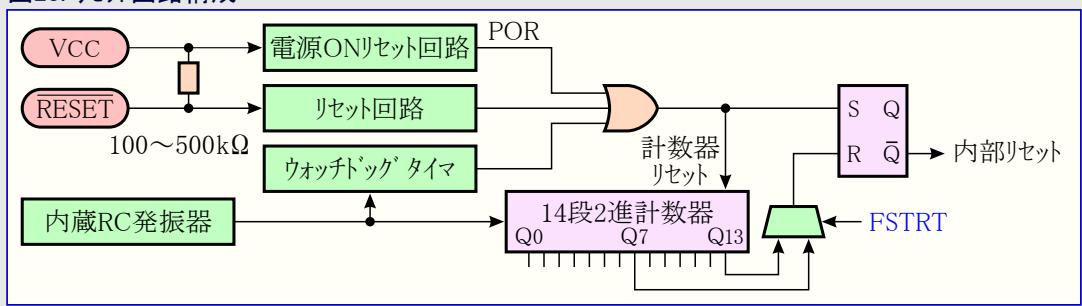

リセット中に、全てのI/Oレジスタは初期値が設定され、その後にアドレス\$000からプログラム実行が始まります。アドレス\$000に配置される命令は、リセット処理ルーチンへの無条件相対分岐(RJMP)命令でなければなりません。プログラムで決して割り込みを許可しないなら、割り込みベクタが使われず、これらの位置に通常のプログラムを配置できます。図23.にリセット部の回路構成を示します。表4.はリセット回路の電気的特性とタイミングを定義します。

図23. リセット回路構成

表4. リセット電気的特性 (VCC=5.0V)

| シンボル  | 項目                   | 最小              | 代表             | 最大     | 単位   |

|-------|----------------------|-----------------|----------------|--------|------|

| VPOT  | 上昇時電源ONリセット閾値電圧      | 0.8             | 1.2            | 1.6    | V    |

|       | 下降時電源ONリセット閾値電圧 (注1) | 0.2             | 0.4            | 0.6    |      |

| VRST  | RESETピン閾値電圧          |                 |                | 0.9VCC |      |

| tTOUT | リセット遅延時間             | FSTRT=非プログラム(1) | 11             | 16     | 21   |

|       |                      |                 | FSTRT=プログラム(0) | 0.25   | 0.28 |

|       |                      |                 |                |        | ms   |

注1: 供給電圧がこの電圧以下にならないと、上昇時の電源ONリセットは動作しません。

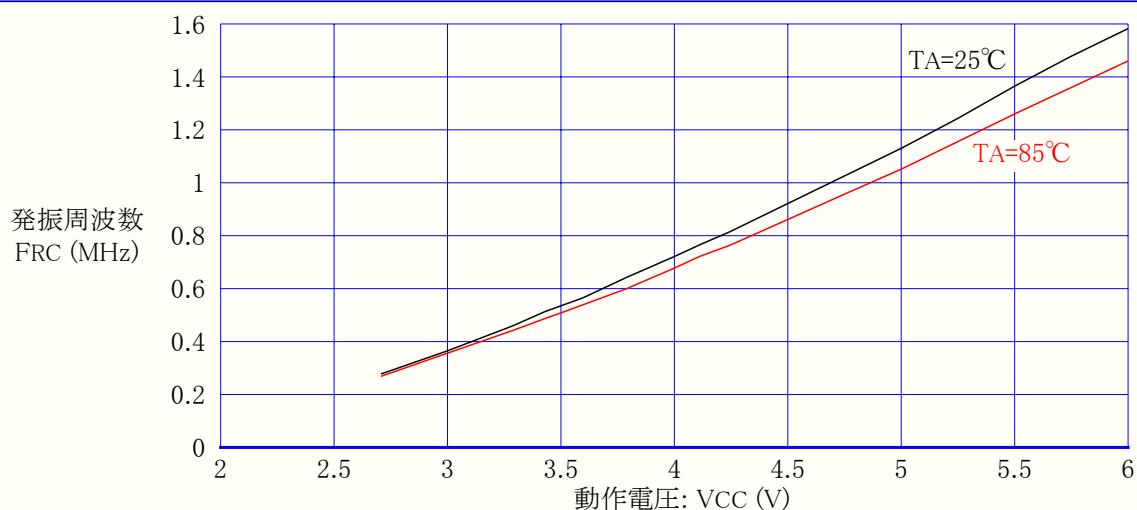

代表的な発振器起動に従った起動時間を選べます。各計時終了(リセット遅延時間)で使われるウォッチドッグ発振器周期数は表5.で示されます。ウォッチドッグ発振器の周波数は、68頁の「代表特性」内で示されるように、電圧に依存します。

表5. ウォッチドッグ発振器の周期数

| FSTRT     | リセット遅延時間 (VCC=5V) | ウォッチドッグ発振器周期数 |

|-----------|-------------------|---------------|

| プログラム(0)  | 0.28ms            | 256           |

| 非プログラム(1) | 16.0ms            | 16K           |

(誤注) 改訂Eまでは、FSTRT=0時、図23.で14段2進カウタの出力はQ8(実際はQ9の誤り)となっています。その結果、対応する表5.の値は、1024分周で1.1msとなっており、表4.の値も各々1.0, 1.1, 1.2msとなっていました。

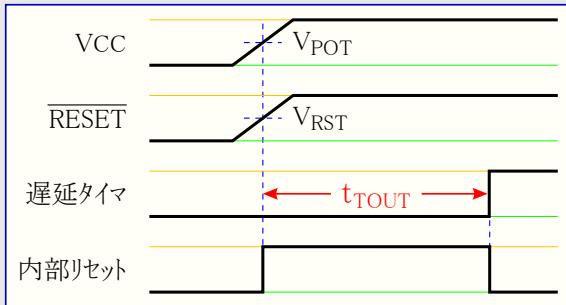

## 電源ONリセット

電源ONリセット(POR)回路は、電源投入時のデバイスリセットを保証します。図23.で示されるように、内部タイマはウォッチドッグ発振器で駆動されます。この内部タイマはVCC上昇時間に拘らず、VCCが電源ON閾値電圧( $V_{POT}$ )に達した後の或る期間後まで、MCUを開始から保護します(図24.参照)。フラッシュメモリ内のFSTRTヒューズ'ビットはセミク振動子や他の高速起動発振器がMCUのクロックに使われる場合、短い起動遅延時間とするためにプログラム(0)することができます。

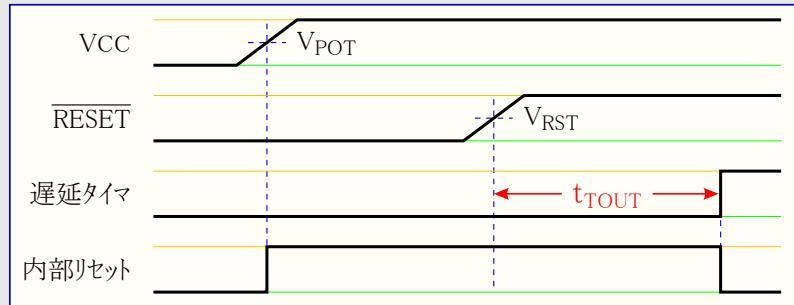

内蔵起動遅延時間で充分な場合、RESETを直接または外部プルアップ抵抗を介してVCCに接続できます。VCC供給後も、RESETピンをLowレベルに保持することで、起動遅延時間を延長することができます。このタイミング例は図25.を参照してください。

図24. 内蔵電源ONリセット (RESETはVCCに接続)

図25. 外部RESET信号による延長電源ONリセット

## 外部リセット

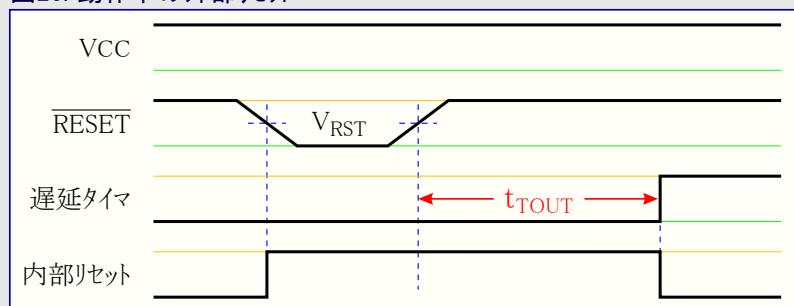

外部リセットはRESETピン上のLowレベルにより生成されます。例えクロックが動いていなくとも、50nsより長いリセットパルスはリセットを生成します。短すぎるパルスはリセットが保証されません。供給された信号の上昇がリセット閾値電圧( $V_{RST}$ )に達すると、遅延タイマは遅延時間( $t_{TOUT}$ )経過後にMCUを起動します。

図26. 動作中の外部リセット

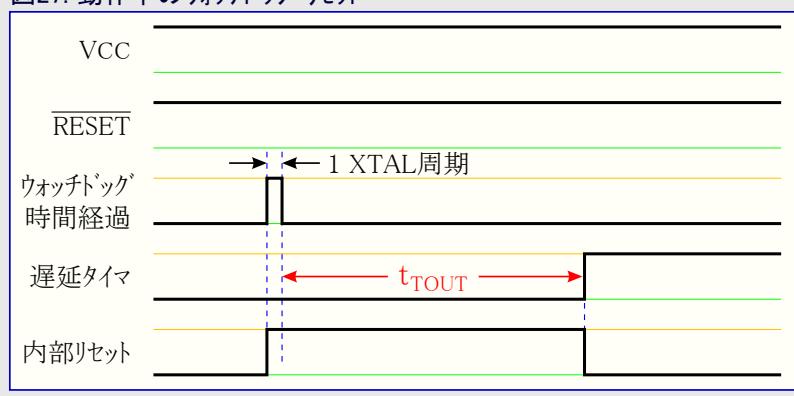

## ウォッチドッグリセット

ウォッチドッグ時間経過で1 XTAL周期幅の短いリセットパルスを生成します。このパルスの下降端で遅延タイマは遅延時間( $t_{TOUT}$ )の計時を始めます。ウォッチドッグ操作の詳細については28頁を参照してください。

図27. 動作中のウォッチドッグリセット

## 割り込みの扱い

AT90S4414/8515には、一般割り込み許可レジスタ(GIMSK)とタイマ/カウンタ割り込み許可レジスタ(TIMSK)の2つの8ビット割り込み許可レジスタがあります。

割り込みが起こると、[ステータスレジスタ\(SREG\)の全割り込み許可\(I\)ビット](#)が解除(0)され、全ての割り込みが禁止されます。ソフトウェアは多重割り込みを許可するために、全割り込み許可(I)ビットを設定(1)できます。この全割り込み許可(I)ビットは、割り込みからの復帰(RETI)命令が実行されると設定(1)されます。

安定して維持できる要因(例えば、比較レジスタとタイマ/カウンタ1の一致)により割り込み要求が起動されると、その要因発生時に割り込み要求フラグが設定(1)されます。割り込み要求フラグが解除(0)され、その割り込み条件が持続されると、次の要因発生まで設定(1)されません。

割り込み処理ルーチンを実行するために、プログラム カウンタが実際の割り込みベクタを指示するとき、割り込みを起こした対応する割り込み要求フラグを自動的に解除(0)します。いくつかの割り込み要求フラグは、そのフラグのビット位置に論理1を書くことによっても解除(0)できます。

対応する割り込み許可ビットが解除(0)されているときに割り込み条件が発生すると、対応する割り込み要求フラグが設定(1)され、その割り込みが許可または、ソフトウェアで解除(0)されるまで保持されます。

全割り込み許可(I)ビットが解除(0)されているときに1つまたは多くの割り込み条件が発生すると、対応する割り込み要求フラグが設定(1)され、全割り込み許可(I)ビットが設定(1)されるまで保持されます。許可後、それらは優先順に実行されます。

外部レベル割り込みには割り込み要求フラグがなく、割り込み条件が有効でありさえすれば割り込み要求が保持されるだけなことに注意してください。

### 一般割り込み許可レジスタ (General Interrupt Mask Register) GIMSK

| ビット         | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 |       |

|-------------|------|------|---|---|---|---|---|---|-------|

| \$3B (\$5B) | INT1 | INT0 | — | — | — | — | — | — | GIMSK |

| Read/Write  | R/W  | R/W  | R | R | R | R | R | R |       |

| 初期値         | 0    | 0    | 0 | 0 | 0 | 0 | 0 | 0 |       |

#### • ビット7 – INT1 : 外部割り込み1許可 (External Interrupt Request 1 Enable)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットと外部割り込み1許可(INT1)ビットがともに設定(1)で、INT1ピンの割り込みが許可されます。MCU制御レジスタ(MCUCR)の割り込み条件制御1のビット1と0(ISC11, ISC10)が、外部割り込みINT1ピンの動作を上昇端、下降端またはLowレベルの何れか定義します。INT1ピンが出力に設定されていても、この割り込み機能は有効です。外部割り込み要求1に対応する割り込みは、プログラムメモリアドレス\$002から実行されます。「[外部割り込み](#)」も参照してください。

#### • ビット6 – INT0 : 外部割り込み0許可 (External Interrupt Request 0 Enable)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットと外部割り込み0許可(INT0)ビットがともに設定(1)で、INT0ピンの割り込みが許可されます。MCU制御レジスタ(MCUCR)の割り込み条件制御0のビット1と0(ISC01, ISC00)が、外部割り込みINT0ピンの動作を上昇端、下降端またはLowレベルの何れか定義します。INT0ピンが出力に設定されていても、この割り込み機能は有効です。外部割り込み要求0に対応する割り込みは、プログラムメモリアドレス\$001から実行されます。「[外部割り込み](#)」も参照してください。

#### • ビット5~0 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

### 一般割り込み要求フラグ レジスタ (General Interrupt Flag Register) GIFR

| ビット         | 7     | 6     | 5 | 4 | 3 | 2 | 1 | 0 |      |

|-------------|-------|-------|---|---|---|---|---|---|------|

| \$3A (\$5A) | INTF1 | INTF0 | — | — | — | — | — | — | GIFR |

| Read/Write  | R/W   | R/W   | R | R | R | R | R | R |      |

| 初期値         | 0     | 0     | 0 | 0 | 0 | 0 | 0 | 0 |      |

#### • ビット7 – INTF1 : 外部割り込み1要求フラグ (External Interrupt Flag1)

INT1ピン上の端(エッジ)が割り込み要求を起こすと、対応する割り込み要求フラグ(INTF1)が設定(1)になります。ステータスレジスタ(SREG)の全割り込み許可(I)ビットと、対応する一般割り込み許可レジスタ(GIMSK)の外部割り込み1許可(INT1)ビットがともに設定(1)されていれば、MCUは割り込みベクタへ飛びます。このフラグは割り込み処理ルーチンが実行されるときに解除(0)されます。このフラグは論理1を書くことによっても解除(0)できます。INT1がレベル割り込みとして設定されるとき、このフラグは常に解除(0)されます。

#### • ビット6 – INTF0 : 外部割り込み0要求フラグ (External Interrupt Flag0)

INT0ピン上の端(エッジ)が割り込み要求を起こすと、対応する割り込み要求フラグ(INTF0)が設定(1)になります。ステータスレジスタ(SREG)の全割り込み許可(I)ビットと、対応する一般割り込み許可レジスタ(GIMSK)の外部割り込み0許可(INT0)ビットがともに設定(1)されていれば、MCUは割り込みベクタへ飛びます。このフラグは割り込み処理ルーチンが実行されるときに解除(0)されます。このフラグは論理1を書くことによっても解除(0)できます。INT0がレベル割り込みとして設定されるとき、このフラグは常に解除(0)されます。

• ビット5~0 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

タイマ/カウンタ割り込み許可レジスタ (Timer/Counter Interrupt Mask Register) **TIMSK**

| ビット         | 7     | 6      | 5      | 4 | 3      | 2 | 1     | 0 |       |

|-------------|-------|--------|--------|---|--------|---|-------|---|-------|

| \$39 (\$59) | TOIE1 | OCIE1A | OCIE1B | – | TICIE1 | – | TOIE0 | – | TIMSK |

| Read/Write  | R/W   | R/W    | R/W    | R | R/W    | R | R/W   | R |       |

| 初期値         | 0     | 0      | 0      | 0 | 0      | 0 | 0     | 0 |       |

• ビット7 – TOIE1 : タイマ/カウンタ1溢れ割り込み許可 (Timer/Counter1 Overflow Interrupt Enable)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットとタイマ/カウンタ1溢れ割り込み許可(TOIE1)ビットが共に設定(1)で、タイマ/カウンタ1溢れ割り込みが許可されます。タイマ/カウンタ1溢れが起こる、換言すると、タイマ/カウンタ割り込み要求フラグレジスタ(TIFR)のタイマ/カウンタ1溢れ割り込み要求フラグ(TOV1)が設定(1)されると、対応する割り込み(ベクタ \$006)が実行されます。

• ビット6 – OCIE1A : 比較A一致割り込み許可 (Timer/Counter1 Output Compare A Match Interrupt Enable)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットと比較A一致割り込み許可(OCIE1A)ビットが共に設定(1)で、比較A一致割り込みが許可されます。タイマ/カウンタ1で比較A一致が起こる、換言すると、タイマ/カウンタ割り込み要求フラグレジスタ(TIFR)の比較A一致割り込み要求フラグ(OCF1A)が設定(1)されると、対応する割り込み(ベクタ \$004)が実行されます。

• ビット5 – OCIE1B : 比較B一致割り込み許可 (Timer/Counter1 Output Compare B Match Interrupt Enable)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットと比較B一致割り込み許可(OCIE1B)ビットが共に設定(1)で、比較B一致割り込みが許可されます。タイマ/カウンタ1で比較B一致が起こる、換言すると、タイマ/カウンタ割り込み要求フラグレジスタ(TIFR)の比較B一致割り込み要求フラグ(OCF1B)が設定(1)されると、対応する割り込み(ベクタ \$005)が実行されます。

• ビット4 – Res : 予約 (Reserved)

このビットは予約されており、常に0として読みます。

• ビット3 – TICIE1 : 捕獲割り込み許可 (Timer/Counter1 Input Capture Interrupt Enable)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットと捕獲割り込み許可(TICIE1)ビットが共に設定(1)で、捕獲割り込みが許可されます。ICPピン上に捕獲要求が起こる、換言すると、タイマ/カウンタ割り込み要求フラグレジスタ(TIFR)の捕獲割り込み要求フラグ(ICF1)が設定(1)されると、対応する割り込み(ベクタ \$003)が実行されます。

• ビット2 – Res : 予約 (Reserved)

このビットは予約されており、常に0として読みます。

• ビット1 – TOIE0 : タイマ/カウンタ0溢れ割り込み許可 (Timer/Counter0 Overflow Interrupt Enable)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットとタイマ/カウンタ0溢れ割り込み許可(TOIE0)ビットが共に設定(1)で、タイマ/カウンタ0溢れ割り込みが許可されます。タイマ/カウンタ0溢れが起こる、換言すると、タイマ/カウンタ割り込み要求フラグレジスタ(TIFR)のタイマ/カウンタ0溢れ割り込み要求フラグ(TOV0)が設定(1)されると、対応する割り込み(ベクタ \$007)が実行されます。

• ビット0 – Res : 予約 (Reserved)

このビットは予約されており、常に0として読みます。

タイマ/カウンタ割り込み要求フラグレジスタ (Timer/Counter Interrupt Flag Register) **TIFR**

| ビット         | 7    | 6     | 5     | 4 | 3    | 2 | 1    | 0 |      |

|-------------|------|-------|-------|---|------|---|------|---|------|

| \$38 (\$58) | TOV1 | OCF1A | OCF1B | – | ICF1 | – | TOV0 | – | TIFR |

| Read/Write  | R/W  | R/W   | R/W   | R | R/W  | R | R/W  | R |      |

| 初期値         | 0    | 0     | 0     | 0 | 0    | 0 | 0    | 0 |      |

• ビット7 – TOV1 : タイマ/カウンタ1溢れ割り込み要求フラグ (Timer/Counter1 Overflow Interrupt Flag)

タイマ/カウンタ1溢れが起こると、TOV1が設定(1)されます。対応する割り込み処理ベクタを実行すると、このTOV1は自動的に解除(0)されます。代わりに、このフラグへ論理1を書くことによってもTOV1は解除(0)されます。ステータスレジスタ(SREG)の全割り込み許可(I)ビットとタイマ/カウンタ割り込み許可レジスタ(TIMSK)のタイマ/カウンタ1溢れ割り込み許可(TOIE1)ビットとTOV1が設定(1)されると、タイマ/カウンタ1溢れ割り込みが実行されます。PWM動作では、タイマ/カウンタ1が\$0000で計数方向を変更するとき、このフラグが設定(1)されます。

• ビット6 – OCF1A : 比較A一致割り込み要求フラグ (Output Compare Interrupt Flag1A)

タイマ/カウンタ1と比較Aレジスタ(OCR1A)の値間で比較一致が起こると、OCF1Aが設定(1)されます。対応する割り込み処理ベクタを実行すると、このOCF1Aは自動的に解除(0)されます。代わりに、このフラグへ論理1を書くことによってもOCF1Aは解除(0)されます。ステータスレジスタ(SREG)の全割り込み許可(I)ビットとタイマ/カウンタ割り込み許可レジスタ(TIMSK)の比較A一致割り込み許可(OCIE1A)ビットとOCF1Aが設定(1)されると、比較A一致割り込みが実行されます。

• ビット5 – OCF1B : 比較B一致割り込み要求フラグ (Output Compare Interrupt Flag1B)

タイマ/カウンタ1と比較Bレジスタ(OCR1B)の値間で比較一致が起こると、OCF1Bが設定(1)されます。対応する割り込み処理ベクタを実行すると、このOCF1Bは自動的に解除(0)されます。代わりに、このフラグへ論理1を書くことによってもOCF1Bは解除(0)されます。ステータスレジスタ(SREG)の全割り込み許可(I)ビットとタイマ/カウンタ割り込み許可レジスタ(TIMSK)の比較B一致割り込み許可(OCIE1B)ビットとOCF1Bが設定(1)されると、比較B一致割り込みが実行されます。

• ビット4 – Res : 予約 (Reserved)

このビットは予約されており、常に0として読みます。

• ビット3 – ICF1 : 捕獲割り込み要求フラグ (Input Capture Interrupt Flag1)

このICF1ビットは、タイマ/カウンタ1の値が捕獲レジスタ(ICR1)に転送されてしまったことを示す、捕獲発生のフラグのため設定(1)されます。対応する割り込み処理ベクタを実行すると、このICF1は自動的に解除(0)されます。代わりに、このフラグへ論理1を書くことによってもICF1は解除(0)されます。ステータスレジスタ(SREG)の全割り込み許可(I)ビットとタイマ/カウンタ割り込み許可レジスタ(TIMSK)の捕獲割り込み許可(TICIE1)ビットとICF1が設定(1)されると、捕獲割り込みが実行されます。

• ビット2 – Res : 予約 (Reserved)

このビットは予約されており、常に0として読みます。

• ビット1 – TOV0 : タイマ/カウンタ0溢れ割り込み要求フラグ (Timer/Counter0 Overflow Interrupt Flag)

タイマ/カウンタ0溢れが起こると、このTOV0ビットが設定(1)されます。対応する割り込みベクタを実行すると、TOV0は自動的に解除(0)されます。代わりに、このフラグへ論理1を書くことによってもTOV0は解除(0)されます。ステータスレジスタ(SREG)の全割り込み許可(I)ビットとタイマ/カウンタ割り込み許可レジスタ(TIMSK)のタイマ/カウンタ0溢れ割り込み許可(TOIE0)ビットとTOV0が設定(1)されると、タイマ/カウンタ0溢れ割り込みが実行されます。

• ビット0 – Res : 予約 (Reserved)

このビットは予約されており、常に0として読みます。

## 外部割り込み

外部割り込みは、INT0とINT1ピンにより起動されます。許可されていれば、INT0, INT1ピンが出力として設定されても、割り込みが起動することに注目してください。この特徴はソフトウェア割り込みを生成する方法を提供します。外部割り込みは上昇端、下降端またはLowレベルで起動できます。これはMCU制御レジスタ(MCUCR)についての詳細で説明されるように設定します。外部割り込みが許可され、レベル起動として設定されるとき、ピンがLowに保持されている限り、この割り込みは継続的に発生します。

外部割り込みは、MCU制御レジスタ(MCUCR)についての詳細で説明されるように設定します。

## 割り込み応答時間

全ての許可された割り込みについての割り込み実行応答時間は最小4クロックです。割り込み要求フラグが設定(1)されてしまった後の4クロック周期で、実際の割り込み処理ルーチン用の割り込みベクタアドレスが実行されます。この4クロック周期期間中、プログラムカウンタ(2バイト)がスタック上に保存(プッシュ)され、スタックポインタが減少(-2)されます。通常、このベクタは割り込み処理ルーチンに対する無条件相対分岐(RJMP)命令で、この分岐に2クロック周期かかります。複数周期の命令実行中に割り込みが起こると、割り込みが扱われる前に、その命令が完了されます。

割り込み処理ルーチンからの復帰(サブルーチン呼び出しについてと同じように)は4クロック周期要します。この4クロック周期中に、スタックからプログラムカウンタ(2バイト)が再設定(ポップ)され、スタックポインタが増加(+2)され、ステータスレジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されます。割り込みを抜けるときは常に主(元)プログラムへ復帰し、保留されている割り込みが扱われる前に、1つ以上の命令を実行します。

ステータスレジスタ(SREG)が割り込みまたはサブルーチンのどちらについてもAVRハードウェアにより操作されないことに注意してください。SREGの保存を必要とする割り込み処理ルーチンについて、これは使用者ソフトウェアにより実行されなければなりません。

安定して維持できる要因(例えば、比較レジスタとタイマ/カウンタ1の一一致)により割り込み要求が起動されると、その要因発生時に割り込み要求フラグが設定(1)されます。割り込み要求フラグが解除(0)され、その割り込み条件が持続されると、次の要因発生まで設定(1)されません。外部レベル割り込みは、割り込み条件が有効でありさえすれば割り込み要求が保持されるだけなことに注意してください。

## MCU制御レジスタ (MCU Control Register) MCUCR

このMCU制御レジスタは、MCU機能一般についての制御ビットを含みます。

| ビット         | 7   | 6   | 5   | 4   | 3     | 2     | 1     | 0     |       |

|-------------|-----|-----|-----|-----|-------|-------|-------|-------|-------|

| \$35 (\$55) | SRE | SRW | SE  | SM  | ISC11 | ISC10 | ISC01 | ISC00 | MCUCR |

| Read/Write  | R/W | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |       |

| 初期値         | 0   | 0   | 0   | 0   | 0     | 0     | 0     | 0     |       |

### • ビット7 – SRE : 外部SRAM許可 (External SRAM Enable)

このSREビットが設定(1)されるとデータ用外部SRAMが許可され、AD7~0(ポートA)、A15~8(ポートC)、 $\overline{RD}$ (PD7)、 $\overline{WR}$ (PD6)のピン機能は交換ピン機能として活性化(有効に)されます。その時、SREビットは各ポート方向レジスタでのどんなピン方向設定も無視します。外部SRAMピン機能の説明については、[6頁の「内蔵SRAMと外部SRAM」と40頁の「外部SRAM\(メモリ\)インターフェース](#)を参照してください。SREビットが解除(0)されると、データ用外部SRAMが禁止され、標準ピンとデータ方向設定が使われます。

### • ビット6 – SRW : 外部SRAM待ち (External SRAM Wait State)

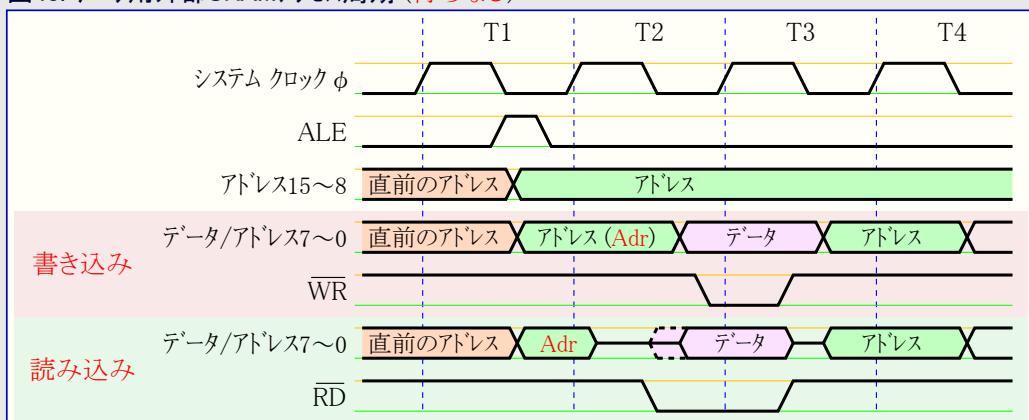

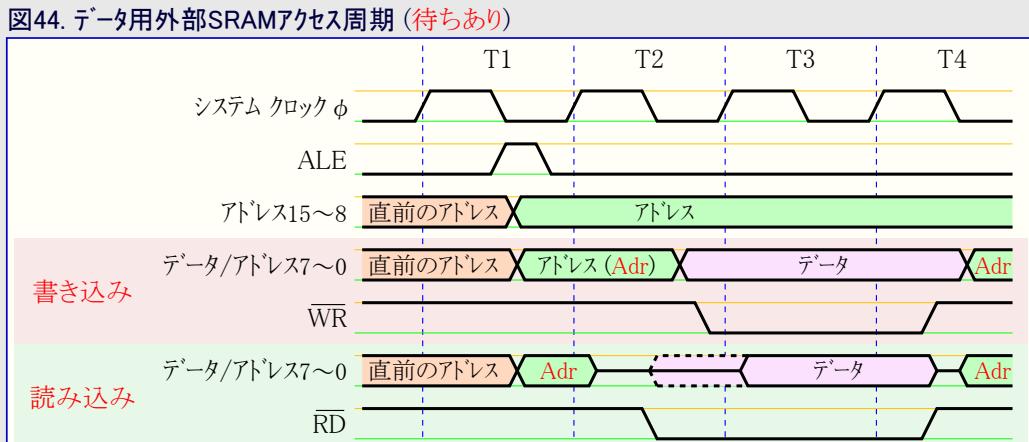

このSRWビットが設定(1)されると、データ用外部SRAMアクセス周期に1周期の待ち状態が挿入されます。SRWビットが解除(0)されると、データ用外部SRAMアクセスは標準の3周期構造で実行されます。[図43](#)と[図44](#)を参照してください。

### • ビット5 – SE : 休止許可 (Sleep Enable)

SLEEP命令が実行されるときにMCUを休止形態へ移行させるには、休止許可(SE)ビットが設定(1)されなければなりません。MCUの目的外休止形態移行をなくすため、SLEEP命令実行直前に休止許可(SE)ビットを設定(1)することが推奨されます。

### • ビット4 – SM : 休止種別 (Sleep Mode)

このビットは利用可能な2つの休止形態種別を選びます。SMが解除(0)されると休止形態としてアイドル動作が選ばれます。SMが設定(1)されると休止形態としてパワーダウン動作が選ばれます。詳細については、次の「[休止形態](#)」項を参照してください。

### • ビット3,2 – ISC11,0 : 外部割り込み1条件制御 (Interrupt Sense Control 1 bit1 and 0)

外部割り込み1はステータスレジスタ(SREG)の全割り込み許可(I)ビットと、一般割り込み許可レジスタ(GIMSK)の外部割り込み1許可(INT1)ビットが、共に設定(1)されている場合の外部割り込み1(INT1)ピンによって起動されます。この割り込みを起動する外部割り込み1(INT1)ピン上の端(エッジ)やレベルは表6で定義されます。

表6. 外部割り込み1(INT1)割り込み条件

| ISC11 | ISC10 | 割り込み発生条件          |

|-------|-------|-------------------|

| 0     | 0     | INT1ピンがLowレベルで発生。 |

|       | 1     | (予約)              |

| 1     | 0     | INT1ピンの下降端で発生。    |

|       | 1     | INT1ピンの上昇端で発生。    |

### • ビット1,0 – ISC01,0 : 外部割り込み0条件制御 (Interrupt Sense Control 0 bit1 and 0)

外部割り込み0はステータスレジスタ(SREG)の全割り込み許可(I)ビットと、一般割り込み許可レジスタ(GIMSK)の外部割り込み0許可(INT0)ビットが、共に設定(1)されている場合の外部割り込み0(INT0)ピンによって起動されます。この割り込みを起動する外部割り込み0(INT0)ピン上の端(エッジ)やレベルは表7で定義されます。

表7. 外部割り込み0(INT0)割り込み条件

| ISC01 | ISC00 | 割り込み発生条件          |

|-------|-------|-------------------|

| 0     | 0     | INT0ピンがLowレベルで発生。 |

|       | 1     | (予約)              |

| 1     | 0     | INT0ピンの下降端で発生。    |

|       | 1     | INT0ピンの上昇端で発生。    |

INTnピンの値は端検出以前から採取比較されています。端割り込みが選ばれると、1 CPUクロック周期より長い幅のパルスは割り込みを発生します。短すぎるパルスは割り込みの発生が保証されません。Lowレベル割り込みが選ばれると、割り込みを発生するためには、現在実行中の命令の完了まで、Lowレベルが保持されなければなりません。許可されていれば、レベル起動割り込みはピンがLowに保持されている限り、割り込み要求を発生し続けます。

## 休止形態

休止形態へ移行するには、MCU制御レジスタ(MCUCR)の休止許可(SE)ビットが設定(1)され、SLEEP命令が実行されなければなりません。MCUが休止形態中に許可されている割り込みが発生すると、MCUは起動復帰して、その割り込み処理ルーチンを実行し、そしてSLEEP命令の次から実行を再開します。レジスタファイル、SRAM、I/Oレジスタの内容は変化しません。休止形態中にリセットが起ると、MCUは起動復帰し、リセットベクタから実行します。

### アイドル動作

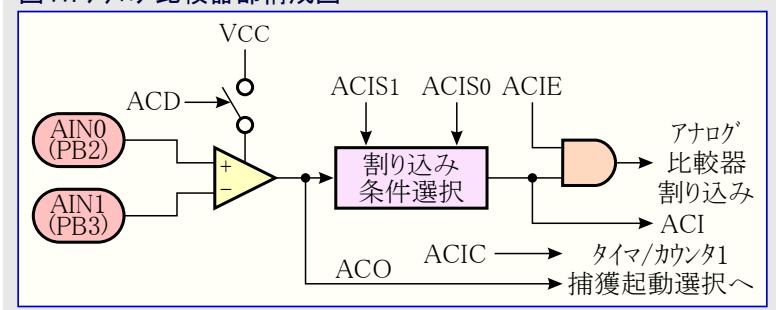

休止種別(SM)ビットが解除(0)されていると、SLEEP命令でMCUがアイドル動作へ移行し、CPUは停止しますが、タイマ/カウンタ、ウォッチドッグ、割り込み機構は継続して動作します。これは、タイマ溢れのような内部割り込みやウォッチドッグのリセットだけでなく、外部で起動される割り込みからもMCUの起動復帰を可能にします。アナログ比較器割り込みからの起動復帰が必要ない場合、[アナログ比較器制御/状態レジスタ\(ACSR\)](#)のアナログ比較器禁止(ACD)ビットを設定(1)することにより、アナログ比較器を電源断にできます。これはアイドル動作での消費電力削減になります。アイドル動作から起動復帰すると、CPUは直ちにプログラムの実行を始めます。

### パワーダウン動作

休止種別(SM)ビットが設定(1)されていると、SLEEP命令でMCUがパワーダウン動作へ移行します。この動作では、外部発振器が停止され、一方、外部割り込みと(許可されていれば)ウォッチドッグは動作を継続します。外部リセット、(許可されていれば)ウォッチドッグリセット、INT0またはINT1の外部レベル割り込みだけがMCUを起動復帰できます。

パワーダウン動作からの起動復帰にレベルで起動された割り込みが使われる時は、このLowレベルがリセット遅延時間( $t_{TOUT}$ )より長い時間保持されなければならないことに注意してください。そうでないとMCUは起動復帰しません。

## タイマ/カウンタ

AT90S4414/8515には8ビットと16ビットの2つの汎用タイマ/カウンタがあります。タイマ/カウンタには、同じ10ビット前置分周器用タイマから選ぶ個別の前置分周器があります。タイマ/カウンタは、内部クロックを基準とするタイマや、外部ピンに接続された起動信号によるカウンタなどの使用ができます。

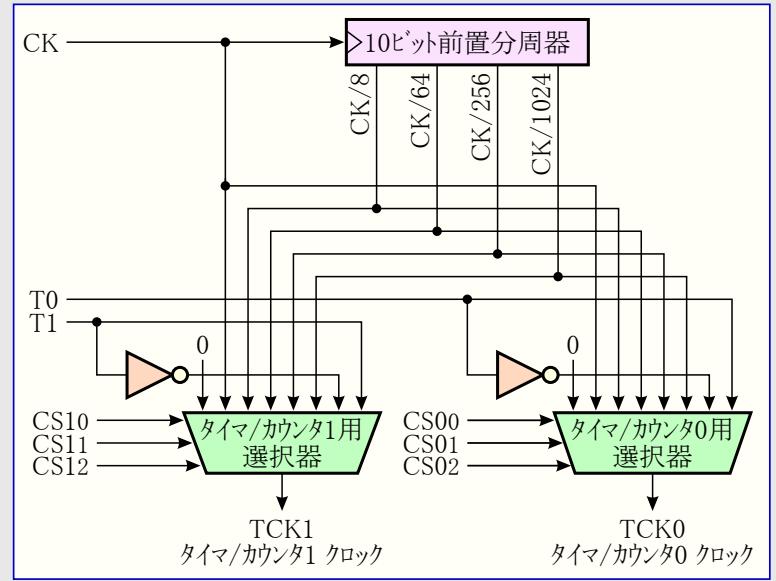

### タイマ/カウンタ前置分周器部

図28.タイマ/カウンタの前置分周器の概略を示します。

前置分周器で分周された4つの異なる選択は、CKを発振器クロックとする、CK/8, CK/64, CK/256, CK/1024です。2つのタイマ/カウンタでは異なる選択として、CK、外部クロック信号、または停止がクロック元として選べます。

図28. タイマ/カウンタ前置分周器部構成

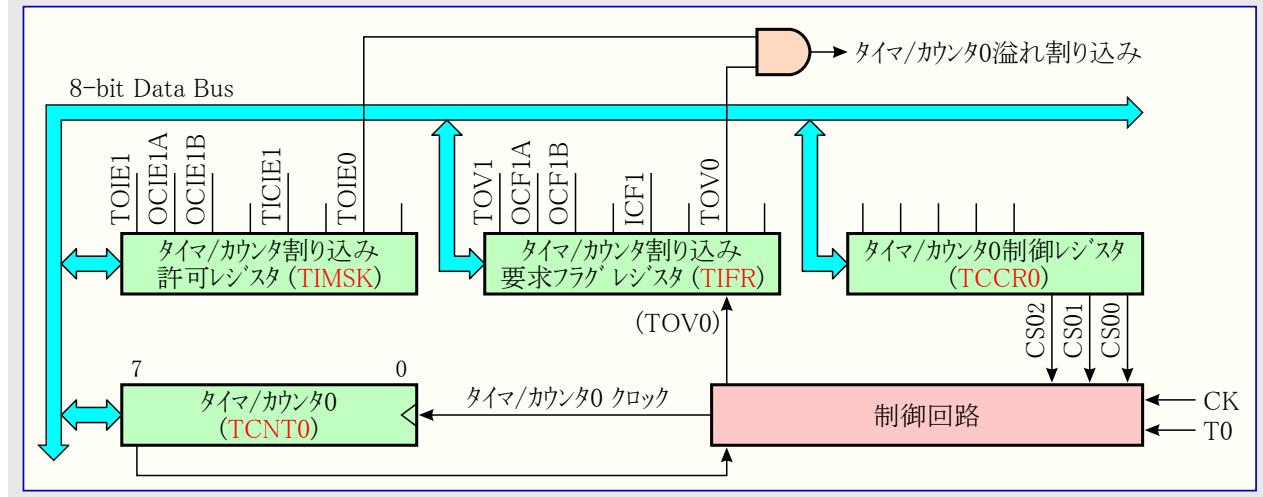

## タイマ/カウンタ0

図29.はタイマ/カウンタ0の構成図を示します。

8ビットのタイマ/カウンタ0は、CK、分周されたCK、または外部ピンからクロック元を選べます。更に、タイマ/カウンタ0制御レジスタ(TCCR0)の詳細で説明されるように停止もできます。溢れ状態フラグ(TOV0)はタイマ/カウンタ割り込み要求フラグレジスタ(TIFR)にあります。制御ビットはタイマ/カウンタ0制御レジスタ(TCCR0)にあります。タイマ/カウンタ0に関する割り込みの許可/禁止設定はタイマ/カウンタ割り込み許可レジスタ(TIMSK)内にあります。

タイマ/カウンタ0が外部的にクロック駆動されるとき、外部信号はCPUの発振器周波数で同期化されます。外部クロックの正しい採取を保証するには、外部クロックの2つの変移間の最小時間が、少なくとも1つの内部CPUクロック周期以上でなければなりません。この外部クロック信号は内部CPUクロックの上昇端で採取されます。

8ビットのタイマ/カウンタ0は低前置分周(使用)機会での高分解能及び高精度の使用が特徴です。同様に高前置分周(使用)機会は低速な目的や稀に動く正確なタイミングの目的についてタイマ/カウンタ0を有効にします。

図29. タイマ/カウンタ0構成図

## タイマ/カウンタ0制御レジスタ (Timer/Counter0 Control Register) TCCR0

| ビット         | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |       |

|-------------|---|---|---|---|---|------|------|------|-------|

| \$33 (\$53) | — | — | — | — | — | CS02 | CS01 | CS00 | TCCR0 |

| Read/Write  | R | R | R | R | R | R/W  | R/W  | R/W  |       |

| 初期値         | 0 | 0 | 0 | 0 | 0 | 0    | 0    | 0    |       |

- ビット7~3 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

- ビット2~0 – CS02~0 : クロック選択0 (Clock Select0, bit 2,1 and 0)

クロック選択0ビット2~0はタイマ/カウンタ0に供給するクロック元を定義します。

表8. タイマ/カウンタ0入力クロック選択

| CS02 | CS01 | CS00 | 意味                             |

|------|------|------|--------------------------------|

| 0    | 0    | 0    | 停止 (タイマ/カウンタ0は動作停止)            |

| 0    | 0    | 1    | CK                             |

| 0    | 1    | 0    | CK/8 (CPUクロックを8分周したクロック)       |

| 0    | 1    | 1    | CK/64 (CPUクロックを64分周したクロック)     |

| 1    | 0    | 0    | CK/256 (CPUクロックを256分周したクロック)   |

| 1    | 0    | 1    | CK/1024 (CPUクロックを1024分周したクロック) |

| 1    | 1    | 0    | 外部T0(PB0)ピンの下降端                |

| 1    | 1    | 1    | 外部T0(PB0)ピンの上昇端                |

停止状態はタイマ/カウンタの許可/禁止機能を提供します。CKの分周出力動作では、発振器クロック(CK)から直接的に分周されます。タイマ/カウンタ0に外部ピン動作が使われると、例えT0(PB0)が出力として設定されていても、このピン上の変移がタイマ/カウンタを計数します。この特徴が計数動作のソフトウェア制御を提供します。

## タイマ/カウンタ0 (Timer/Counter0) TCNT0

| ビット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |       |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|-------|

| \$32 (\$52) | (MSB) |     |     |     |     |     |     | (LSB) | TCNT0 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |       |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |       |

このタイマ/カウンタ0は、読み書きできる上昇カウンタとして実現されます。タイマ/カウンタ0が書かれ、クロック元が存在すると、タイマ/カウンタ0は書き込み動作の次に来るタイマ/カウンタクロック周期で計数を開始/継続します。

## 16ビット タイマ/カウンタ1

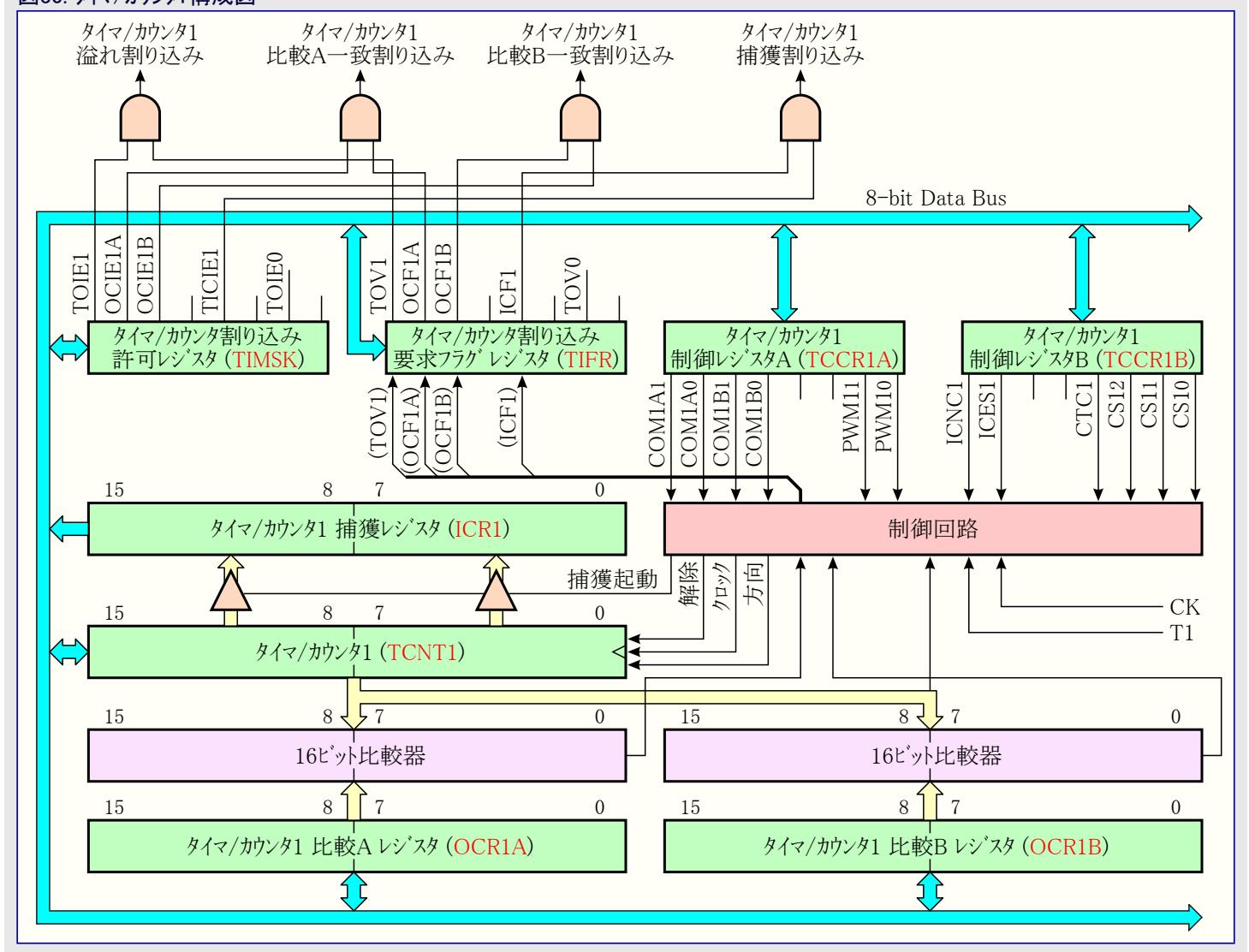

図30.はタイマ/カウンタ1についての構成図を示します。

図30. タイマ/カウンタ1構成図

16ビットのタイマ/カウンタ1はクロック元にCK、分周されたCK、または外部ピンからのクロック元を選べます。更に、[タイマ/カウンタ1制御レジスタ\(TCCR1B\)](#)の詳細で説明されるように停止もできます。各種状態フラグ(溢れ:TOV1、比較A一致:OCF1A、比較B一致: OCF1B、捕獲発生:ICF1)は[タイマ/カウンタ割り込み要求フラグ レジスタ\(TIFR\)](#)にあります。制御ビットは[タイマ/カウンタ1制御レジスタA\(TCCR1A\)](#)と[タイマ/カウンタ1制御レジスタB\(TCCR1B\)](#)にあります。タイマ/カウンタ1に関する割り込みの許可/禁止設定は[タイマ/カウンタ割り込み許可レジスタ\(TIMSK\)](#)内にあります。

タイマ/カウンタ1が外部的にクロック駆動されるとき、外部信号はCPUの発振器周波数で同期化されます。外部クロックの正しい採取を保証するには、外部クロックの2つの変移間の最小時間が、少なくとも1つの内部CPUクロック周期以上でなければなりません。この外部クロック信号は内部CPUクロックの上昇端で採取されます。

16ビットのタイマ/カウンタ1は低前置分周(使用)機会での高分解能及び高精度の使用が特徴です。同様に高前置分周(使用)機会は低速な目的や稀に動く正確なタイミングの目的についてタイマ/カウンタ1を有効にします。

タイマ/カウンタ1は、タイマ/カウンタ1の内容と比較されるデータ元として比較レジスタ(OCR1AとOCR1B)を使う比較出力機能を支援します。この比較出力機能は、選択可能な比較一致でのカウンタの解除(=\$0000)や、両方の比較一致での比較出力(OC1AとOC1B)ピン上の動作を含みます。

タイマ/カウンタ1は8,9または10ビットのパルス幅変調器(PWM)としても使えます。この動作では、タイマ/カウンタ1(TCNT1)と比較レジスタ(OCR1AとOCR1B)は、不具合の無い周期中央パルス方式の独立したPWMとして扱えます。この機能の詳細説明については[27頁](#)を参照してください。

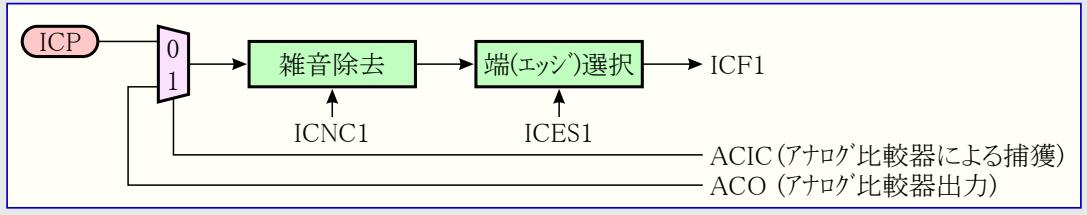

タイマ/カウンタ1の捕獲機能は、ICPピンの外部要因により起動される、タイマ/カウンタ1の内容の捕獲レジスタ(ICR1)への捕獲(複写)を提供します。実際の捕獲要因(条件)は、タイマ/カウンタ1制御レジスタB(TCCR1B)により定義されます。加えて、アナログ比較器は捕獲の起動に設定できます。この詳細については、[39頁](#)の「[アナログ比較器](#)」を参照してください。ICPピンの回路は図31.で示されます。

図31. ICPピン回路構成

雑音除去機能が許可されると、捕獲についての実際の起動条件は4回の採取に渡って監視され、捕獲フラグを有効とするには4回全てが同じでなければなりません。

#### タイマ/カウンタ1制御レジスタA (Timer/Counter1 Control Register A) TCCR1A

| ビット         | 7      | 6      | 5      | 4      | 3 | 2 | 1     | 0     |        |

|-------------|--------|--------|--------|--------|---|---|-------|-------|--------|

| \$2F (\$4F) | COM1A1 | COM1A0 | COM1B1 | COM1B0 | - | - | PWM11 | PWM10 | TCCR1A |

| Read/Write  | R/W    | R/W    | R/W    | R/W    | R | R | R/W   | R/W   |        |

| 初期値         | 0      | 0      | 0      | 0      | 0 | 0 | 0     | 0     |        |

##### ・ビット7,6 – COM1A1,0 : 比較A出力選択 (Compare Output Mode1A bit 1 and 0)

このCOM1A1とCOM1A0制御ビットは、[タイマ/カウンタ1\(TCNT1\)](#)での比較A一致に続く、何れかの出力ピン動作を決めます。何れかの出力ピン動作はOC1A/PD5(比較A出力)ピンに影響を及ぼします。これはI/Oポートの交換機能で、対応する方向制御ビットは出力ピンを制御するため、設定(1)されなければなりません(DDD5=1)。制御設定は表9で示されます。

##### ・ビット5,4 – COM1B1,0 : 比較B出力選択 (Compare Output Mode1B bit 1 and 0)

このCOM1B1とCOM1B0制御ビットは、[タイマ/カウンタ1\(TCNT1\)](#)での比較B一致に続く、何れかの出力ピン動作を決めます。何れかの出力ピン動作はOC1B(比較B出力)ピンに影響を及ぼします。制御設定は表9で示されます。

表9. 比較出力選択

| COM1x1 | COM1x0 | 意味               |

|--------|--------|------------------|

| 0      | 0      | OC1x切斷           |

| 0      | 1      | OC1xピントグル(交互)出力  |

| 1      | 0      | OC1xピン Lowレベル出力  |

| 1      | 1      | OC1xピン Highレベル出力 |

注: • x=AまたはB

- PWM動作では、これらのビットは異なる機能をちます。詳細説明については[27頁の表13](#)を参照してください。

##### ・ビット3,2 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

##### ・ビット1,0 – PWM11,0 : PWM動作選択 (Pulse Width Modulator Select bit 1 and 0)

これらのビットは表10に示されるタイマ/カウンタ1のPWM動作を選びます。この動作は[27頁](#)で説明されます。

表10. PWM動作選択

| PWM11 | PWM10 | 意味       |

|-------|-------|----------|

| 0     | 0     | PWM動作禁止  |

| 0     | 1     | 8ビットPWM  |

| 1     | 0     | 9ビットPWM  |

| 1     | 1     | 10ビットPWM |

## タイマ/カウンタ1制御レジスタB (Timer/Counter1 Control Register B) TCCR1B

| ビット         | 7     | 6     | 5 | 4 | 3    | 2    | 1    | 0    |        |

|-------------|-------|-------|---|---|------|------|------|------|--------|

| \$2E (\$4E) | ICNC1 | ICES1 | — | — | CTC1 | CS12 | CS11 | CS10 | TCCR1B |

| Read/Write  | R/W   | R/W   | R | R | R/W  | R/W  | R/W  | R/W  |        |

| 初期値         | 0     | 0     | 0 | 0 | 0    | 0    | 0    | 0    |        |

### • ビット7 – ICNC1 : 捕獲起動入力雑音除去 (Input Capture1 Noise Canceler)

ICNC1ビットが解除(0)されると、捕獲起動入力の雑音除去機能が禁止されます。捕獲は説明されたように、ICP(捕獲起動入力)ピンで採取された最初の上昇端/下降端で起動されます。ICNC1が設定(1)されると、ICP(捕獲起動入力)ピンで連続する4回の採取が揃い、全ての採取がICES1ビットでの捕獲起動条件設定に対応するhigh/Lowでなければなりません。実際の採取周波数はXTAL(システム)クロック周波数です。

### • ビット6 – ICES1 : 捕獲起動入力端選択 (Input Capture1 Edge Select)

ICES1が解除(0)されている間中、**タイマ/カウンタ1**の内容は捕獲起動入力(ICP)ピンの下降端で**捕獲レジスタ(ICR1)**へ転送されます。ICES1ビットが設定(1)されている間中、タイマ/カウンタ1の内容は捕獲起動入力(ICP)ピンの上昇端で捕獲レジスタへ転送されます。

### • ビット5,4 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

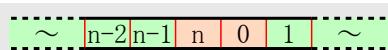

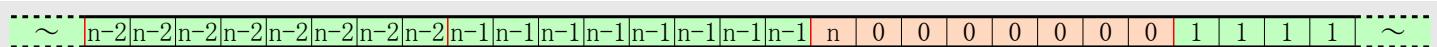

### • ビット3 – CTC1 : 一致解除許可 (Clear Timer/Counter1 on Compare Match)

CTC1制御ビットが設定(1)されると、タイマ/カウンタ1は比較A一致後のクロック周期で\$0000にリセットされます。CTC1制御ビットが解除(0)されると、タイマ/カウンタ1は比較一致による影響を受けず計数動作を続けます。比較一致は一致に続くCPUクロック周期で検出されるため、1より大きい前置分周値が使われる時はこの動作が違う動作になります。前置分周値が1で、比較Aレジスタ(OCR1A)にnが設定されている時にCTC1が設定(1)されると、タイマ/カウンタ1は次のように計数します。

前置分周器がCK/8分周に設定されていると、タイマ/カウンタ1は次のように計数します。

**PWM動作**では、このビットは無効です。

### • ビット2~0 – CS12~0 : クロック選択1 (Clock Select1, bit 2,1 and 0)

このクロック選択1ビット2~0はタイマ/カウンタ1(TCNT1)に供給するクロックを定義します。

表11. タイマ/カウンタ1入力クロック選択

| CS12 | CS11 | CS10 | 意味                             |

|------|------|------|--------------------------------|

| 0    | 0    | 0    | 停止 (タイマ/カウンタ1は動作停止)            |

| 0    | 0    | 1    | CK                             |

| 0    | 1    | 0    | CK/8 (CPUクロックを8分周したクロック)       |

| 0    | 1    | 1    | CK/64 (CPUクロックを64分周したクロック)     |

| 1    | 0    | 0    | CK/256 (CPUクロックを256分周したクロック)   |

| 1    | 0    | 1    | CK/1024 (CPUクロックを1024分周したクロック) |

| 1    | 1    | 0    | 外部T1(PB1)ピンの下降端                |

| 1    | 1    | 1    | 外部T1(PB1)ピンの上昇端                |

停止状態はタイマ/カウンタの動作許可/禁止機能を提供します。CKが分周される動作では発振器クロックCKから直接的に分周されます。タイマ/カウンタ1に外部ピン動作が使われると、T1(PB1)が出力として設定されていても、このピン上の変移はカウンタを駆動します。この特徴が計数動作のソフトウェア制御を可能にします。

## タイマ/カウンタ1 (Timer/Counter1) TCNT1H,TCNT1L (TCNT1)

| ビット<br>\$2D (\$4D) | 15<br>(MSB) | 14  | 13  | 12  | 11  | 10  | 9   | 8   | TCNT1H       |

|--------------------|-------------|-----|-----|-----|-----|-----|-----|-----|--------------|

| Read/Write         | R/W         | R/W | R/W | R/W | R/W | R/W | R/W | R/W |              |

| 初期値                | 0           | 0   | 0   | 0   | 0   | 0   | 0   | 0   |              |

| ビット<br>\$2C (\$4C) | 7           | 6   | 5   | 4   | 3   | 2   | 1   | 0   | (LSB) TCNT1L |

| Read/Write         | R/W         | R/W | R/W | R/W | R/W | R/W | R/W | R/W |              |

| 初期値                | 0           | 0   | 0   | 0   | 0   | 0   | 0   | 0   |              |

この16ビットレジスタは16ビットのタイマ/カウンタ1の前置分周された値を含みます。CPUがこれらのレジスタをアクセスするとき、上位と下位のバイトの両方が同時に読み書きされることを保証するため、このアクセスは8ビットの一時レジスタ(TEMP)を使って実行されます。この一時レジスタは、比較レジスタ(OCR1A, OCR1B)や捕獲レジスタ(ICR1)をアクセスするときにも使われます。主プログラムと割り込みルーチンがTEMPを使うレジスタにアクセスする場合、主プログラムや(多重割り込みを許す)割り込みルーチンからのアクセス中、割り込みは禁止されなければなりません。

## • タイマ/カウンタ1(TCNT1)書き込み (Timer/Counter1 Write)

CPUが上位バイト(TCNT1H)に書くとき、書かれたデータは一時レジスタ(TEMP)に置かれます。次にCPUが下位バイト(TCNT1L)に書くとき、TEMP内のバイトデータと組み合わされ、16ビット全てがタイマ/カウンタ1(TCNT1)へ同時に書かれます。従って、完全な16ビットレジスタ書き込み操作では、**上位バイト(TCNT1H)が先にアクセスされなければなりません**。

## • タイマ/カウンタ1(TCNT1)読み込み (Timer/Counter1 Read)

CPUが下位バイト(TCNT1L)を読むとき、下位バイト(TCNT1L)のデータがCPUへ送られ、上位バイト(TCNT1H)のデータが一時レジスタ(TEMP)に置かれます。CPUが上位バイト(TCNT1H)を読むとき、CPUはTEMP内のデータを受け取ります。従って、完全な16ビットレジスタ読み込み操作では、**下位バイト(TCNT1L)が先にアクセスされなければなりません**。

タイマ/カウンタ1は読み書き可能な上昇/下降(PWM動作時)カウンタとして実現されます。クロック供給元が選ばれ、タイマ/カウンタ1が書かれるとき、タイマ/カウンタ1は書かれた値を設定後、次のタイマ/カウンタ1 クロック周期で計数を開始/継続します。

## タイマ/カウンタ1 比較Aレジスタ (Timer/Counter1 Output Compare Register A) OCR1AH,OCR1AL (OCR1A)

| ビット         | 15    | 14  | 13  | 12  | 11  | 10  | 9   | 8   |              |

|-------------|-------|-----|-----|-----|-----|-----|-----|-----|--------------|

| \$2B (\$4B) | (MSB) |     |     |     |     |     |     |     | OCR1AH       |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W |              |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0   |              |

| ビット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |              |

| \$2A (\$4A) |       |     |     |     |     |     |     |     | (LSB) OCR1AL |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W |              |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0   |              |

## タイマ/カウンタ1 比較Bレジスタ (Timer/Counter1 Output Compare Register B) OCR1BH,OCR1BL (OCR1B)

| ビット         | 15    | 14  | 13  | 12  | 11  | 10  | 9   | 8   |              |

|-------------|-------|-----|-----|-----|-----|-----|-----|-----|--------------|

| \$29 (\$49) | (MSB) |     |     |     |     |     |     |     | OCR1BH       |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W |              |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0   |              |

| ビット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |              |

| \$28 (\$48) |       |     |     |     |     |     |     |     | (LSB) OCR1BL |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W |              |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0   |              |

比較レジスタは読み書き可能な16ビットのレジスタです。

このタイマ/カウンタ1比較レジスタ(OCR1A, OCR1B)は、[タイマ/カウンタ1\(TCNT1\)](#)と継続的に比較されるべきデータを保持します。比較一致での動作は[タイマ/カウンタ1の制御と状態のレジスタ](#)で詳細に示されます。比較一致はタイマ/カウンタ1がOCR値を計数する場合のみ起きます。TCNT1とOCR1AまたはOCR1Bに同じ値を設定するソフトウェア書き込みでは、比較一致を生成しません。

比較一致は比較での出来事に続くCPUクロック周期で比較一致割り込み要求フラグ(OCF1A, OCF1B)を設定(1)します。

この比較レジスタ(OCR1AとOCR1B)は16ビット レジスタなので、両方のバイトが同時に更新されるのを保証するため、OCR1A/Bが書かれる時には一時レジスタ(TEMP)が使われます。CPUが上位バイト(OCR1AHまたはOCR1BH)に書くとき、データはTEMP内に保存されます。CPUが下位バイト(OCR1ALまたはOCR1BL)に書くとき、TEMPの値が同時に上位バイト(OCR1AHまたはOCR1BH)へ書かれます。従って、完全な16ビット レジスタの書き込み操作では、[上位バイト\(OCR1AHまたはOCR1BH\)が先に書かれなければなりません。](#)

この一時レジスタは[タイマ/カウンタ1\(TCNT1\)](#)や[捕獲レジスタ\(ICR1\)](#)をアクセスするときにも使われます。主プログラムと割り込みルーチンがTEMPを使うレジスタにアクセスする場合、主プログラムや(多重割り込みを許す)割り込みルーチンからのアクセス中、割り込みは禁止されなければなりません。

## タイマ/カウンタ1 捕獲レジスタ (Timer/Counter1 Input Capture Register) ICR1H,ICR1L (ICR1)

| ビット         | 15    | 14 | 13 | 12 | 11 | 10 | 9 | 8 |             |

|-------------|-------|----|----|----|----|----|---|---|-------------|

| \$25 (\$45) | (MSB) |    |    |    |    |    |   |   | ICR1H       |

| Read/Write  | R     | R  | R  | R  | R  | R  | R | R |             |

| 初期値         | 0     | 0  | 0  | 0  | 0  | 0  | 0 | 0 |             |

| ビット         | 7     | 6  | 5  | 4  | 3  | 2  | 1 | 0 |             |

| \$24 (\$44) |       |    |    |    |    |    |   |   | (LSB) ICR1L |

| Read/Write  | R     | R  | R  | R  | R  | R  | R | R |             |

| 初期値         | 0     | 0  | 0  | 0  | 0  | 0  | 0 | 0 |             |

捕獲レジスタは読み込みのみ可能な16ビットのレジスタです。

捕獲起動入力(ICP)pinで、[タイマ/カウンタ1制御レジスタB\(TCCR1B\)](#)の捕獲起動入力選択(ICES1)に従った信号の上昇端/下降端が検出されると、現在の[タイマ/カウンタ1\(TCNT1\)](#)の値が捕獲レジスタ(ICR1)に転送されます。同時に[タイマ/カウンタ割り込み要求フラグ レジスタ\(TIFR\)](#)の捕獲割り込み要求フラグ(ICF1)が設定(1)されます。

この捕獲レジスタ(ICR1)が16ビット レジスタのため、両方のバイトが同時に読まれるのを保証するために、ICR1が読まれるときには一時レジスタ(TEMP)が使われます。CPUが下位バイト(ICR1L)を読むとき、そのデータがCPUへ送られ、上位バイト(ICR1H)のデータがTEMPに置かれます。CPUが上位バイト(ICR1H)のデータを読むとき、CPUはTEMP内のデータを受け取ります。従って、完全な16ビット レジスタ読み込み操作では、[下位バイト\(ICR1L\)が先に読まれなければなりません。](#)

この一時レジスタは、タイマ/カウンタ1(TCNT1)や比較レジスタ(OCR1A,OCR1B)をアクセスするときにも使われます。主プログラムと割り込みルーチンがTEMPを使うレジスタにアクセスする場合、主プログラムや(多重割り込みを許す)割り込みルーチンからのアクセス中、割り込みは禁止されなければなりません。

## タイマ/カウンタ1 PWM動作

PWM動作が選ばれると、タイマ/カウンタ1(TCNT1)、比較Aレジスタ(OCR1A)、比較Bレジスタ(OCR1B)は自走動作で不具合のない位相基準の8,9または10ビットPWMとOC1A(PD5)とOC1Bピン出力を形成します。タイマ/カウンタ1は上昇/下降カウントとして動作し、\$0000からTOP(上限値:表12.参照)まで上昇計数し、その周期が繰り返される前に向きを変えて再び\$0000まで下降計数します。タイマ/カウンタ1値がOCR1AまたはOCR1Bの最下位側8,9または10ビットの内容と一致すると、OC1A(PD5)またはOC1Bピンはタイマ/カウンタ1制御レジスタA(TCCR1A)の比較A出力選択(COM1A1, COM1A0)または比較B出力選択(COM1B1, COM1B0)の設定に従って設定(High)または解除(Low)されます。詳細については表13.を参照してください。

表12. PWM分解能対計数上限値、PWM周波数の関係

| PWM分解能 | TOP(計数上限値)   | PWM周波数     | 備考                        |

|--------|--------------|------------|---------------------------|

| 8ビット   | \$00FF(255)  | fTCK1/510  | fTCK1=タイマ/カウンタ1のクロック入力周波数 |

| 9ビット   | \$01FF(511)  | fTCK1/1022 |                           |

| 10ビット  | \$03FF(1023) | fTCK1/2046 |                           |

表13. PWM出力選択(比較出力選択と兼用)

| COM1x1 | COM1x0 | OC1x出力                                       |

|--------|--------|----------------------------------------------|

| 0      | 0      | OC1x出力切断(PD5は標準I/Oとして動作)                     |

| 0      | 1      |                                              |

| 1      | 0      | 上昇計数時の一一致で解除(Low)、下降計数時の一一致で設定(High) [非反転出力] |

| 1      | 1      |                                              |

注: x=AまたはB

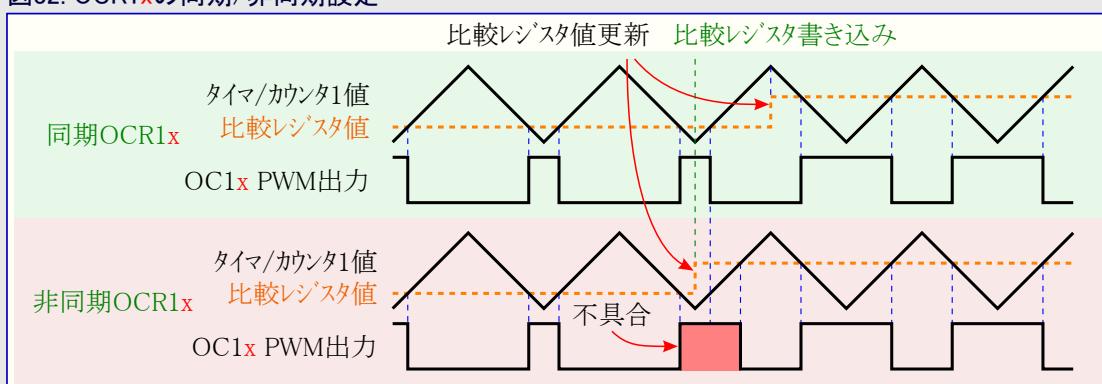

PWM動作では、比較レジスタ(OCR1A/OCR1B)が書かれるとき、最下位側10ビットが一時領域に転送されることに注意してください。これらはタイマ/カウンタ1(TCNT1)が上限値(TOP)に到達するとき、比較レジスタに設定されます。これはOCR1A/OCR1B非同期書き込みでの奇数長PWMパルス(不具合)の発生を防止します。この例については図32.を参照してください。

図32. OCR1xの同期/非同期設定

注: x=AまたはB

書き込みと実際の設定間、OCR1AまたはOCR1B読み込みは一時領域の内容が読まれます。これは常に最も最近書かれた値がOCR1A/OCR1Bの読み出しどとなることを意味します。

OCR1A/OCR1Bが\$0000または上限値(TOP)を含むと、OC1A/OC1B出力は次の比較一致で、TCCR1AのCOM1A1とCOM1A0またはCOM1B1とCOM1B0の指定に従って、HighまたはLowに更新/保持されます。これは表14.で示されます。

注: 比較レジスタ(OCR1A/OCR1B)が上限値(TOP)で、前置分周器を使わない(CS12~0=001)場合、上昇計数と下降計数の値が同時に到達されるため、PWM出力はまったくパルスを生成しません。前置分周器を使う(CS12~0≠001または000)と、タイマ/カウンタ1が上限値に達すると、PWM出力は動きますが、次回にタイマ/カウンタ1が上限値へ達する前の下降計数での至るべき比較一致が判定されませんので、1周期(回)のPWMパルスになってしまいます。

表14. 上限値、下限値でのPWM出力

| COM1x1 | COM1x0 | OCR1x  | OC1x出力 |

|--------|--------|--------|--------|

| 1      | 0      | \$0000 | L      |

|        |        | 上限値    | H      |

| 1      | 1      | \$0000 | H      |

|        |        | 上限値    | L      |

注: x=AまたはB

PWM動作ではタイマ/カウンタ1が\$0000から進む時にタイマ/カウンタ1溢れ(TOV1)フラグが設定(1)されます。タイマ/カウンタ1溢れ割り込みは通常動作、換言すると、ステータスレジスタ(SREG)の全割り込み許可(I)ビットとタイマ/カウンタ割り込み許可レジスタ(TIMSK)のタイマ/カウンタ1溢れ割り込み許可(TOIE1)ビットが許可されていれば、TOV1が設定(1)される時に割り込みが実行されるように、正確に動作します。これは比較一致割り込み(OCF1A, OCF1B)フラグと割り込みについても適用されます。

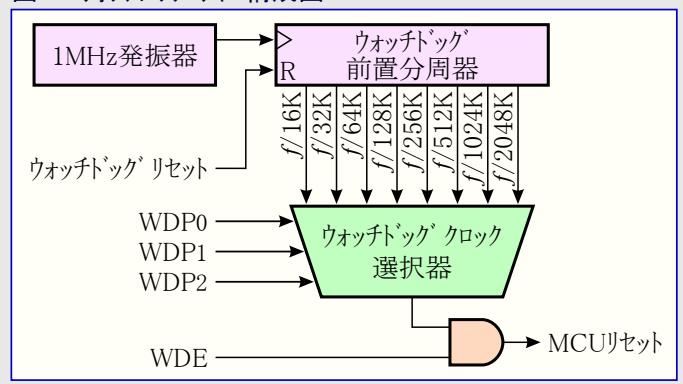

## ウォッチドッグ タイマ

このウォッチドッグ タイマは、1MHzで動作する独立した内蔵発振器から駆動されます。この周波数はVCC=5Vでの代表値です。他の電源電圧での代表値については特性データを参照してください。ウォッチドッグ タイマの前置分周器を制御することにより、ウォッチドッグ リセット周期は調整できます。詳細説明については表15.を参照してください。ウォッチドッグ リセット(WDR)命令はウォッチドッグ タイマをリセットします。8つの異なるクロック周期は、このリセット周期を決めるために選ばれます。他のウォッチドッグ リセット(WDR命令)なしで、このリセット周期が経過すると、AT90S4414/8515はリセットし、リセット ベクタから実行します。ウォッチドッグ リセットの詳細タイミングについては、14頁を参照してください。

予期せぬウォッチドッグ 禁止を防止するため、ウォッチドッグが禁止されるとき、特別なOFF切り替え手順に従わなければなりません。詳細についてはウォッチドッグ タイマ制御レジスタの説明を参照してください。

図33. ウォッチドッグ タイマ構成図

### ウォッチドッグ タイマ制御レジスタ (Watchdog Timer Control Register) WDTCR

| ビット          | 7 | 6 | 5 | 4     | 3   | 2    | 1    | 0    |       |

|--------------|---|---|---|-------|-----|------|------|------|-------|

| \$21 \$ (41) | - | - | - | WDTOE | WDE | WDP2 | WDP1 | WDP0 | WDTCR |

| Read/Write   | R | R | R | R/W   | R/W | R/W  | R/W  | R/W  |       |

| 初期値          | 0 | 0 | 0 | 0     | 0   | 0    | 0    | 0    |       |

• ビット7~5 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

• ビット4 – WDTOE : ウォッチドッグ 停止移行許可 (Watchdog Turn-off Enable)

ウォッチドッグ 許可(WDE)ビットが解除(0)されるとき、このビットは設定(1)されなければなりません。さもなければ、ウォッチドッグは禁止されません。一度設定(1)すると、4クロック周期後、ハードウェアがこのビットを0に解除します。ウォッチドッグ 禁止手順についてはWDEビットの説明を参照してください。

• ビット3 – WDE : ウォッチドッグ 許可 (Watchdog Enable)

このWDEが設定(1)されるとウォッチドッグ タイマが許可され、解除(0)されるとウォッチドッグ タイマ機能が禁止されます。WDEはウォッチドッグ 停止移行許可(WDTOE)ビットが設定(1)されている場合のみ解除(0)できます。許可されたウォッチドッグ タイマを禁止するには次の手順に従わなければなりません。

1. 同じ操作内で、WDTOEとWDEに論理1を書きます。禁止操作開始前が1に設定されていても、論理1がWDEに書かれなければなりません。

2. 次の4クロック以内に、WDEへ論理0を書きます。これがウォッチドッグを禁止します。

• ビット2~0 – WDP2~0 : ウォッチドッグ タイマ 前置分周器選択 (Watchdog Timer Prescaler 2,1 and 0)

このWDP2~0は、ウォッチドッグ タイマが許可されるときのウォッチドッグ タイマの前置分周を決めます。各前置分周値と対応する計時完了周期は表15.に示されます。

表15. ウォッチドッグ 前置分周器選択

| WDP2 | WDP1 | WDP0 | WDT発振周期数 | 代表的な計時完了周期 |          |

|------|------|------|----------|------------|----------|

|      |      |      |          | VCC=3.0V   | VCC=5.0V |

| 0    | 0    | 0    | 16K      | 47ms       | 15ms     |

| 0    | 0    | 1    | 32K      | 94ms       | 30ms     |

| 0    | 1    | 0    | 64K      | 0.19s      | 60ms     |

| 0    | 1    | 1    | 128K     | 0.38s      | 0.12s    |

| 1    | 0    | 0    | 256K     | 0.75s      | 0.24s    |

| 1    | 0    | 1    | 512K     | 1.5s       | 0.49s    |

| 1    | 1    | 0    | 1024K    | 3.0s       | 0.97s    |

| 1    | 1    | 1    | 2048K    | 6.0s       | 1.9s     |

注: 68頁の「代表特性」内で示されるように、ウォッチドッグ 発振器の周波数は電圧に依存します。

ウォッチドッグ タイマが許可される前に、常にウォッチドッグ リセット(WDR)命令が実行されるべきです。これはウォッチドッグ タイマ前置分周器設定に一致するリセット周期を保証します。このリセット操作なしにウォッチドッグが許可されると、ウォッチドッグ タイマは0から計数を開始しないかもしれません。

予期せぬMCUリセットを避けるため、ウォッチドッグ タイマ前置分周器選択の変更前には、ウォッチドッグ タイマが禁止されるかりセットされるべきです。

## EEPROMアクセス

EEPROMをアクセスするレジスタはI/O空間でアクセスできます。

書き込み時間はVCC電圧に依存し、2.5~4msの範囲です。(書き込みは)自己タイミング機能ですが、使用者ソフトウェアは次バイトが書ける時を検知してください。使用者コードがEEPROMに書く命令を含む場合、いくつかの予防処置が取られなければなりません。厳重に濾波した電源では、電源投入/切断でVCCが緩やかに上昇または下降しそうです。これはデバイスが何周期かの時間、使われるクロック周波数に於いて最小として示されるより低い電圧で走行する原因になります。これらの条件下のCPU動作はプログラムカウントに予期せぬ分岐を実行させるかもしれません、結果的にEEPROM書き込みコードを実行する原因になりそうです。この場合、完全にEEPROMを保護するために外部低電圧リセット回路の使用が推奨されます。

不測のEEPROM書き込みを防ぐため、特別な書き込み手順に従わなければなりません。この詳細については「[EEPROM制御レジスタ\(EECR\)](#)」の記述を参照してください。

EEPROMが書かれるとき、CPUは次の命令が実行される前に2クロック周期停止されます。EEPROMが読まれるとき、CPUは次の命令が実行される前に4クロック周期停止されます。

### EEPROMアドレス レジスタ (EEPROM Address Register) EEARH,EEARL (EEAR)

| ビット         | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     | EEAR8   | EEARH |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|---------|-------|

| \$1F (\$3F) | -     | -     | -     | -     | -     | -     | -     | EEAR8 | EEARH   |       |

| Read/Write  | R     | R     | R     | R     | R     | R     | R     | R/W   |         |       |

| 初期値         | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |         |       |

| ビット         | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | EEAR7~0 | EEARL |

| \$1E (\$3E) | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEAR7~0 | EEARL |

| Read/Write  | R/W     |       |

| 初期値         | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |         |       |

#### ・ビット8~0 – EEAR8~0 : EEPROMアドレス (EEPROM Address)

AT90S8515は、EEPROMアドレス レジスタ(EEARHとEEARLのEEAR8~0)で512バイト、AT90S4414は、EEARLのEEAR7~0で256バイトのEEPROM空間のEEPROMアドレスを指定します。AT90S4414にはEEARHがありません。EEPROMデータのバイトは0~255/511間で直線的に配置されています。

### EEPROMデータ レジスタ (EEPROM Data Register) EEDR

| ビット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0   | (LSB) | EEDR |

|-------------|-------|-----|-----|-----|-----|-----|-----|-----|-------|------|

| \$1D (\$3D) | (MSB) |     |     |     |     |     |     |     | (LSB) | EEDR |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |      |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0     |      |

#### ・ビット7~0 – EEDR7~0 : EEPROMデータ (EEPROM Data)

EEPROM書き込み操作について、EEDRはEEPROMアドレス レジスタ(EEAR)で与えられるアドレスのEEPROMに書かれるデータです。EEPROM読み込み操作では、EEDRがEEARで与えられるアドレスのEEPROMから読み出されたデータです。

### EEPROM制御レジスタ (EEPROM Control Register) EECR

| ビット         | 7 | 6 | 5 | 4 | 3 | 2     | 1    | 0    | EEMWE | EEWE | EERE | EECR |

|-------------|---|---|---|---|---|-------|------|------|-------|------|------|------|

| \$1C (\$3C) | - | - | - | - | - | EEMWE | EEWE | EERE | EEMWE | EEWE | EERE | EECR |

| Read/Write  | R | R | R | R | R | R/W   | R/W  | R/W  | R/W   | R/W  | R/W  |      |

| 初期値         | 0 | 0 | 0 | 0 | 0 | 0     | 0    | 0    | 0     | 0    | 0    |      |

#### ・ビット7~3 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

#### ・ビット2 – EEMWE : EEPROM主書き込み許可 (EEPROM Master Write Enable)

このEEMWEビットは、EEPROM書き込み許可(EEWE)ビットの1設定がEEPROM書き込みの原因となるかどうかを決定します。EEMWEが設定(1)されるとき、EEWEの1設定は選ばれたアドレスのEEPROMにデータを書きます。EEMWEが0の場合、EEWEの1設定は無効です。EEMWEがソフトウェアによって設定(1)されてしまうと、4クロック周期後、自動的に解除(0)されます。EEPROM書き込み手順については次の「書き込み許可(EEWE)ビット」の記述を参照してください。

#### • ビット1 – EEWE : EEPROM書き込み許可 (EEPROM Write Enable)

このEEPROM書き込み許可信号(EEWE)はEEPROMへの書き込みストローブです。アドレスとデータが適切に設定されると、EEPROMへこの値を書き込むために、このEEWEビットを設定(1)しなければなりません。論理1がEEWEに書かれるとき、EEPROM主書き込み許可(EEMWE)ビットは設定(1)されなければならず、そうしないと、EEPROM書き込みは行われません。EEPROMを書く時は次の手順に従うべきです(手順2.と3.の順番は重要ではありません)。

1. EEPROM書き込み許可(EEWE)ビットが0になるまで待機します。

2. 今回のEEPROMアドレスをEEPROMアドレスレジスタ(EEARHとEEARL)に書きます。(任意、省略可)

3. 今回のEEPROMデータをEEPROMデータレジスタ(EEDR)に書きます。(任意、省略可)

4. EEPROM制御レジスタ(EECR)のEEPROM主書き込み許可(EEMWE)ビットに論理1を書きます。(EEMWEビットに論理1が書けるためには、同一周期内でEEWEビットは0が書かれなければなりません。)

5. EEMWE設定後4クロック周期内に、EEPROM書き込み許可(EEWE)ビットへ論理1を書きます。

書き込み時間(代表値で、2.5ms/VCC=5V, 4ms/VCC=2.7V)が経過してしまうと、EEWEビットは自動的に解除(0)されます。次のバトを書く前に、このビットをポーリングして0まで待機できます。EEWEが設定(1)されてしまうと、次の命令が実行される前に、CPUは2周期停止されます。

**警告:** 手順4.と5.間の割り込みは、EEPROM主書き込み許可が時間超過となるため、書き込み周期失敗になります。EEPROMをアクセスする割り込み処理ルーチンが他のEEPROMアクセスで割り込み、EEARまたはEEDRを変更すると、割り込まれたEEPROMアクセスが失敗する原因になります。これらの問題を防ぐため、手順2.~5.の間中、ステータスレジスタ(SREG)の全割り込み許可(I)ビットは解除(0)されていることが推奨されます。

#### • ビット0 – EERE : EEPROM読み込み許可 (EEPROM Read Enable)

このEEPROM読み込み許可信号(EERE)はEEPROMへの読み込みストローブです。EEARに適切なアドレスが設定されると、このEEREビットを設定(1)しなければなりません。EEREビットが自動的に解除(0)されると、求められたデータがEEDR内にあります。EEPROM読み込みアクセスは1命令で行われるので、EEREビットのポーリングは必要ありません。EEREが設定(1)されてしまうと、次の命令が実行される前にCPUは4周期停止されます。

読み込み操作を始める前にEEWEビットをポーリングすべきです。新規データまたはアドレスがEEPROM I/Oレジスタに書かれるときに書き込み動作が実行中の場合、書き込み動作は阻止され、結果が不定にされます。

### EEPROMデータ化けの防止

電源電圧が低すぎる時のCPUやEEPROMの動作特性により、低VCCの期間中、EEPROMデータが化けてしまいます。これらはEEPROMを使った基板レベルの問題と同じで、同じ設計上の解決法が適用されるべきです。

EEPROMデータ化けが発生する低電源電圧は、2つの場合が想定できます。1つ目は、EEPROM書き込み動作に必要な最低電圧以下の場合で、2つ目は、CPUが命令を実行するに必要な最低電圧以下の場合です。

次の推奨設計(内の1つで充分)により、EEPROMのデータ化けは容易に避けることができます。

- 電源の供給電圧が不足する時間中、AVRのRESETを有効(Low)に保ちます。これは外部低VCCリセット保護回路による実現が最善で、これはブランクアウト検出器(BOD)として度々参照されます。電源ONリセットと低電圧検出に関する設計上の考慮については、応用記述のAVR180を参照してください。

- 低VCCの時間中、AVRコアをパワーダウン休止動作に保ちます。これはCPUを命令の復号と実行を試みないように防ぎ、不測の書き込みからEEPROMレジスタを保護する効果があります。

- ソフトウェアからメモリ内容を変更できることが必要とされない場合、[フラッシュメモリ](#)に定数を格納します。フラッシュメモリはCPUにより更新されることができないので、データ化けの問題はありません。

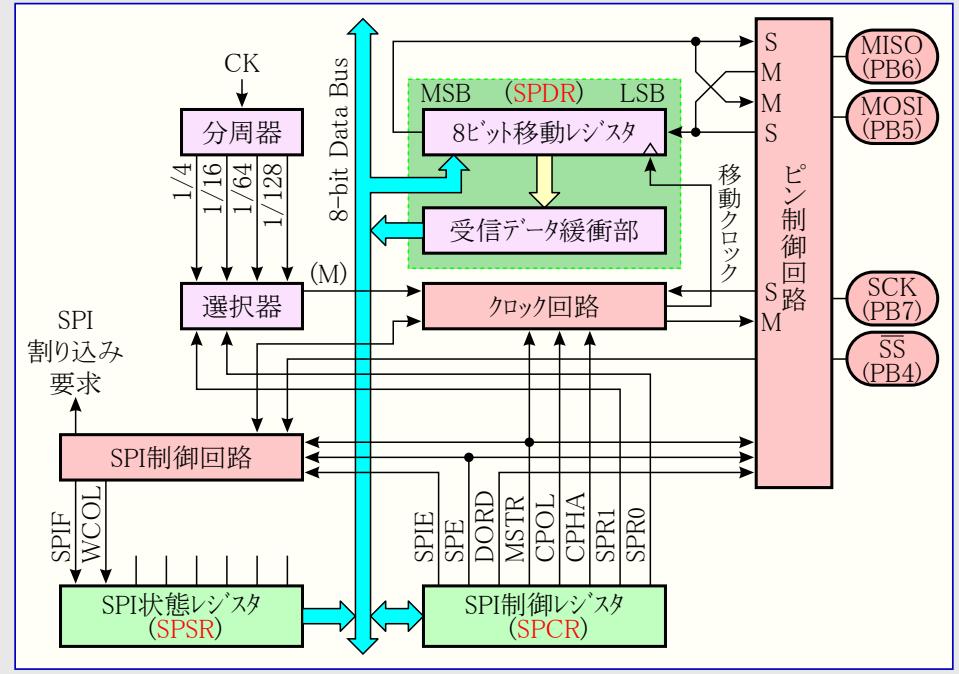

## 直列周辺インターフェース (SPI: Serial Peripheral Interface)

直列周辺インターフェースはAT90S4414/8515と多くのAVRデバイスや周辺デバイス間の高速同期データ転送を行います。SPIは次の特徴を含みます。

- 3線式全二重同期通信

- 主装置/従装置動作

- LSB/MSB先行のデータ通信

- 4つの設定変更可能なビット速度

- 送信終了割り込み

- 送信上書き検出

- アイドル動作からの起動復帰

(従装置動作のみ)

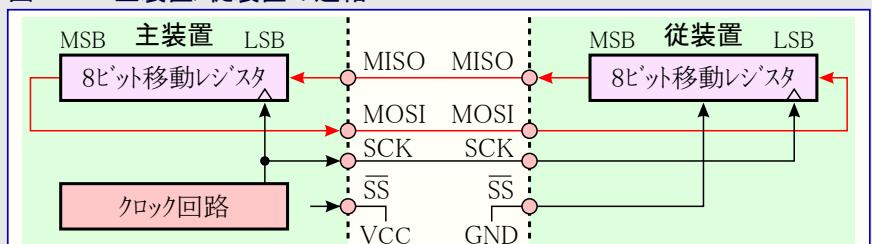

SPIでの主装置と従装置CPU間の相互連絡は図35で示されます。SCK(PB7)ピンは主装置動作でのクロック出力、従装置動作でのクロック入力です。主装置CPUのSPIデータレジスタ(SPDR)書き込みはSPIクロック発生器を起動し、書かれたデータがMOSI(PB5)ピンへ移動出力され、従装置CPUのMOSI(PB5)ピンに移動入力されます。1バイト移動後、SPIクロック発生器は停止し、SPI状態レジスタ(SPSR)の送信終了フラグ(SPIF)が設定(1)されます。SPI制御レジスタ(SPCR)のSPI割り込み許可(SPIE)ビットが設定(1)されていれば割り込みが要求されます。従装置選択入力SS(PB4)は個々の従装置SPIデバイスを選ぶため、Lowに設定します。主装置と従装置の2つの移動レジスタは分配された1つの循環型16ビット長移動レジスタとみなせます。これは図35で示されます。主装置から従装置へデータが移動されると同時にデータは逆方向にも移動されます。これは1移動周期中に主装置と従装置間のデータが交換されたことを意味します。

このシステムは送信方向が单一緩衝、受信方向が2重緩衝です。これは移動周期全てが完了される前に送信すべきバイトをSPIデータレジスタ(SPDR)に書けないことを意味します。しかし、データ受信時、次のバイトが完全に移動入力されてしまう前に、受信されたバイトがSPIデータレジスタ(SPDR)から読まれなければなりません。そうしないと、最初のバイトが失われます。

SPIが許可されると、MOSI, MISO, SCK, SSピンのデータ方向は表16に従って強制されます。

図34. SPI構成図

図35. SPI主装置/従装置の連結

表16. SPIピン方向規定

| ピン名  | 主装置時の方向規定           | 従装置時の方向規定           |

|------|---------------------|---------------------|

| SCK  | ポートB方向レジスタ(DDRB)の指定 | 入力                  |

| MISO | 入力                  | ポートB方向レジスタ(DDRB)の指定 |

| MOSI | ポートB方向レジスタ(DDRB)の指定 | 入力                  |

| SS   | ポートB方向レジスタ(DDRB)の指定 | 入力                  |

注: DDRBの指定については44頁の「ポートBの交換機能」を参照してください。

## SSピンの機能

SPI制御レジスタ(SPCR)の主装置(MSTR)ビットの設定(1)でSPIが主装置として設定されると、使用者がSSピンの方向を決められます。SSが`Output`として設定されると、このピンはSPIシステムに影響を及ぼさない標準出力です。SSが`Input`として設定されると、SPI主装置動作を保証するため、それは`High`を保持しなければなりません。SPIが主装置として設定され、SSピンが`Input`として定義される時にSSピンが周辺回路によって`Low`に駆動されると、他の主装置が従装置としてSPIを選び、データの送出を始めると解釈します。バスの衝突を避けるため、SPIシステムは次の動作を行います。

1. SPI制御レジスタ(SPCR)の主装置(MSTR)ビットが解除(0)され、SPIシステムは従装置になります。SPIが従装置になる結果、MOSIとSCKピンは`Input`になります。

2. SPI状態レジスタ(SPSR)のSPI割り込み要求フラグ(SPIF)が設定(1)され、そしてSPI割り込みが許可され、且つステータスレジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されていれば、割り込み処理ルーチンが実行されます。

従って、割り込み駆動SPI送信が主装置動作で使われ、SSが`Low`に駆動される可能性があるとき、割り込み処理はMSTRビットが未だ設定(1)されているかを常に検査すべきです。一旦MSTRビットが従装置選択によって解除(0)されてしまうと、SPI主装置動作を再び許可するため、それは使用者によって設定(1)されなければなりません。

SPIが従装置として設定されると、SSピンは常に`Input`です。SSが`Low`に保持されると、SPIは活性化され、MISOは使用者によってそのよう(出力)に設定されるなら`Output`になります。他の全ピンは`Input`です。SSが`High`に駆動されると、出力として使用者設定され得るMISOを除く全ピンが外部的に`Input`で、SPIは到着データを受信しないことを意味する受動状態です。一旦SSピンが`High`にされると、SPI回路がリセットすることに注意してください。送信中にSSピンが`High`にされると、SPIは直ちに送受信を停止し、送受信両方のデータが失われるとみなさなければなりません。

## データ転送形式

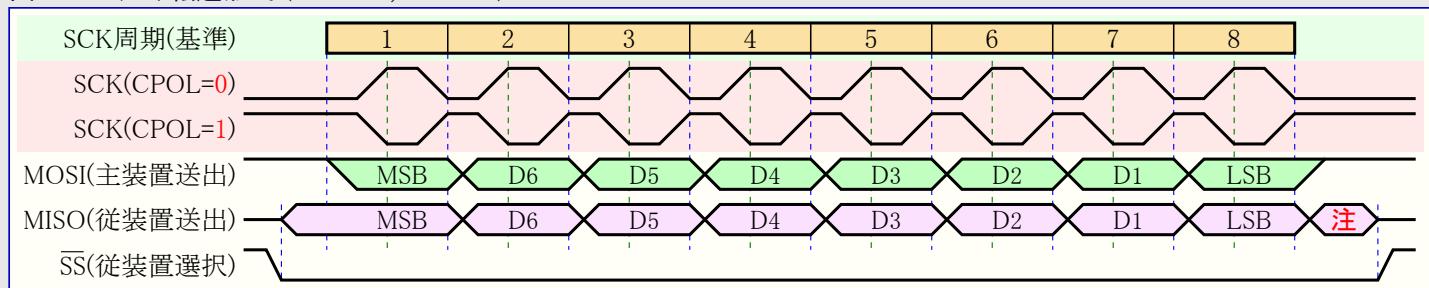

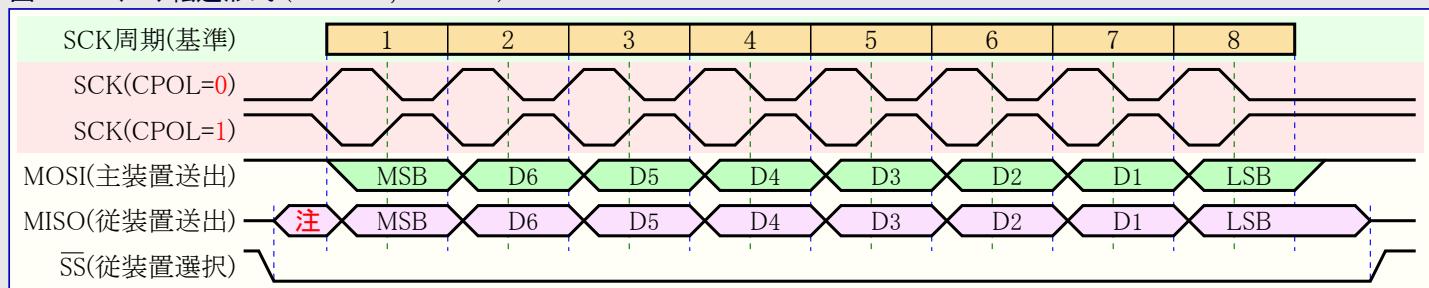

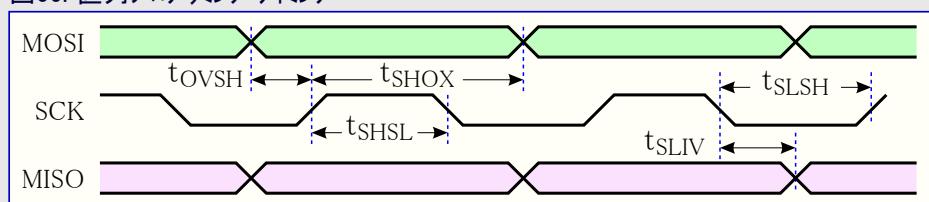

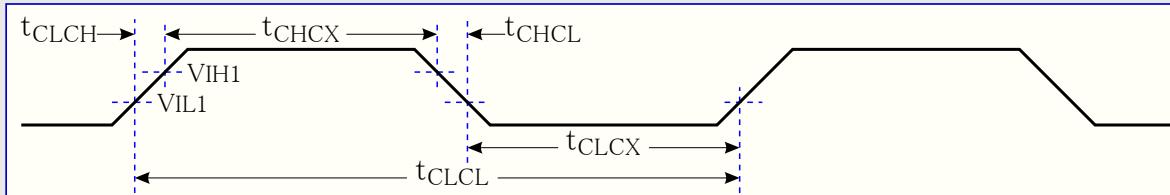

直列データに関してはSPI制御レジスタ(SPCR)のSCK位相(CPHA)ビットとSCK極性(CPOL)ビットで決められるSCKの位相と極性での4つの組み合わせがあります。SPIデータ転送形式は図36.と図37.で示されます。

図36. SPIデータ転送形式 (CPHA=0,DORD=0)

注: 未定義ですが、通常、受信されたデータのMSBです。

図37. SPIデータ転送形式 (CPHA=1,DORD=0)

注: 未定義ですが、通常、直前に送出されたデータのLSBです。

## SPIデータレジスタ (SPI Data Register) SPDR

| ビット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     | SPDR |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|------|

| \$0F (\$2F) | (MSB) |     |     |     |     |     |     | (LSB) |      |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |      |

| 初期値         | 不定    | 不定  | 不定  | 不定  | 不定  | 不定  | 不定  | 不定    |      |

SPIデータレジスタはSPI移動レジスタと汎用レジスタ間のデータ転送に使われる読み書きレジスタです。このレジスタへ書くとデータ送信を開始します。このレジスタを読むと移動レジスタの受信緩衝部を読みます。

## SPI状態レジスタ (SPI Status Register) SPSR

| ビット         | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 |      |

|-------------|------|------|---|---|---|---|---|---|------|

| \$0E (\$2E) | SPIF | WCOL | — | — | — | — | — | — | SPSR |

| Read/Write  | R    | R    | R | R | R | R | R | R |      |

| 初期値         | 0    | 0    | 0 | 0 | 0 | 0 | 0 | 0 |      |

- ビット7 – SPIF : SPI割り込み要求フラグ (SPI Interrupt Flag)

直列転送が完了すると、このSPIFが設定(1)され、SPI制御レジスタ(SPCR)のSPI割り込み許可(SPIE)ビットとステータスレジスタ(SREG)の全割り込み許可(I)ビットが共に設定(1)されていれば、割り込みが生成されます。SPIが主装置動作の時にSSが入力でLowに駆動されると、これもSPIFフラグを設定(1)します。SPIFは対応する割り込みベクタを実行すると、自動的に解除(0)されます。代わりに、SPIFが設定(1)されたSPSRを最初に読み、その後のSPIデータレジスタ(SPDR)のアクセスによってもSPIFは解除(0)されます。

- ビット6 – WCOL : 上書き発生フラグ (Write Collision Flag)

データ転送中にSPIデータレジスタ(SPDR)が書かれると、このWCOLフラグが設定(1)されます。このWCOLフラグ(とSPIFフラグ)はWCOLが設定(1)されたSPI状態レジスタ(SPSR)を最初に読み、その後のSPIデータレジスタ(SPDR)のアクセスによって解除(0)されます。

- ビット5~0 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

AT90S4414/8515のSPIインターフェースはフラッシュメモリやEEPROMの書き換え(読み書き)にも使われます。直列プログラミングと照合については[62頁](#)を参照してください。

## SPI制御レジスタ (SPI Control Register) SPCR

| ビット         | 7    | 6   | 5    | 4    | 3    | 2    | 1    | 0    |      |

|-------------|------|-----|------|------|------|------|------|------|------|

| \$0D (\$2D) | SPIE | SPE | DORD | MSTR | CPOL | CPHA | SPR1 | SPR0 | SPCR |

| Read/Write  | R/W  | R/W | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |      |

| 初期値         | 0    | 0   | 0    | 0    | 0    | 0    | 0    | 0    |      |

- ビット7 – SPIE : SPI割り込み許可 (SPI Interrupt Enable)

全割り込みが許可(SREGのI=1)され、SPI状態レジスタ(SPSR)のSPI割り込み要求フラグ(SPIF)が設定(1)される場合、このビットがSPI割り込みを実行させます。

- ビット6 – SPE : SPI許可 (SPI Enable)

SPEビットが設定(1)されるとSPIが許可されます。どのSPI操作でも、可能とするには、このビットが設定(1)されなければなりません。

- ビット5 – DORD : データ順選択 (Data Order)

DORDビットが設定(1)されるとLSBから送受信されます。DORDビットが解除(0)されるとMSBから送受信されます。

- ビット4 – MSTR : 主装置/従装置選択 (Master/Slave Select)

このビットは設定(1)されると主装置SPI動作、解除(0)されると従装置SPI動作を選びます。SSピンが入力として設定され、MSTRが設定(1)されている間にLowへ駆動されると、MSTRは解除(0)され、SPI状態レジスタ(SPSR)のSPI割り込み要求フラグ(SPIF)が設定(1)になります。SPI主装置動作を再び許可するには、その後MSTRを設定(1)しなければなりません。

- ビット3 – CPOL : SCK極性選択 (Clock Polarity)

このビットが設定(1)されるとSCKはアイドル時にHighとなります。CPOLが解除(0)されるとSCKはアイドル時にLowとなります。付加情報については[図36](#)と[図37](#)を参照してください。

- ビット2 – CPHA : SCK位相選択 (Clock Phase)

このビットの機能については[図36](#)と[図37](#)を参照してください。

- ビット1,0 – SPR1,0 : クロック選択 (SPI Clock Rate Select 1 and 0)

これら2つのビットは主装置として設定されるデバイスのSCK速度を制御します。従装置でのSPR1,0は無効です。SCKと発振器周波数(fCL)間の関連は表17で示されます。

表17. SCK速度選択 (fCL=発振器周波数)

| SPR1 | SPR0 | SCK周波数  |

|------|------|---------|

| 0    | 0    | fCL/4   |

| 0    | 1    | fCL/16  |

| 1    | 0    | fCL/64  |

| 1    | 1    | fCL/128 |

## UART

AT90S4414/8515は送信と受信のレジスタが分離された全二重(フルデューブレックス)のUART(Universal Asynchronous Receiver and Transmitter)が特徴です。主な特徴を次に示します。

- ・多数のポート速度(bps)を発生できるポート発振器

- ・低いクリスタル周波数での高ポート

- ・8または9ビットデータ

- ・雑音濾波器機能

- ・オーバーラン検出

- ・フレーミング異常検出

- ・不正開始ビット検出

- ・受信完了、送信完了、送信データレジスタ空きの3つの独立した割り込み

### データ送信

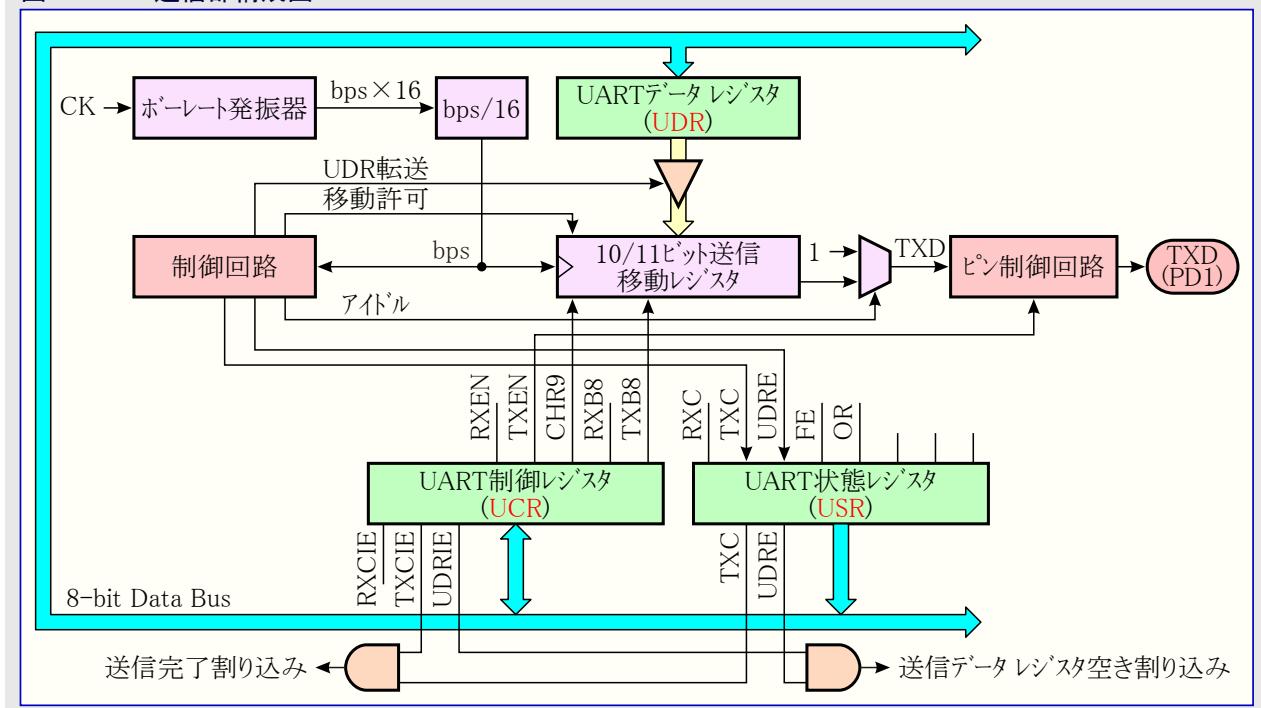

UART送信部の構成図は図38.で示されます。

図38. UART送信部構成図

データ送信はUARTデータレジスタ(UDR)への送信すべきデータの書き込みにより開始されます。データは次の時にUDRから送信移動レジスタへ転送されます。

- ・直前のデータが移動出力されてしまってから停止ビットの後に、新データがUDRに書かれると、移動レジスタは直ちに設定されます。

- ・直前のデータが移動出力されてしまってから停止ビットの前に、新データがUDRに書かれると、正しく送信されている(直前の)データの停止ビットが移動出力されてしまうときに、移動レジスタは設定されます。

10/11ビット送信移動レジスタが空の場合、データはUARTデータレジスタ(UDR)から、この移動レジスタへ転送されます。このとき、UART状態レジスタ(USR)のUARTデータレジスタ空き(UDRE)ビットが設定(1)されます。このビットが設定(1)されると、UARTは次データを受け取る用ができます。UDRから10/11ビット移動レジスタへ転送されると同時に、移動レジスタのビット0が解除(0)され(開始ビット)、ビット9または10が設定(1)されます(停止ビット)。UART制御レジスタ(UCR)の9ビット選択(CHR9)ビット=1で、9ビット長データが選ばれていると、UCRの送信ビット8(TXB8)ビットが送信移動レジスタのビット9に転送されます。

移動レジスタへの転送操作に続くポートクロックで開始ビットがTXDピン上に移動出力されます。その後LSBが先でデータを続けます。停止ビットが移動出力されてしまうとき、送信(移動)中に何れかの新規データが書かれてしまっている場合、移動レジスタは(そのデータ)で設定されます。この設定中にUDREが設定(1)されます。停止ビットが移動出力される時に送るためのUDR内の新規データがない場合、UDREはUDRが再び書かれるまで設定(1)に留まります。新規データが書かれず停止ビットが1ビット長分、TXD上に存在してしまうと、USRの送信完了(TXC)フラグが設定(1)されます。

UCRの送信許可(TXEN)ビットは設定(1)時にUART送信部を許可します。このビットが解除(0)されると、PD1/TXDピンは標準I/Oで使えます。TXENが設定(1)されると、UART送信部はPD1/TXDピンに接続され、それはポートD方向レジスタ(DDRD)のDDD1ビットの設定に拘らず、強制的に出力とされます。

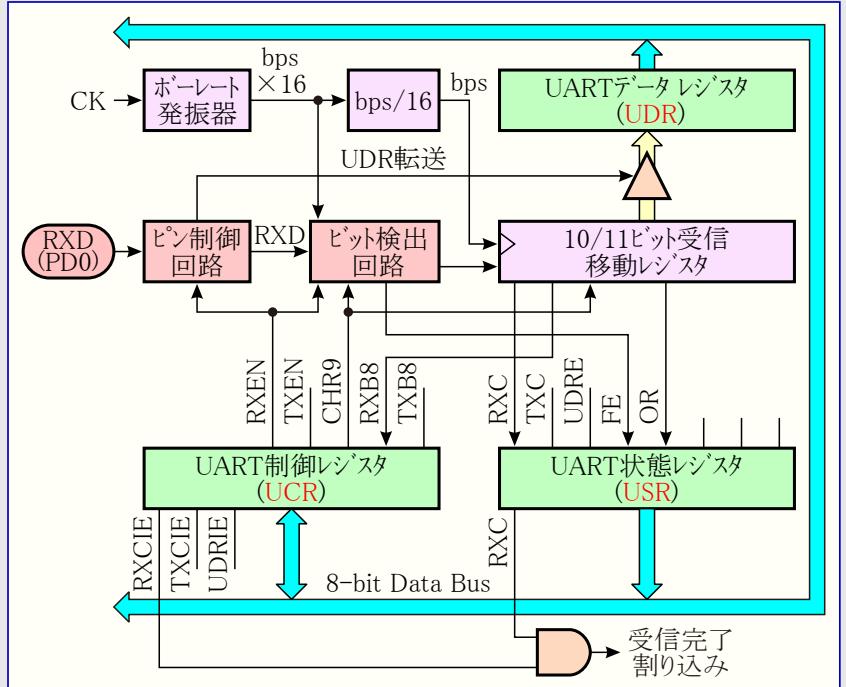

## データ受信

図39.はUART受信部の構成図を示します。

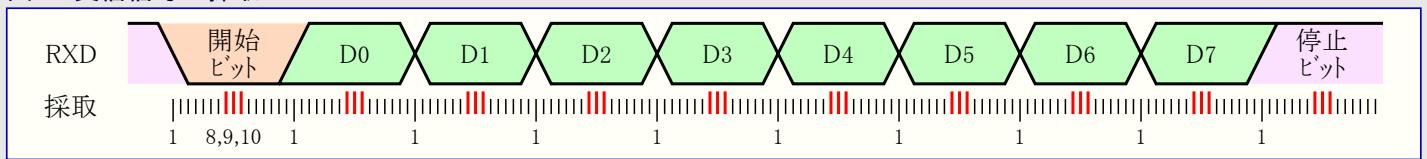

受信部前処理回路はボーレート周波数の16倍のクロックでRXDピン上の信号を採取します。信号線がアイトルの間、1つの論理0の採取は開始ビットの上昇端として判定され、開始ビット検出手順が開始されます。第1採取は、この最初の0採取を示します。1から0への遷移に続き、受信部は第8、9、10採取でRXDピンを採取します。これら3つの採取で2回以上の論理1を見つけると、開始ビットは尖頭雑音として破棄され、受信部は次の1から0への遷移(開始ビット開始)検出を始めます。

そうでなければ、有効な開始ビットが検出され、開始ビットに続くデータビットの採取が実行されます。これらのビットは同様に第8、9、10採取で採取されます。3つの採取の内、少なくとも2つが見つかった論理値がビット値として取得されます。全てのビットは採取されると、受信移動レジスタ内に移動入力されます。到着フレームの採取は図40.で示されます。

図39. UART受信部構成図

図40. 受信信号の採取

停止ビットが受信部に入るとき、停止ビットを受け入れるためには、3採取の多数が1でなければなりません。2つ以上の採取が論理0だと、USRのフレーミング異常(FE)フラグが設定(1)されます。フレーミング異常を検出するため、常にUDRを読む前に、このFEフラグを検査すべきです。

フレーム受信周期の最後で有効な停止ビットが検出されるかによらず、データはUDRへ送られ、USRの受信完了(RXC)フラグが設定(1)されます。実際のUDRは2つの物理的に分離したレジスタで、受信データ用に1つと送信データ用に1つです。UDRが読まれると受信データレジスタが、UDRが書かれると送信データレジスタがアクセスされます。UCRの9ビット選択(CHR9)ビット=1で、9ビット長データが選ばれていると、データがUDRに転送されるときに、UCRの受信ビット8(RXB8)ビットは受信移動レジスタのビット9が設定されます。

受信されたフレーム(データ)があるのに、直前の受信以降、UDRが読まれていないと、USRのオーバーラン(OR)フラグが設定(1)されます。これは、受信移動レジスタに移動入力された最後の受信データが、UDRに転送できないために、失われてしまうことを意味します。ORビットは緩衝されており、UDR内の有効な受信データが読まれる時に更新されます。従って、速いボーレートやCPU負荷が重い場合、どのオーバーランも検出するには、UDR読み込み後、常にこのORフラグを検査すべきです。

UCRの受信許可(RXEN)ビットが解除(0)されると、受信部が禁止されます。これはPD0/RXDピンが標準I/Oピンとして使えることを意味します。RXENが設定(1)されると、UART受信部がPD0/RXDピンに接続され、それはポートD方向レジスタ(PORTD)のDDRDのDDRD0の設定に拘らず、強制的に入力とされます。ポートD出力レジスタ(PORTD)のPORTD0は、このピンのプルアップ抵抗を制御するために未だ使えます。

UCRの9ビット選択(CHR9)ビットが設定(1)されると、送受信されるフレームは開始ビット+9ビットデータ+停止ビットです。送信される第9ビットデータはUCRの送信ビット8(TXB8)ビットです。このビットは、UDR書き込みにより送信が開始される前に、必要とされる値を設定しなければなりません。受信された第9ビットデータは、UCRの受信ビット8(RXB8)ビットです。

## UART制御

### UARTデータレジスタ (UART I/O Data Register) UDR

| ビット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |     |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|-----|

| \$0C (\$2C) | (MSB) |     |     |     |     |     |     | (LSB) | UDR |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |     |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |     |

実際には、UDRは同じI/Oアドレスを共有する物理的に分離した2つのレジスタです。このレジスタに書くとUART送信データレジスタが書かれます。UDRから読むとUART受信データレジスタが読まれます。

### UART状態レジスタ (UART Status Register) USR

| ビット         | 7   | 6   | 5    | 4  | 3  | 2 | 1 | 0 |     |

|-------------|-----|-----|------|----|----|---|---|---|-----|

| \$0B (\$2B) | RXC | TXC | UDRE | FE | OR | - | - | - | USR |

| Read/Write  | R   | R/W | R    | R  | R  | R | R | R |     |

| 初期値         | 0   | 0   | 1    | 0  | 0  | 0 | 0 | 0 |     |

USRはUARTの状態情報を提供する読み込みのみ可能なレジスタです。

#### • ビット7 – RXC : UART受信完了フラグ (UART Receive Complete)

受信されたデータが受信移動レジスタからUARTデータレジスタ(UDR)へ転送されるとき、このビットが設定(1)されます。このビットは、検出されたどんなフレーミング異常にも関係なく設定されます。UART制御レジスタ(UCR)の受信完了割り込み許可(RXCIE)ビットが設定(1)されていると、RXCが設定(1)された時にUART受信完了割り込みが実行されます。RXCはUDR読み込みによって解除(0)されます。割り込み駆動データ受信が使われる時に、UART受信完了割り込み処理ルーチンはRXCを解除(0)するためにUDRを読まなければなりません。そうしないと、一旦割り込み処理ルーチンを終了しても、新規割り込みが発生します。

#### • ビット6 – TXC : UART送信完了フラグ (UART Transmit Complete)

送信移動レジスタ内の完全なデータ(含む停止ビット)が移動出力されてしまい、新規データがUARTデータレジスタ(UDR)に書かれてしまっていないとき、このビットは設定(1)されます。このビットは、送信側が送信完了後、直ちに通信回線を開放し、受信動作へ移行しなければならない半二重(ハーフデュープレックス)通信で特に有用です。

UART制御レジスタ(UCR)の送信完了割り込み許可(TXCIE)ビットが設定(1)されていると、TXCの設定(1)は、UART送信完了割り込みを実行させます。対応する割り込みベクタを実行すると、TXCは自動的に解除(0)されます。代わりに、このビットに論理1を書くことによっても、TXCは解除(0)されます。

#### • ビット5 – UDRE : UART送信データレジスタ空きフラグ (UART Data Register Empty)

UARTデータレジスタ(UDR)に書かれたデータが送信移動レジスタへ転送されるとき、このビットは設定(1)されます。このビットの設定(1)は、送信部が新規送信データを受ける用意ができていることを示します。

UART制御レジスタ(UCR)の送信データレジスタ空き割り込み許可(UDRIE)ビットが設定(1)されていると、UDREが設定(1)されている限り、UART送信データレジスタ空き割り込みが実行されます。UDREはUDR書き込みにより解除(0)されます。割り込み駆動データ送信が使われる時に、UART送信データレジスタ空き割り込み処理ルーチンはUDREを解除(0)するためにUDRに書かなければなりません。そうしないと、一旦割り込み処理ルーチンを終了しても、新規割り込みが発生します。

UDREは送信可を示すため、リセット中に設定(1)されます。

#### • ビット4 – FE : フレーミング異常フラグ (Framing Error)

このフラグはフレーミング異常条件が検出されると、換言すると、到着フレームの停止ビットが0のとき、設定(1)されます。

FEフラグは受信されるデータの停止ビットが1のときに解除(0)されます。

#### • ビット3 – OR : オーバーラン発生フラグ (Overrun)

このフラグはオーバーラン条件(換言すると、次のデータが受信移動レジスタに移動入力されてしまう前に、UARTデータレジスタ(UDR)内に既に存在するデータが読まれないとき)が検出されると設定(1)されます。ORは緩衝されており、そしてそれは一度UDRの有効なデータを読んでも未だ設定(1)されることを意味します。

ORフラグはデータが受信され、UDRへ転送されるときに解除(0)されます。

#### • ビット2~0 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

## UART制御レジスタ (UART Control Register) UCR

| ビット         | 7     | 6     | 5     | 4    | 3    | 2    | 1    | 0    |     |

|-------------|-------|-------|-------|------|------|------|------|------|-----|

| \$0A (\$2A) | RXCIE | TXCIE | UDRIE | RXEN | TXEN | CHR9 | RXB8 | TXB8 | UCR |

| Read/Write  | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R    | R/W  |     |

| 初期値         | 0     | 0     | 0     | 0    | 0    | 0    | 1    | 0    |     |

## • ビット7 – RXCIE : 受信完了割り込み許可 (Receive Complete Interrupt Enable)

このビットが設定(1)のとき、全割り込みが許可(SREGのI=1)されていれば、UART状態レジスタ(USR)の受信完了(RXC)フラグの設定(1)は受信完了割り込みルーチンを実行させます。

## • ビット6 – TXCIE : 送信完了割り込み許可 (Transmit Complete Interrupt Enable)

このビットが設定(1)のとき、全割り込みが許可(SREGのI=1)されていれば、USRの送信完了(TXC)フラグの設定(1)は送信完了割り込みルーチンを実行させます。

## • ビット5 – UDRIE : 送信データレジスタ空き割り込み許可 (Transmit Data Register Empty Interrupt Enable)

このビットが設定(1)のとき、全割り込みが許可(SREGのI=1)されていれば、USRの送信データレジスタ空き(UDRE)フラグの設定(1)は送信データレジスタ空き割り込みルーチンを実行させます。

## • ビット4 – RXEN : 受信許可 (Receiver Enable)

設定(1)されると、このビットはUART受信(部)を許可します。受信(部)が禁止されると、UART状態レジスタ(USR)の受信完了(RXC)、フレーミング異常(FE)、オーバーラン(OR)状態フラグは設定(1)になることができません。これらのフラグが設定(1)の場合、RXENの解除(0)への切り替えは、それらを解除(0)しません。

## • ビット3 – TXEN : 送信許可 (Transmitter Enable)

設定(1)されると、このビットはUART送信(部)を許可します。データ送信中に送信(部)を禁止すると、送信移動レジスタのデータと送信データレジスタ(UDR)の続くデータが完全に送信されてしまう前には、送信部が禁止されません。

## • ビット2 – CHR9 : 9ビットデータ選択 (9Bits Character)

このビットが設定(1)されると、送受信フレームは開始ビット+9ビットデータ+停止ビットです。第9ビットは各々、UART制御レジスタ(UCR)の受信ビット8(RXB8)、送信ビット8(TXB8)を使うことで読み書きされます。この第9データビットは、パリティビットや拡張停止ビットとして使えます。

## • ビット1 – RXB8 : 受信データビット8 (Receive Data Bit 8)

9ビットデータ選択(CHR9)が設定(1)されていると、RXB8は受信されたデータの第9データビット(ビット8)です。

## • ビット0 – TXB8 : 送信データビット8 (Transmit Data Bit 8)

9ビットデータ選択(CHR9)が設定(1)されていると、TXB8は送信されるべきデータの第9データビット(ビット8)です。

## ポート発振器

ポート発振器は、次式に従ってポートを生成する周波数分周器です。

$$BAUD = \frac{f_{CK}}{16 \times (UBRR+1)}$$

BAUD ..... ポート(bps)

$f_{CK}$  ..... Xtal発振(CPUクロック)周波数

UBRR ..... UARTポートレジスタ値(0~255)

## UARTポートレジスタ (UART Baud Rate Register) UBRR

| ビット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |      |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|------|

| \$09 (\$29) | (MSB) |     |     |     |     |     |     | (LSB) | UBRR |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |      |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |      |

UBRRは上記の式に従ってUARTポートを示す、読み書き可能な8ビットレジスタです。(設定例は表18.参照)

表18.のUBRR設定を使うことにより、標準的なクリスタル周波数について、一般的に使われる多くのボーレートが発生できます。実際のボーレートが目的のボーレートに対して誤差2%未満を有効なボーレートとし、それ以外は赤字で示されます。しかし、誤差1%を越えるボーレートの使用は推奨されません。高い誤差率は雑音耐性が低下します。

表18. Xtal、ボーレート対UBRR設定

| ボーレート  | 1MHz     |       | 1.8432MHz |       | 2MHz      |       | 2.4576MHz |       | 3.2768MHz |       | 3.6864MHz |       |

|--------|----------|-------|-----------|-------|-----------|-------|-----------|-------|-----------|-------|-----------|-------|

|        | UBRR     | 誤差(%) | UBRR      | 誤差(%) | UBRR      | 誤差(%) | UBRR      | 誤差(%) | UBRR      | 誤差(%) | UBRR      | 誤差(%) |

| 1200   | 51       | 0.2   | 95        | 0.0   | 103       | 0.2   | 127       | 0.0   | 170       | 0.2   | 191       | 0.0   |

| 2400   | 25       | 0.2   | 47        | 0.0   | 51        | 0.2   | 63        | 0.0   | 84        | 0.4   | 95        | 0.0   |

| 4800   | 12       | 0.2   | 23        | 0.0   | 25        | 0.2   | 31        | 0.0   | 42        | 0.8   | 47        | 0.0   |

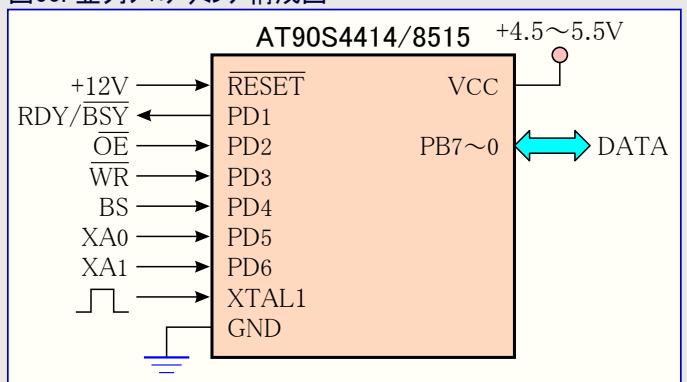

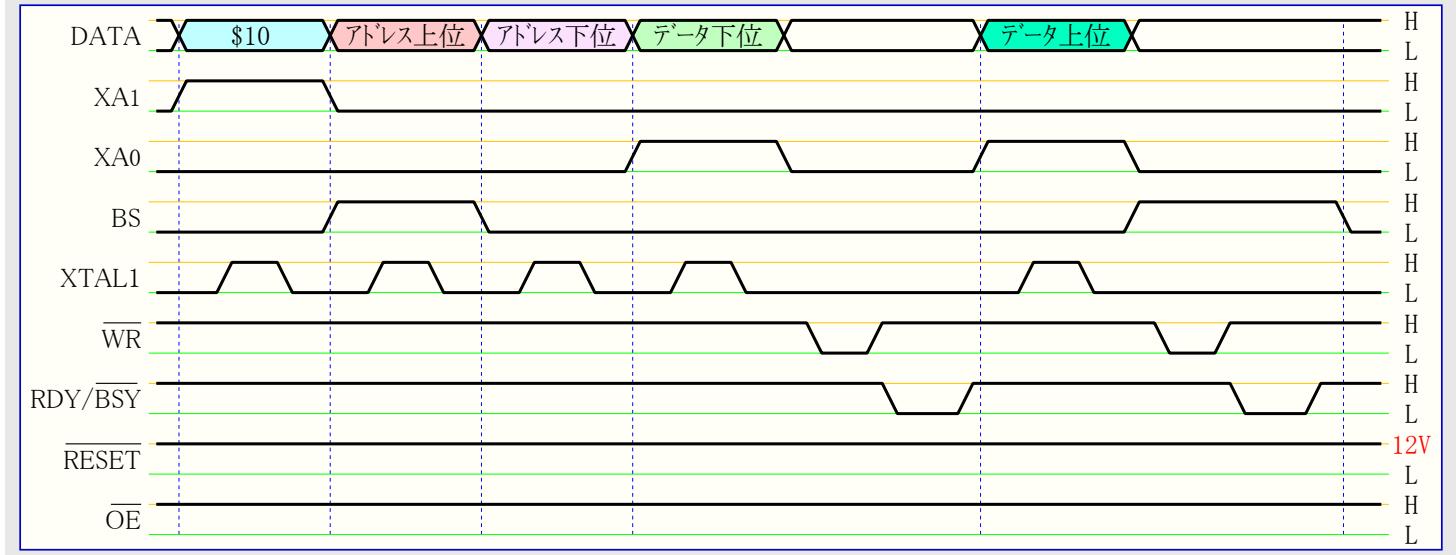

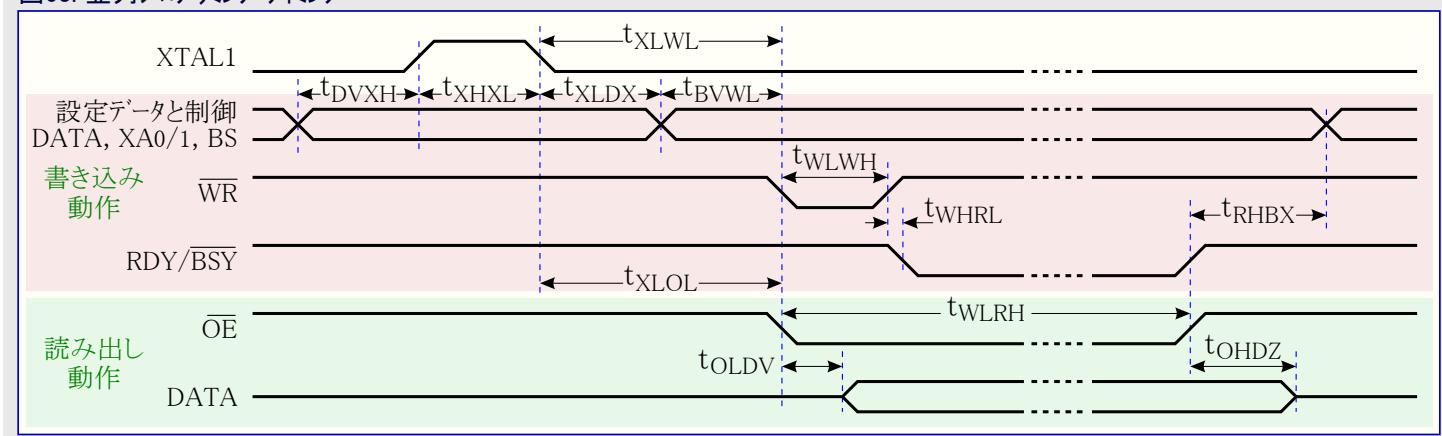

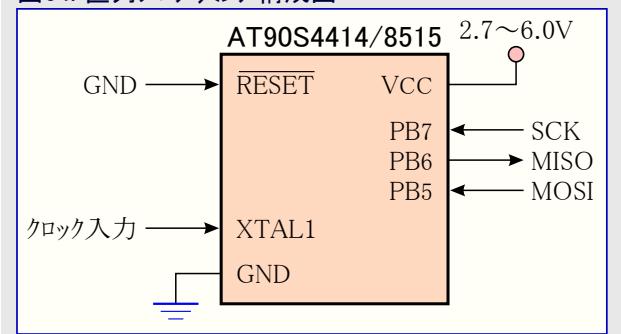

| 9600   | 6        | 7.5   | 11        | 0.0   | 12        | 0.2   | 15        | 0.0   | 20        | 1.6   | 23        | 0.0   |