# Atmel

### ATmega16U4, ATmega32U4

### 16/32Kハ・小実装書き込み可能フラッシュ メモリ、USB制御器付き Atmel 8ビット マイクロ コントローラ

データシート

#### 特徴

- 高性能、低消費AVR® 8ビットマイクロ コントローラ

- 進化したRISC構造

- 強力な131命令(多くは1周期で実行)

- 32個の1バイト長汎用レジスタ

- 完全なスタティック動作

- 16MHz時、16MIPSに達する高速動作

- -2周期実行の乗算命令

- データメモリと不揮発性プログラムメモリ

- 実装自己書き換え可能な16K/32Kバイト(8K/16K語)フラッシュ メモリ内蔵

- 1.25K/2.5Kバ仆の内蔵SRAM

- 512/1KハイトのEEPROM

- 書き換え回数: 10,000/フラッシュ, 100,000/EEPROM

- データ保持力: 20年/85℃, 100年/25℃

- 個別施錠ビットを持つ任意のブートコート、領域

チップ・内ブートプ・ログラムによる実装書き換え

真の書き込み中の読み出し動作

出荷時に外部XTALクロック使用デ・バイスは既定ブートローダが予め書き込み済み

ソフトウェア保護用の設定可能な施錠機能

- // 「北設用の設定可能な肥政機能

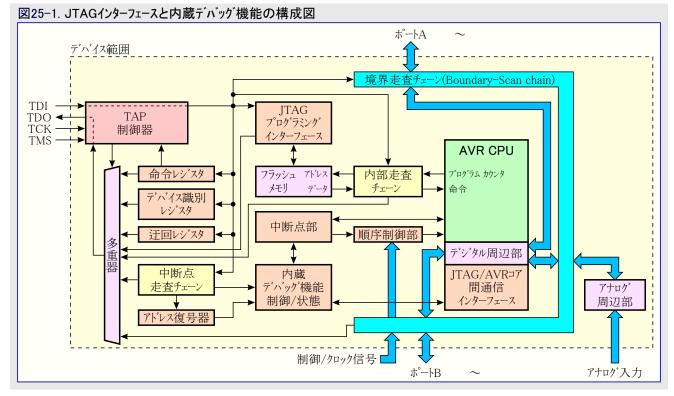

- JTAG (IEEE<sup>®</sup> 1149.1準拠) インターフェース

- JTAG規格に従った境界走査(Boundary-Scan)能力

- 広範囲な内蔵デバッグ機能

- JTAGインターフェース経由でのフラッシュ、EEPROM、ヒュース、施錠ビットのプログラミンク

- ・転送完了での割り込み付きUSB全速(Full-speed)/低速(Low-speed)装置部

- USB仕様改訂2.0(Universal Serial Bus Specification Rev 2.0)完全適合

- 1.5Mbpsと12Mbpsまでのデータ転送速度を支援

- 64バイトまでの制御転送用エンドポイント0

- 大量(Bulk),割り込み(Interrupt),等時(Isochronous)転送と入出力方向が設定可能な 6つのエンドボイント

- 二重バンク動作で256バイトまで設定可能なエンドポイント容量

- 完全に独立したエント゛ポイントメモリ割付用832ハ、イトUSBデュアル ポートRAM(DPRAM)

- 休止(Suspend:サスペント)/再開(Resume:リシューム)割り込み

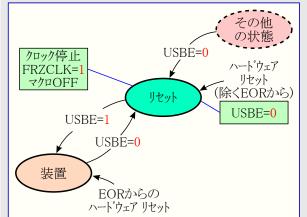

- USBハズリセットでCPUリセット可能

- 全速バス動作用48MHz PLL

- マイクロ コントローラ要求でのUSBバス接続/切断

- 低速(Low-speed)動作に対するクリスタルなし動作

- 内蔵周辺機能

- USBと高速タイマ用チップ上PLL: 32~96MHz動作

- 独立した前置分周器、比較機能付き、1つの8ビットタイマ/カウンタ

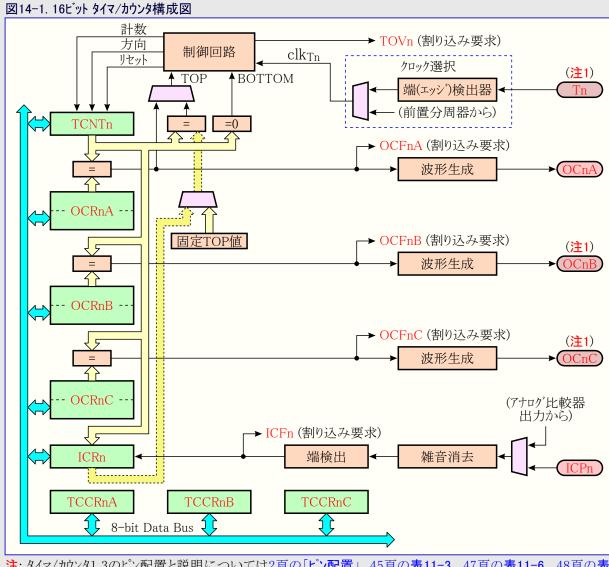

- 独立した前置分周器、比較、捕獲機能付き、2つの16ビットタイマ/カウンタ

- PLL(64MHz)と比較機能付き、1つの10ビット高速タイマ/カウンタ

- 2つの8ビットPWM

- 2~16ビット分解能が設定可能な4つのPWM

- 2~11ビット分解能が設定可能な高速動作用の6つのPWM

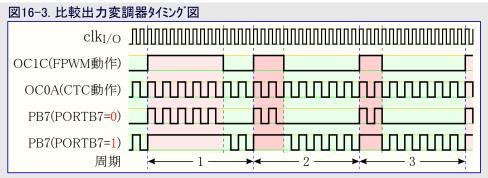

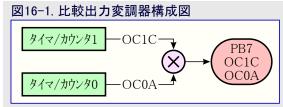

- 比較出力変調器

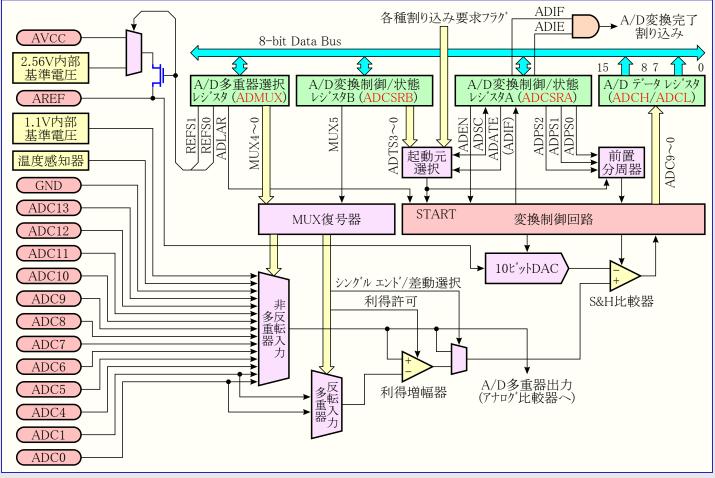

- 12チャネルの10ビット A/D変換器(設定可能な利得付き差動チャネル機能)

- ハードウェア流れ制御付きの設定可能な直列USART

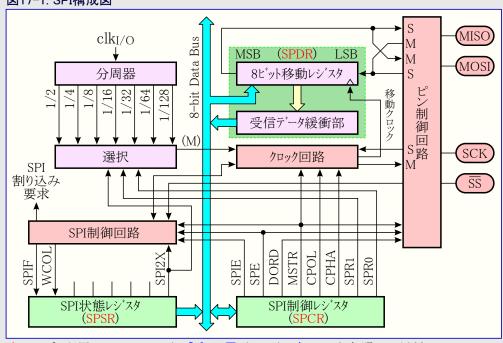

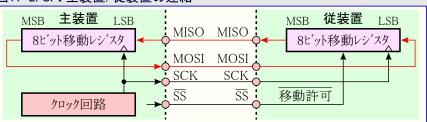

- 主装置/従装置動作SPI直列インターフェース

- バイト対応の2線直列インターフェース

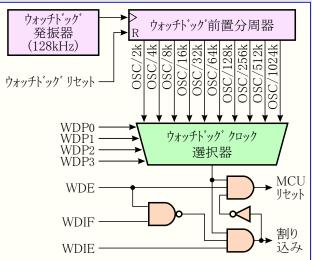

- 設定可能な専用発振器付きウォッチトッグタイマ

- アナログ比較器

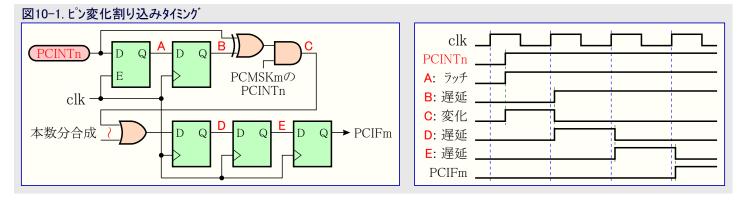

- ピン変化での割り込みと起動復帰

- チップ上の温度感知器

- •特殊マイクロコントローラ機能

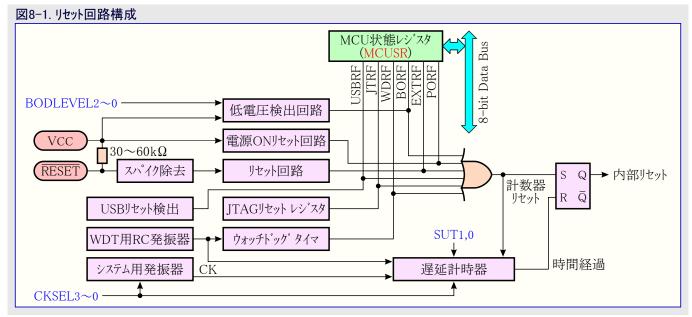

- 電源ONリセット回路と設定可能な低電圧検出器(BOD)

- 校正可能な内蔵8MHz発振器

- 内蔵クロック前置分周器とクロック急速切り換え(内蔵RC/外部発振器)

- 外部及び内部の割り込み

- アイト・ル、A/D変換雑音低減、パワーセーブ、パワーダウン、スタンハイ、拡張スタンハイの 6つの低消費動作

- I/Oと外囲器

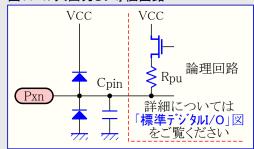

- CMOS出力とLVTTL入力兼備の全I/O

- 26ビットの設定可能なI/O

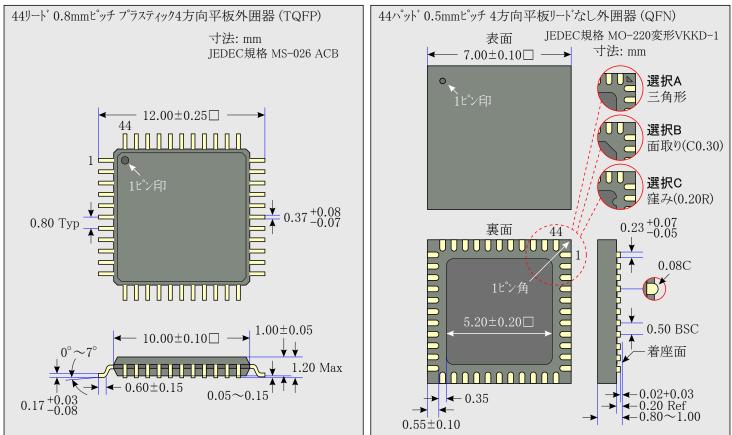

- 44リート TQFP(10×10mm)、44ハ ット QFN(7×7mm)

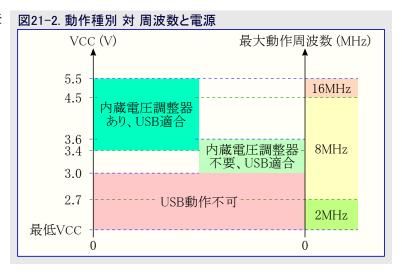

- 動作電圧

- $-2.7 \sim 5.5 V$

- 温度範囲

- --40~85℃(工業用)

- 最大速度

- 8MHz/2.7V (全温度範囲)

- 16MHz/4.5V (全温度範囲)

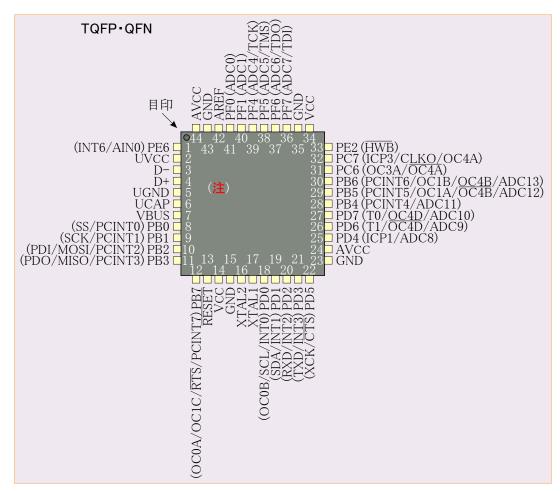

### 1. ピン配置

### 2. 概要

ATmega16U4/32U4はAVR強化RISC構造の低消費CMOS 8ビットマイクロコントローラです。1周期で実行する強力な命令はMHzあたり1 MIPSにも達し、実行速度対電力消費の最適化が容易に行えます。

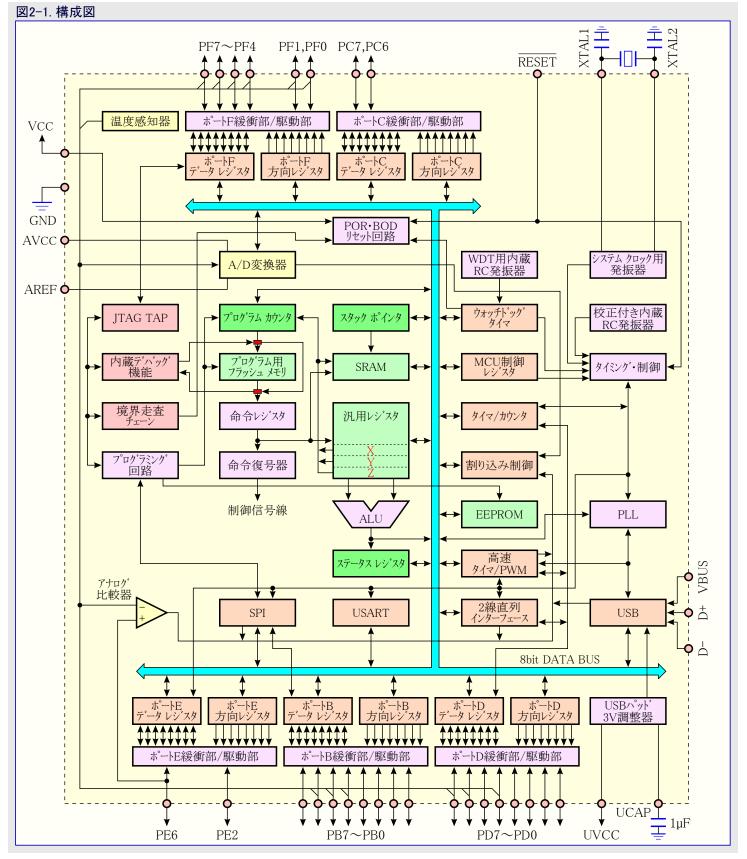

### 2.1. 構成図

AVRコアは32個の汎用作業レジスタと豊富な命令群を兼ね備えています。32個の全レジスタはALU(Arithmetic Logic Unit)に直結され、 レジスタ間命令は1クロック周期で実行されます。AVR構造は現状のCISC型マイクロコントローラに対して10倍程度までの単位処理量向上効 果があります。

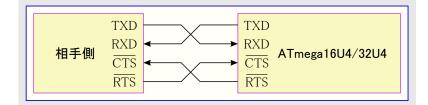

このデバイスは次の特徴、書き込み中読める能力を持つ16K/32Kバイトの実装書き換え可能な7ラッシュメモリ、512/1KバイトのEEPROM、 1.25K/2.5KバイトのSRAM、26本の汎用入出力線(CMOS出力とLVTTL入力)、32個の汎用作業レジスタ、比較動作やPWMを持つ柔軟 な3つのタイマ/カウンタ、比較動作と調整可能なPLL供給元を持つ1つのより高速なタイマ/カウンタ、(CTS/RTS流れ制御信号を含む)1つの USART、バイト対応の2線直列インターフェース、設定可能な増幅器付き任意選択差動段と校正された温度感知器付き12チャネルの10ビット A/D変換器、設定可能な内部発振器付きウォッチドッグタイマ、SPI直列ポート、内蔵デバッグとプログラシング機能にも使われるIEEE標準114 9.1準拠JTAG検査インターフェース、ソフトウェア選択可能な6つの低消費動作機能を提供します。アイドル動作では動作を停止しますが、SRA M、タイマ/カウンタ、SPIポート、割り込み機能は有効で動作を継続します。パワーダウン動作ではレジスタの内容は保護されますが、発振器が 停止するため、以降のハートウェアリセットか外部割り込みまで他の全機能を禁止(無効に)します。A/D変換雑音低減動作ではA/D変換 中の切り替え雑音を最小とするために、A/D変換器を除く全ての周辺機能とCPUを停止します。スタンパイ動作ではクリスタル発振子/セラ ミック振動子用発振器が動作し、一方デバイスのその他は休止します。これは低消費電力と非常に速い起動の組み合わせを許します。 本デバイスはAtmel<sup>®</sup>の高密度不揮発性メモリ技術を使って製造されています。内蔵の実装書き換え(ISP)可能なプログラム用フラッシュメモリ は規定の不揮発性メモリ書き込み器、SPI直列インターフェース経由、AVRコア上ブートプログラムの実行によって再書き込みができます。ブート プログラムは応用領域フラッシュメモリ内の応用プログラムの読み込みにどのインターフェースでも使えます。モノリシックチップとの実装書き換え可

ATmega16U4/32U4 AVRはCコンパイラ、マクロ アセンブラ、ディ、ッカ、シミュレータ、インサーキット エミューレータ、評価キットを含む専用のプログラム及び システム開発ツールで支援されます。

能なフラッシュ メモリと、8ビットRISC型CPUの組み合わせによる本デバイスは多くの組み込み制御の応用に対して高度な柔軟性と対費用

#### 2.2. ピン概要

#### 2.2.1. VCC

デジタル電源ピン。

#### 2.2.2. GND

接地ピン。

#### **2.2.3. PB7~PB0** (ホートB)

効果をもたらす強力なマイクロコントローラです。

ポートBは(ビット毎に選ばれる)内蔵プルアップ抵抗付き8ビット双方向入出力ポートです。ポートB出力緩衝部は高い吐き出しと吸い込み両方の能力の対称駆動特性です。入力としてプルアップ抵抗が活性(有効)なら、外部的にLowへ引かれたポートBピンは電流を吐き出します。リセット条件が有効になるとクロックが動いていなくてもポートBピンはHi-Zにされます。

ポートBは他のポートより優れた駆動能力を持ちます(訳注:該当記述が他にないため、消し忘れかもしれません)。

ポートBは45頁で一覧されるように本デバイスの様々な特殊機能

#### **2.2.4. PC7,PC6** (ポートC)扱います。

ポートCは(ビット毎に選ばれる)内蔵プルアップ抵抗付き8ビット双方向入出力ポートです。ポートC出力緩衝部は高い吐き出しと吸い込み両 方の能力の対称駆動特性です。入力としてプルアップ抵抗が活性(有効)なら、外部的にLowへ引かれたポートCピンは電流を吐き出しま す。リセット条件が有効になるとクロックが動いていなくてもポートCピンはHi-Zにされます。

製品のピン出力にはビット7と6だけが存在します。

ポートCは47頁で一覧される本デバイスの様々な特殊機能も扱います。

#### **2.2.5. PD7~PD0** (ホ°ートD)

ポートDは(ビット毎に選ばれる)内蔵プルアップ抵抗付き8ビット双方向入出力ポートです。ポートD出力緩衝部は高い吐き出しと吸い込み両 方の能力の対称駆動特性です。入力としてプルアップ抵抗が活性(有効)なら、外部的にLowへ引かれたポートDピンは電流を吐き出しま す。リセット条件が有効になるとクロックが動いていなくてもポートDピンはHi-Zにされます。

ポートDは48頁で一覧されるATmega16U4/32U4の様々な特殊機能も扱います。

#### **2.2.6. PE6,PE2** (木°一トE)

ポートEは(ビット毎に選ばれる)内蔵プルアップ抵抗付き8ビット双方向入出力ポートです。ポートE出力緩衝部は高い吐き出しと吸い込み両方の能力の対称駆動特性です。入力としてプルアップ抵抗が活性(有効)なら、外部的にLowへ引かれたポートEピンは電流を吐き出します。リセット条件が有効になるとクロックが動いていなくてもポートEピンはHi-Zにされます。

製品のピン出力にはビット6と2だけが存在します。

ポートEは50頁で一覧されるATmega16U4/32U4の様々な特殊機能も扱います。

#### **2.2.7. PF7~PF4, PF1,PF0** (ポートF)

ポートFはA/D変換器へのアナログ入力として扱います。

A/D変換器が使われない場合、ポートFは8ビット双方向入出力ポートとしても扱います。ポートビンは(ビット毎に選ばれる)内蔵プルアップ抵抗を提供できます。ポートF出力緩衝部は高い吐き出しと吸い込み両方の能力の対称駆動特性です。入力としてプルアップ抵抗が活性(有効)ならば、外部的にLowへ引かれたポートFビンは電流を吐き出します。リセット条件が有効になるとクロックが動いていなくてもポートFビンはHi-Zにされます。

#### 製品のピン出力にはビット3と2が存在しません。

ポートFはJTAGインターフェース機能も扱います。JTAGインターフェースが許可されると、リセットが起きてもPF7(TDI)、PF5 (TMS)、PF4(TCK)ピンのプルアップ抵抗は活性(有効)にされます。

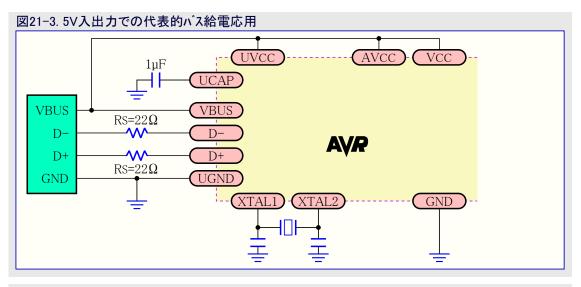

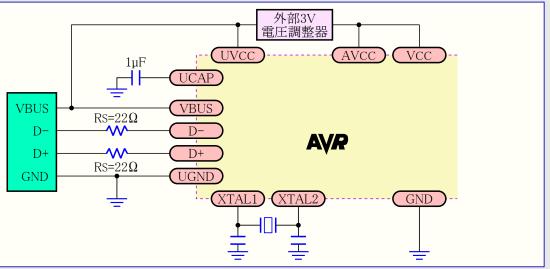

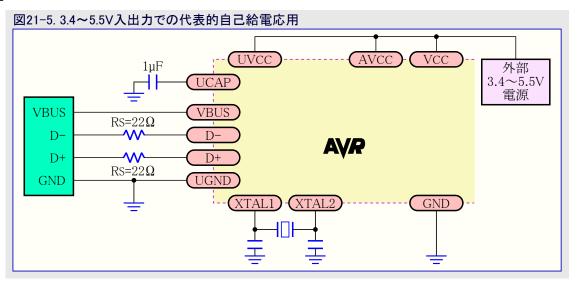

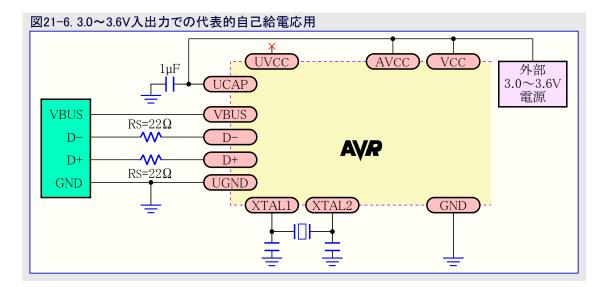

#### 2.2.8. D-

USB全速(Full-speed)/低速(Low-speed)負極性データ上側ホート。22Ω直列抵抗でUSBコネクタD-ピンに接続されるべきです。

#### 2.2.9. D+

USB全速(Full-speed)/低速(Low-speed)正極性データ上側ホート。22Ω直列抵抗でUSBコネクタD+ピンに接続されるべきです。

#### 2.2.10. UGND

USBパッド接地。

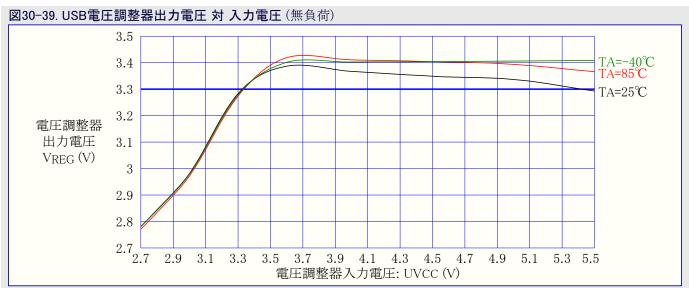

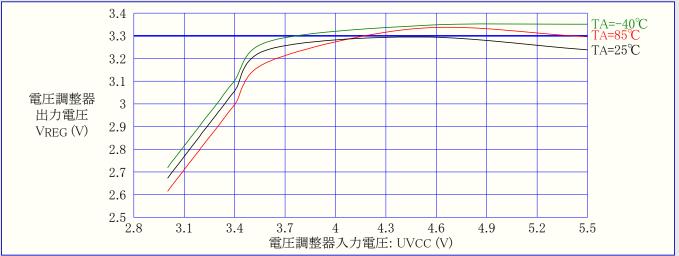

#### 2.2.11. UVCC

USBパッド用内蔵電圧調整器の供給電圧入力。

#### 2.2.12. UCAP

USBパッド用内蔵電圧調整器の供給電圧出力。外部コンデンサ(1µF)に接続されるべきです。

#### 2.2.13. VBUS

USB VBUS監視入。

#### 2.2.14. RESET

リセット入力。最小パルス幅より長いこのピンのLowレベルは、クロックが動いていなくてもリセットを生成します。最小パルス幅は249頁の表29-3. で与えられます。より短いパルスはリセットの生成が保証されません。

#### 2.2.15. XTAL1

発振器反転増幅器への入力と内部クロック操作回路への入力。

#### 2.2.16. XTAL2

発振器反転増幅器からの出力。

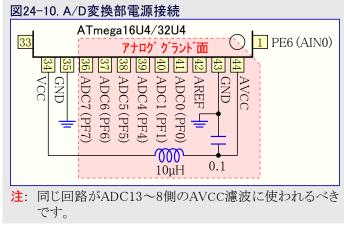

#### 2.2.17. AVCC

AVCCはポートFとA/D変換器用供給電圧(電源)ピンです。例えA/D変換が使われなくても、外部的にVCCへ接続されるべきです。A/D 変換が使われる場合、VCCから低域通過濾波器を通して接続されるべきです。

#### 2.2.18. AREF

AREFはA/D変換器用アナログ基準(電圧)ピンです。

### 3. 諸注意

#### 3.1. お断り

本データシート内で示された代表値はシミュレーションと同じ製法技術で製造された他のAVRマイクロコントローラの特性を基にしています。最小と最大の値はデバイスの特性が記載された後に利用可能になります。

#### 3.2. 資料

包括的なデータシート、応用記述、開発ツール群はhttp://www.atmel.com/avrでのダウンロートで利用可能です。

#### 3.3. コート 例

この文書はデバイスの様々な部分の使用法を手短に示す簡単なコード例を含みます。これらのコード例はアセンブルまたはコンパイルに先 立ってデバイス定義ヘッダファイルがインクルードされると仮定します。全てのCコンパイラ製造業者がヘッダファイル内にビット定義を含めるとは限 らず、またCでの割り込みの扱いがコンパイラに依存することに注意してください。より多くの詳細についてはCコンパイラの資料で確認し てください。

これらのコート「例はアセンフ」ルまたはコンハーイルに先立ってデバイス定義ファイルがインクルートされることが前提です。拡張I/O領域に配置した I/Oレシ、スタに対し、IN, OUT, SBIS, SBIC, CBI, SBI命令は拡張I/O領域へのアクセスを許す命令に置き換えられなければなりません。 代表的にはSBRS, SBRC, SBR, CBR命令と組み合わせたLDS, STS命令です。

#### 3.4. データ保持力

信頼性証明結果はデータ保持誤り率の反映を示し、20年以上/85℃または100年以上/25℃で1PPMよりずっと小さな値です。

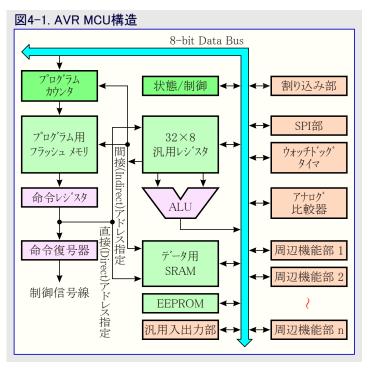

### 4. AVR CPU 37

#### 4.1. 序説

ここでは一般的なAVRコア構造について説明します。このCPUコアの主な機能は正しいプログラム実行を保証することです。従ってCPU はメモリ アクセス、計算実行、周辺制御、割り込み操作ができなければなりません。

#### 4.2. 構造概要

最大効率と平行処理のため、AVRはプログラムとデータに対してメモリ とハ、スを分離するハーハート、構造を使います。プログラムメモリ内の命令 は、単一段のパイプラインで実行されます。1命令の実行中に次の命 令がプログラムメモリから事前取得されます。この概念は全部のクロック 周期で命令実行を可能にします。プログラムメモリは実装書き換え可 能なフラッシュメモリです。

高速レジスタファイルは1クロック周期アクセスの32個の8ビット長汎用レジスタを含みます。これは1クロック周期ALU(Arithmetic Logic Unit)操作を許します。代表的なALU操作では2つのオペランドがレジスタファイルからの出力で、1クロック周期内でその操作が実行され、その結果がレジスタファイルに書き戻されます。

32個中の6つのレシ、スタは効率的なアトレス計算ができるデータ空間ア トレス指定用に、3つの16ビット長間接アトレスポインタ用レシ、スタとして使 われます。これらアトレスポインタの1つはプログラム用フラッシュメモリ内の 定数表参照用アトレスポインタとしても使えます。これら16ビット長付加 機能レシ、スタはX,Y,Zレシ、スタで、本章内で後述されます。

ALUはレシ、スタ間またはレシ、スタと定数間の算術及び論理操作を支援します。単一レシ、スタ操作もALUで実行できます。算術演算操作後、操作結果についての情報を反映するためにステータスレシ、スタ(SREG)が更新されます。

プログラムの流れは条件/無条件分岐や呼び出し命令によって提供され、全アドレス空間を直接アドレス指定できます。AVR命令の多くは

16ビット語(ワート)形式です。全てのプログラムメモリのアトレスは(訳注:定数のみを除き)16または32ビット長命令を含みます。

プログラム用フラッシュ メモリ空間はブート プログラム領域と応用プログラム領域の2つに分けられます。どちらの領域にも書き込み禁止や読み 書き防止用の専用施錠ビットがあります。応用フラッシュ メモリ領域内に書き込むSPM命令はブート プログラム領域内に属さ(存在し)なけれ ばなりません。

割り込みやサブルーチン呼び出し中、戻りアドレスを示すプログラム カウンタ(PC)はスタックに保存されます。スタックは一般的なデータ用SRAM上に 実際には割り当てられ、従ってスタック容量は全SRAM容量とSRAM使用量でのみ制限されます。全ての使用者プログラムはリセット処理ルー チンで(サブルーチン呼び出しや割り込みが実行される前に)、スタックホインタ(SP)を初期化しなければなりません。SPはI/O空間で読み書き アクセスが可能です。データ用SRAMはAVR構造で支援される5つの異なるアドレス指定種別を通して容易にアクセスできます。

AVR構造に於けるメモリ空間は全て直線的な普通のメモリ配置です。

柔軟な割り込み部にはI/O空間の各制御レジスタとステータスレジスタ(SREG)の特別な全割り込み許可(I)ビットがあります。全ての割り込みは割り込み、ケクタ表に個別の割り込み、ケクを持ちます。割り込みには割り込み、ケクタ表の位置に従う優先順があります。下位側割り込み、ケクタアドレスが高い優先順位です。

I/Oメモリ空間は制御レジスタ、SPI、他のI/O機能としてCPU周辺機能用の647トレスを含みます。I/Oメモリは直接またはレジスタファイルの次のデータ空間位置\$20~\$5Fとしてアクセスできます。加えてATmega16U4/32U4にはST/STS/STDとLD/LDS/LDD命令だけ使えるSRAM内の\$60~\$0FFに拡張I/O空間があります。

#### 4.3. ALU (Arithmetic Logic Unit)

高性能なAVRのALUは32個の全汎用レジスタとの直結で動作します。汎用レジスタ間または汎用レジスタと即値間の演算操作は単一クロック周期内で実行されます。ALU操作は算術演算、論理演算、ビット操作の3つの主な種類に大別されます。符号付きと符号なし両方の 乗算と固定小数点形式を支援する乗算器(乗算命令)も提供する構造の実装(製品)もあります。詳細記述については「命令要約」章 をご覧ください。

#### 4.4. ステータス レジスタ (Status Register) SREG

ステータスレジスタは最も直前に実行した演算命令の結果についての情報を含みます。この情報は条件処理を行うためのプログラムの流 れ変更に使えます。ステータスレジスタは「命令ー式手引書」で詳述したように、全てのALU操作後、更新されることに注目してください。 これは多くの場合でそれ用の比較命令使用の必要をなくし、高速でより少ないコードに帰着します。

ステータス レジ スタは割り込み処理ルーチン移行時の保存と割り込みからの復帰時の回復(復帰)が自動的に行われません。これはソフトウェア によって扱われなければなりません。

AVRのステータス レジスタ(SREG)は次のように定義されます。

| ヒット         | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |      |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$3F (\$5F) | Ι   | Т   | Н   | S   | V   | N   | Z   | С   | SREG |

| Read/Write  | R/W |      |

| 初期値         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

#### ● ビット7 - I : 全割り込み許可 (Global Interrupt Enable)

全割り込み許可ビットは割り込みが許可されるために設定(1)されなければなりません。そのとき、個別割り込み許可制御は独立した制御レジスタで行われます。全割り込み許可ビットが解除(0)されると、個別割り込み許可設定に拘らず、どの割り込みも許可されません。I ビットは割り込みが起こった後にハート・ウェアによって解除(0)され、後続の割り込みを許可するために、RETI命令によって設定(1)されます。Iビットは「命令一式手引書」で記述されるようにSEIやCLI命令で応用(プログラム)によって設定(1)や解除(0)もできます。

#### ● ビット6 - T:ビット変数 (Bit Copy Storage)

ビット複写命令、BLD(Bit LoaD)とBST(Bit STore)は操作したビットの転送元または転送先として、このTビットを使います。レジスタファイルのレジスタからのビットはBST命令によってTに複写でき、TのビットはBLD命令によってレジスタファイルのレジスタ内のビットに複写できます。

#### • ビット5 - H : ハーフキャリー フラク (Half Carry Flag)

ハーフキャリー(H)フラグはいくつかの算術操作でのハーフキャリーを示します。ハーフキャリーはBCD演算に有用です。詳細情報については「命令 要約」記述をご覧ください。

#### ● ビット4 - S : 符号 (Sign Bit, S= N Ex-OR V)

S7ラグは常に負(N)フラグと2の補数溢れ(V)フラグの排他的論理和です。詳細情報については「命令要約」記述をご覧ください。

#### ビット3 - V: 2の補数溢れフラグ (2's Complement Overflow Flag)

2の補数溢れ(V)フラグは2の補数算術演算を支援します。詳細情報については「命令要約」記述をご覧ください。

#### ビット2 – N: 負フラク (Negative Flag)

負(N)フラグは算術及び論理操作での負の結果(MSB=1)を示します。詳細情報については「命令要約」記述をご覧ください。

#### • Ľット1 – Z : Ľロ フラク (Zero Flag)

ゼロ(Z)フラグは算術及び論理操作でのゼロ(0)の結果を示します。詳細情報については「命令要約」記述をご覧ください。

#### • E<sup>\*</sup>yh0 – C : ++yJ– 750<sup>\*</sup> (Carry Flag)

キャリー(C)フラグは算術及び論理操作でのキャリー(またはボロー)を示します。詳細情報については「命令要約」記述をご覧ください。

#### 4.5. 汎用レジスタ ファイル

このレジスタファイルはAVRの増強したRISC命令群用に最適化されています。必要な効率と柔軟性を達成するために、次の入出力機構がレジスタファイルによって支援されます。

- •1つの8ビット出力オペラントと1つの8ビットの結果入力

- 2つの8ビット出力オペラントと1つの8ビットの結果入力

- 2つの8ビット出力オペランドと1つの16ビットの結果入力

•1つの16ビット出力オペランドと1つの16ビットの結果入力

図4-2.はCPU内の32個の汎用作業レジスタの構造を示します。

レジスタファイルを操作する殆どの命令は全てのレジスタに直接アクセスし、それらの殆どは単一周期命令です。

図4-2.で示されるように各レシスタは使用者データ空間の最初の32位置へ直接的に配置することで、それらはデータメモリアトレスも割り当てられます。例え物理的にSRAM位置として実装されていなくてもX,Y,Zレシ、スタ(ポインタ)がレシ、スタファイル内のどのレシ、スタの指示にも設定できるように、このメモリ構成は非常に柔軟なレシ、スタのアクセスを提供します。

#### 4.5.1. Xレシ スタ, Yレシ スタ, Zレシ スタ

R26~R31レジスタには通常用途の使用にいくつかの追加機能 があります。これらのレジスタはデータ空間の間接アトレス指定用の 16ビットアトレスポインタです。3つのX,Y,Z間接アトレスレジスタは図 4-3.で記載したように定義されます。

種々のアドレス指定種別で、これらのアドレス レジスタは固定変位、 自動増加、自動減少としての機能を持ちます(詳細については 「命令ー式手引書」をご覧ください)。

#### 図4-2. AVR CPU 汎用レジスタ構成図

|            | 7 0 | アドレス                                  |

|------------|-----|---------------------------------------|

|            | R0  | \$00                                  |

|            | R1  | \$01                                  |

|            | R2  | \$02                                  |

|            | 2   |                                       |

|            | R13 | \$0D                                  |

|            | R14 | \$0E                                  |

| ्रेग मा    | R15 | \$0F                                  |

| 汎用<br>レジスタ | R16 | \$10                                  |

| ファイル       | R17 | \$11                                  |

| 7717       | 2   |                                       |

|            | R26 | \$1A<br>\$1B<br>Xレジスタ 下位バイト<br>上位バイト  |

|            | R27 | \$1B 44 人 上位バイト                       |

|            | R28 | \$1C<br>\$1C<br>\$1D Yレジスタ 下位バイト      |

|            | R29 | \$1D <b>1</b> レイン 上位バイト               |

|            | R30 | *1E<br>\$1E<br>\$1F<br>Zレジスタ<br>上位バイト |

|            | R31 | \$1F <b>エレン ハタ</b> 上位バイト              |

| 凶4−3. X,Y,Z | レシス | 9構成図       |     |            |   |

|-------------|-----|------------|-----|------------|---|

|             | 15  | XH (上位)    |     | XL (下位)    | 0 |

| Χ レシ スタ     | 7   | R27 (\$1B) | 0 7 | R26 (\$1A) | 0 |

|             | 15  | YH (上位)    |     | YL (下位)    | 0 |

| Y レシ スタ     | 7   | R29 (\$1D) | 0 7 | R28 (\$1C) | 0 |

|             | 15  | ZH (上位)    |     | ZL (下位)    | 0 |

| Ζ レジスタ      | 7   | R31 (\$1F) | 0 7 | R30 (\$1E) | 0 |

|             |     |            |     |            |   |

#### 4.6. スタック ポインタ (Stack Pointer) SPH,SPL (SP)

スタックは主に一時データの保存、局所変数の保存、割り込みとサブルーチン呼び出し後の戻りアドレスの保存に使われます。スタック ポインタレ ジスタは常にこのスタックの先頭(<mark>訳注</mark>:次に使われるべき位置)を指し示します。スタックが高位メモリから低位メモリへ伸長するように実行され ることに注意してください。これはスタックへのPUSH命令はスタック ポインタを減少するという意味です。

スタック ポインタはサブルーチンや割り込みのスタックが配置されるデータSRAMのスタック領域を指し示します。データSRAM内のスタック空間はサブ ルーチン呼び出しの実行や割り込みの許可の何れにも先立ってプログラムによって定義されなければなりません。スタック ポインタは\$100以 上を指示するように設定されなければなりません。スタック ポインタの初期値は内蔵SRAMの最終アドレスです。スタック ポインタはPUSH命令 でデータがスタックに格納されると-1され、サブルーチン呼び出しや割り込みで戻りアドレスがスタックに格納されると-2されます。スタック ポインタは POP命令でデータがスタックから引き出されると+1され、サブルーチンからの復帰(RET)命令や割り込みからの復帰(RETI)命令でアドレスがス タックから引き出されると+2されます。

AVRのスタック ホーインタはI/O空間内の2つの8ビット レジスタとして実装されます。実際に使われるビット数は(そのデ・バーイス)実装に依存します。SPLだけが必要とされる程に小さいAVR構造の実装(デ・バース)のデータ空間もあることに注意してください。その場合、SPHレジスタは存在しません。

| ビット         | 15  | 14  | 13  | 12  | 11     | 10   | 9   | 8   |     |

|-------------|-----|-----|-----|-----|--------|------|-----|-----|-----|

| \$3E (\$5E) | -   | -   | -   | -   | (SP11) | SP10 | SP9 | SP8 | SPH |

| Read/Write  | R   | R   | R   | R   | R/W    | R/W  | R/W | R/W |     |

| 初期値         | 0   | 0   | 1   | 0   | 0      | 0    | 0   | 0   |     |

| ヒット         | 7   | 6   | 5   | 4   | 3      | 2    | 1   | 0   | _   |

| \$3D (\$5D) | SP7 | SP6 | SP5 | SP4 | SP3    | SP2  | SP1 | SP0 | SPL |

| Read/Write  | R/W | R/W | R/W | R/W | R/W    | R/W  | R/W | R/W |     |

| 初期値         | 1   | 1   | 1   | 1   | 1      | 1    | 1   | 1   |     |

(訳注)上記の初期値は修正漏れで、RAMENDの場合はATmega16U4=\$05FF,ATmega32U4=\$0AFFと思われます。 (訳注)原書本位置のRAMPZ記述は存在しないため、削除しました。

# Atmel

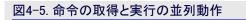

#### 4.7. 命令実行タイミング

本項は命令実行の一般的なアクセスタイシングの概念を記述します。AVR CPUはチップ(デ ハイス)用に選んだクロック元から直接的に生成したCPUクロック(clkCPU)によって駆動されます。内部クロック分周は使われません。

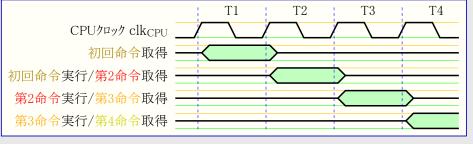

図4-5.はハーハート、構造と高速アクセスレジスタ ファイルの概念によって可能とされる並列の 命令取得と命令実行を示します。これは機 能対費用、機能対クロック、機能対電源部に 関する好結果と対応するMHzあたり1 MIPS を達成するための基本的なパイプラインの概 念です。

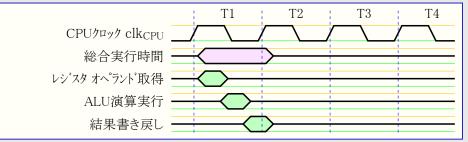

図4-6.はレシブスタファイルに対する内部タイシングの概念を示します。単一クロック周期で2つのレシブスタオヘプントを使うALU操作が実行され、その結果が転送先レシブスタへ書き戻されます。

#### 図4-6.1周期ALU命令

#### 4.8. リセットと割り込みの扱い

AVRは多くの異なる割り込み元を提供します。これらの割り込みと独立したリセット ヘブタ各々はプログラムメモリ空間内に独立したプログラム ヘブタを持ちます。全ての割り込みは割り込みを許可するために、ステータスレジスタ(SREG)の全割り込み許可(I)ビットと共に論理1が書か れなければならない個別の許可ビットを割り当てられます。BLB02またはBLB12 ブート施錠ビットがプログラム(0)されると、プログラムカウンタ値 によっては割り込みが自動的に禁止されるかもしれません。この特質はソフトウェア保護を改善します。詳細については226頁の「メモリ フ ログラミング」章をご覧ください。

既定でのプログラム メモリ空間の最下位アドレスはリセットと割り込みのベクタとして定義されます。ベクタの完全な一覧は36頁の「割り込み」で 示されます。この一覧は各種割り込みの優先順位も決めます。下位側アドレスがより高い優先順位です。リセットが最高優先順位で次が 外部割り込み要求0(INT0)です。割り込みベクタはMCU制御レジスタ(MCUCR)の割り込みベクタ選択(IVSEL)ビットの設定(1)によってブート フラッシュ領域先頭へ移動できます。より多くの情報については36頁の「割り込み」を参照してください。リセット ベクタもBOOTRSTヒューズの プログラム(0)によってブート フラッシュ領域先頭へ移動できます。215頁の「**ブート ローダ支援 - 書き込み中読み出し可能な自己プログラミンウ**゙」 をご覧ください。

割り込みが起こると全割り込み許可(I)ビットが解除(0)され、全ての割り込みは禁止されます。使用者ソフトウェアは多重割り込みを許可す るため、全割り込み許可(I)ビットへ論理1を書けます。その後全ての許可した割り込みが現在の割り込みルーチンで割り込めます。全割り 込み許可(I)ビットは割り込みからの復帰(RETI)命令が実行されると、自動的に設定(1)されます。

根本的に2つの割り込み形式があります。1つ目の形式は割り込み要求75/を設定(1)する事象によって起動されます。これらの割り込みでは割り込み処理ルーチンを実行するために、プログラムカウンタは対応する現実の割り込み、クタを指示し、ハートウェアが対応する割り込み要求75/でを解除(0)します。割り込み要求75/では解除(0)されるべき75/のビット位置へ論理1を書くことによっても解除(0)できます。 対応する割り込み許可ビットが解除(0)されている間に割り込み条件が起こると、割り込み要求75/が設定(1)され、割り込みが許可されるか、またはこの75/がソフトウェアによって解除(0)されるまで記憶(保持)されます。同様に、全割り込み許可(I)ビットが解除(0)されている間に1つまたはより多くの割り込み条件が起こると、対応する割り込み要求75/が設定(1)されて全割り込み許可(I)ビットが設定(1)されるまで記憶され、その(I=1)後で優先順に従って実行されます。

2つ目の割り込み形式は割り込み条件が存在する限り起動し(続け)ます。これらの割り込みは必ずしも割り込み要求7ラグを持っている とは限りません。割り込みが許可される前に割り込み条件が消滅すると、この割り込みは起動されません。

AVRが割り込みから抜け出すと常に主プログラムへ戻り、何れかの保留割り込みが扱われる前に1つ以上の命令を実行します。

ステータス レジスタ(SREG)は割り込みルーチンへ移行時の保存も、復帰時の回復も自動的に行われないことに注意してください。これはソフト ウェアによって扱われなければなりません。 割り込みを禁止するためにCLI命令を使うと、割り込みは直ちに禁止されます。CLI命令と同時に割り込みが起こっても、CLI命令後 に割り込みは実行されません。次例は時間制限EEPROM書き込み手順中に割り込みを無効とするために、これがどう使えるかを示し ます。

| アセンフ゛リ言語フ゜ロク゛ラム例                                                                                                                                                |                                                     |                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| IN<br>CLI<br>SBI<br>SBI<br>OUT                                                                                                                                  | R16, SREG<br>EECR, EEMPE<br>EECR, EEPE<br>SREG, R16 | ; ステータス レジ スタを保存<br>; EEPROM書き込み手順中割り込み禁止<br>; EEPROM主書き込み許可<br>; EEPROM書き込み開始<br>; ステータス レジ スタを復帰                                          |

| C言語プログラム例                                                                                                                                                       |                                                     |                                                                                                                                             |

| <pre>char cSREG;<br/>cSREG = SREG;<br/>disable_interrupt();<br/>EECR  = (1&lt;<eempe);<br>EECR  = (1&lt;<eepe);<br>SREG = cSREG:</eepe);<br></eempe);<br></pre> |                                                     | /* ステータスレジスタ保存変数定義 */<br>/* ステータスレジスタを保存 */<br>/* EEPROM書き込み手順中割り込み禁止 */<br>/* EEPROM主書き込み許可 */<br>/* EEPROM書き込み開始 */<br>/* ステータスレジスタを復帰 */ |

割り込みを許可するためにSEI命令を使うと、次例で示されるようにどの保留割り込みにも先立ってSEI命令の次の命令が実行されます。

| アセンブリ言語プログラム例                          |                                        |

|----------------------------------------|----------------------------------------|

| SEI<br>SLEEP                           | ;全割り込み許可<br>;休止形態移行(割り込み待ち)            |

| C言語プログラム例                              |                                        |

| <pre>enable_interrupt();sleep();</pre> | /* 全割り込み許可 */<br>/* 休止形態移行 (割り込み待ち) */ |

注: SLEEP命令までは割り込み禁止、保留割り込み実行前に休止形態へ移行します。

#### 4.8.1. 割り込み応答時間

許可した全てのAVR割り込みに対する割り込み実行応答は最小4クロック周期です。4クロック周期後、実際の割り込み処理ルーチンに対するプログラム ヘクタ アドレスが実行されます。この4クロック周期時間中にプログラム カウンタ(PC)がスタック上に保存(プッシュ)されます。このヘクタは 標準的に割り込み処理ルーチンへの無条件分岐で、この分岐は3クロック周期要します。複数周期命令実行中に割り込みが起こると、その割り込みが扱われる前に、この命令が完了されます。MCUが休止形態の時に割り込みが起こると、割り込み実行応答時間は4クロック周期増やされます。この増加は選んだ休止形態からの起動時間に加えてです。

割り込み処理ルーチンからの復帰は4クロック周期要します。これらの4クロック周期中、プログラムカウンタ(PC:2ハイト)がスタックから取り戻され(ポップ)、スタックホインタは増加され(+2)、ステータスレジズタ(SREG)の全割り込み許可(I)ビットが設定(1)されます。

### 5. AVRのメモリ

この項は本デバイスの各種メモリを記述します。AVR構造にはプログラム メモリ空間とデータ メモリ空間の2つの主なメモリ空間があります。加えて本デバイスはデータ保存用EEPROMメモリが特徴です。3つのメモリ空間全ては一般的な直線的アドレスです。

| 表5-1. メモリ割付                                  |                                       |             | Γ                                                   |                                                     |  |  |

|----------------------------------------------|---------------------------------------|-------------|-----------------------------------------------------|-----------------------------------------------------|--|--|

| というないというというというというというというというというというというというというという | 別                                     | ニーモニック      | ATmega16U4                                          | ATmega32U4                                          |  |  |

|                                              | 容量                                    | Flash size  | 16Kハㆍイト                                             | 32Kバイト                                              |  |  |

| フラッシュ メモリ                                    | 開始アドレス                                | -           | \$00                                                | 000                                                 |  |  |

|                                              | 終了アドレス                                | Flash end   | \$3FFF( <mark>注1</mark> )/\$1FFF( <mark>注2</mark> ) | \$7FFF( <mark>注1</mark> )/\$3FFF( <mark>注2</mark> ) |  |  |

|                                              | 容量                                    | -           | 32/                                                 | バイト                                                 |  |  |

| 汎用レジスタ                                       | 開始アドレス                                | -           | \$00                                                | 000                                                 |  |  |

|                                              | 終了アドレス                                | -           | \$001F                                              |                                                     |  |  |

|                                              | 容量                                    |             | 64/                                                 | バイト                                                 |  |  |

| (標準)I/Oレシ <sup>゙</sup> スタ                    | 開始アドレス                                | -           | \$0020                                              |                                                     |  |  |

|                                              | 終了アドレス                                | -           | \$005F                                              |                                                     |  |  |

|                                              | 容量           拡張I/Oレジズタ         開始アトレス |             | 160시~시ト                                             |                                                     |  |  |

| 拡張I/Oレシ <sup>゙</sup> スタ                      |                                       |             | \$0060                                              |                                                     |  |  |

|                                              | 終了アドレス                                | -           | \$00FF                                              |                                                     |  |  |

|                                              | 容量                                    | ISRAM size  | 1.25Kバイト                                            | 2.5Kバイト                                             |  |  |

| 内蔵SRAM                                       | 開始アドレス                                | ISRAM start | \$0                                                 | 100                                                 |  |  |

|                                              | 終了アドレス                                | ISRAM end   | \$05FF                                              | \$0AFF                                              |  |  |

|                                              | 容量                                    | XMem size   |                                                     |                                                     |  |  |

| 外部メモリ                                        | 開始アドレス                                | XMem start  | (存在しる                                               | ません。)                                               |  |  |

|                                              | 終了アドレス                                | XMem end    |                                                     |                                                     |  |  |

|                                              | 容量                                    | E2 size     | 512ハイト                                              | 1Kハ <sup>*</sup> イト                                 |  |  |

| 内蔵EEPROM                                     | 開始アドレス                                | -           | \$00                                                | 000                                                 |  |  |

|                                              | 終了アドレス                                | E2 end      | \$01FF                                              | \$03FF                                              |  |  |

注1: バイト アドレスです。

注2: 語(ワート=16ビット)アトレスです。

#### 5.1. 実装書き換え(ISP: In-System Program)可能なプログラム用フラッシュ メモリ

本デバイスはプログラム保存用に実装書き換え可能な16/32Kバイトのフラッシュメモリをチップ上に含みます。全てのAVR命令が16または32 ビット幅のため、このフラッシュメモリは8/16K×16ビットとして構成されます。ソフトウェア保護のため、フラッシュプログラムメモリ空間はブートプログラ ム領域と応用プログラム領域の2つに分けられます。

フラッシュメモリは最低100,000回の消去/書き込み回数耐久性があります。本デバイスのプログラムカ ウンタ(PC)は13/14ビット幅で、故に8/16Kプログラムメモリ位置のアドレス指定です。フートプログラム領 域の操作と関係するソフトウェア保護用フート施錠ビットは215頁の「フートロータ・支援 - 書き込み中読 み出し可能な自己プログラミング」の詳細で記述されます。226頁の「メモリプログラミング」はSPI、JTA G、並列プログラミング動作でのフラッシュメモリプログラミングの詳細な記述を含みます。

定数表は全てのプログラムメモリアドレス空間に配置できます。(LPM命令記述参照) 命令の取得と実行のタイミング図は9頁の「命令実行タイミング」で示されます。

| 3 | 図5-1. プログラム メモリ配置図      |               |  |  |  |  |  |  |

|---|-------------------------|---------------|--|--|--|--|--|--|

|   | 応用プログラム用<br>フラッシュ メモリ   | \$0000        |  |  |  |  |  |  |

|   | ブート プログラム用<br>フラッシュ メモリ | \$1FFF/\$3FFF |  |  |  |  |  |  |

#### 5.2. データ用SRAM メモリ

図5-2.は本デバイスのSRAMメモリ構成方法を示します。

本デバイスはINやOUT命令で予約した64位置で支援されるより多くの周 辺機能部を持つ複合マイクロコントローラです。SRAM(データ空間)内\$60~ \$FFの拡張I/O空間に対してLD/LDS/LDDとST/STS/STD命令だけが 使えます。

下位1536/2816データメモリ位置はレジスタファイル、I/Oメモリ、拡張I/Oメモリ、 データ用内蔵SRAMに充てます。先頭の32位置はレジスタファイル、次の64 位置は標準I/Oメモリ、その次の160位置は拡張I/Oメモリ、そして次の 1280/2560位置はデータ用内蔵SRAMに充てます。

直接、間接、変位付き間接、事前減少付き間接、事後増加付き間接の 5つの異なるアドレス指定種別でデータ メモリ(空間)を網羅します。 レジスタ ファ イル内のレジスタR26~R31は間接アドレス指定ポインタ用レジスタが特徴です。

直接アドレス指定はデータ空間全体に届きます。

変位付き間接動作はYまたはZレジスタで与えられる基準アドレスからの63ア ドレス位置に届きます。

自動の事前減少付きと事後増加付きのレジスタ間接アドレス指定動作を使う時に(使われる)X,Y,Zアドレスレジスタは減少(-1)または増加(+1)されます。

本デバイスの32個の汎用レジスタ、64個のI/Oレジスタ、160個の拡張I/Oレジスタ、1.25K(1280)/2.5K(2560)パイトのデータ用内蔵SRAMはこれら全てのアドレス指定種別を通して全部アクセスできます。レジスタファイルは8頁の「汎用レジスタファイル」で記述されます。

#### 5.2.1. データ メモリ アクセス タイミンク

この項は内部メモリアクセスに対する一般的なアクセスタイミングの 概念を記述します。データ用内蔵SRAMアクセスは図5-3.で記 載されるように2 clk<sub>CPU</sub>周期で実行されます。

(訳注)内蔵SRAMのアクセスを含む代表的な命令はT1,T2の 2周期で実行され、T1で対象アドレスを取得/(算出)/ 確定し、T2で実際のアクセスが行われます。後続する (T1)は次の命令のT1です。

| 図5-3. データ用内蔵                        | SRAMアクセス周期                                  |

|-------------------------------------|---------------------------------------------|

| CPUクロック clk <sub>CPU</sub><br>アト・レス | T1     T2     (T1)       直前のアドレス     有効アドレス |

| データ<br>書き込み<br>WR                   |                                             |

| データ<br>読み込み<br>RD                   |                                             |

#### 図5-2. データ空間とSRAMの配置

|                        |                    | アドレス                 |

|------------------------|--------------------|----------------------|

| レジスタ ファイル              | R0                 | \$0000               |

| (32×8)                 | $\sim$ R31         | ~<br>\$001F          |

| I/O レジスタ               | \$00               | \$0020               |

| (64×8)                 | ~<br>\$3F          | $\sim$ \$005F        |

| 拡張I/O レジスタ             | \$0060             | \$0060               |

| $(160 \times 8)$       | \$00FF             | \$00FF               |

| 内蔵 SRAM                | \$0100             | \$0100               |

| $(1280/2560 \times 8)$ | ≈<br>\$05FF∕\$0AFF | $\sim$ \$05FF/\$0AFF |

|                        |                    |                      |

注:赤字はI/Oアドレス

#### 5.3. データ用EEPROMメモリ

本デバイスは512/1Kバイトのデータ用EEPROMを含みます。それは単一バイトが読み書きできる分離したデータ空間として構成されます。 EEPROMは最低100,000回の消去/書き込み回数の耐久性があります。CPUとEEPROM間のアクセスは以降のEEPROMアドレスレジスタ、 EEPROMデータレジスタ、EEPROM制御レジスタで詳細に記述されます。

EEPROMのSPI、JTAG、並列プログラミングの詳細記述については各々238頁、241頁、229頁をご覧ください。

#### 5.3.1. EEPROMアクセス

EEPROMアクセスレジスタはI/O空間でアクセス可能です。

EEPROMの書き込み(訳注:原文はアクセス)時間は14頁の表5-2.で与えられます。(書き込みは)自己タイシング機能ですが、使用者ソフトウェアは次パイトが書ける時を検知してください。使用者コートがEEPROMに書く命令を含む場合、いくつかの予防処置が取られなければなりません。厳重に濾波した電源では電源投入/切断でVCCが緩やかに上昇または下降しそうです。これはデバイスが何周期かの時間、使われるクロック周波数に於いて最小として示されるより低い電圧で走行する原因になります。これらの状態で問題を避ける方法の詳細については15頁の「EEPROMデータ化けの防止」をご覧ください。

予期せぬEEPROM書き込みを防止するため、特別な書き込み手順に従わなければなりません。この詳細については「EEPROM制御レジスタ」の記述を参照してください。

EEPROMが読まれると、CPUは次の命令が実行される前に4クロック周期停止されます。EEPROMが書かれると、CPUは次の命令が実行される前に2クロック周期停止されます。

| \$22 (\$42)       -       -       -       -       -       (EEAR9)       EEAR8       EEARH         Read/Write       R       R       R       R       R       R/W       R/W         初期値       0       0       0       0       0       7       7       6       5       4       3       2       1       0         ***/>***/**       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ***       ****       ***       *** <t< th=""><th>ビット</th><th>15</th><th>14</th><th>13</th><th>12</th><th>11</th><th>10</th><th>9</th><th>8</th><th></th></t<> | ビット         | 15    | 14    | 13    | 12    | 11    | 10    | 9       | 8     |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|-------|-------|-------|-------|-------|---------|-------|-------|

| 初期値     0     0     0     0     0     不定     不定       ビット     7     6     5     4     3     2     1     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | \$22 (\$42) | —     | -     | -     | -     | -     | -     | (EEAR9) | EEAR8 | EEARH |

| t'yh <u>7 6 5 4 3 2 1 0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Read/Write  | R     | R     | R     | R     | R     | R     | R/W     | R/W   |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 初期値         | 0     | 0     | 0     | 0     | 0     | 0     | 不定      | 不定    |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ビット         | 7     | 6     | 5     | 4     | 3     | 2     | 1       | 0     | _     |

| 21(41) EEAR7   EEAR6   EEAR5   EEAR4   EEAR3   EEAR2   EEAR1   EEAR0   EEARL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | \$21 (\$41) | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1   | EEAR0 | EEARL |

| Read/Write R/W R/W R/W R/W R/W R/W R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Read/Write  | R/W     | R/W   |       |

| 初期値 不定 不定 不定 不定 不定 不定 不定                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 初期値         | 不定      | 不定    |       |

#### 5.3.2. EEARH,EEARL (EEAR) – EEPROMアトレス レジスタ (EEPROM Address Register)

#### ビット15~10 - Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

#### • ビット9~0 - EEAR9~0 : EEPROM7トレス (EEPROM Address)

EEPROMアドレスレジ゙スタ(EEARHとEEARL)は512/1KベイトEEPROM空間のEEPROMアドレスを指定します。EEPROMデータ ベイトは0~ 511/1023間で直線的に配されます。EEARの初期値は不定です。EEPROMがアクセスされるであろう前に適切な値が書かれなければ なりません。

#### 5.3.3. EEDR - EEPROMデータ レシズタ (EEPROM Data Register)

| ビット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |      |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|------|

| \$20 (\$40) | (MSB) |     |     |     |     |     |     | (LSB) | EEDR |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |      |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |      |

#### • ビット7~0 - EEDR7~0 : EEPROMデータ (EEPROM Data)

EEPROM書き込み操作に対してEEDRはEEPROMアドレスレジスタ(EEAR)で与えたアドレスのEEPROMへ書かれるべきデータを含みます。 EEPROM読み込み操作に対してEEDRはEEARで与えたアドレスのEEPROMから読み出したデータを含みます。

#### 5.3.4. EECR - EEPROM制御レジスタ (EEPROM Control Register)

| ビット         | 7 | 6 | 5     | 4     | 3     | 2     | 1    | 0    | _    |

|-------------|---|---|-------|-------|-------|-------|------|------|------|

| \$1F (\$3F) | - | - | EEPM1 | EEPM0 | EERIE | EEMPE | EEPE | EERE | EECR |

| Read/Write  | R | R | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  |      |

| 初期値         | 0 | 0 | 不定    | 不定    | 0     | 0     | 不定   | 0    |      |

ビット7,6 - Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

#### • ビット5.4 - EEPM1.0 : EEPROM7<sup>°</sup>ログラミング種別 (EEPROM Programing Mode Bits)

EEPROMプログラミング種別ビット設定はEEPROMプロ グラミング許可(EEPE)書き込み時にどのプログラミング 動作が起動されるかを定義します。1つの非分離 操作(旧値消去と新値書き込み)、または2つの異な る操作として消去と書き込み操作を分離してデータ をプログラムする(書く)ことが可能です。各動作に対 するプログラミング時間は表5-2.で示されます。EEPE が設定(1)されている間はEEPMnへのどの書き込

| 表5-2. EEPROMプログラミング種別 |           |                                                                                                                       |  |  |  |  |

|-----------------------|-----------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| EEPM0                 | プログラミング時間 | 動作                                                                                                                    |  |  |  |  |

| 0                     | 3.4ms     | 1操作での消去と書き込み(非分離操作)                                                                                                   |  |  |  |  |

| 1                     | 1.8ms     | 消去のみ                                                                                                                  |  |  |  |  |

| 0                     | 1.8ms     | 書き込みのみ                                                                                                                |  |  |  |  |

| 1                     | _         | 将来使用に予約                                                                                                               |  |  |  |  |

|                       |           | EEPM0         プ <sup>°</sup> ログ <sup>*</sup> ラミング <sup>*</sup> 時間           0         3.4ms           1         1.8ms |  |  |  |  |

みも無視されます。リセット中、EEPMnビットはEEPROMがプログラミング作業中を除いて'00'にリセットされます。

#### ビット3 - EERIE : EEPROM操作可割り込み許可 (EEPROM Ready Interrupt Enable)

EERIEの1書き込みはステータスレジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されているなら、EEPROM操作可割り込みを許可しま す。EERIEの0書き込みは、この割り込みを禁止します。EEPROM操作可割り込みはEEPROMプログラム許可(EEPE)が解除(0)されてい ると、継続する割り込みを発生します。

#### ビット2 - EEMPE : EEPROM主プログラム許可 (EEPROM Master Program Enable)

EEMPEビットはEEPROMプログラム許可(EEPE)ビットの1書き込みが有効か無効かどちらかを決めます。EEMPEが設定(1)されると、4クロッ ク周期内のEEPE設定(1)は選んだアドレスのEEPROMをプログラムします。EEMPEが0なら、EEPE設定(1)は無効です。EEMPEがソフトウェア によって設定(1)されてしまうと、4クロック周期後にハートウェアがこのビットを0に解除します。EEPROM書き込み手順については次のEEPE 記述をご覧ください。

#### • ビット1 - EEPE : EEPROMプログラム許可 (EEPROM Program Enable)

EEPROMプログラム許可信号(EEPE)はEEPROMへのプログラミング許可信号です。EEPEが(1を)書かれると、EEPROMはEEPMnビット設定 に従ってプログラムされます。論理1がEEPEへ書かれる前にEEPROM主プログラム許可(EEMPE)ビットは1を書かれなければならず、さもな ければEEPROM書き込み(消去)は行われません。EEPROMを書くとき、次の手順に従うべきです(手順3.と4.の順番は重要ではありま せん)。

- 1. EEPROMプログラム許可(EEPE)ビットが0になるまで待ちます。

- 2. SPM制御/状態レジスタ(SPMCSR)のSPM操作許可(SPMEN)ビットが0になるまで待ちます。

- 3. 今回のEEPROMアドレスをEEPROMアドレス レジスタ(EEAR)に書きます。(任意、省略可)

- 4. 今回のEEPROMデータをEEPROMデータレジスタ(EEDR)に書きます。(任意、省略可)

- 5. EEPROM制御レジスタ(EECR)のEEPROM主プログラム許可(EEMPE)ビットに1を、EEPROMプログラム許可(EEPE)ビットに0を同時に書き ます。

- 6. EEMPEビット設定後4クロック周期内にEEPROMプログラム許可(EEPE)ビットへ論理1を書きます。

CPUがフラッシュメモリ書き込み中、EEPROMはプログラム(書き込みが)できません。ソフトウェアは新規EEPROM書き込みを始める前にフラッ シュメモリのプログラミングが完了されていることを検査しなければなりません。2.はソフトウェアがフラッシュメモリをプログラム(書き込みを)することを CPUに許すブートローダを含む場合だけ関係します。フラッシュメモリが決してCPUによって更新されないなら、2.は省略できます。ブートプ ログラミングについての詳細に関しては215頁の「ブートローダ支援 - 書き込み中読み出し可能な自己プログラミング」をご覧ください。

警告: 手順5.と6.間の割り込みはEEPROM主プログラム許可が時間超過するため、書き込み周期失敗になります。 EEPROMをアクセスす る割り込みルーチンが他のEEPROMアクセスを中断し、EEARかEEDRが変更されると、中断したEEPROMアクセスを失敗させます。こ れらの問題を避けるため、全ての手順中、ステータスレジ、スタ(SREG)の全割り込み許可(I)ビットは解除(0)されていることが推奨され ます。

書き込み(プログラミング)アクセス時間が経過されると、EEPROMプログラム許可(EEPE)ビットはハードウェアによって解除(0)されます。使用者ソフト ウェアは次バイトを書く前にこのビットをホーリングし、0を待つことができます。EEPEが設定(1)されてしまうと、次の命令が実行される前に CPUは2周期停止されます。

#### ● ビット0 - EERE : EEPROM読み込み許可 (EEPROM Read Enable)

EEPROM読み込み許可信号(EERE)はEEPROMへの読み込みストローブです。EEARに正しいアトレスが設定されると、EEPROM読み出 しを起動するためにEEREビットは1を書かれなければなりません。EEPROM読み出しアクセスは(その)1命令で行われ、要求したデータは 直ちに利用できます。EEPROMが読まれるとき、次の命令が実行される前にCPUは4周期停止されます。

使用者は読み込み操作を始める前にEEPEビットをポーリングすべきです。書き込み(プログラム)操作実行中の場合、EEPROMアドレス レジ スタ(EEAR)の変更もEEPROM読み込みもできません。

EEPROMアクセスの時間に校正済み内蔵RC発振器が使われま 表5-3. EEPROM書き込み時間 す。右表はCPUからのEEPROMアクセスに対する代表的な書き 込み時間を示します。

| 項目              | 校正付き内蔵RC<br>発振器周期数 | 代表    |  |

|-----------------|--------------------|-------|--|

| EEPROM書き込み(CPU) | 26,368             | 3.3ms |  |

次のコートが例はアセンブリ言語とC言語でのEEPROM消去、書き込み、または非分離書き込み関数を示します。本例は(例えば全割り込み禁止によって)割り込みが制御され、これらの関数実行中に割り込みが起きない前提です。本例はソフトウェア内にフラッシュ ブート ローダ が無い前提でもあります。そのようなコートが存在する場合、EEPROM書き込み関数は何れかが実行するSPM命令の完了も待たねばなりません。(訳注:共通性から次例は補足修正しています。)

| アセンブリ言語プ   | ログラム例                                         |                                                                                                                                      |                                                                                                                                                                                       |

|------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EEPROM_WR: | SBIC<br>RJMP                                  | EECR, EEPE<br>EEPROM_WR                                                                                                              | ;EEPROMプログラミング完了ならばスキップ<br>;以前のEEPROMプログラミング完了まで待機                                                                                                                                    |

| ,          | LDI<br>OUT<br>OUT<br>OUT<br>SBI<br>SBI<br>RET | R19, (0< <eepm1) (0<<eepm0)<br=""  ="">EECR, R19<br/>EEARH, R18<br/>EEARL, R17<br/>EEDR, R16<br/>EECR, EEMPE<br/>EECR, EEPE</eepm1)> | ; プログラミング種別値取得(本例は非分離)<br>; 対応プログラミング種別設定<br>; EEPROMアドレス上位ベイト設定<br>; EEPROMアドレス下位ベイト設定<br>; EEPROM書き込み値を設定<br>; EEPROM主プログラム許可ビット設定<br>; EEPROMプログラミング開始(プログラム許可ビット設定)<br>; 呼び出し元へ復帰 |

#### C言語プログラム例

void EEPROM\_write(unsigned int uiAddress, unsigned char ucData)

{

| <pre>while(EECR &amp; (1&lt;<eepe));< pre=""></eepe));<></pre>             | /* 以前のEEPROMプログラミング完了まで待機 */ |

|----------------------------------------------------------------------------|------------------------------|

| EECR = (0 << EEPM1)   (0 << EEPM0);                                        | /* 対応プログラミング種別設定 */          |

| EEAR = uiAddress;                                                          | /* EEPROMアドレス設定 */           |

| EEDR = ucData;                                                             | /* EEPROM書き込み値を設定 */         |

| EECR $\mid$ = (1< <eempe);< td=""><td>/* EEPROM主プログラム許可 */</td></eempe);<> | /* EEPROM主プログラム許可 */         |

| EECR $\mid$ = (1< <epe);< td=""><td>/* EEPROMプ゜ログラミンク゛開始 */</td></epe);<>  | /* EEPROMプ゜ログラミンク゛開始 */      |

| }                                                                          |                              |

#### 注:5頁の「コート「例」をご覧ください。

次のコード例はアセンブリ言語とC言語でのEEPROM読み込み関数を示します。本例は割り込みが制御され、これらの関数実行中に割り込みが起きない前提です。

| アセンブリ言語フ                                                                                                                                                                                                                                                                                                                     | ゚ログラム例                         |                                                     |                                                                                                        |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|--|

| EEPROM_RD:                                                                                                                                                                                                                                                                                                                   | SBIC<br>RJMP                   | EECR, EEPE<br>EEPROM_RD                             | ;EEPROMプログラミング完了ならばスキップ<br>;以前のEEPROMプログラミング完了まで待機                                                     |  |  |  |

| ,                                                                                                                                                                                                                                                                                                                            | OUT<br>OUT<br>SBI<br>IN<br>RET | EEARH, R18<br>EEARL, R17<br>EECR, EERE<br>R16, EEDR | ;EEPROMアドレス上位バイト設定<br>;EEPROMアドレス下位バイト設定<br>;EEPROM読み出し開始(読み込み許可ビット設定)<br>;EEPROM読み出し値を取得<br>;呼び出し元へ復帰 |  |  |  |

| C言語プログラム                                                                                                                                                                                                                                                                                                                     | 例                              |                                                     |                                                                                                        |  |  |  |

| C言語プログラム例<br>unsigned char EEPROM_read(unsigned int uiAddress)<br>{<br>while(EECR & (1< <epe));<br>EEAR = uiAddress;<br/>EECR  = (1&lt;<ere);<br>return EEDR;<br/>}<br/>/* 以前のEEPROMプログラシング完了まで待機 */<br/>/* EEPROMプトレス設定 */<br/>/* EEPROM読み出し開始 */<br/>/* EEPROM読み出し開始 */<br/>/* EEPROM読み出し値を取得,復帰 */</ere);<br></epe));<br> |                                |                                                     |                                                                                                        |  |  |  |

注: 5頁の「コート」例」をご覧ください。

#### 5.3.5. EEPROMデータ化けの防止

低VCCの期間中、正しく動作するための供給電圧がCPUとEEPROMに対して低すぎるためにEEPROMデータが化け得ます。これらの 問題はEEPROMを使う基板段階の装置と同じで、同じ設計上の解決策が適用されるべきです。

EEPROMデータ化けは電圧が低すぎる時の2つの状態によって起こされ得ます。1つ目として、EEPROMへの通常の書き込み手順は 正しく動作するための最低電圧が必要です。2つ目として、供給電圧が低すぎると、CPU自身が命令を間違って実行し得ます。 EEPROMデータ化けは次の推奨設計によって容易に避けられます。

不充分な供給電源電圧の期間中、AVRのRESETを活性(Low)に保ってください。これは内蔵低電圧検出器(BOD)を許可することに よって行えます。内蔵BODの検出電圧が必要とした検出電圧と一致しない場合、外部低VCCリセット保護回路が使えます。書き込み 動作実行中にリセットが起こると、この書き込み操作は供給電源電圧が充分ならば(継続)完了されます。

#### 5.4. I/O メモリ (レジスタ)

本デバイスのI/O空間定義は269頁の「レジスタ要約」で示されます。

全てのI/Oと周辺機能はI/O空間に配置されます。全てのI/O位置はI/O空間と32個の汎用作業レジスタ間のデータ転送を行うLD/LDS /LDD命令とST/STS/STD命令によってアクセスされます。アドレス範囲\$00~\$1F内のI/OレジスタはSBI命令とCBI命令の使用で直接的に ビットアクセス可能です。これらのレジスタではSBISとSBIC命令の使用によって単一ビット値が検査できます。より多くの詳細については 「命令要約」章を参照してください。I/O指定命令INとOUTを使う時はI/Oアドレス\$00~\$3Fが使われなければなりません。LD命令とST 命令を使い、データ空間としてI/Oレジスタをアクセスする時はこれらのアドレスに\$20が加算されなければなりません。

本デバイスはINやOUT命令で予約された64位置で支援されるより多くの周辺機能部を持つ複合マイクロコントローラです。SRAM(データ空間)内\$60~\$0FFの拡張I/O領域に対してはLD/LDS/LDDとST/STS/STD命令だけが使えます。

将来のデバイスとの共通性を保つため、アクセスされる場合、予約ビットは0が書かれるべきです。予約済みI/Oメモリアトレスは決して書かれるべきではありません。

状態フラグのいくつかはそれらへ論理1を書くことによって解除(0)されます。CBIとSBI命令は他の多くのAVRの様ではなく、指定ビットだ けを操作し、従って状態フラグのようなものを含むレジスタに使えることに注意してください。CBIとSBI命令は(I/Oアドレス)\$00~\$1Fのレジ スタでのみ動作します。

I/Oと周辺制御レジスタは以降の項で説明されます。

#### 5.4.1. 汎用I/Oレジスタ

本デバイスは3つの汎用I/Oレジスタを含みます。これらのレジスタはどの情報の格納にも使え、特に全体変数や状態フラグの格納に有用です。(I/O)アドレス範囲\$00~\$1Fの汎用I/OレジスタはSBI,CBI,SBIS,SBIC命令の使用で直接ビットアクセスが可能です。

5.4.2. GPIOR2 - 汎用I/Oレジスタ2 (General Purpose I/O Register 2)

| ビット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |        |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$2B (\$4B) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR2 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

#### 5.4.3. GPIOR1 - 汎用I/Oレジスタ1 (General Purpose I/O Register 1)

| ビット          | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      | _      |

|--------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| \$2A (\$4A)  | (MSB)  |        |        |        |        |        |        | (LSB)  | GPIOR1 |

| Read/Write   | R/W    |        |

| 10000, 11100 | 14/ 11 | 14/ 11 | 14/ 11 | 14/ 11 | 10/ 11 | 10/ 11 | 10/ 11 | 10/ 11 |        |

#### 5.4.4. GPIORO - 汎用I/Oレジスタの (General Purpose I/O Register 0)

| ビット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |        |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$1E (\$3E) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR0 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

### 6. システム クロックとクロック選択

#### 6.1. クロック系統とその配給

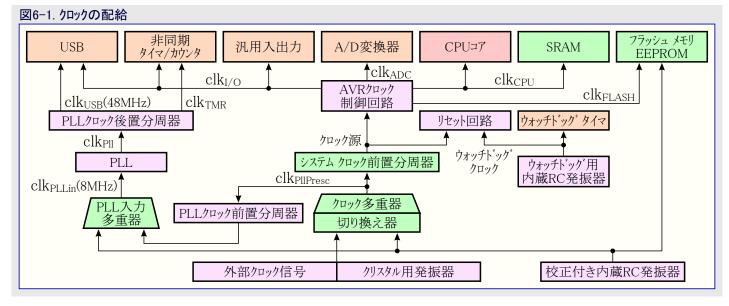

図6-1.はAVR内の主要なクロック系統とその配給を示します。全てのクロックが与えられた時間有効である必要はありません。消費電力低減のために、26頁の「電力管理と休止形態」で記述される各種休止形態の使用によって使われない部分のクロックを停止することができます。クロック系統は以下で詳細に示されます。

#### **6.1.1. СРU クロック** – clk<sub>CPU</sub>

CPUクロックはAVRコアの動作と関係する系統の部分に配給されます。このような部分の例は汎用レジスタファイル、ステータスレジスタ、スタックポインタを保持するデータメモリです。CPUクロックの停止はコアが一般的な操作や計算を実行することを禁止します。

#### **6.1.2. I/O クロック** – clk<sub>I/O</sub>

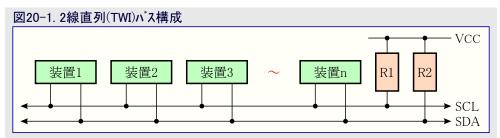

I/Oクロックはタイマ/カウンタ、SPI、USARTのようなI/O部の大部分で使われます。I/Oクロックは外部割り込み部でも使われますが、いくつかの外部割り込みは例えI/Oクロックが停止されても検出されることをこのような割り込みに許す非同期論理回路によって検出されることに注意してください。また、2線直列I/F(TWI)部のアドレス認証は全休止形態で取り扱われます。

#### **6.1.3. フラッシュ クロック** – clk<sub>FLASH</sub>

フラッシュクロックはフラッシュメモリインターフェースの動作を制御します。このフラッシュクロックは常にCPUクロックと同時に活動します。

#### 6.1.4. A/D変換クロック - clk<sub>ADC</sub>

A/D変換器には専用のクロック範囲が提供されます。これはデジタル回路によって生成される雑音を低減するためにCPUとI/Oクロックの 停止を許します。これはより正確なA/D変換結果を与えます。

#### 6.1.5. PLL前置分周クロック - clk<sub>PllPresc</sub>

PLLは8MHz入力を必要とします。前置分周器は必要ならば2分周を使って、(クリスタルまたは外部供給元から)8MHzまたは16MHzどちらかの供給元の使用を使用者に許します。この前置分周器出力はシステム クロック多重器の出力または校正付き内蔵8MHz発振器の選択を使用者に許す、PLL入力多重器へ行きます。

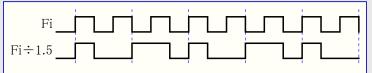

#### 6.1.6. PLL出 カクロック - clk<sub>Pll</sub>

許可時、PLLは32MHz~96MHzの多数の選択から1つの周波数を出力します。出力周波数はPLL周波数制御(PLLFRQ)レジスタに よって決められます。この周波数は電源電圧と無関係です。PLL出力は共通のPLL信号から選んだ分周比(1/1,1/1.5/1/2)の各々の 結果で、2つの異なる周波数(clkusbとclkTMR)生成を使用者に許す後置分周器に接続されます。

#### 6.1.7. 高速タイマ クロック - clk<sub>TMR</sub>

許可時、32MHz~96MHzの多くの選択から、PLLは後置分周器へ行く1つの周波数を出力します。高速タイマ入力周波数は1/1, 1/1.5, 1/2の比率を目的とするPLL後置分周器によって生成されます。これはPLL周波数制御(PLLFRQ)レジスタで決めることができま す。高速タイマ最大入力周波数は電源電圧に依存し、5Vで最大64MHzに達します。

#### 6.1.8. USBクロック – clk<sub>USB</sub>

USBハートウェア部は48MHzクロックを必要とします。このクロックはチップ上のPLLから生成されます。PLLの出力はPLL後置分周器を通り、 周波数は2分周または直接のどちらかでclkusB信号へ接続できます。

#### <mark>6.2</mark>. クロック元

このデバイスには右で示されるようにフラッシュヒュース、ビットによっ て選択可能な後続のクロック元選択があります。選んだクロック元 からのクロックはAVRクロック発生器への入力で、適切な単位部へ 配給されます。

#### 表6-1. クロック元選択

| ሳቦック元              | CKSEL3~0またはEXCKSEL3~0 |

|--------------------|-----------------------|

| 外部クリスタル低電力発振器      | 1111~1000             |

| (予約)               | 0111~0110             |

| 外部低周波数クリスタル発振器     | 0101~0100             |

| (予約)               | 0011                  |

| 校正付き内蔵RC発振器        | 0010                  |

| 外部クロック信号           | 0000                  |

| (予約)               | 0001                  |

| 注・1=非プログラム 0=プログラム |                       |

注:1=非プログラム、0=プログラム

#### 6.2.1. 既定のクロック元 (ATmega16U4とATmega32U4)

このデバイスはクリスタル用低電力発振器(8MHz~16MHz)が許可で、CKDIV8ヒュースがプログラム(0)され、結果として8MHzクリスタルで1.0M Hzのシステム クロックで出荷されます。既定クロック選択ヒュース、設定の概要については228頁の**表28-5**.をご覧ください。

#### 6.2.2. 既定のクロック元 (ATmega16U4RCとATmega32U4RC)

このデバイスは校正付き内蔵RC発振器(8MHz)が許可で、CKDIV8ヒュースがプログラム(0)され、結果として1.0MHzのシステム クロックで出荷 されます。既定クロック選択ヒュース。設定の概要については227頁の**表28-5**.をご覧ください。

#### 6.2.3. クロック起動手順

何れのクロック元も発振を開始するための充分なVCCと、それが安定であると考えられるのに先立つ、最低発振周期数が必要です。

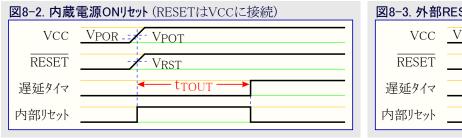

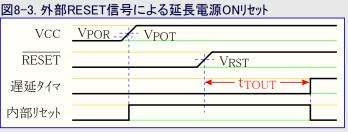

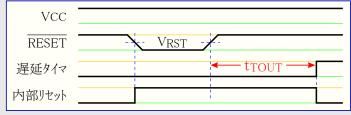

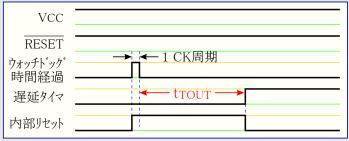

充分なVCCを保証するため、その他全てのリセット元によってデバイスリセットが開放された後、デバイスは起動遅延時間(trour)の内部リセットを発生します。30頁の「システム制御とリセット」はこの内部リセットに対する起動条件を記述します。この遅延(trour)はウォッチト、ッグ発振器で計時され、遅延周期数はSUTとCKSELのヒューズによって設定されます。選択可能な遅延右表で示されます。この表で示されるようにウォッチト、ッグ発振器の周波数は電圧に依存します。

| 表6-2.WDT発振器の代表計時完了値、周期数 |          |           |  |  |  |  |

|-------------------------|----------|-----------|--|--|--|--|

| VCC=3.0V                | VCC=5.0V | 周期数       |  |  |  |  |

| 0ms                     | 0ms      | 0         |  |  |  |  |

| 4.3ms                   | 4.1ms    | 512       |  |  |  |  |

| 69ms                    | 65ms     | 8K (8192) |  |  |  |  |

遅延の主な目的はAVRが最小VCCを印加されるまでAVRをリセットに保つことです。この遅延は実電圧を監視しませんので、VCC上昇時間より長い遅延を選ぶことが必要とされるべきです。これが不可能な場合、内部または外部の低電圧検出回路(BOD)が使われるべきです。BOD回路がリセットを開放する前に充分なVCCを保証するでしょうから、起動遅延時間は禁止され得ます。低電圧検出回路(BOD)なしでの起動遅延時間の禁止は推奨されません。

この発振器はクロックが安定と考えられるのに先立って最低クロック数を発振することを必要とされます。内部リプルカウンタは発振器の出力 クロックを監視し、与えられたクロック周期数に対して内部リセットを活性(有効)に保ちます。このリセットはその後に開放され、デバイスが実行 を開始します。推奨発振器起動時間はクロック種別に依存し、外部的に印加されたクロックに対する6周期から、低周波数クリスタルに対す る32K周期まで変化します。

クロックについての起動手順は計時完了遅延とデバイスがリセットから起動する時の起動時間の両方を含みます。パワータウンまたはパワー セーブから起動するとき、VCCは充分な電圧であると認識され、起動時間だけが含められます。

#### 6.3. クリスタル用低電力発振器

XTAL1とXTAL2は図6-2.で示されるようにチップ上の発振器としての使用に設定できる反転増幅器の各々、入力と出力です。クリスタル発振子またはセラミック振動子のどちらでも使えます。

この発振器はXTAL2出力上の電圧振幅を減少した低電力発振器です。これは最低消費電力を与えますが、他のクロック入力を駆動 する能力はありません。

C1とC2はクリスタル発振子とセラミック振動子の両方について常に等しくすべきです。このコンデンサの最適値は使うクリスタル発振子やセラミック 振動子、浮遊容量の量、その環境の電磁雑音に依存します。 クリスタル発振子使用に対するコンデンサ選択について初期の指針のいく つかは下表で与えられます。 セラミック振動子については製造業者によって与えられたコンデンサ値が使われるべきです。

低電力発振器は示された周波数範囲で各々最適化された3つの異なる種別で動作できます。この動作種別はこの表で示されるよう にCKSEL3~1ヒューズによって選ばれます。

- 注:周波数が仕様(VCC依存)超の場合、CKDIV8 =0が可能ですが、分周後クロックが仕様内であ ることを保証せねばなりません。

- 注1:本選択はクリスタル発振子ではなく、セラミック振動子でのみ使われるべきです。

CKSEL0ヒューズはSUT1,0ヒューズと共に、この表で示されるように起動時間を選びます。

#### 表6-4. クリスタル発振子/セラミック振動子用低電力発振器起動遅延時間選択表

| 20 1.777 | 64.7777777711777777777777777777777777777 |                             |                                    |                             |  |  |  |  |  |

|----------|------------------------------------------|-----------------------------|------------------------------------|-----------------------------|--|--|--|--|--|

| CKSEL0   | SUT1,0                                   | パワーダウン, パワーセーブ<br>からの起動遅延時間 | <u>リセットからの付加遅延</u><br>時間(VCC=5.0V) | 推奨使用法                       |  |  |  |  |  |

|          | 0 0                                      | 258×CK( <mark>注1</mark> )   | $14 \times \text{CK+4.1ms}$        | 外部セラミック振動子、高速上昇電源           |  |  |  |  |  |

| 0        | 01                                       | 258×CK( <mark>注1</mark> )   | $14 \times \text{CK+65ms}$         | 外部セラミック振動子、低速上昇電源           |  |  |  |  |  |

| 0        | 10                                       | 1K×CK ( <b>注2</b> )         | $14 \times CK$                     | 外部セラミック振動子、低電圧検出(BOD)リセット許可 |  |  |  |  |  |

|          | 11                                       | 1K×CK ( <b>注2</b> )         | $14 \times \text{CK+4.1ms}$        | 外部セラミック振動子、高速上昇電源           |  |  |  |  |  |

|          | 0 0                                      | 1K×CK ( <b>注2</b> )         | $14 \times \text{CK+65ms}$         | 外部セラミック振動子、低速上昇電源           |  |  |  |  |  |

| 1        | 01                                       | 16K×CK                      | $14 \times CK$                     | 外部クリスタル発振子、低電圧検出(BOD)リセット許可 |  |  |  |  |  |

| 1        | 10                                       | 16K×CK                      | $14 \times \text{CK+4.1ms}$        | 外部クリスタル発振子、高速上昇電源           |  |  |  |  |  |

|          | 11                                       | 16K×CK                      | $14 \times \text{CK+65ms}$         | 外部クリスタル発振子、低速上昇電源           |  |  |  |  |  |

**注1**: これらの選択はデバイスの最高周波数付近での動作でないとき、応用にとって起動での周波数安定性が重要でない場合だけ使われるべきです。これらの選択はクリスタル発振子用ではありません。

**注2**: これらの選択はセラミック振動子での使用を意図され、起動での周波数安定性を保証します。デバイスの最高周波数付近での動作でないとき、応用にとって起動での周波数安定性が重要でない場合はクリスタル発振子も使えます。

#### 6.4. 低周波数クリスタル用発振器

このデバイスは専用の低周波数発振器によってクロック元として時計用32.768kHzクリスタルを使えます。クリスタル発振子は図6-2.で示される ように接続されるべきです。この発振器が選ばれると、起動時間は下表で示されるようにSUTヒューズとCKSEL0ヒューズによって決定され ます。

| CKSEL0  | SUT1,0 | パワーダウン, パワーセーブ<br>からの起動遅延時間        | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法            |  |  |  |  |

|---------|--------|------------------------------------|------------------------------|------------------|--|--|--|--|

|         | 0 0    | 1K×CK ( <b>注1</b> )                | $14 \times CK$               | 低電圧検出(BOD)リセット許可 |  |  |  |  |

| 0       | 01     | 1K×CK ( <b>注1</b> )                | $14 \times \text{CK+4.1ms}$  | 高速上昇電源           |  |  |  |  |

| 0       | 10     | 1K×CK ( <b>注1</b> )                | $14 \times \text{CK+65ms}$   | 低速上昇電源           |  |  |  |  |

|         | 11     |                                    |                              | (予約)             |  |  |  |  |

|         | 0 0    | $32K \times CK$                    | $14 \times CK$               | 低電圧検出(BOD)リセット許可 |  |  |  |  |

| 1       | 01     | $32\mathrm{K}\!	imes\!\mathrm{CK}$ | $14 \times \text{CK+4.1ms}$  | 高速上昇電源           |  |  |  |  |

| 1       | 10     | 32K×CK                             | $14 \times \text{CK+65ms}$   | 低速上昇電源           |  |  |  |  |

| 11 (予約) |        |                                    |                              |                  |  |  |  |  |

注1: これらの選択は応用にとって起動での周波数安定性が重要でない場合だけ使われるべきです。

### 6.5. 校正付き内蔵RC発振器

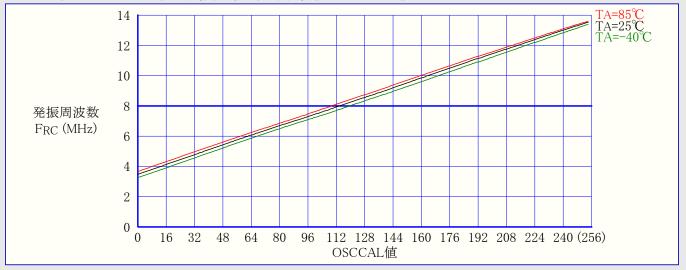

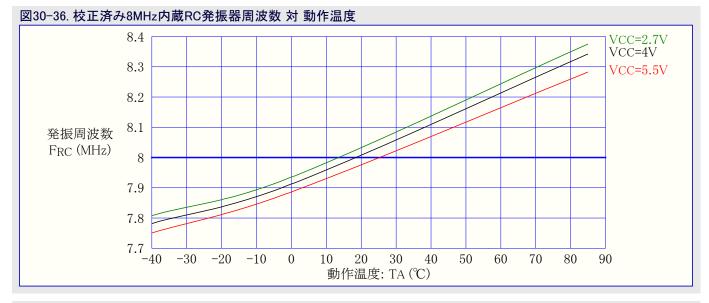

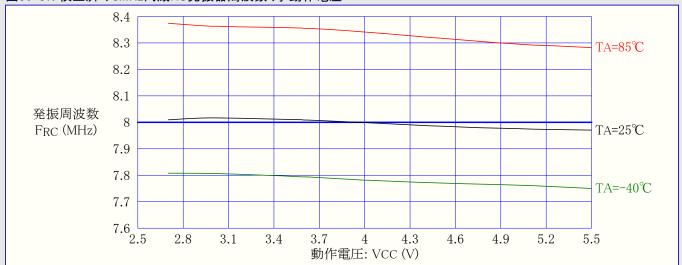

既定による校正された内蔵RC発振器は8.0MHzのクロックを供給します。この周波数は3V/25℃での公称値です。デバイスはCKDIV8 ヒューズがプログラム(0)で出荷されます。より多くの詳細については22頁の「システム クロック前置分周器」をご覧ください。このクロックは下表で 示されるようにCKSELヒューズのプログラミングによってシステム クロックとして選べます。選ばれたなら、外部部品なしで動作します。リセット中、 ハートウェアが発振校正(OSCCAL)レシ、スタに予めプログラムされた校正値バイトを設定し、これによってRC発振器を自動的に校正します。 3V/25℃で、この校正は8MHz±1%の周波数を与えます。この発振器は発振校正(OSCCAL)レシ、スタの変更により、1%の精度内で7.3 ~8.1MHz範囲のどの周波数にも校正することができます。この発振器がチップ(システム)クロックとして使われる時にウォッチト、ッグ発振器は未 だウォッチトッグ タイマとリセット付加遅延タイマに使われます。予め設定された校正値のより多くの情報については228頁の「校正バイト」項を ご覧ください。

#### 表6-6. 校正付き内蔵RC発振器動作種別 CKSEL3~0 周波数範囲 (MHz) 0010 7.3~8.1

注: この8MHz周波数がデバイス仕様(VCCに依存)を越える場合、内部周波数を8分 周するためにCKDIV8ヒューズをプログラム(0)にできます。

この発振器が選ばれると、起動時間は下表で示されるようにSUTヒューズによって決定されます。

#### 表6-7. 校正付き内蔵RC発振器用起動遅延時間選択表

| SUT1,0 | パワーダウン, パワーセーブ<br>からの起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=5.0V) |                  |  |  |  |  |

|--------|-----------------------------|------------------------------|------------------|--|--|--|--|

| 0 0    | 6×CK                        | $14 \times CK$               | 低電圧検出リセット(BOD)許可 |  |  |  |  |

| 0 1    | 6×CK                        | $14 \times \text{CK+4.1ms}$  | 高速上昇電源           |  |  |  |  |

| 10     | 6×CK                        | $14 \times \text{CK+65ms}$   | 低速上昇電源           |  |  |  |  |

| 11     | (予約)                        |                              |                  |  |  |  |  |

6.5.1. OSCCAL - 発振校正レジスタ (Oscillator Calibration Register)

| ビット        | 7    | 6    | 5    | 4      | 3     | 2    | 1    | 0    |        |

|------------|------|------|------|--------|-------|------|------|------|--------|

| (\$66)     | CAL7 | CAL6 | CAL5 | CAL4   | CAL3  | CAL2 | CAL1 | CAL0 | OSCCAL |

| Read/Write | R/W  | R/W  | R/W  | R/W    | R/W   | R/W  | R/W  | R/W  |        |

| 初期値        |      |      |      | デバイス固て | 有の校正値 |      |      |      |        |

#### ● ビット7~0 - CAL7~0:発振校正値 (Oscillator Calibration Value)

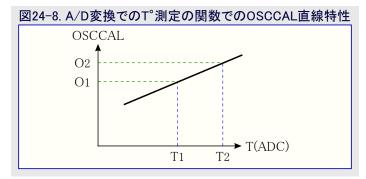

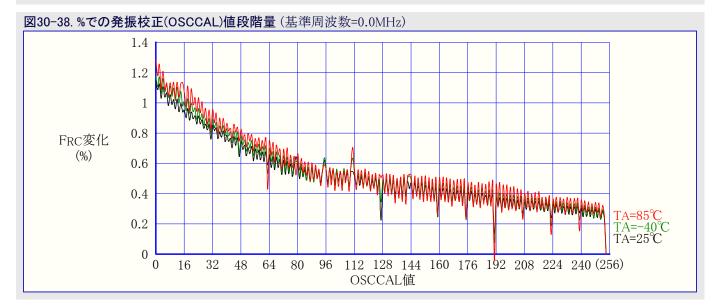

発振校正レジスタは発振器周波数の偏差処理を省くための内蔵発振器の調整に使われます。チップのリセット中に、25℃で8MHzの発振 器周波数を与える工場校正値がこのレジスタへ自動的に書かれます。応用ソフトウェアは発振器周波数を変更するために、このレジスタに 書くことができます。校正範囲は±40%で直線(校正段階:~0.4%)です。25℃での代表的な製造工程で、符号(値)は8MHzに対して 127であるべきで、入力値\$00は最低、\$FFは最高の周波数を与えます。

温度感度は殆ど直線ですが、前述のように製造工程に依存します。この傾斜を決めるため、周波数は2つの温度で測定されなけれ ばなりません。本デバイスの温度感知器が上記の操作を可能にし、これは199頁の「温度感知器校正」で詳述されます。この後に測定 した温度の関数で発振器周波数を校正することが可能です。

この発振器はフラッシュ メモリとEEPROMの書き込みアクセス時間に使われ、これらの書き込み時間はそれに応じて影響されることに注意してください。フラッシュ メモリまたはEEPROMが書かれる場合、8.8MHzより高く校正してはいけません。そうでなければ、フラッシュ メモリまたはEEPROMの書き込みは失敗するかもしれません。

| 6.5.2. RCCTRL - | ・発振器制御レジスタ | (Oscillator | Control Register) |

|-----------------|------------|-------------|-------------------|

|-----------------|------------|-------------|-------------------|

| ビット        | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |        |

|------------|---|---|---|---|---|---|---|--------|--------|

| (\$67)     | - | - | - | - | - | - | - | RCFREQ | RCCTRL |

| Read/Write | R | R | R | R | R | R | R | R/W    |        |

| 初期値        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0      |        |

ビット7~1 - Res : 予約 (Reserved)

これらのビットを設定(1)してはいけません。これらのビットは常に0として読みます。

#### ● ビット0 - RCFREQ : RC発振器周波数選択 (RC Oscillator Frequency Select)

このビットが解除(0:既定値)されると、RC発振器出力周波数は8MHzに設定されます。このビットが設定(1)されると、RC発振器出力周波 数は1MHzです。発振校正(OSCCAL)レジスタが8MHzと1MHzの両方の出力動作で同じ効果(~0.4%/段階)を持つことに注意してくだ さい。

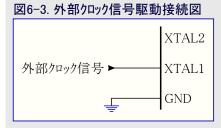

#### 6.6. 外部クロック信号

外部クロック元からデバイスを駆動するには、XTAL1が図6-3.で示されるように駆動されるべき です。外部クロックでデバイスを走行するためには、表6-1.で示されるようにCKSELヒュースが '0000'にプログラム(設定)されなければなりません。

このクロック元が選ばれると、起動時間は下表で示されるようにSUTヒュースによって決定されます。

#### 表6-8. 外部クロック信号駆動用起動遅延時間選択表

| SUT1,0 | パワーダウン, パワーセーブ<br>からの起動遅延時間 | <u>リセットからの付加遅延</u><br>時間 (VCC=5.0V) | 推奨使用法            |  |  |  |  |

|--------|-----------------------------|-------------------------------------|------------------|--|--|--|--|

| 0 0    | 6×CK                        | $14 \times CK$                      | 低電圧検出(BOD)リセット許可 |  |  |  |  |

| 01     | 6×CK                        | $14 \times \text{CK+4.1ms}$         | 高速上昇電源           |  |  |  |  |

| 10     | 6×CK                        | $14 \times \text{CK+65ms}$          | 低速上昇電源           |  |  |  |  |

| 11     | (予約)                        |                                     |                  |  |  |  |  |

外部クロックを供給するとき、MCUの安定な動作を保証するために供給したクロック周波数の急な変化を避けることが必要とされます。或 るクロック周期から次への2%より大きな周波数変化は予測されない事態を引き起こします。このようなクロック周波数での変化中、MCUは リセットに保たれるのを保証することが必要とされます。

システム クロック前置分周器が安定な動作を保証しながら、内部クロック周波数の実行時変更の実現に使えることに注意してください。詳細については22頁の「システム クロック前置分周器」を参照してください。

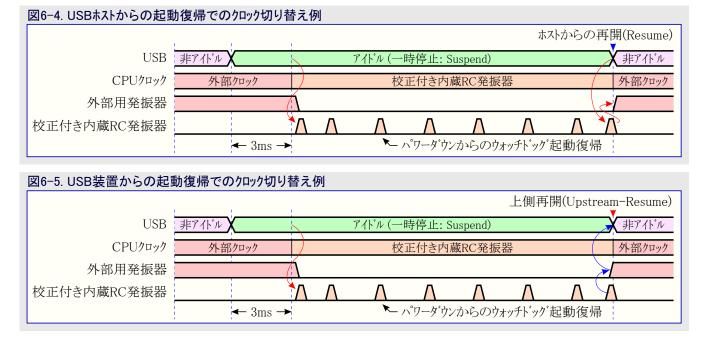

#### 6.7. クロック切り替え

本デバイスはより正確に応用電力と実行時間を制御するために、ソフトウェアによって或るクロック元から別の1つに切り換えることを使用者 に許す、クロック切り換え制御器を含みます。

#### 6.7.1. 使用例

この変更はデバイスがUSB休止(サスペント)動作へ移行する時に必要とされるかもしれません。そして(電力)消費と起動遅延を減らすために外部/ロックから校正付き内蔵RC発振器へ切り替えます。このような構成設定では外部/ロックが禁止されます。その後にファームウェアは応用での事象があるかを検査するために、パワーダウンから起動復帰するのにウォッチトックゲタイマを使えます。応用での事象発生またはUSB信号線での非アイドル状態をUSB制御器が示す(例えば再開(Resume))場合、ファームウェアはUSB操作を再開するために、/ロック多重器を校正付き内蔵RC発振器から外部/ロックへ切り替えます。

この機能は校正付き8MHz内蔵RC発振器、外部クロック信号、クリスタル用低電力発振器間の切り換えだけに使えます。低周波数クリスタル 用発振器はこの機能で使われてはなりません。

**Atmel**

#### 6.8. クロック出力緩衝部 (外部クロック出力)

このデバイスはシステム クロックをCLKOピンに出力できます。この出力を許可するには、CKOUTヒュースがプログラム(0)されなければなりません。この動作はチップのクロックがシステム上の他の回路を駆動する時用です。このヒュースがプログラム(0)されると、I/Oピンの標準動作は無視され、このクロックはリセット中も出力されます。CLKOがクロック出力を扱うとき、校正付き内蔵RC発振器を含む何れのクロック元も選べます。システム クロック前置分周器が使われる場合、出力は分周したシステム クロックです。

#### 6.9. システム クロック前置分周器

このデバイスはシステムクロック前置分周器を持ち、システムクロックはクロック前置分周レジスタ(CLKPR)の設定によって分周できます。この特徴 (機能)は必要とされる処理能力が低い時の消費電力削減に使えます。これは全クロック種別で使え、CPUと全同期周辺機能のクロック周 波数に影響を及ぼします。clk<sub>CPU</sub>,clk<sub>FLASH</sub>,clk<sub>I/O</sub>,clk<sub>ADC</sub>は<mark>表6-9</mark>.で示された値によって分周されます。

前置分周器設定間を切り替えるとき、システム クロック前置分周器は中間(経過途中)の周波数が直前の設定に対応するクロック周波数または新規設定に対応するクロック周波数のどちらよりも高くなく、クロック系で不具合が起きないことを保証します。

前置分周器として実行するリプル カウンタは分周されないクロック周波数で走行し、CPUのクロック周波数より速いかもしれません。従って例 え(カウンタ値が)読めるとしても、前置分周器の状態を決めることはできず、1から他へのクロック分周値切り替えを行う正確な時間は必ず しも予測できません。CLKPS値が書かれる時から新規クロック周波数が活性(有効)になる前にT1+T2~T1+2×T2間かかります。この間 で2つの有効なクロック端が生成されます。ここでのT1は直前のクロック周期、T2は新規前置分周器設定に対応する周期です。

予期せぬクロック周波数の変更を防ぐため、CLKPSビットの変更は次の特別な書き込み手順に従わなければなりません。

1. クロック分周値変更許可(CLKPCE)ビットに1、CLKPR内の他の全ビットに0を書きます。

2. (次からの)4周期以内にCLKPCEビットを0とする欲したCLKPS値を書きます。

前置分周器設定変更時、書き込み手続きが割り込まれないことを保証するため、割り込みは禁止されなければなりません。

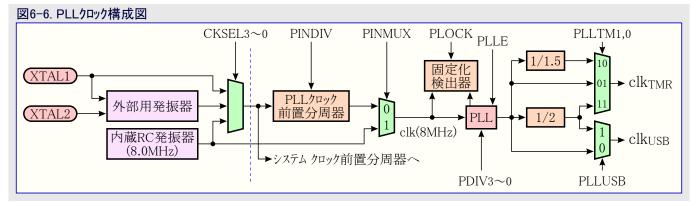

#### 6.10. PLL

このPLLはUSBインターフェースと高速タイマ単位部用の(96MHzまでの)内部高周波数クロックを生成するのに使われ、PLL入力は外部低周 波数クロック(XTAL1ビンからの外部クロック入力ビンまたはクリスタル発振器)から供給されます。

#### 6.10.1. 内部PLL

このデバイスの内部PLLは公称8MHz入力から40MHzと96MHz間のクロック周波数を生成します。

8MHzのPLL入力クロック元は、クロック元多重器出力から8MHzを生成する内部PLLクロック前置分周器の出力です(PLLインターフェースについては「PLLOSR - PLL制御/状態レジスタ」をご覧ください)。

PLL出力信号はUSBと高速タイマ単位部へ配給される前にPLL後置分周器段に入ります。これらの単位部の各々は独立した分周比を 選ぶことができます。

#### 6.11. クロック切り替え方法

#### 6.11.1. 外部クロックから校正付き内蔵RC発振器への切り替え

| <pre>if (Usb_supend_detected()) (</pre> | // if (UDINT.SUSPI==1)                |

|-----------------------------------------|---------------------------------------|

| Usb_ack_suspend();                      | // UDINT.SUPI=0;                      |

| Usb_freeze_clock();                     | // USBCON. FRZCLK=1;                  |

| <pre>Disable_pll();</pre>               | // PLLCSR. PLLE=0;                    |

| Enable_RC_clock();                      | // CLKSELO.RCE=1;                     |

| <pre>while (!RC_clock_ready());</pre>   | <pre>// while (CLKSTA.RCON!=1);</pre> |

| <pre>Select_RC_clock();</pre>           | // CLKSELO.CLKS=0;                    |

| <pre>Disable_external_clock();</pre>    | // CLKSELO.EXTE=0;                    |

| )                                       |                                       |

### **Atmel**

#### 6.11.2. 校正付き内蔵RC発振器から外部クロックへの切り替え

| <pre>if (Usb_wake_up_detected()) (</pre>    | // if (UDINT.WAKEUPI==1)               |

|---------------------------------------------|----------------------------------------|

| Usb_ack_wake_up();                          | // UDINT.WAKEUPI=0;                    |

| Enable_external_clock();                    | // CLKSELO. EXTE=1;                    |

| <pre>while (!External_clock_ready());</pre> | <pre>// while (CLKSTA.EXTON!=1);</pre> |

| <pre>Select_External_clock();</pre>         | // CLKSELO.CLKS=1;                     |

| Enable_pl1();                               | // PLLCSR. PLLE=1;                     |

| <pre>Disable_RC_clock();</pre>              | // CLKSELO.RCE=0;                      |

| <pre>while (!Pll_ready());</pre>            | <pre>// while (PLLCSR.PLOCK!=1);</pre> |

| Usb_unfreeze_clock();                       | // USBCON. FRZCLK=0;                   |

| )                                           |                                        |

#### 6.12. クロック関係用レジスタ

6.12.1. CLKSEL0 - クロック選択レジスタ0 (Clock selection Register 0)

| ビット        | 7      | 6      | 5      | 4      | 3    | 2    | 1 | 0    |         |

|------------|--------|--------|--------|--------|------|------|---|------|---------|

| (\$C5)     | RCSUT1 | RCSUT0 | EXSUT1 | EXSUT0 | RCE  | EXTE | - | CLKS | CLKSEL0 |

| Read/Write | R/W    | R/W    | R/W    | R/W    | R/W  | R/W  | R | R/W  |         |

| 初期値        | 0      | 0      | 0      | 0      | 内容参照 | 内容参照 | 0 | 内容参照 |         |

#### ● ビット7,6 - RCSUT1,0: 校正付き内蔵RC発振器用SUT値 (SUT for RC oscillator)

これら2ビットは校正付き内蔵RC発振器用SUT値です。ヒュース、ビットによってRC発振器が選ばれている場合、そのSUTヒュースがこれらのビット内に複写されます。この付加起動時間はリセット後だけ使われ、クロック切り替え後に使われないため、ファームウェアでの変更は無効です。

● ビット5,4 - EXSUT1,0:外部クロック信号/クリスタル用低電力発振器用SUT値(SUT for External Clock/Low Power Crystal Oscillator) これら2ビットは外部クロック信号/クリスタル用低電力発振器用SUT値です。ヒュース、ビットによって外部クロック信号/クリスタル用低電力発振器が 選ばれている場合、そのSUTヒュースがこれらのビット内に複写されます。ファームウェアは新しい値を書くことによって、これらのビットを変更 できます。この値は外部クロック信号/クリスタル用低電力発振器の次の開始で使われます。

#### ● ビット3 - RCE : 校正付き内蔵RC発振器許可 (Enable RC Oscillator)

校正付き内蔵RC発振器を許可するにはRCEビットが論理1を書かれなければなりません。校正付き内蔵RC発振器を禁止するには RCEビットが論理0を書かれなければなりません。

#### ● ビット2 - EXTE : 外部クロック信号 / クリスタル用低電力発振器許可 (Enable External Clock/Low Power Crystal Oscillator)

外部クロック信号/クリスタル用低電力発振器を許可するにはEXTEビットが論理1を書かれなければなりません。外部クロック信号/クリスタル用 低電力発振器を禁止するにはEXTEビットが論理0を書かれなければなりません。

#### • ビット0 - CLKS : クロック選択 (Clock Selector)

CPUクロックとして外部クロック信号/クリスタル用低電力発振器を選ぶにはCLKSビットが論理1を書かれなければなりません。CPUクロックとして校正付き内蔵RC発振器を選ぶにはCLKSビットが論理0を書かれなければなりません。リセット後、ヒュース、ビット設定によって外部クロック 信号/クリスタル用低電力発振器が選ばれているなら、CLKSビットがハートウェアによって設定(1)されます。 ファームウェアは選択に先立ってクロックが正しく開始されているかを調べなければなりません。

ファームリェノ は選択に亢立つ (クロツクノハ正し、)用炉され (いつかを調^/なりれはなりま

#### 6.12.2. CLKSEL1 - クロック選択レジスタ1 (Clock selection Register 1)

| ビット        | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |         |

|------------|----------|----------|----------|----------|----------|----------|----------|----------|---------|

| (\$C6)     | RCCKSEL3 | RCCKSEL2 | RCCKSEL1 | RCCKSEL0 | EXCKSEL3 | EXCKSEL2 | EXCKSEL1 | EXCKSEL0 | CLKSEL1 |

| Read/Write | R/W      |         |

| 初期値        | 0        | 0        | 1        | 0        | 0        | 0        | 0        | 0        |         |

#### ● ビット7~4 - RCCKSEL3~0: 校正付き内蔵RC発振器用CKSEL値 (CKSEL for RC oscillator)

校正付き内蔵RC発振器用クロック設定。リセット後、本レジスタ内のこの部分は校正付き内蔵RC発振器に対応する値'0010'が格納されま す。校正付き内蔵RC発振器への切り替え前のファームウェアによるこの値の変更は、校正付き内蔵RC発振器が開始しなくなるため禁止 されます。

● ビット3~0 - EXCKSEL3~0:外部クロック信号/クリスタル用低電力発振器用CKSEL値(CKSEL for External Clock/Low Power Crystal Oscillator) 外部クロック信号/クリスタル用低電力発振器用クロック設定。リセット後、ヒュース、ビットによって外部クロック信号/クリスタル用低電力発振器が選ば れているなら、本レジスタ内のこの部分はそのヒュース、設定が格納されます。ファームウェアはクロック切り替え後、起動時間を変更するために これを修正できます。

EXCKSEL3~0構成設定については18頁の表6-1. クロック元選択をご覧ください。校正付き内蔵RC発振器、クリスタル用低電力発振器、 外部クロック信号だけが許されます。

#### 6.12.3. CLKSTA - クロック状態レジスタ (Clock Status Register)

| ビット        | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0     |        |

|------------|---|---|---|---|---|---|------|-------|--------|

| (\$C7)     | - | - | _ | _ | - | _ | RCON | EXTON | CLKSTA |

| Read/Write | R | R | R | R | R | R | R    | R     |        |

| 初期値        | 0 | 0 | 0 | 0 | 0 | 0 | 内容参照 | 内容参照  |        |

ビット7~2 - Res:予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

#### ● ビット1 - RCON:校正付き内蔵RC発振器ON (RC Oscillator On)

校正付き内蔵RC発振器が走行中なら、本ビットはハートウェアによって設定(1)されます。校正付き内蔵RC発振器が停止なら、本ビットは ハードウェアによって解除(0)されます。

• ビット0 - EXTON : 外部クロック信号/クリスタル用低電力発振器ON (External Clock/Low Power Crystal Oscillator On)

外部クロック信号/クリスタル用低電力発振器が走行中なら、本ビットはハート・ウェアによって設定(1)されます。外部クロック信号/クリスタル用低電力発振器が停止なら、本ビットはハート・ウェアによって解除(0)されます。

#### 6.12.4. CLKPR - クロック前置分周レジスタ (Clock Prescale Register)

| ヒット        | 7      | 6 | 5 | 4 | 3      | 2      | 1      | 0      |       |

|------------|--------|---|---|---|--------|--------|--------|--------|-------|

| (\$61)     | CLKPCE | — | - | - | CLKPS3 | CLKPS2 | CLKPS1 | CLKPS0 | CLKPR |

| Read/Write | R/W    | R | R | R | R/W    | R/W    | R/W    | R/W    |       |

| 初期値        | 0      | 0 | 0 | 0 | 内容参照   | 内容参照   | 内容参照   | 内容参照   |       |

#### ● ビット7 - CLKPCE : クロック分周値変更許可 (Clock Prescaler Change Enable)

CLKPSビットの変更を許可するためにCLKPCEビットは論理1を書かれなければなりません。CLKPCEビットは同時にCLKPRの他の全 ビットが0を書かれる時だけ更新されます。CLKPCEは書き込み後4クロック周期またはCLKPSビット書き込み時、ハードウェアによって解除(0) されます。この制限時間(4クロック周期)内のCLKPCEビット再書き込みは制限時間の延長もCLKPCEビットの解除(0)も行いません。

#### ● ビット3~0 - CLKPS3~0: クロック分周値選択 (Clock Prescaler Select Bits 3~0)

これらのビットは選択したクロック元と内部システムクロック間の分周値を定義します。これらのビットは応用の必要条件に合わせた各種クロック 周波数を実行時に書けます。分周値が使われると、分周器はMCUへの主クロックを分周し、全ての同期周辺機能の速度が減じられま す。分周値は下表で与えられます。

CKDIV8ヒューズがCLKPSビットの初期値を決めます。CKDIV8が非プログラム(1)にされると、CLKPSビットは、0000、にリセットされます。CKDI V8がプログラム(0)されると、CLKPSビットは起動時に8分周を与える、0011、ビリセットされます。現在の動作条件でデバイスの最高周波数より高い周波数のクロック元を選択した場合、この機能が使われるべきです。CKDIV8ヒューズ、設定に拘らず、どの値もCLKPSビットへ書けることに注意してください。応用ソフトウェアは現在の動作条件でデバイスの最高周波数より高い周波数のクロック元を選択した場合、充分な分周値が選択されることを保証しなければなりません。このデバイスはCKDIV8ヒューズがプログラム(0)で出荷されます。

#### 表6-9. クロック前置分周器選択

| 10 J. 74778 |    | 70,00 % | 21/1    |   |   |    |    |    |     |       |               |  |   |  |   |  |  |

|-------------|----|---------|---------|---|---|----|----|----|-----|-------|---------------|--|---|--|---|--|--|

| CLKPS       | }  |         |         |   | ( | )  |    |    |     | 1     |               |  |   |  |   |  |  |

| CLKPS2      | 2  |         | 0 1 0 1 |   |   |    |    |    |     |       |               |  |   |  |   |  |  |

| CLKPS1      |    | (       | 0 1     |   |   | (  | C  |    | 1   | 0 1 0 |               |  | ) |  | 1 |  |  |

| CLKPSC      | )  | 0       | 1       | 0 | 1 | 0  | 1  | 0  | 1   | 0     | 1 0 1 0 1 0 1 |  |   |  | 1 |  |  |

| 分周値(数       | 女) | 1       | 2       | 4 | 8 | 16 | 32 | 64 | 128 | 256   | (予約)          |  |   |  |   |  |  |

6.12.5. PLLCSR - PLL制御/状態レジスタ(PLL Control and Status Register)

| ビット         | 7 | 6 | 5 | 4      | 3 | 2 | 1    | 0     |        |

|-------------|---|---|---|--------|---|---|------|-------|--------|

| \$29 (\$49) | — | - | - | PINDIV | - | - | PLLE | PLOCK | PLLCSR |

| Read/Write  | R | R | R | R/W    | R | R | R/W  | R     |        |

| 初期値         | 0 | 0 | 0 | 0      | 0 | 0 | 0    | 0     |        |