# ATmega48P/PV, ATmega88P/PV, ATmega168P/PV

完全 データシート

# 序説

Atmel® picoPower® ATmega48P/PV/88P/PV/168P/PVはAVR®強化RISC構造に基づく低電力CMOS 8ビット マイクロコントローラです。単一クロック周期での強力な命令の実行により、ATmega48P/PV/88P/PV/168P/PVはMHz当たり1 MIPS近くの単位処理量を達成します。これは消費電力対処理速度に対するデバイスの最適化をシステム設計者に許します。

本書は一般の方々の便宜のため有志により作成されたもので、Atmel社とは無関係であることを御承知ください。しおりの[はじめに]での内容にご注意ください。

## 特徴

- 高性能、低消費Atmel® AVR® 8ビット マイクロ コントローラ

- 進化したRISC構造

- 強力な129/131命令(多くは1周期実行)

- 32個の1バイト長汎用レジスタ

- 完全なスタティック動作

- 20MHz時、20MIPSに達する高速動作

- 2周期乗算命令

- 高耐久不揮発性メモリ部

- 実装自己書き換え可能な4K/8K/16Kバイト(2K/4K/8K語)フラッシュ メモリ内蔵

- 256/512/512パイトのEEPROM

- 512/1K/1Kバイトの内蔵SRAM

- 書き換え回数: 10,000/フラッシュ, 100,000/EEPROM

- データ保持力: 20年/85℃, 100年/25℃

- 個別施錠ビットを持つ任意のブート コード領域

- チップウンートプログラムによる実装書き換え

- 真の書き込み中の読み出し動作

- ソフトウェア保護用の設定可能な施錠機能

- Atmel® QTouch®ライフラリ支援

- 容量性接触の釦、滑動部、輪

- QTouchとQMatrix®の採取

- 64までの感知チャネル

- 内蔵周辺機能

- 独立した前置分周器と比較機能付き2つの8ビットタイマ/カウンタ

- 独立した前置分周器、比較、捕獲機能付き1つの16ビットタイマ/カウンタ

- 専用発振器と8ビット タイマ/カウンタによる実時間計数器(RTC)

- 6つのPWM出力

- 6チャネル(PDIP,QFN/MLF28), 8チャネル(TQFP,QFN/MLF32)の10ビットA/D変換器

- 温度測定

- 設定可能な直列USART

- 主装置/従装置動作SPI直列インターフェース

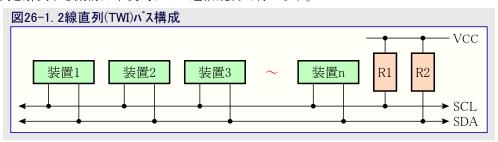

- バイト対応2線直列インターフェース(Philips I2C互換)

- 設定可能な専用発振器付きウォッチドッグ、タイマ

- アナログ比較器

- ピン変化での割り込みと起動復帰

- 特殊マイクロ コントローラ機能

- 電源ONリセット回路と設定可能な低電圧検出器(BOD)

- 校正可能な内蔵RC発振器

- 外部及び内部の割り込み

- アイト・ル、A/D変換雑音低減、パワーセーブ、パワーダウン、スタンバイ、拡張スタンバイの6つの低消費動作

- I/Oと外囲器

- 23ビットの設定可能なI/O

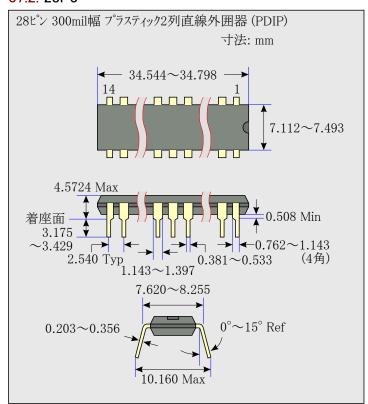

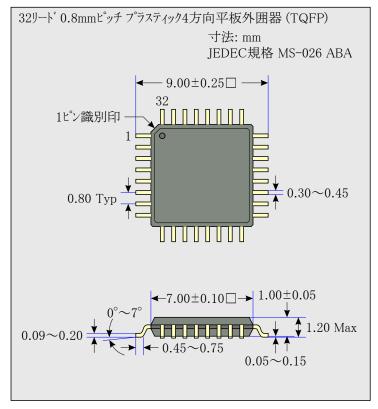

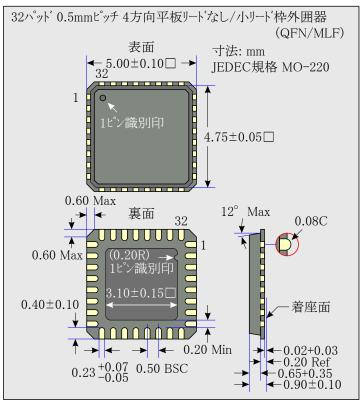

- 28ピンPDIP、28パット。QFN/MLF、32リート、TQFP、32パット。QFN/MLF

- 動作温度

- --40∼85°C

- 動作電圧

- $-2.7 \sim 5.5 \text{V} \text{ (ATmega48P/88P/168P)}$

- -1.8~5.5V (ATmega48PV/88PV/168PV)

- 動作谏度

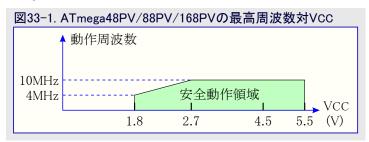

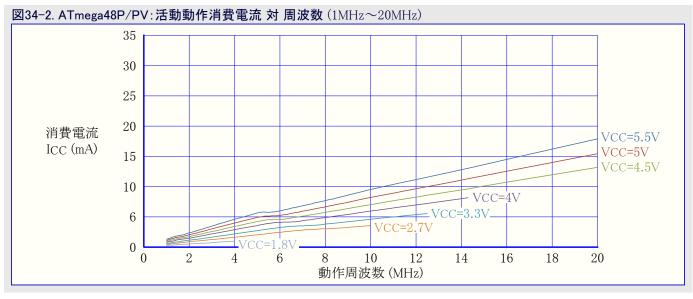

- ATmega48P/88P/168P :  $0\sim10$ MHz/2.7 $\sim5.5$ V,  $0\sim20$ MHz/4.5 $\sim5.5$ V

- ATmega48PV/88PV/168PV:  $0\sim4$ MHz/1.8 $\sim5.5$ V,  $0\sim10$ MHz/2.7 $\sim5.5$ V

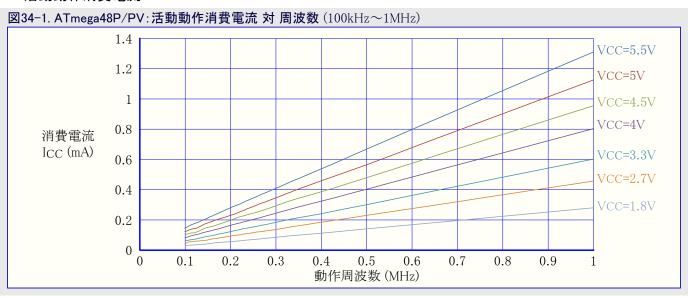

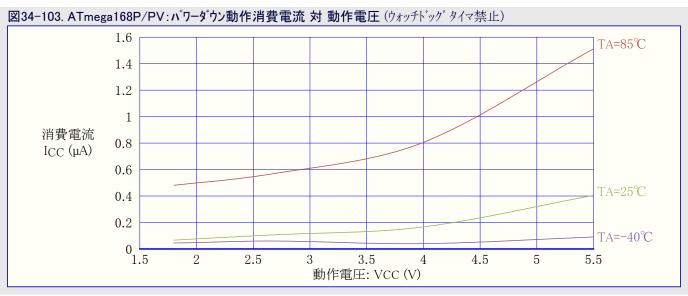

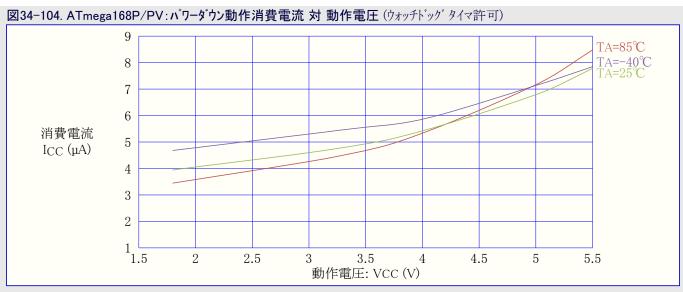

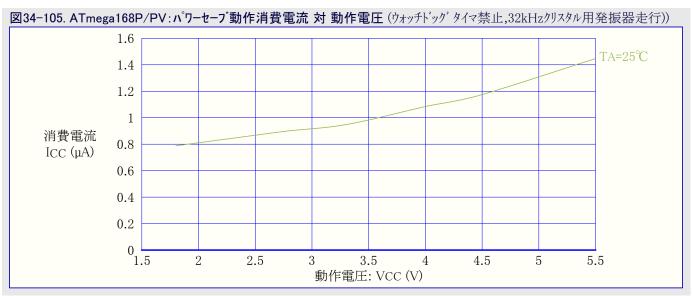

- 代表消費電力 (1MHz,1.8V,25℃)

- 0.3mA (活動動作)

- 0.1µA (パワータウン動作)

- 0.8μA (パワーセーフ`動作,32kHz RTCを含む)

# 目次

|     | 序説                                                            | 15  | SCRST -              | - システム制御とリセット・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                   | 40   |

|-----|---------------------------------------------------------------|-----|----------------------|-------------------------------------------------------------------------------------|------|

|     | 特徴 ····································                       |     | 15.1 AV              | Rのリセット・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                          | • 40 |

| 1   | 概要                                                            |     |                      | ·····································                                               |      |

| 1.  | 製品形態要約・・・・・・・・・・・・・・・・・6                                      |     |                      | 源ONJセット・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                         |      |

| 2.  |                                                               |     |                      | 30                                                                                  |      |

| 3.  |                                                               |     |                      | 電圧検出(BOD)リセット・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                   |      |

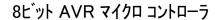

| 4.  | 構成図 ••••• 8                                                   |     |                      | ツチトック゛システム リセット ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                |      |

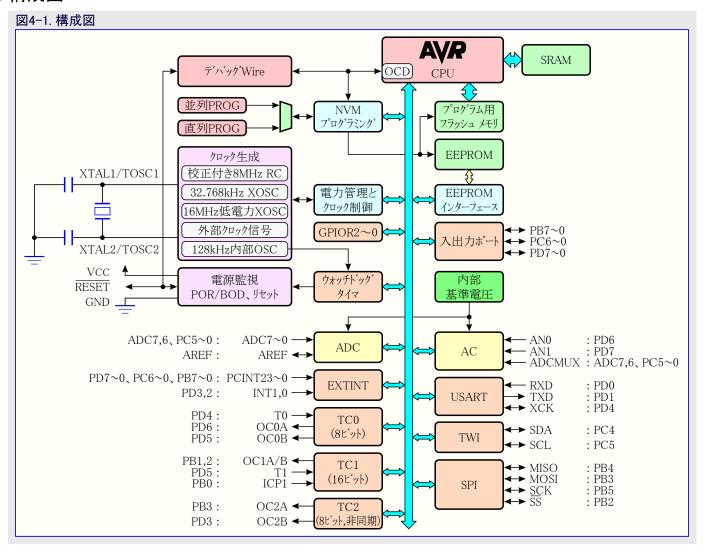

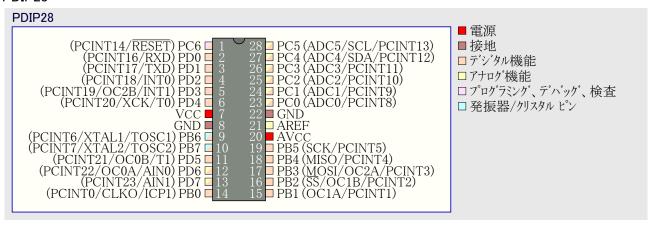

| 5.  | <b>ピン配置 ・・・・・・・・</b> 9                                        |     |                      | ッ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                               |      |

| ٥.  | 5.1. ピン接続図 ······· 9                                          |     |                      | ッチト゛ック゛ タイマ ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                     |      |

|     | <b>5.2.</b> ピン説明・・・・・・・・・・・・・11                               |     |                      | ァトリング・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ット関係レジスタ ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |      |

| 6   | 入出力多重化 ・・・・・・・・・ 12                                           | 16  |                      | り込み                                                                                 |      |

| _   |                                                               | 10. | 161 宇川               | り込みベクタ ・・・・・・・・・・・・・・・・・・・・・・・・                                                     | - 46 |

| 7.  |                                                               |     | 16.1. 割り             | り込みへ、クタ<br>り込みへ、クタ移動関係レジスタ・・・・・・・・・・・・・・                                            | - 40 |

| 8.  | <del>データ保持力・・・・・・・・・・・・・・・13</del>                            | 47  | 10.Z. 剖 <sup>5</sup> | クストンのい クタ/核助医派レン ヘタ ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                             | - 51 |

| 9.  | コート 例について · · · · · · · · · · · · · · · · · · ·               | 17. | EXTINI .             | - 外部割り込み ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                       | 52   |

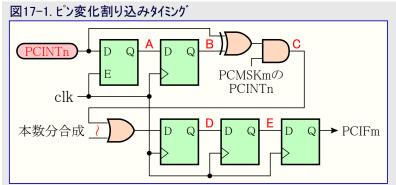

|     | 容量性接触感知 •••••• 13                                             |     | 17.1. ヒン             | 変化割り込みタイミング・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                     | • 52 |

| 10. | 10.1. QTouchライブラリ · · · · · 13                                |     |                      | 部割り込み用レジスタ ・・・・・・・・・・・・・・・・・・・・・・・・                                                 |      |

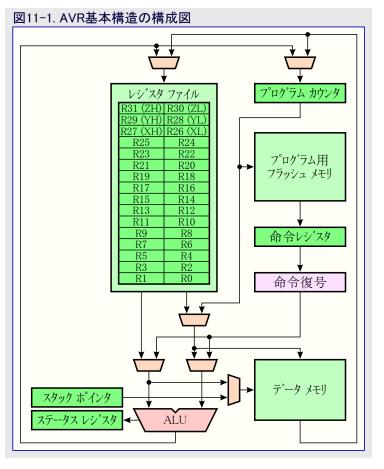

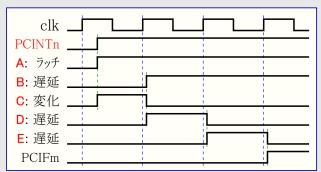

| 11  | AVR CPU 37 · · · · · · · · · · · · · · · · · ·                | 18. |                      | °                                                                                   |      |

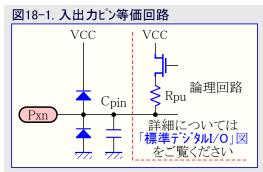

| 11. | 11.1. 概要 ···································                  |     |                      | 要                                                                                   |      |

|     | 11.1. 做妄 14<br>11.2. ALU (Arithmetic Logic Unit)              |     | 18.2. 標準             | 準デジタル入出力としてのポート ・・・・・・・・・                                                           | • 56 |

|     | 11.2. ALU (Arithmetic Logic Unit) 14                          |     | 18.3. 交              | 奥ポート機能 ・・・・・・・・・・・・・・・・・・・・・・・                                                      | • 59 |

|     | 11.3. ステータス レジスタ ・・・・・・・・・・・15                                |     | 18.4. I/C            | )ポート用レジスタ ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                      | • 67 |

|     | 11.4. 汎用レジスタファイル・・・・・・・ 16                                    | 19. | TC0 - 8h             | ごット タイマ/カウンタ0 (PWM) ・・・・・・・・・                                                       | 70   |

|     | 11.5. スタック ホペインタ ・・・・・・・・・・・16                                |     | 19.1. 特征             | <b>数・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・</b>                                        | • 70 |

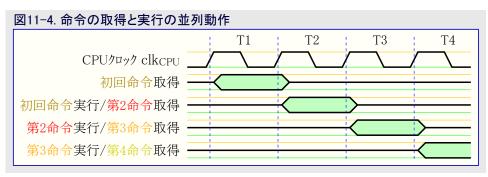

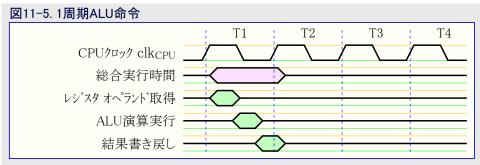

|     | 11.6. 命令実行タイミング・・・・・・ 17                                      |     |                      | 。<br>要 ······                                                                       |      |

|     | 11.7. リセットと割り込みの扱い ・・・・・・ 18                                  |     |                      | マ/カウンタのクロック ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                     |      |

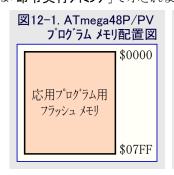

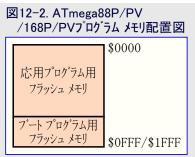

| 12. | AVRのメモリ · · · · · · 20                                        |     |                      | <i>、。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。</i>                                        |      |

|     | 12.1. 概要 ・・・・・・・・・・・ 20                                       |     |                      | & Hand<br>較出力部 ·······                                                              |      |

|     | <b>12.2</b> . 実装書き換え可能なプログラム用フラッシュ メモリ ・・ 20                  |     |                      | 酸血刃品<br>較一致出力部 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                 |      |

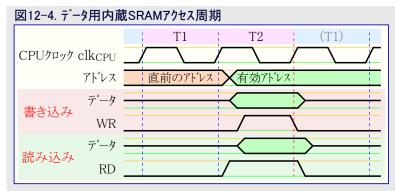

|     | <b>12.3</b> . データ用SRAMメモリ ・・・・・・・・・ 20                        |     |                      | 段                                                                                   |      |

|     | <b>12.4. データ用EEPROMメモリ ・・・・・・・・・・・・・・・・・・・・・・</b> 21          |     |                      | マ/カウンタのタイミンク゛・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                   |      |

|     | 12.5. 1/0メモリ (レジスタ) ・・・・・・・・・・・・・・・・・・・・・・・・21                |     | 10.0. 71             | ット タイマ/カウンタ0用レジスタ ・・・・・・・・・・・・                                                      | - 11 |

|     | 12.6. メモリ関係レジスタ・・・・・・・・・・・・・23                                |     |                      |                                                                                     |      |

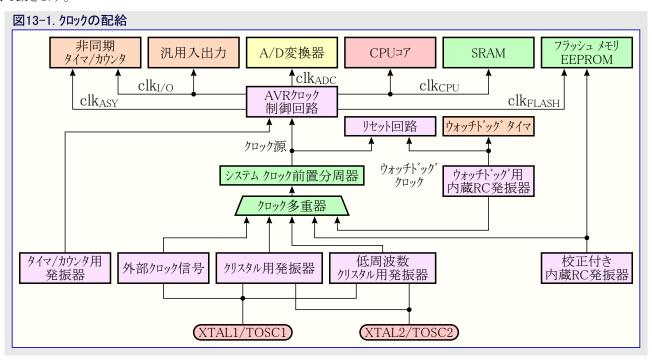

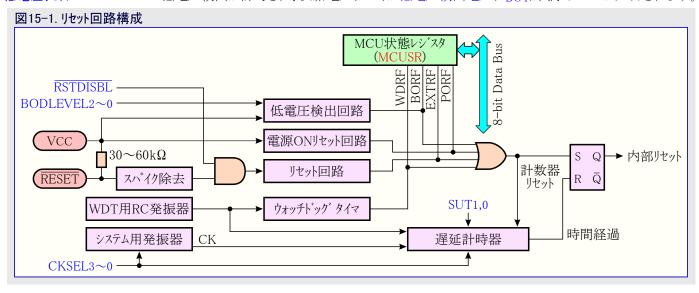

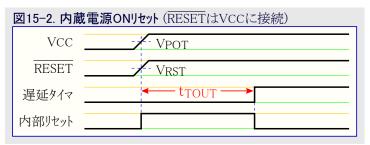

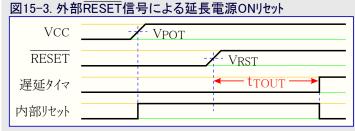

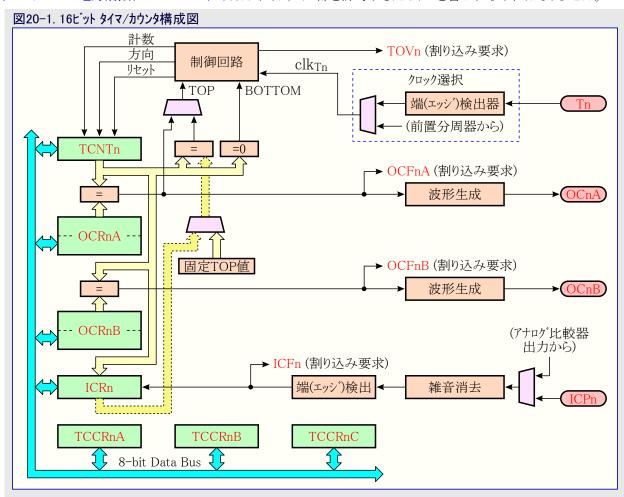

| 13  | システム クロックとクロック選択 ・・・・・・・・・ 27                                 | 20. |                      | らヒ <sup>゛</sup> ット タイマ/カウンタ1 (PWM) ・・・・・・・・・                                        |      |

| 10. | 13.1. クロック系統とその配給・・・・・・・・27                                   |     |                      | 要 •••••                                                                             |      |

|     | 13.2. クロック元・・・・・・・・・・・・・・・・・・28                               |     |                      | 數<br>数                                                                              |      |

|     | 13.3.                                                         |     |                      | <b>戎図 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・</b>                                      |      |

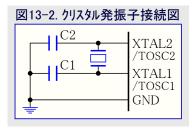

|     | 13.4. クリスタル用色電力光振器・・・・・・・・・29                                 |     |                      | 義                                                                                   |      |

|     |                                                               |     |                      | 系レジスタ ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                          |      |

|     |                                                               |     |                      | ごット レジスタのアクセス ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                  |      |

|     |                                                               |     |                      | マ/カウンタのクロック ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                     |      |

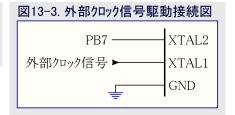

|     | 13.7. 128kHz内部発振器 ・・・・・・・・・ 31<br>13.8. 外部クロック信号 ・・・・・・・・・ 32 |     | 20.8. 計算             | 数器部 ••••••                                                                          | • 87 |

|     | 13.8. 外部747/16方 11111111111111111111111111111111111           |     |                      | <b>獲入力部 ·······</b>                                                                 |      |

|     | 13.9. タイマ/カウンタ用発振器32                                          |     | 20.10. 比             | <b>較出力部 ·······</b>                                                                 | • 89 |

|     | 13.10. システム クロック出力緩衝部 ・・・・・・ 32                               |     |                      | 較一致出力部 ••••••                                                                       |      |

|     | 13.11. システム クロック前置分周器 ・・・・・・ 32                               |     | 20.12. 動作            | 作種別 ••••••                                                                          | • 91 |

|     | 13.12. クロック関係レジスタ・・・・・・ 33                                    |     | 20.13. 51            | マ/カウンタのタイミング・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                    | • 95 |

| 14. | PM - 電力管理と休止形態 ······ 34                                      |     | 20.14. 16t           | ごット タイマ/カウンタ1用レジスタ ・・・・・・・・・                                                        | • 96 |

|     | 14.1. 概要 ・・・・・・・・・・・ 34                                       | 21  |                      | 少0と1の前置分周器・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                      |      |

|     | 14.2. 休止形態種別 ・・・・・・・・・ 34                                     |     | 211 内部               | 部クロック元 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                         | 102  |

|     | 14.3. 低電圧検出器(BOD)禁止 ····· 34                                  |     | 21.2. 前              | <b>置分周器リセット ・・・・・・・・・・・・・・・・・・</b>                                                  | 102  |

|     | <b>14.4. アイドル動作 ・・・・・・・・・・・・・・・</b> 35                        |     | 21.2. 外音             | ョンカーボット<br>部クロック元                                                                   | 102  |

|     | 14.5. A/D変換雜音低減動作 · · · · · · 35                              |     |                      | 期系TC前置分周器制御用レジスタ・・・・・・・                                                             |      |

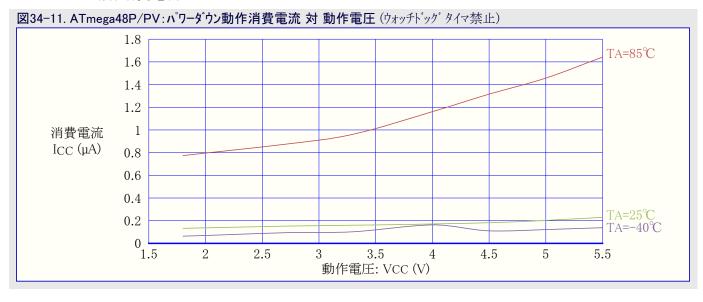

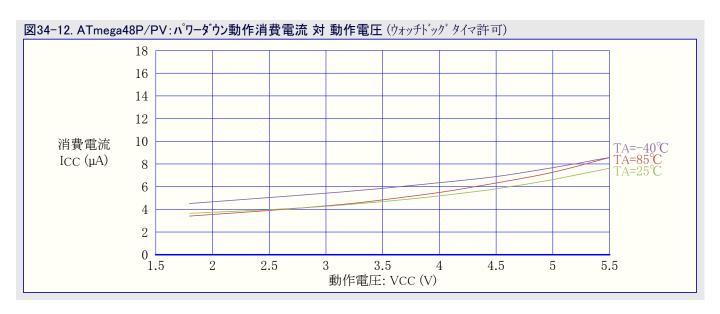

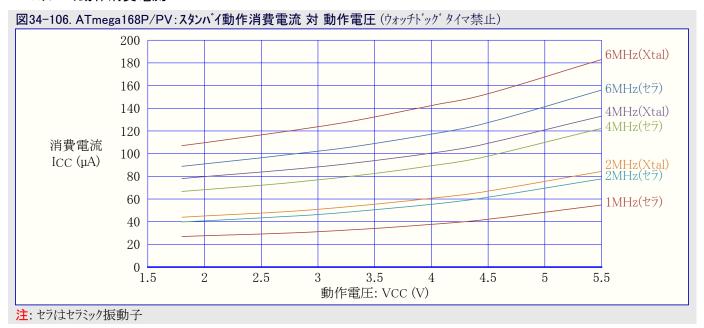

|     | <b>14.6</b> . パワーダウン動作 ・・・・・・・・・・・・・ 35                       | 00  |                      |                                                                                     |      |

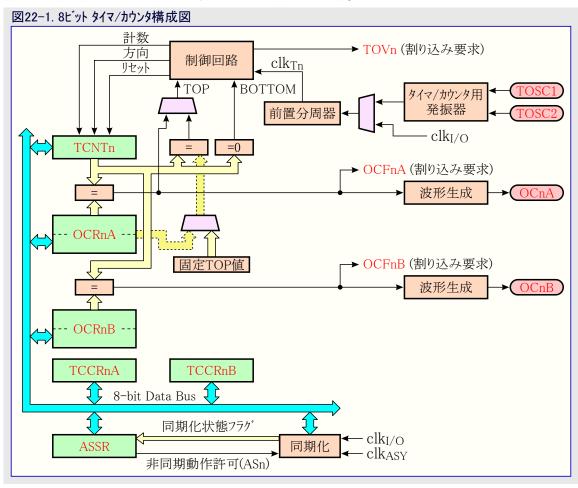

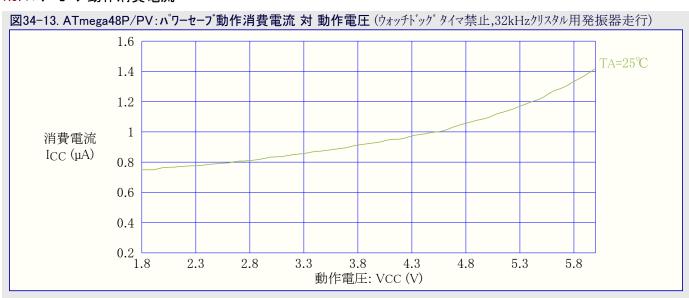

|     | 14.7. パワーセーブ動作・・・・・・・・・・・・・・・・・36                             | 22. |                      | : ット タイマ/カウンタ2 (PWM,非同期動作) • •                                                      |      |

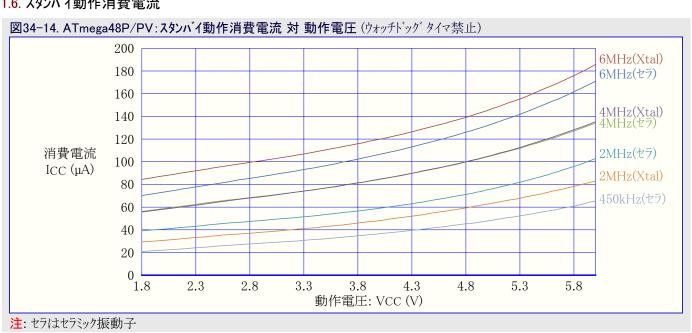

|     | 14.8. スタンバイ動作・・・・・・・・・・・・・・・・36                               |     |                      | <u> </u>                                                                            |      |

|     | 14.9. 拡張スタンバイ動作 ・・・・・・・・・・・ 36                                |     |                      | 要 ·····                                                                             |      |

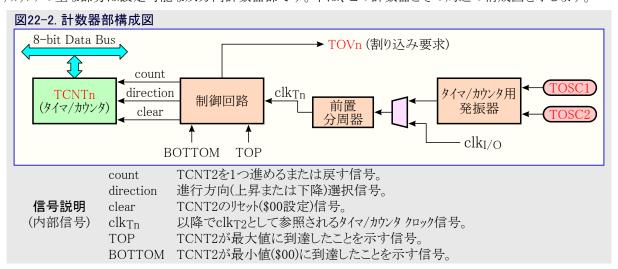

|     | 14.10. 電力削減レジスタ・・・・・・・・・・36                                   |     |                      | マ/カウンタのクロック ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                     |      |

|     | 14.11. 消費電力の最小化 ・・・・・・・・・36                                   |     |                      | 数器部                                                                                 |      |

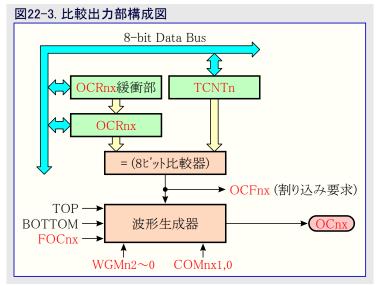

|     | 14.12. 電力管理用レジスタ・・・・・・・・・・・38                                 |     | 22.5. 比              | 較出力部                                                                                | 106  |

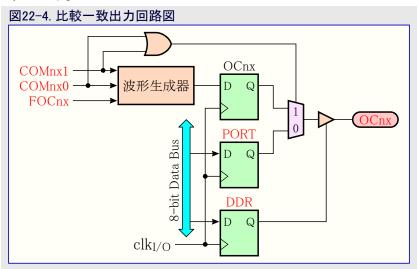

|     | .5.7.1.2.1                                                    |     | 22.6. 比              | 較一致出力部 ·····                                                                        | 107  |

|             |             | 動作種別 ・・・・・・・・ 108                              |             | 29.3.       | 物理インターフェース ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 183 |

|-------------|-------------|------------------------------------------------|-------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

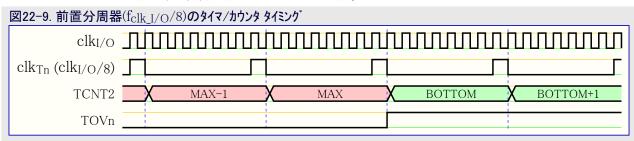

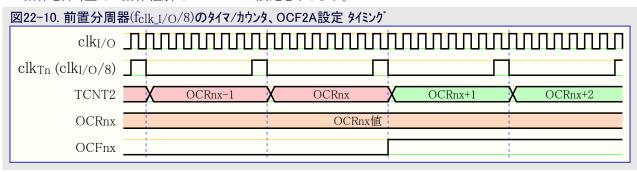

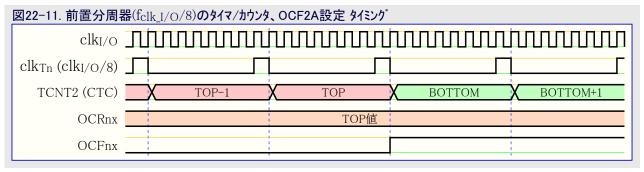

|             | 22.8.       | タイマ/カウンタのタイミング・・・・・・・・・・111                    |             | 29.4.       | ソフトウェア中断点・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 183 |

|             | 22.9.       | <b>タイマ/カウンタ2の非同期動作 ・・・・・・・・</b> 112            |             | 29.5.       | デバッグWIREの制限・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 183 |

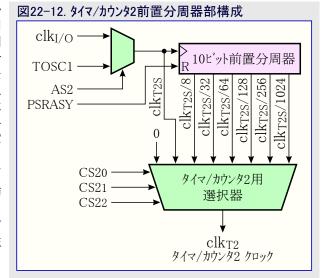

|             | 22.10.      | タイマ/カウンタ2の前置分周器 ・・・・・・・・ 113                   |             | 29.6.       | デバッグWIRE用レジスタ ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|             | 22.11.      | 8ビット タイマ/カウンタ2用レジスタ ・・・・・・・ 114                | 30          |             | ュ <b>の</b> 自己プログラミング - 48P/PV ・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 23          |             |                                                | •••         |             | 概要 ••••••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|             | 23.1.       | 特徴                                             |             | 30.2.       | 自己プログラミングでのフラッシュアトレス指定・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|             | 23.2.       | 概要 ・・・・・・・・・・ 121                              |             |             | 自己プログラミング用レジスタ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|             |             | SSL°ンの機能 ····· 123                             | 21          |             | ロロップ・パング / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / 100 / | 100 |

|             | 23.4.       | データ転送形式 ・・・・・・・・・・ 124                         | <b>3</b> 1. |             | バーノードロージ又版<br>バウココ°ロケニミング)。cop/pv//tcop/pv/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 190 |

|             | 23.5.       |                                                |             | (RVVVV      | パーノードローメス版<br>(自己プログラミング) - 88P/PV/168P/PV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100 |

| 0.4         |             | SPI用レジスタ · · · · · · · 125                     |             | 31.1.       | 特徴                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 24.         |             | 127                                            |             | 31.2.       | 概要                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|             | 24.1.       | 特徴                                             |             | 31.3.       | フラッシュ メモリの応用領域とブートローダ領域・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|             |             | ****                                           |             | 31.4.       | 書き中に読みが可能な領域と不能な領域・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

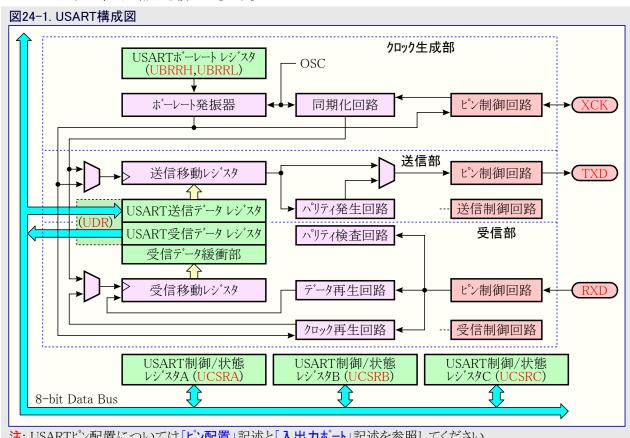

|             |             | 構成図127                                         |             | 31.5.       | ブートローダ施錠ビット ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

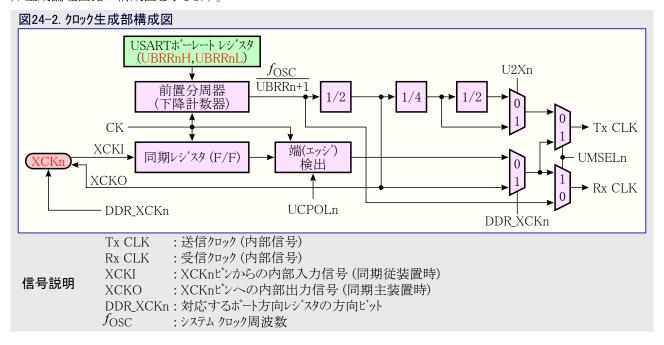

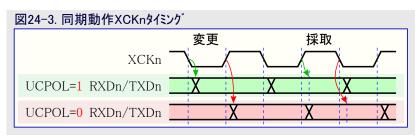

|             |             | クロック生成 ・・・・・・・・ 128                            |             | 31.6.       | ブートローダブログラムへの移行・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

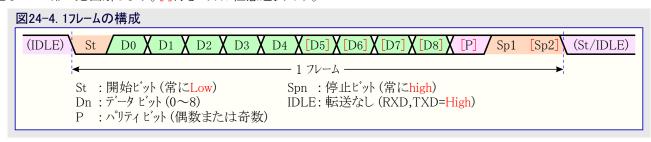

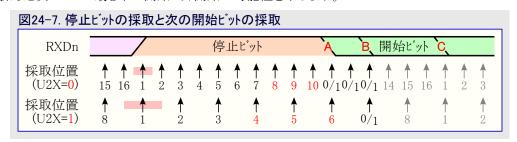

|             |             | フレーム形式・・・・・・・・・129                             |             | 31.7.       | 自己プログラミングでのフラッシュ アドレス指定・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|             |             | USARTの初期化 ・・・・・ 130                            |             | 31.8.       | フラッシュ メモリの自己プログラミング・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|             | 24.7.       | <del>データ送信 - USART送信部 ・・・・・・・・ 131</del>       |             | 31.9.       | ブート ローダ 関係レジスタ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|             | 24.8.       | <b>データ受信 - USART受信部 ・・・・・・・</b> 132            | 32.         | <b>MEMF</b> | PROG - メモリ プログラミング ・・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|             |             | *** *****                                      |             | 32.1.       | プログラム メモリとデータ メモリ用施錠ビット ・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 201 |

|             |             | <b>複数プロセッサ通信動作 ・・・・・・・・・</b> 137               |             | 32.2.       | ヒュース゛ヒ゛ット ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|             | 24.11.      | ボーレート設定例・・・・・・・・・138                           |             | 32.3.       | 識票バイト ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|             | 24.12.      | <b>USART用レジスタ・・・・・・・・・</b> 140                 |             | 32.4.       | 校正バイト ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

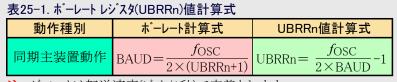

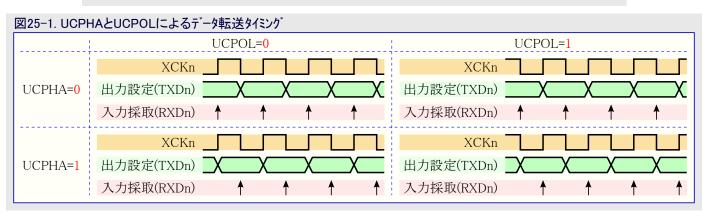

| <b>25</b> . | <b>USAR</b> | TSPI - USARTでのSPI動作 ・・・・・ 144                  |             | 32.5.       | ページ容量・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

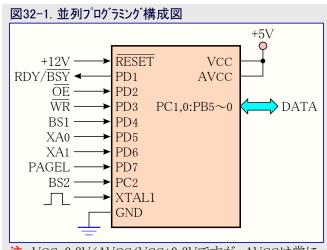

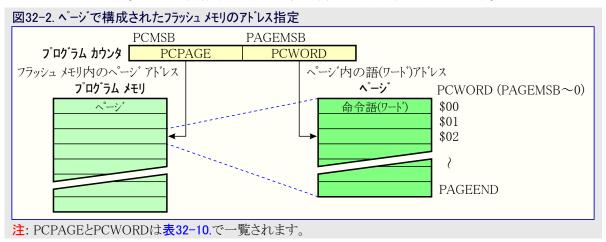

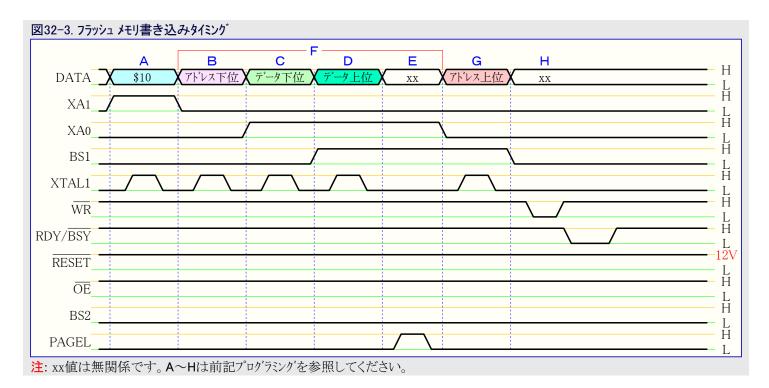

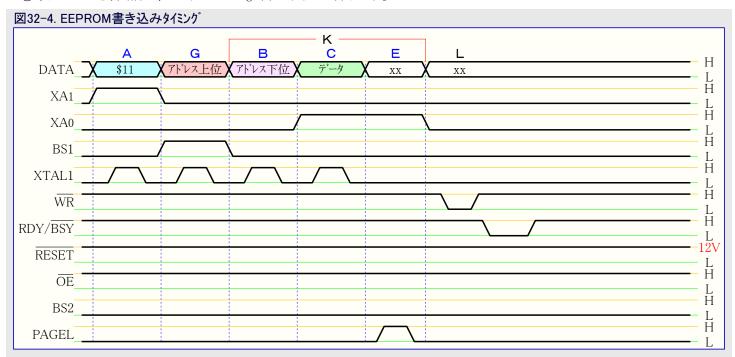

|             | 25.1.       | 特徴                                             |             | 32.6.       | 並列プログラミング・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|             | 25.2.       | 概要 ・・・・・・・・・ 144                               |             | 32.7.       | 並列プログラミング手順・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

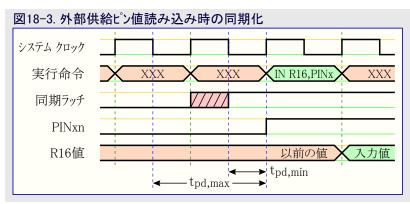

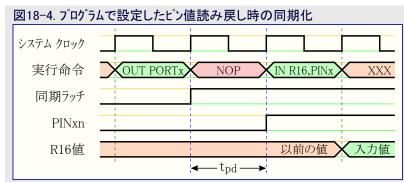

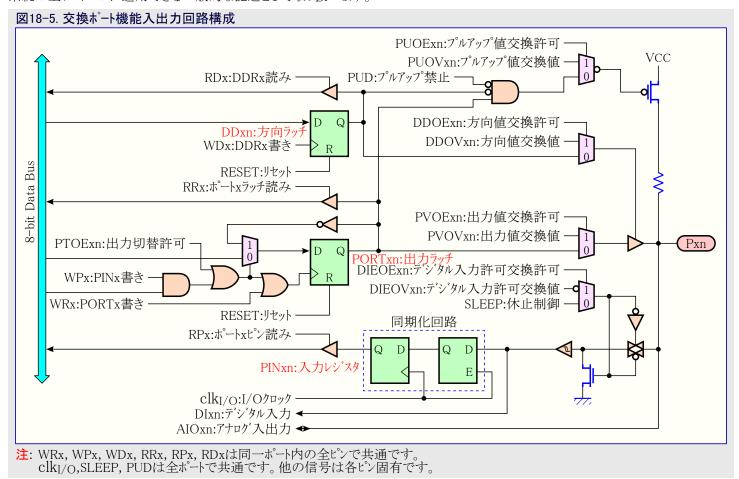

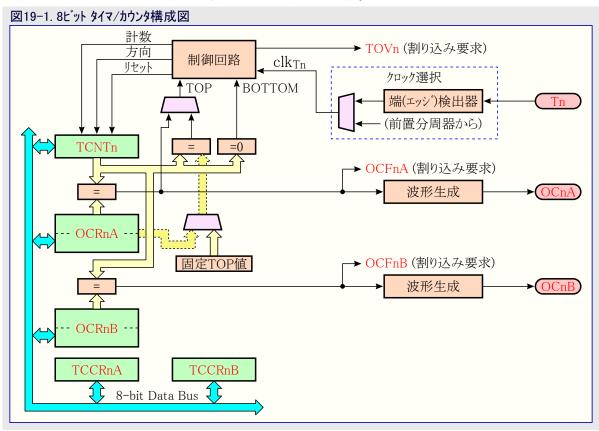

|             | 25.3.       | <b>クロック生成 ・・・・・・・・・・・・・・・</b> 144              |             | 32.8.       | 直列プログラミング・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |