# ATmegaET64M1

# 64KBフラッシュ、2KB EEPROM、4KB SRAM、10ビットADC、10ビットDAC、CAN、UART、12ビットPSC、SPI、PWM付き8ビットと16ビットのタイマ/カウンタを持つ3.3V、8MHz 拡張温度AVR® マイクロ コントローラ

# 序説

ATmegaET64M1はAVR®強化RISC構造に基づく低電力CMOS 8ビット マイクロ コントローラです。単一クロック周期での強力な命令の実行により、ATmegaET64M1はMHz当たり1MIPS近くの単位処理量を達成します。これは消費電力対処理速度に対するデバイスの最適化をシステム設計者に許します。

本書は一般の方々の便宜のため有志により作成されたもので、Microchip社とは無関係であることを御承知ください。しおりの[はじめに]での内容にご注意ください。

# 特徴

- 高性能、低消費AVR 8ビットマイクロコントローラ

- ・進化したRISC構造

- 強力な131命令(多くは1周期で実行)

- 32個の1バイト長汎用レジスタ

- 完全なスタティック動作

- 1MHz当たり、1MIPSに達する高速動作

- 2周期実行の乗算命令

- ・ データ メモリと不揮発性プログラム メモリ

- 実装自己書き換え可能な64Kバイト(32K語)フラッシュ メモリ内蔵

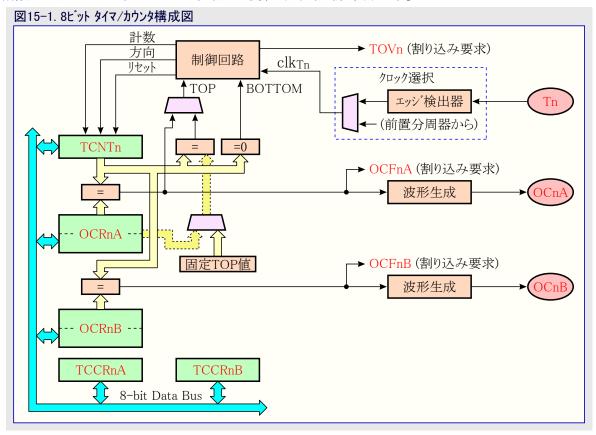

- 2KバイトのEEPROM

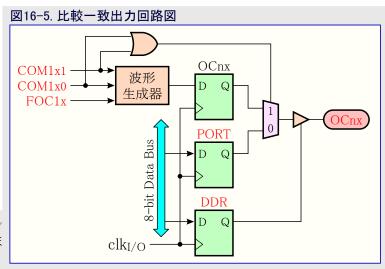

- 4Kバイトの内蔵SRAM

- 書き換え(消去/書き込み)回数: フラッシュ メモリ: 10,000回、EEPROM: 20,000回

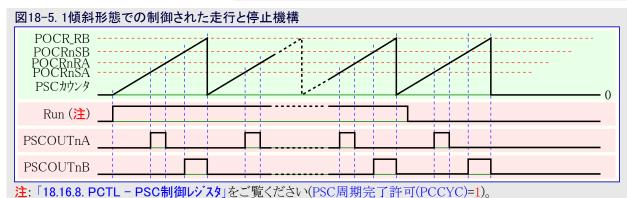

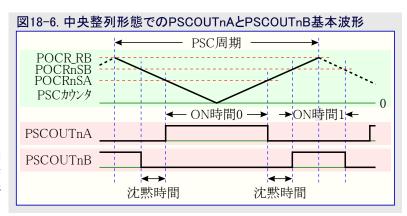

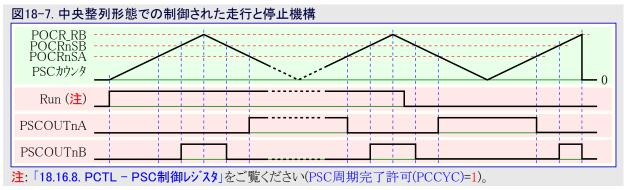

- データ保持力:15年/70℃、10年/125℃

- 個別施錠ビットを持つ任意のブート コード領域

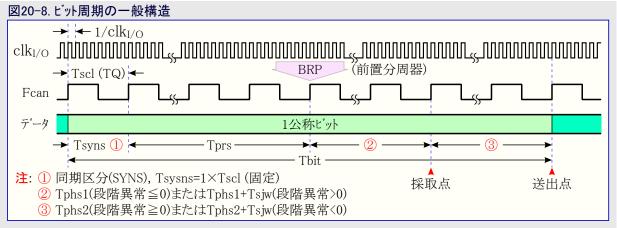

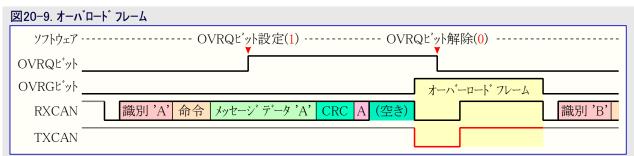

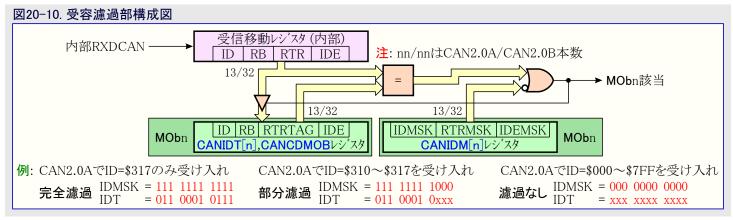

- ・チップ内ブートプログラムによる実装書き換え

- ・真の書き込み中の読み出し動作

- ソフトウェア保護用の設定可能な施錠機能

- デバックWIRE内蔵デバック機能

- 6つのメッセージ項目を持つ制御域網(CAN) 2.0Aと2.0B 制御器 ISO16845保証

- (LIN2.1と1.3の制御器を支援する)8ビットUART

- ・1つの12ビット高速電力段制御器(PSC)

- 柔軟な沈黙時間付き非重複反転PWM出力ピン

- 可変PWMデューティ比と可変PWM周波数

- 全PWMレジスタの同期更新

- 緊急事態用の自動停止機能

- 内蔵周辺機能

- 独立した前置分周器、比較機能付き、1つの汎用8ビット タイマ/カウンタ(TC)

- 独立した前置分周器、比較、捕獲機能付き、1つの汎用16ビットタイマ/カウンタ

- 主装置/従装置動作SPI直列インターフェース

- 10ビット A/D変換器(ADC)

- ・11個までのシングルエント、入力チャネルと、3つの完全な差動チャネル対

- ・設定可能な利得(差動チャネルでの×5,×10,×20,×40)

- 内部基準電圧

- · 電源電圧直接測定

- 可変電圧基準(アナログ)比較器、A/D変換器)用10ビット D/A変換器(DAC)

- 可変検出閾値を持つ4つのアナログ比較器(AC)

- 100μA±2%電流源(LIN節(ノート)認証)

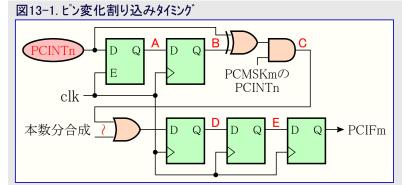

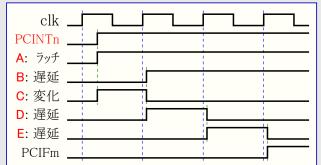

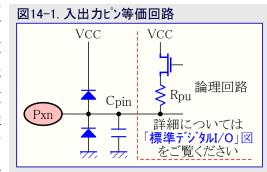

- ピン変化での割り込みと起動復帰

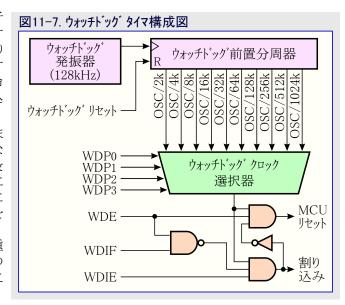

- 独立したチップ上の発振器を持つ設定可能なウォッチドッグ、タイマ(WDT)

- チップ上の温度感知器

- ・ 特殊マイクロ コントローラ機能

- アイドハ、A/D変換雑音低減、パワーダウン、スタンバイの4つの低消費動作

- 電源ONリセット回路(POR)と設定可能な低電圧検出器(BOD)

- SPIポート経由での実装書き込み

- CAN動作用高精度クリスタル用発振器

- 校正付き8MHz内部RC発振器

- 高速PWM用のチップ上PLL

- 動作範囲

- 動作電圧: 3.0~3.6V

- 動作温度: -55~+125℃

- 速度等級

- $-0\sim8MHz$

- · ESD等級

- HBM > 4000V (等級3A)

- CDM > 1000V (等級IV)

- ・I/Oと外囲器

- 27ビットの設定可能なI/O

# 目次

|     | 序説                                                                                   | 12. |           | 割り込み ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                         |          |

|-----|--------------------------------------------------------------------------------------|-----|-----------|-------------------------------------------------------------------|----------|

|     | 特徴2                                                                                  |     | 12.1.     | ATmegaET64M1の割り込みベクタ・・・・・・・・・                                     | • • • 40 |

| 1.  | 概要 ••••• 5                                                                           |     |           | ベクタ移動用レジスタ ・・・・・・・・・・・・・・・                                        |          |

|     | 構成図・・・・・・・・・・5                                                                       | 13. | 外部署       | 剽り込み(EXTINT)・・・・・・・・・・・・・・・・・                                     | • • 44   |

|     | l <sup>2</sup> ン構成 ······ 6                                                          |     | 13.1.     | 概要                                                                | • • • 44 |

| პ.  | こ / 情                                                                                |     | 13.2.     | 外部割り込み用レジスタ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                   | ••• 45   |

| _   | 3.1. ピン説明 · · · · · · · · · · · · · · · · · · ·                                      | 1.4 |           | カポ <sup>°</sup> ート・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・            |          |

| 4.  | <b>注文情報 ······</b> 8                                                                 | 17. | <u>7Д</u> | 概要                                                                | 50       |

| 5.  | <b>資料 ·····</b> 8                                                                    |     |           | 標準デジダル入出力としてのポート・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・              |          |

| 6.  | コート・例について・・・・・・・8                                                                    |     | 14.3.     |                                                                   | 50       |

|     | AVR CPU <b>37</b> · · · · · 9                                                        |     |           | I/Oポート用レジスタ ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                  |          |

| ١.  | 7.1. 概要····································                                          | 15  |           |                                                                   |          |

|     | 7.2. ALU (Arithmetic Logic Unit) 9                                                   | 15. |           | 付き8ビット タイマ/カウンタ0 (TC0) ・・・・・<br>特徴 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 00       |

|     | 7.3. $\lambda \bar{\tau} - 9\lambda \bar{\nu} \bar{\nu} \lambda \bar{\nu} \cdots 10$ |     | 15.1.     | 概要 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                           | 60       |

|     | 7.4. 汎用レジスタファイル・・・・・・・・・・・10                                                         |     |           |                                                                   |          |

|     | 7.5. スタック ポインタ · · · · · · · · · · · · · · · · · · ·                                 |     |           | 計数器部 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                         | 67       |

|     | 7.6. 16ビット レシ スタのアクセス · · · · · · · · · · · · 12                                     |     | 15.4.     | 計                                                                 | 67       |

|     | 7.0. 10c 分 レン 人 3 0 0 7 9 c A                                                        |     | 15.5.     |                                                                   |          |

|     | 7.8. リセットと割り込みの扱い・・・・・・・・・・13                                                        |     | 15.6.     | 比較一致出力部 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                      | 69       |

| 0   |                                                                                      |     | 15.7.     | 動作種別                                                              |          |

| 8.  | AVRのメモリ・・・・・・15                                                                      |     |           | タイマ/カウンタのタイミング・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                |          |

|     | 8.1. 概要                                                                              |     |           | 8ビット タイマ/カウンタ0用レジスタ ・・・・・・・・・                                     |          |

|     | 8.2. 実装書き換え可能なプログラム用フラッシュ メモリ・・・ 15                                                  | 16. |           | 付き16ビット タイマ/カウンタ1(TC1) ・・・・                                       |          |

|     | 8.3. データ用SRAMメモリ                                                                     |     | 16.1.     | 概要                                                                |          |

|     | 8.4. データ用EEPROMメモリ・・・・・・ 16                                                          |     | 16.2.     | 特徴                                                                |          |

|     | 8.5. I/Oメモリ (レジネタ) ・・・・・・・・・・16                                                      |     | 16.3.     | 構成図                                                               |          |

|     | 8.6. メモリ関係レジスタ・・・・・・18                                                               |     | 16.4.     | 定義                                                                |          |

| 9.  | システム クロックとクロック選択 ・・・・・・ 22                                                           |     | 16.5.     | 関係レジスタ ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                       |          |

|     | 9.1. クロック系統とその配給・・・・・・22                                                             |     | 16.6.     | 16ビット <mark>タイマ/カウンタ レジスタのアクセス ・・・・・・</mark>                      |          |

|     | <b>9.2. クロック元 ・・・・・・・・・・</b> 23                                                      |     | 16.7.     | タイマ/カウンタのクロック・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                  |          |

|     | <b>9.3. 既定のウロック元 ·····</b> 23                                                        |     | 16.8.     | 計数器部                                                              |          |

|     | 9.4. クリスタル用低電力発振器・・・・・・ 23                                                           |     | 16.9.     | 捕獲入力部 · · · · · · · · · · · · · · · · · · ·                       |          |

|     | 9.5. 校正付き内蔵RC発振器 ······ 24                                                           |     |           | 比較出力部 · · · · · · · · · · · · · · · · · · ·                       |          |

|     | <b>9.6.</b> PLL                                                                      |     |           | 比較一致出力部 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                      |          |

|     | <b>9.7</b> . <b>128</b> kHz内部発振器 ·············25                                     |     |           | 動作種別 · · · · · · · · · · · · · · · · · · ·                        |          |

|     | <b>9.8.</b> 外部クロック信号 ······25                                                        |     | 16.13.    | タイマ/カウンタ0と1の前置分周器・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・             | ••• 9]   |

|     | 9.9. システム クロック出力緩衝部 ・・・・・・・・ 26                                                      |     |           | タイマ/カウンタのタイミング・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                |          |

|     | 9.10. システム クロック前置分周器 ・・・・・・・・26                                                      |     |           | 16ビット タイマ/カウンタ1用レジスタ ・・・・・・・・                                     |          |

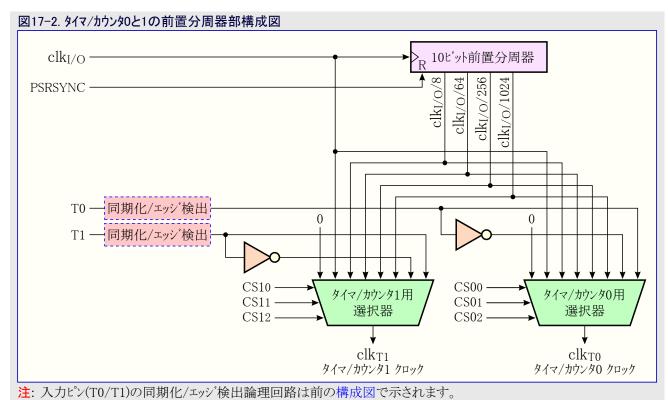

|     | <b>9.11</b> . クロック関係用レジスタ ・・・・・・・・・ 27                                               | 17. | タイマノブ     | かウンタ0と1の前置分周器 ・・・・・・・・・                                           | •• 98    |

| 10. | 電力管理と休止形態 ・・・・・・・・ 29                                                                |     | 17.1.     | 内部クロック元・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                        | ••• 98   |

|     | 10.1. 休止形態種別 ***************** 29                                                    |     | 17.2.     | 前値分周器リセット・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                     | ••• 98   |

|     | <b>10.2. アイドル動作 ・・・・・・・・・・・・・・・</b> 29                                               |     |           | 外部クロック元・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                        |          |

|     | 10.3. A/D変換雑音低減動作 · · · · · · 29                                                     |     | 17.4.     | タイマ/カウンタ捕獲ピン・前値分周器用レジスタ・                                          | 99       |

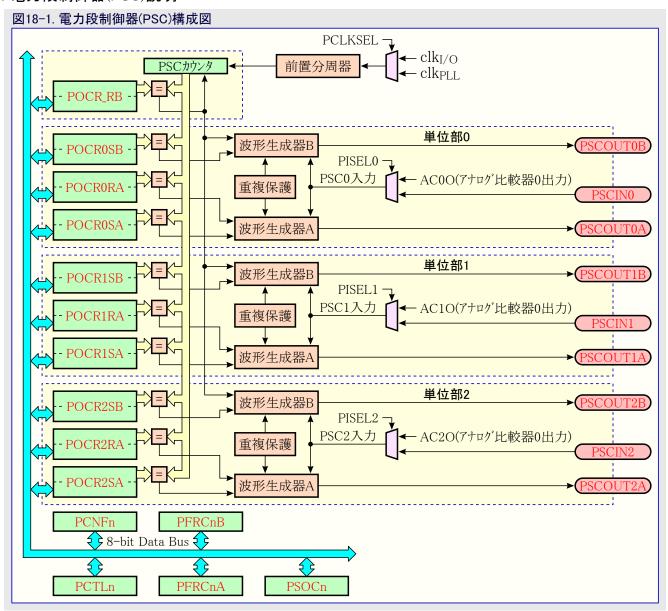

|     | <b>10.4</b> . パプーダウン動作 ・・・・・・・・・・・・・ 30                                              | 18. | PSC -     | - 電力段制御器 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                     | • 100    |

|     | 10.5. スタンバイ動作・・・・・・・・・30                                                             |     | 18.1.     | 特徵                                                                |          |

|     | 10.6. 電力削減(電力削減レジスタ)・・・・・・・・・30                                                      |     | 18.2.     | 概要 ••••••                                                         |          |

|     | 10.7. 消費電力の最小化 ・・・・・・・・・ 30                                                          |     |           | 16ビットレジスタのアクセス・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                |          |

|     | 10.8. 電力管理用レジスタ・・・・・・・・・・・32                                                         |     | 18.4.     | 電力段制御器(PSC)説明 ······                                              |          |

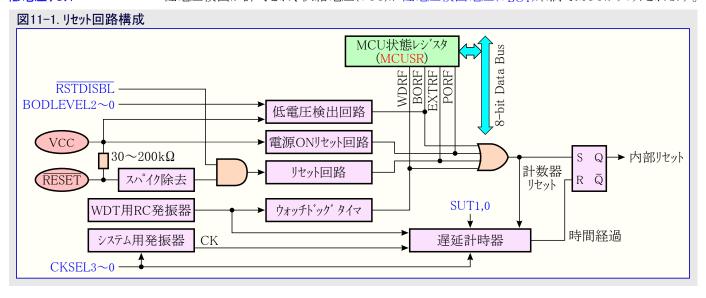

| 11. | システム制御とリセット・・・・・・・・・・・ 34                                                            |     | 18.5.     | 機能説明                                                              |          |

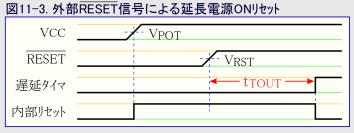

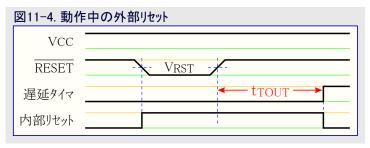

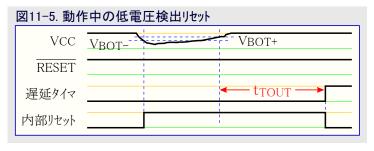

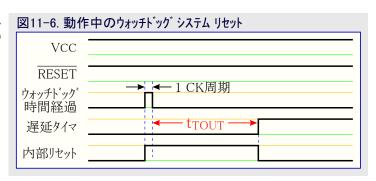

|     | 11.1. AVRのリセット · · · · · · · 34                                                      |     | 18.6.     | 値の更新・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                          | •• 103   |

|     | 11.2. リセット元 ・・・・・・・・・・・・・・・・・ 34                                                     |     | 18.7.     | 重複保護                                                              | • 103    |

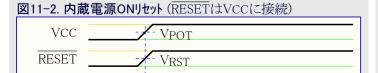

|     | 11.3. 電源ONリセット ······ 35                                                             |     | 18.8.     | 信号説明 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                         | •• 104   |

|     | 11.4. 外部リセット・・・・・・・・・・・・・・・・・・・・・・・35                                                |     |           | 電力段制御器(PSC)入力 ······                                              |          |

|     | 11.5. 低電圧検出(BOD)リセット・・・・・・・ 35                                                       |     |           | _                                                                 |          |

|     | 11.6. ウォッチト・ック・システム リセット ······ 35                                                   |     |           | PSC入力動作1~5:<br>タイミング変更なしで出力非活動                                    | •• 106   |

|     | 11.7. 内部基準電圧 36                                                                      |     | 18.11.    | PSC入力動作6,7:                                                       | . 104    |

|     | 11.8. ウォッチトック・タイマ・・・・・・・・・・・・・・・・・・・・・・・・36                                          |     |           | PSC停止、ソフトウェア操作待機                                                  | - 100    |

|     | 11.9. リセット関係用レジスタ・・・・・・・38                                                           |     | 18.12.    | プナUク 同期化 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                      | • 106    |

|     |                                                                                      |     | 18.13.    | 割り込みの扱い・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                       | •• 106   |

|     | 18.14. PSCクロック元 ······                                               | 107                                    |       | 26.3.          | 物理インターフェース ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・        | 202 |

|-----|----------------------------------------------------------------------|----------------------------------------|-------|----------------|--------------------------------------------------------|-----|

|     | 18.15. 割り込み ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                     |                                        |       | 26.4.          | ソフトウェア中断点・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・          | 202 |

|     | 18.16. 電力段制御器(PSC)用レジ                                                | <mark>スタ • • • • • • • • • 1</mark> 08 |       | 26.5.          | デバッグWIREの制限・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・        | 202 |

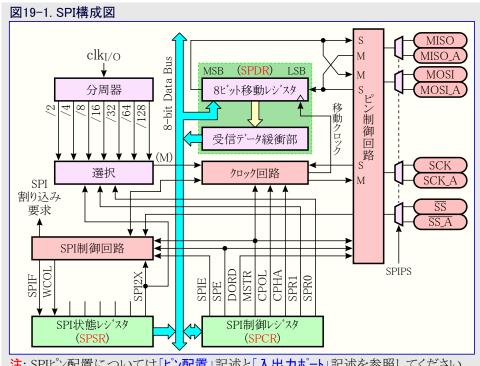

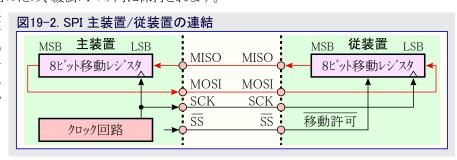

| 19. | 直列周辺インターフェース(SPI)・                                                   | ••••• 115                              |       | 26.6.          | デバッグWIRE用レジスタ ・・・・・・・・・・・・・・・・・                        | 203 |

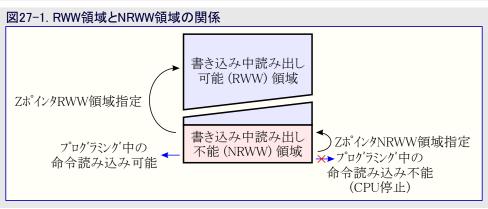

|     | 19.1. 特徴                                                             |                                        | 27.   | 3TLD           | R - ブートローダ支援 -                                         | 20  |

|     | 19.2. 概要 ••••••                                                      |                                        |       |                | RWW自己プログラミング                                           | 204 |

|     | 19.3. SSピンの機能 ······                                                 |                                        |       | 27.1.          | 特徴                                                     | 204 |

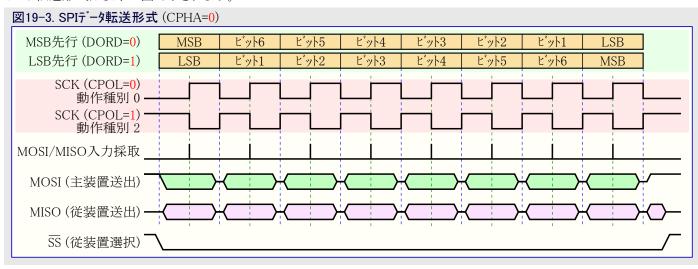

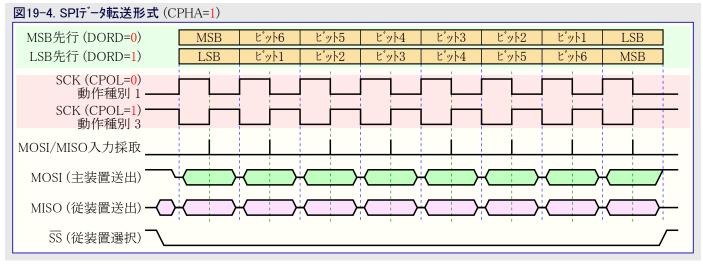

|     | 19.4. データ転送形式 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                   |                                        |       | 27.2.          | 概要 ••••••                                              |     |

|     | 19.5. SPI用レジスタ ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                  |                                        |       | 27.3.          | フラッシュ メモリの応用領域とブート ローダ領域・・・                            |     |

| 20  | CAN - 制御器域網 ·····                                                    |                                        |       | 27.4.          | 書き中に読みが可能な領域と不能な領域・                                    |     |

| 20. | 20.1. 特徴 · · · · · · · · · · · · · · · · · ·                         |                                        |       | 27.5.          | ブートローダ施錠ビット・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・        |     |

|     | 20.2. 概要 ••••••                                                      |                                        |       | 27.6.          | ブートローダブログラムへの移行・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・    |     |

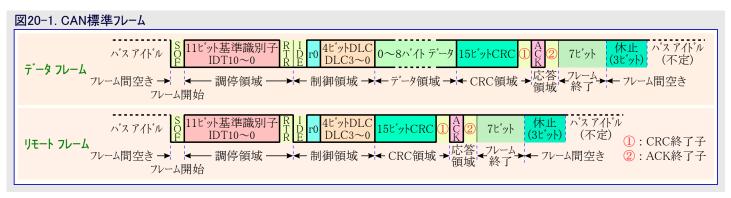

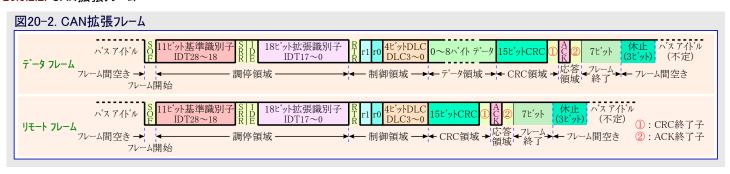

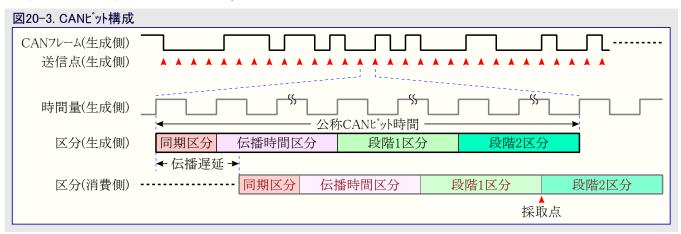

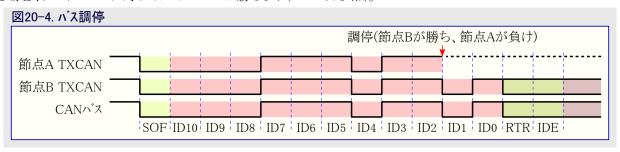

|     | 20.3. CAN規約 ····································                     |                                        |       | 27.7.          | 自己プログラミングでのフラッシュアドレス指定・・・・・                            |     |

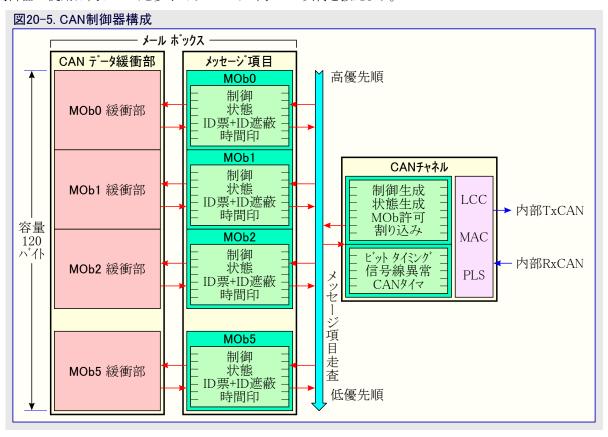

|     | 20.4. CAN制御器 ····································                    |                                        |       | 27.8.          | フラッシュ メモリの自己プログラミング・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |     |

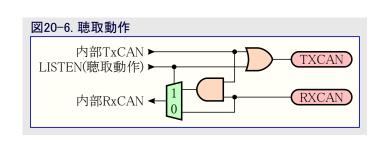

|     | 20.5. CANチャネル ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                   |                                        |       | 27.9.          | ブートローダ・用レジスタ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・       |     |

|     | 20.6. メッセーシ 項目・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                   |                                        |       |                | PRG – メモリ プログラミング・・・・・・・・・                             |     |

|     | 20.7. CANタイマ · · · · · · · · · · · · · · · · · · ·                   |                                        |       | 28.1.          | プログラム メモリとデータ メモリ用施錠ビット・・・・・・・                         |     |

|     |                                                                      |                                        |       | 28.2.          | ヒュース、ヒット・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・           |     |

|     |                                                                      |                                        |       | 28.3.          |                                                        |     |

|     |                                                                      |                                        |       |                | 識票バイト ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・             |     |

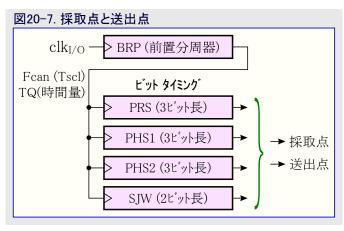

|     | 20.10. CANボーレート設定例 ・・・・・<br>20.11. CAN用レジスタ ・・・・・・・・                 |                                        |       | 28.4.          | 校正バイト ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・             |     |

| 0.4 |                                                                      | 154                                    |       | 28.5.<br>28.6. | ^゚ージ容量・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・             |     |

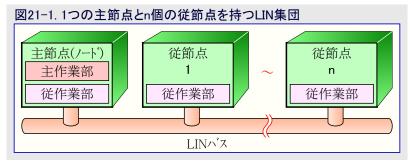

| 21. | LIN/UART -                                                           | t-1+11ADT *** 151                      |       |                |                                                        |     |

|     | 局所相互連結網制御器ま                                                          | CIAUARI                                |       | 28.7.          | 並列プログラミング手順・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・        |     |

|     | 21.1. 特徴                                                             |                                        |       | 28.8.          | 直列プログラミング・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・           |     |

|     | 21.2. 概要                                                             |                                        |       | 28.9.          | 直列プログラミング手順 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・       |     |

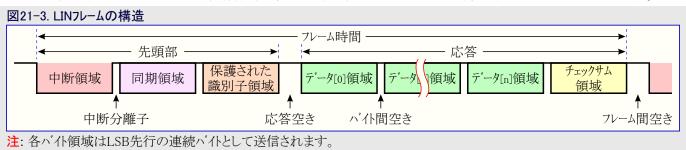

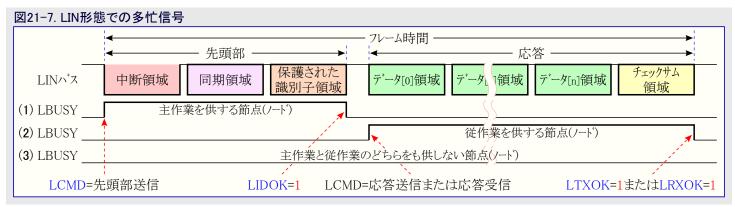

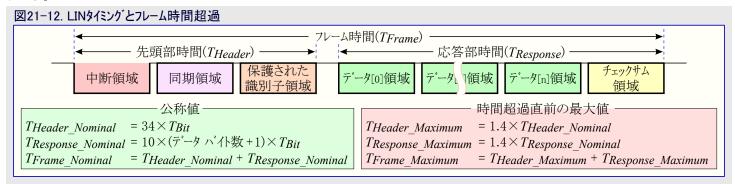

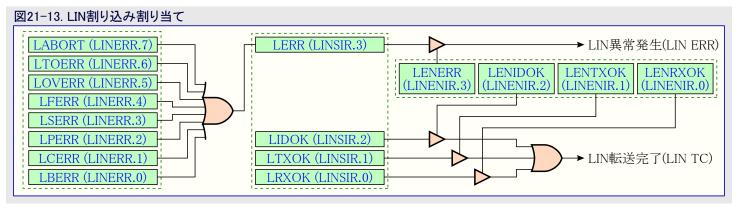

|     | 21.3. LIN規約 ····································                     | 151                                    |       |                | 的特性 •••••                                              |     |

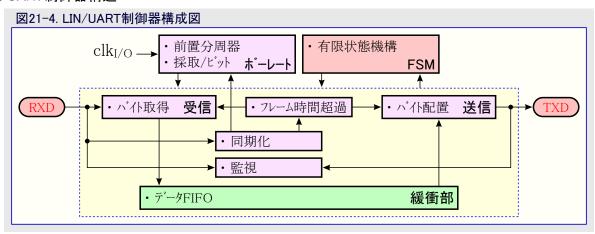

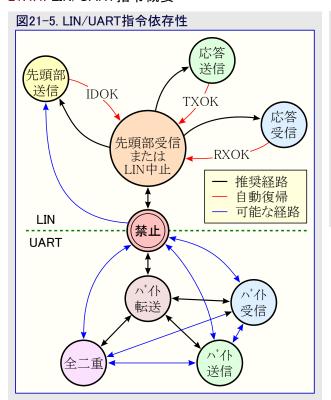

|     | 21.4. LIN/UART制御器 ······                                             | 153                                    |       | 29.1.          | <b>絶対最大定格</b> ••••••••••••••••••••••••••••••••••••     |     |

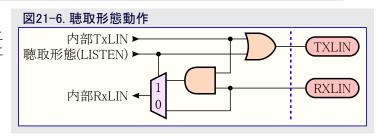

|     | 21.5. LIN/UART説明 ·······                                             |                                        |       | 29.2.          | DC特性 · · · · · · · · · · · · · · · · · · ·             |     |

|     | 21.6. LIN/UART用レジスタ・・・・・                                             |                                        |       | 29.3.          | クロック特性・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・             |     |

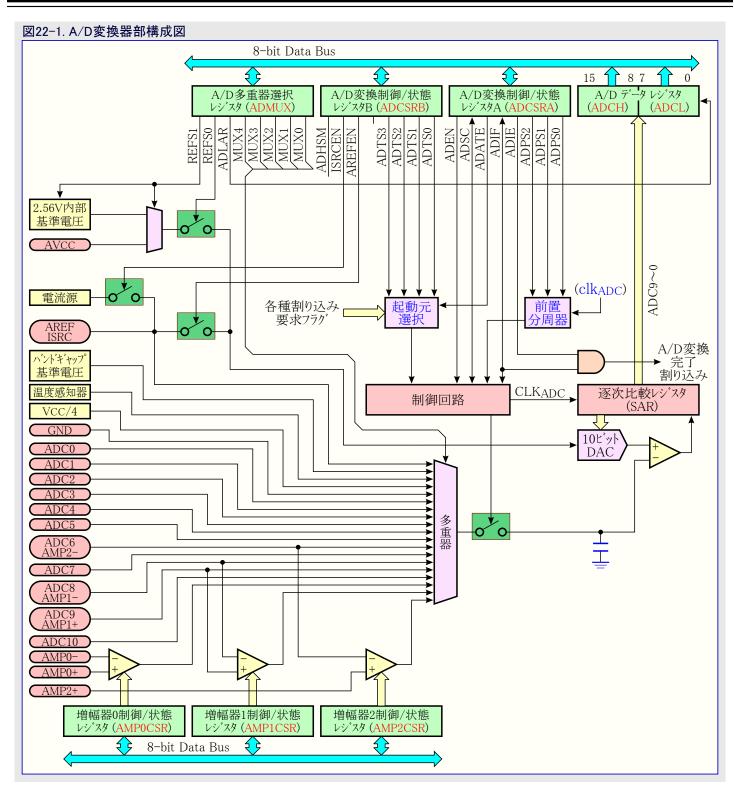

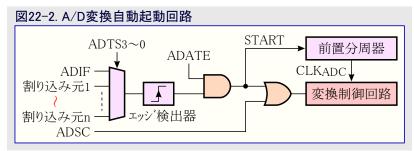

| 22. | A/D変換器 (ADC)······                                                   |                                        |       | 29.4.          | 外部クロック駆動特性・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・         |     |

|     | 22.1. 特徴                                                             |                                        |       | 29.5.          | システムとリセットの特性 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・      |     |

|     | 22.2. 概要 •••••                                                       |                                        |       | 29.6.          | PLL特性 ······                                           |     |

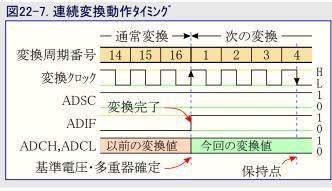

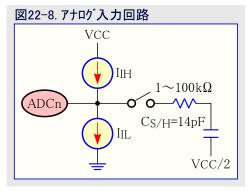

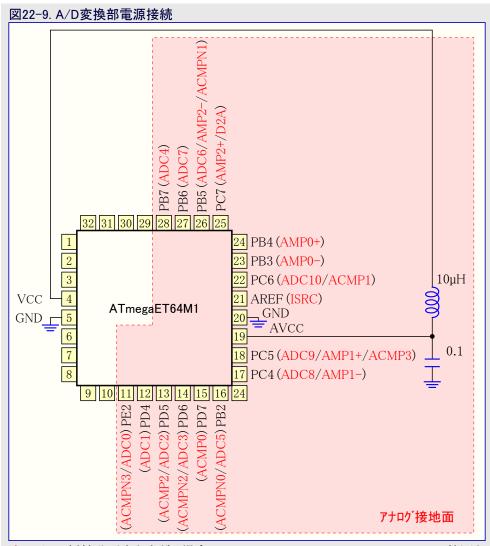

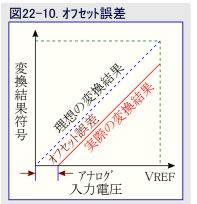

|     | 22.3. 操作 ***********************************                         |                                        |       | 29.7.          | SPI タイミング・特性・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・        |     |

|     | 22.4. 変換の開始                                                          |                                        |       | 29.8.          | A/D変換器特性・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・           |     |

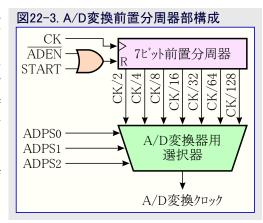

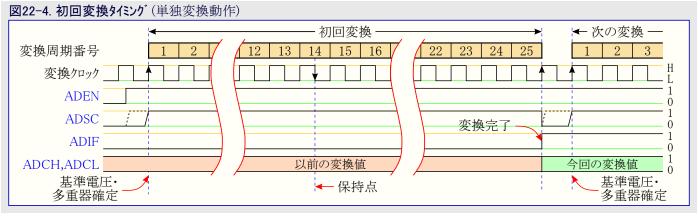

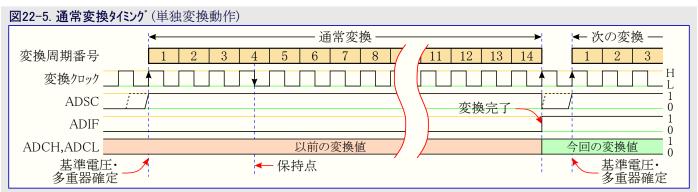

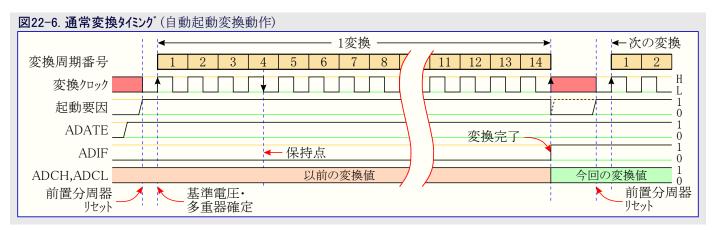

|     | 22.5. 前置分周と変換タイミング・・                                                 |                                        |       | 29.9.          | 並列プログラミング特性 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・       |     |

|     | 22.6. チャネル変更と基準電圧選択                                                  |                                        |       |                | 寺性 • • • • • • • • • • • • • • • • • • •               |     |

|     | 22.7. 雑音低減機能                                                         |                                        |       |                | <b>ピンプルアップ</b> ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・    |     |

|     | 22.8. A/D変換の結果・・・・・・・                                                |                                        |       | 30.2.          | ピン駆動部能力・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・            | 235 |

|     | 22.9. 温度測定                                                           |                                        |       | 30.3.          | ピン閾値とヒステリシス ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・       | 235 |

|     | 22.10. 増幅器                                                           | 180                                    |       |                | BOD閾値とアナログ比較器ヒステリシス・・・・・・・・                            |     |

|     | 22.11. A/D変換用レジスタ・・・・・・                                              |                                        |       |                | 内部発振器周波数 ************************************          |     |

| 23. | ISRC - 電流源 ······                                                    |                                        | 31. l | <i>、</i> ジスタ   | 要約 • • • • • • • • • • • • • • • • • • •               | 241 |

|     | 23.1. 特徴 ***********************************                         |                                        | 32.   | 命令             | 要約 • • • • • • • • • • • • • • • • • • •               | 245 |

|     | 23.2. 代表的な応用 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                    |                                        |       |                | 器情報 ·····                                              |     |

|     | 23.3. 電流源用レジスタ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                   |                                        |       |                | <u>履歴 · · · · · · · · · · · · · · · · · · ·</u>        |     |

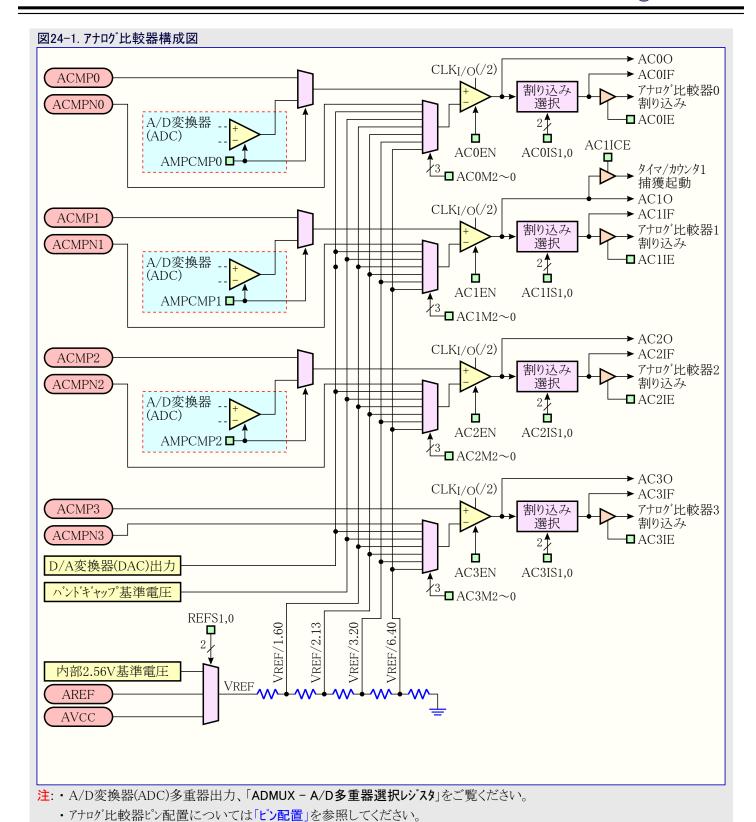

| 24. | AC - アナログ比較器 ・・・・・・                                                  | ••••• 190                              |       |                |                                                        |     |

|     | 24.1. 特徴 ***********************************                         |                                        |       |                | ウェブ サイト・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・            |     |

|     | 24.2. 概要 ••••••                                                      | 190                                    |       |                | の変更通知サービス・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・          |     |

|     | 24.3. ADC増幅器の使い方・・・                                                  | 192                                    | お客    | 様支             | 援                                                      | 250 |

|     | 24.4. アナログ比較器用レジスタ・・・                                                |                                        |       |                | <br>システム ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・          |     |

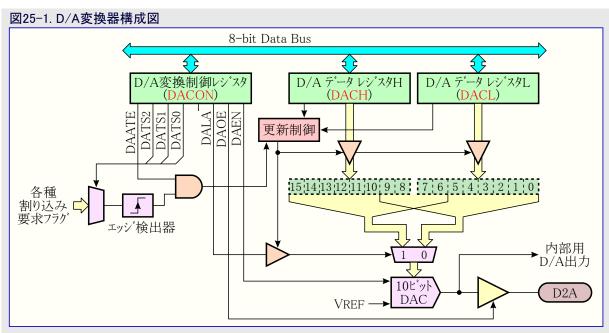

| 25  | DAC - D/A変換器 ······                                                  |                                        |       |                | デバイスコート、保護機能・・・・・・・・・・                                 |     |

| 20. | 25.1. 特徴 · · · · · · · · · · · · · · · · · ·                         |                                        |       |                |                                                        |     |

|     | 25.2. 概要 ***********************************                         |                                        |       |                | •••••                                                  |     |

|     | 25.3. 操作                                                             |                                        | 商標    | •••            | • • • • • • • • • • • • • • • • • • • •                | 251 |

|     | 25.4. 変換の開始・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                      |                                        | DNV   | によっ            | って認証された品質管理システム・・・・・                                   | 251 |

|     | 25.5. D/A変換用レジスタ・・・・・・                                               |                                        |       |                | 販売とサービス・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・            |     |

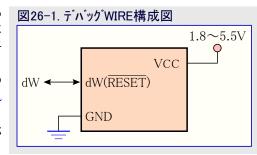

| 26  | デバッグWIRE内蔵デバッグ機能                                                     |                                        | اوس   | H 7.Q          | WAJUC / CA                                             | _02 |

| ۷٠. | 7 ハック WIRE 内蔵 T ハック 機 F 26.1. 特徴 ··································· |                                        |       |                |                                                        |     |

|     | 26.1. 特倒 ***********************************                         | 202                                    |       |                |                                                        |     |

|     | /U / M/ <del>//</del>                                                |                                        |       |                |                                                        |     |

# 1. 概要

AVRコアは32個の汎用作業レシブスタと豊富な命令群を兼ね備えています。32個の全レジブスタはALU(Arithmetic Logic Unit)に直結され、レジブスタ間命令は1クロック周期で実行されます。AVR構造は現状のCISC型マイクロコントローラに対して最大10倍の単位処理量向上効果があります。

ATmegaET64M1は次の特徴、書き込み中読める能力を持つ64Kバ小の実装書き換え可能なプラッシュメモリと2Kバ小のEEPROM、4KバイトのSRAM、27本の汎用入出力線、32個の汎用作業レジスタ、1つの電動機電力段制御器(PSC)、比較動作やPWMを含む柔軟性のある2つのタイマ/カウンタ、ハートウェア LIN動作付きの1つのUART、設定可能な増幅器を持つ2つの差動入力段付きの任意選択差動入力付き11チャネルの10ビット A/D変換器、10ビット D/A変換器、設定可能な別個の内部発振器付きウォッチドッグ タイマ、SPI直列ホート、内蔵デバッグ・システム、ソフトウェアで選択できる4つの低消費動作機能を提供します。アイドル動作では動作を停止しますが、SRAM、タイマ/カウンタ、SPIホート、CAN、LIN/UART、割り込み機能は有効で、動作を継続します。パワーダウン動作ではレジスタの内容は保護されますが、発振器が停止するため、以降のハート・ウェアリセットか外部割り込みまで他の全機能を禁止(無効に)します。A/D変換雑音低減動作ではA/D変換器を除く全ての周辺機能とCPUが停止し、故にA/D変換中の切り替え雑音を最小にします。スタンバイ動作ではクリスタル発振子/セラミック振動子用発振器が動作し、一方デバイスのその他は休止します。これは低消費電力と非常に速い起動の組み合わせを許します。

本デバイスは我々の0.35µm CMOSと高密度NVM技術を使って製造されています。内蔵の実装書き換え(ISP)可能なプログラム用フラッシュメモリは規定のNVM書き込み器、SPI直列インターフェース経由、AVRコア上ブートプログラムの実行によって再書き込みができます。ブートプログラムは応用領域フラッシュメモリ内の応用プログラムの読み込みにどのインターフェースでも使えます。ブート領域フラッシュメモリ内のプログラムは真の「書き込み中の読み出し可」動作により、応用領域フラッシュメモリ更新中も実行を継続します。モノリシックチップ上の実装書き換え可能なフラッシュメモリと、8ビットRISC型CPUの組み合わせによるATmegaET64M1は宇宙環境での多くの組み込み制御の応用に対して高度な柔軟性と対費用効果をもたらす強力なマイクロコントローラです。

ATmegaET64M1 AVRはCコンハペイラ、マクロ アセンフ・ラ、デ・ハ・ッカ、、シミュレータ、インサーキット エミューレータ、評価キットを含む専用のプログラム及びシステム開発ツールで支援されます。

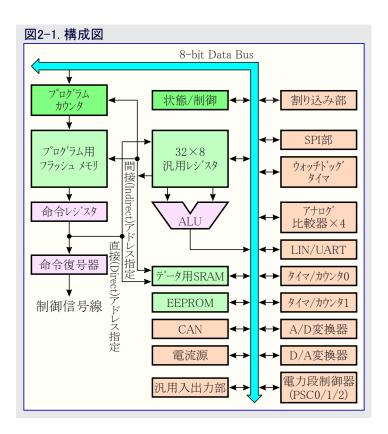

# 2. 構成図

# 3. ピン構成

# 3.1. ピン説明

# 表3-1. ピン割り当て説明

| ピン | I. しフ <u>吉</u> | 形式  | C 11/0-71                                            | 名称、機能                                                                                                                          |

|----|----------------|-----|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 番号 | ピン名            | 分類  | 標準機能                                                 | 代替機能                                                                                                                           |

| 4  | VCC            | 電源  | デジタル電力供給:                                            |                                                                                                                                |

| 5  | GND            | 電源  | 接地: 0V基準                                             |                                                                                                                                |

| 19 | AVCC           | 電源  |                                                      | 変換器、D/A変換器、電流源用の電圧を供給します。例えADCやDACが使われなくても外部的<br>域通過濾波器(ローパスフィルタ)を通してVCCに接続されるべきです。                                            |

| 20 | AGND           | 電源  | アナログ接地: アナログ部用0V基準                                   |                                                                                                                                |

| 21 | AREF           | 電源  | アナログ基準電圧: これはA/D変換器用基準電圧です。                          | 出力として、ISRC(電流源出力)として使われ得ます。                                                                                                    |

| 8  | PB0            | I/O | ┃<br>・ポートBは(ビット毎選択の)内蔵プ                              | MISO(SPI主入力/従出力), PSCOUT2A(PSC2出力A), PCINTO(ピン変化割り込み0入力)                                                                       |

| 9  | PB1            | I/O | ルアップ。抵抗付き8ビット双方向入                                    | MOSI(SPI主出力/従入力), PSCOUT2B(PSC2出力B), PCINT1(ピン変化割り込み1入力)                                                                       |

| 16 | PB2            | I/O | 出力ポートです。ポートB出力緩衝<br>部は共に高い吐き/吸い能力の                   | ADC5(アナログ 入力チャネル5), INT1(外部割り込み1入力), ACMPN0(アナログ 比較器0反転入力), PCINT2 (ピン変化割り込み2入力)                                               |

| 23 | PB3            | I/O | 対称駆動特性です。入力時に                                        | AMP0-(アナログ: 差動増幅器0反転入力), PCINT3 (ピン変化割り込み3入力)                                                                                  |

| 24 | PB4            | I/O |                                                      | AMP0+(アナログ・差動増幅器0非反転入力), PCINT4(ピン変化割り込み4入力)                                                                                   |

| 26 | PB5            | I/O | 部的にLowへ引き込まれたポートBピンには吐き出し電流が流れま                      | ADC6(アナログ 入力チャネル6), INT2(外部割り込み2入力), ACMPN1(アナログ 比較器1反転入力), AMP2-(アナログ 差動増幅器2反転入力), PCINT5(ピン変化割り込み5入力)                        |

| 27 | PB6            | I/O | す。クロックが動作していなくても、<br>'リセット条件活性時にポートBピンは              | ADC7(アナログ入力チャネル7), PSCOUT1B(PSC1出力B), PCINT6(ピン変化割り込み6入力)                                                                      |

| 28 | PB7            | I/O | Hi-Zです。                                              | SCK(SPIクロック入出力), ADC4(アナログ入力チャネル4), PSCOUT0B(電力段制御器(PSC)0出力B), PCINT7(ピン変化割り込み7入力)                                             |

| 30 | PC0            | I/O |                                                      | INT3(外部割り込み3入力), PSCOUT1A(PSC1出力A), PCINT8(ピン変化割り込み8入力)                                                                        |

| 3  | PC1            | I/O | <br>  ポートCは(ビット毎選択の)内蔵プ                              | OC1B(タイマ/カウンタ1比較B出力), PSCIN1(PSC1デジタル入力), SS_A(代替SPI従装置選択入力), PCINT9(ピン変化割り込み9入力)                                              |

| 6  | PC2            | I/O | ルアップ。抵抗付き8ピット双方向入                                    | T0(タイマ/カウンタ0外部クロック入力), TXCAN(CAN送信出力), PCINT10(ピン変化割り込み10入力)                                                                   |

| 7  | PC3            | I/O | 出力ポートです。ポートC出力緩衝部は共に高い吐き/吸い能力の                       | T1(タイマ/カウンタ1外部クロック入力), RXCAN(CAN受信出力), ICP1B(タイマ/カウンタ1捕獲起動代替入力), PCINT11(ピン変化割り込み11入力)                                         |

| 17 | PC4            | I/O | 対称駆動特性です。入力時に<br>プルアップ抵抗が有効の場合、外<br>部的にLowへ引き込まれたポート | ADC8(アナログ 入力チャネル8), AMP1-(アナログ 差動増幅器1 反転入力), ACMPN3(アナログ 比較器3 反転入力), PCINT12(ピン変化割り込み12入力)                                     |

| 18 | PC5            | I/O | Cピンには吐き出し電流が流れます。クロックが動作していなくても、                     | ADC9(アナログ入力チャネル9), AMP1+(アナログ差動増幅器1非反転入力), ACMP3(アナログ比較器3非反転入力), PCINT13(ピン変化割り込み13入力)                                         |

| 22 | PC6            | I/O | リセット条件活性時にポートCピンは<br>Hi-Zです。                         | ADC10(アナログ) 入力チャネル10), ACMP1(アナログ) 比較器1非反転入力), PCINT14(ピン変化割り込み14入力)                                                           |

| 25 | PC7            | I/O |                                                      | D2A(D/A変換器出力), AMP2+(アナロケ・差動増幅器2非反転入力), PCINT15(ピン変化割り込み15入力)                                                                  |

| 29 | PD0            | I/O |                                                      | PSCOUT0A(PSC0出力A), PCINT16(ピン変化割り込み16入力)                                                                                       |

| 32 | PD1            | I/O |                                                      | CLKO(システム クロック出力), PSCINO(PSCOデン・タル入力), PCINT17(ピン変化割り込み17入力)                                                                  |

| 1  | PD2            | I/O | ポートDは(ビット毎選択の)内蔵プ<br>ルアップ抵抗付き8ビット双方向入                | OC1A(タイマ/カウンタ1比較A出力), MISO_A(プログラミングと代替SPI主入力/従出力), PSCIN2(PSC2 デングル入力), PCINT18(ピン変化割り込み18入力)                                 |

| 2  | PD3            | I/O | 出力ポートです。ポートD出力緩衝<br>部は共に高い吐き/吸い能力の<br>対称駆動特性です。入力時に  | TXD(UART送信データ出力), TXLIN(LIN送信出力), OC0A(タイマ/カウンタ0比較A出力), SS (SPI従装置選択入力), MOSI_A(プログラミングと代替SPI主側出力/従側入力), PCINT19(ピン変化割り込み19入力) |

| 12 | PD4            | I/O | プルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートDtプには吐き出し電流が流れま       | (アナロケ)入力チャネル1), SCK_A(プログラミングと代替SPIクロック入出力), PCINT20 (ピン変化割り込み20                                                               |

| 13 | PD5            | I/O | す。クロックが動作していなくても、<br>リセット条件活性時にポートDピンは               | ADC2(アナロケ)入力チャネル2), ACMP2(アナロケ)比較器2非反転入力), PCINT21(ピン変化割り込み21                                                                  |

| 14 | PD6            | I/O | Hi-Zです。                                              | ADC3(アナログ 入力チャネル3), ACMPN2(アナログ 比較器2反転入力), INTO(外部割り込み0入力), PCINT22(ピン変化割り込み22入力)                                              |

| 15 | PD7            | I/O |                                                      | ACMP0(アナロケ)比較器0非反転入力), PCINT23(ピン変化割り込み23入力)                                                                                   |

| 2  | PE0            | I/O | ポートEは(ビット毎選択の)内蔵プルアップ。抵抗付き3ピット双方向入出                  | RESET(外部リセット入力), OCD(内蔵デバックWIRE機能入出力), PCINT24(ピン変化割り込み24入力)                                                                   |

| 10 | PE1            | I/O | 力ポートです。ポートE出力緩衝部                                     | XTAL1(発振増幅器入力), OC0B(タイマ/カウンタ0比較B出力), PCINT25(ピン変化割り込み25入力)                                                                    |

| 11 | PE2            | I/O | は共に高い吐き/吸い能力の対                                       | XTAL2(発振増幅器出力), ADC0(アナログ入力チャネル0), PCINT26(ピン変化割り込み26入力)                                                                       |

|    |                |     | 称駆動特性です。入力時にプル                                       |                                                                                                                                |

アップ抵抗が有効の場合、外部的にLowへ引き込まれたポートEピンには吐き出し電流が流れます。クロックが動作していなくても、リセット条件活性時にポートE ピンはHi-Zです。

RSTDISBLヒュース'がプログラム(0)されると、PE0はI/Oピンとして使われます。PE0の電気的特性がポートEの他のピンのそれらと違うことに注意してください。

RSTDISBLヒューズが非プログラム(1)の場合、PE0はリセット入力として使われます。クロックが動いていなくても、最小パルス幅より長いこのピンのLowレベルはリセットを生成します。

クロック選択ヒューズ設定に依存して、PE1は発振器反転増幅器への入力と内部クロック操作回路への入力として使えます。

クロック選択ヒューズ設定に依存して、PE2は発振器反転増幅器からの出力として使えます。

# 4. 注文情報

| テ゛ハ゛イス       | 速度(MHz) | 電源電圧     | 注文符号               | 外囲器    | 供給          |

|--------------|---------|----------|--------------------|--------|-------------|

| ATmegaET64M1 | 8       | 3.0~3.6V | ATmegaET64M1-MA-HP | TQFP32 | 高信頼性プラスティック |

# 5. 資料

包括的なデータシート、応用記述、開発ツール群はhttp://www.microchip.com/design-centers/8-bit/microchip-avr-mcusでのダウンロードで利用可能です。

# 6. コード例について

この資料はデバイスの様々な部分の使用法を手短に示す簡単なコード例を含みます。全てのCコンパイラ製造業者がヘッタ・ファイル内にビット定義を含めるとは限らず、またCでの割り込みの扱いがコンパイラに依存することに注意してください。より多くの詳細についてはCコンパイラの資料で確認してください。

これらのコート・例はアセンブルまたはコンハ・イルに先立ってデバイス定義ファイルがインクルートされることが前提です。拡張I/O領域に配置したI/Oレジスタに対し、IN, OUT, SBIS, SBIC, CBI, SBI命令は拡張I/O領域へのアクセスを許す命令に置き換えられなければなりません。代表的にはSBRS, SBRC, SBR, CBR命令と組み合わせたLDS, STS命令です。

# 7. AVR CPU 17

# 7.1. 概要

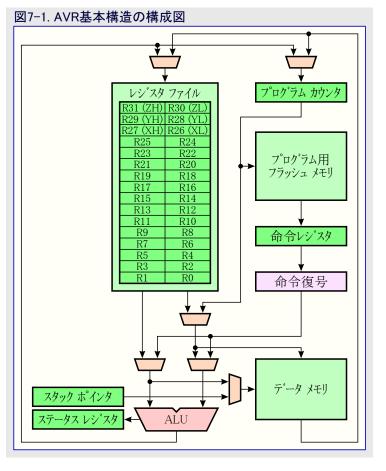

ここでは一般的なAVRコア構造について説明します。このCPUコアの主な機能は正しいプログラム実行を保証することです。従ってCPU はメモリ アクセス、計算実行、周辺制御、割り込み操作ができなければなりません。

最大効率と平行処理のため、AVRはプログラムとデータに対してメモリとハ、スを分離するハーハート・構造を使います。プログラムメモリ内の命令は、単一段のハーイプラインで実行されます。1命令の実行中に次の命令がプログラムメモリから事前取得されます。この概念は全部のクロック周期で命令実行を可能にします。プログラムメモリは実装書き換え可能なフラッシュメモリです。

高速レジスタファイルは1クロック周期アクセスの32個の8ビット長汎用レジスタを含みます。これは1クロック周期ALU(Arithmetic Logic Unit)操作を許します。代表的なALU操作では2つのオペラントがレジスタファイルからの出力で、1クロック周期内でその操作が実行され、その結果がレジスタファイルに書き戻されます。

32個中の6つのレジスタは効率的なアトレス計算ができるデータ空間アトレス指定用に、3つの16ビット長間接アトレスポーインタ用レジスタとして使われます。これらアトレスポーインタの1つはプログラム用フラッシュメモリ内の定数表参照用アトレスポーインタとしても使えます。これら16ビット長付加機能レジスタはX,Y,Zレジスタで、この項内で後述されます。

ALUはレシ、スタ間またはレシ、スタと定数間の算術及び論理操作を支援します。単一レシ、スタ操作もALUで実行できます。算術演算操作後、操作結果についての情報を反映するためにステータスレジスタ(SREG)が更新されます。

プログラムの流れは条件/無条件分岐や呼び出し命令によって提供され、全アドレス空間を直接アドレス指定できます。AVR命令の多くは16ビット語(ワート)形式です。全てのプログラムメモリのアドレスは(訳注:定数のみを除き)16または32ビット長命令を含みます。

プログラム用フラッシュ メモリ空間はプート プログラム領域と応用プログラム 領域の2つに分けられます。 どちらの領域にも書き込み禁止や 読み書き防止用の専用施錠ビットがあります。 応用フラッシュ メモリ領

域内に書き込むSPM命令はブートプログラム領域内に属さ(存在し)なければなりません。

割り込みやサブルーチン呼び出し中、戻りアトンスを示すプログラム カウンタ(PC)はスタックに保存されます。スタックは一般的なデータ用SRAM上に実際には割り当てられ、従ってスタック容量は全SRAM容量とSRAM使用量でのみ制限されます。全ての使用者プログラムはリセット処理ルーチンで(サブルーチン呼び出しや割り込みが実行される前に)、スタック ホーインタ(SP)を初期化しなければなりません。SPはI/O空間で読み書きアクセスが可能です。データ用SRAMはAVR構造で支援される5つの異なるアトンス指定種別を通して容易にアクセスできます。

AVR構造に於けるメモリ空間は全て直線的な普通のメモリ配置です。

柔軟な割り込み部にはI/O空間の各制御レシ、スタとステータスレシ、スタ(SREG)の特別な全割り込み許可(I)ビットがあります。全ての割り込みは割り込みへ、クタ表に個別の割り込みへ、クタを持ちます。割り込みには割り込みへ、クタ表の位置に従う優先順があります。下位側割り込みへ、クタアドレスが高い優先順位です。

I/Oメモリ空間は制御レシ、スタ、SPI、他のI/O機能としてCPU周辺機能用の647トレスを含みます。I/Oメモリは直接またはレシ、スタ ファイルの次のデータ空間位置\$20~\$5Fとしてアクセスできます。加えて、本デバイスにはST/STS/STDとLD/LDS/LDD命令だけ使えるSRAM内の\$60~\$FFに拡張I/O空間があります。

# 7.2. ALU (Arithmetic Logic Unit)

高性能なAVRのALUは32個の全汎用レジスタに直接接続され動作します。汎用レジスタ間または汎用レジスタと即値間の演算操作は単一クロック周期内で実行されます。ALU操作は算術演算、論理演算、ビット操作の3つの主な種類に大別されます。符号付きと符号なし両方の乗算と固定小数点形式を支援する、乗算器(乗算命令)を提供する構造の実装(製品)があります。詳細記述については「命令要約」章をご覧ください。

関連リンク 32. 命令要約

### 7.3. ステータス レジスタ

ステータスレジスタは最も直前に実行した演算命令の結果についての情報を含みます。この情報は条件処理を行うためのプログラムの流れ変更に使えます。ステータスレジスタは「命令一式参考書」で詳述したように、全てのALU操作後、更新されることに注目してください。これは多くの場合でそれ用の比較命令使用の必要をなくし、高速でより少ないコードに帰着します。

ステータス レジスタは割り込み処理ルーチン移行時の保存と割り込みからの復帰時の回復(復帰)が自動的に行われません。これはソフトウェアによって扱われなければなりません。

# 7.3.1. SREG - ステータス レジスタ (Status Register)

名称: SREG 変位: \$5F(\$3F) リセット: \$00

特質:I/O特定命令でI/Oレシ、スタとしてアクセスする時の変位アドレスは\$3Fです。

LD系とST系の命令を使い、データ空間としてI/Oレジスタをアクセスする時は、提供された変位が使われなければなりません。I/O特定命令のINとOUTを使う時は、この変位が\$20で減算され、I/Oアドレスの変位は\$00~\$3F内になります。

| ピット    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

|        | I   | T   | Н   | S   | V   | N   | Z   | С   |

| アクセス種別 | R/W |

| リセット値  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

# ● ビット7 - I: 全割り込み許可 (Global Interrupt Enable)

全割り込み許可ビットは割り込みが許可されるために設定(1)されなければなりません。その時の個別割り込み許可制御は独立した制御レジスタで行われます。全割り込み許可ビットが解除(0)されると、個別割り込み許可設定に拘らず、どの割り込みも許可されません。I ビットは割り込みが起こった後、ハードウェアによって解除(0)され、後続の割り込みを許可するため、RETI命令によって設定(1)されます。I ビットは「命令一式参考書」で記述されるようにSEIやCLI命令で応用(プログラム)によって設定(1)や解除(0)もできます。

# ● ビット6 - T: ビット変数 (Bit Copy Storage)

ビット複写命令、BLD(Bit LoaD)とBST(Bit STore)は操作したビットの転送元または転送先として、このTビットを使います。レジスタ ファイルのレジスタからのビットはBST命令によってTに複写でき、TのビットはBLD命令によってレジスタ ファイルのレジスタ内のビットに複写できます。

# • ビット5 - H : ハーフキャリー フラク (Half Carry Flag)

ハーフキャリー(H)フラグはいくつかの算術操作でのハーフキャリーを示します。ハーフキャリーはBCD演算に有用です。詳細情報については「命令要約」をご覧ください。

# ● ビット4 - S: 符号 (Sign Bit, S= N Ex-OR V)

Sフラグは常に負(N)フラグと2の補数溢れ(V)フラグの排他的論理和です。詳細情報については「命令要約」をご覧ください。

# ● ビット3 - V: 2の補数溢れフラグ(2's Complement Overflow Flag)

2の補数溢れ(V)フラグは2の補数算術演算を支援します。詳細情報については「命令要約」をご覧ください。

### ビット2 - N: 負フラク (Negative Flag)

負(N)フラグは算術及び論理操作での負の結果(MSB=1)を示します。詳細情報については「命令要約」をご覧ください。

### ヒット1 - Z: セロフラク (Zero Flag)

ゼロ(Z)フラグは算術及び論理操作でのゼロ(0)の結果を示します。詳細情報については「命令要約」をご覧ください。

# ビット0 - C: キャリー フラク (Carry Flag)

キャリー(C)フラケ、は算術及び論理操作でのキャリー(またはボロー)を示します。詳細情報については「命令要約」をご覧ください。

# 7.4. 汎用レジスタファイル

このレシブスタファイルはAVRの増強したRISC命令群用に最適化されています。必要な効率と柔軟性を達成するために、次の入出力機構がレジスタファイルによって支援されます。

- ・1つの8ビット出力オペラントと1つの8ビットの結果入力

- ・2つの8ビット出力オペラントと1つの8ビットの結果入力

- ・2つの8ビット出力オペラントと1つの16ビットの結果入力

- ・1つの16ビット出力オペラントと1つの16ビットの結果入力

レジスタファイルを操作する殆どの命令は全てのレジスタに直接アクセスし、それらの殆どは単一周期命令です。図で示されるように各レジスタは使用者データ空間の最初の32位置へ直接的に配置することで、それらはデータメモリアトレスも割り当てられます。例え物理的にSRAM位置として実装されていなくてもX,Y,Zレジスタ(ポインタ)がレジスタファイル内のどのレジスタの指示にも設定できるように、このメモリ構成は非常に柔軟なレジスタのアクセスを提供します。

| 図7-2. A    | AVR CPU 汎用レジスタ村 | 構成図                                 |

|------------|-----------------|-------------------------------------|

|            | 7 0             | アドレス                                |

|            | R0              | \$00                                |

|            | R1              | \$01                                |

|            | R2              | \$02                                |

|            | ₹               |                                     |

|            | R13             | \$0D                                |

|            | R14             | \$0E                                |

| ्रात इस    | R15             | \$0F                                |

| 汎用<br>レジスタ | R16             | \$10                                |

| ファイル       | R17             | \$11                                |

| , , , ,    | ?               |                                     |

|            | R26             | \$1A<br>\$1B Xレシブスター 下位バイト<br>上位バイト |

|            | R27             | \$1B <b>ハッハ</b> 上位バイト               |

|            | R28             | \$1C VISCAR 下位ハイ :                  |

|            | R29             |                                     |

|            | R30             | \$1E Zレジスタ 下位バイト                    |

|            | R31             | \$1F <b>2レッパ</b> 上位バイト              |

|            |                 |                                     |

# 7.4.1. Xレシ、スタ、Yレシ、スタ、Zレシ、スタ

R26~R31レジスタには通常用途の使用にいくつかの追加機能があります。これらのレジスタはデータ空間の間接アトンス指定用の16ビットアトンスポインタです。3つのX,Y,Z間接アトンスレジスタは図で記載したように定義されます。

種々のアドレス指定種別で、これらのアドレス レジスタは固定変位、自動増加、自動減少としての機能を持ちます(詳細については「命令ー式参考書」をご覧ください)。

関連リンク 32. 命令要約

| 図7-3. X,Y | ′,Zレシ | バスタ構成図  |     |         |   |

|-----------|-------|---------|-----|---------|---|

|           | 15    | XH (上位) |     | XL (下位) | 0 |

| X レジスタ    | 7     | R27     | 0 7 | R26     | 0 |

|           | 15    | YH (上位) |     | YL (下位) | 0 |

| Yレジスタ     | 7     | R29     | 0 7 | R28     | 0 |

|           | 15    | ZH (上位) |     | ZL (下位) | 0 |

| Z レジスタ    | 7     | R31     | 0 7 | R30     | 0 |

|           |       |         |     |         |   |

# 7.5. スタック ホペインタ

スタックは主に一時データの保存、局所変数の保存、割り込みとサブルーチン呼び出し後の戻りアドレスの保存に使われます。スタックは高位メモリから低位メモリへ伸長するように実行されます。スタック ポーンタ レジ スタは常にこのスタックの先頭(訳注:次に使われるべき位置)を指し示します。スタック ポーインタはサブルーチンや割り込みのスタックが配置されるデータSRAMのスタック領域を指し示します。スタックPUSH命令はスタックポーンタを減らします。

データSRAM内のスタック空間はサブルーチン呼び出しの実行や割り込みの許可の何れにも先立ってプログラムによって定義されなければなりません。初期スタック ポーインタ値は内部SRAMの最終アドレスに等しく、スタック ポーインタはSRAMの先頭以上に設定されなければなりません。 スタック ポーインタの詳細については表をご覧ください。

| ± 7 4  | 7 4 4 | ⊥°. | $h \rightarrow h \rightarrow$ |

|--------|-------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 衣 /⁻Ⅰ. | スタツソ  | 小子  | ひり命令                                                                                                                                          |

| 衣 / ニ 1、 ヘメソソ ホ イノメ 叩 ヤ |                           |                                           |  |  |  |  |

|-------------------------|---------------------------|-------------------------------------------|--|--|--|--|

| 命令 スタック ポインタ 内容         |                           |                                           |  |  |  |  |

| PUSH                    | -1                        | データがスタック上に押し込まれます。                        |  |  |  |  |

| CALL,ICALL,RCALL        | -2                        | サブルーチン呼び出しまたは割り込みでの戻りアドレスがスタック上に押し込まれます。  |  |  |  |  |

| POP                     | POP +1 データがスタックから引き出されます。 |                                           |  |  |  |  |

| RET,RETI                | +2                        | サブルーチンまたは割り込みからの復帰での戻りアドレスがスタックから引き出されます。 |  |  |  |  |

AVRのスタック ポインタはI/O空間内の2つの8ビット レジスタとして実装されます。実際に使われるビット数は(そのデバイス)実装に依存します。SPLだけが必要とされる程に小さいAVR構造の実装(デバイス)のデータ空間があることに注意してください。その場合、SPHレジスタは存在しません。

# 7.5.1. SPH,SPL - スタック ホーインタ レシ スタ上位/下位バート (Stack Pointer Register Low and High byte)

名称: SPHとSPL(SP) 変位: \$5D(\$3D)

**リセット**: \$10FF

特質:I/O特定命令でI/Oレシ、スタとしてアクセスする時の変位アトンスは\$3Dです。

SPHとSPLのレジスタ対は16ビット値のSPを表します。下位バイト[7~0](接尾辞L)は変位原点でアクセスできます。上位バイト[15~8](接尾辞H)は変位+1でアクセスすることができます。16ビット レジスタの読み書きのより多くの詳細については「16ビット レジスタのアクセス」をご覧ください。

LD系とST系の命令を使い、データ空間としてI/Oレジスタをアクセスする時は、提供された変位が使われなければなりません。I/O特定命令のINとOUTを使う時は、この変位が\$20で減算され、I/Oアドレスの変位は\$00~\$3F内になります。

| <b>ビット</b> | 15  | 14  | 13  | 12  | 11  | 10     | 9   | 8   |

|------------|-----|-----|-----|-----|-----|--------|-----|-----|

|            | -   | _   | -   |     |     | SP12∼8 |     |     |

| アクセス種別     | R   | R   | R   | R/W | R/W | R/W    | R/W | R/W |

| リセット値      | 0   | 0   | 0   | 1   | 0   | 0      | 0   | 0   |

| ヒ"ット       | 7   | 6   | 5   | 4   | 3   | 2      | 1   | 0   |

|            |     |     |     | SP  | 7~0 | ,      |     |     |

| アクセス種別     | R/W | R/W | R/W | R/W | R/W | R/W    | R/W | R/W |

| リセット値      | 1   | 1   | 1   | 1   | 1   | 1      | 1   | 1   |

### ● ビット12~0 - SP12~0: スタック ポインタ値 (Stack Pointer value)

SPHとSPLはSPに組み合わされます。

# 7.6. 16ビットレジスタのアクセス

AVRのデータ バスは8ビット幅で、故に16ビット レジスタのアクセスは非分断操作が必要です。これらのレジスタは2つの読みまたは書きの操作を用いてバイト アクセスされなければなりません。16ビット レジスタは16ビット バスを用いて8ビット バスと1つの一時レジスタに接続されます。

書き込み操作については、16ビット レジスタの上位バイトが下位バイトに先立って書かれなければなりません。そしてその上位バイトは一時レジスタに書かれます。16ビット レジスタの下位バイトが書かれる時に、同じクロック周期で一時レジスタが16ビット レジスタの上位バイトに複写されます。

読み込み操作については、16ビット レジスタの下位バイトが上位バイトに先立って読まれなければなりません。CPUによって下位バイトが 読まれる時に、下位バイトが読まれるのと同じクロック周期で16ビット レジスタの上位バイトが一時レジスタに複写されます。上位バイト読み込 みは今やこの一時レジスタから読みます。

これはレジスタの読み書き時に16ビット レジスタの上位と下位のバイトが常に同時にアクセスされることを保証します。

非分断16ビット レジスタ読み書き操作中に割り込みが起動されて同じレジスタをアクセスする場合、この時間制限手順を不正にし得ます。これを防ぐために、16ビット レジスタの読み書き時に割り込みを禁止することができます。

(訳注) 原書の本項の記述はXMEGA用の記述をそのまま複写したものと思われます。そのため、書き込み操作の上位と下位のバイの書き順が他のAVRと逆になっています。これによって、書き込み操作に関する他の殆どの部分での記述と矛盾が生じています。本書ではこの書き込み操作に関する書き順を矛盾が生じないように、本項と関連する他の一部の記述を修正しています。また、8.6.1.項と重複しています。

# 7.7. 命令実行タイミング

本項は命令実行の一般的なアクセスタイミングの概念を記述します。AVR CPUはチップ(デバイス)用に選択したクロック元から直接的に生成したCPUクロック(clkcPU)によって駆動されます。内部クロック分周は使われません。

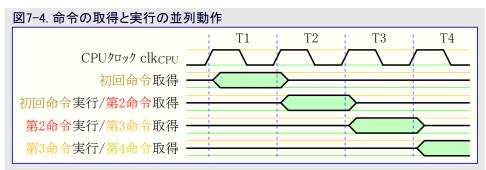

右図はハーハート・構造と高速アクセスレジスタファイルの概念によって可能とされる並列の命令取得と命令実行を示します。これは機能対費用、機能対クロック、機能対電源部に関する好結果と対応するMHzあたり1MIPSを達成するための基本的なパイプラインの概念です。

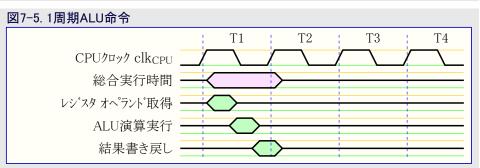

右図はレジスタファイルに対する内部タイミンケ の概念を示します。単一クロック周期で2つの レシ、スタオペプント、を使うALU操作が実行さ れ、その結果が転送先レシ、スタへ書き戻され ます。

# 7.8. リセットと割り込みの扱い

AVRは多くの異なる割り込み元を提供します。これらの割り込みと独立したリセット ベクタ各々はプログラム メモリ空間内に独立したプログラム ベクタを持ちます。全ての割り込みは割り込みを許可するために、ステータス レジスタ(SREG)の全割り込み許可(I)ビットと共に論理1が書かれなければならない個別の許可ビットを割り当てられます。BLB02またはBLB12 ブート施錠ビットがプログラム(0)されると、プログラム カウンタ値によっては割り込みが自動的に禁止されるかもしれません。この特質はソフトウェア保護を改善します。

既定でのプログラム メモリ空間の最下位アトンスはリセットと割り込みへクタとして定義されます。それらは決められた優先順位を持ちます。下位側アトンスがより高い優先順位です。リセットが最高優先順位で次がアナログ比較器0(ANACOMP0)割り込みです。割り込みへクタはMCU制御レン、スタ(MCUCR)の割り込みへクタ選択(IVSEL)と、ットの設定(1)によってブートフラッシュ領域先頭へ移動できます。リセットへクタもBOOTRSTヒュース、のプログラム(0)によってブートフラッシュ領域先頭へ移動できます。

割り込みが起こると全割り込み許可(I)ビットが解除(0)され、全ての割り込みは禁止されます。使用者ソフトウェアは多重割り込みを許可するため、全割り込み許可(I)ビットへ論理1を書けます。その後全ての許可した割り込みが現在の割り込みルーチンで割り込めます。全割り込み許可(I)ビットは割り込みからの復帰(RETI)命令が実行されると、自動的に設定(1)されます。

根本的に2つの割り込み形式があります。

1つ目の形式は割り込み要求フラグを設定(I)する事象によって起動されます。これらの割り込みでは割り込み処理ルーチンを実行するために、プログラムカウンタは対応する現実の割り込みへブタを指示し、ハードウェアが対応する割り込み要求フラグを解除(0)します。割り込み要求フラグでは解除(0)されるべきフラグのビット位置へ論理1を書くことによっても解除(0)できます。対応する割り込み許可ビットが解除(0)されている間に割り込み条件が起こると、割り込み要求フラグが設定(1)され、割り込みが許可されるか、またはこのフラグがソフトウェアによって解除(0)されるまで記憶(保持)されます。同様に、全割り込み許可(I)ビットが解除(0)されている間に1つまたはより多くの割り込み条件が起こると、対応する割り込み要求フラグが設定(1)されて全割り込み許可(I)ビットが設定(1)されるまで記憶され、その(I=1)後で優先順に従って実行されます。

2つ目の割り込み形式は割り込み条件が存在する限り起動し(続け)ます。これらの割り込みは必ずしも割り込み要求フラグを持っているとは限りません。割り込みが許可される前に割り込み条件が消滅すると、この割り込みは起動されません。

AVRが割り込みから抜け出すと常に主プログラムへ戻り、何れかの保留割り込みが扱われる前に1つ以上の命令を実行します。

ステータス レジ スタ(SREG)は割り込みルーチンへ移行時の保存も、復帰時の回復も自動的に行われません。これはソフトウェアによって扱われなければなりません。

割り込みを禁止するためにCLI命令を使うと、割り込みは直ちに禁止されます。CLI命令と同時に割り込みが起こっても、CLI命令後に割り込みは実行されません。次例は時間制限EEPROM書き込み手順中に割り込みを無効とするために、これがどう使えるかを示します。

```

アセンブリ言語プログラム例

R16, SREG

;ステータス レシ スタを保存

IN

;EEPROM書き込み手順中割り込み禁止

CLT

SBI

EECR, EEMPE

;EEPROM主書き込み許可

SBT

EECR, EEPE

;EEPROM書き込み開始

OUT

SREG, R16

;ステータスレジスタを復帰

C言語プログラム例

/* ステータス レジ スタ保存変数定義 */

char cSREG;

/* ステータス レシ スタを保存 */

cSREG = SREG;

/* EEPROM書き込み手順中割り込み禁止*/

_disable_interrupt();

EECR = (1 < EEMPE);

/* EEPROM主書き込み許可 */

EECR \mid = (1 << EEPE);

/* EEPROM書き込み開始 */

SREG = cSREG:

/* ステータス レシ スタを復帰 */

注: 「コート 例について」を参照してください。

```

割り込みを許可するためにSEI命令を使うと、次例で示されるようにどの保留割り込みにも先立ってSEI命令の次の命令が実行されます。

注: SLEEP命令までは割り込み禁止、保留割り込み実行前に休止形態へ移行します。

**注:**「コート 例について」を参照してください。

**関連リンク** 28. MEMPROG - メモリ プロクラミンク

27. BTLDR - ブートローダ支援 - 書き込み中読み出し可能な自己プログラミング

# 7.8.1. 割り込み応答時間

許可した全てのAVR割り込みに対する割り込み実行応答は最小4クロック周期です。4クロック周期後、実際の割り込み処理ルーチンに対するプログラム ヘブタ アドレスが実行されます。この4クロック周期時間中にプログラム カウンタ(PC)がスタック上に保存(プッシュ)されます。このヘブタは標準的に割り込み処理ルーチンへの無条件分岐で、この分岐は3クロック周期要します。複数周期命令実行中に割り込みが起こると、その割り込みが扱われる前に、この命令が完了されます。MCUが休止形態の時に割り込みが起こると、割り込み実行応答時間は4クロック周期増やされます。この増加は選択した休止形態からの起動時間に加えてです。割り込み処理ルーチンからの復帰は4クロック周期要します。これらの4クロック周期中、プログラム カウンタ(PC:2ハブト)がスタックから取り戻され(ポップ)、スタック ポインタは増加され(+2)、ステータス レジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されます。

# 8. AVRのメモリ

# 8.1. 概要

本項は本デバイスの各種メモリを記述します。AVR構造にはプログラム メモリ空間とデータ メモリ空間の2つの主なメモリ空間を持ちます。加えて本デバイスはデータ保存用EEPROMメモリが特徴です。全てのメモリ空間は一般的な直線的アドレスです。

# 8.2. 実装書き換え可能なプログラム用フラッシュ メモリ

ATmegaET64M1はプログラム保存用に実装書き換え可能な64Kバイトのフラッシュメモリをチップ上に含みます。全てのAVR命令が16または32ビット幅のため、このフラッシュメモリは32K×16ビットとして構成されます。

ATmegaET64M1のプログラム カウンタ(PC)は15ビット幅、故に32Kプログラム メモリ位置のアドレス指定です。ブートプログラム領域の操作と関係

するソフトウェア保護用ブート施錠ビットは「BTLDR - ブート ローダ - 書き込み中読み出し可能な自己プログラ ミング」で詳細に記述されます。SPIピンを使うフラッシュ データ直列書き込みの記述については「MEMPRO G - メモリ プログラミング」を参照してください。

定数表はプログラム用メモリ取得(LPM)命令を使って全てのプログラムメモリアドレス空間に配置することができます。

命令の取得と実行のタイミング図は「命令実行タイミング」で示されます。

関連リンク 27. BTLDR - ブートロータ 支援 - 書き中読み可能な自己プログラミング

28. MEMPROG - メモリ プログラミング

7.7. 命令実行タイミング

# 8.3. データ用SRAMメモリ

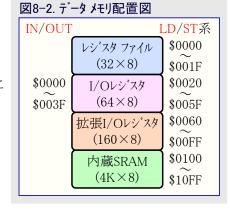

下図は本デバイスのSRAMメモリ構成方法を示します。

本デバイスはINやOUT命令で予約した64位置で支援されるよりも多くの周辺機能部を持つ複合マイクロコントローラです。SRAM(データ空間)内\$60~\$FFの拡張I/O空間に対してはLD/LDS/LDDとST/STS/STD命令だけが使えます。

下位4352データメモリ位置はレジスタファイル、I/Oメモリ、拡張I/Oメモリ、内部データSRAMに充てます。先頭32位置はレジスタファイル、次の64位置は標準I/Oメモリ、その次の160位置は拡張I/Oメモリ、そして次の4096位置は内部データSRAMに充てます。

5つの異なるアドレス指定種別でデータ メモリ(空間)を網羅します。

- 直接

- 直接アドレス指定はデータ空間全体に届きます。

- ・変位付き間接

- 変位付き間接動作はYまたはZレジスタで与えられる基準アドレスからの63アドレス位置に届きます。

- 間接

- レジスタファイル内のR26~R31レジスタは間接アトレス指定ポインタ用レジスタが特徴です。

- 事前減少付き間接

- (使われる)X,Y,Zアドレス レジスタが減少(-1)されます。

- 事後増加付き間接

- (使われる)X,Y,Zアドレス レジスタが増加(+1)されます。

本デバイスの32個の汎用レジスタ、64個のI/Oレジスタ、160個の拡張I/Oレジスタ、4Kバイトのデータ用内蔵SRAMはこれら全てのアドレス指定種別を通して全部アクセスできます。

# 8.3.1. データ メモリ アクセス タイミング

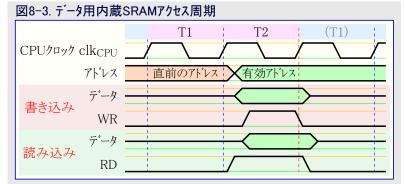

データ用内蔵SRAMアクセスは右図で記載されるように2clk<sub>CPU</sub> 周期で実行されます。

(**訳注**) 内蔵SRAMのアクセスを含む代表的な命令はT1,T2の 2周期で実行され、T1で対象アトレスを取得/(算出)/ 確定し、T2で実際のアクセスが行われます。後続する (T1)は次の命令のT1です。

# 8.4. データ用EEPROMメモリ

ATmegaET64M1は2Kバイトのデータ用EEPROMを含みます。それは単一バイトが読み書きできる分離したデータ空間として構成されます。CPUとEEPROM間アクセスは以降のEEPROMアトレスレジ、スタ、EEPROMデータレジ、スタ、EEPROM制御レジ、スタで詳細に記述されます。SPIまたは並列プログラミングでのEEPROMプログラミングの詳細な記述は関連リンクをご覧ください。

関連リンク 28. MEMPROG - メモリ プログラミング

### 8.4.1. EEPROMアクセス

EEPROMアクセスレジスタはI/O空間でアクセス可能です。

EEPROM書き込み(訳注:原文はアクセス)時間は表8-2.で与えられます。(書き込みは)自己タイシンが機能ですが、使用者ソフトウェアは次バイトが書ける時を検知してください。使用者コートがEEPROMに書く命令を含む場合、いくつかの予防処置が取られねばなりません。厳重に濾波した電源では電源投入/切断でVCCが緩やかに上昇または下降しそうです。これはデバイスが何周期かの時間、使われるクロック周波数に於いて最小として示されるより低い電圧で走行する原因になります。これらの状態で問題を避ける方法の詳細については以下の「8.4.2. EEPROMデータ化けの防止」を参照してください。

予期せぬEEPROM書き込みを防止するため特別な書き込み手順に従わなければなりません。この詳細についてはEEPROM制御レジスタの説明と「非分離バー書き込み」と「分離バー書き込み」を参照してください(訳注:本行内容追加)。

EEPROMが読まれると、CPUは次の命令が実行される前に4クロック周期停止されます。EEPROMが書かれると、CPUは次の命令が実行される前に2クロック周期停止されます。

### 8.4.2. EEPROMデータ化けの防止

低VCCの期間中、正しく動作するための供給電圧がCPUとEEPROMに対して低すぎるためにEEPROMデータが化け得ます。これらの問題はEEPROMを使う基板段階の装置と同じで、同じ設計上の解決策が適用されるべきです。

EEPROMデータ化けは電圧が低すぎる時の2つの状態によって起こされ得ます。1つ目として、EEPROMへの通常の書き込み手順は正しく動作するための最低電圧が必要です。2つ目として、供給電圧が低すぎると、CPU自身が命令を間違って実行し得ます。

EEPROMデータ化けは次の推奨設計によって容易に避けられます。

不充分な供給電源電圧の期間中、AVRのRESETを活性(Low)に保ってください。これは内蔵低電圧検出器(BOD)を許可することによって行えます。内蔵BODの検出電圧が必要とした検出電圧と一致しない場合、外部低VCCリセット保護回路が使えます。書き込み動作実行中にリセットが起こると、この書き込み操作は供給電源電圧が充分ならば(継続)完了されます。

### 8.5. I/Oメモリ (レシ スタ)

本デバイスのI/O空間定義は「レジスタ要約」で示されます。

デバイスの全てのI/Oと周辺機能はI/O空間に配置されます。全てのI/O位置はI/O空間と32個の汎用作業レジスタ間のデータ転送を行うLD/LDS/LDD命令とST/STS/STD命令によってアクセスされます。アドレス範囲\$00~\$1F内のI/OレジスタはSBI命令とCBI命令の使用で直接的にヒットアクセス可能です。これらのレジスタではSBISとSBIC命令の使用によって単一ヒット値が検査できます。I/O指定命令INとOUTを使う時はI/Oアドレス\$00~\$3Fが使われなければなりません。LD命令とST命令を使い、データ空間としてI/Oレジスタをアクセスする時はこれらのアドレスに\$20が加算されなければなりません。本デバイスはINやOUT命令で予約した64位置で支援されるより多くの周辺機能部を持つ複合マイクロコントローラです。SRAM(データ空間)内\$60~\$FFの拡張I/O領域に対してはLD/LDS/LDDとST/STS/STD命令だけが使えます。

将来のデバイスとの共通性を保つため、アクセスされる場合、予約ビットはOが書かれるべきです。予約済みI/Oメモリ アドレスは決して書かれるべきではありません。

状態フラグのいくつかはそれらへ'1'を書くことによって解除( $\frac{0}$ )され、これはフラグ説明で記述されます。CBIとSBI命令は他の多くのAVRと異なり、指定ビットだけを操作し、従って状態フラグのようなものを含むレジスタに使えることに注意してください。CBIとSBI命令は( $\frac{1}{O}$ )、 $\frac{1}{V}$ 0% ( $\frac{1}{V}$ 0% ( $\frac{1}{V}$ 0% )  $\frac{1}{V}$ 0% ( $\frac{1}{V}$ 0%

I/Oと周辺制御レジスタは以降の項で説明されます。

関連リンク 28. MEMPROG - メモリ プロク・ラミンク・

31. レジスタ要約

32. 命令要約

# 8.5.1. 汎用I/Oレジスタ

本デバイスは3つの汎用I/Oレジスタを含みます。これらのレジスタはどの情報の格納にも使え、特に全体変数や状態フラグの格納に有用です。(I/O)アドレス範囲\$00~\$1Fの汎用I/OレジスタはSBI,CBI,SBIS,SBIC命令の使用で直接ビット アクセスが可能です。

(訳注) 参考のため、以下のEEPROMアクセス方法を追加しました。

# 8.a.1. 非分離バイト プログラミング

非分離バイト プログラミングの使用は最も簡単な動作です。EEPROMにバイトを書くとき、使用者はEEARにアドレス、EEDRにデータを書かなければなりません。EEPMnビットが'00'ならば、(EEMPEが1を書かれる後の4周期内の)EEPEの1書き込みは消去/書き込み動作を起動します。消去と書き込みの両周期は1操作で行われ、総プログラミング時間は表8-1.で与えられます。EEPEビットは消去と書き込み動作が完了されるまで設定(1)に留まります。デバイスがプログラミング動作中、他のどのEEPROM操作の実行も不可能です。

# 8.a.2. 分離バイト プログラミング

2つの異なる操作として消去と書き込み周期を分離することが可能です。これは或る時間制限(代表的には電源電圧不足)に対してシステムが短いアクセス時間を必要とする場合に有用かもしれません。この方法の優位性を得るため、書かれるべき位置が書き込み操作前に消去されてしまっていることが必要とされます。しかし、消去と書き込みが分離されるため、時間が重大な操作の実行をシステムが許す時(代表的には電源投入後)に消去操作を行うことが可能です。

### 8.a.3. 消去

ハ・イトを消去するにはアト・レスがEEARに書かれなければなりません。EEPMn ビットが '01'なら、(EEMPEが1を書かれた後の4周期内の) EEPEの1書き込みは消去動作だけを起動します(プログラミング・時間は表8-1.で与えられます)。EEPE ビットは消去動作が完了されるまで設定(1)に留まります。 デバイススがプログラミング動作中、他のどのEEPROM操作の実行も不可能です。

### 8.a.4. 書き込み

(特定)位置を書くため、使用者はEEARにアトンス、EEDRにデータを書かなければなりません。EEPMnt゙ットが'10'なら、(EEMPEが1を書かれる後の4周期内の)EEPEの1書き込みは書き込み動作だけを起動します(プログラミング時間は表8-1.で与えられます)。EEPEビットは書き込み動作が完了されるまで設定(1)に留まります。書かれるべき位置が書き込み前に消去されてしまっていなければ、元の保存したデータは失ったとみなされなければなりません。デバイスがプログラミング動作中、他のどのEEPROM操作の実行も不可能です。

# 8.6. メモリ関係レジスタ

# 8.6.1. 16ビットレジスタのアクセス

AVRのデータ バスは8ビット幅で、故に16ビット レジスタのアクセスは非分断操作が必要です。これらのレジスタは2つの読みまたは書きの操作を用いてバイト アクセスされなければなりません。16ビット レジスタは16ビット バスを用いて8ビット バスと1つの一時レジスタに接続されます。

書き込み操作については、16ビット レジスタの上位バイトが下位バイトに先立って書かれなければなりません。そしてその上位バイトは一時レジスタに書かれます。16ビット レジスタの下位バイトが書かれる時に、同じクロック周期で一時レジスタが16ビット レジスタの上位バイトに複写されます。

読み込み操作については、16ビット レジスタの下位バイトが上位バイトに先立って読まれなければなりません。CPUによって下位バイトが 読まれる時に、下位バイトが読まれるのと同じクロック周期で16ビット レジスタの上位バイトが一時レジスタに複写されます。上位バイト読み込 みは今やこの一時レジスタから読みます。

これはレジスタの読み書き時に16ビット レジスタの上位と下位のバイトが常に同時にアクセスされることを保証します。

非分断16ビット レジスタ読み書き操作中に割り込みが起動されて同じレジスタをアクセスする場合、この時間制限手順を不正にし得ます。これを防ぐために、16ビット レジスタの読み書き時に割り込みを禁止することができます。

# 8.6.2. EEARH,EEARL - EEPROMアドレス レジスタ上位/下位バイト (EEPROM Address Register Low and High byte)

名称: EEARHとEEARL (EEAR)

変位:\$41(\$21)

リセット: '00000xxx xxxxxxxx'

特質: I/O特定命令でI/Oレジスタとしてアクセスする時の変位アドレスは\$21です。

EEARHとEEARLのレシ、スタ対は16ビット値のEEARを表します。下位バイト[7~0](接尾辞L)は変位原点でアクセスできます。上位バイト[15~8](接尾辞H)は変位+1でアクセスすることができます。16ビットレジ、スタの読み書きのより多くの詳細については上の「16ビットレジ、スタのアクセス」を参照してください。

LD系とST系の命令を使い、データ空間としてI/Oレジスタをアクセスする時は、提供された変位が使われなければなりません。I/O特定命令のINとOUTを使う時は、この変位が\$20で減算され、I/Oアドレスの変位は\$00~\$3F内になります。

| ピット    | 15  | 14  | 13  | 12  | 11   | 10  | 9        | 8   |

|--------|-----|-----|-----|-----|------|-----|----------|-----|

|        | _   | -   | -   | _   | -    |     | EEAR10~8 |     |

| アクセス種別 | R   | R   | R   | R   | R    | R/W | R/W      | R/W |

| リセット値  | 0   | 0   | 0   | 0   | 0    | 不定  | 不定       | 不定  |

| ピット    | 7   | 6   | 5   | 4   | 3    | 2   | 1        | 0   |

|        |     |     |     | EEA | R7∼0 |     |          |     |

| アクセス種別 | R/W | R/W | R/W | R/W | R/W  | R/W | R/W      | R/W |

|        |     |     |     |     |      |     |          |     |

| リセット値  | 不定  | 不定  | 不定  | 不定  | 不定   | 不定  | 不定       | 不定  |

### ● ビット9~0 - EEAR9~0: EEPROMアドレス (EEPROM Address)

EEPROMアドレスレシ、スタ(EEARHとEEARL)は2Kハ、イトのEEPROM空間内のEEPROMアドレスを指定します。EEPROMデータハ、イトは0~2047間で直線的に配されます。EEARの初期値は不定です。EEPROMがアクセスされ得る前に適切な値が書かれなければなりません。

# 8.6.3. EEDR - EEPROMデータレジスタ (EEPROM Data Register)

名称: EEDR 変位: \$40(\$20) リセット: \$00

特質:I/O特定命令でI/Oレシ、スタとしてアクセスする時の変位アトンスは\$20です。

LD系とST系の命令を使い、データ空間としてI/Oレジスタをアクセスする時は、提供された変位が使われなければなりません。I/O特定命令のINとOUTを使う時は、この変位が\$20で減算され、I/Oアドレスの変位は\$00~\$3F内になります。

| <u> </u> | 7       | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|----------|---------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

|          | EEDR7~0 |     |     |     |     |     |     |     |  |  |  |

| アクセス種別   | R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| リセット値    | 0       | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

# ● ビット7~0 - EEDR7~0: EEPROMデータ (EEPROM Data)

EEPROM書き込み操作に対してEEDRはEEPROMアドレス レジスタ(EEAR)で与えたアドレスのEEPROMへ書かれるべきデータを含みます。 EEPROM読み込み操作に対してEEDRはEEARで与えたアドレスのEEPROMから読み出したデータを含みます。

# 8.6.4. EECR - EEPROM制御レジスタ (EEPROM Control Register)

名称: EECR 変位: \$3F(\$1F) リセット: '00xx00xx'

特質:I/O特定命令でI/Oレシ、スタとしてアクセスする時の変位アトンスは\$1Fです。

LD系とST系の命令を使い、データ空間としてI/Oレジスタをアクセスする時は、提供された変位が使われなければなりません。I/O特定命令のINとOUTを使う時は、この変位が\$20で減算され、I/Oアドレスの変位は\$00~\$3F内になります。

| ピット    | 7 | 6 | 5   | 4    | 3     | 2     | 1    | 0    |

|--------|---|---|-----|------|-------|-------|------|------|

|        | - | _ | EEP | M1,0 | EERIE | EEMPE | EEPE | EERE |

| アクセス種別 | R | R | R/W | R/W  | R/W   | R/W   | R/W  | R/W  |

| リセット値  | 0 | 0 | 不定  | 不定   | 0     | 0     | 不定   | 0    |

### ● ビット5,4 - EEPM1,0: EEPROMプログラミング種別(EEPROM Programing Mode Bits)

EEPROMプログラミング種別ビット設定はEEPROMプログラミング許可(EEPE)書き込み時にどのプログラミング動作が起動されるかを定義しま

す。1つの非分離操作(旧値消去と新値書き込み)、または2つの異なる操作として消去と書き込み操作を分離してデータをプログラムする(書く)ことが可能です。各動作に対するプログラミング時間は右表で示されます。EEPEが設定(1)されている間はEEPMnへのどの書き込みも無視されます。リセット中、EEPMn は、ットはEEPROMがプログラミング作業中を除いて、2001 1 1.8ms 1 1 1 - にリセットされます。

| 表8-1. EEPROM/ ログプミノグ 性別 |   |           |                     |  |  |  |

|-------------------------|---|-----------|---------------------|--|--|--|

| EEPM1 EEPM0 プログラミング時間   |   | プログラミング時間 | 動作                  |  |  |  |

| 0                       | 0 | 3.4ms     | 1操作での消去と書き込み(非分離操作) |  |  |  |

| 0                       | 1 | 1.8ms     | 消去のみ                |  |  |  |

| 1                       | 0 | 1.8ms     | 書き込みのみ              |  |  |  |

| 1                       | 1 | _         | 将来使用に予約             |  |  |  |

# ● ビット3 - EERIE: EEPROM操作可割り込み許可(EEPROM Ready Interrupt Enable)

EERIEの1書き込みはステータスレジ、スタ(SREG)の全割り込み許可(I)ビットが設定(1)されているなら、EEPROM操作可割り込みを許可します。EERIEの0書き込みは、この割り込みを禁止します。EEPROM操作可割り込みは不揮発性メモリ(フラッシュ メモリとEEPROM)がプログラミングの準備可ならば継続する割り込みを発生します。EEPROM書き込みとSPM命令の間、本割り込みは生成されません。

### • ビット2 - EEMPE: EEPROM主プログラム許可 (EEPROM Master Program Enable)

EEMPEビットはEEPROMプログラム許可(EEPE)ビットの'1'書き込みが有効か無効かどちらかを決めます。EEMPEが設定(1)されると、4クロック周期内のEEPE設定(1)は選択したアトレスのEEPROMをプログラムします。

EEMPEが0なら、EEPE設定(1)は無効です。EEMPEがソフトウェアによって'1'が書かれてしまうと、4クロック周期後にハート'ウェアがこのヒ'ットを0に解除します。EEPROM書き込み手順については次のEEPE記述をご覧ください。

### • ビット1 - EEPE: EEPROMプログラム許可(EEPROM Program Enable)

EEPROMプログラム許可信号(EEPE)はEEPROMへの書き込み許可信号です。EEPEが(1を)書かれると、EEPROMはEEPMnビット設定に従ってプログラムされます。EEPEへ、1、が書かれる前にEEPROM主プログラム許可(EEMPE)ビットは、1、を書かれなければならず、さもなければEEPROM書き込み(消去)は行われません。EEPROMを書くとき、次の手順に従うべきです(手順3.と4.の順番は重要ではありません)。

- 1. EEPROMプログラム許可(EEPE)ビットがOになるまで待ちます。

- 2. SPM制御/状態レジスタ(SPMCSR)のSPM操作許可(SPMEN)ビットが0になるまで待ちます。

- 3. 今回のEEPROMアドレスをEEPROMアドレス レジスタ(EEAR)に書きます。(任意、省略可)

- 4. 今回のEEPROMデータをEEPROMデータレジスタ(EEDR)に書きます。(任意、省略可)

- 5. EEPROM制御レシ、スタ(EECR)のEEMPEL、ットに、1、EEPEL、ットに、0、を同時に書きます。

- 6. EEMPEt ット設定後4クロック周期内にEEPROMプログラム許可(EEPE) ビットへ'1'を書きます。

CPUがフラッシュ メモリ書き込み中、EEPROMはプログラム(書き込みが)できません。ソフトウェアは新規EEPROM書き込みを始める前にフラッシュ メモリのプログラミングが完了されていることを検査しなければなりません。2.はソフトウェアがフラッシュ メモリをプログラム(書き込みを)することをCPUに許すフート ローダを含む場合だけ関係します。フラッシュ メモリが決してCPUによって更新されないなら、2.は省略できます。

### ▲警告

手順5.と6.間の割り込みはEEPROM主プログラム許可が時間超過するため、書き込み周期失敗になります。EEPROMをアクセスする割り込みルーチンが他のEEPROMアクセスを中断し、EEARかEEDRが変更されると、中断したEEPROMアクセスを失敗させます。これらの問題を避けるため、全ての手順中、ステータスレジスタ(SREG)の全割り込み許可(I)ビットは解除(0)されていることが推奨されます。

書き込み(プログラミング)アクセス時間が経過されると、EEPROMプログラム許可(EEPE)ビットはハードウェアによって解除(0)されます。 EEPEが設定(1)されてしまうと、次の命令が実行される前にCPUは2周期停止されます。

### ● ビット0 - EERE: EEPROM読み込み許可(EEPROM Read Enable)

EEPROM読み込み許可信号(EERE)はEEPROMへの読み込みストローブです。EEARに正しいアトレスが設定されると、EEPROM読み出しを起動するためにEEREビットは'1'を書かれなければなりません。EEPROM読み出しアクセスは(その)1命令で行われ、要求したデータは直ちに利用できます。EEPROMが読まれるとき、次の命令が実行される前にCPUは4周期停止されます。

使用者は読み込み操作を始める前にEEPEビットをポーリングすべきです。書き込み(プログラム)操作実行中の場合、EEPROMアドレス レジスタ(EEAR)の変更もEEPROM読み込みもできません。

EEPROMアクセスの時間には校正済み内蔵RC発振器が使われます。CPUからのEEPROMアクセスに対する代表的な書き込み時間については右表をご覧ください。

| 表8-2. EEPROM書き込み時間 |                    |       |  |  |

|--------------------|--------------------|-------|--|--|

| 項目                 | 校正付き内蔵RC<br>発振器周期数 | Тур   |  |  |

| EEPROM書き込み(CPU)    | 26,368             | 3.3ms |  |  |

次のコート、例はアセンブリ言語とC言語でのEEPROM消去、書き込み、または非分離書き込み関数を示します。本例は(例えば全割り込み禁止によって)割り込みが制御され、これらの関数実行中に割り込みが起きない前提です。本例はソフトウェア内にフラッシュ ブート ロータ が無い前提でもあります。そのようなコートが存在する場合、EEPROM書き込み関数は何れかが実行するSPM命令の完了も待たねばなりません。(訳注:共通性から次例は補足修正しています。)

```

アセンブリ言語プログラム例

;EEPROMプログラミング完了ならばスキップ

EEPROM_WR:

SBIC

EECR, EEPE

;以前のEEPROMプログラミング完了まで待機

R.JMP

EEPROM WR

LDI

R19, (0<<EEPM1) | (0<<EEPM0)

;プログラミング種別値取得(本例は非分離)

EECR, R19

;対応プログラミング種別設定

OUT

;EEPROMアトレス上位バイト設定

OUT

EEARH, R18

OUT

EEARL, R17

;EEPROMアドレス下位バイト設定

OUT

EEDR, R16

;EEPROM書き込み値を設定

;EEPROM主プログラム許可ビット設定

SBT

EECR, EEMPE

;EEPROMプログラミング開始(プログラム許可ビット設定)

SBI

EECR, EEPE

RET

;呼び出し元へ復帰

C言語プログラム例

void EEPROM_write(unsigned int uiAddress, unsigned char ucData)

/* 以前のEEPROMプログラミング完了まで待機 */

while(EECR & (1<<EPE));</pre>

EECR = (0 < \langle EEPM1 \rangle | (0 < \langle EEPM0 \rangle ;

/* 対応プログラミング種別設定 */

/* EEPROMアドレス設定 */

EEAR = uiAddress;

/* EEPROM書き込み値を設定 */

EEDR = ucData;

EECR = (1 << EEMPE);

/* EEPROM主プログラム許可*/

EECR \mid = (1 < \langle EEPE \rangle;

/* EEPROMプログラミング開始*/

```

### **注:**「コート・例について」を参照してください。

次のコート・例はアセンブリ言語とC言語でのEEPROM読み込み関数を示します。本例は割り込みが制御され、これらの関数実行中に割り込みが起きない前提です。

```

アセンブリ言語プログラム例

EEPROM RD:

SBIC

EECR, EEPE

;EEPROMプログラミング完了ならばスキップ

;以前のEEPROMプログラミング完了まで待機

RJMP

EEPROM_RD

OUT

;EEPROMアドレス上位バイト設定

EEARH, R18

;EEPROMアドレス下位バイト設定

OUT

EEARL, R17

;EEPROM読み出し開始(読み込み許可ビット設定)

SBT

EECR, EERE

TN

R16, EEDR

;EEPROM読み出し値を取得

RET

;呼び出し元へ復帰

C言語プログラム例

unsigned char EEPROM_read(unsigned int uiAddress)

while(EECR & (1<<EPE));</pre>

/* 以前のEEPROMプログラミング完了まで待機 */

EEAR = uiAddress;

/* EEPROMアドレス設定 */

EECR \mid = (1 \le EERE);

/* EEPROM読み出し開始 */

return EEDR;

/* EEPROM読み出し値を取得,復帰 */

注: 「コート'例について」を参照してください。

```

# 8.6.5. GPIOR2 - 汎用I/Oレジスタ2 (General Purpose I/O Register 2)

名称: GPIOR2 変位: \$3A(\$1A)

リセット: \$00

特質:I/O特定命令でI/Oレシ、スタとしてアクセスする時の変位アトンスは\$1Aです。

LD系とST系の命令を使い、データ空間としてI/Oレジスタをアクセスする時は、提供された変位が使われなければなりません。I/O特定命令のINとOUTを使う時は、この変位が\$20で減算され、I/Oアドレスの変位は\$00~\$3F内になります。

| <u> </u> | 7         | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|----------|-----------|-----|-----|-----|-----|-----|-----|-----|

|          | GPIOR27~0 |     |     |     |     |     |     |     |

| アクセス種別   | R/W       | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| リセット値    | 0         | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

ビット7~0 - GPIOR27~0:汎用I/Oレジスタ2 (General Purpose I/O)

# 8.6.6. GPIOR1 - 汎用I/Oレジスタ1 (General Purpose I/O Register 1)

名称: GPIOR1 変位: \$39(\$19) リセット: \$00

特質: I/O特定命令でI/Oレジスタとしてアクセスする時の変位アドレスは\$19です。

LD系とST系の命令を使い、データ空間としてI/Oレジスタをアクセスする時は、提供された変位が使われなければなりません。I/O特定命令のINとOUTを使う時は、この変位が\$20で減算され、I/Oアドレスの変位は\$00~\$3F内になります。

| Ľ'ット   | 7         | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----------|-----|-----|-----|-----|-----|-----|-----|

|        | GPIOR17~0 |     |     |     |     |     |     |     |

| アクセス種別 | R/W       | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| リセット値  | 0         | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

ビット7~0 - GPIOR17~0: 汎用I/Oレシスタ1 (General Purpose I/O)

# 8.6.7. GPIORO - 汎用I/OレジスタO (General Purpose I/O Register 0)

名称: GPIOR0 変位: \$3E(\$1E) リセット: \$00

特質:I/O特定命令でI/Oレシ、スタとしてアクセスする時の変位アト、レスは\$1Eです。

LD系とST系の命令を使い、データ空間としてI/Oレジスタをアクセスする時は、提供された変位が使われなければなりません。I/O特定命令のINとOUTを使う時は、この変位が\$20で減算され、I/Oアドレスの変位は\$00~\$3F内になります。

| ピット       | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------|-----|-----|-----|-----|-----|-----|-----|-----|

| GPIOR07~0 |     |     |     |     |     |     |     |     |

| アクセス種別    | R/W |

| リセット値     | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|           |     |     |     |     |     |     |     |     |

ヒット7~0 - GPIOR07~0:汎用I/Oレジスタの(General Purpose I/O)

# 9. システム クロックとクロック選択

# 9.1. クロック系統とその配給

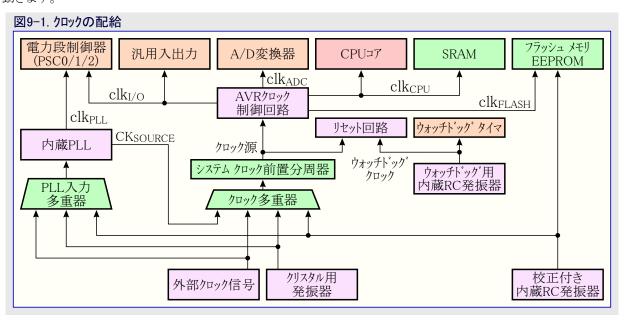

下図はデバイス内の主要クロック系統とそれらの配給を示します。全てのクロックが与えられた時間有効である必要はありません。消費電力低減のため、各種休止形態を用いることによって、使われない部分のクロックを停止することができます。クロック系統は以降の項で記述されます。

システム クロック周波数はシステム クロック前置分周器から生成された周波数を参照します。AVRクロック制御部からの全てのクロック出力は同じ周波数で動きます。

# 9.1.1. CPUクロック – clk<sub>CPU</sub>

CPUクロックはAVRコアの動作と関係する系統の部分に配給されます。このような部分の例は汎用レジスタ ファイル、ステータス レジスタ、スタックポインタを保持するデータ メモリです。CPUクロックの停止はコアが一般的な操作や計算を実行することを禁止します。

### 9.1.2. I/Oクロック - clk<sub>I/O</sub>

I/Oクロックはタイマ/カウンタ、SPI、USARTのようなI/O部の大部分で使われます。I/Oクロックは外部割り込み部でも使われますが、特定の部分はclk<sub>I/O</sub>が停止される時に非同期で実行されます(<mark>訳注:</mark>整合性のため本行修正)。

注: パワーダウン動作から起き上がるのにレベル起動割り込みが使われる場合、そのレベル割り込みを起動するような完全な起動のために 必要とされた割り込みはMCUに対して充分な長さを保持しなければなりません。始動時間の終了前にそのレベルが消滅すると、 MCUは未だ起き上がりますが、割り込みが生成されません。始動時間はSUTとCKSELのヒューズによって定義されます。

# 9.1.3. フラッシュ クロック - clk<sub>FLASH</sub>

フラッシュ クロックはフラッシュ メモリ インターフェースの動作を制御します。このフラッシュ クロックは常にCPUクロックと同時に活動します。

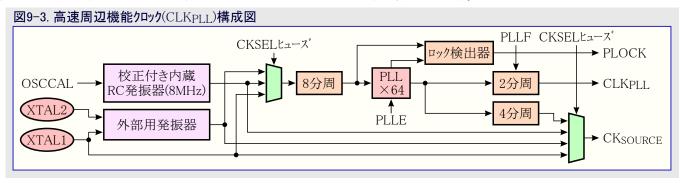

### 9.1.4. PLLクロック - clkpt.t.

PLLクロックは64/32MHzから直接的にクロック駆動されるのを高速周辺機能に許します。

PLLから得たクロックは宇宙環境でCPUをクロック駆動するのに使うことができません。

### 9.1.5. A/D変換クロック - clkADC

A/D変換器には専用のクロック範囲が提供されます。これはデジタル回路によって生成された雑音を低減するためにCPUとI/Oクロックの停止を許します。これはより正確なA/D変換結果を与えます。

# 9.2. クロック元

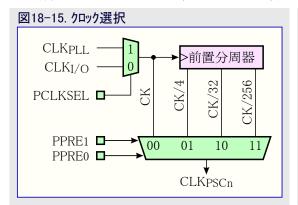

本デバイスには右図で示されるようにフラッシュ ヒュース ビットによって選択可能な後続のクロック元選択があります。選択したクロック元からのクロックはAVRクロック発生器への入力で、適切な単位部へ配給されます。

各クロック任意選択に対する選択は次項で与えられます。CPUがパワーダウンから起動する時、選択したクロック元は命令実行開始前に安定な発振器動作を保証する起動時間に使われます。CPUがリセットから始まる時、これらは通常動作開始前に安定電圧へ達するのを電源に許す付加遅延です。ウォッチドッグ発振器はこの起動時間の実時間部のタイミングに使われます。各計時完了に使われるウォッチドッグ(WDT)発振器の周期数は右下の表で示されます。

表9-1. クロック種別選択

| システム クロック        | PLL入力            | CKSEL3~0  |

|------------------|------------------|-----------|

| 外部クリスタル/セラミック発振子 | 校正付き内蔵RC発振器      | 1111~1000 |

| (利用不可)           | (利用不可)           | 011x      |

| (利用不可)           | (利用不可)           | 0101      |

| 外部クリスタル/セラミック発振子 | 外部クリスタル/セラミック発振子 | 0100      |

| (利用不可)           | (利用不可)           | 0011      |

| 校正付き内蔵RC発振器      | 校正付き内蔵RC発振器      | 0010      |

| (利用不可)           | (利用不可)           | 0001      |

| 外部クロック信号         | 校正付き内蔵RC発振器      | 0000      |

注: 1=非プログラム、0=プログラム

| 表9-2. WDT発振器の代表計時完了値、周期数 |             |  |  |  |  |

|--------------------------|-------------|--|--|--|--|

| VCC=3.0V                 | 周期数         |  |  |  |  |

| 4.3ms                    | 4K (4096)   |  |  |  |  |

| 69ms                     | 64K (65536) |  |  |  |  |

# 9.3. 既定のクロック元

本デバイスはCKSEL=0010, SUT=10, CKDIV8=非プログラム(1)で出荷されます。既定のクロック元設定は最長起動時間の(8.0MHzの)校正付き内蔵RC発振器で、分周なしの初期システム クロックです。この既定設定は全ての使用者が実装または並列書き込み器を使い、それらを希望したクロック元設定にできることを保証します。

# 9.4. クリスタル用低電力発振器

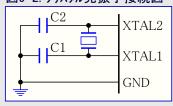

XTAL1とXTAL2は下図で示されるように、チップ上の発振器としての使用に設定できる反転増幅器の各々、入力と出力です。クリスタル発振子またはセラミック振動子のどちらでも使えます。

この発振器はXTAL2出力上の電圧振幅を減少した低電力発振器です。これは最低消費電力を与えますが、他のクロック入力を駆動する能力はありません。

C1とC2はクリスタル発振子とセラミック振動子の両方について常に等しくすべきです。このコンデンサの最適値は使うクリスタル発振子やセラミック振動子、浮遊容量の量、その環境の電磁雑音に依存します。クリスタル発振子使用に対するコンデンサ選択について初期の指針のいくつかは表9-3.で与えられます。セラミック振動子については製造業者によって与えられたコンデンサ値が使われるべきです。

低電力発振器は示された周波数範囲で各々最適化された3つの異なる種別で動作できます。この動作種別は下表で示されるように CKSEL3~1ヒュース、によって選択されます。

図9-2. クリスタル発振子接続図

表9-3. クリスタル用低電力発振器動作種別

| CKSEL3~1 | 周波数範囲      | 推奨C1,2容量 |

|----------|------------|----------|

| 100 (注)  | 0.4~0.9MHz | 1        |

| 101      | 0.9~3.0MHz | 12∼22pF  |

| 110      | 3.0~8.0MHz | 12∼22pF  |

| 111      | 8.0~16MHz  | 12~22pF  |

**注**: 本選択はクリスタル発振子ではなく、セラミック振動子でのみ使われるべきです。

CKSEL0ヒューズはSUT1,0ヒューズと共に次表で示されるように起動時間を選択します。

表9-4. クリスタル発振子/セラミック振動子用低電力発振器起動遅延時間選択表

| CKSEL0 | SUT1,0 | パワーダウンからの<br>起動遅延時間  | リセットからの付加遅延<br>時間 (VCC=3.3V) | 推奨使用法                       |

|--------|--------|----------------------|------------------------------|-----------------------------|

|        | 0 0    | 258×CK ( <b>注1</b> ) | $14 \times \text{CK+4.3ms}$  | 外部セラミック振動子、高速上昇電源           |

| 0      | 0 1    | 258×CK ( <b>注1</b> ) | $14 \times \text{CK+69ms}$   | 外部セラミック振動子、低速上昇電源           |

| U      | 1 0    | 1K×CK ( <b>注2</b> )  | 14×CK                        | 外部セラミック振動子、低電圧検出(BOD)リセット許可 |

|        | 1 1    | 1K×CK ( <b>注2</b> )  | $14 \times \text{CK+4.3ms}$  | 外部セラミック振動子、高速上昇電源           |

|        | 0 0    | 1K×CK ( <b>注2</b> )  | $14 \times \text{CK+69ms}$   | 外部セラミック振動子、低速上昇電源           |

| 1      | 0 1    | 16K×CK               | 14×CK                        | 外部クリスタル発振子、低電圧検出(BOD)リセット許可 |

| 1      | 1 0    | 16K×CK               | $14 \times \text{CK+4.3ms}$  | 外部クリスタル発振子、高速上昇電源           |

|        | 1 1    | 16K×CK               | $14 \times \text{CK+69ms}$   | 外部クリスタル発振子、低速上昇電源           |

**注1**: これらの選択はデバイスの最高周波数付近での動作でないとき、応用にとって起動での周波数安定性が重要でない場合だけ使われるべきです。これらの選択はクリスタル発振子用ではありません。

**注2**: これらの選択はセラミック振動子での使用を意図され、起動での周波数安定性を保証します。デバイスの最高周波数付近での動作でないとき、応用にとって起動での周波数安定性が重要でない場合はクリスタル発振子も使えます。

### 関連リンク 18.14. PSCクロック元

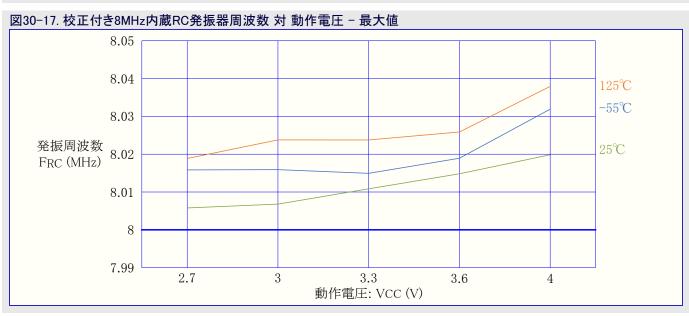

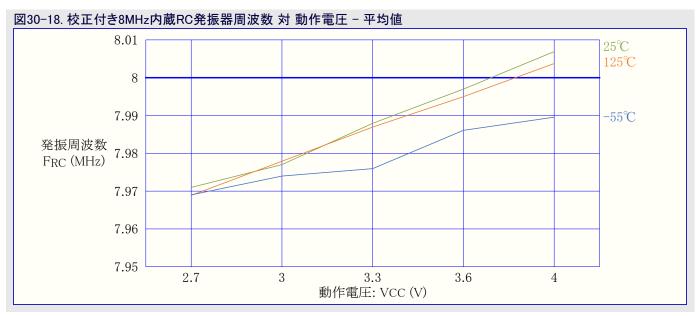

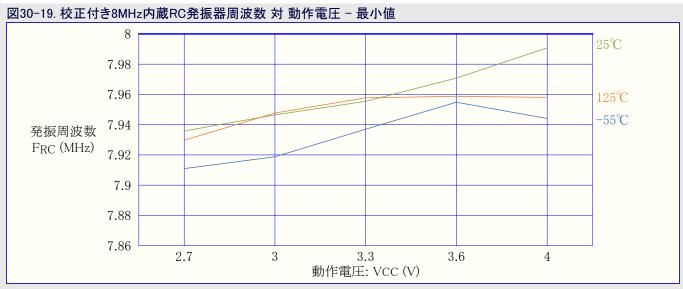

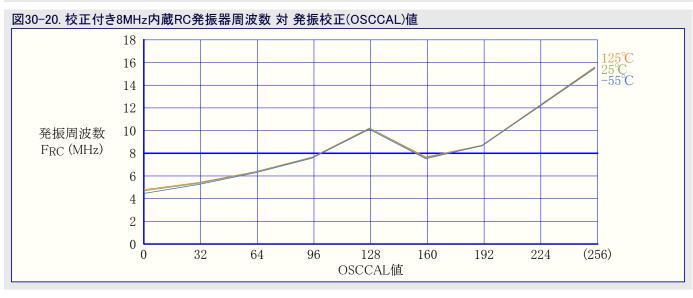

# 9.5. 校正付き内蔵RC発振器

既定による校正された内蔵RC発振器は8.0MHzのクロックを供給します。電圧と温度に依存しますが、このクロックは使用者によって高精度な校正ができます。このデバイスはCKDIV8ヒューズがプログラム(0)で出荷されます。

このクロックは下表で示されるようにCKSELヒューズのプログラミングによってシステム クロックとして選択できます。リセット中、ハートウェアが発振校正 (OSCCAL)レジスタに予めプログラムされた校正ハイトを設定し、これによってRC発振器を自動的に校正します。 XTAL2が未接続(NC)のままにされる間、XTAL1とGND間に10kΩのプルダウンが接続されるべきです。

ソフトウェアからOSCCALレシ、スタを変更することによって、工場校正を使うよりも高い精度を得ることができます。

この発振器がチップ(システム)クロックとして使われる時に、ウォッチト、ック、発振器は未だウォッチト、ック、タイマとリセット付加遅延計時器に使われます。

# 表9-5. 校正付き内蔵RC発振器動作種別

| CKSEL3~0 | 周波数範囲 (MHz) |

|----------|-------------|

| 0 0 1 0  | 7.3~8.1     |

注: デバイスはこの選択で出荷されます。

注: この8MHz周波数がデバイス仕様(VCCに依存)を越える場合、内部周波数を8分周するためにCKDIV8ヒュースをプログラム(0)にできます。

この発振器が選択されると、起動時間はSUTヒュースによって決定されます。

# 表9-6. 校正付き内蔵RC発振器用起動遅延時間選択表

| 表9 <sup>-0.</sup> 校正的合内做RO先振奋用起到连延时间选扒衣 |                     |                              |                  |  |  |

|-----------------------------------------|---------------------|------------------------------|------------------|--|--|

| SUT1,0                                  | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=3.3V) | 推奨使用法            |  |  |

| 0 0                                     | 6×CK                | 14×CK ( <b>注2</b> )          | 低電圧検出リセット(BOD)許可 |  |  |

| 0 1                                     | 6×CK                | $14 \times \text{CK+4.3ms}$  | 高速上昇電源           |  |  |

| 10 (注1)                                 | 6×CK                | 14×CK+69ms                   | 低速上昇電源           |  |  |

| 1 1                                     | (予約)                |                              |                  |  |  |

**注1**: デバイスはこの選択で出荷されます。

**関連リンク** 9.10. システム クロック前置分周器

28.5. 校正バイ

9.11.1. OSCCAL - 発振校正レジスタ

# 9.6. PLL

高い精度と周波数のPWM波形を生成するために、電力段制御器(PSC)は高周波数クロック入力が必要です。このクロックはPLLによって生成されます。全てのPWM精度を維持するため、PLLの周波数係数はソフトウェアによって設定されなければなりません。8MHzのシステムクロックでのPLL出力は32MHzまたは64MHzです。

# 9.6.1. 内部PLL

ATmegaET64M1の内部PLLは公称1MHzから64倍されたクロック周波数を生成します。この1MHzのPLL入力クロック元は1MHzに分周された内蔵RC発振器の出力です。

PLLはこのRC発振器に固定化し、発振校正レジスタ(OSCCAL)経由のRC発振器調整は同時に高速周辺機能クロックも調整します。けれども分周したRC発振器が1MHzより高い周波数にされるのが可能でも、高速周辺機能クロックは(最悪の場合)70MHzで飽和し、最高周波数での発振に留まります。この場合、PLLがもはやRC発振器クロックで固定化されないことに注意されるべきです。

従ってPLLを正しい動作範囲に保持するため、1MHzより低い周波数にOSCCAL補正を行うことが推奨されます。内部PLLはPLL制御/状態レジスタ(PLLCSR)のPLL許可(PLLE)ビットが設定(1)される時だけ許可されます。PLLCSRのPLL固定化(PLOCK)ビットはPLLが固定化されている時に設定(1)されます。

内部1MHz RC発振器とPLLはパワーダウンとスタンバイの休止形態でOFFへ切り替えられます。

表9-7. PLLシステム クロック用起動遅延時間選択表

| CKSEL3~0           | SUT1,0 | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=3.3V) |

|--------------------|--------|---------------------|------------------------------|

|                    | 0 0    | 1K×CK               | 14×CK                        |

| 0 1 0 1            | 0 1    | 1K×CK               | $14 \times \text{CK+4.3ms}$  |

| (外部クリスタル/セラミック発振子) | 1 0    | 16K×CK              | $14 \times \text{CK+4.3ms}$  |

|                    | 1 1    | 16K×CK              | 14×CK+69ms                   |

|                    | 0 0    | 1K×CK               | 14×CK                        |

| 0 0 1 1            | 0 1    | 1K×CK               | $14 \times \text{CK+4.3ms}$  |

| (校正付き内蔵RC発振器)      | 1 0    | 1K×CK               | 14×CK+69ms                   |

|                    | 1 1    | 16K×CK              | 14×CK                        |

|                    | 0 0    | 6×CK ( <b>注</b> )   | 14×CK                        |

| 0 0 0 1            | 0 1    | 6×CK ( <b>注</b> )   | $14 \times \text{CK+4.3ms}$  |

| (外部クロック信号)         | 1 0    | 6×CK ( <b>注</b> )   | 14×CK+69ms                   |

|                    | 1 1    | (予                  | 約)                           |

注: この値は正しい再起動を提供せず、このクロック機構でパワーダウン動作を使ってはいけません。

# 9.7. 128kHz内部発振器

128kHz内部発振器は128kHzのクロックを供給する低電力発振器です。この周波数は3V,25℃での公称値です。このクロックはウォッチドッグ発振器によって使われます。

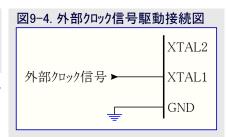

# 9.8. 外部クロック信号

外部クロック元からデバイスを駆動するにはXTAL1が右図で示されるように駆動されるべきです。外部クロックでデバイスを走行するためにはCKSELヒューズが'0000'にプログラム(設定)されなければなりません。

表9-8. 外部クロック信号動作種別 CKSEL3~0 周波数範囲 0000 0~8MHz

このクロック元が選択されると、起動時間は下表で示されるようにSUTヒューズによって決定されます。

# 表9-9. 外部クロック信号駆動用起動遅延時間選択表

| SUT1,0 | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=3.3V) | 推奨使用法            |  |  |  |  |  |

|--------|---------------------|------------------------------|------------------|--|--|--|--|--|

| 0 0    | 6×CK                | 14×CK                        | 低電圧検出(BOD)リセット許可 |  |  |  |  |  |

| 0 1    | 6×CK                | 14×CK+4.3ms                  | 高速上昇電源           |  |  |  |  |  |

| 1 0    | 6×CK                | 14×CK+69ms                   | 低速上昇電源           |  |  |  |  |  |

| 1 1    |                     | (予約)                         |                  |  |  |  |  |  |

外部クロックを供給するとき、MCUの安定な動作を保証するために供給したクロック周波数の急な変化を避けることが必要とされます。或るクロック周期から次への2%より大きな周波数変化は予測されない事態を引き起こします。2%より大きな変化が必要とされる場合、変化中にMCUがリセットに保たれることを保証してください。

システム クロック前置分周器は安定な動作を保証しながら、内部クロック周波数の実行時変更の実現に使うことができます。

# 9.9. クロック出力緩衝部(外部クロック出力)

このデバイスはシステム クロックをCLKOピンに出力できます。本出力を許可するにはCKOUTヒューズがプログラム(0)されなければなりません。この動作はチップのクロックがシステム上の他の回路を駆動する時用です。このヒューズがプログラム(0)されると、I/Oピンの標準動作は無視され、このクロックはリセット中も出力されます。CLKOがクロック出力を扱うとき、校正付き内蔵RC発振器を含む何れのクロック元も選択できます。システム クロック前置分周器が使われると、CKOUTヒューズがプログラム(0)された時の出力は分周したシステム クロックです。

# 9.10. システム クロック前置分周器

本デバイスはシステム クロック前置分周器を持ち、システム クロックはクロック前置分周レジスタ(CLKPR)を構成設定することによって分周できます。この特徴(機能)は必要とされる処理能力が低い時の消費電力削減に使えます。これは全クロック種別で使え、CPUと全同期周辺機能のクロック周波数に影響を及ぼします。clk<sub>CPU</sub>、clk<sub>FLASH</sub>、clk<sub>I/O</sub>、clk<sub>ADC</sub>はCLKPR記述で示された値によって分周されます。

前置分周器設定間を切り替えるとき、システム クロック前置分周器は中間(経過途中)の周波数が直前の設定に対応するクロック周波数または新規設定に対応するクロック周波数のどちらよりも高くなく、クロック系で不具合が起きないことを保証します。前置分周器として実行するリプル カウンタは分周されないクロック周波数で走行し、CPUのクロック周波数より速いかもしれません。従って例え(カウンタ値が)読めるとしても、前置分周器の状態を決めることはできず、1から他へのクロック分周値切り替えを行う正確な時間は必ずしも予測できません。クロック分周値選択(CLKPS3~0)ビット値が書かれる時から新規クロック周波数が活性(有効)になる前にT1+T2~T1+2×T2間かかります。この間で2つの有効なクロック端が生成されます。ここでのT1は直前のクロック周期、T2は新規前置分周器設定に対応する周期です。

予期せぬクロック周波数の変更を防ぐため、CLKPSビットの変更は次の特別な書き込み手順に従わなければなりません。

- 1. クロック分周値変更許可(CLKPCE)ビットに'1'、CLKPR内の他の全ビットに'0'を書いてください。 CLKPR=\$80

- 2. (次からの)4周期以内にCLKPRでCLKPCEへ'0'を書くと同時にCLKPS3~0へ望む値を書いてください。 前置分周器設定変更時、書き込み手続きが割り込まれないことを保証するため、割り込みは禁止されなければなりません。

**関連リンク** 9.11.3. CLKPR - クロック前置分周レシブスタ

# 9.11. クロック関係レジスタ

# 9.11.1. OSCCAL - 発振校正レジスタ (Oscillator Calibration Register)

名称: OSCCAL 変位: \$66

リセット: デバイス固有の校正値

特質:-

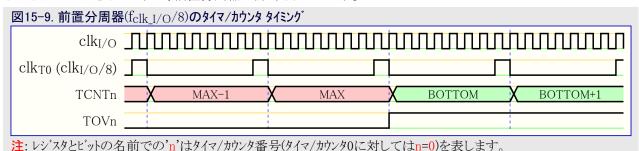

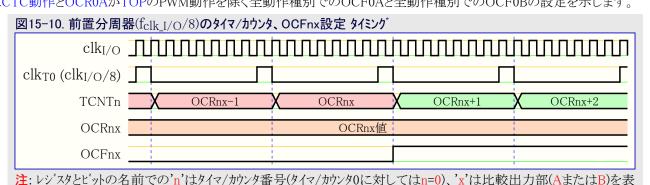

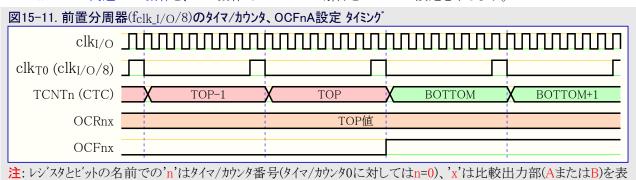

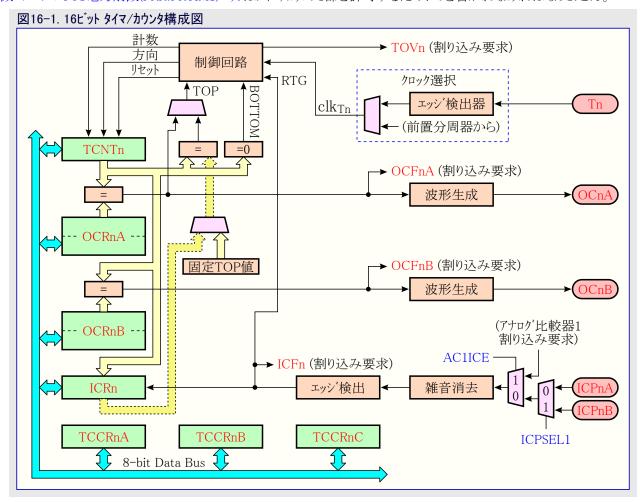

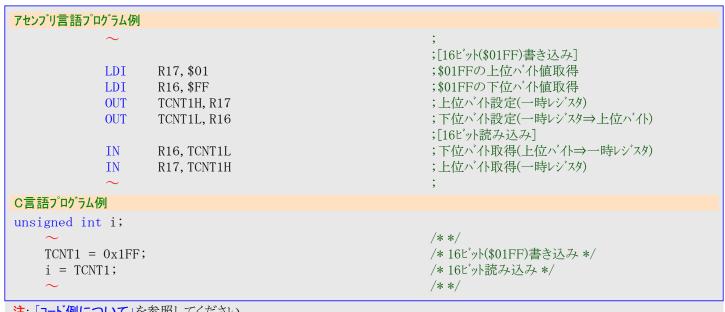

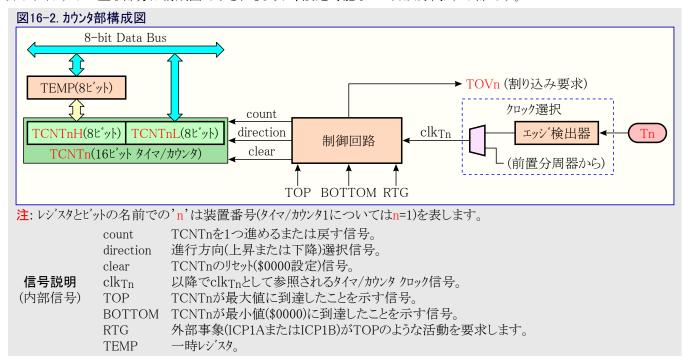

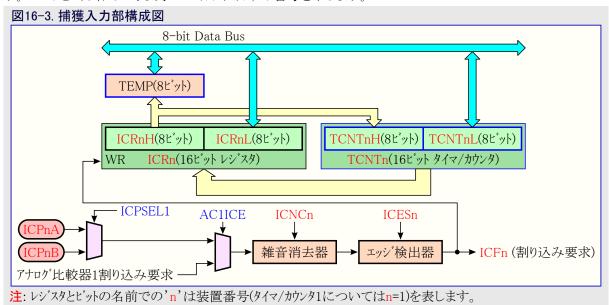

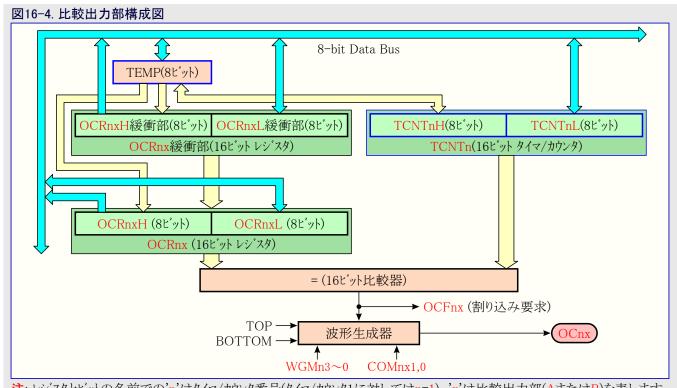

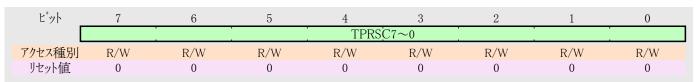

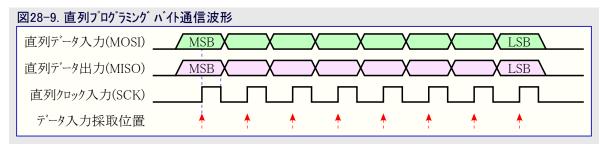

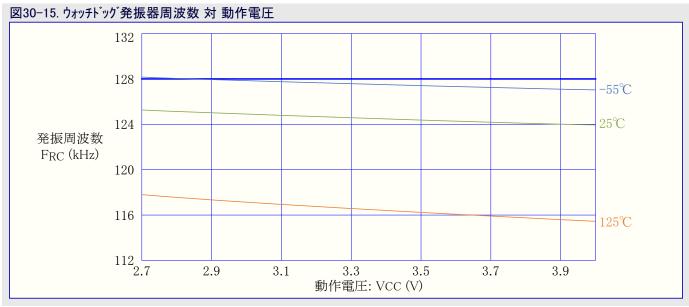

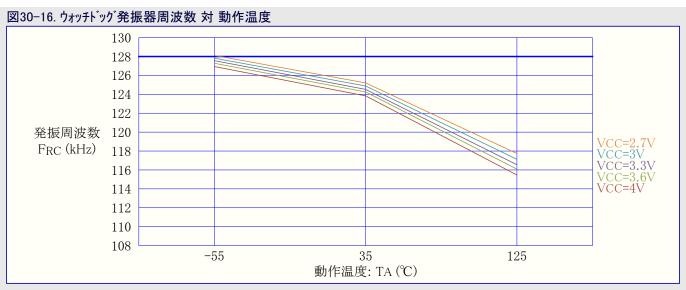

# ● ビット7~0 - CAL7~0:発振校正値 (Oscillator Calibration Value)