# tinyAVR<sup>®</sup> データシート

# 序説

ATtiny4/5/9/10はAVR<sup>®</sup>強化RISC構造に基づく低電力CMOS 8ビットマイクロコントローラです。ATtiny4/5/9/10は32ハイトの SRAMを持つ512から1024ハイトまでのフラッシュメモリの6/8ビンデバイスです。単一クロック周期での強力な命令の実行により、 デバイスはMHz当たり1MIPS(100万命令/秒)近くの単位処理量を達成します。これは消費電力対処理速度に対するデバイ スの最適化をシステム設計者に許します。

本書は一般の方々の便宜のため有志により作成されたもので、Microchip社とは無関係であることを御承知ください。しおりの[はじめに]での内容にご注意ください。

# 特徴

- ・高性能、低消費AVR® 8ビットマイクロ コントローラ

- ・進化したRISC構造

- 強力な112命令 多くは1クロック周期実行

- 16個の1バイト長汎用レジスタ

- 完全なスタティック動作

- 12MHz時、12MIPSに達する高速動作

- ・データ用メモリとプログラム用不揮発性メモリ

- 実装書き換え可能な512/1Kバイト(256/512語)フラッシュ メモリ内蔵

- 32バイトの内蔵SRAM

- フラッシュ書き込み/消去回数: 10,000

- データ保持力: 20年/85℃, 100年/25℃

- ・内蔵周辺機能

- 容量性接触感知用QTouch®ライブラリ支援(1チャネル)

- 前置分周器と2つのPWM出力付き、1つの16ビットタイマ/カウンタ

- 4チャネル 8ビット A/D変換器 (ATtiny5/10のみ)

- 独立したチップ上発振器を持つウォッチトック タイマ

- アナログ比較器

- ・特殊マイクロコントローラ機能

- 実装書き込み可能 (5Vでのみ)

- 内部及び外部の割り込み

- アイドル、A/D変換雑音低減、スタンバイ、パワーダウンの4つの低消費動作

- 強化した電源ONリセット回路

- 割り込みとリセットを持つ設定可能な供給電圧レヘブル監視器

- 校正付き内蔵RC発振器

- ・I/Oと外囲器

- 4ビットの設定変更可能なI/O

- 6ピンSOTと8ハットUDFN

- ・動作電圧

- -1.8~5.5V

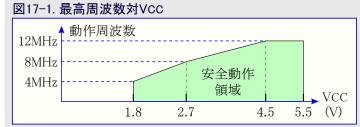

- 動作速度

- $-0\sim 4$ MHz $/1.8\sim 5.5$ V

- $-0 \sim 8 MHz/2.7 \sim 5.5 V$

- $-0\sim 12 MHz/4.5\sim 5.5 V$

- ・工業用と拡張の温度範囲:-40~+85℃/+125℃

- ・低消費電力

- 活動動作: 200µA (1MHz,1.8V)

- アイドル動作: 25µA (1MHz,1.8V)

- パワーダウン動作 : <0.1µA (1.8V)

| 次 |

|---|

|   |

|     | 序説                  |                                                                                                   |

|-----|---------------------|---------------------------------------------------------------------------------------------------|

|     | 特徴                  |                                                                                                   |

| 1.  |                     | <br>置 ······5                                                                                     |

| 1.  | 1.1.                | 5世<br>ピン説明 ······5                                                                                |

| 0   |                     | 情報 •••••• 6                                                                                       |

| 2.  |                     | 1 <b>⊨ ¥</b> Ω 6                                                                                  |

| 3.  | 概要                  | •                                                                                                 |

|     | 3.1.                | ATtiny4,ATtiny5,ATtiny9,ATtiny10の比較・・・・・7                                                         |

| 4.  |                     | <b>情報</b> · · · · · · · · 8                                                                       |

|     | 4.1.                | 資料 ····· 8                                                                                        |

|     | 4.2.                | □ド例 ······8                                                                                       |

|     | 4.3.                | 容量性接触感知 ・・・・・・・・・・・・・・・・・ 8                                                                       |

| _   | 4.4.                | データ保持力 ・・・・・・ 8                                                                                   |

| 5.  |                     | <b>CPU ⊐7</b> ····· 9                                                                             |

|     | 5.1.                | 基本構造概要 · · · · · · · · · · · · 9                                                                  |

|     | 5.2.                | ALU (Arithmetic Logic Unit) •••••• 9                                                              |

|     | 5.3.                | ステータス レジ スタ · · · · · · · · · · · · · · · · · ·                                                   |

|     | 5.4.                | 汎用レジスタファイル ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・10<br>スタック ホペンタ ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・10 |

|     | 5.5.                | スダックホインダ ······10<br>命令実行タイミング ······10                                                           |

|     | 5.6.<br>5.7.        | 前令美行91520 10<br>リセットと割り込みの扱い 11                                                                   |

|     |                     | コア関係レジスタ ······12                                                                                 |

| 0   | 5.8.                |                                                                                                   |

| 6.  |                     |                                                                                                   |

|     | 6.1.                | 実装書き換え可能なプログラム用フラッシュ メモリ ・・・ 14<br>データ メモリ ・・・・ 14                                                |

|     | 6.2.<br>6.3.        | アーダメモリ 14<br>I/Oメモリ (レジネタ) ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                   |

| -   |                     |                                                                                                   |

| 7.  | クロック                | 体系                                                                                                |

|     | 7.1.                | <b>クロック副系統</b> ・・・・・・・・・・・・・・・・・・・・・・ 16<br><b>クロック元</b> ・・・・・・・・・・・・・・・・・・・・・・・・・・・ 16           |

|     | 7.2.                | シロック元 ····································                                                        |

|     | 7.3.<br>7.4.        | 9774 7497前直分局器 17<br>始動 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                      |

|     | 7.4.<br>7.5.        | 2019<br>クロック関係レジスタ ····· 19                                                                       |

| 0   |                     | 管理と休止形態動作 ············21                                                                          |

| 8.  | <b>电</b> 力<br>8.1.  |                                                                                                   |

|     | 8.2.                | <b>休止形態動作種別</b> 21<br>電力削減レジスタ 22                                                                 |

|     | o.z.<br>8.3.        | <b>電力</b> 前減レンス<br>消費電力の最小化 ························22                                            |

|     | 8.4.                | 宿力管理用レジスタ ······23                                                                                |

| 0   | 2.7=                |                                                                                                   |

| 9.  |                     |                                                                                                   |

|     | 9.1.                |                                                                                                   |

|     | 9.Z.<br>0.2         | クビットノレ 24<br>ウナッチトック タイフ 26                                                                       |

|     | 9.5.<br>9.4         | 1111111111111111111111111111111111111                                                             |

| 10. | 。<br>割り             | A市14町2-リセット<br>AVRのリセット<br>リセット元<br>ウォッチトック、タイマ<br>リセット関係レジ、スタ<br>20<br>割り込み、クタ<br>29             |

| 10. | <b>ロリッ</b> ノ<br>101 | ፈሪን<br>መሀር እ ዲላ እስል · · · · · · · · · · · · · · · · · · ·                                         |

|     | 10.1.               | 副り込み、<br>外部割り込み ····································                                              |

|     | 10.2.               | 割り込み用レジスタ・・・・・・・・・・・・・・・・・・31                                                                     |

| 11  |                     | カポート・・・・・・・・・・・・・・・・・・ 33                                                                         |

| 11. | <u>лш</u><br>11.1.  | 概要 · · · · · · · · · · · · · · · · · · ·                                                          |

|     | 11.1.               | <ul> <li>概要</li> <li>標準デジダル入出力としてのホート・・・・・・・ 33</li> </ul>                                        |

|     | 11.2.               | · 深年1775072000000000000000000000000000000000                                                      |

|     | 11.4.               | <b>I/Oホ</b> ート用レジスタ ······ 40                                                                     |

| 12. |                     | ルト タイマ/カウンタ0 (PWM) ・・・・・・・・・・・・・・・・・・・・・・・・41                                                     |

| ۲Ζ. | 12.1.               | 特徴 ···································                                                            |

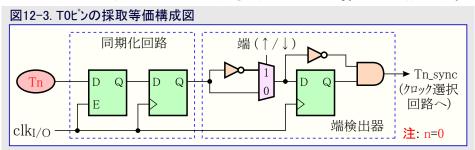

|     | 12.1.               | 将国                                                                                                |

|     | 12.2.               | $h \Box \eta h \overline{\Box}$                                                                   |

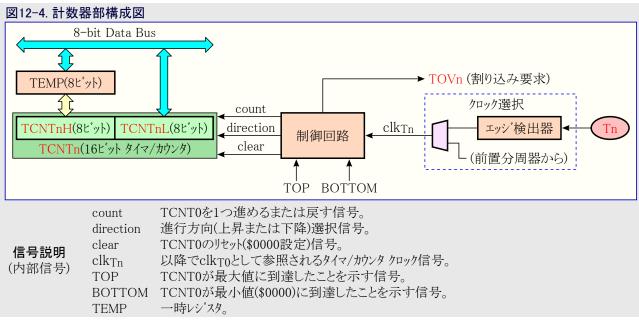

|     | 12.3.               | 計数器部 ••••••••••••••••••••••••••••••••••••                                                         |

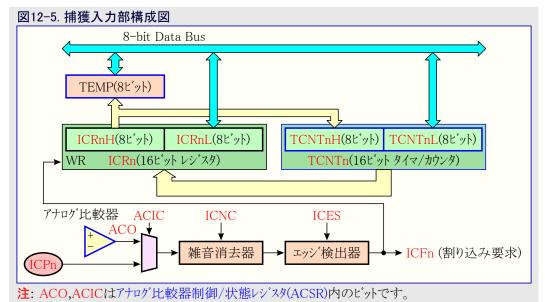

|     | 12.5.               | 計数器部       44         捕獲入力部       45                                                              |

|     |                     |                                                                                                   |

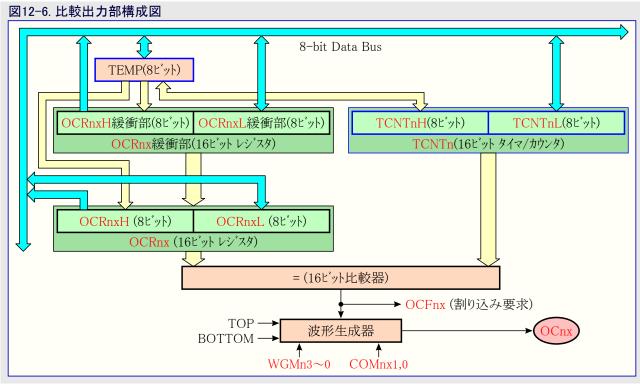

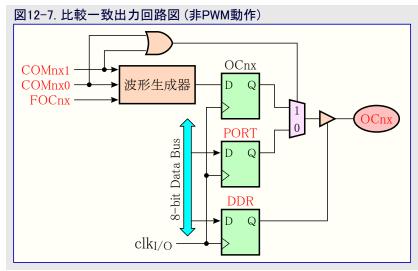

|     | 12.6.  | 比較出力部 46                                                                                                                                                                                                                                                                                                                          |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 12.7.  | 比較一致出力部 ······ 47<br>動作種別 ······ 49                                                                                                                                                                                                                                                                                               |

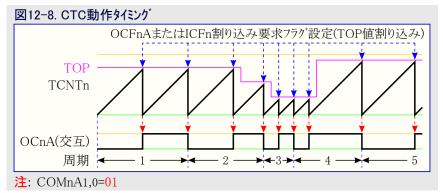

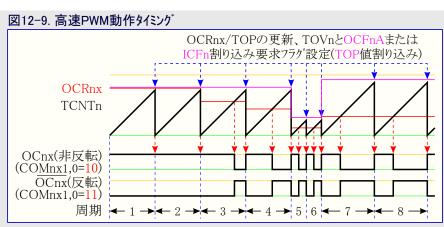

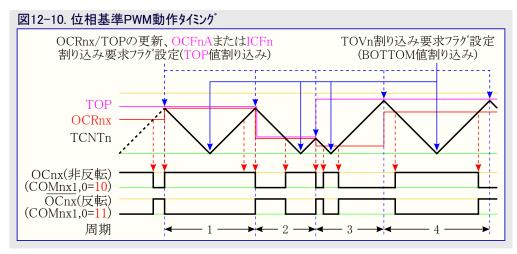

|     | 12.8.  | 動作種別 •••••• 49                                                                                                                                                                                                                                                                                                                    |

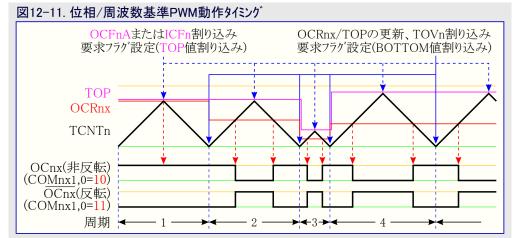

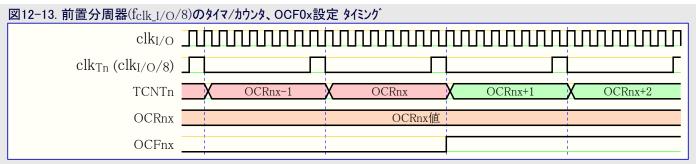

|     | 12.9.  | タイマ/カウンタのタイミング 図 ・・・・ 53                                                                                                                                                                                                                                                                                                          |

|     | 12.10. | <b>16L</b> <sup>*</sup> ット レシ <sup>*</sup> スタのアクセス 54                                                                                                                                                                                                                                                                             |

|     | 12.11. | 16ビット タイマ/カウンタ0用レシ <sup>*</sup> スタ ····· 56                                                                                                                                                                                                                                                                                       |

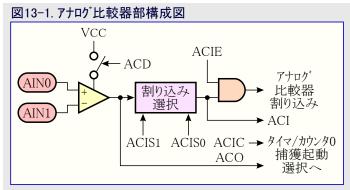

| 13. | アナロク   | *比較器 ••••••62                                                                                                                                                                                                                                                                                                                     |

|     | 13.1.  | アナログ比較器用レジスタ ・・・・ 62                                                                                                                                                                                                                                                                                                              |

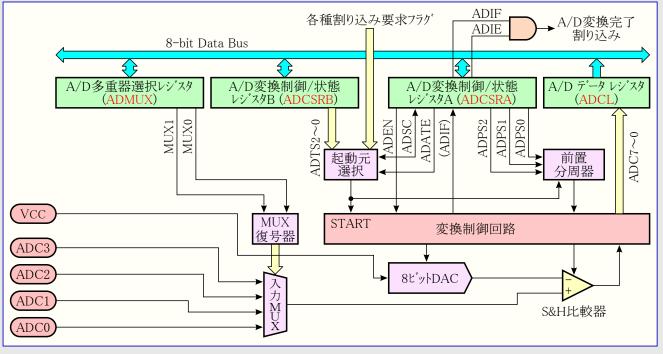

| 14. | A/D 弦  | <b>E換器</b> 64<br>特徵 64<br>概要 64                                                                                                                                                                                                                                                                                                   |

|     | 14.1.  | 特徴 ••••••64                                                                                                                                                                                                                                                                                                                       |

|     | 14.2.  | 概要 ••••••64                                                                                                                                                                                                                                                                                                                       |

|     | 14.3.  | 操作 •••••• 64                                                                                                                                                                                                                                                                                                                      |

|     | 14.4.  | <b>変換の開始</b> ······ 65                                                                                                                                                                                                                                                                                                            |

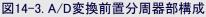

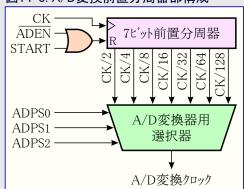

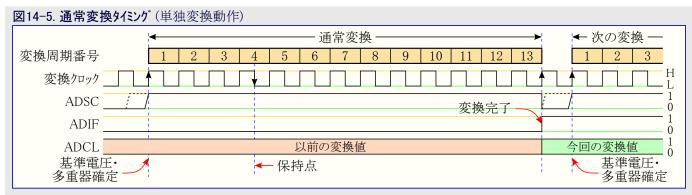

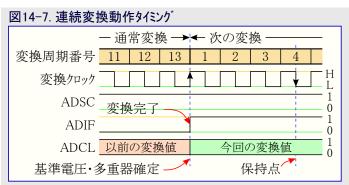

|     | 14.5.  | 前置分周と変換タイミング ・・・・・・・・・・・・・・ 65                                                                                                                                                                                                                                                                                                    |

|     | 14.6.  | <ul> <li>前置方向と変換外(シ)</li> <li>チャネル変更と基準電圧</li> <li>4音低減機能</li> <li>67</li> <li>アナログ入力回路</li> <li>67</li> </ul>                                                                                                                                                                                                                    |

|     | 14.7.  | <b>雑音低減機能</b> •••••• 67                                                                                                                                                                                                                                                                                                           |

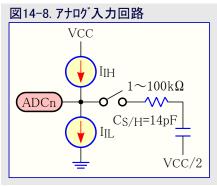

|     | 14.8.  | <b>アナログ入力回路</b> •••••••67                                                                                                                                                                                                                                                                                                         |

|     | 14.9.  | <b>維首低减技術</b> ******************************68                                                                                                                                                                                                                                                                                    |

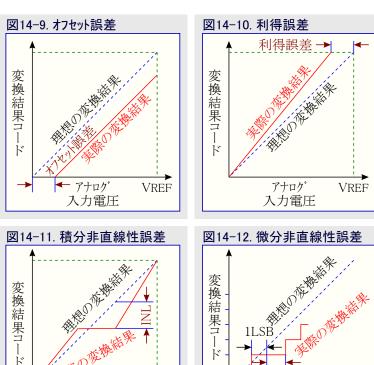

|     | 14.10. | A/D変換の精度定義 ······ 68                                                                                                                                                                                                                                                                                                              |

|     | 14.11. | A/D変換の結果 ······ 68                                                                                                                                                                                                                                                                                                                |

|     | 14.12. | A/D変換用レジスタ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                                                                                    |

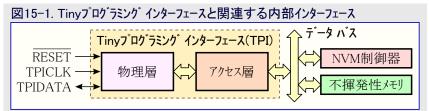

| 15. | プログラ   | <b>דבילי לטארסברא הארט אין אין אין אין אין אין אין אין אין אין</b>                                                                                                                                                                                                                                                                |

|     | 15.1.  | 特徴                                                                                                                                                                                                                                                                                                                                |

|     | 15.2.  | 概要 •••••• 71                                                                                                                                                                                                                                                                                                                      |

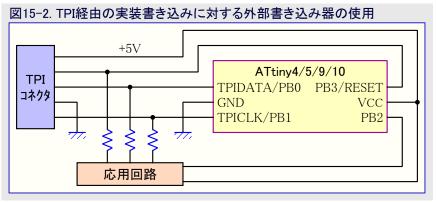

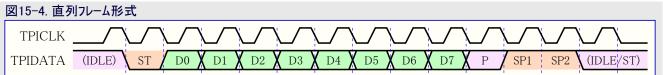

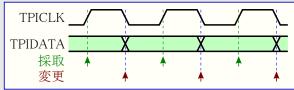

|     | 15.3.  | Tinyプログラミング インターフェースの物理層 ・・・・・ 71                                                                                                                                                                                                                                                                                                 |

|     | 15.4.  | <b>Tinyプログラミング インターフェースのアクセス層</b> ・・・・・ 74                                                                                                                                                                                                                                                                                        |

|     | 15.5.  | <b>命令一式</b> ······ 74                                                                                                                                                                                                                                                                                                             |

|     | 15.6.  | <b>不揮発性メモリ制御器のアクセス</b> ・・・・・ 76                                                                                                                                                                                                                                                                                                   |

|     | 15.7.  | 制御/状態空間レジスタ説明 ・・・・・ 76                                                                                                                                                                                                                                                                                                            |

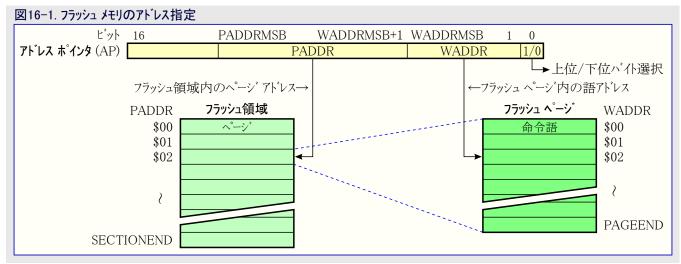

| 16. | メモリこ   | <b>プログラミング・・・・・</b> 78                                                                                                                                                                                                                                                                                                            |

|     | 16.1.  | 特徴 ····· 78                                                                                                                                                                                                                                                                                                                       |

|     | 16.2.  | 概要 •••••• 78                                                                                                                                                                                                                                                                                                                      |

|     | 16.3.  | 不揮発性メモリ ····································                                                                                                                                                                                                                                                                                      |

|     | 16.4.  | <b>NVMのアクセス</b>                                                                                                                                                                                                                                                                                                                   |

|     | 16.5.  | <b>自己プログラミンク</b> ゙・・・・・82                                                                                                                                                                                                                                                                                                         |

|     | 16.6.  | <b>外部プログラミンク</b> ゙・・・・・・82                                                                                                                                                                                                                                                                                                        |

|     | 16.7.  | <b>NVMプログラミング用レジスタ</b> ・・・・・ 83                                                                                                                                                                                                                                                                                                   |

| 17. | 電気的    | 外部プログラミング       82         NVMプログラミング用レジスタ       83         均特性       84         絶対最大定格       84         DC特性       84         速度       85         クロック特性       85         システムとリセットの特性       85         アナログ比較器特性       86         直列プログラミング特性       87         寺性       88         周辺機能部供給電流       88         活動動作消費電流       88 |

|     | 17.1.  | <b>絶対最大定格</b> ************************************                                                                                                                                                                                                                                                                                |

|     | 17.2.  | <b>DC特性</b> ······ 84                                                                                                                                                                                                                                                                                                             |

|     | 17.3.  | <b>速度</b> ······85                                                                                                                                                                                                                                                                                                                |

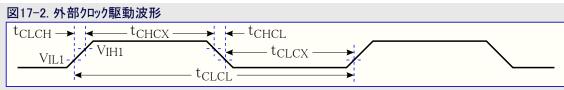

|     | 17.4.  | <b>クロック特性</b> ************************************                                                                                                                                                                                                                                                                                |

|     | 17.5.  | <b>システムとリセットの特性 ・・・・・ 85</b>                                                                                                                                                                                                                                                                                                      |

|     | 17.6.  | <b>アナログ比較器特性</b> ************************************                                                                                                                                                                                                                                                                             |

|     | 17.7.  | A/D変換器特性 ······ 86                                                                                                                                                                                                                                                                                                                |

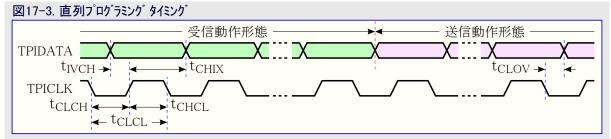

|     | 17.8.  | <b>直列プログラミング特性</b> *********************************87                                                                                                                                                                                                                                                                            |

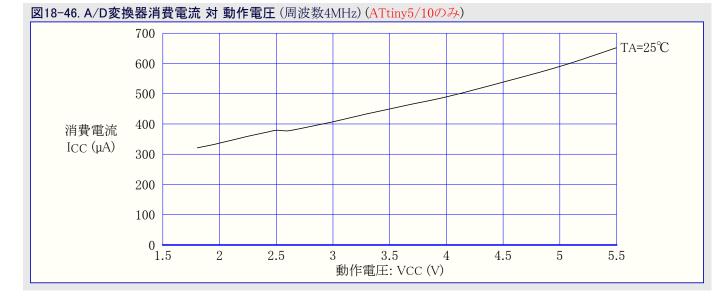

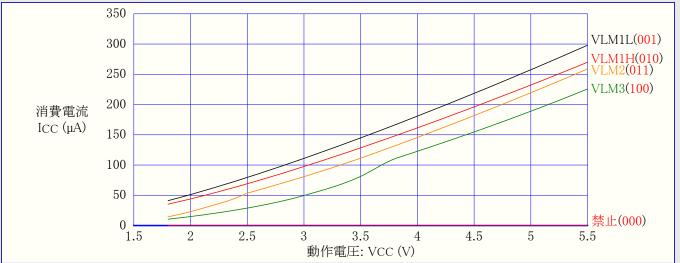

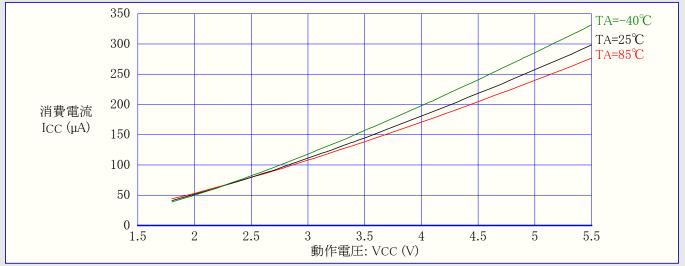

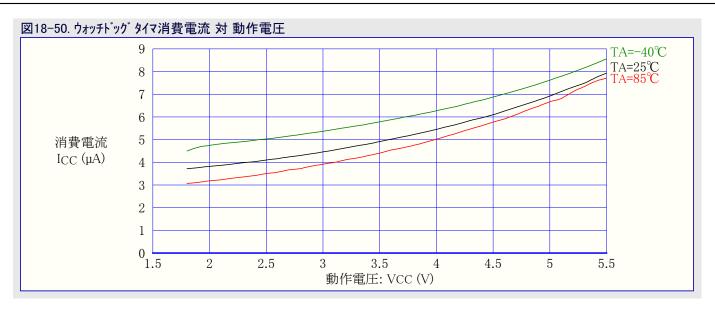

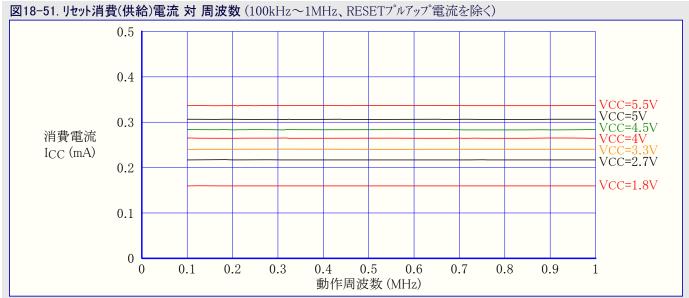

| 18. | 代表物    | 寺性 •••••• 88                                                                                                                                                                                                                                                                                                                      |

|     | 18.1.  | 周辺機能部供給電流 •••••• 88                                                                                                                                                                                                                                                                                                               |

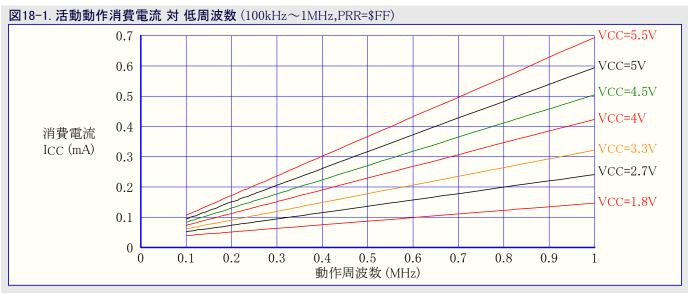

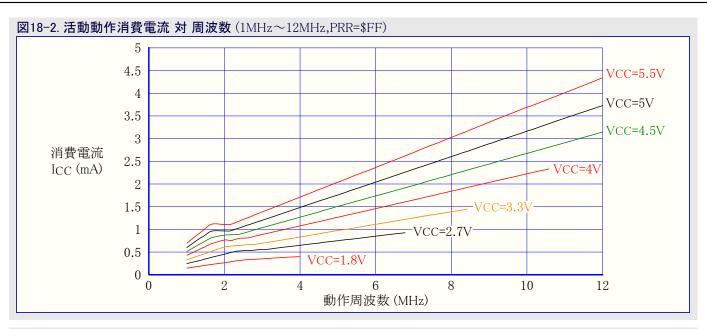

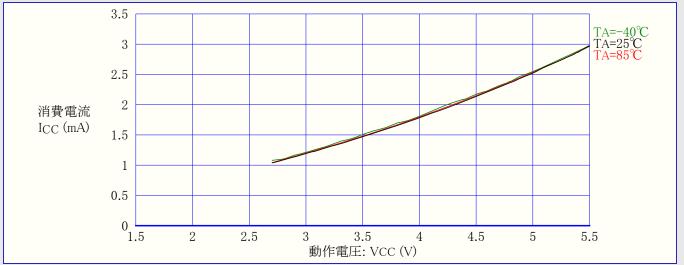

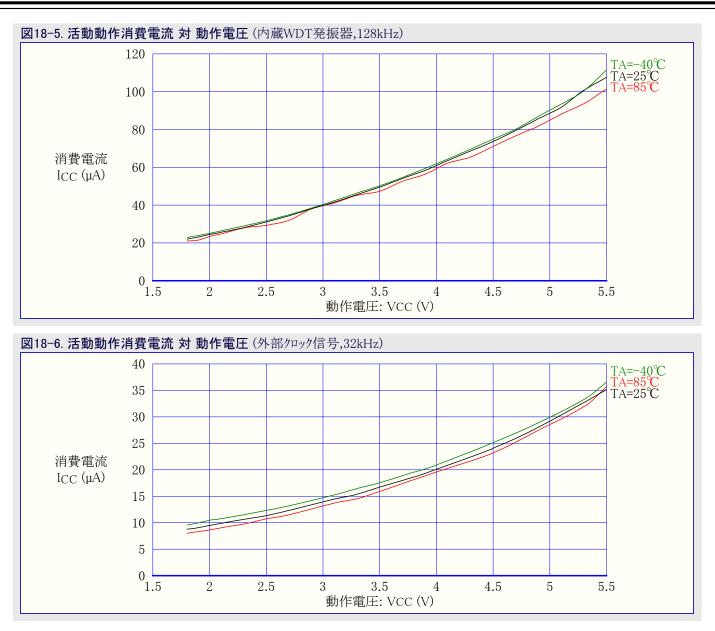

|     | 18.2.  | 活動動作消費電流 ······ 88<br>アイドル動作消費電流 ····· 90                                                                                                                                                                                                                                                                                         |

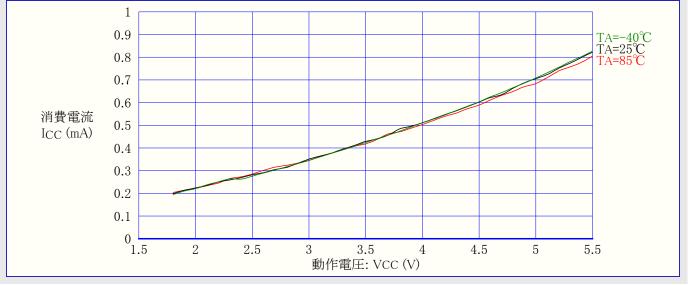

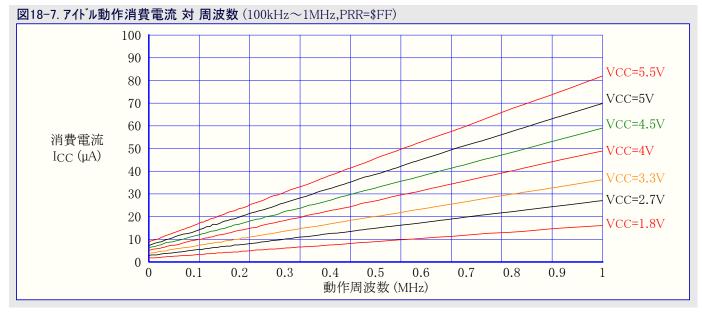

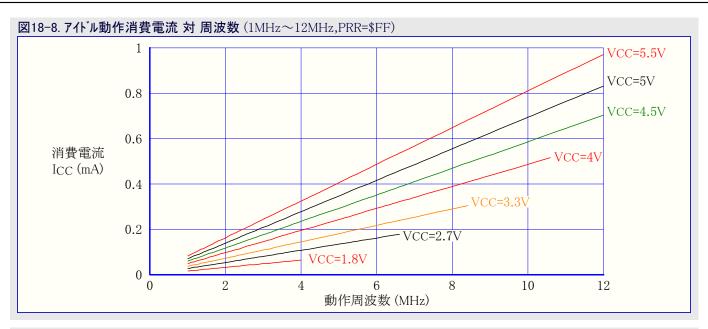

|     | 18.3.  | アイドル動作消費電流 ・・・・・ 90                                                                                                                                                                                                                                                                                                               |

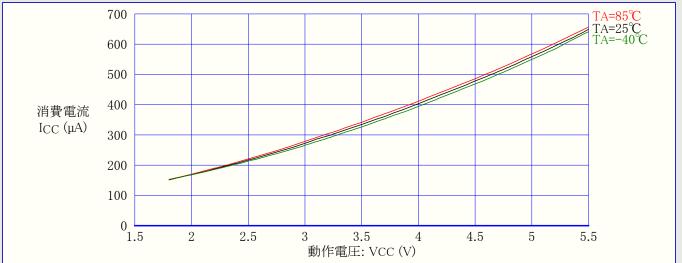

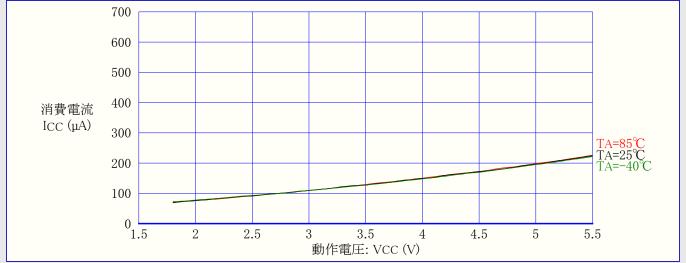

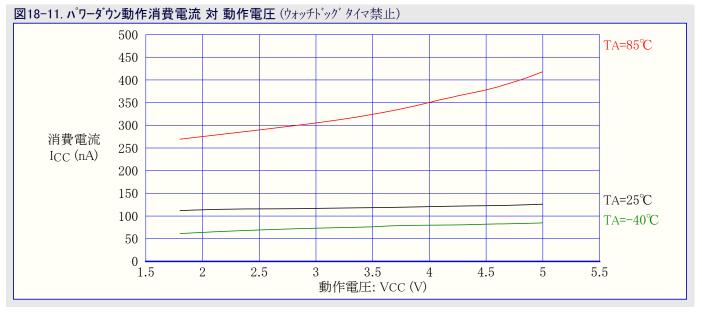

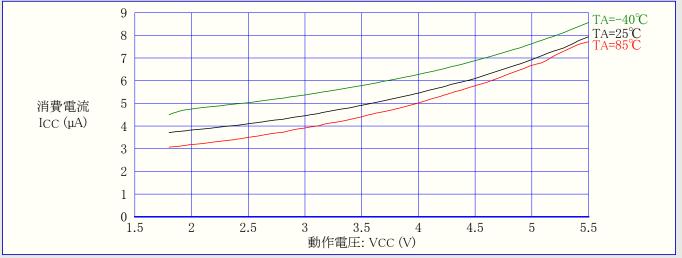

|     | 18.4.  | <b>パワーダウン動作消費電流</b> ・・・・・・・・・・・・・・・92                                                                                                                                                                                                                                                                                             |

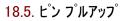

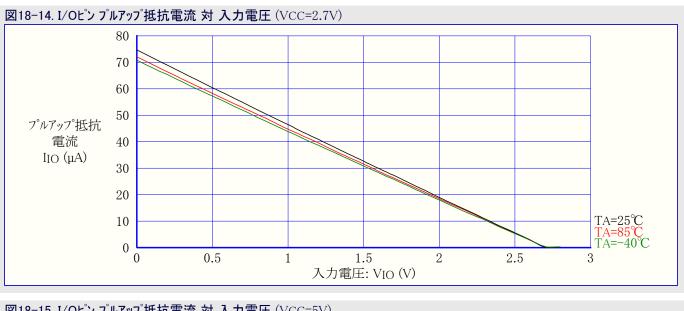

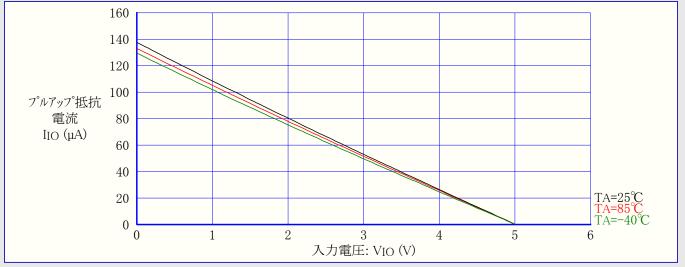

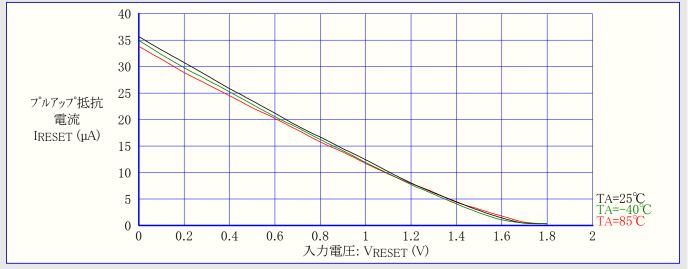

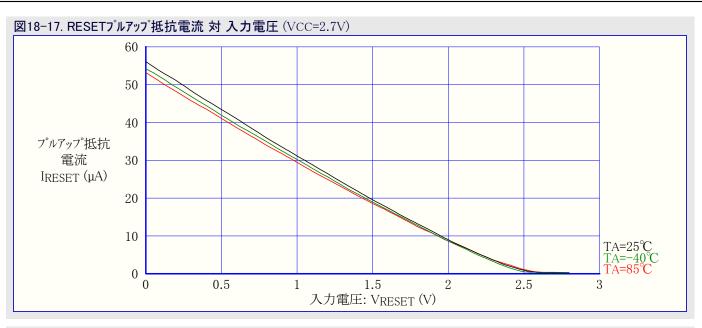

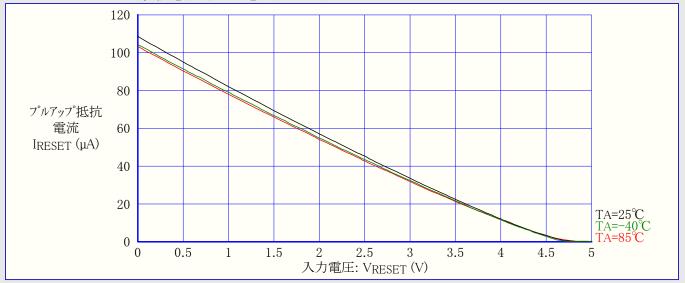

|     | 18.5.  | <b>ピン プルアップ</b> ····· 92                                                                                                                                                                                                                                                                                                          |

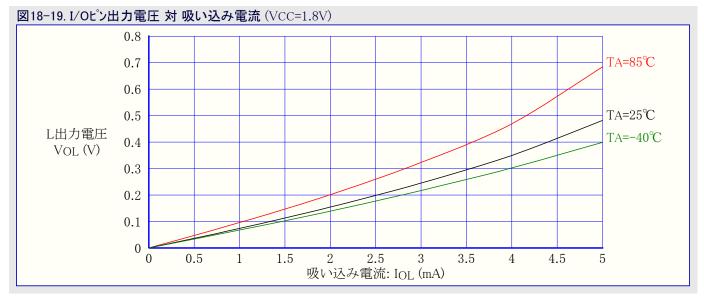

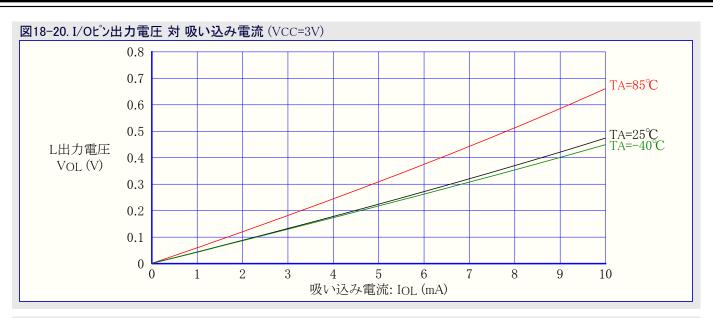

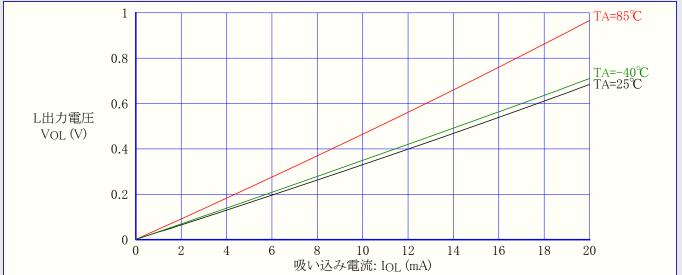

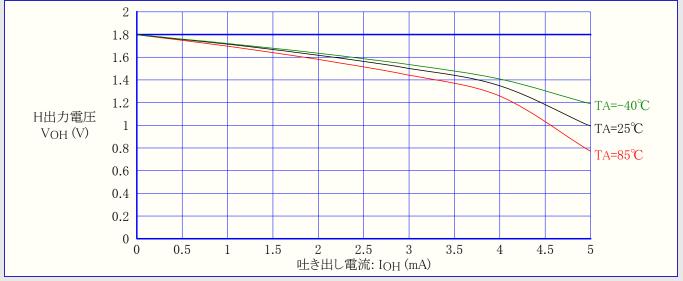

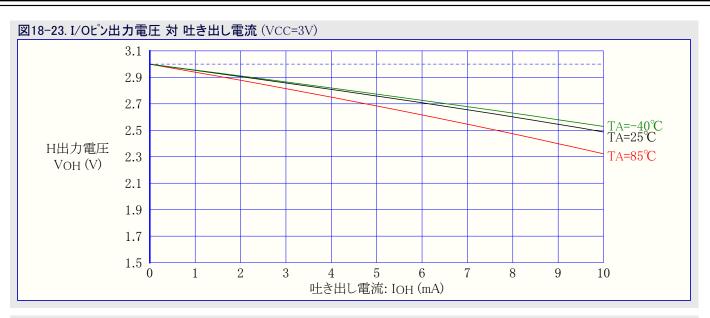

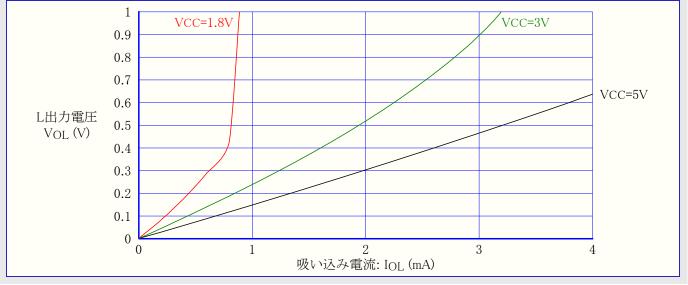

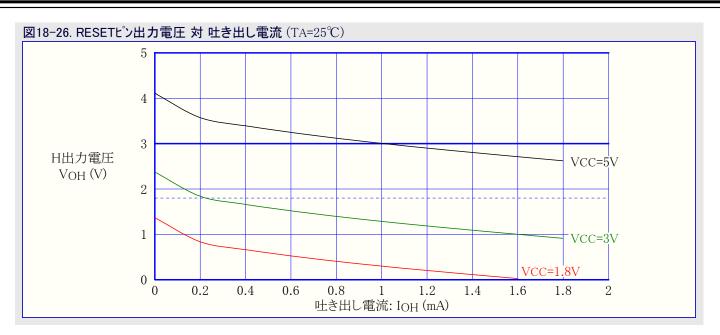

|     | 18.6.  | <b>ピン駆動能力</b> ······ 93                                                                                                                                                                                                                                                                                                           |

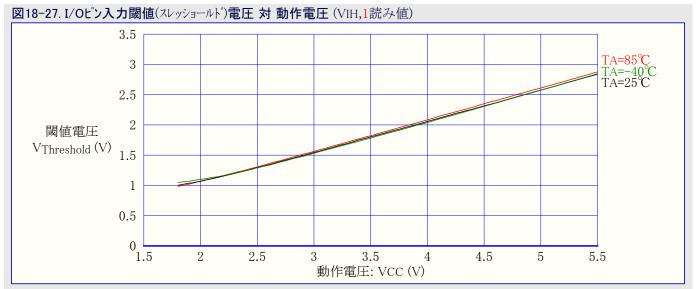

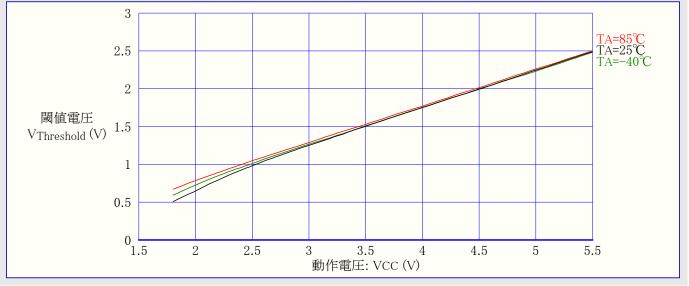

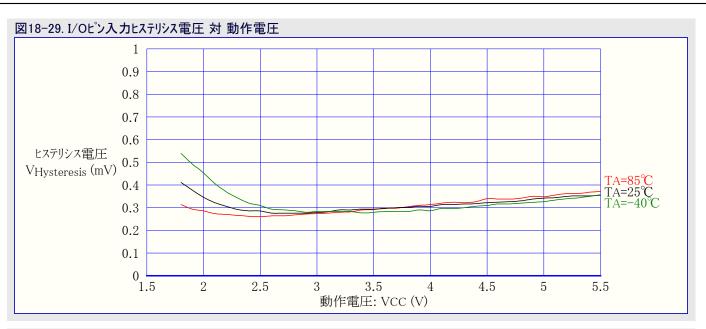

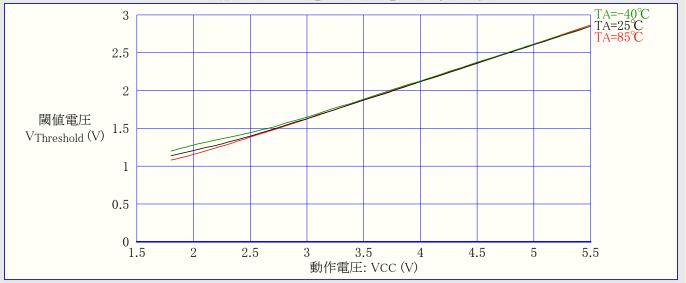

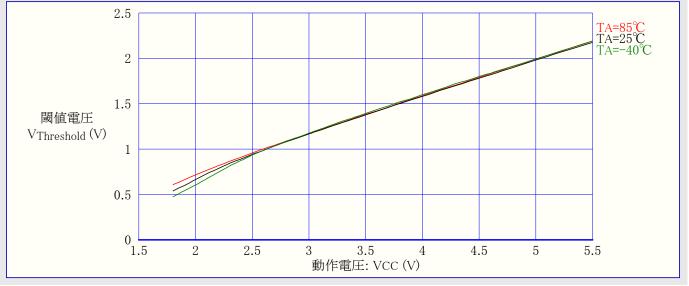

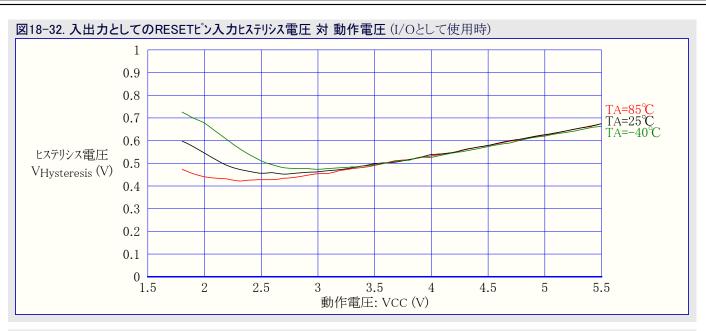

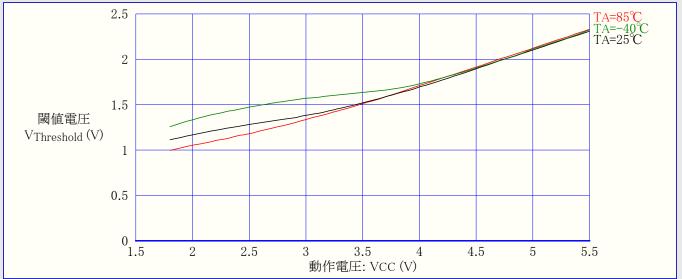

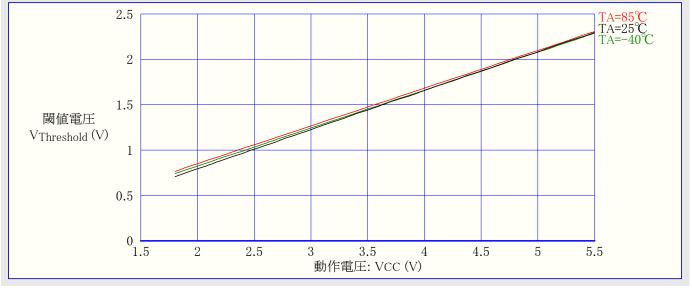

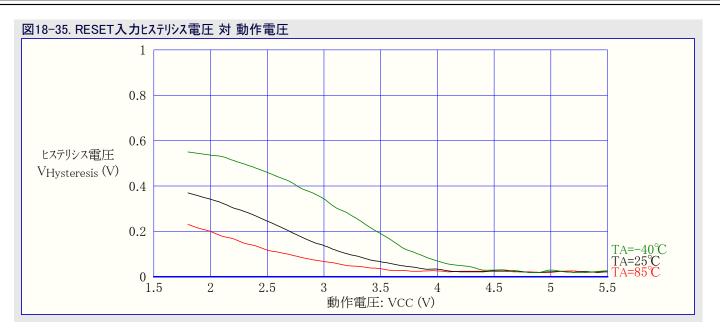

|     | 18.7.  | <b>ピン 閾値とヒステリシス ······ 97</b>                                                                                                                                                                                                                                                                                                     |

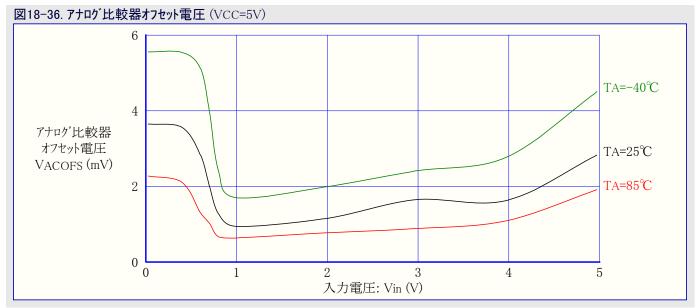

|     | 18.8.  | <b>アナログ比較器オフセット</b> ・・・・・・・・・・・・・・・・・・・・・・100                                                                                                                                                                                                                                                                                     |

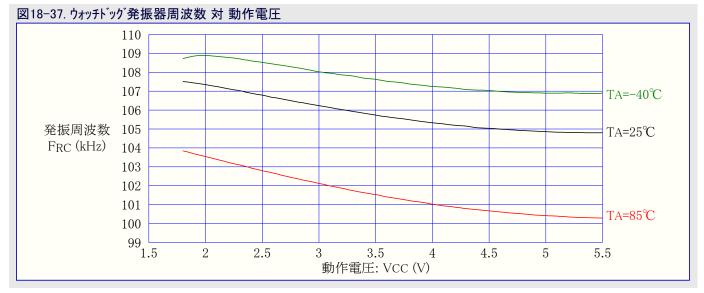

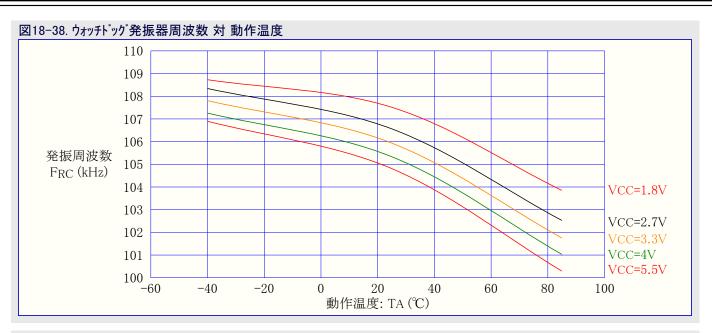

|     | 18.9.  | <b>内部発振器周波数</b> ••••••100                                                                                                                                                                                                                                                                                                         |

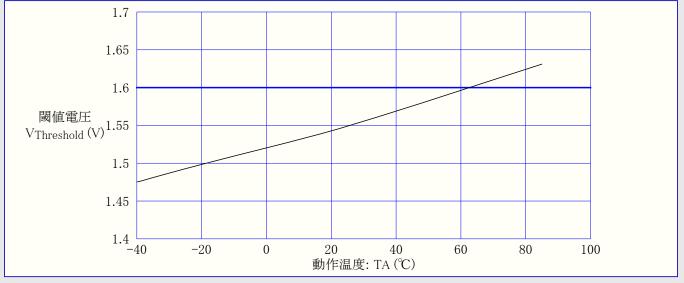

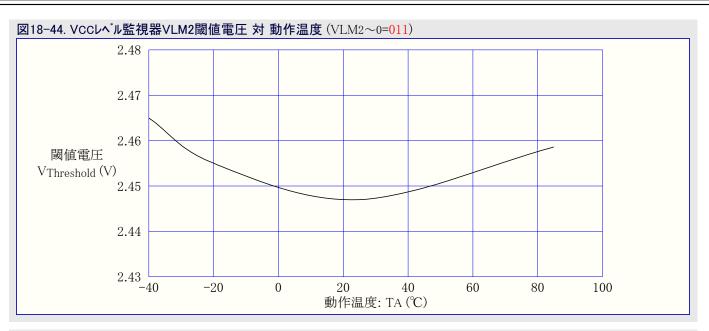

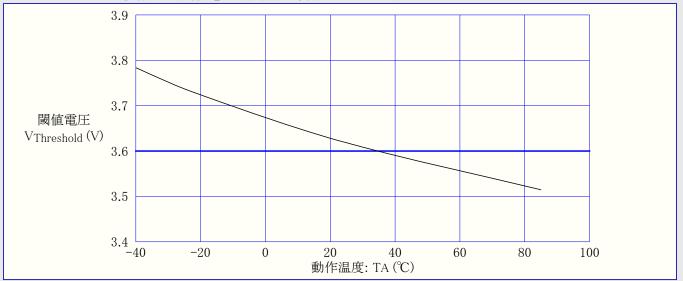

|     | 18.10. | <b>VLM閾值</b> ······ 102                                                                                                                                                                                                                                                                                                           |

|     | 18.11. | アイドル動作消費電流       90         パワーダウン動作消費電流       92         ピンプルアップ       92         ピン駆動能力       93         ピン閾値とヒステリシス       97         アナログ比較器オフセット       100         内部発振器周波数       102         周辺機能部消費電流       103                                                                                                             |

|     |        |                                                                                                                                                                                                                                                                                                                                   |

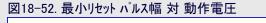

|     | 18.1 <b>2</b> . | リセット消費電流とリセット パルス幅 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |

|-----|-----------------|---------------------------------------------------------|

| 19. | レジス             | <b>要約</b> · · · · · · · · · · · · · · · · · · ·         |

| 20. | 命令              | 要約 •••••• 107                                           |

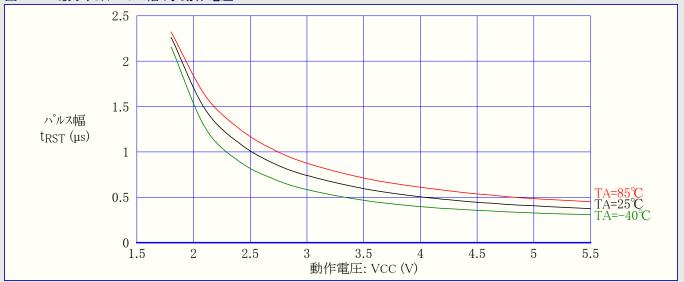

| 21. | 外囲              | 器情報 ····· 109                                           |

|     | <b>21</b> .1.   | <b>6ST1</b>                                             |

|     | 21.2.           | 8MA4 · · · · · 109                                      |

| 22. | 障害              | <b>青報 ••••••</b> 110                                    |

| 23. | データン            | <b>/-ト改訂履歴 ·····</b> 111                                |

|     | 23.1.           | <b>改訂8127A - 2009年4月 ·····</b> 111                      |

|     | 23.2.           | <b>改訂8127B - 2009年8月 ······</b> 111                     |

|     | 23.3.           | <b>改訂8127C - 2009年10月 ······</b> 111                    |

|     | 23.4.           | <b>改訂8127D - 2010年2月 ······</b> 111                     |

|     | 23.5.           | <b>改訂8127E - 2011年11月</b> ······ 112                    |

|     | 23.6.           | <b>改訂8127F - 2013年2月</b> ······ 112                     |

|     | 23.7.           | <b>改訂8127G - 2015年9月</b> ····· 112                      |

|     | 23.8.           | 改訂8127H - 2016年11月 ····· 112                            |

|     | 23.9.           | <b>改訂A - 2018年8月</b> ····· 112                          |

# 1. ピン配置

# 1.1. ピン概要

1.1.1. VCC

電圧供給

1.1.2. GND

接地

**1.1.3. PB3~PB0** (术°一卜B)

ポートBはビット単位で選択される内蔵プルアップ抵抗付きの4ビット双方向入出力ポートです。出力緩衝部は共に高い吐き出し/吸い込み 能力の対称駆動特性です。入力としてプルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートビンには吐き出し電流が流れ ます。リセット条件が有効になると、例えクロックが動いていなくても、ポートビンはHi-Zにされます。

ポートは38頁で一覧にされるように、ATtiny4/5/9/10の様々な特殊な特徴の機能も扱います。

# 1.1.4. RESET

リセット入力。リセット ピンが禁止されていなければ、例えクロックが走行していなくても、最小パルス幅より長いこのピンのLowレヘルはリセットを生成します。最小パルス幅は85頁の表17-4.で与えられます。より短いパルスはリセットの生成が保証されません。 リセット ピンは((駆動能力の)弱い)入出力ピンとしても使うことができます。

# 2. 注文情報

| デバイス     | 電源電圧             | 速度(MHz) ( <mark>注1</mark> ) | 動作範囲                                | 外囲器 ( <u>注</u> 2) | 注文コート <sup>*</sup> (注3)           |

|----------|------------------|-----------------------------|-------------------------------------|-------------------|-----------------------------------|

|          |                  | 12                          | 工業用 (-40℃~85℃) ( <b>注4</b> )        | 6ST1              | ATtiny4-TSHR ( <mark>注5</mark> )  |

| ATtiny4  | $1.8 \sim 5.5 V$ | 12                          | 工業用(-40℃-85℃)(/±4)                  | 8MA4              | ATtiny4-MAHR ( <mark>注6</mark> )  |

|          |                  | 10                          | 拡張品 (-40℃~125℃) ( <mark>注6</mark> ) | 6ST1              | ATtiny4-TS8R ( <mark>注5</mark> )  |

|          |                  | 12                          | 工業用 (-40℃~85℃) ( <b>注4</b> )        | 6ST1              | ATtiny5-TSHR ( <b>注5</b> )        |

| ATtiny5  | 1.8~5.5V         | 12                          | 工采用(=400=*850)(元4)                  | 8MA4              | ATtiny5-MAHR ( <mark>注6</mark> )  |

|          |                  | 10                          | 拡張品 (-40℃~125℃) ( <mark>注6</mark> ) | 6ST1              | ATtiny5-TS8R ( <mark>注5</mark> )  |

|          | $1.8 \sim 5.5 V$ | 12                          | 工業用 (-40℃~85℃) ( <b>注4</b> )        | 6ST1              | ATtiny9-TSHR ( <b>注5</b> )        |

| ATtiny9  |                  | 12                          |                                     | 8MA4              | ATtiny9-MAHR ( <mark>注6</mark> )  |

|          |                  | 10                          | 拡張品 (-40℃~125℃) ( <mark>注6</mark> ) | 6ST1              | ATtiny9-TS8R ( <mark>注5</mark> )  |

|          |                  | 12                          | 工業用 (-40℃~85℃) ( <mark>注4</mark> )  | 6ST1              | ATtiny10-TSHR ( <mark>注5</mark> ) |

| ATtiny10 | $1.8 \sim 5.5 V$ | 12                          |                                     | 8MA4              | ATtiny10-MAHR ( <mark>注6</mark> ) |

|          |                  | 10                          | 拡張品 (-40℃~125℃) ( <mark>注6</mark> ) | 6ST1              | ATtiny10-TS8R ( <mark>注5</mark> ) |

注1: 速度対電源電圧については85頁の「17.3. 速度」項をご覧ください。

注2: 全ての外囲器は鉛フリー、ハロゲン化合物フリーで完全に安全で、これらは有害物質使用制限に関する欧州指令(RoHS指令)に 適合します。

注3: テープとリール。

注4: このデバイスはウェハー(チップ<sup>®</sup>単体)形状でも供給できます。最低数量と詳細な注文情報については最寄のMicrochip営業所へお 問い合わせください。

注5: 表側/裏側印は以下のとおりです。

- 表: 各々、T4x,T5x,T9x,T10x、ここでのx=ダイ改訂番号

- 裏: zHzzzまたはz8zzz、ここでのH=(-40℃~85℃)と8=(-40℃~125℃)

注6: このデバイスに関する電気的特性と代表特性についてはwww.microchip.comで追補A:125℃でのATtiny4/5/9/10仕様を調べてください。

|      | 外囲器形式                                      |  |  |  |  |  |

|------|--------------------------------------------|--|--|--|--|--|

| 6ST1 | 6リート・2.90×1.60mm プラスティック小型外形外囲器 (SOT23)    |  |  |  |  |  |

| 8MA4 | 6パッド2×2×0.6mm プラスティック極薄2列平板リードなし外囲器 (UDFN) |  |  |  |  |  |

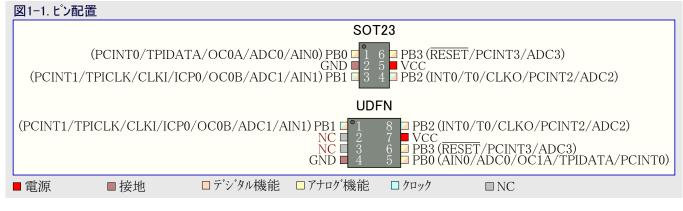

# 3. 概要

ATtiny4/5/9/10は簡潔なAVR強化RISC構造を基にした低消費CMOS 8ビットマイクロコントローラです。1クロック周期での強力な命令の実行により、ATtiny4/5/9/10はMHzあたり1MIPSに達する処理量を成し遂げ、処理速度対消費電力の最適化を設計者に許します。

AVRコアは16個の汎用作業レジスタを伴う豊富な命令群とシステムレジスタを結合します。全レジスタはALU(Arithmetic Logic Unit)に直結され、1クロック周期で実行される単一命令でのアクセスを2つの独立したレジスタに許します。その結果としての基本構造は簡潔且つコート、効率的で、同時に伝統的なCISC型マイクロコントローラに対して10倍程度までの処理量を達成します。

ATtiny4/5/9/10は512/1024ベイトの実装書き込み可能なフラッシュメモリ、32ベイトのSRAM、4本の汎用入出力線、16個の汎用作業レジス タ、2つのPWMチャネルを持つ16ビット タイマ/カウンタ、内部及び外部割り込み、内蔵発振器付きの設定変更可能なウォッチドッグ タイマ、校正 付き内蔵発振器、ソフトウェアで選択できる4つの低消費動作を提供します。ATtiny5/10には4チャネルの8ビット A/D変換器も装備されてい ます。

アイドル動作はCPUを停止し、一方SRAM、タイマ/ カウンタ、A/D変換器(ATtiny5/10のみ)、アナログ比較器、割り込み機構に機能の継続を 許します。A/D変換雑音低減動作はA/D変換器を除く全I/O部とCPUを停止することによってA/D変換中の切り替え雑音を最小にし ます。パワーダウン動作ではレジスタがそれらの内容を保ち、次の割り込みかハードウェアリセットまで、全てのチップ機能が禁止されます。スタン パイ動作ではデバイスの残りが休止する一方で発振器が走行し、低消費電力と組み合わされた非常に速い始動を許します。

本デバイスは高密度不揮発性メモリ技術を使って製造されます。チップ上の実装書き換え可能なフラッシュ メモリは伝統的な不揮発性メモリ書 き込み器による実装書き換えをプログラム用メモリに許します。

ATtiny4/5/9/10 AVRはマクロ アセンブラと評価キットを含む完全なプログラム及びシステム開発ツールの1式によって支援されます。

# 3.1. ATtiny4,ATtiny5,ATtiny9,ATtiny10の比較

デバイスの比較は表3-1.で示されます。

# 表3-1. ATtiny4,ATtiny5,ATtiny9,ATtiny10間の違い

| デバイス名    | フラッシュ メモリ           | A/D変換器 | 識票             |

|----------|---------------------|--------|----------------|

| ATtiny4  | 512バイト              | 無      | \$1E,\$8F,\$0A |

| ATtiny5  | 512バイト              | 有      | \$1E,\$8F,\$09 |

| ATtiny9  | 1Kハ <sup>*</sup> イト | 無      | \$1E,\$90,\$08 |

| ATtiny10 | 1Kハ <sup>*</sup> イト | 有      | \$1E,\$90,\$03 |

# 4. 一般情報

# 4.1. 資料

包括的なドライハ、応用記述、データシート、及び開発ツールの説明はwww.microchip.comでのダウンロートで利用可能です。

# 4.2. コート 例

この資料はデバイスの様々な部分の使用法を手短に示す簡単なコート`例を含みます。これらのコート`例はアセンブルまたはコンパイルに先 立って、デバイス定義ヘッダファイルがインクルートされると仮定します。全てのCコンパイラ製造業者がヘッダファイル内にビット定義を含めるとは限 らず、またCでの割り込みの扱いがコンパイラに依存することに注意してください。より多くの詳細についてはCコンパイラの資料で確認し てください。

# 4.3. 容量性接触感知

QTouchライフ<sup>\*</sup>ラリは殆どのAVRマイクロコントローラでの接触感知インターフェースに対する使い易い解決策を提供します。QTouchライフ<sup>\*</sup>ラリは QTouch<sup>®</sup>とQMatrix™の採取法に対する支援を含みます。

接触感知はQTouchライブラリをリンクして接触チャネルと感知器を定義するのに応用プログラミングインターフェース(API)を使うことによってどの応用にも容易に追加することができます。チャネル情報を取得して接触感知器の状態を判断するために応用はその後に接触感知APIを呼び出します。

QTouchライブラリは無料でウェブサイトからダウンロート・することができます。より多くの情報と実装の詳細についてはウェブサイトからも入手可能な「QTouchライブラリ使用者の手引き」を参照してください。

# 4.4. データ保持力

信頼性証明結果はデータ保持誤り率の反映を示し、20年以上/85℃または100年以上/25℃で1PPMよりずっと小さな値です。

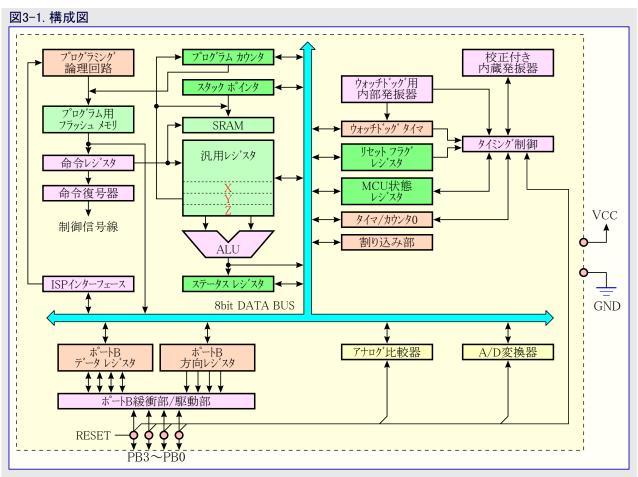

# 5. AVR CPU 37

本項はAVRコア構造を一般的に説明します。このCPUコアの主な機能は正しいプログラム実行を保証することです。従ってCPUはメモリアク セス、計算実行、周辺制御、割り込み操作ができなければなりません。

# 5.1. 基本構造概要

最大効率と平行処理のため、AVRはプログラムとデータに対してメモリ とハ、スを分離するハーハート、構造を使います。プログラムメモリ内の命令 は単一段のハペイプラインで実行されます。1命令の実行中に次の命 令がプログラムメモリから事前取得されます。この概念は全部のクロック 周期で命令実行を可能にします。プログラムメモリは実装書き換え可 能なフラッシュメモリです。

高速レジスタファイルは1クロック周期アクセスの16個の8ビット長汎用レジスタを含みます。これは1クロック周期ALU(Arithmetic Logic Unit)操作を許します。代表的なALU操作では2つのオペラントがレジスタファイルからの出力で、1クロック周期内でその操作が実行されてその結果がレジスタファイルに書き戻されます。

16個中の6つのレシ、スタは効率的なアトレス計算ができるデータ空間ア トレス指定用に3つの16ビット長間接アトレスポインタ用レシ、スタとして使 われます。これらアトレスポインタの1つはプログラム用フラッシュメモリ内の 定数表参照用アトレスポインタとしても使えます。これら16ビット長付加 機能レシ、スタはX,Y,Zレシ、スタで、本項内で後述されます。

ALUはレシ、スタ間またはレシ、スタと定数間の算術及び論理操作を支援します。単一レシ、スタ操作もALUで実行できます。算術演算操作後、操作結果についての情報を反映するために、ステータスレシ、スタ(SREG)が更新されます。

#### 図5-1. AVR構造構成図

プログラムの流れは条件/無条件分岐や呼び出し命令によって提供され、全アトレス空間を直接アトレス指定する能力があります。殆どの AVR命令は単一16ビット語(ワート)形式ですが、32ビット幅の命令も存在します。実際の命令1式はいくつかのデバイスが(全)命令1式の部 分だけを実装するように変わります。

割り込みやサブルーチン呼び出し中、戻りアドレスを示すプログラムカウンタ(PC)はスタックに保存されます。スタックは一般的なデータ用SRAM上に 実際には割り当てられ、従ってスタック容量はSRAM容量とSRAM使用量でのみ制限されます。全ての使用者プログラムはリセット処理ルーチ ンで(サブルーチン呼び出しや割り込みが実行される前に)、スタックポインタ(SP)を初期化しなければなりません。SPはI/O空間で読み書きア クセスが可能です。データ用SRAMはAVR構造で支援される4つの異なるアドレス指定種別を通して容易にアクセスできます。

AVR構造に於けるメモリ空間は全て直線的な普通のメモリ配置です。

柔軟な割り込み部にはI/O空間の各制御レジスタとステータスレジスタ(SREG)の特別な全割り込み許可(I)ビットがあります。全ての割り込み は割り込み、ケクタ表に個別の割り込み、ケクタを持ちます。割り込みには割り込み、ケクタ表の位置に従う優先順があります。下位側割り込 み、ケクタアドレスが高い優先順位です。

I/Oメモリ空間は制御レシ、スタや他のI/O機能としてCPU周辺機能用の64アドレスを含みます。I/Oメモリはデータ空間位置\$0000~\$003Fとしてアクセスできます。

# **5.2.** ALU (Arithmetic Logic Unit)

高性能なAVRのALUは16個全ての汎用レジスタに直接接続され動作します。汎用レジスタ間または汎用レジスタと即値間の演算操作は 単一クロック周期内で実行されます。ALU操作は算術演算、論理演算、ビット操作の3つの主な種類に大別されます。符号付きと符号な し両方の乗算と固定小数点形式を支援する乗算器(乗算命令)も提供する構造の実装(製品)もあります。詳細記述については「AVR 命令一式」資料と110頁の「命令要約」章をご覧ください。

# 5.3. ステータス レジスタ

ステータスレジスタは最も直前に実行した演算命令の結果についての情報を含みます。この情報は条件処理を行うためのプログラムの流 れ変更に使えます。ステータスレジスタは「AVR命令ー式」資料と107頁の「命令要約」章で詳述されるように、全てのALU操作後、更新さ れることに注目してください。これは多くの場合でそれ用の比較命令使用の必要をなくし、高速でより少ないコート、に帰着します。

ステータス レジスタは割り込み処理ルーチン移行時の保存と割り込みからの復帰時の回復(復帰)が自動的に行われません。これはソフトウェアによって扱われなければなりません。

# 5.4. 汎用レジスタ ファイル

このレシブスタファイルはAVRの増強したRISC命令群用に最適化されています。必要な効率と柔軟性を達成するために、次の入出 力機構がレシブスタファイルによって支援されます。

- ・1つの8ビット出力オペラントと1つの8ビットの結果入力

- ・2つの8ビット出力オペラントと1つの8ビットの結果入力

・1つの16ビット出力オペラントと1つの16ビットの結果入力

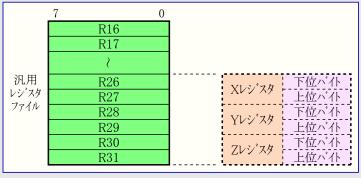

右の図5-2.はCPU内の16個の汎用作業レジスタの構造を示します。

注: AVRレジスタファイルの代表的な実装は32個の汎用レシ、スタを 含みますが、ATtiny4/5/9/10は16個のレジスタだけを実装し ます。互換性のため、レシ、スタはR0~R15ではなく、R16~ R31で番号付けされます。

#### 図5-2. AVR CPU 汎用レジスタ構成図

レジスタファイルを操作する殆どの命令は全てのレジスタに直接アクセスし、それらの殆どは単一クロック周期命令です。

# 5.4.1. Xレシ スタ, Yレシ スタ, Zレシ スタ

R26~R31レジスタには通常用途の使用にいくつかの追加機能 があります。これらのレジスタはデータ空間の間接アトス指定用の16 ビットアトレスホプインタです。3つのX,Y,Z間接アトレスレジスタは図 5-3.で記載したように定義されます。

各種アドレス指定動作でこれらのアドレス レジスタは自動増加、自動 減少として機能します(詳細については「AVR命令ー式」資料と 107頁の「命令要約」章をご覧ください)。

# 図5−3. X,Y,Zレジスタ構成図

|         | 15 | XH (上位)    |     | XL (下位)    | 0 |

|---------|----|------------|-----|------------|---|

| Χ レシ スタ | 7  | R27 (\$1B) | 0 7 | R26 (\$1A) | 0 |

|         | 15 | YH (上位)    |     | YL (下位)    | 0 |

| Y レシ スタ | 7  | R29 (\$1D) | 0 7 | R28 (\$1C) | 0 |

|         | 15 | ZH (上位)    |     | ZL (下位)    | 0 |

| Ζ レシ スタ | 7  | R31 (\$1F) | 0 7 | R30 (\$1E) | 0 |

# **5.5.** スタック ポインタ

スタックは主に一時データの保存、局所変数の保存、割り込みとサブルーチン呼び出し後の戻りアドレスの保存に使われます。スタック ポインタレ ジスタは常にこのスタックの先頭(<mark>訳注</mark>:次に使われるべき位置)を指し示します。スタックは高位メモリから低位メモリへ伸長するように実行され ることに注意してください。これはスタックPUSH命令がスタックポインタを減らすことを意味します。

スタック ポインタはサブルーチンと割り込みのスタックが配置されたデータSRAMのスタック領域を指し示します。データSRAM内のスタック空間は何れ かのサブルーチン呼び出しが実行される、または割り込みが許可されるのに先立ってプログラムによって定義されなければなりません。ス タック ポインタは\$40以上を指示するように設定されなければなりません。スタック ポインタはデータがPUSH命令でスタックに押し込まれる時に1 つ減らされ、サブルーチンや割り込みで戻りアドレスがスタックに押し込まれる時に2つ減らされます。スタック ポインタはPOP命令でデータがスタック から引き出される時に1つ増やされ、サブルーチンからの戻り(RET)または割り込みからの戻り(RETI)でデータがスタックから引き出される時に 2つ増やされます。

AVRのスタック ポインタはI/O空間内の2つの8ビット レジスタとして実装されます。実際に使われるビット数は(そのデバイス)実装に依存します。SPLだけが必要とされる程に小さいAVR構造の実装(デバイス)のデータ空間もあることに注意してください。その場合、SPHレジスタは存在しません。

# 5.6. 命令実行タイミング

本項は命令実行の一般的なアクセスタイミングの概念を記述します。AVR CPUはチップ(デバイス)用に選択したクロック元から直接的に生成したCPUクロック(clkCPU)によって駆動されます。内部クロック分周は使われません。

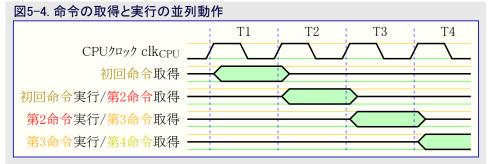

図5-4.はハーハート、構造と高速アクセスレジスタ ファイルの概念によって可能とされる並列の 命令取得と命令実行を示します。これは機 能対費用、機能対クロック、機能対電源部に 関する好結果と対応するMHzあたり1MIPS を達成するための基本的なパイプラインの概 念です。

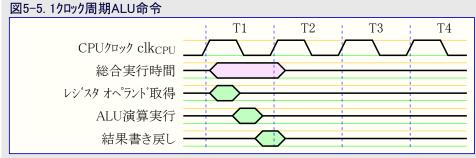

図5-5.はレジスタファイルに対する内部タイシングの概念を示します。単一クロック周期で2つのレジ、スタオヘ。ラント、を使うALU操作が実行され、その結果が転送先レジスタへ書き戻されます。

# 5.7. リセットと割り込みの扱い

AVRは多くの異なる割り込み元を提供します。これらの割り込みと独立したリセット ヘブタ各々はプログラムメモリ空間内に独立したプログラム ヘブタを持ちます。全ての割り込みは割り込みを許可するために、ステータスレジスタ(SREG)の全割り込み許可(I)ビットと共に論理1が書か れなければならない個別の許可ビットを割り当てられます。

既定でのプログラム メモリ空間の最下位アドレスはリセットと割り込みのベクタとして定義されます。ベクタの完全な一覧は29頁の「割り込み」で 示されます。この一覧は各種割り込みの優先順位も決めます。下位側アドレスがより高い優先順位です。リセットが最高優先順位で、次 が外部割り込み要求0(INT0)です。

割り込みが起こると全割り込み許可(I)ビットが解除(0)され、全ての割り込みは禁止されます。使用者ソフトウェアは多重割り込みを許可するため、全割り込み許可(I)ビットへ論理1を書けます。その後全ての許可した割り込みが現在の割り込みルーチンで割り込めます。全割り込み許可(I)ビットは割り込みからの復帰(RETI)命令が実行されると、自動的に設定(1)されます。

根本的に2つの割り込み形式があります。1つ目の形式は割り込み要求750を設定(1)する事象によって起動されます。これらの割り込みでは割り込み処理ルーチンを実行するために、プログラムカウンタは対応する現実の割り込み、クタを指示し、ハートウェアが対応する割り込み要求750を解除(0)します。割り込み要求750では解除(0)されるべき750のビット位置へ論理1を書くことによっても解除(0)できます。 対応する割り込み許可ビットが解除(0)されている間に割り込み条件が起こると、割り込み要求750が設定(1)されて割り込みが許可されるか、またはこの750がソフトウェアによって解除(0)されるまで記憶(保持)されます。同様に、全割り込み許可(I)ビットが解除(0)されている間に1つまたはより多くの割り込み条件が起こると、対応する割り込み要求750が設定(1)されて全割り込み許可(I)ビットが設定(1)されるまで記憶され、その(I=1)後で優先順に従って実行されます。

2つ目の割り込み形式は割り込み条件が存在する限り起動し(続け)ます。これらの割り込みは必ずしも割り込み要求フラクを持っている とは限りません。割り込みが許可される前に割り込み条件が消滅すると、この割り込みは起動されません。

AVRが割り込みから抜け出すと常に主プログラムへ戻り、何れかの保留割り込みが扱われる前に1つ以上の命令を実行します。

ステータスレジスタ(SREG)は割り込みルーチンへ移行時の保存も、復帰時の再設定も自動的に行われないことに注意してください。これはソフトウェアによって扱われなければなりません。

割り込みを禁止するCLI命令を使うと、割り込みは直ちに禁止されます。CLI命令と同時に割り込みが起こっても、CLI命令後に割り込みは実行されません。

割り込みを許可するSEI命令を使うと、以下の例で示されるようにどの保留割り込みにも先立ち、SEI命令の次の命令が実行されます。

| アセンブリ言語プログラム例 |                       |

|---------------|-----------------------|

| SEI           | ;全割り込み許可              |

| SLEEP         | ;休止形態動作移行(移行後に割り込み待ち) |

注:8頁の「コート」例」をご覧ください。

# 5.7.1. 割り込み応答時間

許可した全てのAVR割り込みに対する割り込み実行応答は最小4クロック周期です。4クロック周期後、実際の割り込み処理ルーチンに対す るプログラム ヘブタアトレスが実行されます。この4クロック周期間にプログラム カウンタ(PC)がスタック上に保存(プッシュ)されます。このヘブクタは標準 的に割り込み処理ルーチンへの無条件分岐で、この分岐は2クロック周期(訳注:原文は3(JMP命令=3を想定、実際はRJMP命令=2))要しま す。複数周期命令実行中に割り込みが起こると、その割り込みが扱われる前に、この命令が完了されます。MCUが休止形態動作の 時に割り込みが起こると、割り込み実行応答時間は4クロック周期、増やされます。この増加は選択した休止形態動作からの起動時間 に加えてです。

割り込み処理ルーチンからの復帰は4クロック周期要します。これらの4クロック周期中、プログラムカウンタ(PC:2ハイト)がスタックから取り戻され(ポップ)、スタックポインタは増加され(+2)、ステータスレジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されます。

# 5.8. コア関係レジスタ

5.8.1. CCP - 構成設定変更保護レジスタ(Configuration Change Protection Register)

| ビット        | 7 | 6 | 5 | 4   | 3    | 2 | 1 | 0   | _   |

|------------|---|---|---|-----|------|---|---|-----|-----|

| \$3C       |   |   |   | CCI | P7∼0 |   |   |     | CCP |

| Read/Write | W | W | W | W   | W    | W | W | R/W |     |

| 初期値        | 0 | 0 | 0 | 0   | 0    | 0 | 0 | 0   |     |

● ビット7~0 - CCP7~0 : 構成設定変更保護 (Configuration Change Protenction)

保護されたI/Oレジスタの内容を変更するため、CCPレジスタは最初に正しい識票を書かれなければなりません。CCPが書かれた後、保護されたI/Oレジスタは次からの4CPU命令周期中に書けます。これらの周期中は全ての割り込みが無視されます。これらの周期後に割り込みはCPUによって自動的に再び取り扱われて、どの保留割り込みもそれらの優先権に従って実行されます。

保護されたI/Oレジスタの識票が書かれると、CCP0は保護機能が許可されている限り1として読めます。CCP7~2は常に0として読めます。

表5-1.は認証に於ける識票を示します。

| 表5-1.構成設定変更保護レジスタによって認証される識票 |                               |              |  |  |  |  |

|------------------------------|-------------------------------|--------------|--|--|--|--|

| 識票 適用群 説明 説明                 |                               |              |  |  |  |  |

| \$D8                         | IOREG: CLKMSR, CLKPSR, WDTCSR | 保護されたI/Oレジスタ |  |  |  |  |

5.8.2. SPH,SPL (SP) - スタック ホペインタ (Stack Pointer)

| ビット        | 15     | 14     | 13     | 12     | 11     | 10     | 9      | 8      |     |

|------------|--------|--------|--------|--------|--------|--------|--------|--------|-----|

| \$3E       | SP15   | SP14   | SP13   | SP12   | SP11   | SP10   | SP9    | SP8    | SPH |

| Read/Write | R      | R      | R      | R      | R      | R      | R      | R      |     |

| 初期値        | RAMEND |     |

| ヒット        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      | _   |

| \$3D       | SP7    | SP6    | SP5    | SP4    | SP3    | SP2    | SP1    | SP0    | SPL |

| Read/Write | R      | R      | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |     |

| 初期値        | RAMEND |     |

### 5.8.3. SREG - ステータス レジズタ (Status Register)

| ビット        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _    |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$3F       | Ι   | Т   | Н   | S   | V   | N   | Z   | С   | SREG |

| Read/Write | R/W |      |

| 初期値        | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

#### ● ビット7 - I: 全割り込み許可 (Global Interrupt Enable)

割り込みが許可されるには全割り込み許可ビットが設定(1)されなければなりません。その時の個別割り込み許可制御は独立した制御 レジスタで行われます。全割り込み許可ビットが解除(0)されると、個別割り込み許可設定に拘らず、どの割り込みも許可されません。Iビッ トは割り込みが起こった後にハートウェアによって解除(0)され、後続の割り込みを許可するため、RETI命令によって設定(1)されます。I ビットは「AVR命令一式」資料と107頁の「命令要約」章で記述されるようにSEIやCLI命令で応用(プログラム)によって設定(1)や解除(0)も できます。

#### ● ビット6 - T : ビット変数 (Bit Copy Storage)

ビット複写命令、BLD(Bit LoaD)とBST(Bit STore)は操作したビットの転送元または転送先として、このTビットを使います。レジスタファイルのレジスタからのビットはBST命令によってTに複写でき、TのビットはBLD命令によってレジスタファイルのレジスタ内のビットに複写できます。

#### • ビット5 - H : ハーフキャリー フラク (Half Carry Flag)

ハーフキャリー(H)フラグはいくつかの算術操作でのハーフキャリーを示します。ハーフキャリーはBCD演算に有用です。詳細情報については「AVR 命令ー式」資料と107頁の「命令要約」章をご覧ください。

● ビット4 - S: 符号 (Sign Bit, S= N Ex-OR V)

S7ラグは常に負(N)フラグと2の補数溢れ(V)フラグの排他的論理和です。詳細情報については、「AVR命令ー式」資料と107頁の「命令 要約」章をご覧ください。

#### ビット3 - V: 2の補数溢れフラグ (2's Complement Overflow Flag)

2の補数溢れ(V)フラグは2の補数算術演算を支援します。詳細情報については「AVR命令ー式」資料と107頁の「命令要約」章をご覧ください。

#### ビット2 - N: 負フラク (Negative Flag)

負(N)フラグは算術及び論理操作での負の結果(MSB=1)を示します。詳細情報については「AVR命令ー式」資料と107頁の「命令要約」章をご覧ください。

#### • ビット1 - Z : セロ フラク (Zero Flag)

ゼロ(Z)フラグは算術及び論理操作でのゼロ(0)の結果を示します。詳細情報については「AVR命令ー式」資料と107頁の「命令要約」章

をご覧ください。

#### • Ľット0 – C : キャリー フラク (Carry Flag)

キャリー(C)フラグは算術及び論理操作でのキャリー(またはボロー)を示します。詳細情報については「AVR命令ー式」資料と107頁の「命令 要約」章をご覧ください。

# <mark>6</mark>. メモリ

本章項はATtiny4/5/9/10の各種メモリを記述します。デバイスはプログラム メモリ空間とデータ メモリ空間の2つの主なメモリ空間を持ちます。

# 6.1. 実装書き換え可能なプログラム用フラッシュ メモリ

ATtiny4/5/9/10はプログラム保存用に実装書き換え可能な512/1024ベイトのフラッシュ メモリをチップ上に含みます。全てのAVR命令が16または32ビット幅のため、このフラッシュ メモリは256/512×16ビットとして構成されます。

フラッシュ メモリは最低10,000回の消去/書き込み周回の耐久性があります。ATtiny4/5/9/10のプログラム カウンタ(PC)は8/9ビット幅、従って \$0000から始まる256/512プログラム メモリ位置をアドレス指定する能力があります。78頁の「メモリ プログラミング」はフラッシュ メモリの(TPI)直列プ ログラミングの詳細な記述を含みます。

定数表は全てのプログラムメモリアドレス空間に配置することができます。プログラムメモリが直接アクセスできないため、これはデータメモリに割り当てられています。割り当てられたプログラムメモリはデータメモリのバイトアドレス\$4000から始まります(図6-1.をご覧ください)。

プログラム用フラッシュ メモリへの内部的な書き込みは禁止され、従ってプログラム メモリはファームウェアに対して読み込み専用として見えます。フ ラッシュ メモリは未だ外部的に書けますが、プログラム用メモリ空間に対する内部的な書き込み操作は成功しません。

命令の取得と実行のタイミング図は10頁の「命令実行タイミング」で示されます。

# 6.2. デ<sup>・</sup>ータ メモリ

データメモリはI/Oメモリ、内部SRAM、不揮発性メモリ(NVM)施錠ビット、フラッシュメモリ を含みます。ATtiny4/5/9/10のメモリ空間がどう構成されるかの図解にいては 図6-1.をご覧ください。

最初の64位置はI/Oメモリ用に予約され、同時に後続する32データメモリ位置は データ用内部SRAMをアドレス指定します。

不揮発性メモリ施錠ビットと全てのフラッシュ メモリ領域がデータ メモリ空間に割り当てられています。これらの位置はデバイスのファームウェアに関して読み込み専用として見えます。

データメモリ用の4つの異なるアドレス指定形態は、直接、間接、事前減少付き間接、事後増加付き間接です。レジスタファイル内のレジスタR26~R31は間接アドレス指定ホインタ用レジスタとして機能します。

INとOUTの命令はI/Oメモリの64位置全てをアクセスできます。LDSとSTSの命令を 用いる直接アトレス指定は\$0040~\$00BF間の128位置に届きます。

間接アドレス指定はデータ空間全体に届きます。自動の事前減少付きと事後増加 付きのレジスタ間接アドレス指定動作を使う時に(使われた)X,Y,Zアドレスレジスタが 減少(-1)または増加(+1)されます。

### 図6-1. データ メモリ配置図(バイト アドレス)

| I/O空間           | \$0000 <b>~</b> \$003F |

|-----------------|------------------------|

| SRAMデータ メモリ     | \$0040~\$005F          |

| (予約)            | \$0060~\$3EFF          |

| NVM施錠ビット        | \$3F00~\$3F01          |

| (予約)            | \$3F02~\$3F3F          |

| 構成設定ビット         | \$3F40~\$3F41          |

| (予約)            | \$3F42~\$3F7F          |

| 校正ビット           | \$3F80~\$3F81          |

| (予約)            | \$3F82~\$3FBF          |

| デ゙バイス識別ビット      | \$3FC0~\$3FC3          |

| (予約)            | $3FC4 \sim 3FFF$       |

| プログラム用フラッシュ メモリ | \$4000~\$41FF/\$43FF   |

| (予約)            | $4400 \sim FFFF$       |

# 6.2.1. デ<sup>\*</sup>ータ メモリ アクセス タイミンク<sup>\*</sup>

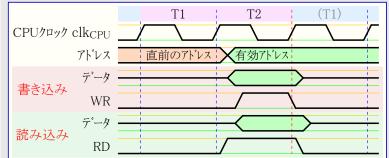

本項は内部メモリアクセスに対する一般的なアクセスタイミングの 概念を記述します。データ用内蔵SRAMアクセスは図6-2.で記 載されるように2clk<sub>CPU</sub>周期で実行されます。

(訳注)内蔵SRAMのアクセスを含む代表的な命令はT1,T2の 2周期で実行され、T1で対象アトレスを取得/(算出)/ 確定し、T2で実際のアクセスが行われます。後続する (T1)は次の命令のT1です。

# 図6-2. データ用内蔵SRAMアクセス周期

# 6.3. I/Oメモリ (レジネタ)

ATtiny4/5/9/10のI/O空間定義は106頁の「レジスタ要約」で示されます。

ATtiny4/5/9/10の全てのI/Oと周辺機能はI/O空間に置かれます。全てのI/O位置はLDとSTの命令を使ってアクセスすることができ、 I/O空間と16個の汎用作業レジスタ間のデータ転送を許します。アドレス範囲\$00~\$1F内のI/OレジスタはSBI命令とCBI命令を使って直接 的にビットアクセスが可能です。これらのレジスタではSBISとSBICの命令を使うことによって単一ビット値を検査することができます。より多く の詳細については「AVR命令一式」資料と107頁の「命令要約」章をご覧ください。I/O指定命令INとOUTを使う時はI/Oアドレス\$00~ \$3Fが使われなければなりません。

将来のデバイスとの共通性を保つため、アクセスされる場合、予約ビットは0が書かれるべきです。予約済みI/Oメモリアトレスは決して書かれるべきではありません。

状態フラグのいくつかはそれらへ論理1を書くことによって解除(0)されます。CBIとSBI命令は指定ビットだけを操作し、従って状態フラグのようなものを含むレジスタに使えることに注意してください。CBIとSBI命令はI/Oアドレス範囲\$00~\$1Fのレジスタでのみ動作します。 I/Oと周辺制御レジスタは以降の項で説明されます。

# 7. ウロック体系

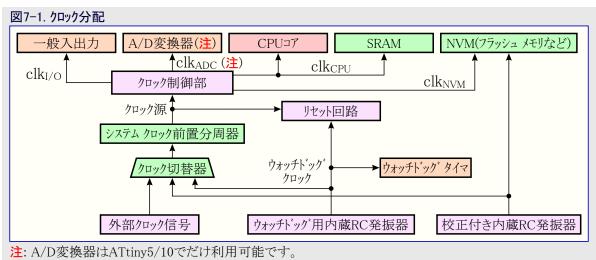

図7-1.はATtiny4/5/9/10に於ける主要なクロック系統とその配給を表します。全てのクロックが与えられた時間有効である必要はありません。消費電力低減のため、21頁の「電力管理と休止形態動作」章で記述される各種休止形態動作と電力削減レジスタビットを使うことにより、使われていない部分のクロックを停止できます。クロック体系は下で詳述されます。

# 7.1. クロック副系統

クロック副系統は下の項で詳述されます。

### 7.1.1. CPU クロック – clk<sub>CPU</sub>

CPUクロックはAVRコアの動作と関係する系統部分に配給されます。このような部分の例はシステムレジスタとデータ用SRAMメモリです。CPUクロックの停止はコアが一般的な操作や計算を実行することを禁止します。

### 7.1.2. I/O クロック – clk<sub>I/O</sub>

I/Oクロックはタイマ/カウンタのようなI/O部の大部分で使われます。I/Oクロックは外部割り込み部でも使われますが、いくつかの外部割り込みは例えI/Oクロックが停止されても検出されることをこのような割り込みに許す非同期論理回路によって検出されることに注意してください。

#### 7.1.3. NVMクロック – clk<sub>NVM</sub>

NVMクロックは不揮発性メモリ(NVM)制御部の動作を制御します。NVMクロックは通常CPUクロックと同時に活動します。

#### 7.1.4. A/D変換クロック - clk<sub>ADC</sub>

A/D変換器には専用のクロック範囲が提供されます。これはデジタル回路によって生成される雑音を低減するためにCPUとI/Oクロックの 停止を許します。これはより正確なA/D変換結果を与えます。

A/D変換器(ADC)はATtiny5/10でだけ利用可能です。

# 7.2. クロック元

全ての同期クロック信号は主クロックから配給されます。デバイスは次のような3つの主クロック用切り替え供給元を持ちます。

- ・校正付き8MHz内蔵発振器(16頁をご覧ください。)

- ・外部クロック信号(17頁をご覧ください。)

- ・128kHz内部発振器(17頁をご覧ください。)

活動するクロック元を選択して変更する方法については19頁の表7-3.をご覧ください。

# 7.2.1. 校正付き8MHz内蔵発振器

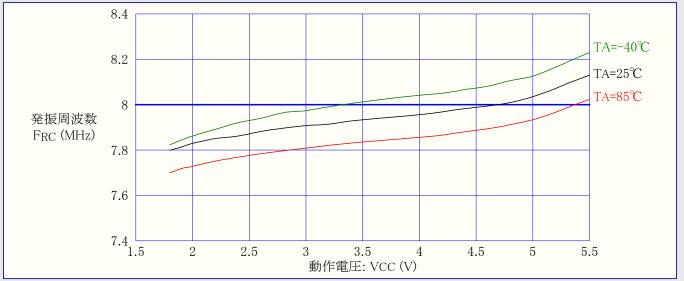

校正された内蔵RC発振器は概ね8MHzのクロック信号を提供します。電圧と温度に依存しますが、このクロックは使用者によって高精度な校正ができます。より多くの詳細については85頁の表17-2.、101頁の図18-39.と図18-40.をご覧ください。

このクロックはクロック主設定レジスタ(CLKMSR)のクロック主選択(CLKMS)ビットを00に設定することによって主クロックとして選択できます。一旦 許可されると、発振器は外部部品なしで動作します。リセット中、ハートウェアが発振校正(OSCCAL)レジスタに校正値バイトを設定し、これに よって発振器を自動的に校正します。この校正の精度は85頁の表17-2.で工場校正として示されます。

この発振器が主クロックとして使われる時に未だウォッチトッグ発振器がウォッチトッグタイマとリセット時間経過に使われます。予め設定された校 正値のより多くの情報については80頁の「校正領域」をご覧ください。

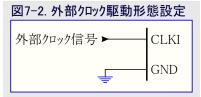

#### 7.2.2. 外部クロック信号

外部クロック元でデバイスを使うには、CLKIが図7-2.で示されるように駆動されるべきです。外部ク ロックはクロック主設定レジスタ(CLKMSR)のクロック主選択(CLKMS)ビットを10に設定することによって主 クロックとして選ばれます。

外部クロックを印加する時にMCUの安定な動作を保証するため、印加したクロック周波数の急な変化を避けることが必要とされます。或るクロック周期から次への2%より大きな周波数変化は予測されない事態を引き起こします。クロック周波数での変更のような間、MCUはリセットに保たれるのを保証することが必要とされます。

#### 7.2.3. 128kHz内部発振器

128kHz内部発振器は128kHzのクロックを提供する低電力発振器です。周波数は供給電圧、温度、一群の変量に依存します。このクロックはクロック主設定レジスタ(CLKMSR)のクロック主選択(CLKMS)と、ットを01に設定することによって主クロックとして選択することができます。

#### 7.2.4. クロック元切り替え

主クロック元は19頁の「CLKMSR - クロック主設定レジスタ」を使って走行時に切り替えることができます。どのクロック元を切り替える時にもクロックシステムは主クロックに異常が起きないことを保証します。

# 7.2.5. 既定のクロック元

デバイスが電源投入またはリセットされる時に、主クロックとして常に校正付き8MHz内蔵発振器が選択されます。同期システムクロックはシステム クロック前置分周器によって8分周に制御された主クロックです。クロック前置分周レジスタ(CLKPSR)の前置分周選択(CLKPS)ビットは後でシス テムクロック周波数を変更するために書くことができます。次の「システムクロック前置分周器」項をご覧ください。

#### 7.3. システム クロック前置分周器

システム クロックはシステム クロック前置分周器経由で主クロックから配給されます。システム クロックは20頁の「CLKPSR - クロック前置分周レジスタ」を 設定することによって分周できます。システム クロック前置分周器は処理能力に対する必要条件が低い時の消費電力低減、またはシステム クロックを最大周波数の制限内に持って来るのに使うことができます。前置分周器は全ての主クロック元任意選択で使うことができ、CPU と全ての同期周辺機能のクロック周波数に影響を及ぼします。

システム クロック前置分周器は未だ安定動作を保証すると同時に内部クロック周波数の走行時変更の実行に使うことができます。

#### 7.3.1. 切り替え時間

前置分周器設定を切り替える時に、システム クロック前置分周器は中間(経過途中)の周波数が直前の設定に対応するクロック周波数または新規設定に対応するクロック周波数のどちらよりも高くなく、システム クロックで異常が起きないことを保証します。

前置分周器として実行するリプル カウンタは主クロックの周波数で動き、それはCPUのクロック周波数よりも速いかもしれません。従って例え (カウンタ値が)読めるとしても、前置分周器の状態を決めることはできず、1から他へのクロック分周値切り替えを行う正確な時間は必ずし も予測できません。

CLKPS値が書かれる時から新規クロック周波数が活性(有効)になる前にT1+T2~T1+2×T2間かかります。この間で2つの有効なクロック端が生成されます。ここでのT1は直前のクロック周期、T2は新規前置分周器設定に対応する周期です。

#### 7.4. 始動

# 7.4.1. リセットからの始動

リセット元が活性(有効)になる時に内部リセットは直ちに有効設定にされます。内部リセットはリセット下が開放されて始動手順が完了されるまで有効設定にされ続けます。始動手順は次のような3つの段階を含みます。

1. リセット元が開放された後の最初の段階はリセット始動時間を計数するデバイスから成ります。このリセット始動時間の目的は供給電圧が 充分な水準に達するのを保証することです。リセット始動時間は128KHz内部発振器を使って計数されます。リセット始動時間の詳細 については表7-1.をご覧ください。

実際の供給電圧は始動回路によって監視されません。例えデバイスが早くに充分な供給電圧水準へ達したとしても、デバイスはリセット始動時間まで計数することに注意してください。

- 2. 2つ目の段階は発振器始動時間を計数することで、これは校正付き内蔵発振器がシステムの他の部分によって使われる前にそれ が安定状態に達することを保証します。校正付き内蔵発振器はそれが安定と見做され得る前に最低周期数の発振が必要です。 発振器始動時間の詳細については表7-1.をご覧ください。

- 3. 内部リセットを開放する前の最後段階はデバイスを正しく構成設定するために不揮発性メモリから校正値と構成設定値を設定することです。構成設定時間は表7-1.で一覧にされます。

| 表7-1. 校止付き | 表7-1.校止付き内蔵発振器使用時の始動時間                                             |                |                             |  |  |  |  |  |  |  |  |  |

|------------|--------------------------------------------------------------------|----------------|-----------------------------|--|--|--|--|--|--|--|--|--|

| リセット       | リセット 発振器 構成設定 総始動時間                                                |                |                             |  |  |  |  |  |  |  |  |  |

| 64ms       | 64ms         6周期         21周期         64ms+6発振器周期+21システム クロック周期(注) |                |                             |  |  |  |  |  |  |  |  |  |

| 注・デバイスの雷ジ  | 原投入後またけリャット谷                                                       | そのシステムクロックけ自動的 | に8分周された校正付き8MHz内蔵発振器に設定されます |  |  |  |  |  |  |  |  |  |

注:デバイスの電源投入後またはリセット後のシステム クロックは自動的に8分周された校正付き8MHz内蔵発振器に設定されます。

# 7.4.2. パワーダウン動作からの始動

パワーダウン休止動作からの起動時、供給電圧は充分な水準であると仮定 され、発振器の安定動作を保証するために発振器始動時間だけが計数 されます。発振器始動時間は選択されている主クロックで計数され、始動 時間はその選択されたクロックに依存します。詳細については表7-2.をご 覧ください。

| 表7-2. パワーダウン休止動作からの始動時間 |                    |  |  |  |  |  |  |  |  |

|-------------------------|--------------------|--|--|--|--|--|--|--|--|

| 発振器始動時間 総始動時間           |                    |  |  |  |  |  |  |  |  |

| 6周期                     | 6発振器周期( <b>注</b> ) |  |  |  |  |  |  |  |  |

|                         |                    |  |  |  |  |  |  |  |  |

注: 始動時間は主クロック発振器周期で測定されます。

# 7.4.3. アイドル,A/D変換雑音低減,スタンバイ動作からの始動

アイドル、A/D変換雑音低減、スタンハイ動作からの起動時、発振器は既に動いており、発振器始動時間は全く持ち込まれません。 A/D変換器(ADC)はATtiny5/10でだけ利用可能です。

# 7.5. クロック関係レシ、スタ

7.5.1. CLKMSR - クロック主設定レジスタ (Clock Main Settings Register)

| ヒット        | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0      |        |

|------------|---|---|---|---|---|---|--------|--------|--------|

| \$37       | - | - | - | - | - | - | CLKMS1 | CLKMS0 | CLKMSR |

| Read/Write | R | R | R | R | R | R | R/W    | R/W    |        |

| 初期値        | 0 | 0 | 0 | 0 | 0 | 0 | 0      | 0      |        |

ビット7~2 - Res:予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

• ビット1,0 - CLKMS1,0: クロック主選択 (Clock Main Select Bits)

これらのビットはシステムの主クロック元を選びます。このビットは主クロックの供給元を切り替えるために走行時に書くことができます。クロックシ ステムは不具合なしでの主クロック元切り替えを保証します。

主クロック切り替えは表7-3.で示されます。

主クロック元の予期せぬ切り替えを避けるため、CLKMSビットを変更するには次のような保護された変更手順に従わなければなりません。

- 1. 保護されたI/Oレジスタの変更許可用の識票を構成設定変更保護 (CCP)レジスタに書いてください。

- 2.4命令周期内に望む値でCLKMSビットを書いてください。

| 7.5.2. OSCCAL - 発振校正レジスタ (Oscillator Calibration Register) | 7.5.2. OSCCAL - | · 発振校正レジスタ (Oscillator | · Calibration Register) |

|------------------------------------------------------------|-----------------|------------------------|-------------------------|

|------------------------------------------------------------|-----------------|------------------------|-------------------------|

| ビット        | 7    | 6    | 5    | 4      | 3     | 2    | 1    | 0    | _      |

|------------|------|------|------|--------|-------|------|------|------|--------|

| \$39       | CAL7 | CAL6 | CAL5 | CAL4   | CAL3  | CAL2 | CAL1 | CAL0 | OSCCAL |

| Read/Write | R/W  | R/W  | R/W  | R/W    | R/W   | R/W  | R/W  | R/W  |        |

| 初期値        |      |      |      | デバイス固て | 有の校正値 |      |      |      |        |

# ● ビット7~0 - CAL7~0:発振校正値 (Oscillator Calibration Value)

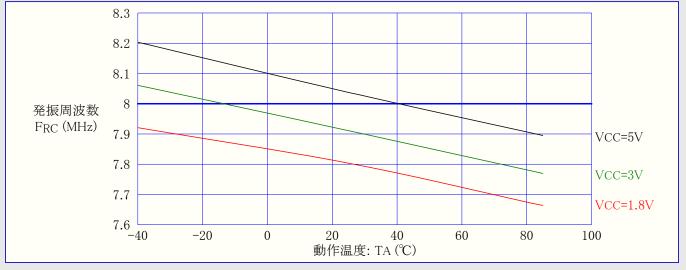

発振校正レジスタは内蔵発振器の調整に使われ、発振器周波数の偏差処理を省きます。チップのリセット中に予めプログラムされた値が自動的にこのレジスタへ書かれ、85頁の「**表17-2. 校正付き内蔵RC発振器の校正精度**」で指定されるように工場校正された周波数を与 えます。

応用ソフトウェアは周波数を変更するために、このレジスタに書くことができます。この発振器は85頁の「表17-2. 校正付き内蔵RC発振器 の校正精度」の表で指定されるように周波数を校正することができます。この範囲外への校正は保証されません。

CAL7~0ビットは発振器の周波数を調整するのに使われます。\$00の設定は最低周波数を生じ、\$FFの設定は最高周波数を与えます。

| 表7-3. 主ク | 長7-3. 主クロックの選択 |                     |  |  |  |  |  |  |  |  |  |  |

|----------|----------------|---------------------|--|--|--|--|--|--|--|--|--|--|

| CLKMS1   | CLKMS0         | 主クロック元              |  |  |  |  |  |  |  |  |  |  |

| 0        | 0              | 校正付き8MHz内蔵発振器       |  |  |  |  |  |  |  |  |  |  |

| 0        | 1              | 128kHz内部発振器(WDT発振器) |  |  |  |  |  |  |  |  |  |  |

| 1        | 0              | 外部クロック信号            |  |  |  |  |  |  |  |  |  |  |

| 1        | 1              | (予約)                |  |  |  |  |  |  |  |  |  |  |

7.5.3. CLKPSR - クロック前置分周レジスタ (Clock Prescale Register)

| ヒット        | 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      |        |

|------------|---|---|---|---|--------|--------|--------|--------|--------|

| \$36       | - | - | - | - | CLKPS3 | CLKPS2 | CLKPS1 | CLKPS0 | CLKPSR |

| Read/Write | R | R | R | R | R/W    | R/W    | R/W    | R/W    |        |

| 初期値        | 0 | 0 | 0 | 0 | 0      | 0      | 1      | 1      |        |

ビット7~4 - Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

● ビット3~0 - CLKPS3~0 : クロック分周値選択 (Clock Prescaler Select Bits 3~0)

これらのビットは選択したクロック元と内部システムクロック間の分周係数を定義します。これらのビットはクロック周波数を変えて応用の必要条件に合わせるため、走行時に書くことができます。前置分周器はMCUへの主クロック入力を分周するため、これによって全ての同期周辺機能の速度が減じられます。分周係数は表7-4.で与えられます。

| 表 | 表7-4. クロック前置分周器選択(注:既定値) |     |                                      |   |   |   |   |   |   |     |      |   |   |   |   |   |   |

|---|--------------------------|-----|--------------------------------------|---|---|---|---|---|---|-----|------|---|---|---|---|---|---|

|   | CLKPS3                   |     | 0                                    |   |   |   |   |   |   |     | 1    |   |   |   |   |   |   |

|   | CLKPS2                   |     | (                                    | ) |   |   |   | 1 |   | 0 1 |      |   |   |   |   |   |   |

|   | CLKPS1                   | 0 1 |                                      |   | ( | C |   | 1 | ( | )   |      | 1 | ( | ) | 1 |   |   |

|   | CLKPS0                   | 0   | 0 1 0 1                              |   |   |   | 1 | 0 | 1 | 0   | 1    | 0 | 1 | 0 | 1 | 0 | 1 |

|   | 分周係数(数)                  | 1   | 1 2 4 8( <del>注</del> ) 16 32 64 128 |   |   |   |   |   |   |     | (予約) |   |   |   |   |   |   |

予期せぬクロック周波数の変更を防ぐため、CLKPSビットの変更するには保護された変更手順に従わなければなりません。

1. 保護されたI/Oレジスタの変更許可用の識票を構成設定変更保護(CCP)レジスタに書いてください。

2. (次からの)4命令周期内に望む値でCLKPSビットを書いてください。

始動でクロック分周係数8を選択するためにCLKPSビットは0011にリセットされます。応用ソフトウェアは選択したクロック元が現在の動作条件に 於いてデバイスの最大周波数よりも高い周波数を持つ場合に、充分な分周係数が使われるのを保証しなければなりません。書き込み 手続きが割り込まれないことを保証するため、前置分周器設定変更時に割り込みは禁止されなければなりません(訳注:本行の記述 はCCP書き込みによって自動的に割り込みが禁止されるため不適切です。消し忘れと思われます)。

# 8. 電力管理と休止形態動作

高機能と産業的に先行するコード効率は低電力の応用に対してAVRマイクロコントローラを理想的に選択させます。加えて休止形態動作 は応用でMCU内の未使用部を一時停止することを可能にし、それによって節電します。AVRは応用で必要な消費電力に仕立てるこ とを使用者に許す様々な休止形態動作を提供します。

# 8.1. 休止形態動作種別

16頁の図7-1.はATtiny4/5/9/10の各種クロック系統とその配給を示します。この図は適切な休止形態動作選択で役立ちます。表8-1. は各種休止形態動作とそれらの起動元を示します。

|   |           | 11001                 | 動作クロッ                 | ク範囲       | ]                 | 発振器動作        | 復帰起動元 (割り込み) |                               |        |           |                   |  |  |  |

|---|-----------|-----------------------|-----------------------|-----------|-------------------|--------------|--------------|-------------------------------|--------|-----------|-------------------|--|--|--|

|   | 休止形態種別    | clk<br><sub>CPU</sub> | clk<br><sub>NVM</sub> | clk<br>10 | clk<br>ADC<br>(注) | 主クロック<br>供給元 | INT0<br>ピン変化 | A/D変換完了<br>( <mark>注</mark> ) | その他I/O | ウォッチト゛ック゛ | VCCレベル監視<br>(VLM) |  |  |  |

| ľ | アイドル      |                       |                       | 0         | 0                 | 0            | 0            | 0                             | 0      | 0         | 0                 |  |  |  |

|   | A/D変換雑音低減 |                       |                       |           | 0                 | 0            | 1            | 0                             |        | 0         | 0                 |  |  |  |

|   | スタンバイ     |                       |                       |           |                   | 0            | 1            |                               |        | 0         |                   |  |  |  |

|   | パワータ゛ウン   |                       |                       |           |                   |              | 1            |                               |        | 0         |                   |  |  |  |

**注**: A/D変換器はATtiny5/10でだけ利用可能です。

① INTOについてはレベル割り込みのみです。

4つの休止形態動作のどれかへ移行するには休止形態制御レジスタ(SMCR)の休止許可(SE)ビットが論理1を書かれ、SLEEP命令が実行されなければなりません。SMCRの休止形態種別選択(SM2~0)ビットはSLEEP命令によってどの休止形態(アイト・ル、A/D変換雑音低減、スタンハイ、パワーダウン)が活性(有効)にされるのかを選びます。要約については表8-2.をご覧ください。

MCUが休止形態動作中に許可した割り込みが起こると、MCUは起動します。その時にMCUは起動時間に加えて4周期停止され、割り込みルーチンを実行し、そしてSLEEP命令の次の命令から実行を再開します。デバイスが休止状態から起動するとき、レジスタファイルとSRAMの内容は変えられません。休止形態動作中にリセットが起こると、MCUは起動し、リセット、クタから実行します。

レベルで起動した割り込みが起動復帰に使われる場合、MCUを起動(とMCUがその割り込み処理ルーチンへ移行)するには、変更したレベルが一定時間保持されなければならないことに注意してください。詳細については30頁の「外部割り込み」をご覧ください。

# 8.1.1. アイドル動作

休止形態種別選択(SM2~0)ビットが、000'を書かれると、SLEEP命令はMCUをアイドル動作へ移行させ、CPUを停止しますが、A/D変換器、アナログ比較器、タイマ/カウンタ、ウォッチトッグ、割り込み機構の継続動作を許します。この休止形態は基本的にclkCPUとclkNVMを停止する一方、他のクロックに走行を許します。

アイドル動作はMCUにタイマ溢れなどの内部割り込みだけでなく、外部で起動された割り込みからの起動も可能にします。アナログ比較器割り込みからの起動が必要とされないなら、62頁の「ACSR - アナログ比較器制御/状態レジスタ」のアナログ比較器禁止(ACD)ビットを設定(1)することにより、アナログ比較器を電源断にできます。これはアイドル動作での消費電力を削減します。A/D変換が許可されるなら(ATtiny5/10のみ)、この動作に移行すると変換が自動的に始まります。

# 8.1.2. A/D変換雑音低減動作

SM2~0ビットが'001'を書かれると、SLEEP命令はMCUをA/D変換雑音低減動作へ移行させ、CPUを停止しますが、A/D変換器、外部割り込み、ウォッチドッグの(許可されていれば)継続動作を許します。この休止形態はclkI/O, clkCPU, clkNVMを停止する一方で他の クロックに走行を許します。

この動作形態はA/D変換に対する雑音環境を改善し、より高い分解能の測定を可能にします。A/D変換器が許可されている場合、 この動作に移行すると、変換が自動的に始まります。A/D変換完了割り込みからの他、外部リセット、ウォッチト・ッグ・システムリセット、VCCレヘ・ ル監視(VLM)割り込み、INT0の外部レヘル割り込み、ピン変化割り込みだけが、A/D変換雑音低減動作からMCUを起動できます(訳注: 本行追加)。

例えATtiny5/10だけがA/D変換器(ADC)を装備されていても、この動作種別は全てのデバイスで利用可能です。

# 8.1.3. パワーダウン動作

SM2~0ビットが'010'を書かれると、SLEEP命令はMCUをパワーダウン動作へ移行させます。この動作では発振器が停止される一方、外部割り込み、ウォッチトックが機能は(許可されていれば)継続して動作します。ウォッチトックブリセット、INT0の外部レヘル割り込み、ピン変化割り込みだけがMCUを起動できます。この休止形態は生成した全てのクロックを停止し、非同期部の動作だけを許します。

# 8.1.4. スタンバイ動作

SM2~0ビットが'100'を書かれると、SLEEP命令はMCUをスタンハイ動作へ移行させます。この動作は発振器が走行(動作)を保たれる例 外を除いてパワーダウン動作と同じです。発振器が既に走行していて始動が必要ないので、これは起動時間を減らします。

# 8.2. 電力削減レジスタ

電力削減レジスタ(PRR、23頁の「PRR - 電力削減レジスタ」をご覧ください。)は個別周辺機能へのクロックを停止することによって消費電力を削減するための方法を提供します。周辺機能へのクロックが停止されると、以下のようになります。

- ・周辺機能の現在の状態が固定化されます。

- ・関連するレジスタは読み書きすることができません。

・周辺機能によって使われる資源は専有されたままに留まります。

周辺機能は殆どの場合に於いてクロックを停止する前に禁止されるべきです。電力削減レジスタ(PRR)のビットを解除(0)することが周辺機能部を起し、停止前と同じ状態にします。

周辺機能の停止は全体に亘る重要な消費電力の削減のために活動動作とアイドル動作で使えます。例については88頁の「周辺機能 部供給電流」をご覧ください。その他の休止形態動作ではクロックが予め停止されます。

### 8.3. 消費電力の最小化

これらはAVRコアが制御するシステムで消費電力の最小化を試みる時に考慮するための様々な問題です。一般的に休止形態動作は可能な限り多く使用されるべきで、休止形態種別は動作するデバイスの機能が可能な限り少なくなるように選択されるべきです。必要とされない全ての機能は禁止されるべきです。特に次の機能部は最低可能消費電力の達成を試みるとき、特別な考慮を必要とするでしょう。

#### 8.3.1. アナログ比較器

アイドル動作またはA/D変換雑音削減動作へ移行するとき、アナログ比較器は使われないなら、禁止されるべきです。その他の休止形態動作でのアナログ比較器は自動的に禁止されます。更なる詳細については62頁の「**アナログ比較器」**をご覧ください。

### 8.3.2. A/D変換器 (ADC)

許可したなら、A/D変換器は全ての休止形態動作で許可されます。節電するため、休止形態動作の何れかへ移行する前にA/D変換器は禁止されるべきです。A/D変換器がOFFそして再びONに切り替えられると、次の(最初の)変換は延長された(初回)変換になります。A/D変換器操作の詳細については64頁の「A/D変換器」をご覧ください。

A/D変換器(ADC)はATtiny5/10でだけ利用可能です。

#### 8.3.3. ウォッチト ック タイマ

ウォッチトック「タイマが応用で必要とされないなら、この単位部はOFFされるべきです。ウォッチトック「タイマが許可されていると全休止形態動作で許可され、故に常時電力を消費します。これはより深い休止形態動作での総消費電流にとって重要な一因になります。ウォッチトック「タイマ設定法の詳細については26頁の「ウォッチトック」タイマ」を参照してください。

# 8.3.4. ホート ピン

休止形態動作へ移行するとき、全てのポートピンは最小電力使用に設定されるべきです。最も重要なことはその時にピンが抵抗性負 荷を駆動しないのを保証することです。I/Oクロック(clk<sub>I</sub>/O)が停止される休止形態動作ではデバイスの入力緩衝部が禁止されます。こ れは必要とされない時に入力論理回路によって電力が消費されないことを保証します。いくつかの場合で入力論理回路は起動条件 を検出するために必要とされ、その時は許可されます。どのピンが許可されるかの詳細については35頁の「デジタル入力許可と休止形 態動作」項を参照してください。入力緩衝部が許可され、入力信号が浮いている状態のままか、またはアナログ信号電圧がVCC/2付近 の場合、入力緩衝部は過大な電力を消費するでしょう。

アナログ入力ピンに対するデジタル入力緩衝部は常に禁止されるべきです。入力ピンでのVCC/2付近のアナログ信号入力は活動動作でも 重要な電流を引き起こし得ます。デジタル入力緩衝部はデジタル入力禁止レジスタの(DIDR0)の書き込みによって禁止できます。詳細に ついては70頁の「DIDR0 - デジタル入力禁止レジスタ0」をご覧ください。

# 8.4. 電力管理用レジスタ

### 8.4.1. SMCR - 休止形態制御レジスタ (Sleep Mode Control Register)

SMCR制御レジスタは電力管理用の制御ビットを含みます。

| ビット        | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   | _    |

|------------|---|---|---|---|-----|-----|-----|-----|------|

| \$3A       | - | - | - | - | SM2 | SM1 | SM0 | SE  | SMCR |

| Read/Write | R | R | R | R | R/W | R/W | R/W | R/W |      |

| 初期値        | 0 | 0 | 0 | 0 | 0   | 0   | 0   | 0   |      |

ビット7~4 - Res : 予約 (Reserved)

このビットは予約されており、常に0として読みます。

● ビット3~1 - SM2~0 : 休止形態種別選択 (Sleep Mode Select Bit 2, 1 and 0)

これらのビットは表8-2.で示される利用可能なの休止形態動作を選択します。

#### 表8-2.休止形態動作種別選択

| SM2 | SM1 | SM0 | 休止形態動作種別       |

|-----|-----|-----|----------------|

| 0   | 0   | 0   | アイドル動作         |

| 0   | 0   | 1   | A/D変換雑音低減動作(注) |

| 0   | 1   | 0   | パワーダウン動作       |

| 0   | 1   | 1   | (予約)           |

| 1   | 0   | 0   | スタンバイ動作        |

| 1   | 0   | 1   | (予約)           |

| 1   | 1   | 0   | (予約)           |

| 1   | 1   | 1   | (予約)           |

**注**: 例えATtiny5/10だけがA/D変換器(ADC)を装備されていても、この動作種別は全てのデバイスで利用可能です。

### ● ビット0 - SE : 休止許可 (Sleep Enable)

SLEEP命令が実行される時にMCUを休止形態動作へ移行させるには、休止許可(SE)ビットが論理1を書かれなければなりません。 MCUの目的外休止形態動作移行を避けるため、SLEEP命令実行直前に休止許可(SE)ビットを設定(1)し、起動後直ちに解除(0)するこ とが推奨されます。

#### 8.4.2. PRR - 電力削減レジスタ (Power Reduction Register)

| ビット        | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0      |     |

|------------|---|---|---|---|---|---|-------|--------|-----|

| \$35       | - | - | - | - | - | - | PRADC | PRTIM0 | PRR |

| Read/Write | R | R | R | R | R | R | R/W   | R/W    |     |

| 初期値        | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0      |     |

#### ビット7~2 - Res:予約 (Reserved)

このビットは予約されており、常に0として読みます。

### ● ビット1 - PRADC : A/D変換器電力削減 (Power Reduction ADC)

このビットへの1書き込みはA/D変換器(ADC)を停止します。A/D変換器は停止前に禁止されなければなりません。ADCが停止されて いる時にアナログ比較器はADC入力多重器(MUX)を使えません。

A/D変換器(ADC)はATtiny5/10でだけ利用可能です。

#### • ビット0 - PRTIM0 : タイマ/カウンタ0電力削減 (Power Reduction Timer/Counter0)

このビットへの1書き込みはタイマ/カウンタ0部を停止します。タイマ/カウンタ0が許可されると、停止前と同様に動作は継続します。

注: アナログ比較器は「ACSR - アナログ比較器制御/状態レジスタ」のアナログ比較器禁止(ACD)ビットを使うことで禁止されます。(訳注:共通 性から本注追加)

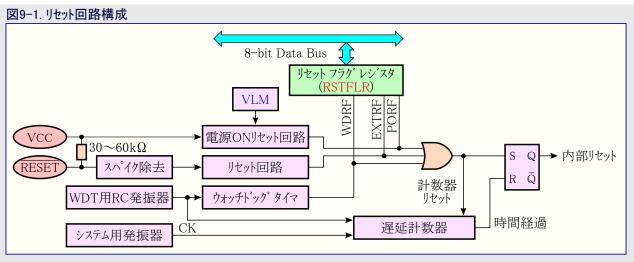

# 9. システム制御とリセット

# 9.1. AVRのリセット

リセット中、全てのI/Oレジスタはそれらの初期値に設定され、プログラムはリセット ベクタから実行を開始します。リセット ベクタに配置される命令 は、きっとリセット処理ルーチンへの無条件相対分岐(RJMP)命令でしょう。プログラムが決して割り込み元を許可しないなら、割り込みベクタは 使われず、これらの位置に通常のプログラムコートが配置できます。図9-1.の回路構成図はリセット論理回路を示します。リセット回路の電 気的特性は85頁の「システムとリセットの特性」項で定義されます。

AVRのI/Oポートはリセット元が有効になると直ちにそれらの初期状態にリセットされます。これはどのクロック元の走行も必要ありません。 全てのリセット元が無効にされてしまった後、遅延計数器(タイマ)が始動され、内部リセットを引き伸ばします。これは通常動作開始前に安定電圧へ達することを電源に許します。始動手順は17頁の「リセットからの始動」で記述されます。

# 9.2. リセット元

ATtiny4/5/9/10は次の4つのリセット元を持ちます。

- ・電源ONリセット・・・・・・・・・・・・・・・・供給電圧が電源ONリセット閾値電圧(VPOA)以下でMCUがリセットされます。

- ・VCCレヘル監視(VLM)リセット・・・VCCピンの電圧が選択した起動レベル以下の時にMCUがリセットされます。

- ・ウォッチト、ック、システムリセット・・・・・ウォッチト、ック、システムリセット動作が許可され、ウォッチト、ック、タイマが終了すると、MCUがリセットされます。

# 9.2.1. 電源ONリセット

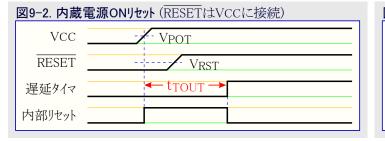

電源ONリセット(POR)ハ<sup>ル</sup>ルスはチップ上の検出回路によって生成されます。検出電圧は85頁の「システムとリセットの特性」項で定義されます。 POR信号はVCCが検出電圧以下の時は必ず活性(有効)にされます。POR回路は供給電圧異常検出は勿論、始動リセットの起動にも 使えます。

電源ONリセット回路はデバイスが電源投入でリセットされることを保証します。電源ONリセット閾値電圧(VPOR)への到達はVCCの上昇後に デバイスがどのくらいリセットを保つかを決める遅延計数器(タイマ)を起動します。VCCがこの検出電圧以下に低下すると、リセット信号はど んな遅延もなく再び有効にされます。

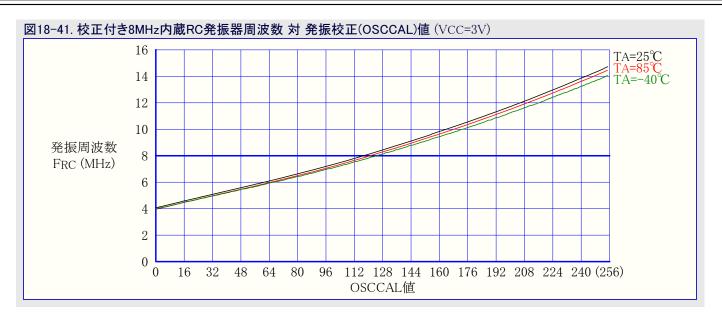

#### 9.2.2. VCCレヘル監視

ATtiny4/5/9/10は固定の起動レベルに対してVCCピンの電圧レベルを比較するVCCレベル監視(VLM)回路を持ちます。起動レベルは電圧レベル監視器起動レベル(VLM2~0)ビットで設定されます。28頁の「VLMCSR - VCCレベル監視制御/状態レジスタ」をご覧ください。

VLM回路はVCCビンの電圧が選択した起動レベル以下かどうかを示す状態フラグ(VLMF)を提供します。このフラグはVLMCSRから読む ことができますが、VLMF状態フラグが設定(1)された時に割り込みを生成することも可能です。この割り込みはVLMCSRレジスタのVLM 割り込み許可(VLMIE)ビットによって許可されます。状態フラグは起動レベルを変更すること、またはそれに0を書くことによって解除(0)す ることができます。このフラグはVCCビンの電圧が選択した起動レベル以上に上がって戻る時に自動で解除(0)されます。

VLMは供給低下でのリセット特性を改善するのにも使うことができます。VLMなしでの電源ONリセット(POR)はMCUが必ずしももう機能的でないレベルへ供給電圧が落ちる前に活動しません。VLMではより早いリセットを生成することが可能です。

活動(有効)時、VLM回路は104頁の図18-48.で図解されるように、或る程度の電力を消費します。節電のため、VLM回路は完全に OFF、または一定間隔でONとOFFを切り替えることができます。けれども、検出には或る程度の時間がかかり、従って安定な合図の ために充分な長さで回路を許可することが推奨されます。86頁の「VCCレヘ・ル監視器」をご覧ください。

VLMが活性(有効)でVCCピンの電圧が選択した起動レベル以上の時が標準として動作で、VLMは短時間の間、停止することができます。VCCピンの電圧が選択した閾値以下に落ちた場合、VLMは構成設定に依存して割り込みで合図するか、またはリセットを生成するかのどちらかです。

VLMが低供給電圧でのリセット生成に構成設定されると、VCCがそのリセットレベル以下である限り、デバイスはリセットを保ちます。リセットレベル詳細については28頁の表9-4.をご覧ください。供給電圧がリセットレベル以上に上昇した場合、その(リセット)条件が取り払われ、MCUはリセットを出て電源投入始動手順を始めます。

供給電圧がPORを起動するのに足るまで落ちた場合、供給電圧が回復された後で電源ONJセットフラグ(PORF)が設定(1)されます。

#### 9.2.3. 外部リセット

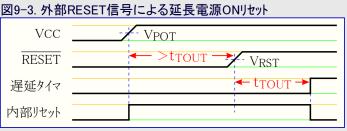

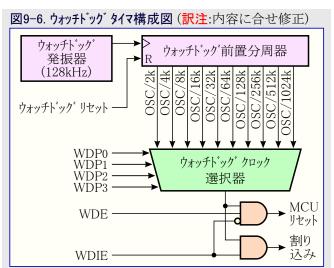

許可されていれば外部リセットはRESETビンのLowレベルによって生成されます。クロックが動いていなくても、最小パルス幅(85頁の「システムとリセットの特性」項をご覧ください。)以上のリセットパルスはリセットを生成します。短すぎるパルスはリセット生成が保証されません。印加された信号の上昇がリセット閾値電圧(VRST)に達すると(遅延タイマを起動し)、遅延タイマは遅延時間(tTOUT)経過後にMCUを始動します。外部リセットは電源ON始動計数の間、無視されます。電源ONリセット後、最初の電源ON遅延計数完了時にRESETビンがLowの場合にだけ内部リセットが延長されます。24頁の図9-2.と図9-3.をご覧

ください。外部リセットはRSTDISBLヒューズによって禁止することができます(訳注:共通性から本行追加)。

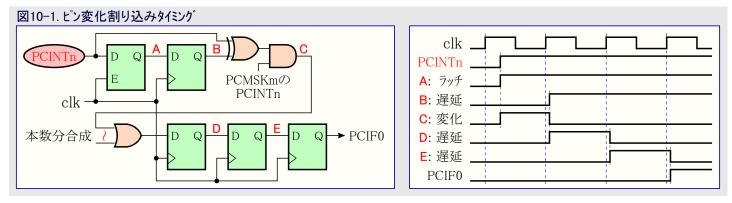

# 9.2.4. ウォッチト ック システム リセット

ウォッチトック「時間経過時、(内部的に)1CK周期幅の短いリセット パルス を生成します。遅延タイマはこのパルスの下降端で遅延時間(t<sub>TOUT</sub>) の計時を始めます。ウォッチトック「タイマの操作の詳細については26 頁の「ウォッチト、ック」 タイマ」を、リセット保持時間の詳細については85頁 の表17-4.をご覧ください。

#### 図9-5. 動作中のウォッチドッグ システム リセット

| VCC              |  |

|------------------|--|

| RESET            |  |

| ウォッチト・ック<br>時間経過 |  |

| 遅延タイマ            |  |

| 内部リセット           |  |

# 9.3. ウォッチト ゙ック゛ タイマ

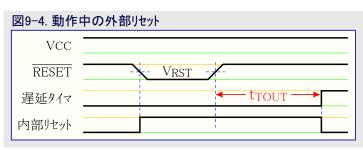

ウォッチトック タイマは128KHzで走行するチップ 上の発振器からクロック駆動 されます。図9-6.をご覧ください。ウォッチトック タイマ前置分周器を制御す ることにより、ウォッチトック リセット間隔は表9-3.で示されるように調整する ことができます。ウォッチトック リセット(WDR)命令はウォッチトック タイマをリセット します。ウォッチトック タイマはそれが禁止される時とデバイスリセットが起きる 時にもリセットされます。リセット期間を決めるために10種クロック周期期間を 選ぶことができます。他のウォッチトック リセットなしにリセット期間が経過した 場合、ATtiny4/5/9/10はリセットしてリセット ベクタから実行します。ウォッチ トック リセットのタイシング詳細については27頁の表9-3.をご覧ください。

ウォッチドッグタイマはリセットの代わりに割り込みを生成する設定にもできます。これはパワーダウン動作から起動するのにウォッチドッグを使う時に大変 有用となり得ます。

表9-1.で示されるように予期せぬウォッチトック禁止や予期せぬ計時終了 周期変更を防ぐため、WDTON構成設定ビットによって2つの異なる安 全レヘルが選択されます。詳細については次の「ウォッチトック、タイマ構成設 定変更用手順」をご覧ください。

#### 表9-1. WDTON構成設定ビットの設定によるウォッチドック、機能設定

| WDTON構成設定ビット                         | 安全レヘル | WDT初期状態 | WDT禁止方法   | 計時完了時間変更方法 |

|--------------------------------------|-------|---------|-----------|------------|

| 非プログラム(1)                            | 1     | 禁止      | 保護された変更手順 | なし(常時可)    |

| フ <sup>°</sup> ロク <sup>・</sup> ラム(0) | 2     | 許可      | なし(常時許可)  | 保護された変更手順  |

### 9.3.1. ウォッチト ック タイマ構成設定変更用手順

ウォッチトック構成設定変更手順は安全レベル間で異なります。

#### 9.3.1.1. 安全レヘル1

この動作種別ではウォッチドッグ タイマが初めに禁止されますが、どんな制限もなくウォッチドッグ システム リセット許可(WDE)ビットに1を書くことに よって許可できます。許可したウォッチドッグ タイマを禁止する時に特別な手順が必要とされます。許可したウォッチドッグ タイマを禁止するに は次の手順に従わなければなりません。

- 1. 保護されたI/Oレジスタの変更許可用の識票を構成設定変更保護(CCP)レジスタに書いてください。

- 2. (次からの)4命令周期内に同じ操作(命令)で欲したWDEとウォッチトッグタイマ前置分周選択(WDP3~0)ビットを書いてください。

#### 9.3.1.2. 安全レヘル2

この動作種別ではウォッチドッグタイマが常に許可され、WDEビットは常に1として読めます。ウォッチドッグ計時完了周期を変更する時に保護された変更が必要とされます。ウォッチドッグ計時完了周期を変更するには次の手順に従わなければなりません。

- 1. 保護されたI/Oレジスタの変更許可用の識票を構成設定変更保護(CCP)レジスタに書いてください。

- 2. (次からの)4命令周期内に同じ操作(命令)でWDP2~0ビットを書いてください。WDEビットに書かれた値は無関係です。

#### 9.3.2. コート 例

次のコート「例はウォッチト、ック(WDT)をOFFに切り替える方法を示します。本例は(例えば全割り込み禁止によって)割り込みが制御され、 それ故この関数実行中に割り込みが起きない前提です。

| アセンブリ言語  | ブログラム例                                        |                                                                                                                                                                                                                                                                   |                                                                                                                           |

|----------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| WDT_OFF: | WDR<br>IN<br>ANDI<br>OUT<br>LDI<br>OUT<br>LDI | R16, RSTFLR<br>R16, ~(1< <wdrf)<br>RSTFLR, R16<br/>R16, \$D8<br/>CCP, R16<br/>R16, (0&lt;<wde)< th=""><th>;ウォッチト、ック、タイマリセット<br/>;現RSTFLR値を取得<br/>;WDRFビットのみ0値を取得<br/>;RSTFLRのWDRFを解除(0)<br/>;変更許可識票値を取得<br/>;構成設定変更許可手順開始<br/>;WDE論理0値を取得</th></wde)<></wdrf)<br> | ;ウォッチト、ック、タイマリセット<br>;現RSTFLR値を取得<br>;WDRFビットのみ0値を取得<br>;RSTFLRのWDRFを解除(0)<br>;変更許可識票値を取得<br>;構成設定変更許可手順開始<br>;WDE論理0値を取得 |

|          | OUT<br>RET                                    | WDTCSR, R16                                                                                                                                                                                                                                                       | ;ウォッチトッグ禁止<br>;呼び出し元へ復帰                                                                                                   |

注:8頁の「コート」例」をご覧ください。

# 9.4. リセット関係レジスタ

9.4.1. WDTCSR - ウォッチトック タイマ制御/状態レジスタ (Watchdog Timer Control and Status Register)

| ビット        | 7    | 6    | 5    | 4 | 3   | 2    | 1    | 0    | _      |

|------------|------|------|------|---|-----|------|------|------|--------|

| \$31       | WDIF | WDIE | WDP3 | - | WDE | WDP2 | WDP1 | WDP0 | WDTCSR |

| Read/Write | R/W  | R/W  | R/W  | R | R/W | R/W  | R/W  | R/W  |        |

| 初期値        | 0    | 0    | 0    | 0 | 不定  | 0    | 0    | 0    |        |

#### • ビット7 - WDIF : ウォッチトック割り込み要求フラク (Watchdog Timer Interrupt Flag)

ウォッチドック「タイマが割り込みに設定され、ウォッチドック「タイマで計時完了が起こると、本ビットが設定(1)されます。対応する割り込み処理へ、 クタを実行すると、WDIFはハート・ウェアによって解除(0)されます。代わりにWDIFはこのフラグへの論理1書き込みによっても解除(0)されま す。ステータスレシ、スタ(SREG)の全割り込み許可(I)ビットとウォッチト、ック、割り込み許可(WDIE)が設定(1)されると、ウォッチト、ック、計時完了割り込 みが実行されます。

#### • ビット6 - WDIE : ウォッチトッグ割り込み許可 (Watchdog Timer Interrupt Enable)

このビットが1を書かれ、SREGの全割り込み許可(I)ビットが設定(1)されると、ウォッチト・ック・割り込みが許可されます。この設定での組み合わせでウォッチト・ック・システムリセット許可(WDE)ビットが解除(0)されると、ウォッチト・ック・タイマは割り込み動作形態になり、ウォッチト・ック・タイマで計時完了が起こると、対応する割り込みが要求されます。

WDEが設定(1)されると、ウォッチトッグタイマは割り込み及びシステムリセット動作形態です。ウォッチトッグタイマでの最初の計時完了がウォッチトックが割り込み要求(WDIF)フラグを設定(1)します。対応する割り込み、クタの実行はハートウェアによってWDIEとWDIFを自動的に解除(0)しま す(ウォッチトッグはシステムリセット動作形態になります)。これは割り込みを使うのと同時にウォッチト、ッグタイマ保護を維持するのに有用です。 割り込み及びシステムリセット動作形態に留まるには、各割り込み後にWDIEが設定(1)されなければなりません。然しながら、これがウォッチ トッグ、システムリセット動作形態の安全機能を危険に晒すかもしれないため、これは割り込み処理ルーチン自身内で行われるべきではあり ません。次の計時完了に先立って割り込みが実行されない場合、システムリセットが適用(実行)されます。

# 表9-2. ウォッチトック タイマ構成設定

| WDTON | WDE | WDIE | 動作種別           | 計時完了での動作             |

|-------|-----|------|----------------|----------------------|

| 1     | 0   | 0    | 停止             | なし                   |

| 1     | 0   | 1    | 割り込み           | 割り込み                 |

| 1     | 1   | 0    | システム リセット      | リセット                 |

| 1     | 1   | 1    | 割り込み及びシステムリセット | 割り込み、その後システムリセット動作種別 |

| 0     | Х   | Х    | システム リセット      | リセット                 |

注: WDTON構成設定ビットは0でプログラム、1で非プログラムに設定です。

#### • ビット4 - Res : 予約 (Reserved)

このビットは予約されており、常に0として読みます。

### • ビット3 - WDE : ウォッチト゛ック゛ システム リセット許可 (Watchdog System Reset Enable)

WDEはリセットフラグレジスタ(RSTFLR)のウォッチトッグリセットフラグ(WDRF)によって無効にされます。これはWDRFが設定(1)されると、WDE が常に設定(1)されることを意味します。WDEを解除(0)するにはWDRFが先に解除(0)されなければなりません。この特徴は失敗を引き起こす状態中の複数リセットと失敗後の安全な起動を保証します。

#### ● ビット5,2~0 - WDP3~0 : ウォッチトック タイマ前置分周選択 (Watchdog Timer Prescaler)

このWDP3~0ビットはウォッチドック、タイマが走行する時のウォッチドック、タイマの前置分周を決めます。各種前置分周値と対応する計時完了 周期は**表9-3**.で示されます。

| 表9-3. ウォッチト ック 前       | 表9−3. ウォッチドッグ前置分周選択 |      |      |        |       |      |      |      |      |       |      |       |   |   |   |   |

|------------------------|---------------------|------|------|--------|-------|------|------|------|------|-------|------|-------|---|---|---|---|

| WDP3                   |                     |      |      | (      | )     |      |      |      |      |       |      | -     | 1 |   |   |   |

| WDP2                   | 0                   |      |      |        | 1     |      |      |      | 0    |       |      |       | 1 |   |   |   |

| WDP1                   | (                   | )    |      | 1      | (     | )    |      | l    | (    | 0 1   |      | 1 0 1 |   |   | 1 |   |

| WDP0                   | 0                   | 1    | 0    | 1      | 0     | 1    | 0    | 1    | 0    | 1     | 0    | 1     | 0 | 1 | 0 | 1 |

| WDT発振周期数               | 2k                  | 4k   | 8k   | 16k    | 32k   | 64k  | 128k | 256k | 512k | 1024k |      |       |   |   |   |   |

| 代表的計時完了<br>周期 (VCC=5V) | 16ms                | 32ms | 64ms | 0.125s | 0.25s | 0.5s | 1.0s | 2.0s | 4.0s | 8.0s  | (予約) |       |   |   |   |   |

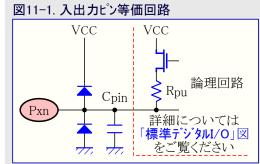

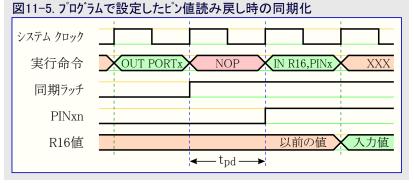

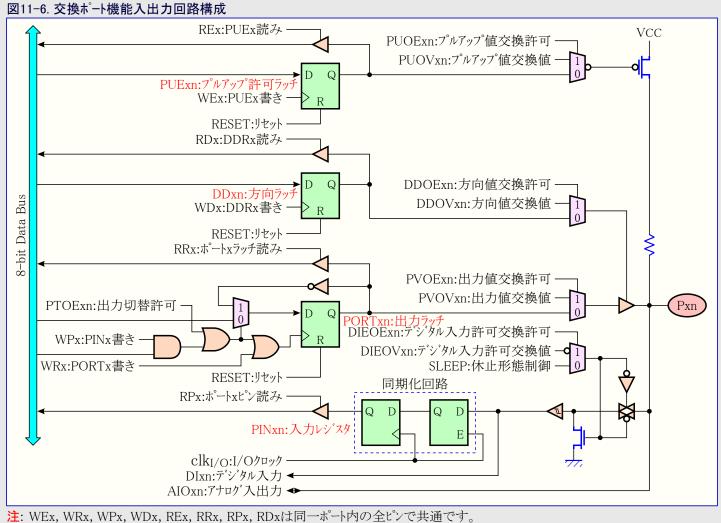

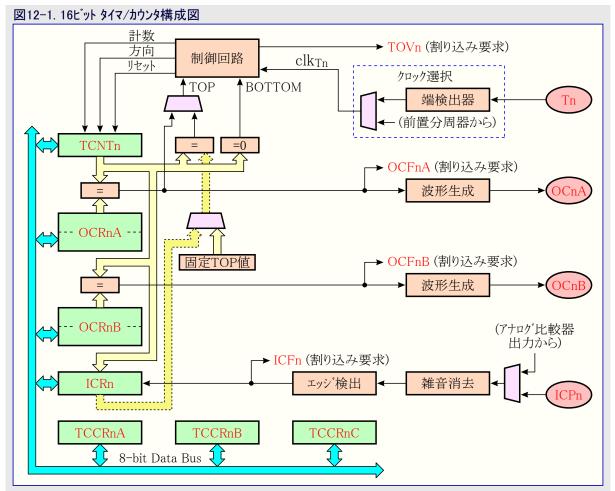

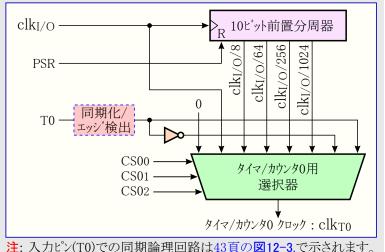

9.4.2. VLMCSR - VCCレヘール監視制御/状態レジスタ (VCC Monitoring Control and Status Register)