## 特徴

- AVR® RISC構造

- AVR -高性能、低消費8ビットRISC構造

- ・強力な90命令(多くは1周期で実行)

- ・32個の1バイト長汎用レジスタ

- ・8MHz時、8MIPSに達する高速動作

- 不揮発性プログラム用メモリとデータ用メモリ

- ・プログラム用1Kバイト(512語)**フラッシュメモリ**内蔵

- Quickflash™ OTP(ワンタイム プログラマブル) ... ATtiny10

- 実装書き換え(ISP: In-System Program)可能 ... ATtiny12

- 1000回の書き換えが可能 ... ATtiny11/12

- ・実装書き換え(ISP)可能な64バイトの**EEPROM** ... ATtiny12

- 100,000回の書き換えが可能

- ・プログラム フラッシュメモリとデータEEPROM保護用の設定可能な**施錠機能**

- 内蔵周辺機能

- ・ピン変化での割り込みと起動復帰

- ・独立した前置分周器付き**8ビット タイマ/カウント**

- ・**アナログ比較器**

- ・設定可能な専用発振器付き**ウォッチドッグ タイマ**

- 特殊マイクロコントローラ機能

- ・アイドルとパワーダウンの2つの**低消費動作**

- ・外部及び内部の**割り込み**

- ・SPIポート経由実装書き換え(ISP) ... ATtiny12

- ・電源ONリセット回路(ATtiny12は**増強された電源ONリセット回路**)

- ・内蔵RC発振器が選択可能(ATtiny12は校正付き内蔵RC発振器)

- 電気的特長

- ・高速、低消費なCMOS製法

- ・完全なスタティック動作

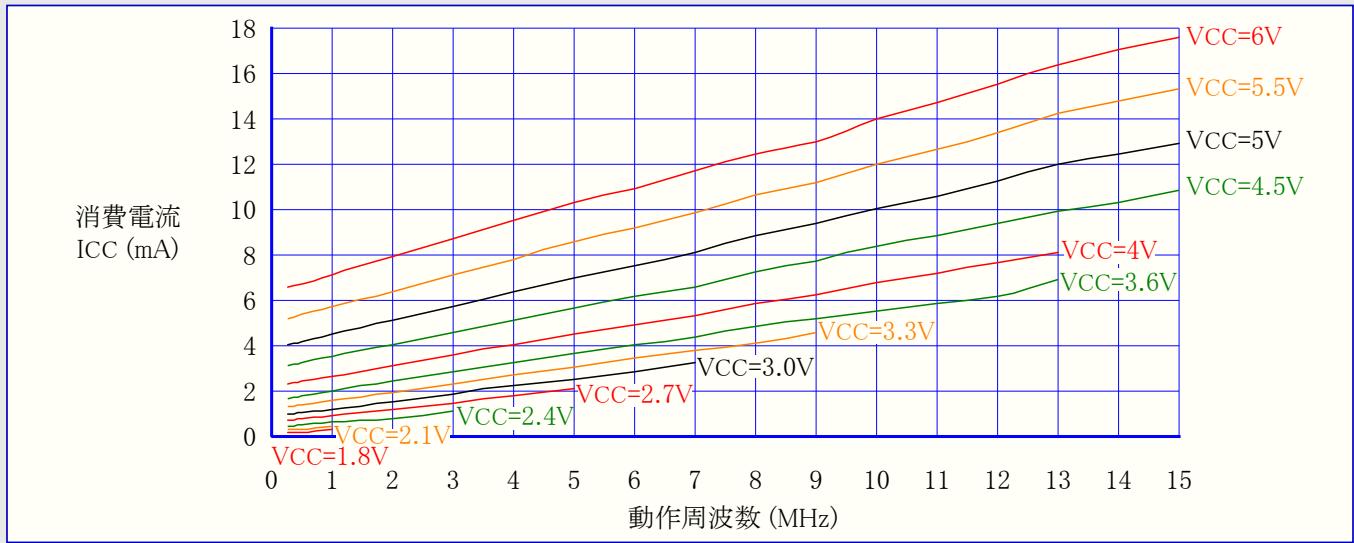

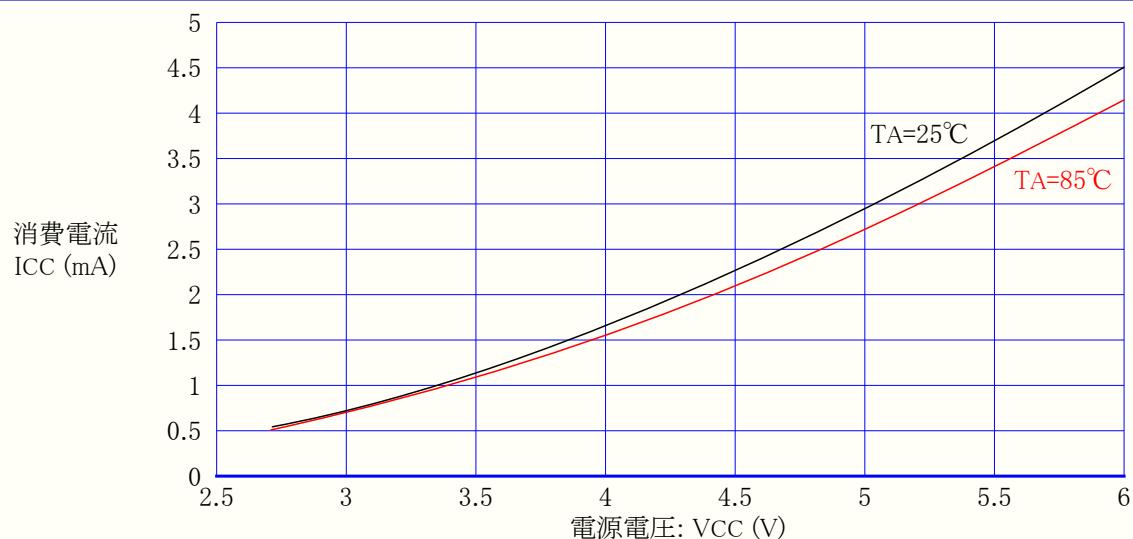

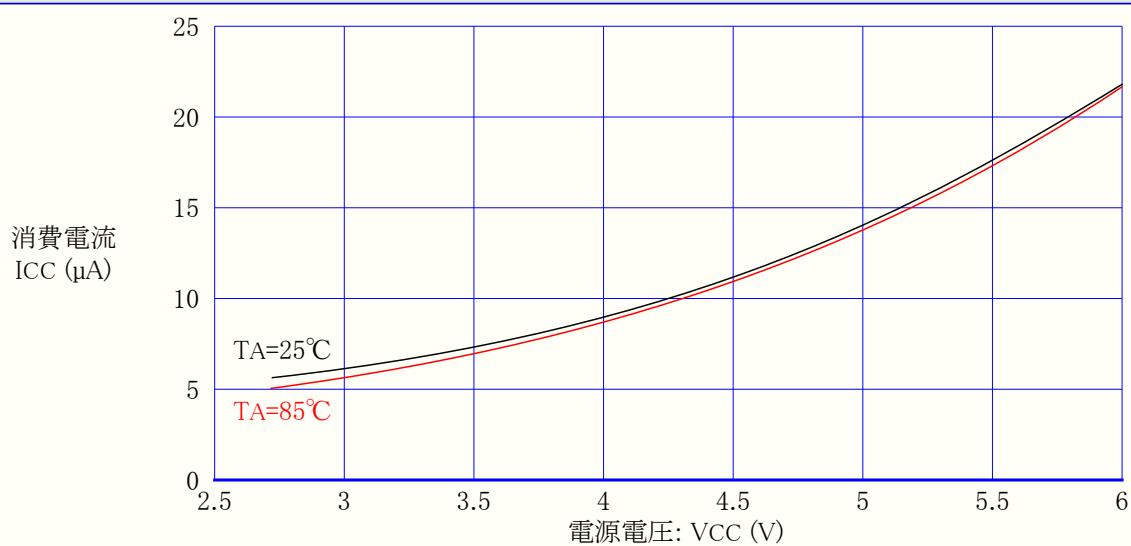

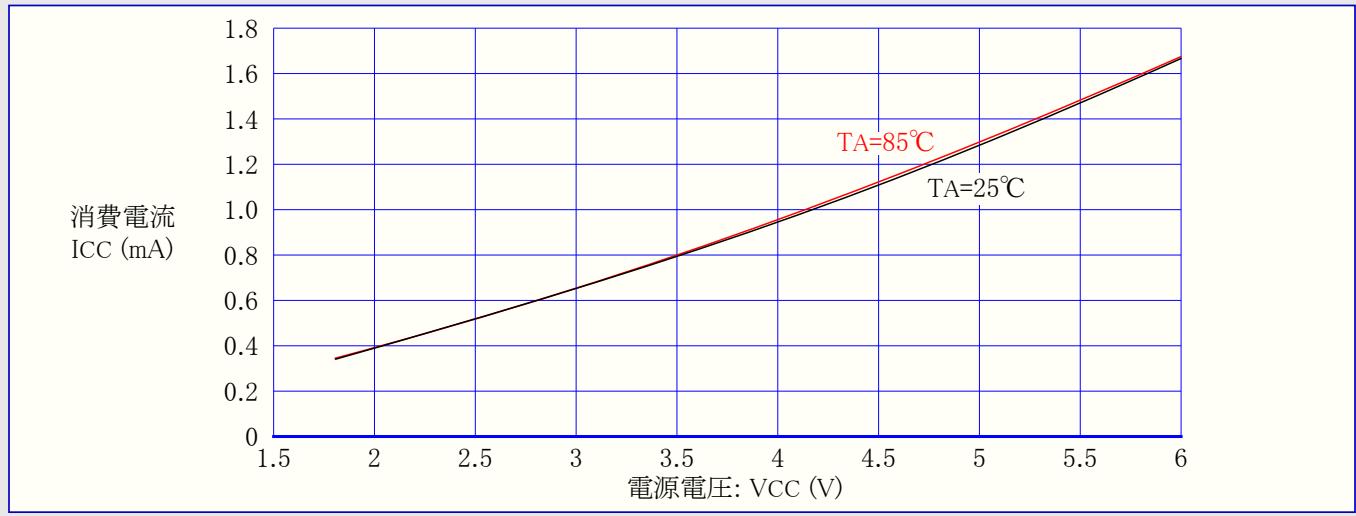

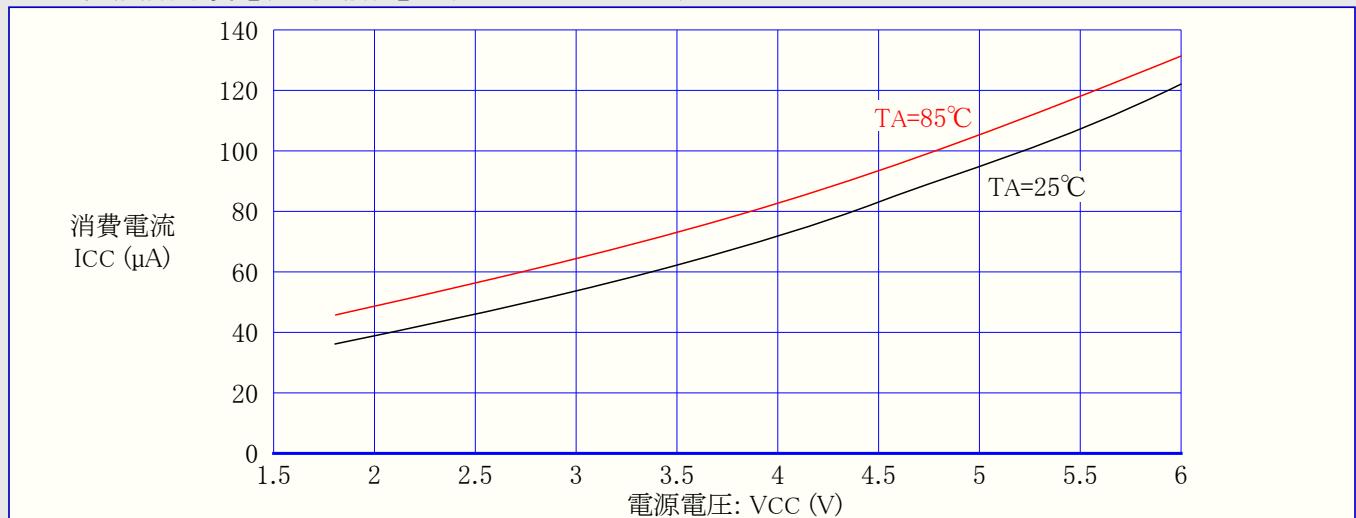

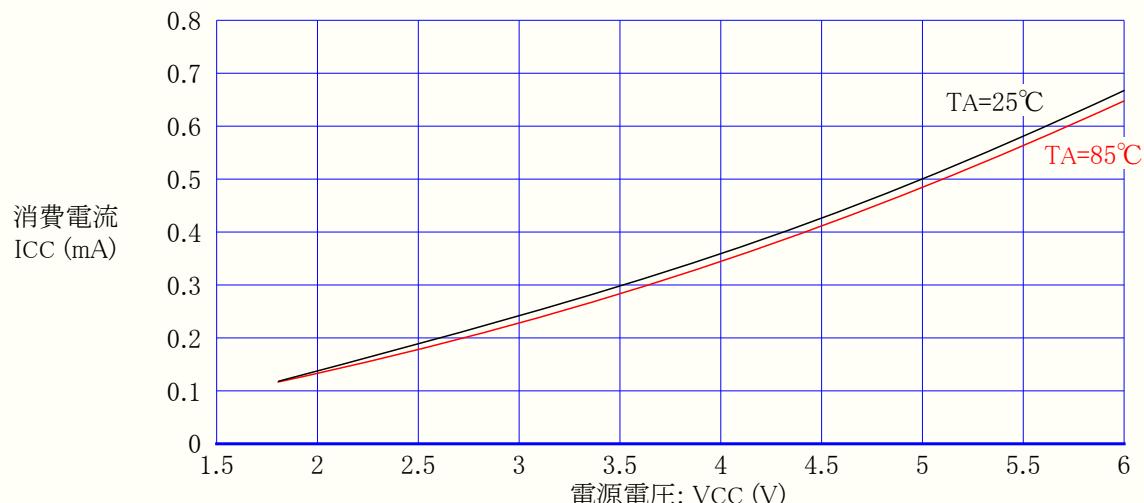

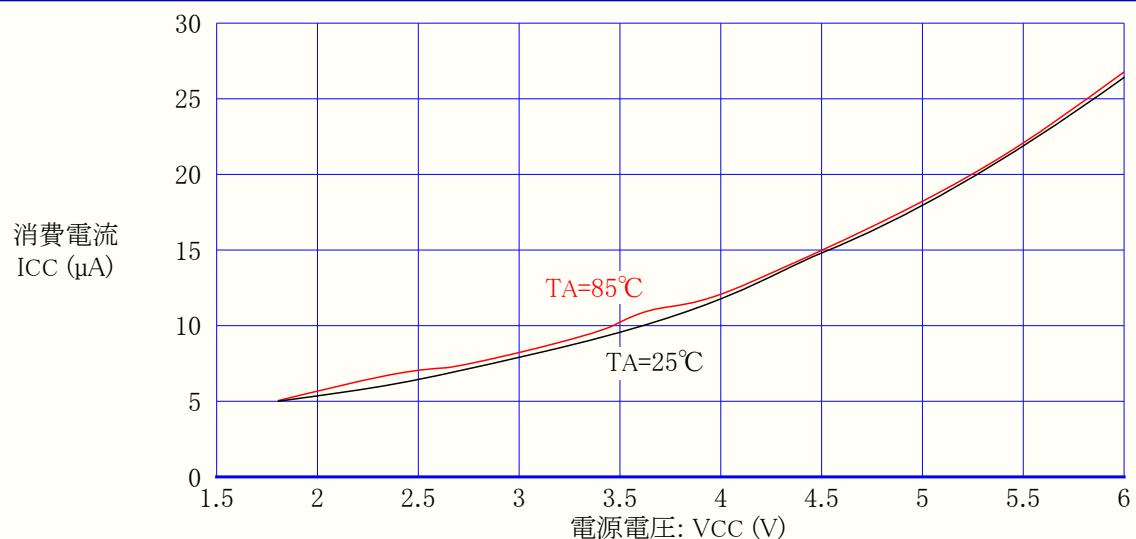

- 消費電流 (条件: 4MHz, 3V, 25°C)

- ・活動動作 ..... 2.2mA

- ・アイドル動作 ..... 0.5mA

- ・パワーダウン動作 ..... 1μA未満

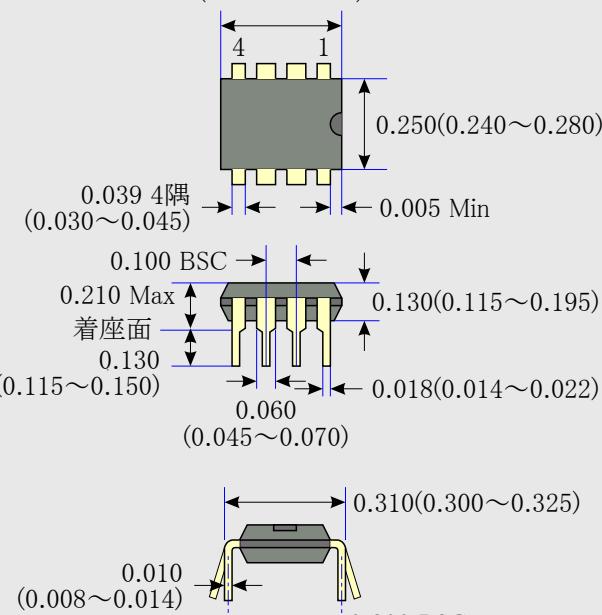

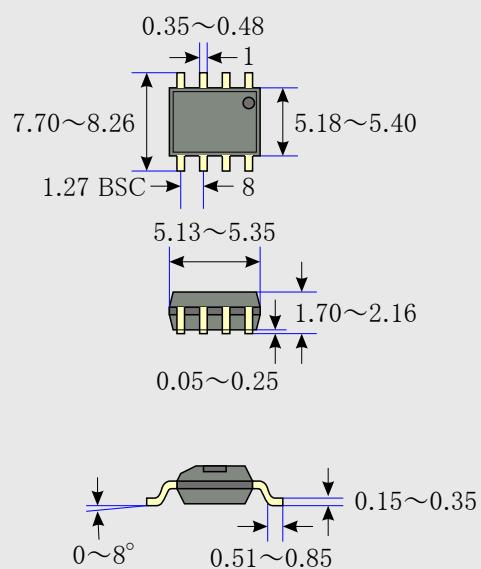

- 外囲器

- ・8ピンPDIP、8リードSOIC

- 動作電圧

- ・1.8~5.5V (ATtiny12V-1)

- ・2.7~5.5V (ATtiny11L-2/ATtiny12L-4)

- ・4.0~5.5V (ATtiny11-6/ATtiny12-8)

- 動作速度

- ・0~1.2MHz (ATtiny12V-1)

- ・0~2MHz (ATtiny11L-2)

- ・0~4MHz (ATtiny12L-4)

- ・0~6MHz (ATtiny11-6)

- ・0~8MHz (ATtiny12-8)

注: ATtiny10はATtiny11のOTP版です。

本書は一般の方々の便宜のため有志により作成されたもので、Atmel社とは無関係であることを御承知ください。しおりの[はじめに]での内容にご注意ください。

8ビット **AVR®**

マイクロ コントローラ

1Kバイト

フラッシュ メモリ内蔵

ATtiny10

ATtiny11

ATtiny12

本製品での新規設計は推奨されません。

ATtiny10は既に廃品種です。

### 重要注意:

本書のATtiny10はかなり以前に製造終了品となった、ATtiny11のOTP版です。

2008年から始まったAVR8LコアのATtiny10とは名称が同じですが、全く別物であることに注意してください。

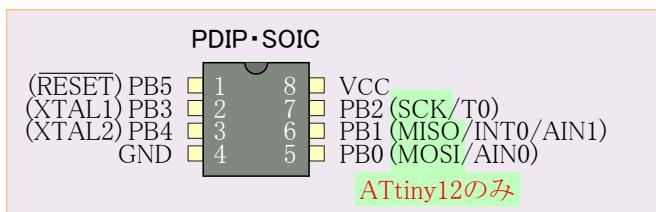

## ピン配置

Rev. 1006B-10/99, 1006BJ13-01/22

Rev. 1006F-06/07, 1006FJ7-01/22

## 概要

ATtiny10/11/12はAVR RISC構造の低消費CMOS 8ビットマイクロコントローラです。1周期で実行する強力な命令はMHzあたり1MIPSにも達し、実行速度対電力消費の最適化が容易に行えます。

AVRは32個の汎用レジスタと豊富な命令群を兼ね備えています。32個の全レジスタはALU(Arithmetic Logic Unit)に直結され、レジスタ間命令は1クロック周期で実行されます。AVR構造は現状のCISC型マイクロコントローラに対し、最大10倍の単位処理量向上効果があります。

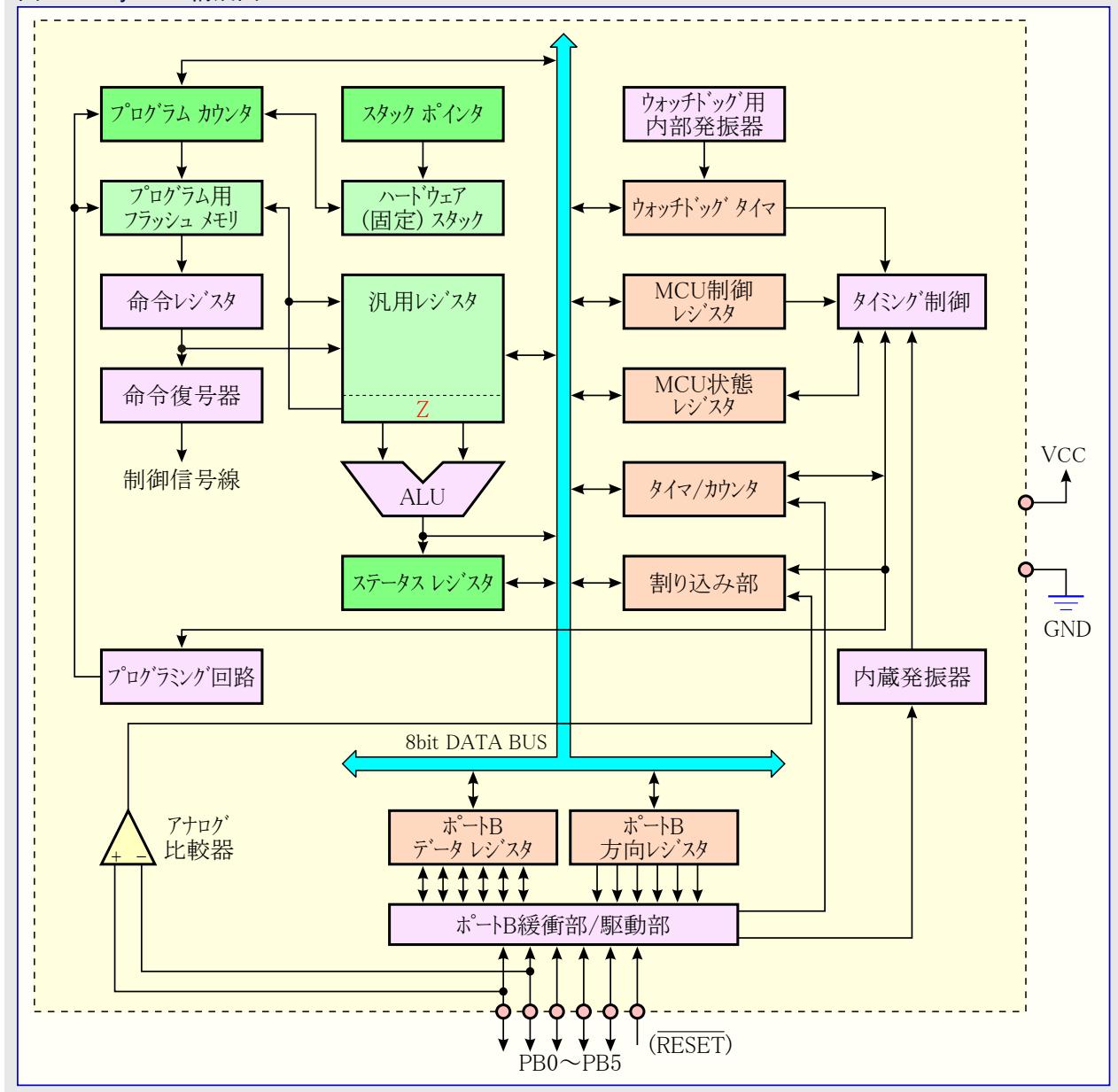

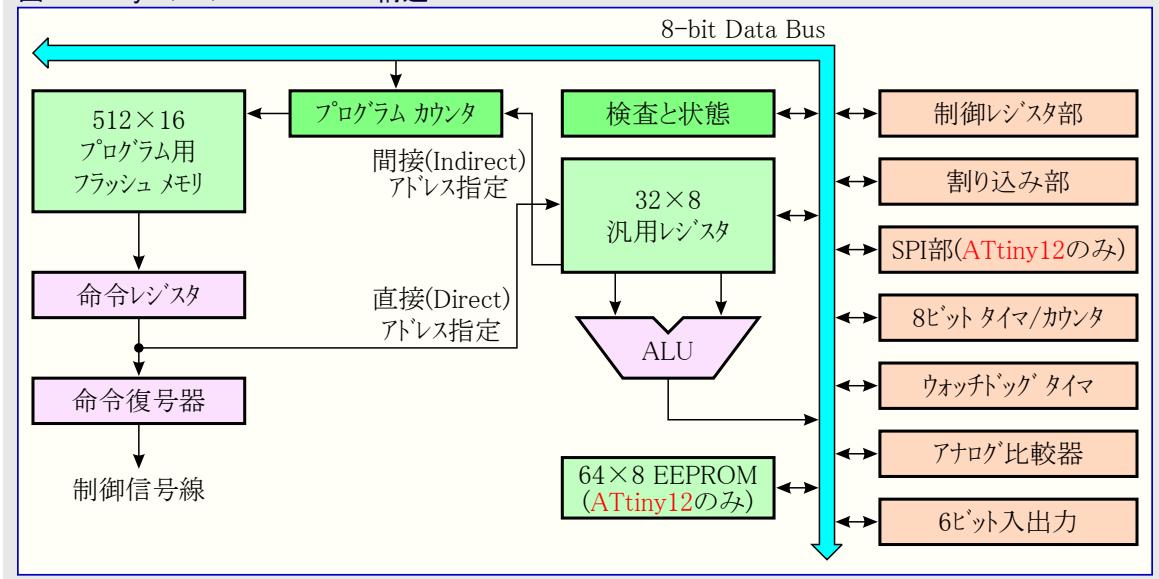

## ATtiny10/11構成図

ATtiny10/11は1Kバイトのフラッシュメモリ、5ビットまでの汎用入出力線、1ビットの入力線、32個の汎用レジスタ、8ビットタイマ/カウンタ、内部及び外部割り込み、設定変更可能な内部発振器付きウォッチドッグタイマ、ソフトウェアで選択できる2つの低消費動作を提供します。アイドル動作では動作を停止しますが、タイマ/カウンタと割り込み機能は有効で、動作を継続します。パワーダウン動作ではレジスタの内容は保護されますが、発振器が停止するため、以降のハードウェアリセットか外部割り込みまで、他の全機能を無効にします。ピン変化での割り込みまたは起動復帰機能は、パワーダウン動作中の最低電力消費の特徴のままで、外部の出来事に対する高い応答性をATtiny10/11で可能にします。

本デバイスはAtmelの高密度不揮発性メモリ技術を使って製造されています。モノリシックチップ上のフラッシュメモリと、拡張された8ビットRISC型CPUの組み合わせによるAtmelのATtiny10/11は、多くの組み込み制御の応用に対して高度な柔軟性と対費用効果をもたらす強力なマイクロコントローラです。

ATtiny10/11 AVRはマクロアセンブラー、デバッガ、シミュレータ、インサキットエミュレータ、評価キットを含む完全なプログラム及びシステム開発ツールで支援されます。

図1. ATtiny10/11構成図

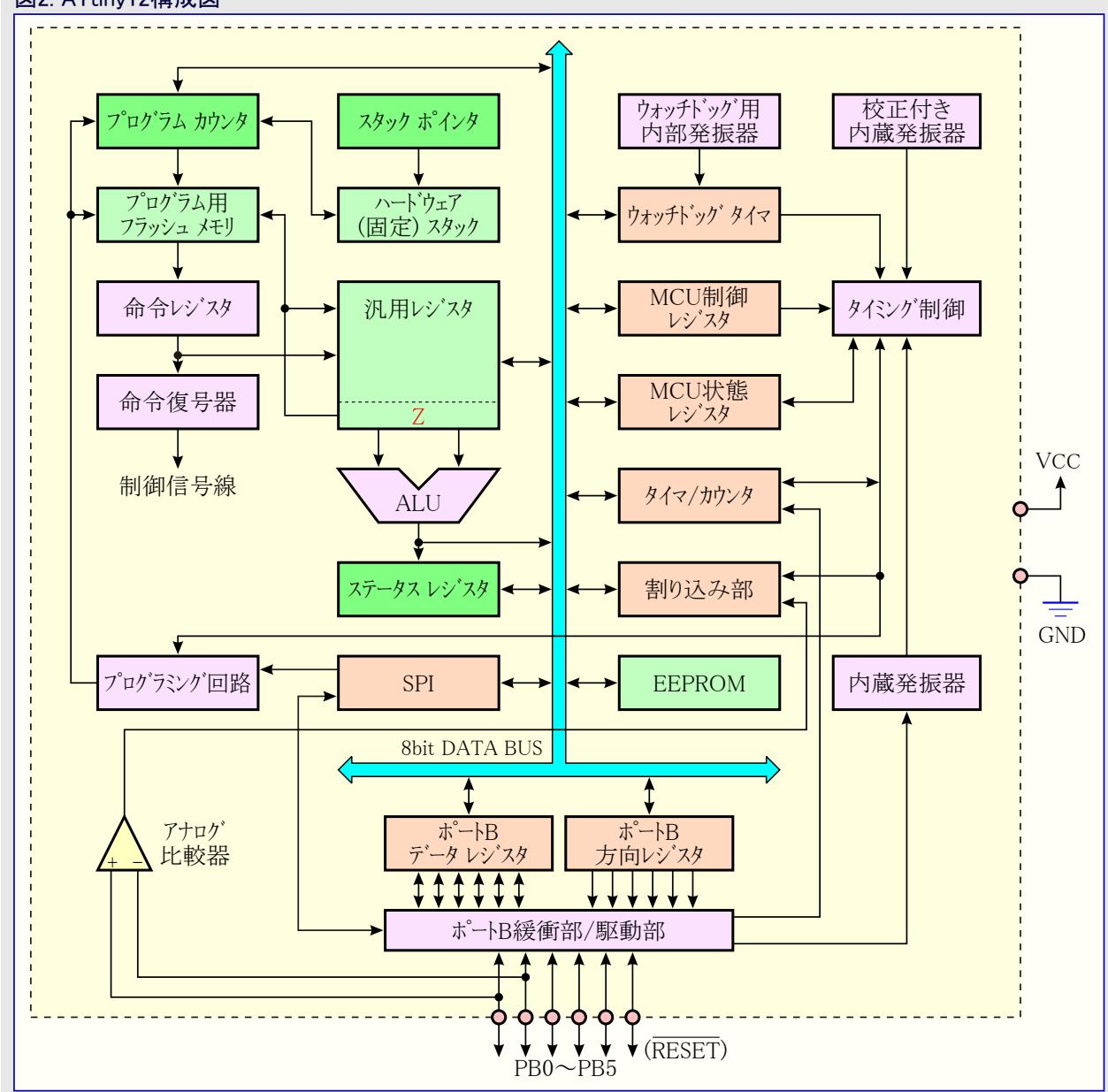

## ATtiny12構成図

ATtiny12は1Kバイトの実装書き換え可能なフラッシュメモリ、64バイトのEEPROM、6ビットまでの汎用入出力線、32個の汎用レジスタ、8ビットタイマ/カウンタ、内部及び外部割り込み、設定変更可能な内部発振器付きウォッチドッグタイマ、ソフトウェアで選択できる2つの低消費動作を提供します。アイドル動作では動作を停止しますが、タイマ/カウンタと割り込み機能は有効で、動作を継続します。パワーダウン動作ではレジスタの内容は保護されますが、発振器が停止するため、以降のハードウェアリセットか外部割り込みまで、他の全機能を無効にします。ピン変化での割り込みまたは起動復帰機能は、パワーダウン動作中の最低電力消費の特徴のままで、外部の出来事に対する高い応答性をATtiny12で可能にします。

本デバイスはATMELの高密度不揮発性メモリ技術を使って製造されています。モノリシックチップ上のフラッシュメモリと、拡張された8ビットRISC型CPUの組み合わせによるATMELのATtiny12は、多くの組み込み制御の応用に対して高度な柔軟性と対費用効果をもたらす強力なマイクロコントローラです。

ATtiny12 AVRはマクロアセンブリ、デバッガ、シミュレータ、インサーキットエミュレータ、評価キットを含む完全なプログラム及びシステム開発ツールで支援されます。

図2. ATtiny12構成図

## ATtiny10/11/12の主な違い

ATtiny10/11/12の各デバイスに於ける主な動作環境の違いを次に示します。

表1. 相違一覧

| デバイス名        | フラッシュメモリ容量 | EEPROM容量 | 電圧範囲     | 動作周波数    |

|--------------|------------|----------|----------|----------|

| ATtiny10/11L | 1Kバイト      | -        | 2.7～5.5V | 0～2MHz   |

| ATtiny10/11  |            |          | 4.0～5.5V | 0～6MHz   |

| ATtiny12V    |            | 64バイト    | 1.8～5.5V | 0～1.2MHz |

| ATtiny12L    |            |          | 2.7～5.5V | 0～4MHz   |

| ATtiny12     |            |          | 4.0～5.5V | 0～8MHz   |

## ピン概要

VCC

電源ピン。

GND

接地ピン。

PB5～PB0 (ポートB)

ポートBは6ビットの入出力ポートです。PB4～0は(ビット単位で選択される)内蔵プルアップ抵抗を供給できるI/Oピンです。ATtiny10/11のPB5は入力専用です。ATtiny12のPB5は入力またはオープンドレイン出力です。リセット条件が活性(有効)になると、例えクロックが動作していないくとも、ポートピンはHi-Zにされます。以下で示されるように、入力またはI/OピンとしてのPB5～3ピンの使用は、リセットとクロック設定に依存して制限されます。

表2. ヒューズ設定によるPB5～3機能一覧

| クロック種別          | PB5             | PB4        | PB3        |

|-----------------|-----------------|------------|------------|

| 外部リセット許可        | リセット入力          | 無関係(入出力)   | 無関係(入出力)   |

| 外部リセット禁止        | 無関係(入力/入出力) (注) |            |            |

| 外部クリスタル/セラミック発振 | 無関係(入力/入出力) (注) | 発振器出力(発振子) | 発振器入力(発振子) |

| 外部RC発振、外部クロック信号 |                 | 無関係(入出力)   | 外部RC入力     |

| 内蔵RC発振          |                 |            | 無関係(入出力)   |

注: PB5はATtiny10/11で入力専用、ATtiny12で入力またはオープンドレイン出力です。

RESET

リセット入力。外部リセットはRESETピンのLowレベルにより生成されます。50nsより長いリセットパルスは、クロックが動作していないくともリセットを発生します。短すぎるパルスはリセットの生成が保証されません。

XTAL1

発振増幅器の反転入力。または外部発振入力。

XTAL2

発振増幅器の出力。

## クロック任意選択

このデバイスは次のクロック元種別を持ち、以下で示されるフラッシュヒューズビットによって選択できます。

各クロック動作種別についての各種選択は12頁の表7.と13頁の表9.で示されるように異なる起動時間を与えます。

表3. クロック選択

| クロック種別           | CKSEL2~0 (ATtiny10/11) | CKSEL3~0 (ATtiny12) |

|------------------|------------------------|---------------------|

| 外部クリスタル/セラミック発振子 | 1 1 1                  | 1 1 1 1 ~ 1 0 1 0   |

| 外部低周波数クリスタル発振子   | 1 1 0                  | 1 0 0 1 ~ 1 0 0 0   |

| 外部RC発振           | 1 0 1                  | 0 1 1 1 ~ 0 1 0 1   |

| 内蔵RC発振           | 1 0 0                  | 0 1 0 0 ~ 0 0 1 0   |

| 外部クロック信号         | 0 0 0                  | 0 0 0 1 ~ 0 0 0 0   |

| (予約)             | その他                    | -                   |

注: 1=非プログラム、0=プログラム

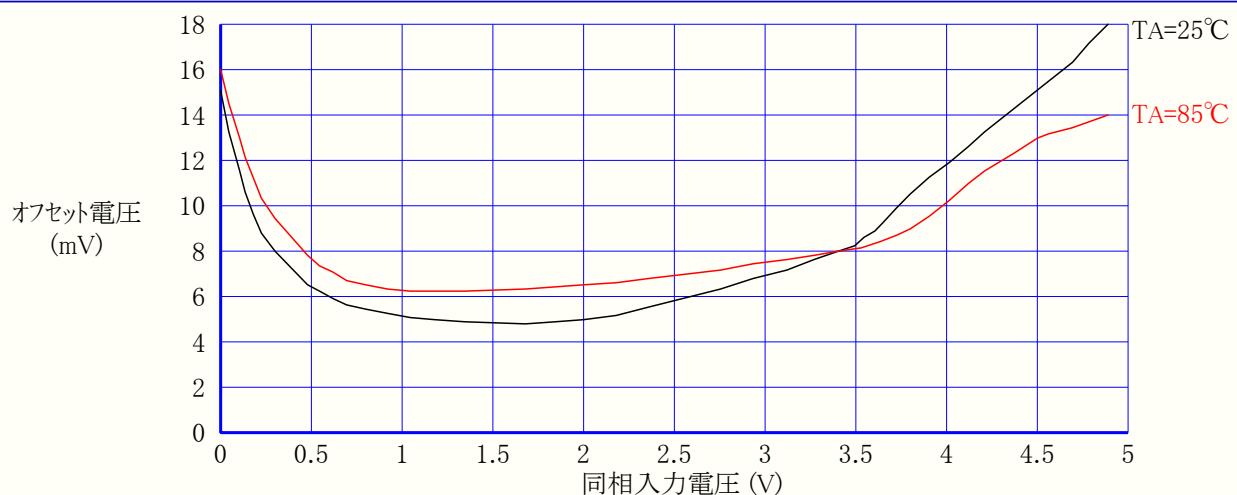

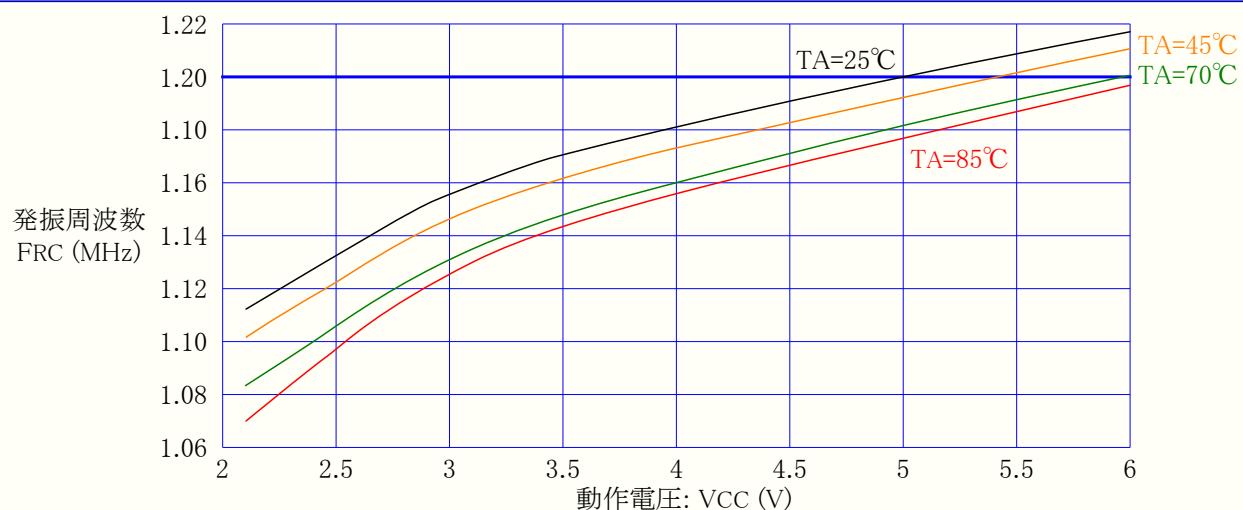

## 内蔵RC発振器

内蔵RC発振器は1MHz(ATtiny10/11), 1.2MHz(ATtiny12)の固定周波数で動作するチップ上の発振器です。選択されたならば、デバイスは外付け部品なしで動作できます。ATtiny10/11ではウォッチドッグ用発振器がこのクロックに使われ、一方ATtiny12は独立の校正された発振器を使います。

(訳注) ATtiny12の内蔵RC発振周波数が改訂Cデータシートで1.0MHzから1.2MHzに変更されています。

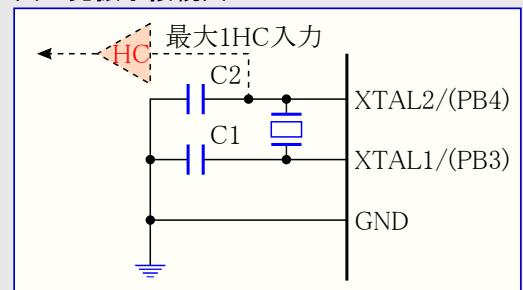

## クリスタル用発振器

図3.で示されるようにXTAL1とXTAL2はチップ上の発振器としての使用に設定できる反転増幅器の各々入力と出力です。クリスタル発振子かセラミック振動子のどちらでも使えます。クリスタル発振子とセラミック振動子の最大周波数は4MHzです。低周波数クリスタル動作での最低電圧は2.5Vです。

注: 外部デバイス用クロックとしてMCU発振器を使う時は図で示されるようにHC緩衝器が接続されるべきです。

図3. 発振子接続図

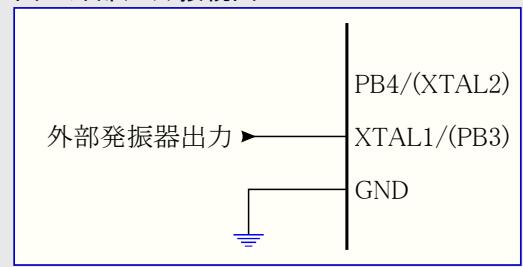

## 外部クロック信号

外部クロック信号でデバイスを駆動するには、図4.で示されるようにXTAL1が駆動されるべきです。

図4. 外部クロック接続図

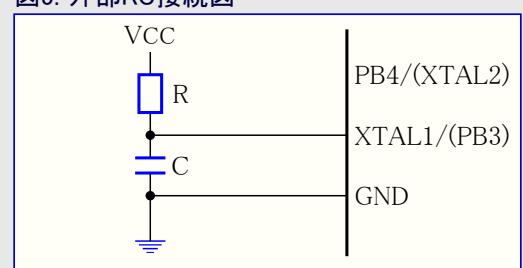

## 外部RC発振器

タイミングに敏感でない応用については図5.で示される外部RC設定が使えます。RとCの選択法の詳細については38頁の表29.をご覧ください。外部RC発振器は隣接するピンからの雑音に敏感で、問題を避けるため、PB5(RESET)は出力またはリセットピンとして、PB4は出力ピンとして使われるべきです。

図5. 外部RC接続図

## 構造概要

1クロック周期アクセス時間の高速レジスタファイルには32個の8ビット長汎用レジスタが含まれます。これは1クロック周期中に1つのALU(Arithmetic Logic Unit)命令が実行されることを意味します。1クロック周期で、2つのオペラントはレジスタファイルから出力され、命令が実行され、その結果がレジスタファイルに書き戻されます。

32個中の2つのレジスタは間接メモリアクセス用16ビットポインタとして使えます。このポインタはZポインタ(レジスタ)と呼ばれ、レジスタファイルとプログラム用フラッシュメモリをアドレス指定できます。

ALUはレジスタ間、レジスタと定数間の算術及び論理操作を行います。単一レジスタ操作も同様にALUで実行されます。図6.はATtiny10/11/12 AVR RISC構造を示します。AVRのメモリとバスはプログラム用とデータ用に各々分離したハーバード構造で構成されます。プログラムメモリは2段のパイプラインでアクセスされます。1命令の実行中に、次の命令をプログラムメモリから事前取得します。この概念は全てのクロック周期で命令が実行されるのを可能にします。プログラムメモリは実装書き換え(ISP)可能なフラッシュメモリです。

図6. ATtiny10/11/12 AVR RISC構造

512アドレス空間全ではプログラムカウンタ(PC)相対の無条件分岐(RJMP)命令と呼び出し(RCALL)命令で直接的にアクセスされます。全てのAVR命令は单一の16ビット語形式で、プログラムメモリ内の全てのアドレスが单一の16ビット長命令を含むことを意味します。

割り込みやサブルーチン呼び出しでの戻りアドレスを示すプログラムカウンタ(PC)はスタックに保存されます。このスタックはサブルーチンと割り込み専用の深さ3段のハードウェアスタックです。

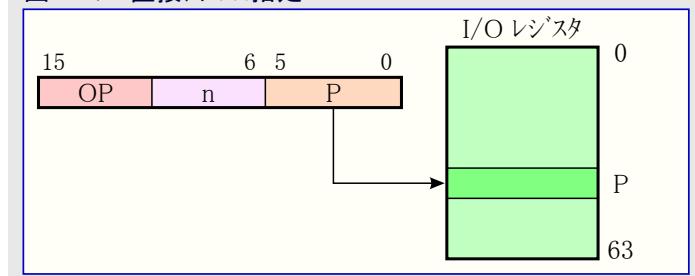

I/Oメモリ空間は制御レジスタ、タイマ/カウンタ、その他I/O機能など、CPU周辺機能用の64アドレスを含みます。AVR構造に於けるメモリ空間は全て規則的で直線的なメモリ配置です。

柔軟な割り込み部にはI/O空間の個別の制御レジスタと、ステータスレジスタ(SREG)の全割り込み許可(I)ビットがあります。各割り込みの全てにはプログラムメモリ先頭の割り込みベクタ表内に個別の割り込みベクタがあります。各割り込みは、この割り込みベクタ表の位置に従った優先順です。下位側割り込みベクタアドレスが高い優先順位です。

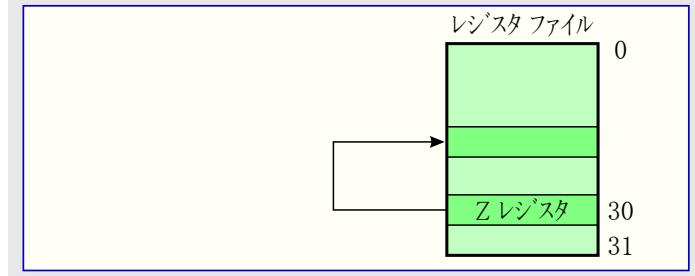

## 汎用レジスタファイル

図7に32個の汎用レジスタの構成を示します。

全てのレジスタに対するレジスタ操作命令はレジスタ直接指定ができ、1周期でアクセスします。SBCI, SUBI, CPI, ANDI, ORIの5つの算術、論理定数演算命令と、定数をレジスタに設定するLDI命令だけが例外です。これらの命令はレジスタファイル後半のR16～R31に対してだけ適用されます。通常のSBC, SUB, CP, AND, ORや他の全てのレジスタ間、单一レジスタ操作命令はレジスタファイルの全レジスタに適用されます。

R30とR31レジスタはフラッシュメモリとレジスタファイルの間接アクセスに使われる16ビットポインタ(Zレジスタ)を形成します。レジスタファイルがアクセスされるとき、R31の内容はCPUにより破棄(無視)されます。

図7. AVR CPU 汎用レジスタ構成図

| 汎用<br>レジスタ<br>ファイル | 7   | 0 | アドレス              |

|--------------------|-----|---|-------------------|

|                    | R0  |   | \$00              |

|                    | ＼   |   |                   |

|                    | R15 |   | \$0F              |

|                    | R16 |   | \$10              |

|                    | ＼   |   |                   |

|                    | R29 |   | \$1D              |

|                    | R30 |   | \$1E              |

|                    | R31 |   | \$1F              |

|                    |     |   | Zレジスタ 下位バイト 上位バイト |

## ALU (Arithmetic Logic Unit)

高性能なAVRのALUは32個全ての汎用レジスタに直接接続され、動作します。レジスタファイル内のレジスタ間ALU操作は、1クロック周期内で実行されます。ALU操作は、算術演算、論理演算、ビット操作の3つの主な種類に大別されます。AVR製品系統のいくつかのマイクロコントローラはALUの算術演算部のハードウェア乗算器が特徴です。

## プログラム用フラッシュメモリ

ATtiny10/11/12には、プログラム保存用に1Kバイトのフラッシュメモリが内蔵されています。全ての命令が单一の16ビット/1語のため、フラッシュメモリは512×16ビットとして構成されています。フラッシュメモリは少なくとも1000回再書き込みの耐久性があります。

ATtiny10/11/12のプログラムカウンタ(PC)は9ビット幅で、プログラムメモリ内の512(語)アドレスを指定します。

フラッシュメモリ書き込みの詳細な記述については[31頁](#)をご覧ください。

## データ用EEPROMメモリ (ATtiny12のみ)

ATtiny12にはデータ用に64バイトのEEPROMが内蔵されています。EEPROMは1バイト単位で読み書きができる、独立したデータ空間として構成されています。EEPROMは100,000回以上の書き換えが可能です。EEPROMとCPU間のアクセスは[25頁](#)のEEPROMアドレスレジスタ、EEPROMデータレジスタ、EEPROM制御レジスタの詳細説明で記述されます。

SPI書き込み(直列プログラミング)の詳細な記述については[35頁](#)をご覧ください。

## サブルーチン、割り込み用スタック

ATtiny10/11/12はサブルーチンと割り込み用に深さ3段のハードウェア(固定)スタックを使います。このスタックは9ビット幅で、サブルーチンや割り込み実行中、プログラムカウンタ(PC)の戻りアドレスを格納します。

PC相対呼び出し(RCALL)命令や割り込み時、スタックレベル0にPCの戻りアドレスがプッシュ(格納)され、他のスタックレベル1,2のデータはスタック内で1段深くなります。RETやRETI命令が実行されると、スタックレベル0から戻りアドレスをPCにポップ(復帰)し、他のスタックレベル1,2のデータはスタック内で1段浅くなります。

3つを超えるサブルーチンや割り込みが続いて実行されると、スタックに書かれた最初の値が上書きされます。4つの復帰アドレスA1, A2, A3, A4をプッシュし、サブルーチンや割り込みの復帰による結果は、ハードウェアスタックからA4, A3, A2とも一度A2をポップします。

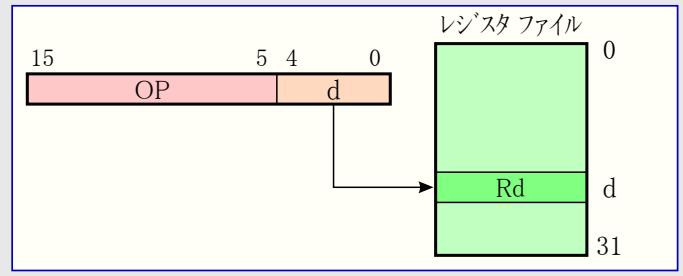

## プログラム及びデータ空間に対するアドレス指定種別

ATtiny10/11/12 AVR RISCマイクロ コントローラは強力で効率的なアドレス指定種別を支援します。本項はATtiny10/11/12で支援される様々なアドレス指定種別を記述します。図内のOPは命令語の動作コード部を意味します。単純化のため、全ての図がアドレス指定ビットの正確な位置を示すとは限りません。

### 単一レジスタ(Rd)直接

図8. 単一レジスタ直接アドレス指定

オペランドはレジスタd(Rd)を示します。

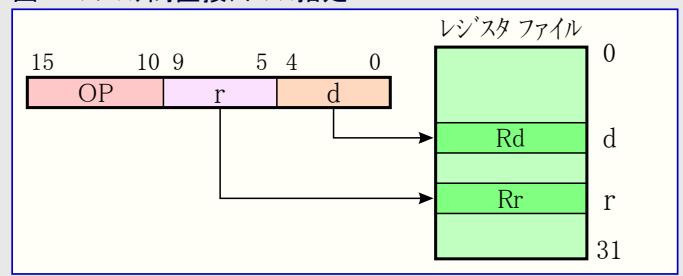

### レジスタ間接(Rd, Rr)直接

図10. レジスタ間接アドレス指定

オペランドはレジスタr(Rr)とd(Rd)を示し、結果はレジスタd(Rd)に格納されます。

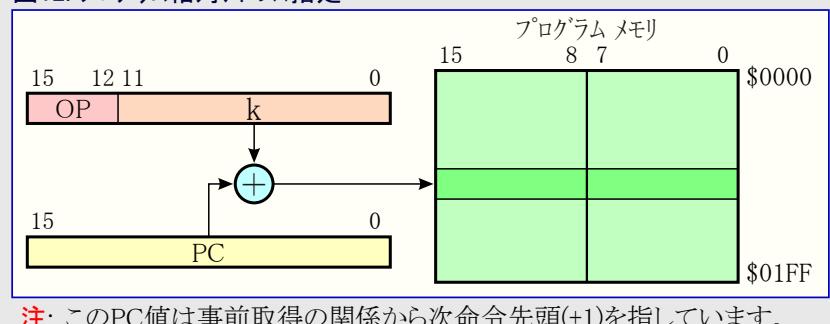

### RJMP, RCALL命令によるプログラム相対アドレス指定

図12. プログラム相対アドレス指定

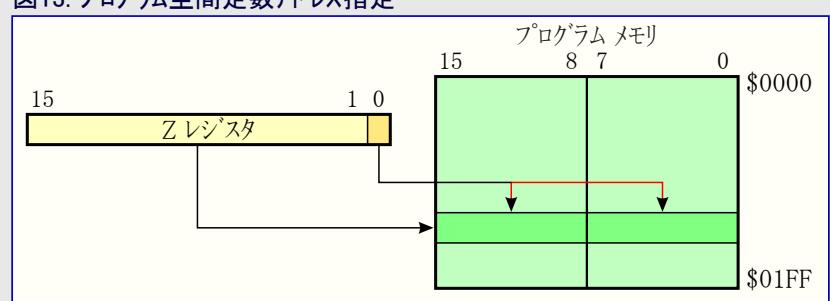

### LPM命令による定数アドレス指定

図13. プログラム空間定数アドレス指定

### レジスタ間接

図9. レジスタ間接アドレス指定

オペランドはZレジスタ(R30)で示されるレジスタです。

### I/O直接

図11. I/O直接アドレス指定

オペランドはI/OアドレスPと、転送元または転送先となるレジスタn (Rn)を示します。

プログラムはPC+k+1のアドレスから継続実行されます。相対値kは符号付きで、-2048~2047です。

バイト定数のアドレスはZレジスタの内容で示されます。上位15ビットが0~511の語(ワード)アドレスを指示し、最下位ビットがバイト位置を表し、LSB=0で下位バイト、LSB=1で上位バイトを示します。

## メモリアクセスと命令実行タイミング

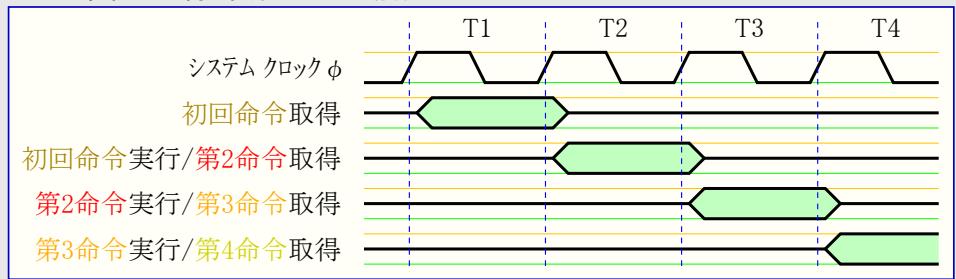

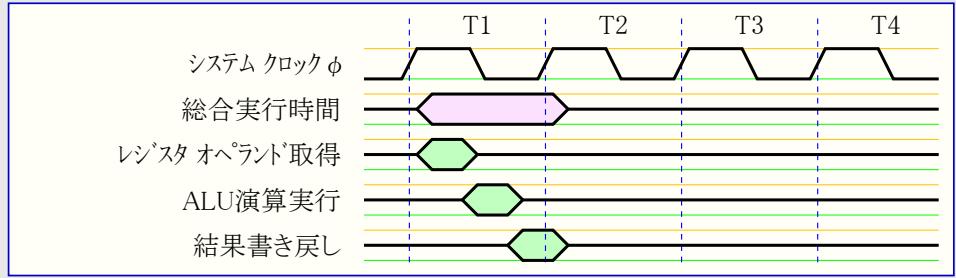

本項は命令実行についての一般的なアクセスタイミングの概念を記述します。

AVR CPUは外部クリスタルまたは内蔵RC発振器で直接的に発生されたシステムクロックφによって駆動されます。内部クロック分周は使われません。

図14.はハーバード構造と高速アクセスレジスタファイルの概念によって可能となる命令取得と命令実行の並列動作を示します。これは機能対費用、対クロック、対電源部での好結果に相当するMHzあたり1MIPSまでを得る基本的なパイプラインの概念です。

図15.はレジスタファイルに対する内部タイミングの概念を示します。2つのレジスタオペランドを使うALU操作は、転送先レジスタへの結果書き戻しを含め、單一クロック周期で実行されます。

図14. 命令の取得と実行の並列動作

図15. 1周期ALU命令

## I/O レジスタ

ATtiny10/11/12のI/O領域定義は次表に示されます。

表4. ATtiny10/11/12 I/Oレジスタ

| アドレス | レジスタ略名 | レジスタ名称                                        |

|------|--------|-----------------------------------------------|

| \$3F | SREG   | Status REGister                               |

| \$3B | GIMSK  | General Interrupt MaSK register               |

| \$3A | GIFR   | General Interrupt Flag register               |

| \$39 | TIMSK  | Timer/Counter Interrupt MaSK register         |

| \$38 | TIFR   | Timer/Counter Interrupt Flag register         |

| \$35 | MCUCR  | MCU general Control Register                  |

| \$34 | MCUSR  | MCU Status Register                           |

| \$33 | TCCR0  | Timer/Counter 0 Control Register              |

| \$32 | TCNT0  | Timer/CouNTer 0 (8bit)                        |

| \$31 | OSCCAL | Oscillator Calibration Register (ATtiny12のみ)  |

| \$21 | WDTCSR | WatchDog Timer Control Register               |

| \$1E | EEAR   | EEPROM Address Register (ATtiny12のみ)          |

| \$1D | EEDR   | EEPROM Data Register (ATtiny12のみ)             |

| \$1C | EECR   | EEPROM Control Register (ATtiny12のみ)          |

| \$18 | PORTB  | Data Register, Port B                         |

| \$17 | DDRB   | Data Direction Register, Port B               |

| \$16 | PINB   | Input Pins, Port B                            |

| \$08 | ACSR   | Analog Comparator Control and Status Register |

注: 予約と未使用の位置は、この表で示されていません。

ATtiny10/11/12の全てのI/Oと周辺部はI/O空間に配置されています。各I/O位置は、I/O空間と32個の汎用レジスタ間のデータ移動を行うIN命令とOUT命令によってアクセスされます。アドレス\$00～\$1F範囲内のI/Oレジスタは、SBIとCBI命令を使う直接ビットアクセスが可能です。これらのレジスタでは、SBISとSBIC命令の使用により、单一ビット値の検査ができます。より詳細な内容は命令要約を参照してください。

将来のデバイスとの共通性を保つため、予約ビットに書く場合は0を書くべきです。予約済みI/Oアドレスは決して書かれるべきではありません。

I/Oと周辺制御レジスタは次章で説明されます。

## ■ ステータス レジスタ (Status Register) SREG

AVRのステータス レジスタ(SREG)は、I/O領域の\$3Fで、次のように定義されています。

| ビット        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |      |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$3F       | I   | T   | H   | S   | V   | N   | Z   | C   | SREG |

| Read/Write | R/W |      |

| 初期値        | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

### ■ ビット7 – I : 全割り込み許可 (Global Interrupt Enable)

この全割り込み許可ビットは割り込みを許可する場合、設定(1)しなければなりません。各割り込みの許可は、各制御レジスタで個別に行います。全割り込み許可ビットが解除(0)されると、個別に割り込みが許可されていても割り込みは発生しません。このIビットは割り込み発生後、自動的に解除(0)され、後続の割り込みを許可するため、割り込み処理のRETI命令によって設定(1)されます。

### ■ ビット6 – T : ビット変数 (Bit Copy Storage)

このTビットはBLD(Bit LoaD)命令とBST(Bit STore)命令の転送元または転送先として使われます。BLD命令はTをレジスタ ファイルのレジスタのビットに複写し、BST命令はレジスタ ファイルのレジスタからビットをTに複写します。

### ■ ビット5 – H : ハーフキャリー フラグ (Half Carry Flag)

このHフラグはいくつかの算術演算命令でのハーフキャリーを示します。ハーフキャリーはBCD演算に有用です。詳細情報については[命令要約](#)を参照してください。

### ■ ビット4 – S : 符号 (Sign Bit, S= N Ex-OR V)

このSフラグは常に負(N)フラグと2の補数溢れ(V)フラグの排他的論理和です。詳細情報については命令要約を参照してください。

### ■ ビット3 – V : 2の補数溢れフラグ (2's Complement Overflow Flag)

この2の補数溢れ(V)フラグは2の補数算術演算を補助します。詳細情報については命令要約を参照してください。

### ■ ビット2 – N : 負フラグ (Negative Flag)

このNフラグは算術及び論理演算の結果が負であること(MSB=1)を示します。詳細情報については命令要約を参照してください。

### ■ ビット1 – Z : ゼロ フラグ (Zero Flag)

このZフラグは算術及び論理演算の結果がゼロ(0)であることを示します。詳細情報については命令要約を参照してください。

### ■ ビット0 – C : キャリー フラグ (Carry Flag)

このCフラグは算術及び論理演算でキャリーが発生したことを示します。詳細情報については命令要約を参照してください。

ステータス レジスタは割り込み処理ルーチン移行時の保存と、割り込み処理ルーチンから復帰時の再設定が、自動的に行われないことに注意してください。これはソフトウェアによって操作しなければなりません。

## リセットと割り込みの扱い

ATtiny10/11には4種類、ATtiny12には5種類の割り込みがあります。これらの割り込みとリセットのベクタは、プログラムメモリ空間内に各々個別のベクタを持っています。全ての割り込みは、割り込みを許可するために個別の許可ビットとステータスレジスタ(SREG)の全割り込み許可(DI)ビットを設定(1)しなければなりません。

プログラムメモリ空間の最下位アドレスは、リセットと割り込みのベクタとして自動的に定義されています。このベクタの全一覧は表5に示されます。この一覧が各割り込みの優先順位も決めます。下位アドレスがより高い優先順位です。リセットが最高優先順位で、以下、外部割り込み要求0(INT0)の順です。

表5. リセットと割り込みのベクタ

| ベクタ番号 | プログラムアドレス | 発生元                                         | 備考                       |

|-------|-----------|---------------------------------------------|--------------------------|

| 1     | \$000     | リセット                                        | 電源ONまたはウォッチドッグ等のリセット     |

| 2     | \$001     | INT0                                        | 外部割り込み要求0                |

| 3     | \$002     | PIN_CHG                                     | I/Oピンレベル変化               |

| 4     | \$003     | タイマ/カウンタ0 OVF0                              | タイマ/カウンタ0溢れ              |

| 5     | \$004     | ANA_COMP (ATtiny10/11)<br>EE_RDY (ATtiny12) | アナログ比較器出力遷移<br>EEPROM操作可 |

| 6     | \$005     | ANA_COMP (ATtiny12)                         | アナログ比較器出力遷移              |

ATtiny10/11に於けるリセットと割り込みのベクタの最も代表的な設定例を次に示します。

| アドレス  | ラベル    | 命令            | 注釈           |

|-------|--------|---------------|--------------|

| \$000 |        | RJMP RESET    | ;各種リセット      |

| \$001 |        | RJMP EXT_INT0 | ;外部割り込み要求0   |

| \$002 |        | RJMP PIN_CHG  | ;I/Oピンレベル変化  |

| \$003 |        | RJMP TIM_OVF0 | ;タイマ/カウンタ0溢れ |

| \$004 |        | RJMP ANA_COMP | ;アナログ比較器出力遷移 |

| ;     |        |               |              |

| \$005 | RESET: | {             | ;以下、I/O初期化など |

ATtiny12に於けるリセットと割り込みのベクタの最も代表的な設定例を次に示します。

| アドレス  | ラベル    | 命令            | 注釈           |

|-------|--------|---------------|--------------|

| \$000 |        | RJMP RESET    | ;各種リセット      |

| \$001 |        | RJMP EXT_INT0 | ;外部割り込み要求0   |

| \$002 |        | RJMP PIN_CHG  | ;I/Oピンレベル変化  |

| \$003 |        | RJMP TIM_OVF0 | ;タイマ/カウンタ0溢れ |

| \$004 |        | RJMP EE_RDY   | ;EEPROM操作可   |

| \$005 |        | RJMP ANA_COMP | ;アナログ比較器出力遷移 |

| ;     |        |               |              |

| \$006 | RESET: | {             | ;以下、I/O初期化など |

## リセット発生元

ATtiny10/11/12には次の3または4つのリセット発生元があります。

- ・ **電源ONリセット** ..... 電源電圧が**電源ONリセット閾値電圧(VPOT)**以下でリセットになります。

- ・ **外部リセット** ..... **RESET**ピンが50ns以上Lowレベルに保たれるとリセットになります。

- ・ **ウォッチドッグリセット** ..... ウォッチドッグが許可され、ウォッチドッグ タイマ周期が経過するとリセットになります。

- ・ **低電圧検出(BOD)リセット** ..... 供給電圧(VCC)が**或る電圧**以下に下がるとリセットになります。(ATtiny12のみ)

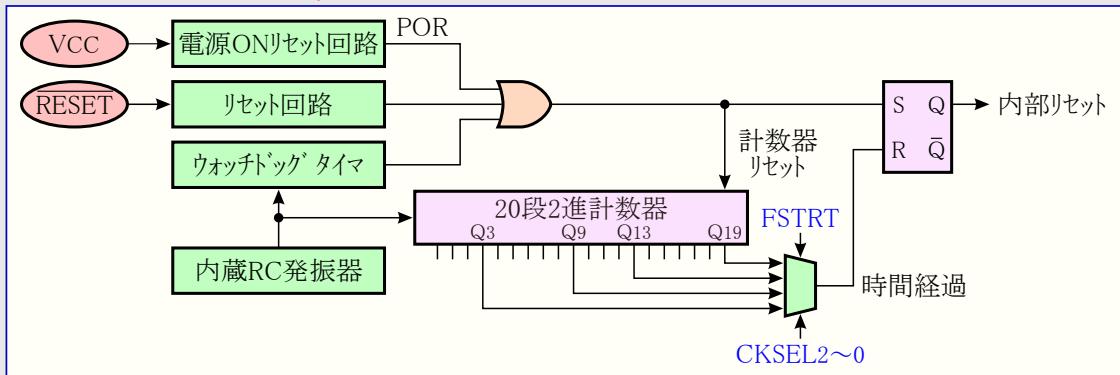

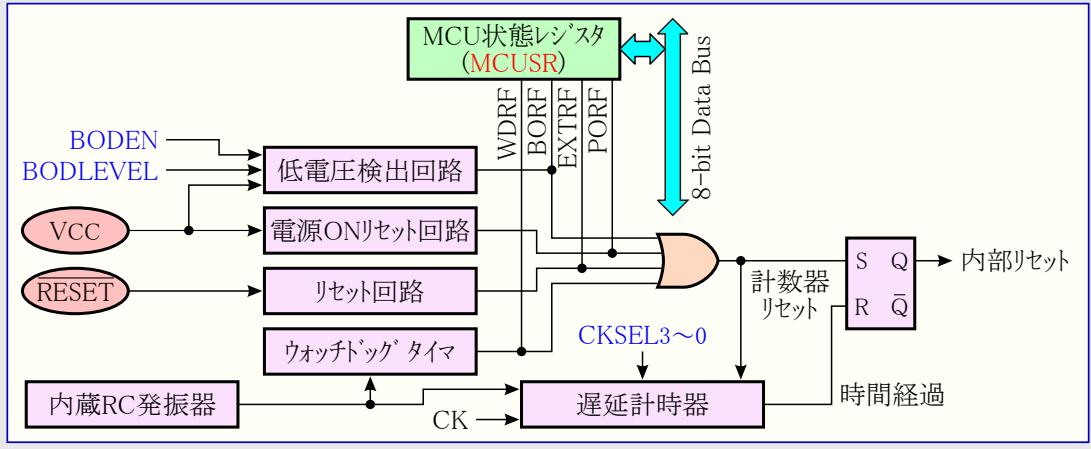

リセット中に全てのI/Oレジスタは初期値が設定され、その後にアドレス\$000からプログラム実行が始まります。アドレス\$000に配置される命令はきっとリセット処理ルーチンへの無条件相対分岐(RJMP)命令でしょう。プログラムで決して割り込みを許可しないなら、割り込みベクタが使われず、これらの位置に通常のプログラムを配置できます。図16.の回路構成はATtiny10/11のリセット回路を示します。図17.はATtiny 12のリセット回路を示します。表6.はATtiny10/11についてのリセット回路の電気的特性値を定義します。表8.はATtiny12についてのリセット回路の特性値を示します。

図16. リセット回路構成 (ATtiny10/11)

表6. リセット電気的特性 (ATtiny10/11)

| シンボル | 項目                   | 最小  | 代表     | 最大  | 単位 |

|------|----------------------|-----|--------|-----|----|

| VPOT | 上昇時電源ONリセット閾値電圧      | 1.0 | 1.4    | 1.8 | V  |

|      | 下降時電源ONリセット閾値電圧 (注1) | 0.4 | 0.6    | 0.8 |    |

| VRST | RESETピン閾値電圧          |     | 0.6VCC |     |    |

注1: 供給電圧がこの電圧以下にならないと、上昇時の電源ONリセットは動作しません。

## 電源ONリセット (ATtiny10/11)

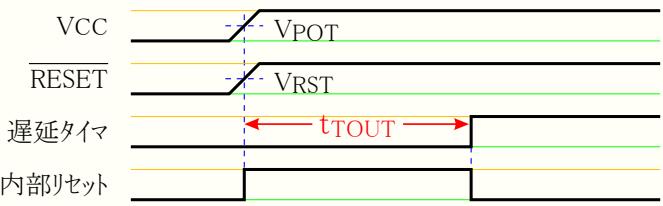

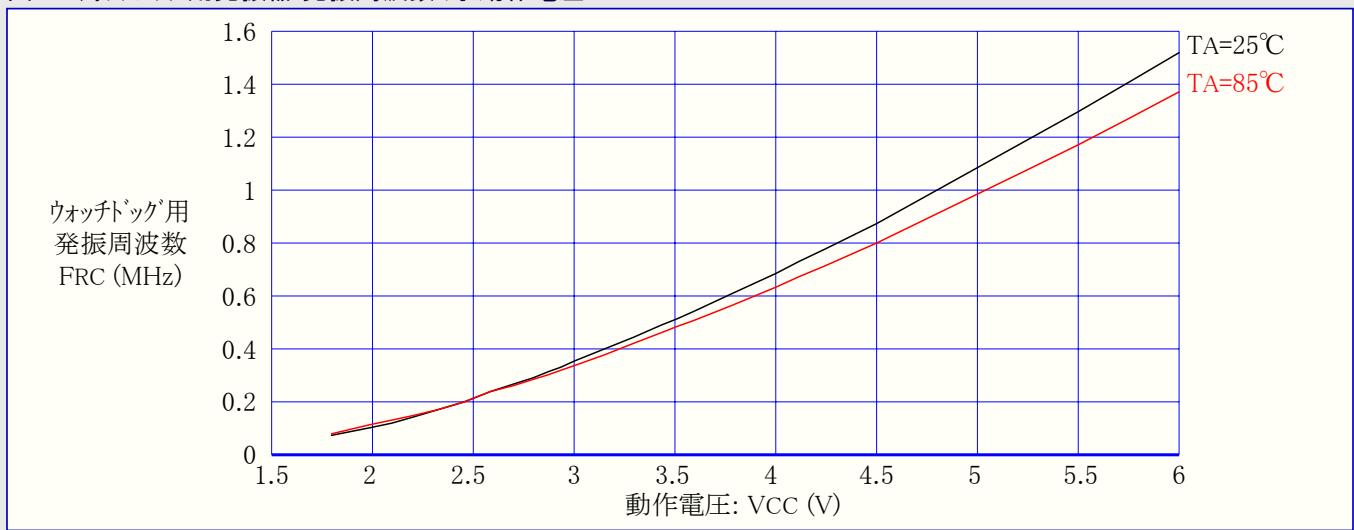

電源ONリセット(POR)回路は電源投入時のデバイスリセットを保証します。図16.で示されるように内部タイマはウォッチドッグ発振器で駆動されます。この内部タイマはVCC上昇時間に拘らず、VCCが**電源ON閾値電圧(VPOT)**に達した後の或る期間後までMCUを開始から保護します(図18.参照)。フラッシュメモリ内の**FSTRT**ヒューズビットは短い起動遅延時間を与えるためにプログラム(0)することができます。各クロック種別に対する起動時間は次表で示されます。起動時間のタイミングにはウォッチドッグ発振器が使われ、39頁の「ATtiny10/11 代表特性」章で示されるように、この発振器は電圧に依存します。

表7. リセット遅延時間 (ATtiny10/11, VCC=2.7V)

| クロック種別           | CKSEL2~0 | リセット遅延時間 (t <sub>TO</sub> UT) |                        |

|------------------|----------|-------------------------------|------------------------|

|                  |          | FSTRT 非プログラム(1)               | FSTRT プログラム(0)         |

| 外部クリスタル/セラミック発振子 | 1 1 1    | 67ms                          | 4.2ms                  |

| 外部低周波数クリスタル発振子   | 1 1 0    | 4.2s                          | 4.2s                   |

| 外部RC発振           | 1 0 1    | 4.2ms                         | 67μs                   |

| 内蔵RC発振           | 1 0 0    | 4.2ms                         | 67μs                   |

| 外部クロック信号         | 0 0 0    | 4.2ms                         | 5クロック (パワーダウンからは2クロック) |

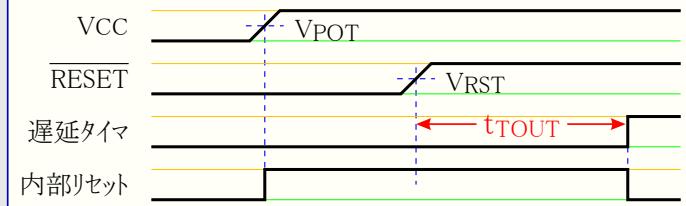

内蔵起動遅延時間で充分な場合、RESETは直接または外部プルアップ抵抗を介してVCCに接続できます。VCC供給後も、RESETピンをLowレベルに保持することで、起動遅延時間は延長できます。このタイミング例については図19.を参照してください。

図17. リセット回路構成 (ATtiny12)

表8. リセット電気的特性 (ATtiny12)

| シンボル             | 項目                       | 最小                 | 代表     | 最大  | 単位  |

|------------------|--------------------------|--------------------|--------|-----|-----|

| V <sub>POT</sub> | 上昇時電源ONリセット<br>閾値電圧      | BODEN=非プログラム(1)/禁止 | 1.0    | 1.4 | 1.8 |

|                  |                          | BODEN=プログラム(0)/許可  | 0.6    | 1.2 | 1.8 |

|                  | 下降時電源ONリセット<br>閾値電圧 (注1) | BODEN=非プログラム(1)/禁止 | 0.4    | 0.6 | 0.8 |

|                  |                          | BODEN=プログラム(0)/許可  | 0.6    | 1.2 | 1.8 |

| V <sub>RST</sub> | RESETピン閾値電圧              |                    | 0.6VCC |     |     |

| V <sub>BOT</sub> | 低電圧検出(BOD)<br>閾値電圧       | BODLEVEL=非プログラム(1) | 1.5    | 1.8 | 1.9 |

|                  |                          | BODLEVEL=プログラム(0)  | 2.3    | 2.7 | 2.8 |

注1: 供給電圧がこの電圧以下にならないと、上昇時の電源ONリセットは動作しません。

右表はリセットからの起動時間を示します。休止形態からは(表の)CK計数部だけが使われます。起動時間の実時間部のタイミングについてはウォッチドッグ発振器が使われます。この実時間に対するウォッチドッグ発振器の計数値は表10で示されます。

表10. ウォッチドッグ発振器の周期数

| BODLEVEL  | タイミング(VCC)   | 周期数 |

|-----------|--------------|-----|

| 非プログラム(1) | 3.6ms (1.8V) | 256 |

|           | 57ms (1.8V)  | 4K  |

| プログラム(0)  | 4.2ms (2.7V) | 1K  |

|           | 67ms (2.7V)  | 16K |

47頁の「ATtiny12 代表特性」章で示されるように、ウォッチドッグ発振器の周波数は電圧に依存します。(BODENヒューズを非プログラムのままですることで)低電圧検出(BOD)が禁止されていても、BODLEVELヒューズは起動(遅延)時間を選ぶのに使えます。

このデバイスはCKSEL3~0=0010で出荷されます。

表9. CKSELヒューズによるリセット遅延選択 (ATtiny12)

| CKSEL3~0 | クロック種別          | リセット遅延時間(t <sub>TOUT</sub> ) |                        |

|----------|-----------------|------------------------------|------------------------|

|          |                 | VCC=1.8V<br>BODLEVEL=1       | VCC=2.7V<br>BODLEVEL=0 |

| 0 0 0 0  | 外部クロック信号        | 3.6ms + 6×CK                 | 4.2ms + 6×CK           |

|          |                 | 6×CK                         | 6×CK                   |

| 0 0 1 0  | 内蔵RC発振          | 57ms + 6×CK                  | 67ms + 6×CK            |

|          |                 | 3.6ms + 6×CK                 | 4.2ms + 6×CK           |

| 0 0 1 1  | 内蔵RC発振          | 6×CK                         | 6×CK                   |

|          |                 | 57ms + 6×CK                  | 67ms + 6×CK            |

| 0 1 0 0  | 外部RC発振          | 3.6ms + 6×CK                 | 4.2ms + 6×CK           |

|          |                 | 6×CK                         | 6×CK                   |

| 0 1 0 1  | 外部RC発振          | 57ms + 6×CK                  | 67ms + 6×CK            |

|          |                 | 3.6ms + 6×CK                 | 4.2ms + 6×CK           |

| 0 1 1 0  | 外部RC発振          | 6×CK                         | 6×CK                   |

|          |                 | 57ms + 32K×CK                | 67ms + 32K×CK          |

| 0 1 1 1  | 外部低周波数クリスタル発振   | 57ms + 1K×CK                 | 67ms + 1K×CK           |

|          |                 | 3.6ms + 1K×CK                | 4.2ms + 1K×CK          |

| 1 0 0 0  | 外部低周波数クリスタル発振   | 16K×CK                       | 16K×CK                 |

|          |                 | 57ms + 1K×CK                 | 67ms + 1K×CK           |

| 1 0 0 1  | 外部クリスタル/セラミック発振 | 3.6ms + 1K×CK                | 4.2ms + 1K×CK          |

|          |                 | 16K×CK                       | 16K×CK                 |

| 1 0 1 0  | 外部クリスタル/セラミック発振 | 57ms + 16K×CK                | 67ms + 16K×CK          |

|          |                 | 3.6ms + 16K×CK               | 4.2ms + 16K×CK         |

| 1 0 1 1  | (注1)            | 16K×CK                       | 16K×CK                 |

|          |                 | 57ms + 1K×CK                 | 67ms + 1K×CK           |

| 1 1 0 0  | (注1)            | 3.6ms + 1K×CK                | 4.2ms + 1K×CK          |

|          |                 | 16K×CK                       | 16K×CK                 |

| 1 1 0 1  | (注1)            | 57ms + 1K×CK                 | 67ms + 1K×CK           |

|          |                 | 3.6ms + 1K×CK                | 4.2ms + 1K×CK          |

| 1 1 1 0  | (注1)            | 1K×CK                        | 1K×CK                  |

|          |                 | 16K×CK                       | 16K×CK                 |

| 1 1 1 1  |                 | 1K×CK                        | 1K×CK                  |

注1: リセット遅延時間内のクロック数制限のため、セラミック振動子の使用が推奨されます。

## 電源ONリセット (ATtiny12)

電源ONリセット(POR)パルスは内蔵検出回路により生成されます。この検出電圧は公称1.4Vです。PORはVCCが検出電圧以下で必ず有効にされます。このPOR回路は供給電圧低下の検出だけでなく開始時のリセット起動にも使われます。

電源ONリセット回路は電源投入時のデバイスリセットを保証します。電源ONリセット閾値電圧(VPOT)への到達は、VCC上昇後、デバイスがリセットを保持する遅延を決める遅延タイム(カウンタ)を起動します。遅延タイムの計時完了時間はCKSELヒューズを通して定義できます。遅延時間の各選択は表9で示されます。VCCが検出電圧以下に低下するとき、リセット信号は遅延なしで再び活性化(有効に)されます。

内蔵起動遅延時間で充分な場合、RESETは直接または外部プルアップ抵抗を介してVCCに接続できます。VCC供給後も、RESETピンをLowレベルに保持することで、起動遅延時間は延長できます。このタイミング例については図19を参照してください。

図18. 内蔵電源ONリセット (RESETはVCCに接続)

図19. 外部RESET信号による延長電源ONリセット

## 外部リセット

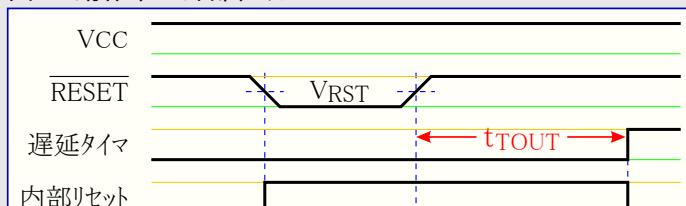

外部リセットはRESETピン上のLowレベルによって生成されます。例えクロックが動いていなくても、50nsより長いリセットパルスはリセットを生成します。短すぎるパルスはリセットが保証されません。供給された信号の上昇がリセット閾値電圧(VRST)に達すると、遅延タイムは遅延時間(t<sub>TOUT</sub>)経過後にMCUを起動します。

図20. 動作中の外部リセット

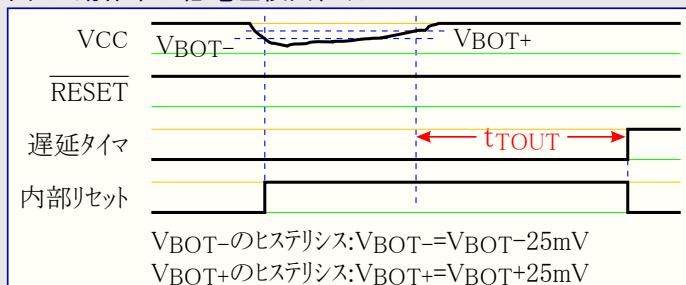

## 低電圧(ブラウンアウト)検出リセット (ATtiny12)

ATtiny12には動作中のVCC電圧を監視する内蔵低電圧検出(BOD)回路があります。BOD回路はBODENヒューズによって許可/禁止ができます。BODENが許可(BODEN=プログラム(0))され、VCCが検出電圧以下の値に低下すると、低電圧検出リセットは直ちに有効とされます。VCCが検出電圧以上に上昇すると、遅延後に無効とされます。この遅延はPOR信号の遅延(表9参照)と同じ方法で使用者によって定義されます。BOD検出電圧はBODLEVELヒューズにより、1.8V(非プログラム(1))、または2.7V(プログラム(0))が選択できます。この検出電圧には、スパイク無効の低電圧検出を保証するために50mVのヒステリシスがあります。

このBOD回路は電圧が2.7Vで7μs、1.8Vで24μs(代表値)より長く検出電圧以下に留まった場合だけ、VCCの低下を検出します。

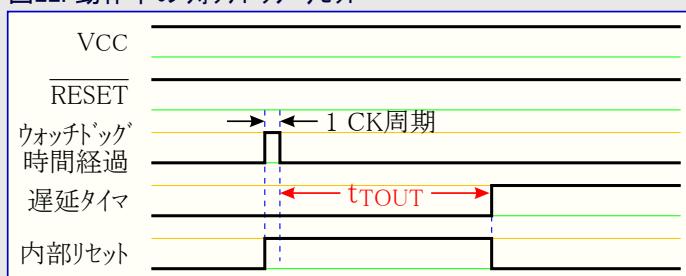

## ウォッチドッグリセット

ウォッチドッグ時間経過で1CK周期幅の短いリセットパルスを生成します。このパルスの下降端で遅延タイムは遅延時間(t<sub>TOUT</sub>)の計時を始めます。ウォッチドッグ操作の詳細については24頁を参照してください。

図21. 動作中の低電圧検出リセット

図22. 動作中のウォッチドッグリセット

## ■ MCU状態レジスタ (MCU Status Register) MCUSR (ATtiny10/11)

MCU状態レジスタはどのリセット元でMCUリセットが起こされたかの情報を提供します。

| ビット        | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0    |       |

|------------|---|---|---|---|---|---|-------|------|-------|

| \$34       | — | — | — | — | — | — | EXTRF | PORF | MCUSR |

| Read/Write | R | R | R | R | R | R | R/W   | R/W  |       |

| 初期値        | 0 | 0 | 0 | 0 | 0 | 0 | 内容参照  | 内容参照 |       |

### ■ ビット7~2 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みられます。

### ■ ビット1 – EXTRF : 外部リセット フラグ (External Reset Flag)

電源ONリセット後、このビットは不定です。このビットは外部リセットによって設定(1)されます。ウォッチドッグリセットは、このビットを無変化、そのままにします。

### ■ ビット0 – PORF : 電源ONリセット フラグ (Power-on Reset Flag)

このビットは電源ONリセットによって設定(1)されます。外部リセットやウォッチドッグリセットは、このビットを無変化、そのままにします。

要約のため、表11.は3つのリセット動作後の、これら2ビットの値を示します。

リセット条件の確認に、これらのビットを使うため、プログラム内で出来るだけ早くEXTRFとPORF両方を解除(0)すべきです。EXTRFとPORFの値の検査は、このビットが解除(0)される前に行います。外部またはウォッチドッグリセットが起こる前に、これらのビットが解除(0)される場合、リセット元は次の真理値表(表12.)を使うことで見つけられます。

表11. リセット発生元によるフラグの変化

| リセット発生元     | EXTRF | PORF |

|-------------|-------|------|

| 電源ON リセット   | 不定    | 1    |

| 外部リセット      | 1     | 不変   |

| ウォッチドッグリセット | 不変    | 不変   |

表12. フラグによるリセット発生元判定

| EXTRF | PORF | リセット発生元     |

|-------|------|-------------|

| 0     | 0    | ウォッチドッグリセット |

| 0     | 1    | 電源ON リセット   |

| 1     | 0    | 外部リセット      |

| 1     | 1    | 電源ON リセット   |

## ■ MCU状態レジスタ (MCU Status Register) MCUSR (ATtiny12)

MCU状態レジスタはどのリセット元でMCUリセットが起こされたかの情報を提供します。

| ビット        | 7 | 6 | 5 | 4 | 3    | 2    | 1     | 0    |       |

|------------|---|---|---|---|------|------|-------|------|-------|

| \$34       | — | — | — | — | WDRF | BORF | EXTRF | PORF | MCUSR |

| Read/Write | R | R | R | R | R/W  | R/W  | R/W   | R/W  |       |

| 初期値        | 0 | 0 | 0 | 0 | 内容参照 | 内容参照 | 内容参照  | 内容参照 |       |

### ■ ビット7~4 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みられます。

### ■ ビット3 – WDRF : ウォッチドッグリセット フラグ (Watchdog Reset Flag)

このビットはウォッチドッグリセットが起こると設定(1)されます。このビットは電源ONリセットか、このフラグへの論理0書き込みによって解除(0)されます。

### ■ ビット2 – BORF : 低電圧検出(BOD)リセット フラグ (Brown-out Reset Flag)

このビットは低電圧検出(BOD)リセットが起こると設定(1)されます。このビットは電源ONリセットか、このフラグへの論理0書き込みによって解除(0)されます。

### ■ ビット1 – EXTRF : 外部リセット フラグ (External Reset Flag)

このビットは外部リセットが起こると設定(1)されます。このビットは電源ONリセットか、このフラグへの論理0書き込みによって解除(0)されます。

### ■ ビット0 – PORF : 電源ONリセット フラグ (Power-on Reset Flag)

このビットは電源ONリセットによって設定(1)されます。このビットは、このフラグへの論理0書き込みによって解除(0)されます。

リセット条件の確認に、これらのビットを使うため、プログラム内で出来るだけ早くMCUSRを読み、その後に解除(0)すべきです。他のリセットが起こる前に、このレジスタ(MCUSR)が解除(0)される場合、そのリセット元はこれらのリセットフラグを調べることによって得られます。

## 内部基準電圧 (ATtiny12)

ATtiny12の特徴として公称1.22Vの内部基準電圧があります。この内部基準電圧は低電圧検出(ブラウンアウト検出)に使われ、アナログ比較器の入力にも使えます。

### 基準電圧許可信号と起動時間

この基準電圧には使用方法に影響を及ぼす起動時間が存在します。最大起動時間は10μsです。電力削減のため、この基準電圧は常にONではありません。この基準電圧は次の状況中ONです。

- ・低電圧検出リセット許可(BODENヒューズ=プログラム(0))時

- ・アナログ比較器基準電圧接続(アナログ比較器制御/状態レジスタ(ACSR)の基準電圧入力選択(AINBG)=1)時

従って、低電圧検出(BOD)が許可されていないと、AINBGの設定(=1)後、常にアナログ比較器出力が使われる前に、基準電圧を起動させなければなりません(安定時間が必要)。内部基準電圧は概ね10μAを消費し、[パワーダウン動作](#)での電力消費削減のため、この動作へ移行するとき、この基準電圧をOFFに切り替えられます。

### 割り込みの扱い

ATtiny10/11/12には一般割り込み許可レジスタ(GIMSK)とタイマ/カウンタ割り込み許可レジスタ(TIMSK)の2つの8ビット割り込み許可レジスタがあります。

割り込みが起こると、[ステータスレジスタ\(SREG\)の全割り込み許可\(I\)ビット](#)が解除(0)され、全ての割り込みが禁止されます。ソフトウェアは多重割り込みを許可するために、全割り込み許可(I)ビットを設定(1)できます。この全割り込み許可(I)ビットは、割り込みからの復帰(RETI)命令が実行されると設定(1)されます。

割り込み処理ルーチンを実行するために、プログラム カウンタが実際の割り込みベクタを指示するとき、割り込みを起こした対応する割り込み要求フラグを自動的に解除(0)します。いくつかの割り込み要求フラグは、そのフラグのビット位置に論理1を書くことによっても解除(0)できます。

対応する割り込み許可ビットが解除(0)されているときに割り込み条件が発生すると、対応する割り込み要求フラグが設定(1)され、その割り込みが許可または、ソフトウェアで解除(0)されるまで保持されます。

全割り込み許可(I)ビットが解除(0)されているときに1つまたは多くの割り込み条件が発生すると、対応する割り込み要求フラグが設定(1)され、全割り込み許可(I)ビットが設定(1)されるまで保持されます。許可後、それらは優先順に実行されます。

外部レベル割り込みには割り込み要求フラグがなく、割り込み条件が有効でありさえすれば割り込み要求が保持されるだけなことに注意してください。

[ステータスレジスタ\(SREG\)](#)は割り込み処理ルーチンへの移行時の保存と割り込み処理ルーチンからの復帰時の再設定が自動的に行われないことに注意してください。これはソフトウェアにより操作しなければなりません。

### 割り込み応答時間

全ての許可された割り込みについての割り込み実行応答時間は最小4クロックです。割り込み要求フラグが設定(1)されてしまった後の4クロック周期で、実際の割り込み処理ルーチン用の割り込みベクタアドレスが実行されます。この4クロック周期期間中、プログラム カウンタ(9ビット)がスタック上に保存(プッシュ)されます。通常、このベクタは割り込み処理ルーチンに対する無条件相対分岐(RJMP)命令で、この分岐に2クロック周期かかります。複数周期の命令実行中に割り込みが起こると、割り込みが扱われる前に、その命令が完了されます。ATtiny12では、MCUが休止形態のときに割り込みが起こると、割り込み応答時間が4クロック周期増やされます。

割り込み処理ルーチンからの復帰は4クロック周期要します。この4クロック周期中に、スタックからプログラム カウンタ(9ビット)が再設定(ポップ)され、[ステータスレジスタ\(SREG\)の全割り込み許可\(I\)ビット](#)が設定(1)されます。割り込みを抜けるときは常に主(元)プログラムへ復帰し、保留されている割り込みが扱われる前に、1つ以上の命令を実行します。

## ■ 一般割り込み許可レジスタ (General Interrupt Mask Register) GIMSK

| ビット        | 7 | 6    | 5    | 4 | 3 | 2 | 1 | 0 |       |

|------------|---|------|------|---|---|---|---|---|-------|

| \$3B       | — | INT0 | PCIE | — | — | — | — | — | GIMSK |

| Read/Write | R | R/W  | R/W  | R | R | R | R | R |       |

| 初期値        | 0 | 0    | 0    | 0 | 0 | 0 | 0 | 0 |       |

## ■ ビット7 – Res : 予約 (Reserved)

このビットは予約されており、常に0として読みます。

## ■ ビット6 – INT0 : 外部割り込み0許可 (External Interrupt Request 0 Enable)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットと外部割り込み0許可(INT0)ビットが、共に設定(1)でINT0ピンの割り込みが許可されます。MCU制御レジスタ(MCUCR)の割り込み条件制御0のビット1と0(ISC01,ISC00)が、外部割り込みINT0ピンの動作を上昇端、下降端、ピン変化(両端)、またはLowレベルの何れかを定義します。INT0ピンが出力に設定されていても、このピンの動きは割り込み要求を起こします。対応する外部割り込み0の割り込みはプログラムメモリアドレス\$001から実行されます。「[外部割り込み](#)」もご覧ください。

## ■ ビット5 – PCIE : ピン変化割り込み許可 (Pin Change Interrupt Enable)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットとピン変化割り込み許可(PCIE)ビットが、共に設定(1)でピン変化割り込みが許可されます。入力または入出力ピンのどちらかの何れかの変化が割り込みを起こします。対応するピン変化割り込み要求の割り込みはプログラムメモリアドレス\$002から実行されます。「[ピン変化割り込み](#)」もご覧ください。

## ■ ビット4~0 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

## ■ 一般割り込み要求フラグ レジスタ (General Interrupt Flag Register) GIFR

| ビット        | 7 | 6     | 5    | 4 | 3 | 2 | 1 | 0 |      |

|------------|---|-------|------|---|---|---|---|---|------|

| \$3A       | — | INTF0 | PCIF | — | — | — | — | — | GIFR |

| Read/Write | R | R/W   | R/W  | R | R | R | R | R |      |

| 初期値        | 0 | 0     | 0    | 0 | 0 | 0 | 0 | 0 |      |

## ■ ビット7 – Res : 予約 (Reserved)

このビットは予約されており、常に0として読みます。

## ■ ビット6 – INTF0 : 外部割り込み0要求フラグ (External Interrupt Flag0)

INT0ピン上のエッジが割り込み要求を起こす時に応答する割り込み要求フラグ(INTF0)が設定(1)になります。この時にステータスレジスタ(SREG)の全割り込み許可(I)ビットと応答する一般割り込み許可レジスタ(GIMSK)の外部割り込み0許可(INT0)ビットが共に設定(1)されていれば、MCUは割り込みベクタへ飛びます。このフラグは割り込み処理ルーチンが実行されると、解除(0)されます。このフラグは論理1を書くことによっても解除(0)できます。INT0がレベル割り込みとして設定されるとき、このフラグは常に解除(0)されます。

## ■ ビット5 – PCIF : ピン変化割り込み要求フラグ (Pin Change Interrupt Flag)

入力または入出力ピンのどちらかの出来事が割り込み要求を起こす時にピン変化割り込み要求(PCIF)フラグが設定(1)になります。この時にステータスレジスタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レジスタ(GIMSK)のピン変化割り込み許可(PCIE)ビットが共に設定(1)されていれば、アドレス\$002の割り込みベクタへ飛びます。このフラグは割り込み処理ルーチンが実行されると、解除(0)されます。このフラグは論理1を書くことによっても解除(0)できます。

## ■ ビット4~0 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

## ■ タイマ/カウンタ割り込み許可レジスタ (Timer/Counter Interrupt Mask Register) TIMSK

| ビット        | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0 |       |

|------------|---|---|---|---|---|---|-------|---|-------|

| \$39       | — | — | — | — | — | — | TOIE0 | — | TIMSK |

| Read/Write | R | R | R | R | R | R | R/W   | R |       |

| 初期値        | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0 |       |

### ■ ビット7~2 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

### ■ ビット1 – TOIE0 : タイマ/カウンタ0溢れ割り込み許可 (Timer/Counter0 Interrupt Enable)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットとタイマ/カウンタ0溢れ割り込み許可(TOIE0)ビットが共に設定(1)で、タイマ/カウンタ0溢れ割り込みが許可されます。タイマ/カウンタ0溢れが起こる、換言すると、[タイマ/カウンタ割り込み要求フラグレジスタ\(TIFR\)](#)のタイマ/カウンタ0溢れ割り込み要求フラグ(TOV0)が設定(1)されると、対応する割り込み(ベクタ \$003)が実行されます。

### ■ ビット0 – Res : 予約 (Reserved)

このビットは予約されており、常に0として読みます。

## ■ タイマ/カウンタ割り込み要求フラグレジスタ (Timer/Counter Interrupt Flag Register) TIFR

| ビット        | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0 |      |

|------------|---|---|---|---|---|---|------|---|------|

| \$38       | — | — | — | — | — | — | TOV0 | — | TIFR |

| Read/Write | R | R | R | R | R | R | R/W  | R |      |

| 初期値        | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 |      |

### ■ ビット7~2 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

### ■ ビット1 – TOV0 : タイマ/カウンタ0溢れ割り込み要求フラグ (Timer/Counter0 Overflow Interrupt Flag)

タイマ/カウンタ0溢れが起こると、このTOV0ビットが設定(1)されます。対応する割り込みベクタを実行すると、TOV0は自動的に解除(0)されます。代わりに、このフラグへ論理1を書くことによってもTOV0は解除(0)されます。[ステータスレジスタ\(SREG\)](#)の全割り込み許可(I)ビットとタイマ/カウンタ割り込み許可レジスタ(TIMSK)のタイマ/カウンタ0溢れ割り込み許可(TOIE0)ビットとTOV0が設定(1)されると、タイマ/カウンタ0溢れ割り込みが実行されます。

### ■ ビット0 – Res : 予約 (Reserved)

このビットは予約されており、常に0として読みます。

## 外部割り込み

外部割り込みはINT0ピンにより起動されます。許可されていれば、INT0ピンが出力として設定されていても、割り込みが起動することに注目してください。この特徴はソフトウェア割り込みを生成する方法を提供します。外部割り込みは上昇端、下降端、ピン変化(両端)、またはLowレベルで起動できます。これは[MCU制御レジスタ\(MCUCR\)](#)についての詳細で説明されるように設定します。外部割り込みが許可され、レベル起動として設定されるとき、ピンがLowに保持されている限り、この割り込みは継続的に発生します。

外部割り込みは、MCU制御レジスタ(MCUCR)についての詳細で説明されるように設定します。

## ピン変化割り込み

ピン変化割り込みは、入力または入出力ピンのどちらかの何れかの変化により起動されます。PB2~0ピンの変化は常に割り込みを起こします。PB5~3ピンの変化は、[4頁の「ピン概要」](#)項で記載されるように、そのピンが入力または入出力に設定される場合に割り込みを起こします。許可されていれば、変化するピンが例え出力として設定されていても、起動することに注目してください。この特徴はソフトウェア割り込みを生成する方法を提供します。ピンの動きが他の割り込み、例えは外部割り込みを起動する場合でも、ピン変化割り込みが起動することにも注目してください。これは1つの外部要因が複数の割り込みを起こせることを意味します。

ピンの値はエッジ検出に先立って採取されています。ピン変化割り込みが許可されていれば、1CPUクロック周期よりも長く留まるパルスは割り込みを発生します。短すぎるパルスは割り込みの発生が保証されません。

## ■ MCU制御レジスタ (MCU Control Register) MCUCR

このMCU制御レジスタは、一般的なMCU機能の制御ビットで構成されます。

| ビット        | 7 | 6     | 5   | 4   | 3 | 2 | 1     | 0     |       |

|------------|---|-------|-----|-----|---|---|-------|-------|-------|

| \$35       | – | (PUD) | SE  | SM  | – | – | ISC01 | ISC00 | MCUCR |

| Read/Write | R | R(W)  | R/W | R/W | R | R | R/W   | R/W   |       |

| 初期値        | 0 | 0     | 0   | 0   | 0 | 0 | 0     | 0     |       |

注: プルアップ禁止(PUD)ビットはATtiny12だけで利用可能です。

### ■ ビット7,6 (ATtiny10/11)、ビット7 (ATtiny12) – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

### ■ ビット6 (ATtiny12) – PUD : プルアップ禁止 (Pull-up Disable)

このビットの設定(1)は、ポートBの全プルアップを禁止します。このビットが解除(0)されると、28頁の「[入出力ポートB](#)」項で記述されるようにプルアップは個別に許可できます。

### ■ ビット5 – SE : 休止許可 (Sleep Enable)

SLEEP命令が実行されるときにMCUを休止形態へ移行させるには、休止許可(SE)ビットが設定(1)されなければなりません。MCUの目的的休止形態移行を防ぐため、SLEEP命令実行直前に休止許可(SE)ビットを設定(1)することが推奨されます。

### ■ ビット4 – SM : 休止種別 (Sleep Mode)

このビットは利用可能な2つの休止形態種別を選択します。SMが解除(0)されると休止形態としてアイドル動作が選択されます。SMが設定(1)されると休止形態としてパワーダウン動作が選択されます。詳細については、次の「[休止形態](#)」節を参照してください。

### ■ ビット3,2 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

### ■ ビット1,0 – ISC01,0 : 外部割り込み0条件制御 (Interrupt Sense Control 0 bit1 and 0)

外部割り込み0はステータスレジスタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レジスタ(GIMSK)の外部割り込み0許可(INT0)ビットが、共に設定(1)されている場合の外部割り込み0(INT0)ピンによって起動されます。次表は外部割り込みを発生するためのISCビット設定法を示します。

INT0ピンの値はエッジ検出以前から採取比較されています。エッジ割り込みが選択されると、1CPUクロック周期より長く留まるパルスは割り込みを発生します。短すぎるパルスは割り込みの発生が保証されません。Lowレベル割り込みが選択されると、割り込みを発生するためには、現在実行中の命令の完了までLowレベルが保持されなければなりません。許可されていれば、レベル起動割り込みはピンがLowに保持されている限り、割り込み要求を発生し続けます。

表13. 外部割り込み0(INT0)割り込み条件

| ISC01 | ISC00 | 割り込み発生条件          |

|-------|-------|-------------------|

| 0     | 0     | INT0ピンがLowレベルで発生。 |

|       | 1     | INT0ピンのレベル変化(両端)。 |

| 1     | 0     | INT0ピンの下降端で発生。    |

|       | 1     | INT0ピンの上昇端で発生。    |

## 休止形態

休止形態へ移行するには、MCU制御レジスタ(MCUCR)の**休止許可(SE)**ビットが設定(1)され、**SLEEP**命令が実行されなければなりません。MCUCRの**休止種別(SM)**ビットが選択する休止形態(アイドル動作またはパワーダウン動作)は**SLEEP**命令により有効にされます。MCUが休止形態中に許可されている割り込みが発生すると、MCUが起動復帰し、

**ATtiny10/11**では、その割り込み処理ルーチンを実行し、そして**SLEEP**命令の次から実行を再開します。**ピン変化**でのパワーダウン動作からの復帰では、**ピン変化割り込み要求フラグ(PCIF)**が更新される前に2命令周期が実行されます。これらの間、プロセッサは命令を実行しますが、割り込み状態は読みず、割り込み処理ルーチンも未だ開始されていません。

**ATtiny12**では、MCUが4周期停止され、その後に割り込み処理ルーチンを実行し、そして**SLEEP**命令の次から実行を再開します。

レジスタファイルとI/Oレジスタの内容は無変化です。休止形態中にリセットが起こると、MCUは起動復帰し、リセットベクタから実行します。

### アイドル動作

休止種別(SM)ビットが解除(0)されていると、**SLEEP**命令でMCUがアイドル動作へ移行し、CPUは停止しますが、タイマ/カウンタ、ウォッチドッグ、割り込み機構は継続して動作します。これは、タイマ溢れのような内部割り込みや**ウォッチドッグ**のリセットだけでなく、外部で起動される割り込みからもMCUの起動復帰を可能にします。アナログ比較器割り込みからの起動復帰が必要とされない場合、**アナログ比較器制御/状態レジスタ(ACSR)**の**アナログ比較器禁止(ACD)**ビットを設定(1)することにより、アナログ比較器を電源断にできます。これはアイドル動作での消費電力削減になります。**ATtiny10/11**では、アイドル動作から起動復帰すると、CPUは直ちにプログラムの実行を始めます。

### パワーダウン動作

休止種別(SM)ビットが設定(1)されていると、**SLEEP**命令でMCUがパワーダウン動作へ移行します。この動作では、外部発振器が停止され、一方、外部割り込みと(許可されていれば)ウォッチドッグは動作を継続します。外部リセット、(許可されていれば)ウォッチドッグリセット、(INT0)の外部レベル割り込み、またはピン変化割り込みだけがMCUを起動復帰できます。

**ATtiny10/11**ではパワーダウン動作からの起動復帰にレベルで起動された割り込みまたはピン変化割り込みが使われる場合、変更されたレベルが**リセット遅延時間(tTOUT)**より長い時間保持されなければならないことに注意してください。さもなければMCUは起動復帰に失敗します。

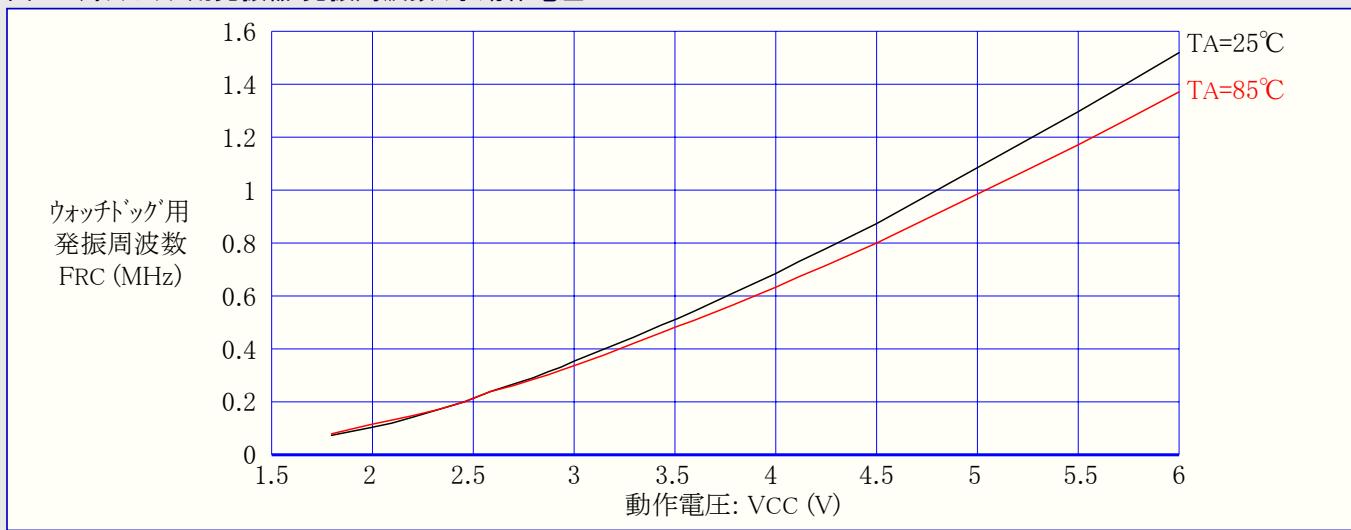

**ATtiny12**ではパワーダウン動作からの起動復帰に、レベルで起動された割り込みまたはピン変化割り込みが使われる場合、MCUを起動するために、変更されたレベルは一定時間保持されなければならないことに注意してください。これはMCUの雑音不安定性を減らします。この起動時間は**リセット遅延時間のCK計数部(表9.参照)**と同じです。入力が2回のウォッチドッグ発振器周期で必要とされるレベルだとMCUはパワーダウン動作から起動復帰します。起動時間が2つのウォッチドッグ発振器周期より短い場合、入力が起動時間の幅分、必要とされるレベルであれば、MCUは起動復帰します。起動時間が終了される前に起動復帰条件が消滅すると、MCUは対応する割り込みの実行を除いて、パワーダウン動作から起動復帰します。ウォッチドッグ発振器の周期は公称2.7μs(3V,25°C)です。**47頁の「ATtiny12代表特性」**章内で示されるように、ウォッチドッグ発振器の周波数は電圧に依存します。

**ATtiny12**ではパワーダウン動作から復帰するとき、起動復帰条件発生から起動復帰の効果が現れるまで遅延を伴います。これは停止されてしまっている後に、再開のためのクロックが許可され、安定状態になるためです。この起動時間は**リセット遅延時間**を定義する**CKSELヒューズ**により同じく定義されます。

(訳注) 原書では本項目全体がATtiny10/11とATtiny12で個別に記述されていますが、各項目内個別記載に変更しました。

## 校正付き内蔵RC発振器 (ATtiny12)

ATtiny12では校正された内蔵RC発振器が5V, 25°Cで公称1.2MHz固定のクロックを提供します。このクロックはシステムクロックとして使えます。このクロックをシステムクロックとする選択方法の情報については5頁の「クロック元」章をご覧ください。この発振器は発振校正レジスタ(OSCCAL)への校正値書き込みによって校正できます。この発振器がシステムクロックとして使われるときでも、ウォッチドッグタイムとリセット遅延には未だウォッチドッグ用発振器が使われます。予めプログラムされた校正値の使用法の詳細については31頁の「校正バイト」をご覧ください。5V, 25°Cで、予めプログラムされた校正バイトは公称周波数の±1%内の周波数を与えます。

### ■ 発振校正レジスタ (Oscillator Calibration Register) OSCCAL

| ビット        | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    | OSCCAL |

|------------|------|------|------|------|------|------|------|------|--------|

| \$31       | CAL7 | CAL6 | CAL5 | CAL4 | CAL3 | CAL2 | CAL1 | CAL0 |        |

| Read/Write | R/W  |        |

| 初期値        | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |        |

#### ■ ビット7~0 – CAL7~0 : 発振校正值 (Oscillator Calibration Value)

発振周波数の偏差による処理を省くため、このアドレスへの校正バイト書き込みが内蔵RC発振器を調整します。OSCCALが0のときに利用可能な最低周波数が選択されます。このレジスタへの0以外の値書き込みが内蔵RC発振器周波数を増加します。このレジスタへの\$FF書き込みが利用可能最高周波数を与えます。校正された発振器はEEPROMのアクセス時間に使われます。EEPROMが書かれる場合、公称周波数より10%以上高く校正してはいけません。さもないと、EEPROM書き込み操作は失敗するかもしれません。この発振器は1.2MHzへの校正を意図したもので、このため他の値への調整が保証されないことに注意してください。

表14. 内蔵RC発振器周波数範囲

| OSCCAL値 | 最小     | 最大     |

|---------|--------|--------|

| \$00    | 0.6MHz | 1.2MHz |

| \$7F    | 0.8MHz | 1.7MHz |

| \$FF    | 1.2MHz | 2.5MHz |

(訳注) 内蔵RC発振周波数が改訂Cデータシートで1.0MHzから1.2MHzに変更されたために表も変更されました。

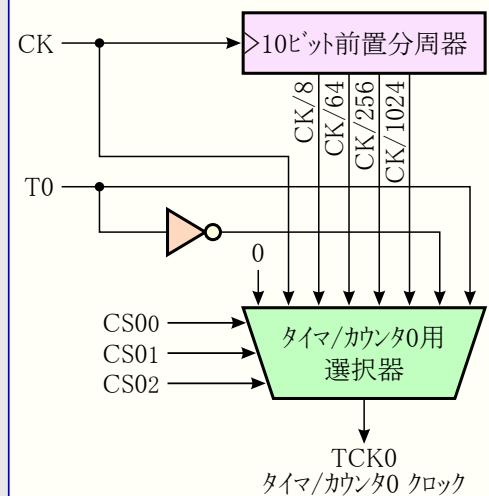

## タイマ/カウンタ

ATtiny10/11/12には8ビットの汎用タイマ/カウンタが1つあります。このタイマ/カウンタ0にはシステムクロックを分周する10ビット前置分周器があります。このタイマ/カウンタ0は内部クロックを基準とするタイマや、外部ピンに接続された起因信号によるカウンタなどの使用ができます。

### タイマ/カウンタ前置分周器部

図23.はタイマ/カウンタの前置分周器を示します。

前置分周器で分周された4つの異なる選択は、CKを発振器クロックとする、CK/8, CK/64, CK/256, CK/1024です。CK、外部クロック信号、または停止もクロック元として選択できます。

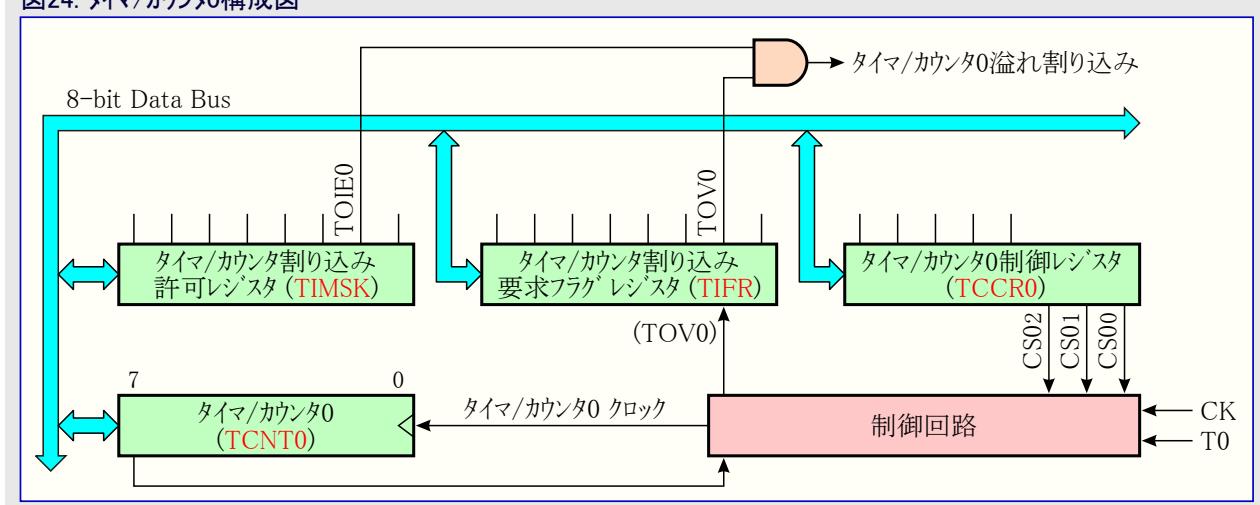

図24.はタイマ/カウンタ0の構成図を示します。

8ビットのタイマ/カウンタ0はCK、分周されたCK、または外部ピンからクロック元を選択できます。加えてタイマ/カウンタ0制御レジスタ(TCCR0)の詳細で説明されるように停止もできます。溢れ状態フラグ(TOVO)はタイマ/カウンタ割り込み要求フラグレジスタ(TIFR)にあります。制御ビットはタイマ/カウンタ0制御レジスタ(TCCR0)にあります。タイマ/カウンタ0についての割り込みの許可/禁止設定はタイマ/カウンタ割り込み許可レジスタ(TIMSK)内にあります。

タイマ/カウンタ0が外部的にクロック駆動されるとき、外部信号はCPUの発振器周波数で同期化されます。外部クロックの正しい採取を保証するには、外部クロックの2つの変移間の最小時間が少なくとも1つの内部CPUクロック周期以上でなければなりません。この外部クロック信号は内部CPUクロックの上昇端で採取されます。

8ビットのタイマ/カウンタ0は低前置分周(使用)機会での高分解能及び高精度の使用が特徴です。同様に高前置分周(使用)機会は低速な目的やまれに動く正確なタイミングの目的についてタイマ/カウンタ0を有効にします。

図23. タイマ/カウンタ前置分周器構成

図24. タイマ/カウンタ0構成図

## ■ タイマ/カウンタ0制御レジスタ (Timer/Counter0 Control Register) TCCR0

| ビット        | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |       |

|------------|---|---|---|---|---|------|------|------|-------|

| \$33       | — | — | — | — | — | CS02 | CS01 | CS00 | TCCR0 |

| Read/Write | R | R | R | R | R | R/W  | R/W  | R/W  |       |

| 初期値        | 0 | 0 | 0 | 0 | 0 | 0    | 0    | 0    |       |

## ■ ビット7~3 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

## ■ ビット2~0 – CS02~0 : クロック選択0 (Clock Select0, bit 2,1 and 0)

クロック選択0ビット2~0はタイマ/カウンタ0に供給するクロック元を定義します。

表15. タイマ/カウンタ0入力クロック選択

| CS02 | CS01 | CS00 | 意味                             |

|------|------|------|--------------------------------|

| 0    | 0    | 0    | 停止 (タイマ/カウンタ0は動作停止)            |

| 0    | 0    | 1    | CK                             |

| 0    | 1    | 0    | CK/8 (CPUクロックを8分周したクロック)       |

| 0    | 1    | 1    | CK/64 (CPUクロックを64分周したクロック)     |

| 1    | 0    | 0    | CK/256 (CPUクロックを256分周したクロック)   |

| 1    | 0    | 1    | CK/1024 (CPUクロックを1024分周したクロック) |

| 1    | 1    | 0    | 外部T0(PB2)ピンの下降端                |

| 1    | 1    | 1    | 外部T0(PB2)ピンの上昇端                |

停止状態はタイマ/カウンタの許可/禁止機能を提供します。CKの分周出力動作では、発振器クロック(CK)から直接的に分周されます。タイマ/カウンタ0に外部ピン動作が使われると、例えT0(PB2)が出力として設定されていても、このピン上の変移がタイマ/カウンタを計数します。この特徴が計数動作のソフトウェア制御を提供します。

## ■ タイマ/カウンタ0 (Timer/Counter0) TCNT0

| ビット        | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |       |

|------------|-------|-----|-----|-----|-----|-----|-----|-------|-------|

| \$32       | (MSB) |     |     |     |     |     |     | (LSB) | TCNT0 |

| Read/Write | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |       |

| 初期値        | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |       |

このタイマ/カウンタ0は、読み書きできる上昇カウンタとして実装されます。タイマ/カウンタ0が書かれ、クロック元が存在すると、タイマ/カウンタ0は書き込み動作の次に来るタイマ/カウンタクロック周期で計数を開始/継続します。

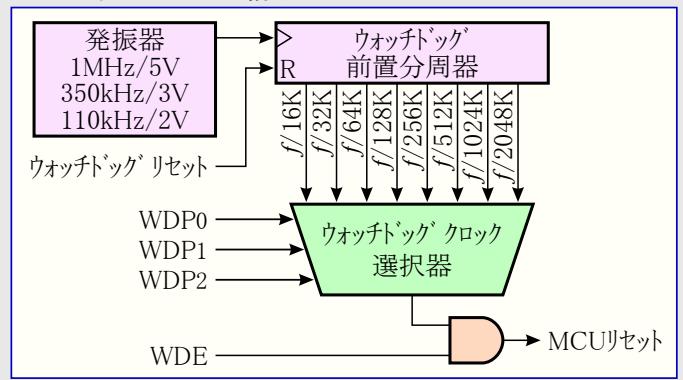

## ウォッチドッグ タイマ

このウォッチドッグ タイマは独立の内蔵発振器から駆動されます。ウォッチドッグ タイマの前置分周器を制御することにより、表16.で示されるようにウォッチドッグ リセット周期は調整できます。ウォッチドッグ リセット(WDR)命令はウォッチドッグ タイマをリセットします。8種の異なるクロック周期はリセット周期を決めるために選択できます。WDR命令なしで、このリセット周期が経過すると、ATtiny10/11/12はリセットし、リセット ベクタから実行します。ウォッチドッグ リセットの詳細タイミングについては14頁を参照してください。

予期せぬウォッチドッグ 禁止を防止するため、ウォッチドッグが禁止されるとき、特別なOFF切り替え手順に従わなければなりません。詳細についてはウォッチドッグ タイマ制御レジスタの記述を参照してください。

図25. ウォッチドッグ タイマ構成図

### ■ ウォッチドッグ タイマ制御レジスタ (Watchdog Timer Control Register) WDTCR

| ビット        | 7 | 6 | 5 | 4     | 3   | 2    | 1    | 0    |       |

|------------|---|---|---|-------|-----|------|------|------|-------|

| \$21       | — | — | — | WDTOE | WDE | WDP2 | WDP1 | WDP0 | WDTCR |

| Read/Write | R | R | R | R/W   | R/W | R/W  | R/W  | R/W  |       |

| 初期値        | 0 | 0 | 0 | 0     | 0   | 0    | 0    | 0    |       |

#### ■ ビット7~5 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

#### ■ ビット4 – WDTOE : ウォッチドッグ停止移行許可 (Watchdog Turn-off Enable)

ウォッチドッグ許可(WDE)ビットが解除(0)されるとき、このビットは設定(1)されなければなりません。さもなければ、ウォッチドッグは禁止されません。一度設定(1)すると、4クロック周期後、ハードウェアがこのビットを0に解除します。ウォッチドッグ禁止手順についてはWDEビットの記述を参照してください。

#### ■ ビット3 – WDE : ウォッチドッグ許可 (Watchdog Enable)

このWDEが設定(1)されるとウォッチドッグ タイマが許可され、解除(0)されるとウォッチドッグ タイマ機能が禁止されます。WDEはウォッチドッグ停止移行許可(WDTOE)ビットが設定(1)されているときだけ解除(0)できます。許可されているウォッチドッグ タイマを禁止するには次の手順に従わなければなりません。

1. 同じ操作内で、WDTOEとWDEに論理1を書きます。禁止操作開始前が1に設定されていても、論理1がWDEに書かれなければなりません。

2. 次の4クロック以内に、WDEへ論理0を書きます。これがウォッチドッグを禁止します。

#### ■ ビット2~0 – WDP2~0 : ウォッチドッグ タイマ前置分周選択 (Watchdog Timer Prescaler 2,1 and 0)

このWDP2~0は、ウォッチドッグ タイマが許可される時のウォッチドッグ タイマの前置分周を決めます。各前置分周値と対応する計時完了周期は表16.に示されます。

表16. ウォッチドッグ 前置分周選択

| WDP2 | WDP1 | WDP0 | WDT発振周期数 | 代表的な計時完了周期 |          |

|------|------|------|----------|------------|----------|

|      |      |      |          | VCC=3.0V   | VCC=5.0V |

| 0    | 0    | 0    | 16K      | 47ms       | 15ms     |

| 0    | 0    | 1    | 32K      | 94ms       | 30ms     |

| 0    | 1    | 0    | 64K      | 0.19s      | 60ms     |

| 0    | 1    | 1    | 128K     | 0.38s      | 0.12s    |

| 1    | 0    | 0    | 256K     | 0.75s      | 0.24s    |

| 1    | 0    | 1    | 512K     | 1.5s       | 0.49s    |

| 1    | 1    | 0    | 1024K    | 3.0s       | 0.97s    |

| 1    | 1    | 1    | 2048K    | 6.0s       | 1.9s     |

注: 39頁の「ATtiny10/11 代表特性」項で示されるように、ウォッチドッグ発振器の周波数は電圧に依存します。

ウォッチドッグ タイマが許可される前に、常にウォッチドッグ リセット(WDR)命令が実行されるべきです。これはウォッチドッグ タイマ前置分周器設定に一致するリセット周期を保証します。このリセット操作なしにウォッチドッグが許可されると、ウォッチドッグ タイマは0から計数を開始しないかもしれません。

予期せぬMCUリセットを避けるため、ウォッチドッグ タイマ前置分周選択の変更前にはウォッチドッグ タイマが禁止されるかリセットされるべきです。

## EEPROMアクセス (ATtiny12)

EEPROMをアクセスするレジスタはI/O空間でアクセスできます。

書き込み時間は校正されたRC発振器の周波数に依存し、3.1～6.8msの範囲です。詳細については表17をご覧ください。(書き込みは)自己タイミング機能ですが、使用者ソフトウェアは次バイトが書ける時を検知してください。EEPROMが新規データを受け入れる準備ができるときに起動するために、特別なEEPROM操作可割り込みが設定できます。EEPROM書き込み最低電圧は2.2Vです。

不測のEEPROM書き込みを防ぐため、2段構えの書き込み手順に従わなければなりません。この詳細については「EEPROM制御レジスタ(EECR)」の記述を参照してください。

EEPROMが書かれるとき、CPUは次の命令が実行される前に2クロック周期停止されます。EEPROMが読まれるとき、CPUは次の命令が実行される前に4クロック周期停止されます。

### ■ EEPROMアドレス レジスタ (EEPROM Address Register) EEAR

| ビット        | 7 | 6 | 5     | 4     | 3     | 2     | 1     | 0     |      |

|------------|---|---|-------|-------|-------|-------|-------|-------|------|

| \$1E       | — | — | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEAR |

| Read/Write | R | R | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |      |

| 初期値        | 0 | 0 | 不定    | 不定    | 不定    | 不定    | 不定    | 不定    |      |

### ■ ビット5～0 – EEAR5～0 : EEPROMアドレス (EEPROM Address)

EEPROMアドレス レジスタ(EEAR)は64バイトのEEPROM空間のEEPROMアドレスを指定します。EEPROMデータのバイトは0～63間で直線的に配置されています。リセット中、EEARレジスタは解除されません。その代わり、レジスタ内のデータが保持されます。

### ■ EEPROMデータ レジスタ (EEPROM Data Register) EEDR

| ビット        | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |      |

|------------|-------|-----|-----|-----|-----|-----|-----|-------|------|

| \$1D       | (MSB) |     |     |     |     |     |     | (LSB) | EEDR |

| Read/Write | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |      |

| 初期値        | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |      |

### ■ ビット7～0 – EEDR7～0 : EEPROMデータ (EEPROM Data)

EEPROM書き込み操作について、EEDRはEEPROMアドレス レジスタ(EEAR)で与えられるアドレスのEEPROMに書かれるデータです。EEPROM読み込み操作では、EEDRがEEARで与えられるアドレスのEEPROMから読み出されたデータです。

### ■ EEPROM制御 レジスタ (EEPROM Control Register) EECR

| ビット        | 7 | 6 | 5 | 4 | 3     | 2     | 1    | 0    |      |

|------------|---|---|---|---|-------|-------|------|------|------|

| \$1C       | — | — | — | — | EERIE | EEMWE | EEWE | EERE | EECR |

| Read/Write | R | R | R | R | R/W   | R/W   | R/W  | R/W  |      |

| 初期値        | 0 | 0 | 0 | 0 | 0     | 0     | 不定   | 0    |      |

### ■ ビット7～4 – Res : 予約 (Reserved)

これらのビットは予約されており、常に0として読みます。

### ■ ビット3 – EERIE : EEPROM操作可割り込み許可 (EEPROM Ready Interrupt Enable)

ステータス レジスタ(SREG)の全割り込み許可(I)ビットとこのEERIEが設定(1)されると、EEPROM操作可割り込みが許可されます。解除(0)されると、この割り込みは禁止されます。EEWEが解除(0)されていると、EEPROM操作可割り込みは継続する割り込みを発生します。

### ■ ビット2 – EEMWE : EEPROM主書き込み許可 (EEPROM Master Write Enable)

このEEMWEビットは、EEPROM書き込み許可(EEWE)ビットの1設定がEEPROM書き込みの原因となるかどうかを決定します。EEMWEが設定(1)されるとき、EEWEの1設定は選択されたアドレスのEEPROMにデータを書きます。EEMWEが0の場合、EEWEの1設定は無効です。EEMWEがソフトウェアによって設定(1)されてしまうと、4クロック周期後、自動的に解除(0)されます。EEPROM書き込み手順については次の「書き込み許可(EEWE)ビット」の説明を参照してください。

### ■ ビット1 – EEWE : EEPROM書き込み許可 (EEPROM Write Enable)

このEEPROM書き込み許可信号(EEWE)はEEPROMへの書き込みストローブです。アドレスとデータが適切に設定されると、EEPROMへこの値を書き込むために、このEEWEビットを設定(1)しなければなりません。論理1がEEWEに書かれるとき、EEPROM主書き込み許可(EEMWE)ビットは設定(1)されなければならず、そうしないと、EEPROM書き込みは行われません。EEPROMを書く時は次の手順に従うべきです(手順②と③の順番は重要ではありません)。

1. EEPROM書き込み許可(EEWE)ビットが0になるまで待機します。

2. 今回のEEPROMアドレスをEEPROMアドレスレジスタ(EEAR)に書きます。(任意、省略可)

3. 今回のEEPROMデータをEEPROMデータレジスタ(EEDR)に書きます。(任意、省略可)

4. EEPROM制御レジスタ(ECR)のEEPROM主書き込み許可(EEMWE)ビットに論理1を書きます。

5. EEMWE設定後4クロック周期内に、EEPROM書き込み許可(EEWE)ビットへ論理1を書きます。

**警告:** 手順4.と5.間の割り込みは、EEPROM主書き込み許可が時間超過となるため、書き込み周期失敗になります。EEPROMをアクセスする割り込み処理ルーチンが他のEEPROMアクセスで割り込み、EEARかEEDRが変更されると、割り込まれたEEPROMアクセスが失敗する原因になります。これらの問題を防ぐため、手順2.~5.の間中、ステータスレジスタ(SREG)の全割り込み許可(I)ビットは解除(0)されていることが推奨されます。

書き込み時間(表17.参照)が経過してしまうと、EEWEビットは自動的に解除(0)されます。次のバイトを書く前に、このビットをポーリングして0まで待機できます。EEWEが設定(1)されてしまうと、次の命令が実行される前に、CPUは2周期停止されます。

### ■ ビット0 – EERE : EEPROM読み込み許可 (EEPROM Read Enable)

このEEPROM読み込み許可信号(EERE)はEEPROMへの読み込みストローブです。EEARに適切なアドレスが設定されると、このEEREビットを設定(1)しなければなりません。EEREビットが自動的に解除(0)されると、求められたデータがEEDR内にあります。EEPROM読み込みアクセスは1命令で行われるので、EEREビットのポーリングは必要ありません。EEREが設定(1)されてしまうと、次の命令が実行される前にCPUは4周期停止されます。

読み込み操作を始める前にEEWEビットをポーリングすべきです。新規データまたはアドレスがEEPROM I/Oレジスタに書かれるときに書き込み動作が実行中の場合、書き込み動作は阻止され、結果が不定にされます。

EEPROM書き込みアクセスの時間に校正付き内蔵RC発振器が使われます。右の表はCPUからのEEPROMアクセスについて代表的な書き込み時間を持っています。

表17. 代表的なEEPROM書き込み時間

| 項目                | 校正付きRC発振器クロック数 | 最小    | 最大    |

|-------------------|----------------|-------|-------|

| EEPROM書き込み(CPUから) | 4096           | 3.1ms | 6.8ms |

(**誤注**) 内蔵RC発振器クロック数が2048から4096に変更されています。

よって、書き込み時間も変更となっています。

### EEPROMデータ化けの防止

電源電圧が低すぎる時のCPUやEEPROMの動作特性により、低VCCの期間中、EEPROMデータが化けてしまいます。これらはEEPROMを使った基板レベルの問題と同じで、同じ設計上の解決法が適用されるべきです。

EEPROMデータ化けが発生する低電源電圧は、2つの場合が想定できます。1つ目は、EEPROM書き込み動作に必要な最低電圧以下の場合で、2つ目は、CPUが命令を実行するのに必要な最低電圧以下の場合です。

次の推奨設計(内の1つで充分)により、EEPROMのデータ化けは容易に避けることができます。

- ・電源の供給電圧が不足する時間中、AVRのRESETを有効(Low)に保ちます。これは動作電圧が検出電圧と一致する場合、内蔵低電圧検出器(BOD)を許可することにより行えます。一致しない場合、外部低VCCリセット保護回路が適用できます。

- ・低VCCの時間中、AVRコアをパワーダウン休止動作に保ちます。これはCPUを命令の復号と実行を試みないように防ぎ、不測の書き込みからEEPROMレジスタを保護する効果があります。

- ・ソフトウェアからメモリ内容を変更できることが必要とされない場合、フラッシュメモリに定数を格納します。フラッシュメモリはCPUにより更新されることができないので、データ化けの問題はありません。

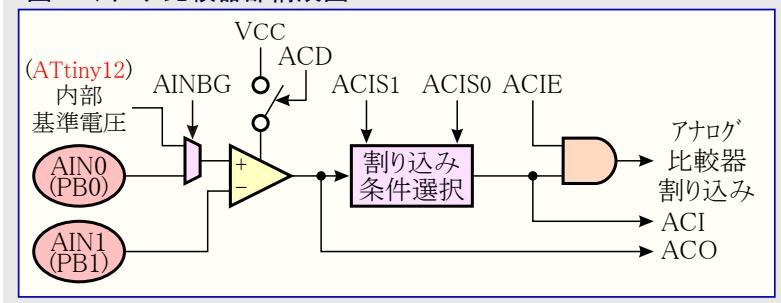

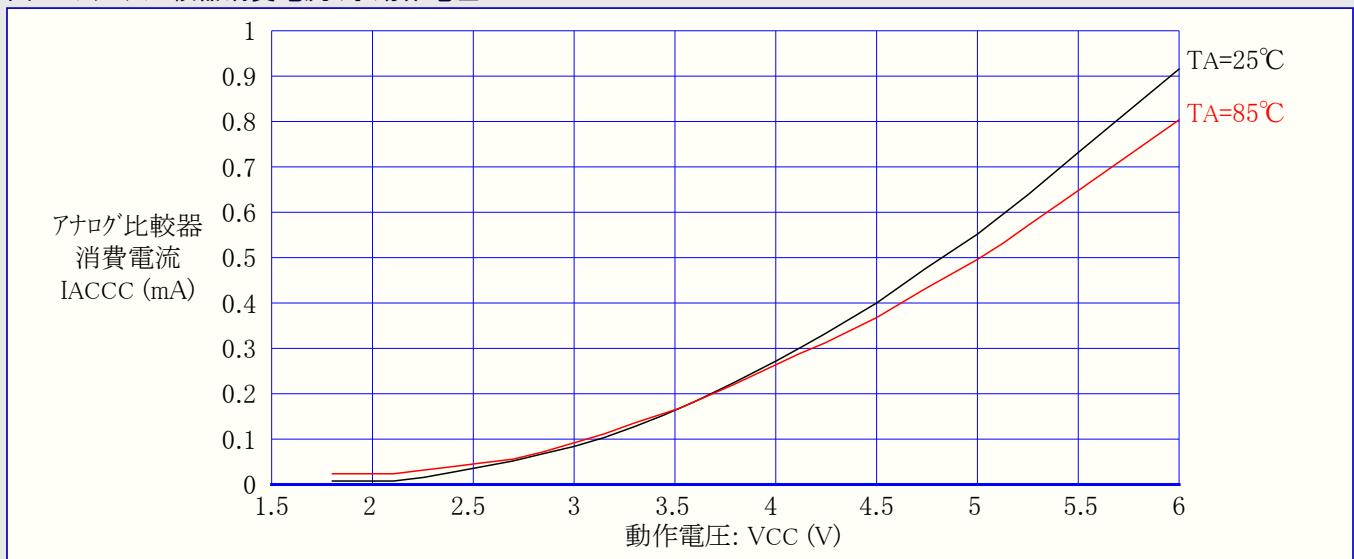

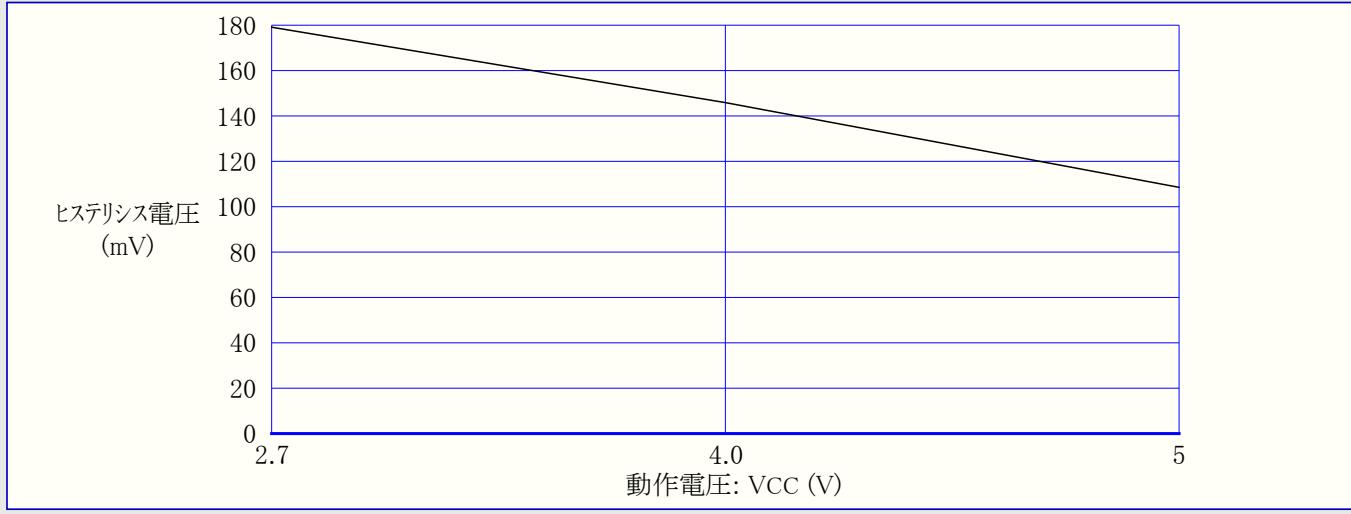

## アナログ比較器

アナログ比較器は非反転入力AIN0(PB0)と反転入力AIN1(PB1)の入力値を比較します。AIN0(PB0)非反転入力の電圧がAIN1(PB1)反転入力の電圧より高いと、アナログ比較器制御/状態レジスタ(ACSR)のアナログ比較器出力(ACO)ビットを設定(1)します。この比較器出力はアナログ比較器専用の独立した割り込みを起動できます。比較器出力の上昇端、下降端、またはその両方での割り込み起動が選べます。この比較とその周辺回路の構成図は図26で示されます。

図26. アナログ比較器部構成図

### ■ アナログ比較器 制御/状態レジスタ (Analog Comparator Control and Status Register) ACSR

| ビット        | 7   | 6       | 5   | 4   | 3    | 2 | 1     | 0     | ACSR |

|------------|-----|---------|-----|-----|------|---|-------|-------|------|

| \$08       | ACD | (AINBG) | ACO | ACI | ACIE | - | ACIS1 | ACIS0 |      |

| Read/Write | R/W | R(W)    | R   | R/W | R/W  | R | R/W   | R/W   |      |

| 初期値        | 0   | 0       | 不定  | 0   | 0    | 0 | 0     | 0     |      |

注: AINBGはATtiny12でだけ利用可能です。

#### ■ ビット7 – ACD : アナログ比較器禁止 (Analog Comparator Disable)

このビットが設定(1)されると、アナログ比較器への電力がOFFに切り替えられます。このビットはアナログ比較器をOFFにするため、何時でも設定(1)できます。ACDビットを変更するとき、ACSRのアナログ比較器割り込み許可(ACIE)ビットを解除(0)することにより、アナログ比較器割り込みが禁止されなければなりません。さもなければ、このビットが変更されるとき、割り込みが起き得ます。

#### ■ ビット6 – Res : 予約 (Reserved) (ATtiny10/11)

このビットは予約されており、常に0として読みます。

#### ■ ビット6 – AINBG : 内部基準電圧選択 (Analog Comparator Bandgap Select) (ATtiny12)

BODENヒューズがプログラム(0)で低電圧検出(BOD)リセットが許可され、本ビットが設定(1)されると、比較器非反転入力の標準入力(AIN0)を内部基準電圧 $1.22 \pm 0.05$ Vに置換します。このビットが解除(0)されると、標準入力AIN0(PB0)ピンが比較器非反転入力に印加されます。

#### ■ ビット5 – ACO : アナログ比較器出力 (Analog Comparator Output)

ACOは比較器出力へ直接、接続されています。

#### ■ ビット4 – ACI : アナログ比較器割り込み要求フラグ (Analog Comparator Interrupt Flag)

比較器出力の動きが、アナログ比較器割り込み条件(ACIS1, ACIS0)ビットで定義された割り込み動作を起こすとき、本ビットは設定(1)されます。アナログ比較器割り込み許可(ACIE)ビットが設定(1)され、ステータスレジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されていると、アナログ比較器割り込み処理ルーチンが実行されます。対応する割り込みベクタを実行するとき、ACIは自動的に解除(0)されます。代わりにこのフラグへ論理1を書くことによっても、ACIは解除(0)されます。

#### ■ ビット3 – ACIE : アナログ比較器割り込み許可 (Analog Comparator Interrupt Enable)

ACIEビットが設定(1)され、ステータスレジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されると、アナログ比較器割り込みが有効化されます。解除(0)されると、この割り込みは禁止されます。

#### ■ ビット2 – Res : 予約 (Reserved)

このビットは予約されており、常に0として読みます。

#### ■ ビット1,0 – ACIS1,0 : アナログ比較器割り込み条件 (Analog Comparator Interrupt Mode Select)

これらのビットはアナログ比較器割り込みを引き起こす出来事を決めます。各設定は表18に示されます。

表18. アナログ比較器割り込み条件選択

| ACIS1 | ACIS0 | 割り込み発生条件       |

|-------|-------|----------------|

| 0     | 0     | 比較器出力の変移 (トグル) |

| 0     | 1     | (予約)           |

| 1     | 0     | 比較器出力の下降端      |

| 1     | 1     | 比較器出力の上昇端      |

注: このACIS1, ACIS0ビットを変更するとき、ACSRのアナログ比較器割り込み許可(ACIE)ビットを解除(0)することにより、アナログ比較器割り込みが禁止されなければなりません。さもなければ、このビットが変更される時に割り込みが起き得ます。

警告: このレジスタのACI以外のビットに対するCBIまたはSBI命令の使用は、ACIが1として読まれる場合に1が書き戻されるため、このフラグを解除(0)してしまいます。

## 入出力ポートB

AVRの全てのポートは標準デジタルI/Oポートとして使われる時に真の読み-修正-書き(リードモーティフライ)動作を有します。これはCBIやSBI命令で、他の何れのピンの方向をも不測の変化なしにポートピンの1つの方向が変更できることを意味します。駆動(出力)値変更や、(入力として設定されている場合の)プルアップ抵抗の許可/禁止(有無)についても同じく適用されます。

ATtiny10/11のポートBは5ビットの双方向I/Oポートと1ビットの入力ポートです。ATtiny12のポートBは6ビットの双方向I/Oポートです。

ポートBについては3つのI/Oメモリアドレス位置が、各々、データ出力レジスタ(PORTB), \$18、データ方向レジスタ(DDRB), \$17、データ入力レジスタ(PINB), \$16に割り当てられます。ポートBデータ入力レジスタ(入力ピン)アドレスは読み込みのみ可能で、一方データ出力レジスタとデータ方向レジスタは読み書きが可能です。

ポートPB5～3には4頁の「ピン概要」項で記述される特別な機能があります。PB5は外部リセットとして設定されなければ、プルアップなしの入力です。ATtiny12のPB5は論理0(Low)も出力でき、オープンドレイン出力として動作します。PB4, PB3がクロック機能に使われない場合、それらは入出力ピンです。全てのポートピンには、個別に選択可能なプルアップ抵抗があります。

PB0～4のポートB出力緩衝部は20mAのシンク電流を流せますので、LED表示器を直接駆動できます。ATtiny12のPB5は12mAの吸い込み電流を流せます。PB0～4ピンが入力として使われ、外部的にLowへ引き込まれると、内蔵プルアップ抵抗が有効化されると、それらには吐き出し電流が流れます。

ポートBピンの交換機能は表19に示されます。

表19. ポートBピンの交換機能

| ポートピン | 交換機能                     | デバイス           |

|-------|--------------------------|----------------|

| PB0   | AIN0 (アナログ比較器非反転入力)      | ATtiny10/11/12 |

|       | MOSI (直列プログラミング用データ入力)   | ATtiny12       |

| PB1   | AIN1 (アナログ比較器反転入力)       | ATtiny10/11/12 |

|       | INT0 (外部割り込み0入力)         | ATtiny12       |

| PB2   | MISO (直列プログラミング用データ出力)   | ATtiny12       |

|       | T0 (タイマ/カウント0外部クロック入力)   | ATtiny10/11/12 |

| PB3   | SCK (直列プログラミング用直列クロック入力) | ATtiny12       |

|       | XTAL1 (発振器入力)            | ATtiny10/11/12 |

| PB4   | XTAL2 (発振器出力)            | ATtiny10/11/12 |

| PB5   | RESET (外部リセット入力)         | ATtiny10/11/12 |

PB2～0ピンが交換機能で使われるとき、ポートB方向レジスタ(DDRB)とポートB出力レジスタ(PORTB)は交換機能の説明に従って設定されなければなりません。PB5～3が交換機能を使われるとき、対応するDDRBとPORTBビットの値は無視されます。

### ■ ポートB出力レジスタ (Port B Data Register) PORTB

| ビット        | 7 | 6 | 5 | 4      | 3      | 2      | 1      | 0      | PORTB |

|------------|---|---|---|--------|--------|--------|--------|--------|-------|

| \$18       | — | — | — | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 | PORTB |

| Read/Write | R | R | R | R/W    | R/W    | R/W    | R/W    | R/W    |       |

| 初期値        | 0 | 0 | 0 | 0      | 0      | 0      | 0      | 0      |       |

### ■ ポートB方向レジスタ (Port B Data Direction Register) DDRB

| ビット        | 7 | 6 | 5      | 4    | 3    | 2    | 1    | 0    | DDRB |

|------------|---|---|--------|------|------|------|------|------|------|

| \$17       | — | — | (DDB5) | DDB4 | DDB3 | DDB2 | DDB1 | DDB0 | DDRB |

| Read/Write | R | R | R(/W)  | R/W  | R/W  | R/W  | R/W  | R/W  |      |

| 初期値        | 0 | 0 | 0      | 0    | 0    | 0    | 0    | 0    |      |

注: DDB5はATtiny12でだけ利用可能です。

### ■ ポートB入力レジスタ (Port B Input Address) PINB

| ビット        | 7 | 6 | 5     | 4     | 3     | 2     | 1     | 0     | PINB |

|------------|---|---|-------|-------|-------|-------|-------|-------|------|

| \$16       | — | — | PINB5 | PINB4 | PINB3 | PINB2 | PINB1 | PINB0 | PINB |

| Read/Write | R | R | R     | R     | R     | R     | R     | R     |      |

| 初期値        | 0 | 0 | 不定    | 不定    | 不定    | 不定    | 不定    | 不定    |      |

実際のポートB入力レジスタ(PINB)はレジスタではなく、このアドレスはポートB各ピンの物理的な値へのアクセスができます。ポートB出力レジスタ(PORTB)を読む時はポートB出力ラッチが読まれ、ポートB入力レジスタ(PINB)を読む時は、このピン上に存在する論理値が読まれます。

## ポートB 標準デジタル入出力

標準I/Oピンとして使われるとき、ポートBの最下位側5ピンは同じ機能動作です。

標準I/OピンPBnは、[ポートB方向レジスタ\(DDRB\)](#)のDDBnビットがそのピンの入出力方向を選択し、DDBnが設定(1)されると、出力ピンとして設定されます。DDBnが解除(0)されると、入力ピンとして設定されます。[ポートB出力レジスタ\(PORTB\)](#)のPORTBnが設定(1)され、そのピンが入力ピンとして設定されている場合、MOSフルアップ抵抗が有効化されます。ATtiny12ではMCU制御レジスタ(MCUCR)のフルアップ禁止(PUD)ビットの設定(1)により、この機能が禁止できます。このフルアップ抵抗をOFFに切り替えるには、PORTBnが解除(0)されるか、またはそのピンが出力として設定されるか、またATtiny12ではMCUCRのPUDビットの設定(1)で行えます。ポートBピンはリセット条件が有効になると、例えクロックが動作していないくともHi-Z状態にされます。

表20. ポートBピンに対するDDBnの関係

| DDBn | PORTBn | 入出力 | フルアップ抵抗 | 備考                                                                |

|------|--------|-----|---------|-------------------------------------------------------------------|

| 0    | 0      | 入力  | なし      | 高インピーダンス(Hi-Z)                                                    |

| 0    | 1      | 入力  | あり      | PBnに外部からLowを入力すると吐き出し電流が流れます。ATtiny12ではPUDの設定(1)によってフルアップが禁止されます。 |

| 1    | 0      | 出力  | なし      | Low出力                                                             |

| 1    | 1      | 出力  | なし      | High出力                                                            |

注: nは4,3~0でビット番号を示します。

ATtiny10/11のPB5が入力専用なことに注意してください。ATtiny12のPB5は入力かオープンドレイン出力です。このピンが12V(高電圧直列)プログラミングに使われるため、ピン上の電圧をVCC+0.5Vに制限する静電破壊防止ダイオードがありません。従って、通常動作中にこのピンの電圧がVCC+1V以上に上昇しないことを保証するために特別な注意が必要とされるべきです。これは予期せぬリセットやプログラミング動作への移行の原因になるかもしれません。

## ポートBの交換機能

全てのポートBピンはピン変化割り込みを起動できるピン変化検出器に接続されます。詳細については[18頁の「ピン変化割り込み」](#)をご覧ください。加えてポートBには次の交換機能があります。

### • RESET - ポートB ビット5 : PB5

RESET : [RSTDISBLヒューズ](#)が非プログラム(1)のとき、このピンは外部リセットとして扱います。RSTDISBLヒューズがプログラム(0)されると、このピンは標準入力ピンです。ATtiny12では、オープンドレイン出力ピンでもあります。

### • XTAL2 - ポートB ビット4 : PB4

XTAL2 : クロック発振器出力です。このピンがクロックの目的に使われない時は標準I/Oピンです。詳細については[4頁の「ピン概要」](#)項を参照してください。

### • XTAL1 - ポートB ビット3 : PB3

XTAL1 : クロック発振器入力または外部クロック信号入力です。このピンがクロックの目的に使われない時は標準I/Oピンです。詳細については[4頁の「ピン概要」](#)項を参照してください。

### • T0/(SCK) - ポートB ビット2 : PB2

T0 : このピンはタイマ/カウンタ外部クロック入力としても扱えます。より多くの詳細については[「タイマ/カウンタ」](#)記述をご覧ください。タイマ/カウンタ外部クロック駆動選択時、例え出力として設定されていても、このピン上の有効動作はタイマ/カウンタをクロック駆動します。

SCK(ATtiny12のみ) : ATtiny12での直列プログラミング動作で、このピンは直列クロック入力(SCK)として扱います。

### • INT0/AIN1/(MISO) - ポートB ビット1 : PB1

INT0 : このピンは外部割り込み0入力として扱えます。詳細と許可の方法については[「割り込みの扱い」](#)記述をご覧ください。このピンが出力として設定されていても、このピン上の有効動作が割り込みを起動することに注意してください。

AIN1 : このピンは内蔵アナログ比較器の反転入力としても扱います。

MISO(ATtiny12のみ) : ATtiny12での直列プログラミング動作で、このピンは直列データ出力(MISO)として扱います。

### • AIN0/(MOSI) - ポートB ビット0 : PB0

AIN0 : このピンは内蔵アナログ比較器の非反転入力としても扱います。

MOSI(ATtiny12のみ) : ATtiny12での直列プログラミング動作で、このピンは直列データ入力(MOSI)として扱います。

[パワーダウン動作](#)中、シェミットトリガデジタル入力がアナログ比較器入力ピンから切り離されます。これはパワーダウン動作中、過大な電力消費の原因とならずに、VCC/2近辺のアナログ電圧が存在するのを許容します。

## メモリ プログラミング

### プログラム メモリとデータ メモリ用施錠ビット

ATtiny10/11/12 MCUは非プログラム(1)のままか、表21.で示される付加機能を得るためにプログラム(0)できる2つの施錠ビットを提供します。この施錠ビットはチップ消去でのみ1に消去できます。

表21. 施錠ビットの保護種別

| 保護番号 | メモリ施錠ビット |     | 保護種別                                  |

|------|----------|-----|---------------------------------------|

|      | LB1      | LB2 |                                       |

| 1    | 1        | 1   | メモリ施錠機能は許可されません。                      |

| 2    | 0        | 1   | フラッシュ メモリとEEPROMのプログラミング機能が禁止されます。(注) |

| 3    | 0        | 0   | 保護種別2と同様、更に照合も禁止されます。                 |

注: 高電圧直列プログラミング動作でのヒューズ ビットの書き込みも禁止されます。施錠ビットの書き込み前にヒューズ ビットを書いてください。

### ヒューズ ビット (ATtiny10/11)

ATtiny10/11には5つのヒューズ ビット、FSTRT, RSTDISBL, CKSEL2~0があります。

- FSTRT: 使うには12頁の「表7. リセット遅延時間 (ATtiny10/11, VCC=2.7V)」をご覧ください。既定値は非プログラム(1)です。

- RSTDISBL: RSTDISBLがプログラム(0)されると、PB5ピンの外部リセット機能が禁止されます(注)。既定値は非プログラム(1)です。

- CKSEL2~0: 使用のためのCKSEL2~0の組み合わせについては5頁の「表3. クロック選択」をご覧ください。既定値は'100'(内蔵RC発振器)です。

ヒューズ ビットの状態はチップ消去による影響を受けません。

注: RSTDISBLヒューズがプログラム(0)される場合、その後、プログラミング装置(書き込み器)はATtiny10/11が電源ONリセット中、PB5に+12Vを印加すべきです。そうしないと、PB0駆動の衝突による原因でプログラミング動作への移行失敗が有り得ます。

### ヒューズ ビット (ATtiny12)

ATtiny12には8つのヒューズ ビット、BODLEVEL, BODEN, SPIEN, RSTDISBL, CKSEL3~0があります。全てのヒューズ ビットは高電圧と低電圧の直列プログラミング動作の両方でプログラミングできます。ヒューズの変更はプログラミング中、どんな効果も持ちません(保留されます)。

- BODLEVEL: BODLEVELヒューズは低電圧検出電圧の選択と起動(リセット遅延)時間の変更をします。14頁の「低電圧(プラウンアウト)検出リセット (ATtiny12)」と13頁の「表9. CKSELヒューズによるリセット遅延選択 (ATtiny12)」をご覧ください。既定値はプログラム(0)です。

- BODEN: BODENヒューズがプログラム(0)されると、低電圧検出器(BOD)が許可されます。14頁の「低電圧(プラウンアウト)検出リセット(ATtiny12)」をご覧ください。既定値は非プログラム(1)です。

- SPIEN: SPIENヒューズ ビットがプログラム(0)されると、低電圧直列プログラミングが許可されます。既定値はプログラム(0)です。低電圧直列プログラミング動作中のこのヒューズの非プログラム(1)化は、将来の実装書き換えの意図を禁止してしまいます。

- RSTDISBL: RSTDISBLがプログラム(0)されると、PB5ピンの外部リセット機能が禁止されます(注)。既定値は非プログラム(1)です。低電圧直列プログラミング動作中のこのヒューズの非プログラム(1)化は、将来の実装書き換えの意図を禁止してしまいます。

- CKSEL3~0: 使用のためのCKSEL3~0の組み合わせについては5頁の「表3. クロック選択」と13頁の「表9. CKSELヒューズによるリセット遅延選択 (ATtiny12)」をご覧ください。既定値は'0010'(内蔵RC発振器、長起動時間)です。

ヒューズ ビットの状態はチップ消去による影響を受けません。

注: RSTDISBLヒューズがプログラム(0)される場合、その後、プログラミング装置(書き込み器)はATtiny12が電源ONリセット中、PB5に+12Vを印加すべきです。そうしないと、PB0若しくはPB5駆動の衝突による原因でプログラミング動作への移行失敗が有り得ます。

## 識票バイト

全てのAtmelマイクロコントローラはデバイス識別用に3バイトの識票符号を持ちます。この3バイトは他から分離された空間に存在します。

ATtiny10の識票符号を次に示します。

- ① \$000 : \$1E 製造業者Atmelを示します。

- ② \$001 : \$90 フラッシュメモリ容量1Kバイトを示します。

- ③ \$002 : \$03 ②値\$90と合せ、ATtiny10を示します。

ATtiny11の識票符号を次に示します。

- ① \$000 : \$1E 製造業者Atmelを示します。

- ② \$001 : \$90 フラッシュメモリ容量1Kバイトを示します。

- ③ \$002 : \$04 ②値\$90と合せ、ATtiny11を示します。

ATtiny12の識票符号を次に示します。

- ① \$000 : \$1E 製造業者Atmelを示します。

- ② \$001 : \$90 フラッシュメモリ容量1Kバイトを示します。

- ③ \$002 : \$05 ②値\$90と合せ、ATtiny12を示します。

**注:** 両方の施錠ビットがプログラム(0)される(保護種別3)と、識票バイトは低電圧直列動作で読みません。識票バイトの読み込みは\$00, \$01,\$02が戻ります。

## 校正バイト (ATtiny12)

ATtiny12には内蔵RC発振器用の1バイト校正值があります。このバイトは識票アドレス空間のアドレス\$000の上位バイトにあります。メモリプログラミング中に外部書き込み器はこの位置を読み、通常のプログラム用フラッシュメモリまたはEEPROM内の選択した位置に書かなければなりません。起動時に使用者プログラムはこのメモリ位置を読み、その値を発振校正レジスタ(OSCCAL)に書かなければなりません。

## フラッシュメモリとEEPROMのプログラミング

### ATtiny10/11

AtmelのATtiny10/11は1Kバイトのプログラム用フラッシュメモリを提供します。

ATtiny10/11には、プログラム用内蔵フラッシュメモリが、消去(全ビット=1)され、プログラムされる準備が整った状態で搭載されています。このデバイスは高電圧(12V)直列プログラミング動作を支援します。プログラミング中、+12Vピンから低電流(<1mA)が引き込まれるだけです。ATtiny10/11のフラッシュメモリはバイト単位で書かれます(プログラミングされます)。

### ATtiny12

AtmelのATtiny12は実装再書き込み可能な1Kバイトのプログラム用フラッシュメモリと64バイトのデータ用EEPROMメモリを提供します。

ATtiny12にはプログラム用内蔵フラッシュメモリとデータ用EEPROMメモリが、消去(全ビット=1)され、プログラムされる準備が整った状態で搭載されています。

このデバイスは高電圧(12V)直列プログラミング動作と低電圧直列プログラミング動作を支援します。+12Vはプログラム許可のためだけに使われ、このピンにより特筆すべき電流は流されません。低電圧直列プログラミング動作は実装済みのATtiny12にプログラムとデータを書き込む便利な方法を提供します。

ATtiny12のフラッシュメモリとEEPROMはどちらのプログラミング動作でもバイト単位でプログラムされます。EEPROMについては低電圧直列プログラミング動作での自動書き込み命令で自動消去周期が提供されます。

### ATtiny10/11/12

プログラミング中の供給電圧は表22に従っていなければなりません。

表22. プログラミング中の供給電圧

| デバイス         | 低電圧直列プログラミング | 高電圧直列プログラミング |

|--------------|--------------|--------------|

| ATtiny10/11L | 適用不可         |              |

| ATtiny10/11  |              |              |

| ATtiny12V    | 2.2~5.5V     | 4.5~5.5V     |

| ATtiny12L    | 2.7~5.5V     |              |

| ATtiny12     | 4.0~5.5V     |              |

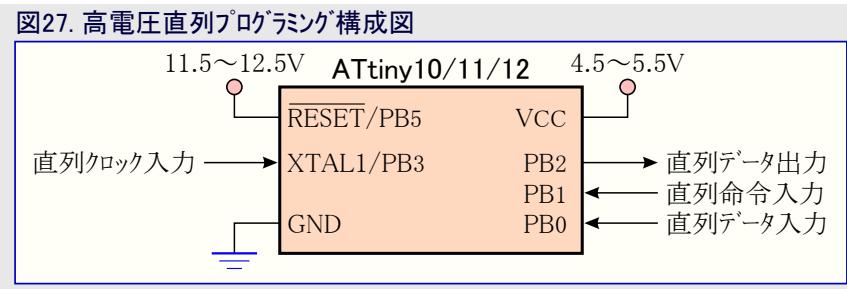

## 高電圧直列プログラミング

本項はATtiny10/11/12でのプログラム用フラッシュメモリ、データ用EEPROM(ATtiny12のみ)、施錠ピット、ヒューズピットの高電圧直列プログラミングと照合の方法を記述します。

## 高電圧直列プログラミング手順

高電圧直列プログラミング動作でのATtiny10/11/12のプログラミングと照合は、次の手順が推奨されます(命令形式は表23.参照)。

1. 次の手順で電源を投入します。

VCCとGND間に4.5~5.5Vを印加します。PB5とPB0をLow(0)に設定し、最低100ns待ちます。最小100nsのパルス幅で最低4回、PB3を交互(High/Low)切り替えします。PB3をLow(0)に設定します。最低100ns待ちます。PB0を変更する前に、PB5~12Vを印加し、最低100ns待ちます。何れかの命令を与える前に8μs待ちます。

2. フラッシュメモリは最初にアドレス、次に下位、上位バイトデータを供給することにより、1バイト単位で書き込まれます。書き込み命令は自己タイミングで行われ、PB2(RDY/BSY)ピンがHighになるまで待機します。

3. EEPROM(ATtiny12のみ)は最初にアドレス、次にバイトデータを供給することにより、1バイト単位で書き込まれます。書き込み命令は自己タイミングで行われ、PB2(RDY/BSY)ピンがHighになるまで待機します。

4. 何れのメモリ位置も、選択されたアドレスの内容を直列出力(PB2)ピンに読み戻す、読み出し命令の使用で検証ができます。

5. 電源OFF手順

- PB3をLow(0)にします。

- PB5をHigh(1)にします。

- VCC電源をOFFにします。

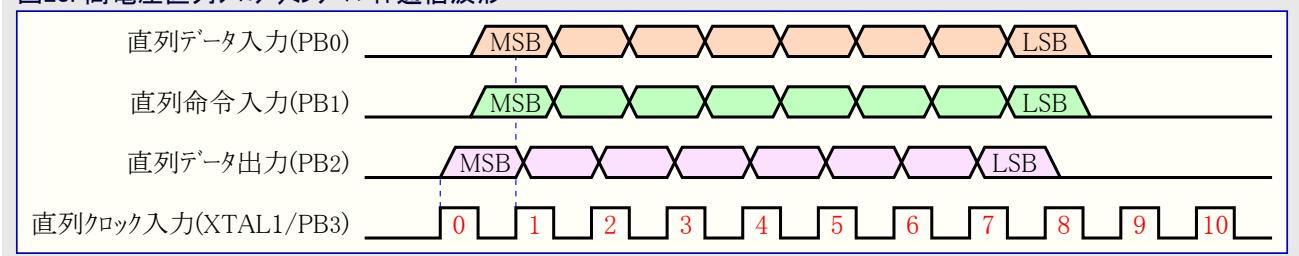

ATtiny10/11/12との直列データを読み書きするとき、データは直列クロックの上昇端でクロック駆動されます。詳細については図28.、図29.、表24.を参照してください。

図28. 高電圧直列プログラミング バイト通信波形

表23. 高電圧直列プログラミング命令一式

| 命令                         | 命令形式 |                |                |                | 備考                                            |

|----------------------------|------|----------------|----------------|----------------|-----------------------------------------------|

|                            | PB   | 第1バイト          | 第2バイト          | 第3バイト          | 第4バイト                                         |

| チップ消去                      | 0    | 0 1000 0000 00 | 0 0000 0000 00 | 0 0000 0000 00 | 0 0000 0000 00                                |

|                            | 1    | 0 0100 1100 00 | 0 0110 0100 00 | 0 0110 1100 00 | 0 0100 1100 00                                |

|                            | 2    | x XXXX XXXX XX                                |

| フラッシュメモリ書き込みアドレス設定         | 0    | 0 0001 0000 00 | 0 0000 000H 00 | 0 LLLL LLLL 00 | 第3バイトは新規アドレス毎、第2バイトは新規ページ毎に設定します。             |

|                            | 1    | 0 0100 1100 00 | 0 0001 1100 00 | 0 0000 1100 00 |                                               |

|                            | 2    | x XXXX XXXX XX | x XXXX XXXX XX | x XXXX XXXX XX |                                               |

| フラッシュメモリ下位バイト書き込み          | 0    | 0 WWWW WWWW 00 | 0 0000 0000 00 | 0 0000 0000 00 | 第3バイト後PB2=Highまで待機します。新規アドレス毎に第1~3バイトを繰り返します。 |

|                            | 1    | 0 0010 1100 00 | 0 0110 0100 00 | 0 0110 1100 00 |                                               |

|                            | 2    | x XXXX XXXX XX | x XXXX XXXX XX | 0 0000 0000 00 |                                               |

| フラッシュメモリ上位バイト書き込み          | 0    | 0 WWWW WWWW 00 | 0 0000 0000 00 | 0 0000 0000 00 | 第2,3バイトは新規アドレス毎に設定します。                        |

|                            | 1    | 0 0011 1100 00 | 0 0111 0100 00 | 0 0111 1100 00 |                                               |

|                            | 2    | x XXXX XXXX XX | x XXXX XXXX XX | 0 0000 0000 00 |                                               |

| フラッシュメモリ読み出しアドレス設定         | 0    | 0 0000 0010 00 | 0 0000 000H 00 | 0 LLLL LLLL 00 | 第2,3バイトは新規アドレス毎に設定します。                        |

|                            | 1    | 0 0100 1100 00 | 0 0001 1100 00 | 0 0000 1100 00 |                                               |

|                            | 2    | x XXXX XXXX XX | x XXXX XXXX XX | x XXXX XXXX XX |                                               |

| フラッシュメモリ下位バイト読み出し          | 0    | 0 0000 0000 00 | 0 0000 0000 00 |                | 新規アドレス毎に第1,2バイトを繰り返します。                       |

|                            | 1    | 0 0110 1000 00 | 0 0110 1100 00 |                |                                               |

|                            | 2    | x XXXX XXXX XX | R RRRR RRRX XX |                |                                               |

| フラッシュメモリ上位バイト読み出し          | 0    | 0 0000 0000 00 | 0 0000 0000 00 |                | 新規アドレス毎に第2バイトを繰り返します。                         |

|                            | 1    | 0 0111 1000 00 | 0 0111 1100 00 |                |                                               |

|                            | 2    | x XXXX XXXX XX | R RRRR RRRX XX |                |                                               |

| EEPROM書き込みアドレス設定(ATtiny12) | 0    | 0 0001 0001 00 | 0 00LL LLLL 00 |                | 第2バイトは新規アドレス毎に設定します。                          |

|                            | 1    | 0 0100 1100 00 | 0 0000 1100 00 |                |                                               |

|                            | 2    | x XXXX XXXX XX | x XXXX XXXX XX |                |                                               |

| EEPROMバイト書き込み(ATtiny12)    | 0    | 0 WWWW WWWW 00 | 0 0000 0000 00 | 0 0000 0000 00 | 第3バイト後PB2=Highまで待機します。新規アドレス毎に第1~3バイトを繰り返します。 |

|                            | 1    | 0 0010 1100 00 | 0 0110 0100 00 | 0 0110 1100 00 |                                               |

|                            | 2    | x XXXX XXXX XX | x XXXX XXXX XX | 0 0000 0000 00 |                                               |

| EEPROM読み出しアドレス設定(ATtiny12) | 0    | 0 0000 0011 00 | 0 00LL LLLL 00 |                | 第2バイトは新規アドレス毎に設定します。                          |

|                            | 1    | 0 0100 1100 00 | 0 0000 1100 00 |                |                                               |

|                            | 2    | x XXXX XXXX XX | x XXXX XXXX XX |                |                                               |

| EEPROMバイト読み出し(ATtiny12)    | 0    | 0 0000 0000 00 | 0 0000 0000 00 |                | 新規アドレス毎に第2バイトを繰り返します。                         |

|                            | 1    | 0 0110 1000 00 | 0 0110 1100 00 |                |                                               |

|                            | 2    | x XXXX XXXX XX | R RRRR RRRX XX |                |                                               |

| ヒューズビット書き込み(ATtiny10/11)   | 0    | 0 0100 0000 00 | 0 0008 7543 00 | 0 0000 0000 00 | 第3バイト後tWLWH_PFB時間待機します。                       |

|                            | 1    | 0 0100 1100 00 | 0 0010 1100 00 | 0 0110 0100 00 |                                               |

|                            | 2    | x XXXX XXXX XX | x XXXX XXXX XX | x XXXX XXXX XX |                                               |

| ヒューズビット書き込み(ATtiny12)      | 0    | 0 0100 0000 00 | 0 BA97 6543 00 | 0 0000 0000 00 | 第4バイト後PB2=Highまで待機します。                        |

|                            | 1    | 0 0100 1100 00 | 0 0010 1100 00 | 0 0110 0100 00 |                                               |

|                            | 2    | x XXXX XXXX XX | x XXXX XXXX XX | x XXXX XXXX XX |                                               |

| 施錠ビット書き込み                  | 0    | 0 0010 0000 00 | 0 0000 0210 00 | 0 0000 0000 00 | 第4バイト後PB2=Highまで待機します。                        |

|                            | 1    | 0 0100 1100 00 | 0 0010 1100 00 | 0 0110 0100 00 |                                               |

|                            | 2    | x XXXX XXXX XX | x XXXX XXXX XX | x XXXX XXXX XX |                                               |

| ヒューズビット読み出し(ATtiny10/11)   | 0    | 0 0000 0100 00 | 0 0000 0000 00 | 0 0000 0000 00 |                                               |

|                            | 1    | 0 0100 1100 00 | 0 0110 1000 00 | 0 0110 1100 00 |                                               |

|                            | 2    | x XXXX XXXX XX | x XXXX XXXX XX | x xx87 543X XX |                                               |

| ヒューズビット読み出し(ATtiny12)      | 0    | 0 0000 0100 00 | 0 0000 0000 00 | 0 0000 0000 00 |                                               |

|                            | 1    | 0 0100 1100 00 | 0 0110 1000 00 | 0 0110 1100 00 |                                               |

|                            | 2    | x XXXX XXXX XX | x XXXX XXXX XX | B A976 543X XX |                                               |

| 施錠ビット読み出し                  | 0    | 0 0000 0100 00 | 0 0000 0000 00 | 0 0000 0000 00 |                                               |

|                            | 1    | 0 0100 1100 00 | 0 0111 1000 00 | 0 0111 1100 00 |                                               |

|                            | 2    | x XXXX XXXX XX | x XXXX XXXX XX | x XXXX 21XX XX |                                               |

| 識票バイト読み出し                  | 0    | 0 0000 1000 00 | 0 0000 00LL 00 | 0 0000 0000 00 | 新規アドレス毎に第2~4バイトを繰り返します。                       |

|                            | 1    | 0 0100 1100 00 | 0 0000 1100 00 | 0 0110 1000 00 |                                               |

|                            | 2    | x XXXX XXXX XX | x XXXX XXXX XX | R RRRR RRRX XX |                                               |

| 校正バイト読み出し(ATtiny12)        | 0    | 0 0000 1000 00 | 0 0000 0000 00 | 0 0000 0000 00 |                                               |

|                            | 1    | 0 0100 1100 00 | 0 0000 1100 00 | 0 0111 1000 00 |                                               |

|                            | 2    | x XXXX XXXX XX | x XXXX XXXX XX | R RRRR RRRX XX |                                               |

注: H = アドレス上位バイトのビット

1 = 施錠ビット1 (LB1)

5 = CKSEL2 ヒューズビット

9 = SPIEN ヒューズビット

L = アドレス下位バイトのビット

2 = 施錠ビット2 (LB2)

6 = CKSEL3 ヒューズビット

A = BODEN ヒューズビット

R = 読み出しデータ (MCU出力)

3 = CKSEL0 ヒューズビット

7 = RSTDISBL ヒューズビット

B = BODLEVEL ヒューズビット

W = 書き込みデータ (MCU入力)

4 = CKSEL1 ヒューズビット

8 = FSTRT ヒューズビット

x = 0か1 (無視または無効)

## 高電圧直列プログラミング特性

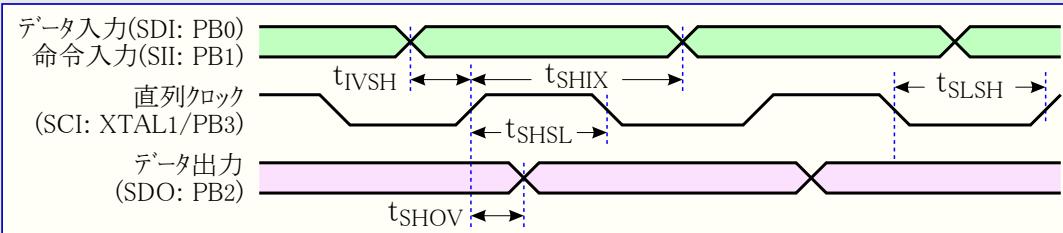

図29. 高電圧直列プログラミング タイミング

表24. 高電圧直列プログラミング特性 (特記条件を除いて、TA=25°C±10% , VCC=5.0V±10%)

| シンボル      | 項目                  | 最小  | 代表  | 最大  | 単位 |

|-----------|---------------------|-----|-----|-----|----|

| tSHSL     | SCIパルスHレベル幅         | 100 |     |     | ns |

| tSLSH     | SCIパルスLレベル幅         | 100 |     |     |    |

| tIVSH     | SCI↑に対するSDI,SII準備時間 | 50  |     |     |    |

| tSHIX     | SCI↑に対するSDI,SII保持時間 | 50  |     |     |    |

| tSHOV     | SCI↑に対するSDO出力遅延時間   | 10  | 16  | 32  |    |

| tWLWH_PFB | ヒューズ書き込み第3バット後待機時間  | 1.7 | 2.5 | 3.4 | ms |

(訳注) ヒューズ書き込み第3バット後待機時間(tWLWH\_PFB)が、各々 1.0, 1.5, 1.8から変更されています。

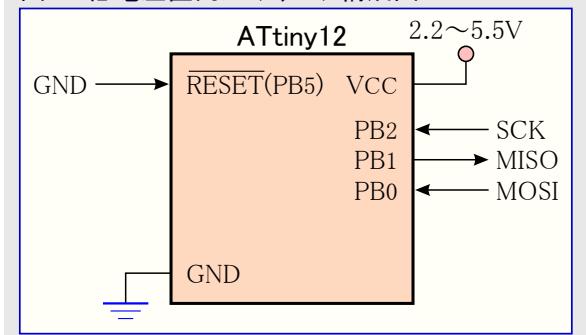

## 低電圧直列プログラミング (ATtiny12のみ)

フラッシュメモリとEEPROMの両方はRESETがLowレベルの間に直列SPIバスを使ってプログラミングを行うことができます。この直列インターフェースはSCK入力、MOSI入力、MISO出力で構成されます(図30参照)。RESETをLowレベルに設定後、プログラムや消去命令が実行される前に、[プログラミング許可命令](#)が最初に実行されなければなりません。

低電圧直列プログラミングでチップ消去命令が1回だけ実行される場合、消去後に1バイトデータがフラッシュメモリへ書かれてしまうかもしれません。次の方法の使用はフラッシュメモリが消去されることを保証します。

- チップ消去命令を実行します。

- フラッシュメモリのアドレス\$000に\$FFを書きます。

- 2度目のチップ消去命令を実行します。

EEPROMに対しては自己タイミングによる書き込み命令内で先行して自動消去周期が提供される(低電圧直列プログラミングのみ)ので、最初にチップ消去命令を実行する必要はありません。チップ消去命令はフラッシュメモリとEEPROMの全ての内容を\$FFにします。

フラッシュメモリとEEPROMメモリは、プログラム用フラッシュメモリが\$0000～\$01FF、データ用EEPROMメモリが\$0000～\$003Fの分離されたアドレス空間を持ちます。

低電圧直列プログラミング中、このデバイスは何れのクロック種別によてもクロック駆動できます。直列クロック(SCK)入力のLow区間とHigh区間の最小値は次のように定義されます。

Low区間 > 2 MCU クロック周期    High区間 > 2 MCU クロック周期

図30. 低電圧直列プログラミング構成図

## 低電圧直列プログラミング手順

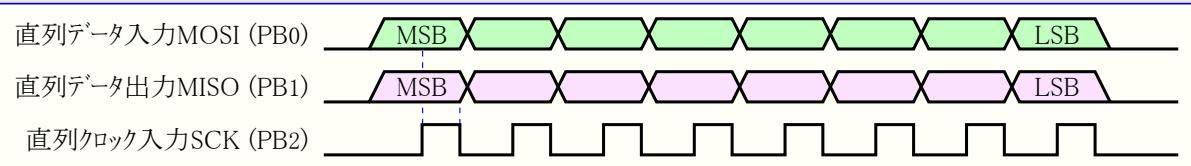

ATtiny12に直列データを書く時はSCKの上昇端で行われ、読む時はSCKの下降端で行われます。これらの詳細タイミングについては図31、図32、表26をご覧ください。低電圧直列プログラミング動作でATtiny12のプログラミングと照合をするには次の手順が推奨されます。(4バイトの命令形式は表25を参照)

- 次の手順で電源を投入します。

RESETとSCKがLow(0)に設定されている間に、VCCとGND間へ電源を印加します。CKSELヒューズの設定に従って、クリスタル/振動子、外部クロック、または外部RCを適用するか、またはデバイスを内蔵RC発振器で動作させます。いくつかのシステムに於いて、電源投入中、SCKがLow(0)に保持されることを書き込み器が保証できません。この場合、SCKがLow(0)に設定されてしまった後、100ms待機します。そして、RESETには最低XTAL1周期幅2つ分の正パルスが与えられなければなりません。

- 最低20ms待機し、MOSI(PB0)ピンに[プログラミング許可命令](#)を送ることによって直列プログラミングを可能にします。

- 通信の同期が外れていると、直列プログラミング命令が動作しません。同期しているとき、プログラム許可命令の第3バイト送出時に第2バイト(\$53)を送り返します。この送り返しが成功か失敗かによらず、命令の4バイト全てが送信されなければなりません。送り返しが\$53でなかった場合、SCKに正パルスを与え、新規プログラミング許可命令を行います。32回の試行で\$53が検出できない場合、低電圧直列プログラミング機能のないデバイスが接続されています。

- チップ消去が実行される場合(フラッシュメモリの消去のために実行が必要)、この命令実行後tWD\_ERASE(36頁の表27参照)時間待機して、RESETに正パルスを与え、手順2.からを行います。

- フラッシュメモリやEEPROMは適切な書き込み命令内でアドレスとデータを供給することによって1バイト単位で書かれます。EEPROMメモリ位置は、新規(今回)データが書かれる前、最初に自動消去されます。フラッシュメモリやEEPROMの次のバイトが書けるときを検出するためにデータポーリングを使ってください。ポーリングが使われない場合、次の命令送出前にtWD\_FLASHまたはtWD\_EEPROM(36頁の表28参照)時間待機します。消去されているデバイスでは、\$FFのデータを書く必要がありません。

- 何れのメモリ位置も、選択されたアドレスの内容を直列出力MISO(PB1)ピンに読み戻す、読み出し命令を使って検証できます。

- プログラミング終了時、通常動作とするためには、RESETをHigh(1)に設定します。

- 電源OFF手順(必要な場合)

- XTAL1/PB3をLow(0)にします。(外部クロックが使われる場合)

- RESETをHigh(1)にします。

- VCC電源をOFFにします。

## データポーリング

フラッシュメモリまたはEEPROM内でバイトが書かれているとき、書かれているアドレス位置を読むと、値\$FFが得られます。書かれた値が正しく読めると同時に、デバイスは新規バイトの準備が整います。これは次バイトが書けるときを決めるのに使われます。これは値\$FFについて行えず、この値を書くときは、次バイト書き込み前に最低tWD\_FLASHまたはtWD\_EEPROM待たなければなりません。チップ消去されたデバイスの内容は全て\$FFですので、書き込み値\$FFのアドレスの書き込みは飛ばすことができます。これはデバイスをチップ消去しないでEEPROMが再書き込みされる場合、適用されません。この場合、値\$FFについてデータポーリングは使えず、次バイト書き込み前に最低tWD\_EEPROM待たなければなりません。tWD\_FLASHとtWD\_EEPROM値については表28をご覧ください。

図31. 低電圧直列プログラミング バイト通信波形

表25. 低電圧直列プログラミング命令一式

| 命令           | 命令形式      |           |           |           | 動作                        |

|--------------|-----------|-----------|-----------|-----------|---------------------------|

|              | 第1バイト     | 第2バイト     | 第3バイト     | 第4バイト     |                           |

| プログラミング許可    | 1010 1100 | 0101 0011 | xxxx xxxx | xxxx xxxx | RESET=Low中、プログラミングを許可します。 |

| チップ消去        | 1010 1100 | 100x xxxx | xxxx xxxx | xxxx xxxx | フラッシュメモリとEEPROMを消去します。    |

| フラッシュメモリ読み出し | 0010 P000 | xxxx xxxH | LLLL LLLL | RRRR RRRR | アドレスH:LのP(H/L)バイトを読み出します。 |

| フラッシュメモリ書き込み | 0100 P000 | xxxx xxxH | LLLL LLLL | WWWW WWWW | アドレスH:LのP(H/L)バイトに書き込みます。 |

| EEPROM読み出し   | 1010 0000 | xxxx xxxx | xxLL LLLL | RRRR RRRR | アドレスLのバイトを読み出します。         |

| EEPROM書き込み   | 1100 0000 | xxxx xxxx | xxLL LLLL | WWWW WWWW | アドレスLのバイトに書き込みます。         |

| 施錠ビット読み出し    | 0101 1000 | xxxx xxxx | xxxx xxxx | xxxx x21x | 施錠ビット(LB1,LB2)を読み出します。    |

| 施錠ビット書き込み    | 1010 1100 | 1111 1211 | xxxx xxxx | xxxx xxxx | 施錠ビット(LB1,LB2)を書き込みます。    |

| ヒューズビット読み出し  | 0101 0000 | xxxx xxxx | xxxx xxxx | A987 6543 | ヒューズビットを読み出します。           |

| ヒューズビット書き込み  | 1010 1100 | 101x xxxx | xxxx xxxx | A987 6543 | ヒューズビットを書き込みます。           |

| 識票バイト読み出し    | 0011 0000 | xxxx xxxx | xxxx xxLL | RRRR RRRR | アドレスLの識票バイトを読み出します。       |

| 校正バイト読み出し    | 0011 1000 | xxxx xxxx | 0000 0000 | RRRR RRRR | 内蔵RC発振器用校正バイトを読み出します。     |

注1: H: アドレス上位バイトのビット

L: アドレス下位バイトのビット

P: 0=下位バイト、1=上位バイト

R: 読み出しデータ (MCU出力)

W: 書き込みデータ (MCU入力)

1: 施錠ビット1 (LB1)

2: 施錠ビット2 (LB2)

3: CKSEL0 ヒューズビット

4: CKSEL1 ヒューズビット

5: CKSEL2 ヒューズビット

6: CKSEL3 ヒューズビット

7: RSTDISBL ヒューズビット

8: SPIEN ヒューズビット

9: BODEN ヒューズビット

A: BODLEVEL ヒューズビット

x: 0か1 (無視または無効)

注2: 識票バイトは保護種別3(LB1=0, LB2=0)の状態では読み出せません。

## 低電圧直列プログラミング特性

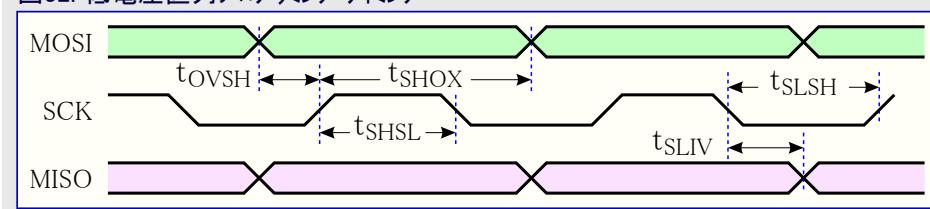

図32. 低電圧直列プログラミング タイミング

表26. 低電圧直列プログラミング特性 (特記条件を除いて、TA=-40°C~85°C, VCC=2.2~5.5V)

| シンボル    | 項目                 | 最小       | 代表   | 最大 | 単位  |

|---------|--------------------|----------|------|----|-----|

| 1/tCLCL | 発振器周波数             | 2.2~2.7V | 0    | 1  | MHz |