# 特徴

- AVR® RISC構造の利用

- 高性能、低消費AVR® RISC構造

- ・強力な123命令(多くは1周期で実行)

- 32個の1バイト長汎用レジスタ

- ・完全なスタティック動作

- ・20MHz時、20MIPSに達する高速動作

# ■ データ メモリと不揮発性プログラム メモリ

- ・実装自己書き換え(ISP)可能な2Kバイト(1K語)フラッシュメモリ内蔵

- ・10,000回の書き換え可能

- 実装書き換え可能な128パイのEEPROM

- ・100,000回の書き換え可能

- 128バイの内蔵SRAM

- ・プログラム用フラッシュ メモリとデータ用EEPROM保護用の設定可能な施錠機能

#### ■ 内蔵周辺機能

- ・分離された前置分周器と比較動作付き1つの8ビットタイマ/カウンタ

- ・分離された前置分周器と比較、捕獲動作付き1つの16ビットタイマ/カウンタ

- 4つのPWM出力

- ・アナログ比較器

- ・設定可能な専用発振器付きウォッチト、ック、タイマ

- ・多用途直列インターフェース(USI)

- 全二重USART

#### ■ 特殊マイクロ コントローラ機能

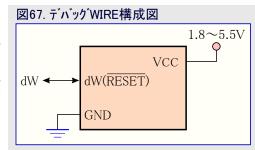

- ・デバッグWIRE内蔵デバッグ機能

- ・SPIポート経由の実装書き込み

- ・外部及び内部の割り込み

- ・アイドル、パワーダウン、スタンバイの3つの低消費動作

- ・強化した電源ONJセット回路

- ・設定可能な低電圧検出器(BOD)回路

- ・校正付き内蔵RC発振器

## ■ I/Oと外囲器

- 18ビットの設定可能なI/O

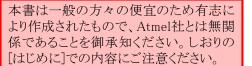

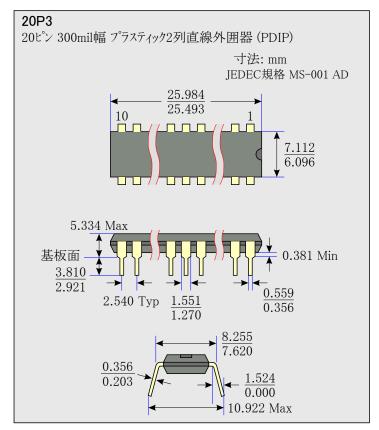

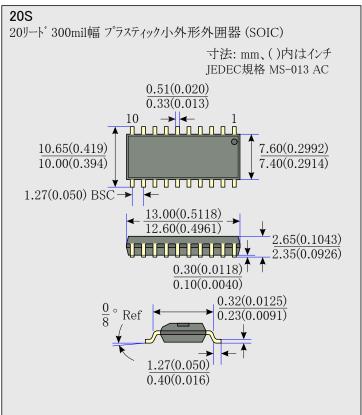

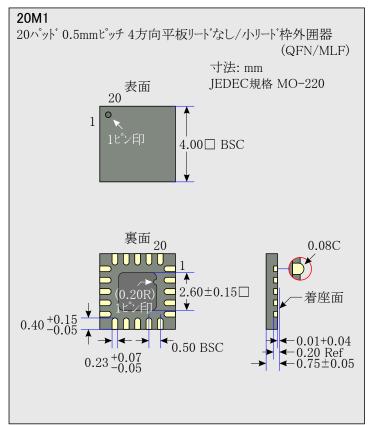

- 20ピンPDIP、20リードSOIC、 20パット、QFN/MLF

## ■ 動作電圧

- 1.8~5.5V (ATtiny2313V)

- 2.7~5.5V (ATtiny2313)

#### ■ 動作速度

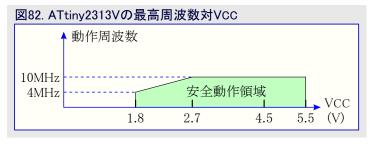

- ATtiny2313V:

- $0\sim4 MHz/1.8\sim5.5 V$

- 0~10MHz/2.7~5.5V

- ATtiny2313 :

- $0 \sim 10 MHz/2.7 \sim 5.5 V$

- $\cdot 0 \sim 20 MHz/4.5 \sim 5.5 V$

#### ■ 代表消費電力

- · 230µA (1MHz,1.8V,活動動作)

- · 20µA (32kHz,1.8V,活動動作)

- ・0.1μA未満 (1.8V,パワータ`ウン動作)

8ビット **AVA**® マイクロ コントローラ 実装書き換え可能な 2 K ハ ベイト フラッシュ メモリ内蔵

ATtiny2313 ATtiny2313V

Rev. 2543M-10/16, 2543MJ3-06/22

# ピン配置

# 概要

ATtiny2313はAVR強化RISC構造を基にした低消費CMOS 8ビット マイクロ コントローラです。1周期での強力な命令の実行により、ATtiny2 313はMHzあたり1MIPSに達する単位処理量を成し遂げ、処理速度対消費電力の最適化を設計者に許します。

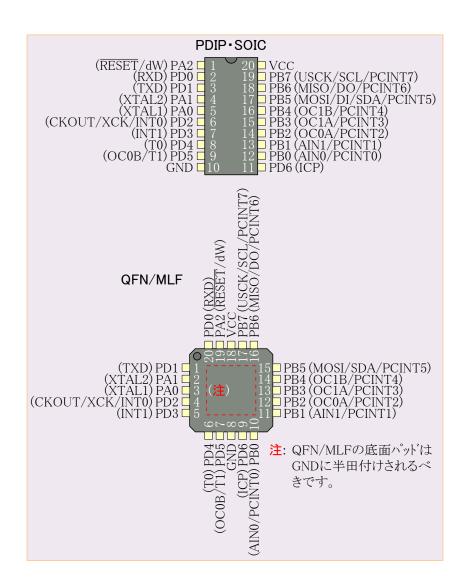

# 構成図

AVRコアは32個の汎用作業レジスタと豊富な命令群の組み合わせです。32個の全レジスタはALU(Arithmetic Logic Unit)に直結され、レジスタ間命令は1クロック周期で実行されます。AVR構造は現状のCISC型マイクロコントローラに対して最大10倍の単位処理量向上効果があります。

ATtiny2313は2Kハ・ハの実装書き込み可能なフラッシュメモリ、128ハ・ハのEEPROM、128ハ・ハのSRAM、18本の汎用入出力線、32個の汎用作業レジ、スタ、内蔵デ・バック・用の単線インターフェース、比較動作付きの2つの柔軟なタイマ/カウンタ、内部及び外部割り込み、設定変更可能な直列USART、開始条件検出器付き多用途直列インターフェース(USI)、内蔵発振器付きの設定変更可能なウォッチト・ック・タイマ、ソフトウェアで選択できる3つの低消費動作を提供します。アイトル動作はCPUを停止し、一方SRAM、タイマ/カウンタ、割り込み機構に機能の継続を許します。ハ・ワータ・ウン動作は発振器を停止しますがレジ、スタの内容を保護し、以降のハート・ウェアリセットか外部割り込みまで他の全機能を禁止します。スタンハ・イ動作ではクリスタル発振子/セラミック振動子用発振器が動作する一方で、デ・バーイスのその他は休止します。これは低消費電力と非常に速い起動の組み合わせを許します。

本デバイスはAtmelの高密度不揮発性メモリ技術を使って製造されています。内蔵の実装書き換え(ISP)可能なフラッシュ メモリはプログラム メモリに使え、規定の不揮発性メモリ書き込み器かSPI直列インターフェース経由によって再書き込みができます。モノリシック チップ 上の実装書き換え可能なフラッシュ メモリと拡張された8ビットRISC型CPUの組み合わせによるATtiny2313は、多くの組み込み制御の応用に対して高度な柔軟性と対費用効果をもたらす強力なマイクロコントローラです。

ATtiny2313 AVRはCコンパイラ、マクロ アセンブラ、デバッカ、シミュレータ、インサーキット エミューレータ、評価キットを含む完全なプログラム及びシステム開発ツールで支援されます。

## ピン概要

VCC

電源ピン。

#### **GND**

接地ピン。

#### **PA2~PA0** (ポートA)

ポートAは(ビット単位で選択される)内蔵プルアップ抵抗付きの3ビット双方向入出力ポートです。ポートA出力緩衝部は共に高い吐き出し/吸い込み能力の対称駆動特性です。入力の時にプルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートAピンには吐き出し電流が流れます。 リセット条件が有効になると、クロックが走行していなくても、ポートAピンはHi-Zにされます。

ポートAは34頁で示されるATtinv2313の様々な特殊機能も扱います。

#### **PB7~PB0**(本°-トB)

ポートBは(ビット単位で選択される)内蔵プルアップ抵抗付きの8ビット双方向入出力ポートです。ポートB出力緩衝部は共に高い吐き出し/吸い込み能力の対称駆動特性です。入力の時にプルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートBピンには吐き出し電流が流れます。リセット条件が有効になると、クロックが走行していなくても、ポートBピンはHi-Zにされます。

ポートBは35頁で示されるATtiny2313の様々な特殊機能も扱います。

#### **PD6~PD0** (ポートD)

ポートDは(ビット単位で選択される)内蔵プルアップ抵抗付きのアビット双方向入出力ポートです。ポートD出力緩衝部は共に高い吐き出し/吸い込み能力の対称駆動特性です。入力の時にプルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートDピンには吐き出し電流が流れます。リセット条件が有効になると、クロックが走行していなくても、ポートDピンはHi-Zにされます。

ポートDは37頁で示されるATtiny2313の様々な特殊機能も扱います。

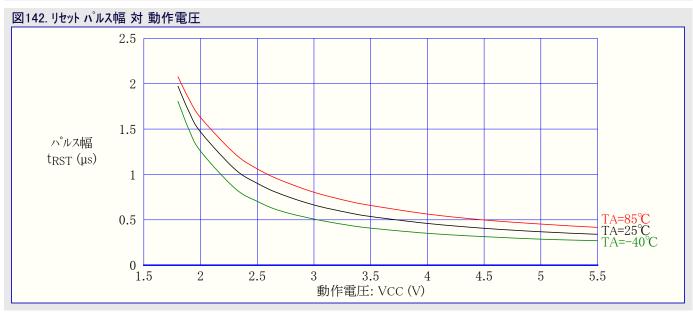

## RESET

リセット入力。例えクロックが走行していなくても、最小パルス幅はり長いこのピンのLowレヘ・ルはリセットを生成します。最小パルス幅は120頁の表80.で与えられます。より短いパルスはリセットの生成が保証されません。リセット入力はPA2及びdW(デバッグWIRE)との切り替え機能です。

#### XTAL1

発振器反転増幅器への入力と内部クロック操作回路への入力。XTAL1はPA0との切り替え機能です。

# XTAL2

発振器反転増幅器からの出力。XTAL2はPA1との切り替え機能です。

# 一般情報

# 資料

包括的なデータシート、応用記述、開発ツール群はhttp://www.atmel.com/avrでのダウンロードで利用可能です。

# コード例

この資料はデバイスの様々な部分の使用法を手短に示す簡単なコート・例を含みます。これらのコート・例はアセンブルまたはコンパイルに先立ってデバイス定義へッタ・ファイルがインクルートされると仮定します。全てのCコンパイラ製造業者がヘッタ・ファイル内にビット定義を含めるとは限らず、またCでの割り込みの扱いがコンパイラに依存することに注意してください。より多くの詳細についてはCコンパイラの資料で確認してください。

# データ保持力

信頼性証明結果はデータ保持誤り率の反映を示し、20年以上/85℃または100年以上/25℃で1PPMよりずっと小さな値です。

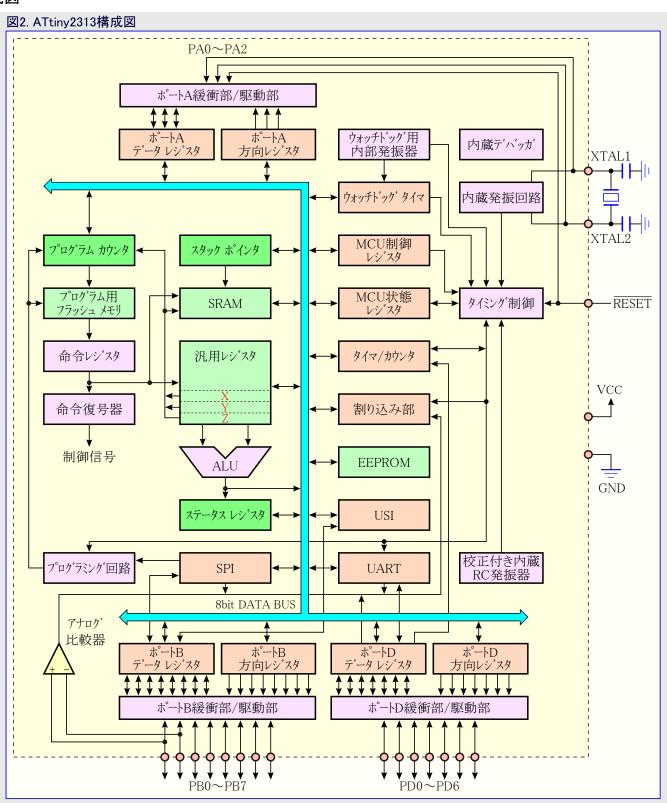

# AVR CPU 17

#### 序説

本項はAVRコア構造を一般的に説明します。このCPUコアの主な機能は正しいプログラム実行を保証することです。従ってCPUはメモリアクセス、計算実行、周辺制御、割り込み操作ができなければなりません。

# 構造概要

最大効率と平行処理のため、AVRはプログラムとデータに対してメモリとハンスを分離するハーハート、構造を使います。プログラムメモリ内の命令は単一段のハーイプラインで実行されます。1命令の実行中に次の命令がプログラムメモリから事前取得されます。この概念は全部のクロック周期で命令実行を可能にします。プログラムメモリは実装書き換え可能なフラッシュメモリです。

高速レジスタファイルは1クロック周期アクセスの32個の8ビット長汎用レジスタを含みます。これは1クロック周期ALU(Arithmetic Logic Unit)操作を許します。代表的なALU操作では2つのオペラントがレジスタファイルからの出力で、1クロック周期内でその操作が実行され、その結果がレジスタファイルに書き戻されます。

32個中の6つのレジスタは効率的なアトンス計算ができるデータ空間アトンス指定用に3つの16ビット長間接アトンスポインタ用レジスタとして使われます。これらアトンスポインタの1つはプログラム用フラッシュメモリ内の定数表参照用アトンスポインタとしても使えます。これら16ビット長付加機能レジスタはX,Y,Zレジスタで、本項内で後述されます。

ALUはレジスタ間またはレジスタと定数間の算術及び論理操作を支援します。単一レジスタ操作もALUで実行できます。算術演算操作後、操作結果についての情報を反映するために、ステータスレジスタ (SREG)が更新されます。

プログラムの流れは条件/無条件分岐や呼び出し命令によって提供され、全アドレス空間を直接アドレス指定できます。AVR命令の多くは

16ビット語(ワード)形式です。全てのプログラム メモリのアドレスは(訳注:定数のみを除き)16または32ビット長命令を含みます。

割り込みやサブルーチン呼び出し中、戻りアトンスを示すプログラム カウンタ(PC)はスタックに保存されます。スタックは一般的なデータ用SRAM上に実際には割り当てられ、従ってスタック容量は全SRAM容量とSRAM使用量でのみ制限されます。全ての使用者プログラムはリセット処理ルーチンで(サブルーチン呼び出しや割り込みが実行される前に)、スタック ホーインタ(SP)を初期化しなければなりません。SPはI/O空間で読み書きアクセスが可能です。データ用SRAMはAVR構造で支援される5つの異なるアトンス指定種別を通して容易にアクセスできます。

AVR構造に於けるメモリ空間は全て直線的な普通のメモリ配置です。

柔軟な割り込み部にはI/O空間の各制御レシ、スタとステータスレシ、スタ(SREG)の特別な全割り込み許可(I)ビットがあります。全ての割り込みは割り込みへ、クタ表に個別の割り込みへ、クタを持ちます。割り込みには割り込みへ、クタ表の位置に従う優先順があります。下位側割り込みへ、クタアドレスが高い優先順位です。

I/Oメモリ空間は制御レジスタや他のI/O機能としてCPU周辺機能用の64アドレスを含みます。I/Oメモリは直接またはレジスタ ファイルの次のデータ空間位置\$20~\$5Fとしてアクセスできます。

#### **ALU** (Arithmetic Logic Unit)

高性能なAVRのALUは32個の全汎用レシ、スタに直接接続され動作します。汎用レシ、スタ間または汎用レシ、スタと即値間の演算操作は単一クロック周期内で実行されます。ALU操作は算術演算、論理演算、ビット操作の3つの主な種類に大別されます。符号付きと符号なし両方の乗算と固定小数点形式を支援する乗算器(乗算命令)も提供する構造の実装(製品)もあります。詳細記述については「命令要約」章をご覧ください。

# ■ ステータス レシ スタ (Status Register) SREG

ステータスレジスタは最も直前に実行した演算命令の結果についての情報を含みます。この情報は条件処理を行うためのプログラムの流れ変更に使えます。ステータスレジスタは「命令一式手引書」で詳述したように、全てのALU操作後、更新されることに注目してください。これは多くの場合でそれ用の比較命令使用の必要をなくし、高速でより少ないコードに帰着します。

ステータス レシ スタは割り込み処理ルーチン移行時の保存と割り込みからの復帰時の回復(復帰)が自動的に行われません。これはソフトウェアによって扱われなければなりません。

AVRのステータス レシ、スタ(SREG)は次のように定義されます。

| ピット         | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _    |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$3F (\$5F) | I   | Т   | Н   | S   | V   | N   | Z   | С   | SREG |

| Read/Write  | R/W |      |

| 初期値         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

#### ■ ビット7 - I: 全割り込み許可 (Global Interrupt Enable)

全割り込み許可ビットは割り込みが許可されるために設定(1)されなければなりません。その時の個別割り込み許可制御は独立した制御レジスタで行われます。全割り込み許可ビットが解除(0)されると、個別割り込み許可設定に拘らず、どの割り込みも許可されません。I ビットは割り込みが起こった後にハードウェアによって解除(0)され、後続の割り込みを許可するために、RETI命令によって設定(1)されます。Iビットは「命令一式手引書」で記述されるようにSEIやCLI命令で応用(プログラム)によって設定(1)や解除(0)もできます。

#### ■ L'yh6 - T: L'yh変数 (Bit Copy Storage)

ビット複写命令、BLD(Bit LoaD)とBST(Bit STore)は操作したビットの転送元または転送先として、このTビットを使います。レジスタ ファイルのレジスタからのビットはBST命令によってTに複写でき、TのビットはBLD命令によってレジスタ ファイルのレジスタ内のビットに複写できます。

#### **■ ビット5 - H**: **ハーフキャリー フラク** (Half Carry Flag)

ハーフキャリー(H)フラグはいくつかの算術操作でのハーフキャリーを示します。ハーフキャリーはBCD演算に有用です。詳細情報については「<mark>命令要約</mark>」記述をご覧ください。

#### ■ ビット4 - S: 符号 (Sign Bit, S= N Ex-OR V)

Sフラグは常に負(N)フラグと2の補数溢れ(V)フラグの排他的論理和です。詳細情報については「命令要約」記述をご覧ください。

#### ■ ビット3 - V: 2の補数溢れフラグ(2's Complement Overflow Flag)

2の補数溢れ(V)フラグは2の補数算術演算を支援します。詳細情報については「命令要約」記述をご覧ください。

#### **■ Ľット2 - N**: **負フラク** (Negative Flag)

負(N)フラグは算術及び論理操作での負の結果(MSB=1)を示します。詳細情報については「命令要約」記述をご覧ください。

#### **■ L**"y**h1** - **Z** : **t**"**D 777** (Zero Flag)

ゼロ(Z)フラグは算術及び論理操作でのゼロ(0)の結果を示します。詳細情報については「**命令要約**」記述をご覧ください。

#### **■ L** \* **vb O O** : **キャリー フラク** \* (Carry Flag)

キャリー(C)フラグは算術及び論理操作でのキャリー(またはボロー)を示します。詳細情報については「**命令要約**」記述をご覧ください。

# 汎用レジスタファイル

このレシブスタファイルはAVRの増強したRISC命令群用に最適化されています。必要な効率と柔軟性を達成するために、次の入出力機構がレジスタファイルによって支援されます。

- ・1つの8ビット出力オペランドと1つの8ビットの結果入力

- ・2つの8ビット出力オペラントと1つの8ビットの結果入力

- ・2つの8ビット出力オペランドと1つの16ビットの結果入力

- ・1つの16ビット出力オペランドと1つの16ビットの結果入力

図4.はCPU内の32個の汎用作業レジスタの構造を示します。

レジスタファイルを操作する殆どの命令は全てのレジスタに直接アクセスし、それらの殆どは単一周期命令です。

図4.で示されるように各レジスタは使用者データ空間の最初の32位置へ直接的に配置することで、それらはデータメモリアドレスも割り当てられます。例え物理的にSRAM位置として実装されていなくてもX,Y,Zレジスタ(ポインタ)がレジスタファイル内のどのレジスタの指示にも設定できるように、このメモリ構成は非常に柔軟なレジスタのアクセスを提供します。

| 図4. AV      | R CPU 汎用レジスタ構り | <b></b> |                       |

|-------------|----------------|---------|-----------------------|

|             | 7 0            | アドレス    |                       |

|             | R0             | \$00    |                       |

|             | R1             | \$01    |                       |

|             | R2             | \$02    |                       |

|             | }              |         |                       |

|             | R13            | \$0D    |                       |

|             | R14            | \$0E    |                       |

| уп 🖽        | R15            | \$0F    |                       |

| 汎用<br>レシブスタ | R16            | \$10    |                       |

| ファイル        | R17            | \$11    |                       |

| , , ,       | }              |         |                       |

|             | R26            | \$1A    | Xレジスター 下位バイト<br>上位バイト |

|             | R27            | \$1B    | 上位バイト                 |

|             | R28            | \$1C    | マレンブファ 下位バイト          |

|             | R29            | \$1D    | 上化ハイト                 |

|             | R30            | \$1E    | フレンブスター 下位バイト         |

|             | R31            | \$1F    | 上位バイト                 |

## Xレシ、スタ、Yレシ、スタ、Zレシ、スタ

R26~R31レジスタには通常用途の使用にいくつかの追加機能があります。これらのレジスタはデータ空間の間接アトレス指定用の16ビットアトレスポインタです。3つのX,Y,Z間接アトレスレジスタは図5.で記載したように定義されます。

種々のアドレス指定種別で、これらのアドレス レジスタは固定変位、 自動増加、自動減少としての機能を持ちます(詳細については 「命令一式手引書」をご覧ください)。

| 図5. X,Y,Zレシ          | ゛スタ樟 | <b>「成図</b> |     |            |   |

|----------------------|------|------------|-----|------------|---|

|                      | 15   | XH (上位)    |     | XL (下位)    | 0 |

| X レジスタ               | 7    | R27 (\$1B) | 0 7 | R26 (\$1A) | 0 |

|                      | 15   | YH (上位)    |     | YL (下位)    | 0 |

| Y レシ <sup>*</sup> スタ | 7    | R29 (\$1D) | 0 7 | R28 (\$1C) | 0 |

|                      | 15   | ZH (上位)    |     | ZL (下位)    | 0 |

| Z レシ <sup>・</sup> スタ | 7    | R31 (\$1F) | 0 7 | R30 (\$1E) | 0 |

|                      |      |            |     |            |   |

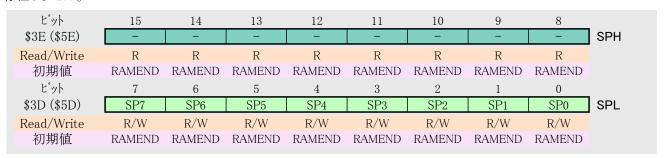

# ■ スタック ポインタ (Stack Pointer) SPL (SP)

スタックは主に一時データの保存、局所変数の保存、割り込みとサブルーチン呼び出し後の戻りアドレスの保存に使われます。スタック ポインタ レジスタは常にこのスタックの先頭(<mark>訳注</mark>:次に使われるべき位置)を指し示します。スタックが高位メモリから低位メモリへ伸長するように実行されることに注意してください。これはスタックへのPUSH命令はスタック ポインタを減少するという意味です。

スタック ポインタはサブルーチンや割り込みのスタックが配置されるデータSRAMのスタック領域を指し示します。データSRAM内のスタック空間はサブルーチン呼び出しの実行や割り込みの許可の何れにも先立ってプログラムによって定義されなければなりません。スタック ポインタは \$60以上を指示するように設定されなければなりません。スタック ポインタは PUSH命令でデータがスタックに格納されると-1され、サブルーチン呼び出しや割り込みで戻りアトンスがスタックに格納されると-2されます。スタック ポインタは POP命令でデータがスタックから引き出されると+1され、サブルーチンからの復帰(RET)命令や割り込みからの復帰(RETI)命令でアトンスがスタックから引き出されると+2されます。

AVRのスタック ポインタはI/O空間内の2つの8ビット レジスタとして実装されます。実際に使われるビット数は(そのデバイス)実装に依存します。SPLだけが必要とされる程に小さいAVR構造の実装(デバイス)のデータ空間もあることに注意してください。その場合、SPHレジスタは存在しません。

# 命令実行タイミング

本項は命令実行の一般的なアクセス タイミング の概念を記述します。AVR CPUはチップ(デバイス)用に選択したクロック元から直接的に生成したCPUクロック(clk<sub>CPU</sub>)によって駆動されます。内部クロック分周は使われません。

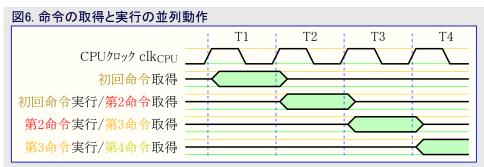

図6.はハーハート・構造と高速アクセスレジスタファイルの概念によって可能とされる並列の命令取得と命令実行を示します。これは機能対費用、機能対クロック、機能対電源部についての好結果と対応するMHzあたり1MIPSを達成するための基本的なパイプラインの概念です。

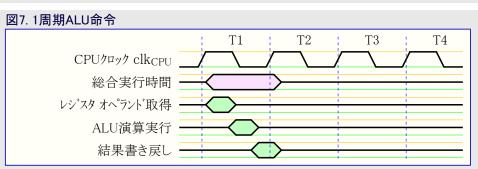

図7.はレシ、スタファイルに対する内部タイミンケの概念を示します。単一クロック周期で2つのレジ、スタオペラント、を使うALU操作が実行され、その結果が転送先レジ、スタへ書き戻されます。

# リセットと割り込みの扱い

AVRは多くの異なる割り込み元を提供します。これらの割り込みと独立したリセット ベクタ各々はプログラム メモリ空間内に独立したプログラム ベクタを持ちます。全ての割り込みは割り込みを許可するため、ステータス レジスタ(SREG)の全割り込み許可(I)ビットと共に論理1が書かれなければならない個別の許可ビットを割り当てられます。

プログラム メモリ空間の最下位アドレスは既定でリセットと割り込みへクタとして定義されます。 へクタの完全な一覧は29頁の「**割り込み**」で示されます。この一覧は各種割り込みの優先順位も決めます。 下位側アドレスがより高い優先順位です。 リセットが最高優先順位で、次が外部割り込み要求の(INTO)です。 より多くの情報については29頁の「割り込み」を参照してください。

割り込みが起こると全割り込み許可(I)ビットが解除(0)され、全ての割り込みは禁止されます。使用者ソフトウェアは多重割り込みを許可するため、全割り込み許可(I)ビットへ論理1を書けます。その後全ての許可した割り込みが現在の割り込みルーチンで割り込めます。全割り込み許可(I)ビットは割り込みからの復帰(RETI)命令が実行されると、自動的に設定(1)されます。

根本的に2つの割り込み形式があります。1つ目の形式は割り込み要求フラグを設定(I)する事象によって起動されます。これらの割り込みでは割り込み処理ルーチンを実行するために、プログラム カウンタは対応する現実の割り込みへ、クタを指示し、ハートウェアが対応する割り込み要求フラグを解除(0)します。割り込み要求フラグは解除(0)されるべきフラグのビット位置へ論理1を書くことによっても解除(0)できます。対応する割り込み許可ビットが解除(0)されている間に割り込み条件が起こると、割り込み要求フラグが設定(1)され、割り込みが許可されるか、またはこのフラグがソフトウェアによって解除(0)されるまで記憶(保持)されます。同様に、全割り込み許可(I)ビットが解除(0)されている間に1つまたはより多くの割り込み条件が起こると、対応する割り込み要求フラグが設定(1)されて全割り込み許可(I)ビットが設定(1)されるまで記憶され、その(I=1)後で優先順に従って実行されます。

2つ目の割り込み形式は割り込み条件が存在する限り起動し(続け)ます。これらの割り込みは必ずしも割り込み要求フラグを持っているとは限りません。割り込みが許可される前に割り込み条件が消滅すると、この割り込みは起動されません。

AVRが割り込みから抜け出すと常に主プログラムへ戻り、何れかの保留割り込みが扱われる前に1つ以上の命令を実行します。

ステータス レジスタ(SREG)は割り込みルーチンへ移行時の保存も、復帰時の再設定も自動的に行われないことに注意してください。これはソフトウェアによって扱われなければなりません。

割り込みを禁止するためにCLI命令を使うと、割り込みは直ちに禁止されます。CLI命令と同時に割り込みが起こっても、CLI命令後に割り込みは実行されません。次例は時間制限EEPROM書き込み手順中に割り込みを無効とするために、これがどう使えるかを示します。

| アセンブリ言語プログラム例                  |                                                                                                                      |                                                                                                                                    |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| IN<br>CLI<br>SBI<br>SBI<br>OUT | R16, SREG  EECR, EEMPE EECR, EEPE SREG, R16                                                                          | ;ステータスレジスタを保存<br>;EEPROM書き込み手順中割り込み禁止<br>;EEPROM主書き込み許可<br>;EEPROM書き込み開始<br>;ステータスレジスタを復帰                                          |

| C言語プログラム例                      |                                                                                                                      |                                                                                                                                    |

| cSREG<br>dis<br>EECR<br>EECR   | <pre>cSREG; = SREG; able_interrupt();  = (1&lt;<eempe); =="" csreg:<="" pre=""  ="(1&lt;&lt;EEPE);"></eempe);></pre> | /* ステータス レジ スタ保存変数定義 */ /* ステータス レジ スタを保存 */ /* EEPROM書き込み手順中割り込み禁止 */ /* EEPROM主書き込み許可 */ /* EEPROM書き込み開始 */ /* ステータス レジ スタを復帰 */ |

割り込みを許可するためにSEI命令を使うと、次例で示されるようにどの保留割り込みにも先立ってSEI命令の次の命令が実行されます。

| アセンブリ言語プログラム例       |                       |

|---------------------|-----------------------|

| SEI                 | ;全割り込み許可              |

| SLEEP               | ;休止形態移行(割り込み待ち)       |

| C言語プログラム例           |                       |

| enable_interrupt(); | /* 全割り込み許可 */         |

| sleep();            | /* 休止形態移行 (割り込み待ち) */ |

注: SLEEP命令までは割り込み禁止、保留割り込み実行前に休止形態へ移行します。

#### 割り込み応答時間

許可した全てのAVR割り込みに対する割り込み実行応答は最小4クロック周期です。4クロック周期後、実際の割り込み処理ルーチンに対するプログラム ベクタ アドレスが実行されます。この4クロック周期時間中にプログラム カウンタ(PC)がスタック上に保存(プッシュ)されます。このベクタは標準的に割り込み処理ルーチンへの無条件分岐で、この分岐は2クロック周期(記主:原文は3(JMP命令=3を想定、実際はRJMP命令=2))要します。複数周期命令実行中に割り込みが起こると、その割り込みが扱われる前に、この命令が完了されます。MCUが休止形態の時に割り込みが起こると、割り込み実行応答時間は4クロック周期増やされます。この増加は選択した休止形態からの起動時間に加えてです。

割り込み処理ルーチンからの復帰は4クロック周期要します。これらの4クロック周期中、プログラム カウンタ(PC:2バイト)がスタックから取り戻され(ポップ)、スタック ポープンタは増加され(+2)、ステータス レジ、スタ(SREG)の全割り込み許可(I)ビットが設定(1)されます。

# AVR ATtiny2313のメモリ

この項はATtiny2313の各種メモリを記述します。AVR構造にはプログラムメモリ空間とデータメモリ空間の2つの主なメモリ空間があります。加えてATtiny2313はデータ保存用EEPROMメモリが特徴です。3つのメモリ空間全ては一般的な直線的アトレスです。

# 実装書き換え可能なプログラム用フラッシュメモリ

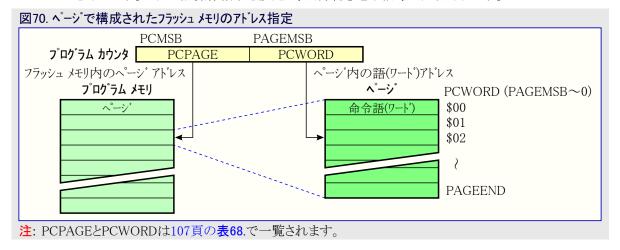

ATtiny2313はプログラム保存用に実装書き換え可能な2Kバイトのフラッシュ メモリをチップ上に含みます。全てのAVR命令が16または32ビット幅のため、このフラッシュ メモリは1K×16ビットとして構成されます。

フラッシュ メモリは最低10,000回の消去/書き込み回数の耐久性があります。ATtiny2313のプログラム カウンタ(PC)は10ビット幅、故に1Kプログラム メモリ位置のアトレス指定です。<math>106頁の「メモリプログラミング」はSPIピンを使うフラッシュ メモリの直列プログラミングの詳細な記述を含みます。

定数表は全てのプログラム メモリ アドレス空間に配置できます。(LPM命令記述参照)

命令の取得と実行のタイミング図は9頁の「命令実行タイミング」で示されます。

# 図8. プログラム メモリ配置図 プログラム用 フラッシュ メモリ 1K×16 \$03FF

# データ用SRAM メモリ

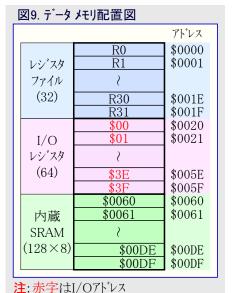

図9.はATtiny2313のSRAMメモリ構成方法を示します。

下位224データメモリ位置はレシ、スタファイル、I/Oメモリ、内蔵データSRAMに充てます。最初の32位置はレシ、スタファイル、次の64位置は標準I/Oメモリに充て、最後の128位置は内蔵データSRAMに充てます。

直接、間接、変位付き間接、事前減少付き間接、事後増加付き間接の5つの異なるアトレス指定種別でデータ メモリ(空間)を網羅します。レジスタファイル内のレジスタR26~R31は間接アトレス指定ポインタ用レジスタが特徴です。

直接アドレス指定はデータ空間全体に届きます。

変位付き間接動作はYまたはZレシ、スタで与えられる基準アト、レスからの63アト、レス位置に届きます。

自動の事前減少付きと事後増加付きのレシ、スタ間接アト、レス指定動作を使う時に(使われる)X, Y,Zアト・レス レジ、スタは減少(-1)または増加(+1)されます。

ATtiny2313の32個の汎用レジスタ、64個のI/Oレジスタ、128バイトのデータ用内蔵SRAMはこれら全てのアドレス指定種別を通して全部アクセスできます。レジスタファイルは8頁の「汎用レジスタファイル」で記述されます。

#### データ メモリ アクセス タイミング

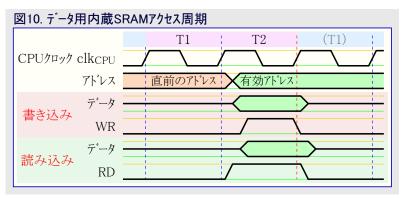

この項は内部メモリ アクセスに対する一般的なアクセス タイミングの概念を記述します。 データ用内蔵SRAMアクセスは図10.で記載されるように2clkcpu周期で実行されます。

(訳注) 内蔵SRAMのアクセスを含む代表的な命令はT1,T2の 2周期で実行され、T1で対象アトレスを取得/(算出)/ 確定し、T2で実際のアクセスが行われます。後続する (T1)は次の命令のT1です。

# データ用EEPROMメモリ

ATtiny2313は128バイトのデータ用EEPROMを含みます。それは単一バイトが読み書きできる分離したデータ空間として構成されます。EE PROMは最低100,000回の消去/書き込み回数の耐久性があります。CPUとEEPROM間のアクセスは以降のEEPROMアドレス レジスタ、EEPROMฅ゙ータ レジスタ、EEPROM制御レジスタで詳細に記述されます。EEPROMの直列プログラミングの詳細な記述については115頁をご覧ください。

#### **EEPROMアクセス**

EEPROMアクセスレジスタはI/O空間でアクセス可能です。

EEPROMの消去/書き込み(<mark>訳注</mark>:原文はアクセス)時間は表1.で与えられます。(書き込みは)自己タイング機能ですが、使用者ソフトウェアは次パイが書ける時を検知してください。使用者コートがEEPROMに書く命令を含む場合、いくつかの予防処置が取られなければなりません。厳重に濾波した電源では電源投入/切断でVCCが緩やかに上昇または下降しそうです。これはデバイスが何周期かの時間、使われるクロック周波数に於いて最小として示されるより低い電圧で走行する原因になります。これらの状態で問題を避ける方法の詳細については14頁の「EEPROMデータ化けの防止」をご覧ください。

予期せぬEEPROM書き込みを防止するため特別な書き込み手順に従わなければなりません。この詳細についてはEEPROM制御レジスタの説明と13頁の「非分離バー書き込み」と「分離バー書き込み」を参照してください(訳注:本行内容追加)。

EEPROMが読まれると、CPUは次の命令が実行される前に4クロック周期停止されます。EEPROMが書かれると、CPUは次の命令が実行される前に2クロック周期停止されます。

#### ■ EEPROMアトレス レシ、スタ (EEPROM Address Register) EEAR

| ピット         | 7 | 6     | 5     | 4     | 3     | 2     | 1     | 0     |      |

|-------------|---|-------|-------|-------|-------|-------|-------|-------|------|

| \$1E (\$3E) | - | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEAR |

| Read/Write  | R | R/W   |      |

| 初期値         | 0 | 不定    |      |

#### ■ **ビット7** - **Res** : 予約 (Reserved)

このビットは予約されており、常に0として読まれます。

#### ■ ビット6~0 - EEAR6~0: EEPROMアドレス (EEPROM Address)

EEPROMアドレス レジスタ(EEAR)は128バイトEEPROM空間のEEPROMアドレスを指定します。EEPROMデータ バイトは0~127間で直線的に配されます。EEARの初期値は不定です。EEPROMがアクセスされるであろう前に適切な値が書かれなければなりません。

## ■ EEPROMデータレジスタ (EEPROM Data Register) EEDR

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |      |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|------|

| \$1D (\$3D) | (MSB) |     |     |     |     |     |     | (LSB) | EEDR |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |      |

| 初期値         | 不定    | 不定  | 不定  | 不定  | 不定  | 不定  | 不定  | 不定    |      |

#### ■ ビット7~0 - EEDR7~0: EEPROMデータ (EEPROM Data)

EEPROM書き込み操作に対してEEDRはEEPROMアドレス レジスタ(EEAR)で与えたアドレスのEEPROMへ書かれるべきデータを含みます。 EEPROM読み込み操作に対してEEDRはEEARで与えたアドレスのEEPROMから読み出したデータを含みます。

#### ■ **EEPROM制御レジスタ** (EEPROM Control Register) **EECR**

| ピット         | 7 | 6 | 5     | 4     | 3     | 2     | 1    | 0    |      |

|-------------|---|---|-------|-------|-------|-------|------|------|------|

| \$1C (\$3C) | - | - | EEPM1 | EEPM0 | EERIE | EEMPE | EEPE | EERE | EECR |

| Read/Write  | R | R | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  |      |

| 初期値         | 0 | 0 | 不定    | 不定    | 0     | 0     | 不定   | 0    |      |

#### ■ ビット7.6 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

#### ■ ビット5.4 - EEPM1.0: EEPROMプログラミング種別(EEPROM Programing Mode Bits)

EEPROMプログラミング種別ビット設定はEEPROMプログラミング 種別ビット設定はEEPROMプログラミング 種別グラミング 普列 グラミング 許可(EEPE)書き込み時にどのプログラミング 動作が起動されるかを定義します。1つの非分離操作(旧値消去と新値書き込み)、または2つの異なる操作として消去と書き込み操作を分離してデータをプログラムする(書く)ことが可能です。各動作に対するプログラミング 時間は表1.で示されます。EEPEが設定(1)されている間はEEPMnへのどの書き込みも

| 表1. EE | 表1. EEPROM7 ロク フミンク 種別 |                 |                     |  |  |  |  |  |  |  |

|--------|------------------------|-----------------|---------------------|--|--|--|--|--|--|--|

| EEPM1  | EEPM0                  | Mo プログラミング時間 動作 |                     |  |  |  |  |  |  |  |

| 0      | 0                      | 3.4ms           | 1操作での消去と書き込み(非分離操作) |  |  |  |  |  |  |  |

| 0      | 1                      | 1.8ms           | 消去のみ                |  |  |  |  |  |  |  |

| 1      | 0                      | 1.8ms           | 書き込みのみ              |  |  |  |  |  |  |  |

| 1      | 1                      | _               | 将来使用に予約             |  |  |  |  |  |  |  |

|        |                        |                 |                     |  |  |  |  |  |  |  |

無視されます。リセット中、EEPMnビットはEEPROMがプログラミング作業中を除いて'00'にリセットされます。

#### ■ ビット3 - EERIE: EEPROM操作可割り込み許可(EEPROM Ready Interrupt Enable)

EERIEの1書き込みはステータスレジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されているなら、EEPROM操作可割り込みを許可します。EERIEの0書き込みは、この割り込みを禁止します。EEPROM操作可割り込みは不揮発性メモリ(フラッシュ メモリとEEPROM)がプログラミングの準備可ならば継続する割り込みを発生します。

#### ■ ビット2 - EEMPE: EEPROM主プログラム許可 (EEPROM Master Program Enable)

EEMPEL'ットはEEPROMプログラム許可(EEPE)ヒットの1書き込みが有効か無効かどちらかを決めます。

EEMPEが設定(1)されると、4クロック周期内のEEPE設定(1)は選択したアドレスのEEPROMをプログラムします。EEMPEが0なら、EEPE設定(1)は無効です。EEMPEがソフトウェアによって設定(1)されてしまうと、4クロック周期後にハードウェアがこのビットを0に解除します。

#### ■ ビット1 - EEPE: EEPROMプログラム許可(EEPROM Program Enable)

EEPROMプログラム許可信号(EEPE)はEEPROMへのプログラミング許可信号です。EEPEが(1を)書かれると、EEPROMはEEPMnビット設定に従ってプログラムされます。論理1がEEPEへ書かれる前にEEPROM主プログラム許可(EEMPE)ビットは1を書かれなければならず、さもなくばEEPROM書き込み(消去)は行われません。書き込み(プログラミング)アクセス時間が経過されると、EEPROMプログラム許可(EEPE)ビットはハードウェアによって解除(0)されます。EEPEが設定(1)されてしまうと、次の命令が実行される前にCPUは2周期停止されます。

#### ■ ビット0 - EERE: EEPROM読み込み許可(EEPROM Read Enable)

EEPROM読み込み許可信号(EERE)はEEPROMへの読み込みストローフです。EEARに正しいアトレスが設定されると、EEPROM読み出しを起動するためにEEREビットは1を書かれなければなりません。EEPROM読み出しアクセスは(その)1命令で行われ、要求したデータは直ちに利用できます。EEPROMが読まれるとき、次の命令が実行される前にCPUは4周期停止されます。使用者は読み込み操作を始める前にEEPEビットをポーリングすべきです。書き込み(プログラム)操作実行中の場合、EEPROMアトレスレジスタ(EEAR)の変更もEEPROM読み込みもできません。

# 非分離バイトプログラミング

非分離バイト プログラミングの使用は最も簡単な動作です。EEPROMにバイトを書くとき、使用者はEEARにアドレス、EEDRにデータを書かなければなりません。EEPMnビットが'00'ならば、(EEMPEが1を書かれる後の4周期内の)EEPEの1書き込みは消去/書き込み動作を起動します。消去と書き込みの両周期は1操作で行われ、総プログラミング時間は表1.で与えられます。EEPEビットは消去と書き込み動作が完了されるまで設定(1)に留まります。デバイスがプログラミング動作中、他のどのEEPROM操作の実行も不可能です。

#### 分離バイトプログラミング

2つの異なる操作として消去と書き込み周期を分離することが可能です。これは或る時間制限(代表的には電源電圧不足)に対してシステムが短いアクセス時間を必要とする場合に有用かもしれません。この方法の優位性を得るため、書かれるべき位置が書き込み操作前に消去されてしまっていることが必要とされます。しかし、消去と書き込みが分離されるため、時間が重大な操作の実行をシステムが許す時(代表的には電源投入後)に消去操作を行うことが可能です。

# 消去

ハイトを消去するにはアトレスがEEARに書かれなければなりません。EEPMnビットが'01'なら、(EEMPEが1を書かれた後の4周期内の) EEPEの1書き込みは消去動作だけを起動します(プログラミング時間は表1.で与えられます)。EEPEビットは消去動作が完了されるまで設定(1)に留まります。デバイスがプログラミング動作中、他のどのEEPROM操作の実行も不可能です。

## 書き込み

(特定)位置を書くため、使用者はEEARにアトンス、EEDRにデータを書かなければなりません。EEPMnビットが'10'なら、(EEMPEが1を書かれる後の4周期内の)EEPEの1書き込みは書き込み動作だけを起動します(プログラミング時間は表1.で与えられます)。EEPEビットは書き込み動作が完了されるまで設定(1)に留まります。書かれるべき位置が書き込み前に消去されてしまっていなければ、元の格納データは失ったと見做されなければなりません。デバイスがプログラミング動作中、他のどのEEPROM操作の実行も不可能です。

EEPROMアクセスの時間に校正済み内蔵RC発振器が使われます。発振器周波数が18頁の「**発振校正レジスタ - OSCCAL**」で記述した必要条件内であることを確かめてください。

次のコート・例はアセンブリ言語とC言語でのEEPROM消去、書き込み、または非分離書き込み関数を示します。本例は(例えば全割り込み禁止によって)割り込みが制御され、これらの関数実行中に割り込みが起きない前提です。

```

アセンブリ言語プログラム例

EEPROM_WR:

;EEPROMプログラミング完了ならばスキップ

SBIC

EECR, EEPE

RJMP

EEPROM WR

;以前のEEPROMプログラミング完了まで待機

R18, (0<<EEPM1) | (0<<EEPM0)

LDI

;プログラミング種別値取得(本例は非分離)

;対応プログラミング種別設定

EECR, R18

OUT

OUT

EEAR, R17

;EEPROMアドレス設定

;EEPROM書き込み値を設定

OUT

EEDR, R16

;EEPROM主プログラム許可ビット設定

SBI

EECR, EEMPE

;EEPROMプログラミング開始(プログラム許可ビット設定)

SBI

EECR, EEPE

;呼び出し元へ復帰

RET

C言語プログラム例

void EEPROM_write(unsigned char ucAddress, unsigned char ucData)

while (EECR & (1<<EPE));

/* 以前のEEPROMプログラミング完了まで待機 */

EECR = (0 << EEPM1) \mid (0 << EEPM0);

/* 対応プログラミング種別設定 */

/* EEPROMアドレス設定*/

EEAR = ucAddress;

EEDR = ucData;

/* EEPROM書き込み値を設定 */

EECR = (1 < EEMPE);

/* EEPROM主プログラム許可*/

/* EEPROMプログラミング開始*/

EECR \mid = (1 << EEPE);

```

次のコート・例はアセンブリ言語とC言語でのEEPROM読み込み関数を示します。本例は割り込みが制御され、これらの関数実行中に割り込みが起きない前提です。

```

アセンブリ言語プログラム例

;EEPROMプログラミング完了ならばスキップ

EEPROM RD:

SBIC

EECR, EEPE

EEPROM RD

;以前のEEPROMプログラミング完了まで待機

R.JMP

OUT

EEAR, R17

;EEPROMアトレス設定

;EEPROM読み出し開始(読み込み許可ビット設定)

SBI

EECR, EERE

;EEPROM読み出し値を取得

ΙN

R16, EEDR

RET

;呼び出し元へ復帰

C言語プログラム例

unsigned char EEPROM read(unsigned char ucAddress)

while (EECR & (1<<EPE));

/* 以前のEEPROMプログラミング完了まで待機 */

EEAR = ucAddress;

/* EEPROMアドレス設定*/

EECR = (1 < EERE);

/* EEPROM読み出し開始 */

/* EEPROM読み出し値を取得,復帰 */

return EEDR;

}

```

# EEPROMデータ化けの防止

低VCCの期間中、正しく動作するための供給電圧がCPUとEEPROMに対して低すぎるためにEEPROMデータが化け得ます。これらの問題はEEPROMを使う基板段階の装置と同じで、同じ設計上の解決策が適用されるべきです。

EEPROMデータ化けは電圧が低すぎる時の2つの状態によって起こされ得ます。1つ目として、EEPROMへの通常の書き込み手順は正しく動作するための最低電圧が必要です。2つ目として、供給電圧が低すぎると、CPU自身が命令を間違って実行し得ます。

EEPROMデータ化けは次の推奨設計によって容易に避けられます。

不充分な供給電源電圧の期間中、AVRのRESETを活性(Low)に保ってください。これは内蔵低電圧検出器(BOD)を許可することによって行えます。内蔵BODの検出電圧が必要とした検出電圧と一致しない場合、外部低VCCリセット保護回路が使えます。書き込み動作実行中にリセットが起こると、この書き込み操作は供給電源電圧が充分ならば(継続)完了されます。

# I/O メモリ (レジスタ)

ATtiny2313のI/O空間定義は141頁の「レジスタ要約」で示されます。

ATtiny2313の全てのI/Oと周辺機能はI/O空間に配置されます。全てのI/O位置はI/O空間と32個の汎用作業レシ、スタ間のデータ転送を行うLD/LDS/LDD命令とST/STS/STD命令によってアクセスされます。アトレス範囲\$00~\$1F内のI/Oレシ、スタはSBI命令とCBI命令の使用で直接的にビットアクセス可能です。これらのレシ、スタではSBISとSBIC命令の使用によって単一ビット値が検査できます。より多くの詳細については「命令要約」章を参照してください。I/O指定命令INとOUTを使う時はI/Oアトレス\$00~\$3Fが使われなければなりません。LD命令とST命令を使い、データ空間としてI/Oレシ、スタをアクセスする時はこれらのアトレスに\$20が加算されなければなりません。

将来のデバイスとの共通性を保つため、アクセスされる場合、予約ビットはOが書かれるべきです。予約済みI/Oメモリ アドレスは決して書かれるべきではありません。

状態フラグのいくつかはそれらへ論理1を書くことによって解除(0)されます。CBIとSBI命令は他の多くのAVRの様ではなく、指定ビットだけを操作し、従って状態フラグのようなものを含むレジスタに使えることに注意してください。CBIとSBI命令は(I/Oアドレス)\$00~\$1Fのレジスタでのみ動作します。

I/Oと周辺制御レジスタは以降の項で説明されます。

# 汎用I/Oレジスタ

ATtiny2313は3つの汎用I/Oレシ、スタを含みます。これらのレシ、スタはどの情報の格納にも使え、特に全体変数や状態フラケの格納に有用です。(I/O)アドレス範囲\$00~\$1Fの汎用I/Oレシ、スタはSBI,CBI,SBIS,SBIC命令の使用で直接ビットアクセスが可能です。

## ■ 汎用I/Oレジスタ2 (General Purpose I/O Register 2) GPIOR2

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |        |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$15 (\$35) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR2 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

#### ■ 汎用I/Oレジスタ1 (General Purpose I/O Register 1) GPIOR1

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     | _      |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$14 (\$34) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR1 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

# ■ 汎用I/OレジスタO (General Purpose I/O Register 0) GPIORO

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |        |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$13 (\$33) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR0 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

# システム クロックとクロック選択

# クロック系統とその配給

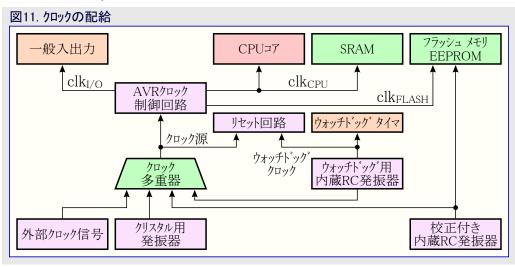

図11.はAVR内の主要なクロック系統とその配給を示します。全てのクロックが与えられた時間有効である必要はありません。消費電力低減のため、21頁の「電力管理と休止形態」で記述される各種休止形態の使用によって、使われていない部分のクロックが停止できます。クロック系統は以下で詳述されます。

#### CPU クロック - clk<sub>CPU</sub>

CPUクロックはAVRコアの動作と関係する系統の部分に配給されます。このような部分の例は汎用レジスタ ファイル、ステータス レジスタ、スタック ポインタを保持するデータ メモリです。CPUクロックの停止はコアが一般的な操作や計算を実行することを禁止します。

#### I/O クロック - clk<sub>I/O</sub>

I/Oクロックはタイマ/カウンタやUSARTのようなI/O部の大部分で使われます。I/Oクロックは外部割り込み部でも使われますが、いくつかの外部割り込みは例えI/Oクロックが停止されても検出されることをこのような割り込みに許す非同期論理回路によって検出されることに注意してください。多用途直列(USI)部の開始条件検出はclk<sub>I/O</sub>が停止される時に非同期に実行され、全休止形態でUSI開始条件検出を可能とすることにも注意してください。

#### フラッシュ クロック - clk<sub>FLASH</sub>

フラッシュ クロックはフラッシュ メモリ インターフェースの動作を制御します。このフラッシュ クロックは常にCPUクロックと同時に活動します。

#### クロック元

このデバイスには右で示されるようにフラッシュ ヒュース ビットによって選択可能な後続のクロック元選択があります。選択したクロック元からのクロックはAVRクロック発生器への入力で、適切な単位部へ配給されます。

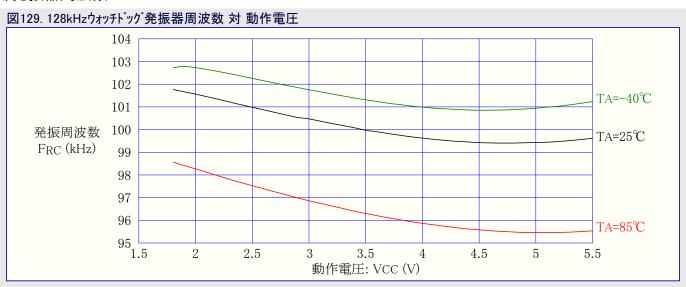

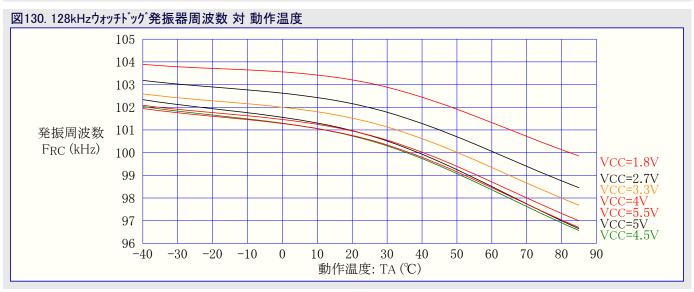

各クロック選択に対する様々な選択は次項で得られます。CPUがハ<sup>o</sup>ワーダウンから起動するとき、選択したクロック元は命令実行開始前に安定な発振器動作を保証する起動時間に使われます。CPUがリセットから始まるとき、これらは通常動作開始前に安定電圧へ達するのを電源に許す付加遅延です。ウォッチトゥグ発振器は、この起動時間の実時間部のタイミングに使われます。各計時終了に使われるウォッチトゥグ(WDT)発振器の各周期数は表3.で示されます。121頁の「代表特性」で示されるようにウォッチトゥグ発振器の周波数は電圧に依存します。

| 表2. クロック種別選択          |           |  |  |  |  |

|-----------------------|-----------|--|--|--|--|

| クロック種別                | CKSEL3~0  |  |  |  |  |

| 外部クリスタル/セラミック発振子      | 1111~1000 |  |  |  |  |

| 128kHz内部(WDT)発振器      | 0110      |  |  |  |  |

| 8MHz校正付き内蔵RC発振器       | 0100      |  |  |  |  |

| 4MHz校正付き内蔵RC発振器       | 0010      |  |  |  |  |

| 外部クロック信号              | 0000      |  |  |  |  |

| (予約)                  | 0xx1      |  |  |  |  |

| 注・1=非プログラム ∩=プログラム v= | ·∩キた/ナ1   |  |  |  |  |

<u>注: 1=非プログラム、0=プログラム、x=0または1</u>

| 表3. WDT発振器の代表的計時終了値、周期数 |       |           |  |  |

|-------------------------|-------|-----------|--|--|

| VCC=3.0V                | 周期数   |           |  |  |

| 4.3ms                   | 4.1ms | 512       |  |  |

| 69ms                    | 65ms  | 8K (8192) |  |  |

## 既定のクロック元

このデバイスはCKSEL=0100, SUT=10, CKDIV8=プログラム(0)で出荷されます。従って既定クロック元設定は最長起動時間の8MHzで走行する内蔵RC発振器を8で前置分周し、結果として1MHzに帰着する初期システム クロックです。この既定設定は全ての使用者が実装または並列書き込み器を使って、それらを希望したクロック元設定にできることを保証します。

# クリスタル用発振器

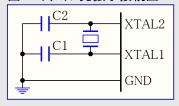

XTAL1とXTAL2は**図12**.で示されるように、チップ上の発振器としての使用に設定できる反転増幅器の各々、入力と出力です。クリスタル発振子またはセラミック振動子のどちらでも使えます。

C1とC2はクリスタル発振子とセラミック振動子の両方について常に等しくすべきです。このコンデンサの最適値は使うクリスタル発振子やセラミック振動子、浮遊容量の量、その環境の電磁雑音に依存します。クリスタル発振子使用に対するコンデンサ選択について初期の指針のいくつかは表4.で与えられます。セラミック振動子については製造業者によって与えられたコンデンサ値が使われるべきです。

発振器は示された周波数範囲で最適化された4つの異なる動作ができます。この動作は、表4.で示されたCKSEL3~1ヒューズによって選択されます。

# 図12. クリスタル発振子接続図

# 表4. クリスタル用発振器動作

| CKSEL3~1 | 周波数範囲      | 推奨C1,2容量 |

|----------|------------|----------|

| 100 (注)  | 0.4~0.9MHz | -        |

| 101      | 0.9~3.0MHz | 12∼22pF  |

| 110      | 3.0~8.0MHz | 12∼22pF  |

| 111      | 8.0∼ MHz   | 12∼22pF  |

**注**: この選択はクリスタル発振子ではなく、セラミック 振動子でのみ使われるべきです。

CKSEL0ヒュース'はSUT1,0ヒュース'と共に、表5.で示される起動遅延時間を選択します。

# 表5. クリスタル発振子/セラミック振動子用起動遅延時間選択表

| 10. / //// | 33. 分为水光振于/ 67.5分振到于用起到连延时间选扒衣 |                      |                              |                             |  |  |  |  |

|------------|--------------------------------|----------------------|------------------------------|-----------------------------|--|--|--|--|

| CKSEL0     | SUT1,0                         | パワーダウンからの<br>起動遅延時間  | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法                       |  |  |  |  |

|            | 0 0                            | 258×CK ( <b>注1</b> ) | $14 \times \text{CK+4.1ms}$  | 外部セラミック振動子、高速上昇電源           |  |  |  |  |

| 0          | 0 1                            | 258×CK ( <b>注1</b> ) | $14 \times \text{CK+65ms}$   | 外部セラミック振動子、低速上昇電源           |  |  |  |  |

| U          | 1 0                            | 1K×CK ( <b>注2</b> )  | 14×CK                        | 外部セラミック振動子、低電圧検出(BOD)リセット許可 |  |  |  |  |

|            | 1 1                            | 1K×CK ( <b>注2</b> )  | $14 \times \text{CK+4.1ms}$  | 外部セラミック振動子、高速上昇電源           |  |  |  |  |

|            | 0 0                            | 1K×CK ( <b>注2</b> )  | $14 \times \text{CK+65ms}$   | 外部セラミック振動子、低速上昇電源           |  |  |  |  |

| 1          | 0 1                            | 16K×CK               | 14×CK                        | 外部クリスタル発振子、低電圧検出(BOD)リセット許可 |  |  |  |  |

| 1          | 1 0                            | 16K×CK               | $14 \times \text{CK+4.1ms}$  | 外部クリスタル発振子、高速上昇電源           |  |  |  |  |

|            | 1 1                            | 16K×CK               | 14×CK+65ms                   | 外部クリスタル発振子、低速上昇電源           |  |  |  |  |

**注1**: これらの選択はデバイスの最高周波数付近での動作でないとき、応用にとって起動での周波数安定性が重要でない場合だけ使われるべきです。これらの選択はクリスタル発振子用ではありません。

**注2**: これらの選択はセラミック振動子での使用を意図され、起動での周波数安定性を保証します。デバイスの最高周波数付近での動作でないとき、応用にとって起動での周波数安定性が重要でない場合はクリスタル発振子も使えます。

# 校正付き内蔵RC発振器 (訳注:共通性のため内容を一部追加/修正)

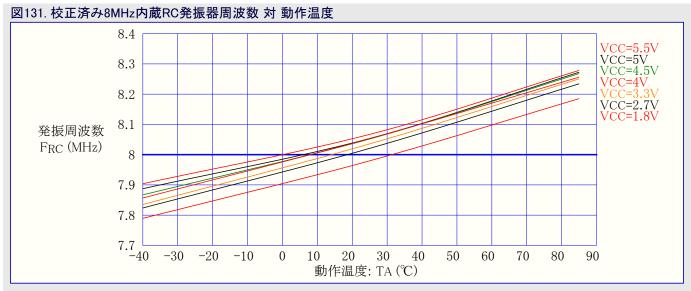

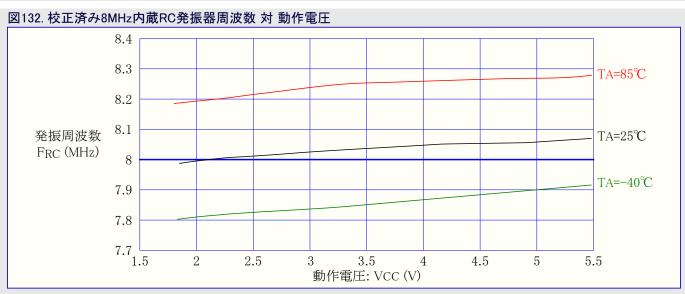

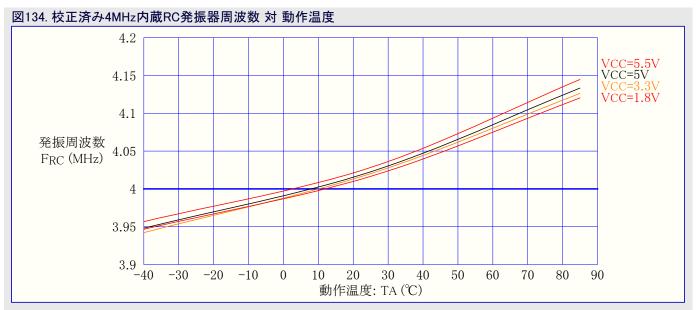

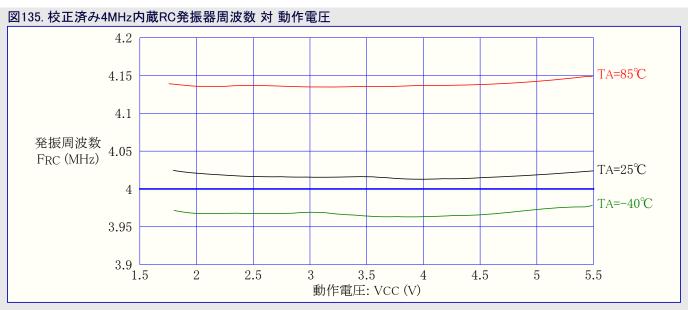

校正された内蔵RC発振器は8MHzまたは4MHzクロックを供給します。この周波数は 3V,25℃での公称値です。この周波数が(VCCに依存して)デバイスの仕様を越える場 合、起動中に内部周波数を8分周するためにCKDIV8ヒューズがプログラム(0)されなけれ ばなりません。より多くの詳細については20頁の「システム クロック前置分周器」をご覧く ださい。このクロックは表6.で示されるようにCKSELヒュース、のプログラミングによってシステムク ロックとして選択できます。 選択したなら、外部部品なしで動作します。 リセット中、ハート **注1**: デバイスはこの選択で出荷されます。

| 表6. 校正付き内蔵RC発振器動作 |

|-------------------|

|-------------------|

| CKSEL3~0 | 公称周波数 (MHz) |

|----------|-------------|

| 0 1 0 0  | 8.0 (注1)    |

| 0 0 1 0  | 4.0         |

ウュアが発振校正レジスタ(OSCCAL)に校正値バイトを設定し、これによってRC発振器を自動的に校正します。 3V,25℃でこの校正は公 称周波数±10%以内の周波数を与えます。atmel.com/avrで利用可能な応用記述に記載された実行時校正法の使用で、与えられた どのVCCと温度でも±2%の精度を達成することができます。この発振器がチップ(システム)クロックとして使われるとき、ウォッチト・ッケ発振器は 未だウォッチドッグタイマとリセット付加遅延タイマに使われます。予め設定された校正値のより多くの情報については、107頁の「**校正バイト**」 項をご覧ください。このデバイスはCKDIV8ヒュースがプログラム(0)で出荷されます。

この発振器が選択されると、起動時間は表7.で示されるようにSUTヒューズによって決定されます。

#### 表7. 校正付き内蔵RC発振器用起動遅延時間選択表

| SUT1,0            | パワーダウンからの<br>起動遅延時間 | リセットからの<br>付加遅延時間          | 推奨使用法            |  |  |

|-------------------|---------------------|----------------------------|------------------|--|--|

| 0 0               | 6×CK                | 14×CK ( <b>注1</b> )        | 低電圧検出(BOD)リセット許可 |  |  |

| 0 1               | 6×CK                | 14×CK+4.1ms                | 高速上昇電源           |  |  |

| 1 0 ( <b>注2</b> ) | 6×CK                | $14 \times \text{CK+65ms}$ | 低速上昇電源           |  |  |

| 1 1               | (予約)                |                            |                  |  |  |

注1: RSTDISBLヒューズがプログラム(0)されると、プログラミング動作への移行可を保証するため、付加遅延時間は14×CK+4msに増や されます。

注2: デバイスはこの選択で出荷されます。

# ■ 発振校正レジスタ (Oscillator Calibration Register) OSCCAL

| ピット         | 7 | 6    | 5    | 4    | 3      | 2    | 1    | 0    | _      |

|-------------|---|------|------|------|--------|------|------|------|--------|

| \$31 (\$51) | _ | CAL6 | CAL5 | CAL4 | CAL3   | CAL2 | CAL1 | CAL0 | OSCCAL |

| Read/Write  | R | R/W  | R/W  | R/W  | R/W    | R/W  | R/W  | R/W  |        |

| 初期値         | 0 |      |      | デバ   | 42固有の校 | 正値   |      |      |        |

■ ビット7 - Res: 予約 (Reserved) (訳注:共通性のため追加)

このビットは予約されており、常に0として読まれます。

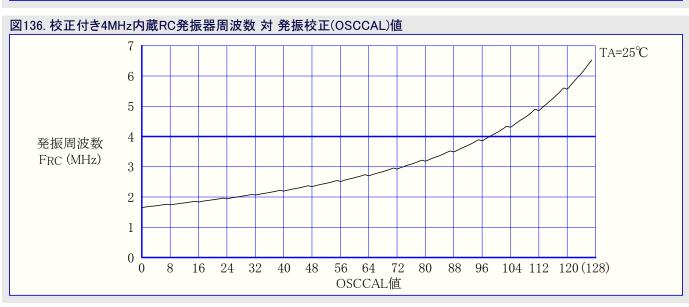

#### ■ ビット6~0 - CAL6~0:発振校正値 (Oscillator Calibration Value)

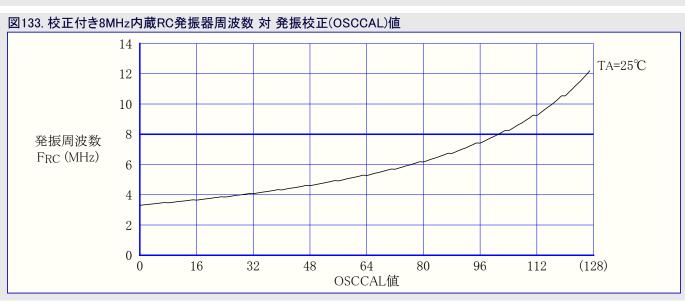

このアドレスへの校正バイト書き込みは発振器周波数の偏差処理を省くために内蔵 発振器を調整します。これはチップ リセット中、自動的に行われます。OSCCALが0の 時に最低利用可能周波数が選択されます。このレシブスタへ0以外の値を書くことは 内蔵発振器の周波数を増加します。このレジスタへの\$7F書き込みは最高使用可能 周波数にします。校正付き発振器はフラッシュメモリとEEPROMのアクセス時間に使われ ます。フラッシュ メモリやEEPROMが書かれる場合、公称周波数より上へ10%を越えて 校正してはいけません。そうでなければフラッシュ メモリやEEPROM書き込みは失敗 するかもしれません。この発振器は8MHzまたは4MHzへの校正を意図したもので あることに注意してください。表8.で示されるような他の値への調整は保証されません。

| ± ^ | # # 00 | <b>2</b> 6 4⊏ BB 6 | 事 2世 樂 | - 445 IIII |

|-----|--------|--------------------|--------|------------|

| ÆX  | 内蔵RC   | 至 振 态 l            | 引冷外    | * 审门  开    |

| OSCCAL値 | 公称周波数に対する割合 |       |  |  |

|---------|-------------|-------|--|--|

| USUCAL恒 | 最小          | 最大    |  |  |

| \$00    | 50 %        | 100 % |  |  |

| \$3F    | 75 %        | 150 % |  |  |

| \$7F    | 100 %       | 200 % |  |  |

校正付き内蔵RC発振器を校正するとき、MCUの安定な動作を保証するために大きな段階での校正値変更を避けてください。或るク ロック周期から次への2%より大きな周波数変化は予測されない事態を引き起こします。OSCCAL変更は各校正について\$20を越える べきではありません。

# 外部クロック信号

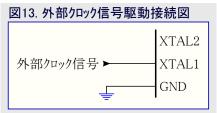

ます。

外部クロック元からデバイスを駆動するためにXTAL1は 図13.で示されるように駆動されるべきです。外部クロックでデバイスを走行するためにはCKSELヒュースが '0000'にプログラム(設定)されなければなりません。

| 表9. 外部クロック信号動作 |         |  |  |  |

|----------------|---------|--|--|--|

| CKSEL3~0       | 周波数範囲   |  |  |  |

| 0 0 0 0        | 0∼16MHz |  |  |  |

'0000'にプログラム(設定)されなければなりません。

このクロック元が選択されると、起動時間は**表10**.で示されるようにSUTヒューズによって決定され

| 表10    | 外部カロック   | 信号取制   | 田記動渥   | 延時間選択表 |

|--------|----------|--------|--------|--------|

| 1X IU. | フトロロノロノノ | 16 与敝野 | 川川に当川年 | 些时间选为农 |

| SUT1,0 | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法            |  |  |  |  |  |

|--------|---------------------|------------------------------|------------------|--|--|--|--|--|

| 0 0    | 6×CK                | 14×CK                        | 低電圧検出(BOD)リセット許可 |  |  |  |  |  |

| 0 1    | 6×CK                | 14×CK+4.1ms                  | 高速上昇電源           |  |  |  |  |  |

| 1 0    | 6×CK                | 14×CK+65ms                   | 低速上昇電源           |  |  |  |  |  |

| 11     | (予約)                |                              |                  |  |  |  |  |  |

外部クロックを供給するとき、MCUの安定な動作を保証するために供給したクロック周波数の急な変化を避けることが必要とされます。或るクロック周期から次への2%より大きな周波数変化は予測されない事態を引き起こします。このようなクロック周波数での変化中、MCUはリセットに保たれるのを保証することが必要とされます。

システム クロック前置分周器が安定な動作を保証しながら、内部クロック周波数の実行時変更の実現に使えることに注意してください。詳細については20頁の「システム クロック前置分周器」を参照してください(<mark>訳注</mark>:共通性のため本行追加)。

# 128kHz内部発振器

128kHz内部発振器は128kHzのクロックを供給する低電力発振器です。この周波数は3V,25℃での公称値です。このクロックはCKSEL ヒューズを'0110'にプログラミング(設定)することによってシステム クロックとして選択できます。

このクロック元が選択されると、起動時間は表11.で示されるようにSUTヒューズによって決定されます。

表11.128kHz内部発振器用起動遅延時間選択表

| SUT1,0 | パワーダウンからの<br>起動遅延時間 | リセットからの<br>付加遅延時間   | 推奨使用法            |  |  |  |  |  |  |

|--------|---------------------|---------------------|------------------|--|--|--|--|--|--|

| 0 0    | 6×CK                | 14×CK ( <b>注1</b> ) | 低電圧検出(BOD)リセット許可 |  |  |  |  |  |  |

| 0 1    | 6×CK                | 14×CK+4ms           | 高速上昇電源           |  |  |  |  |  |  |

| 1 0    | 6×CK                | 14×CK+64ms          | 低速上昇電源           |  |  |  |  |  |  |

| 11     |                     | (予約)                |                  |  |  |  |  |  |  |

注1: RSTDISBLヒューズがプログラム(0)されると、プログラミング動作への移行可を保証するため、付加遅延時間は14×CK+4msに増やされます。

# システム クロック前置分周器

ATtiny2313のシステム クロックはクロック前置分周レシ、スタ(CLKPR)の設定によって分周できます。この特徴(機能)は必要とされる処理能力が低い時の消費電力削減に使えます。これは全クロック種別で使え、CPUと全同期周辺機能のクロック周波数に影響を及ぼします。 clk<sub>CPU</sub>、clk<sub>FLASH</sub>、clk<sub>I/O</sub>は表12.で示された値によって分周されます。

前置分周器設定間を切り替えるとき、システム クロック前置分周器は中間(経過途中)の周波数が直前の設定に対応するクロック周波数または新規設定に対応するクロック周波数のどちらよりも高くなく、クロック系で不具合が起きないことを保証します。

前置分周器として実行するリプル カウンタは分周されないクロック周波数で走行し、CPUのクロック周波数より速いかもしれません。従って例え(カウンタ値が)読めるとしても、前置分周器の状態を決めることはできず、1から他へのクロック分周値切り替えを行う正確な時間は必ずしも予測できません。CLKPS値が書かれる時から新規クロック周波数が活性(有効)になる前にT1+T2~T1+2×T2間かかります。この間で2つの有効なクロック端が生成されます。ここでのT1は直前のクロック周期、T2は新規前置分周器設定に対応する周期です。

予期せぬクロック周波数の変更を防ぐため、CLKPSビットの変更は次の特別な書き込み手順に従わなければなりません。

- 1. クロック分周値変更許可(CLKPCE)ビットに1、CLKPR内の他の全ビットに0を書きます。

- 2. (次からの)4周期以内にCLKPCEビットをOとする欲したCLKPS値を書きます。

前置分周器設定変更時、書き込み手続きが割り込まれないことを保証するため、割り込みは禁止されなければなりません。

# ■ クロック前置分周レシ、スタ (Clock Prescale Register) CLKPR

| ピット         | 7      | 6 | 5 | 4 | 3      | 2      | 1      | 0      |       |

|-------------|--------|---|---|---|--------|--------|--------|--------|-------|

| \$26 (\$46) | CLKPCE | - | _ | - | CLKPS3 | CLKPS2 | CLKPS1 | CLKPS0 | CLKPR |

| Read/Write  | R/W    | R | R | R | R/W    | R/W    | R/W    | R/W    |       |

| 初期値         | 0      | 0 | 0 | 0 | 内容参照   | 内容参照   | 内容参照   | 内容参照   |       |

#### ■ ビット7 - CLKPCE: クロック分周値変更許可 (Clock Prescaler Change Enable)

CLKPSビットの変更を許可するためにCLKPCEビットは論理1を書かれなければなりません。CLKPCEビットは同時にCLKPRの他の全 ビットが0を書かれる時だけ更新されます。CLKPCEは書き込み後4クロック周期またはCLKPSビット書き込み時、ハードウェアによって解除(0) されます。この制限時間(4クロック周期)内のCLKPCEビット再書き込みは制限時間の延長もCLKPCEビットの解除(0)も行いません。

#### ■ ビット3~0 - CLKPS3~0: クロック分周値選択 (Clock Prescaler Select Bits 3~0)

これらのビットは選択したクロック元と内部システム クロック間の分周値を定義します。これらのビットは応用の必要条件に合わせた各種クロック周波数を実行時に書けます。分周値が使われると、分周器はMCUへの主クロックを分周し、全ての同期周辺機能の速度が減じられます。分周値は表12.で与えられます。

CKDIV8tュース、がCLKPSt、ットの初期値を決めます。CKDIV8が非プログラム(1)にされると、CLKPSt、ットは、0000、にリセットされます。 CKDIV8がプログラム(0)されると、CLKPSt、ットは起動時に8分周を与える、0011、にリセットされます。現在の動作条件でデバイスの最高周波数より高い周波数のクロック元を選択した場合、この機能が使われるべきです。CKDIV8tュース、設定に拘らず、どの値もCLKPSt、ットへ書けることに注意してください。応用ソフトウェアは現在の動作条件でデバイスの最高周波数より高い周波数のクロック元を選択した場合、充分な分周値が選択されることを保証しなければなりません。本デバイスはCKDIV8tュース、がプログラム(0)で出荷されます。

| 表12. クロック前置分 | 周器選 | 択   |   |   |    |         |    |     |     |         |   |   |   |   |   |   |   |

|--------------|-----|-----|---|---|----|---------|----|-----|-----|---------|---|---|---|---|---|---|---|

| CLKPS3       |     | 0 1 |   |   |    |         |    |     |     |         |   |   |   |   |   |   |   |

| CLKPS2       |     | 0 1 |   |   |    |         |    |     |     | 0 1     |   |   |   |   |   |   |   |

| CLKPS1       | (   | 0 1 |   |   |    | 0 1 0 1 |    |     |     | (       | ) |   | 1 | ( | ) |   | 1 |

| CLKPS0       | 0   | 1   | 0 | 1 | 0  | 1       | 0  | 1   | 0   | 1       | 0 | 1 | 0 | 1 | 0 | 1 |   |

| 分周値(数)       | 1   | 2   | 4 | 8 | 16 | 32      | 64 | 128 | 256 | 56 (予約) |   |   |   |   |   |   |   |

# 電力管理と休止形態

休止形態は応用でMCU内の未使用部を一時停止することを可能にし、それによって節電します。AVRは応用で必要な消費電力に 仕立てることを使用者に許す様々な休止形態を提供します。

3つの休止形態の何れかへ移行するにはMCU制御レジスタ(MCUCR)の休止許可(SE)ビットが論理1を書かれ、SLEEP命令が実行されなければなりません。MCUCRの休止種別選択(SM1,0)ビットはSLEEP命令によって活性(有効)にされる休止形態(アイドル,パワーダウン, スタンハイ)のどれかを選びます。一覧については表13.をご覧ください。MCUが休止形態中に許可した割り込みが起こると、MCUは起動します。その時にMCUは起動時間に加えて4周期停止され、割り込みルーチンを実行し、そしてSLEEP命令の次の命令から実行を再開します。デハイスが休止から起動するとき、レジスタファイルとSRAMの内容は変えられません。休止形態中にリセットが起こると、MCUは起動し、リセット ヘブクから実行します。

16頁の図11.はATtiny2313の各種クロック系統とその配給を示します。この図は適切な休止形態を選択する助けになります。

#### ■ MCU制御レジスタ (MCU Control Register) MCUCR

このMCU制御レジスタは電力管理用の制御ビットを含みます。

| ピット         | 7   | 6   | 5   | 4   | 3     | 2     | 1     | 0     |       |

|-------------|-----|-----|-----|-----|-------|-------|-------|-------|-------|

| \$35 (\$55) | PUD | SM1 | SE  | SM0 | ISC11 | ISC10 | ISC01 | ISC00 | MCUCR |

| Read/Write  | R/W | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |       |

| 初期値         | 0   | 0   | 0   | 0   | 0     | 0     | 0     | 0     |       |

#### ■ ビット5 - SE:休止許可(Sleep Enable)

SLEEP命令が実行される時にMCUを休止形態へ移行させるには、休止許可(SE)ビットが論理1を書かれなければなりません。MCUの目的外休止形態移行を避けるため、SLEEP命令実行直前に休止許可(SE)ビットを設定(1)し、起動後直ちに解除(0)することが推奨されます。

## ■ ビット6,4 - SM1,0: 休止種別選択 (Sleep Mode Select Bits 1 and 0)

これらのビットは表13.で示される利用可能な3つの休止形態の1つを選択します。

| 表13. 休止形態種別選択  |   |          |  |  |  |  |  |  |  |  |

|----------------|---|----------|--|--|--|--|--|--|--|--|

| SM1 SM0 休止形態種別 |   |          |  |  |  |  |  |  |  |  |

| 0              | 0 | アイドル動作   |  |  |  |  |  |  |  |  |

| 0              | 1 | パプーダウン動作 |  |  |  |  |  |  |  |  |

| 1              | 0 | スタンハーイ動作 |  |  |  |  |  |  |  |  |

| 1              | 1 | パプーダウン動作 |  |  |  |  |  |  |  |  |

注: スタンバイ動作は外部クリスタル発振子また はセラミック振動子での使用に対してだけ 推奨されます。

# アイドル動作

休止種別選択(SM1,0)ビットが'00'を書かれるとき、SLEEP命令はMCUをアイドル動作へ移行させ、CPUを停止しますが、USART、アナログ比較器、多用途直列インターフェース(USI)、タイマ/カウンタ、ウォッチトッグ、割り込み機構の継続動作を許します。この休止形態は基本的にclkCPUとclkFLASHを停止する一方、他のクロックに走行を許します。

ア介・ル動作はMCUにタイマ溢れやUSARTの送信完了などの内部割り込みだけでなく、外部で起動された割り込みからの起動も可能にします。アナログ比較器割り込みからの起動が必要とされないなら、アナログ比較器制御/状態レジ、スタ(ACSR)のアナログ比較器禁止(ACD)ビットを設定(1)することによってアナログ比較器を電源断にできます。これはアイデル動作での消費電力を削減します。

#### パワーダウン動作

SM1,0ビットが'01'または'11'を書かれると、SLEEP命令はMCUをパワーダウン動作へ移行させます。この動作では外部発振器が停止される一方、外部割り込み、多用途直列インターフェース(USI)の開始条件検出、ウォッチドッグ機能は(許可ならば)継続して動作します。外部リセット、ウォッチドッグリセット、低電圧検出(BOD)リセット、USI開始条件検出割り込み、INT0またはINT1の外部レヘル割り込み、ピン変化割り込みだけがMCUを起動できます。この休止形態は基本的に生成した全てのクロックを停止し、非同期部の動作だけを許します。

レヘールで起動した割り込みがハプワーダウン動作からの復帰に使われる場合、MCUを起動するためには変更したレヘールが一定時間保持されなければならないことに注意してください。詳細については40頁の「外部割り込み」を参照してください。

パワーダウン動作から起動するとき、起動条件が起きてから起動の効果が現れるまで遅延があります。これは停止されてしまっている後の再始動と安定になることをクロックに許します。この起動(遅延)時間は16頁の「**クロック元**」で記述されるように、リセット遅延時間を定義するのと同じCKSELヒューズによって定義されます。

## スタンバイ動作

外部クリスタル発振子/セラミック振動子クロック種別が選択され、SM1,0ビットが'10'の時に、SLEEP命令はMCUをスタンバイ動作へ移行させます。この動作は(外部クリスタル用)発振器が走行(動作)を保たれる例外を除いてパワーダウン動作と同じです。デバイスはスタンバイ動作から6クロック周期で起動します。

#### 表14. 各休止形態に於ける動作クロック範囲と復帰起動要因

|            | 動作クロック範囲   |              | 発振器動作     |              | 復帰起重              | 加要因(割り込み)     |                   |               |            |

|------------|------------|--------------|-----------|--------------|-------------------|---------------|-------------------|---------------|------------|

| 休止種別       | clk<br>CPU | clk<br>flash | clk<br>10 | 主クロック<br>供給元 | INT0,INT1<br>ピン変化 | USI開始条件<br>検出 | SPM/EEPROM<br>操作可 | ウォッチ<br>ト゛ック゛ | その他<br>I/O |

| アイドル       |            |              | 0         | 0            | 0                 | 0             | 0                 | 0             | 0          |

| パプータ・ウン    |            |              |           |              | 2                 | 0             |                   | 0             |            |

| スタンバイ (注1) |            |              |           | 0            | 2                 | 0             |                   | 0             |            |

注1: クロック元として推奨した外部クリスタル発振子またはセラミック振動子が選択された場合だけです。

② INT0とINT1についてはレヘル割り込みのみです。

# 消費電力の最小化

これらはAVRが制御するシステムで消費電力の最小化を試みる時に考慮するためのそれぞれの検討点です。一般的に休止形態は可能な限り多く使われるべきで、休止種別は動作するデバイスの機能が可能な限り少なくなるために選択されるべきです。必要とされない全ての機能は禁止されるべきです。特に次の機能部は最低可能消費電力の達成を試みるとき、特別な考慮を必要とするでしょう。

#### アナログ比較器

アイドル動作へ移行するとき、アナログ比較器は使われないなら、禁止されるべきです。その他の休止形態でのアナログ比較器は自動的に禁止されます。しかしアナログ比較器が入力として内部基準電圧を使う設定の場合、全休止形態でアナログ比較器は禁止されるべきです。さもなければ内部基準電圧は休止形態と無関係に許可されます。アナログ比較器設定法の詳細については100頁の「アナログ比較器」を参照してください。

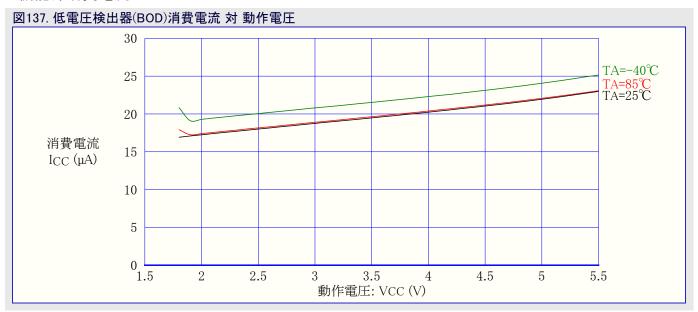

#### 低電圧検出器 (BOD)

低電圧検出器(BOD)が応用で必要とされないなら、この単位部はOFFにされるべきです。低電圧検出器がBODLEVELヒューズによって許可されていると全休止形態で許可され、故に常時電力を消費します。これはより深い休止形態での総消費電流にとって重要な一因になります。低電圧検出器(BOD)設定法の詳細については24頁の「低電圧検出 (BOD)」を参照してください。

# 内部基準電圧

内部基準電圧は低電圧検出器(BOD)とアナログ比較器によって必要とされる時に許可されます。これら単位部が上の項で記述されたように禁止されると、内部基準電圧は禁止され、電力を消費しません。再び許可する場合、この出力が使われる前に使用者は基準電圧へ起動(安定時間)を与えなければなりません。基準電圧が休止形態でON保持される場合、この出力は直ちに使えます。起動時間の詳細については25頁の「内部基準電圧」を参照してください。

#### ウォッチト ック タイマ

ウォッチト、ック、タイマが応用で必要とされないなら、この単位部はOFFにされるべきです。ウォッチト、ック、タイマが許可されていると全休止形態で許可され、故に常時電力を消費します。これはより深い休止形態での総消費電流にとって重要な一因になります。ウォッチト、ック、タイマ 設定法の詳細については26頁の「ウォッチト、ック、タイマ」を参照してください(訳注:原書に対して参照先修正)。

#### ポートピン

休止形態へ移行するとき、全てのポートピンは最小電力使用に設定されるべきです。最も重要なことはその時にピンが抵抗性負荷を駆動しないのを保証することです。I/Oクロック(clkɪ/O)が停止される休止形態ではデバイスの入力緩衝部が禁止されます。これは必要とされない時に入力論理回路によって電力が消費されないことを保証します。いくつかの場合で入力論理回路は起動条件を検出するために必要とされ、その時は許可されます。どのピンが許可されるかの詳細については32頁の「デジタル入力許可と休止形態」を参照してください。入力緩衝部が許可され、入力信号が浮いている状態のままか、またはアナログ信号電圧がVCC/2付近の場合、入力緩衝部は過大な電力を消費するでしょう。

アナログ、入力ピンに対するデジタル入力緩衝部は常に禁止されるべきです。入力ピンでのVCC/2付近のアナログ信号入力は活動動作でも重要な電流を引き起こし得ます。デジタル入力緩衝部はデジタル入力禁止レジスタ(DIDR)の書き込みによって禁止できます。詳細については101頁の「デジタル入力禁止レジスタ - DIDR」を参照してください。

#### 内蔵デバッグ機能(dW)(訳注:共通性から追加)

内蔵デバッグ機能がDWENヒュースによって許可され、チップが休止形態へ移行すると、主クロック元は許可に留まり、従って常に電力を消費します。これはより深い休止形態での総消費電流にとって重要な一因になります。

# システム制御とリセット

#### AVRのリセット

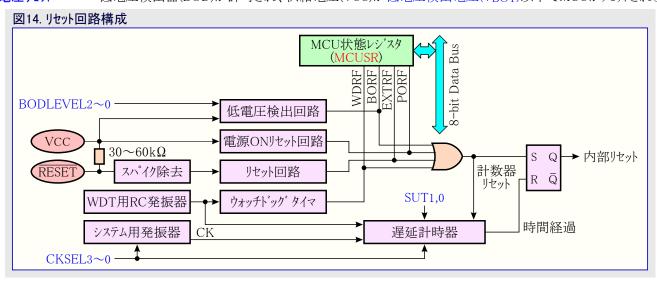

リセット中、全てのI/Oレシ、スタはそれらの初期値に設定され、プログラムはリセット、グタから実行を開始します。 リセット、グタに配置される命令は、きっとリセット処理ルーチンへの無条件相対分岐(RJMP)命令でしょう。 プログラムが決して割り込み元を許可しないなら、割り込み、グタは使われず、これらの位置に通常のプログラムコートが配置できます。 **図14**.の回路構成図はリセット論理回路を示します。 **表80**.はリセット回路の電気的特性を定義します。

AVRのI/Oポートはリセット元が有効になると直ちにそれらの初期状態にリセットされます。これはどのクロック元の走行も必要ありません。

全てのリセット元が無効にされてしまった後、遅延計数器(タイマ)が始動され、内部リセットを引き伸ばします。これは通常動作開始前に安定電圧へ達することを電源に許します。遅延タイマの遅延時間はSUTヒューズとCKSELヒューズを通して使用者によって定義されます。この遅延時間についての各種選択は16頁の「クロック元」で示されます。

## リセット元

ATtiny2313には次の4つのリセット元があります。

- ・電源ONリセット・・・・・供給電圧が電源ONリセット閾値電圧(VPOT)以下でMCUがリセットされます。

- ・外部リセット・・・・・・・ RESET ピンが最小パルス幅以上Lowレヘブルに保たれると、MCUがリセットされます。

- ・ウォッチトック・リセット・・・ウォッチトック・システム リセット動作が許可され、ウォッチトック・タイマが終了すると、MCUがリセットされます。

- ・低電圧リセット・・・・・ 低電圧検出器(BOD)が許可され、供給電圧(VCC)が低電圧検出電圧(VBOT)以下でMCUがリセットされます。

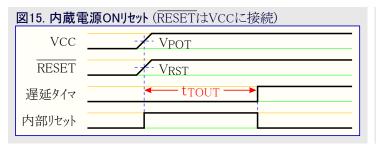

# 電源ONリセット

電源ONリセット(POR)パルスはチップ。上の検出回路によって生成されます。検出電圧は表80.で定義されます。POR信号はVCCが検出電圧以下の時は必ず活性(有効)にされます。POR回路は供給電圧異常検出は勿論、始動リセットの起動にも使えます。

電源ONJセット回路はデバイスが電源投入でリセットされることを保証します。電源ONJセット閾値電圧(VPOT)への到達はVCCの上昇後にデバイスがどのくらいリセットを保つかを決める遅延計数器(タイマ)を起動します。VCCがこの検出電圧以下に低下すると、リセット信号はどんな遅延もなく再び有効にされます。

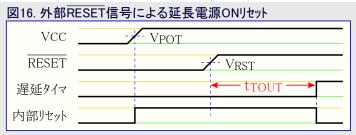

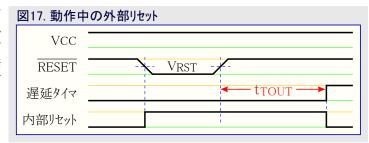

## 外部リセット

外部リセットはRESETt°ンのLowレヘルによって生成されます。クロックが動いていなくても、最小ハルス幅(表80.参照)以上のリセットハルスはリセットを生成します。短すぎるハルスはリセット生成が保証されません。印加された信号の上昇がリセット閾値電圧(VRST)に達すると(遅延タイマを起動し)、遅延タイマは遅延時間(tTOUT)経過後にMCUを始動します。

#### 低電圧(ブラウンアウト)検出リセット

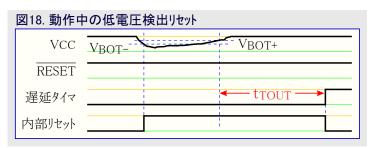

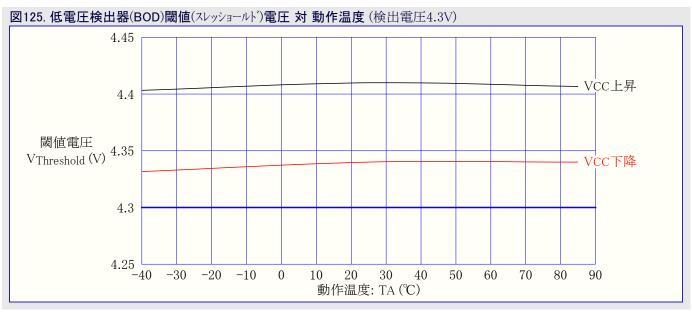

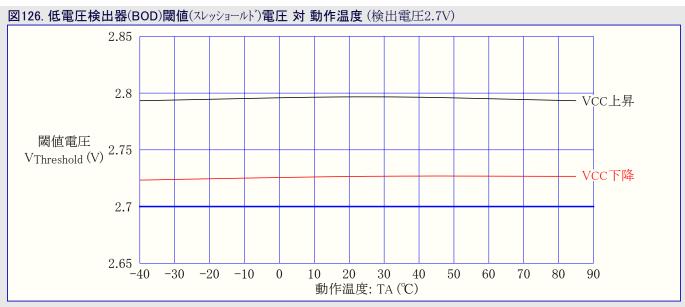

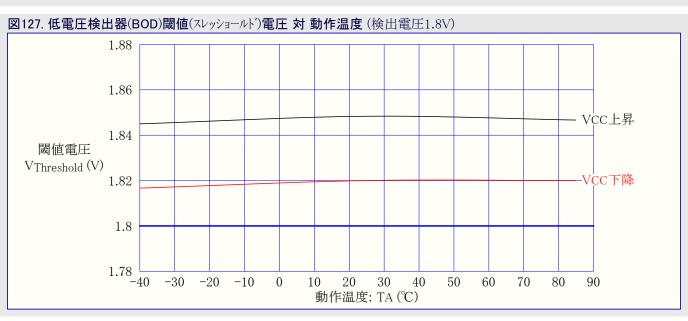

ATtiny2313には固定化された起動(検出)電圧と比較することによって動作中のVCCを監視するチップ。上の低電圧検出(BOD)回路があります。BODの起動電圧はBODLEVELtュース。によって選択できます。この起動電圧はスパイク対策BODを保証するためにヒステリシスを持ちます。検出電圧のヒステリシスはVBOT+=VBOT +VHYST/2、VBOT-=VBOT-VHYST/2と解釈されるべきです。

BODが許可され、VCCが起動電圧以下に下降すると(図18.の VBOT-)、低電圧リセットが直ちに有効とされます。VCCが起動電圧以上に上昇すると(図18.のVBOT+)、(遅延タイマが起動され)遅延タイマは遅延時間(trour)経過後にMCUを始動します。

BOD回路は電圧が表16.で与えられるtBOD時間より長く起動電圧以下に留まる場合のみ、VCCでの低下を検出します。

|   | 表16. 低電圧検出(BOD)特性 |               |    |    |    |    |  |  |  |  |  |

|---|-------------------|---------------|----|----|----|----|--|--|--|--|--|

|   | シンホ゛ル             | 項目            | 最小 | 代表 | 最大 | 単位 |  |  |  |  |  |

| I | V <sub>HYST</sub> | 低電圧検出ヒステリシス電圧 |    | 50 |    | mV |  |  |  |  |  |

| I | $t_{ m BOD}$      | 最小低電圧検出時間     |    | 2  |    | μs |  |  |  |  |  |

## 表15. BODLEVELヒューズ(VBOT) 設定(注1)

| BODLEVEL2~0    | 最小   | 代表  | 最大 | 単位 |  |  |  |  |  |

|----------------|------|-----|----|----|--|--|--|--|--|

| 111            | 低電圧  | 卜禁止 |    |    |  |  |  |  |  |

| 1 1 0          |      | 1.8 |    |    |  |  |  |  |  |

| 1 0 1          |      | 2.7 |    | V  |  |  |  |  |  |

| 1 0 0          |      | 4.3 |    |    |  |  |  |  |  |

| $000 \sim 011$ | (予約) |     |    |    |  |  |  |  |  |

注1: いくつかのデバイスでVBOTが公称最低動作電圧以下の可能性があります。この状態のデバイスについては製造検査中、VCC=VBOTに落として検査されています。これはマイクロコントローラの正しい動作がもはや保証されない電圧になる前に低電圧検出(BOD)リセットが起きることを保証します。この検査はATtiny2313VについてBODLEVEL=110を、ATtiny 2313についてBODLEVEL=101を使って実行されます。

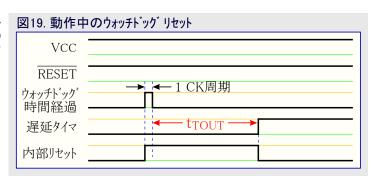

# ウォッチト゛ック゛ リセット

ウォッチトック・時間経過時、(内部的に)1CK周期幅の短いリセット パルスを生成します。このパルスの下降端で遅延タイマは遅延時間(t<sub>TOUT</sub>) の計時を始めます。ウォッチトック・タイマ操作の詳細については26頁を参照してください。

# ■ MCU状態レジスタ (MCU Status Register) MCUSR

MCU状態レシブスタはどのリセット元がMCUリセットを起こしたかの情報を提供します。

| ピット         | 7 | 6 | 5 | 4 | 3    | 2    | 1     | 0    |       |

|-------------|---|---|---|---|------|------|-------|------|-------|

| \$34 (\$54) | _ | - | - | - | WDRF | BORF | EXTRF | PORF | MCUSR |

| Read/Write  | R | R | R | R | R/W  | R/W  | R/W   | R/W  |       |

| 初期値         | 0 | 0 | 0 | 0 | 内容参照 | 内容参照 | 内容参照  | 内容参照 |       |

#### ■ ビット7~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

#### ■ ビット3 - WDRF: ウォッチドック゛リセット フラク゛(Watchdog Reset Flag)

このビットはウォッチドッグ リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット (0)されます。

#### ■ ビット2 - BORF: 低電圧リセット フラク (Brown-Out Reset Flag)

このビットは低電圧リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

#### ■ ビット1 - EXTRF: 外部リセット フラク (External Reset Flag)

このビットは外部リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

#### ■ ビット0 - PORF: 電源ONリセット フラク (Power-on Reset Flag)

このビットは電源ONリセットが起こると設定(1)されます。このビットはこのフラグへの論理0書き込みによってのみリセット(0)されます。

リセット条件の確認にリセット フラグを使うために使用者はプログラム内で可能な限り早くMCUSRを読み、それから解除(0)すべきです。別のリセットが起こる前にこのレジスタが解除(0)されると、リセット元はリセット フラグを調べることによって得られます。

# 内部基準電圧

ATtiny2313は内部基準電圧が特徴です。この基準電圧は低電圧検出(BOD)に使われ、アナログ比較器入力としても使えます。

# 基準電圧許可信号と起動時間

この基準電圧には使われるべき方法に影響を及ぼすかもしれない起動時間があります。この起動時間は表17.で与えられます。節電のために、この基準電圧は常にONではありません。この基準電圧は次の状態中ONです。

- 1. 低電圧検出リセット許可時 (BODLEVEL2~0ヒュース のプログラム(0)により)

- 2. アナログ 比較器基準電圧接続時 (アナログ 比較器制御/状態レジスタ(ACSR)の基準電圧入力選択(ACBG)=1)

従って低電圧検出(BOD)が許可されていないと、ACBGの設定(=1)後、使用者はアナログ比較器出力が使われる前に、基準電圧へ起動時間を与えなければなりません。ハプローダウン動作での消費電力を減らすため、使用者はハプローダウン動作へ移行する前に基準電圧がOFFされるのを保証することで上の2つの状態を避けられます。

#### 表17. 内部基準電圧特性

| シンホ゛ル             | 項目   | 条件                  | 最小  | 代表  | 最大  | 単位 |

|-------------------|------|---------------------|-----|-----|-----|----|

| $V_{BG}$          | 基準電圧 |                     | 1.0 | 1.1 | 1.2 | V  |

| t <sub>BG</sub>   | 起動時間 | VCC=2.7V<br>TA=25°C |     | 40  | 70  | μs |

| $I_{\mathrm{BG}}$ | 消費電流 | 1A-25 C             |     | 15  |     | μA |

# ウォッチト゛ック゛タイマ

ATtiny2313は強化されたウォッチドッグタイマ(WDT)を持ちます。主な機能を次に示します。

- 独立した内蔵発振器からのクロック駆動

- 3つの動作種別

- 割り込み

- システム リセット

- 割り込みとシステム リセット

- •選択可能な16ms~8sの計時完了時間

- 安全動作用のウォッチト、ック、常時ONハート、ウェア ヒュース、

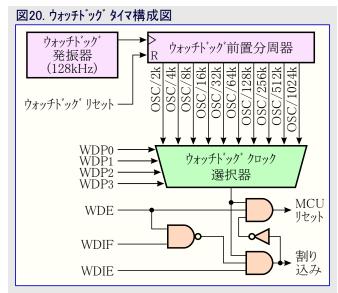

ウォッチドッグタイマ(WDT)はチップ上の独立した128kHz発振器の間隔で計時するタイマです。WDTは計数器が与えられた計時完了値に達した時に割り込みまたはシステムリセットを生じます。通常動作では計時完了値へ達する前に計数器を再始動するために、システムはウォッチドッグリセット(WDR)命令を使う必要があります。システムが計数器を再始動しなければ、割り込みまたはシステムリセットが起こるでしょう。

割り込み動作種別では、タイマ計時完了時にWDTが割り込みを生じます。この割り込みは休止形態からデバイスを起動するためや、一般的なシステムタイマとしても使えます。1つの例は或る動作に対して許された最

大時間を制限することで、その動作が予測されたより長く走行する時に割り込みを生じます。システム リセット動作種別ではタイマ計時完了時にWDTがリセットを生じます。これは一般的にコート・外走行の場合の中断を防止するのに使われます。3つ目の動作種別は先に割り込みを生じ、その後にシステム リセット動作種別に切り替えることで、他の2つの動作種別の組み合わせとなる、割り込み及びシステム リセット動作種別です。この動作種別は例えばシステム リセットに先立って重要なパラメータを保存することによって安全な停止を許します。

ウォッチト、ック、常時ON(WDTON)ヒュース、のプログラム(0)はウォッチト、ック、タイマをシステムリセット動作種別に強制します。このヒュース、のプログラム(0)でシステムリセット動作(WDE)ヒ、ットと割り込み動作(WDIE)ヒ、ットは各々、'1'と'0'に固定されます。

更にプログラム保護を保証するためにウォッチドッグ設定の変更は時間制限手順に従わなければなりません。システム リセット許可(WDE)の解除と計時完了時間設定の変更についての手順は次のとおりです。

- 1. 同じ操作(命令)でウォッチト、ッグ変更許可(WDCE)とWDEに論理1を書きます。WDEビットの直前の値に拘らず、論理1がWDEに書かれなければなりません。

- 2. 次からの4クロック周期内に同じ操作(命令)で欲したWDEとウォッチドッグタイマ前置分周選択(WDP3~0)ビットを書きますが、WDCEビットは解除(0)されてです。これは1操作(命令)で行わなければなりません。

次のコート・例はウォッチト・ッグ、タイマをOFFに切り替えるアセンフ・リ言語とC言語の関数を示します。本例は(例えば全割り込み禁止によって)割り込みが制御され、それ故これらの関数実行中に割り込みが起きない前提です。

```

アセンブリ言語プログラム例

WDT_OFF:

;全割り込み禁止

CLI

WDR

;ウォッチドック゛タイマ リセット

R16, MCUSR

;MCUSR値を取得

ΤN

ANDI

R16, ~ (1<<WDRF)

;WDRF論理0値を取得

;ウォッチト、ック、リセットフラク、(WDRF)解除

OUT

MCUSR, R16

R16, WDTCSR

;現WDTCSR値を取得(他ビット保護用)

IN

;WDCEとWDE論理1値を設定

R16, (1<<WDCE) | (1<<WDE)

ORI

OUT

WDTCSR, R16

;WDCEとWDEに論理1書き込み

LDI

R16, (0<<WDE)

;WDE論理0値を取得

OUT

WDTCSR, R16

;ウォッチト・ック、禁止

SEI

;全割り込み許可

RET

;呼び出し元へ復帰

C言語プログラム例

void WDT_off(void)

__disable_interrupt();

/* 全割り込み禁止 */

/* ウォッチト゛ック゛ タイマ リセット */

__watchdog_reset();

MCUSR &= ^{\sim} (1<<WDRF);

/* ウォッチト、ック、リセット フラク (WDRF)解除 */

WDTCSR |= (1<<WDCE) | (1<<WDE);

/* WDCEとWDEに論理1書き込み */

WDTCSR = 0x00;

/* ウォッチト・ック 禁止 */

/* 全割り込み許可 */

__enable_interrupt();

```

注: このコート 例はデバイス定義ファイルがインクルート されることが前提です。

注: ウォッチト、ック、が偶然に許可されると(例えばポインタの逸脱や低電圧(プラウンアウト)状態)、デバイスはリセットし、ウォッチト、ック・は許可に留まります。コート、がウォッチト、ック、操作の初期設定をしなければ、これは計時完了の無限繰り返しを引き起こすかもしれません。この状態を避けるため、応用ソフトウェアは例えウォッチト、ック、が使われなくても、初期化ルーチンでWDRFフラク、とWDE制御ビットを常に解除(0)すべきです。

次のコート・例はウォッチト、ック、タイマの計時完了値変更用のアセンフ、リ言語とC言語の関数を示します。

```

アセンブリ言語プログラム例

WDT_PRS:

CLT

;全割り込み禁止

;ウォッチトック タイマ リセット

WDR

IN

R16, WDTCSR

;現WDTCSR値を取得(他ビット保護用)

ORI

R16, (1<<WDCE) | (1<<WDE)

;WDCEとWDE論理1値を設定

OUT

;WDCEとWDEに論理1書き込み

WDTCSR, R16

R16, (1<<WDE) | (1<<WDP2) | (1<<WDP0)

LDI

;WDE=1,計時間隔=0.5s値を取得

;0.5s監視間隔リセット動作開始

OUT

WDTCSR, R16

SEI

;全割り込み許可

;呼び出し元へ復帰

RET

C言語プログラム例

void WDT_off(void)

_disable_interrupt();

/* 全割り込み禁止 */

/* ウォッチト・ック・タイマ リセット */

_watchdog_reset();

WDTCSR = (1 << WDCE) | (1 << WDE);

/* WDCEとWDEに論理1書き込み */

WDTCSR = (1 << WDE) \mid (1 << WDP2) \mid (1 << WDP0);

/* 0.5s 監視間隔リセット動作開始 */

/* 全割り込み許可 */

__enable_interrupt();

注: このコート・例はデバイス定義ファイルがインクルートされることが前提です。

```

注: ウォッチドッグ タイマ前置分周選択(WDP3~0)ビットの変更がより短い計時完了周期に変わってしまう結果になり得るため、ウォッチドッグ タイマはWDPビットのどんな変更にも先立ってリセット(WDR命令)されるべきです。

## ■ ウォッチドック タイマ制御/状態レシ スタ (Watchdog Timer Control Register) WDTCSR

| ピット         | 7    | 6    | 5    | 4    | 3   | 2    | 1    | 0    |        |

|-------------|------|------|------|------|-----|------|------|------|--------|

| \$21 (\$41) | WDIF | WDIE | WDP3 | WDCE | WDE | WDP2 | WDP1 | WDP0 | WDTCSR |

| Read/Write  | R/W  | R/W  | R/W  | R/W  | R/W | R/W  | R/W  | R/W  |        |

| 初期値         | 0    | 0    | 0    | 0    | 不定  | 0    | 0    | 0    |        |

#### ■ ビット7 - WDIF: ウォッチドッグ割り込み要求フラグ(Watchdog Interrupt Flag)

ウォッチト、ック、タイマが割り込みに設定され、ウォッチト、ック、タイマで計時完了が起こると、本ヒ、ットが設定(1)されます。対応する割り込み処理へクタを実行すると、WDIFはハート・ウェアによって解除(0)されます。代わりにWDIFはこのフラグへの論理1書き込みによっても解除(0)されます。ステータスレシ、スタ(SREG)の全割り込み許可(I)ビットとウォッチト、ック・割り込み許可(WDIE)が設定(1)されていれば、ウォッチト、ック・計時完了割り込みが実行されます。

#### ■ ビット6 - WDIE: ウォッチドッグ割り込み許可 (Watchdog Interrupt Enable)

このビットが1を書かれ、ステータス レジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されると、ウォッチドッグ割り込みが許可されます。この設定(=1)との組み合わせでウォッチドッグ リセット許可(WDE)ビットが解除(0)されると、割り込み動作種別になり、ウォッチドッグ タイマで計時完了が起こると、対応する割り込みが実行されます。

WDEが設定(1)されると、ウォッチドッゲタイマは割り込み及びシステムリセット動作種別になります。ウォッチドッゲタイマでの最初の計時完了がウォッチドッゲ割り込み要求(WDIF)フラケを設定(1)します。対応する割り込みへ、クタの実行はハート・ウェアによってWDIEとWDIFを自動的に解除(0)します。これは割り込みを使う間のウォッチト、ッケ、リセット保護を維持するのに有用です。割り込み及びシステムリセット動作種別に留まるには、各割り込み後にWDIEが設定(1)されなければなりません。然しながら、ウォッチト、ッケ、システムリセット動作種別の安全機能に危険を及ぼすかもしれないため、これは割り込み処理ルーチン自身内で行われるべきではありません。次の計時完了に先立って割り込みが実行されない場合、システムリセットが適用(実行)されます。

| 表18. ウォッ | 表18. ウォッチドッグ タイマ設定 |      |                |                      |  |  |  |  |  |

|----------|--------------------|------|----------------|----------------------|--|--|--|--|--|

| WDTON    | WDE                | WDIE | 動作種別           | 計時完了での動作             |  |  |  |  |  |

| 1        | 0                  | 0    | 停止             | なし                   |  |  |  |  |  |

| 1        | 0                  | 1    | 割り込み           | 割り込み                 |  |  |  |  |  |

| 1        | 1                  | 0    | システム リセット      | リセット                 |  |  |  |  |  |

| 1        | 1                  | 1    | 割り込み及びシステムリセット | 割り込み、その後システムリセット動作種別 |  |  |  |  |  |

| 0        | Х                  | Х    | システム リセット      | リセット                 |  |  |  |  |  |

# ■ ビット4 - WDCE : ウォッチドッグ変更許可 (Watchdog Change Enable)

このビットはウォッチドッグ リセット許可(WDE)と前置分周器ビットの変更用の時間制限手順で使われます。WDEビットの解除(0)や前置分周器ビット変更のため、WDCEは設定(1)されなければなりません。

一旦1を書かれると、4クロック周期後にハードウェアがWDCEを解除(0)します。

#### ■ ビット3 - WDE: ウォッチドック゛リセット許可 (Watchdog System Reset Enable)

WDEはMCU状態レジスタ(MCUSR)のウォッチドッグ リセット フラク´(WDRF)によって無効にされます。これはWDRFが設定(1)されると、WDEが常に設定(1)されることを意味します。WDEを解除(0)するにはWDRFが先に解除(0)されなければなりません。この特徴は失敗を引き起こす状態中の複数リセットと失敗後の安全な起動を保証します。

## ■ ビット5,2~0 - WDP3~0: ウォッチドッグ タイマ前置分周選択 (Watchdog Timer Prescaler 3,2,1 and 0)

注: WDTONヒューズは、0がプログラム、1が非プログラムを意味します。

このWDP3~0ビットはウォッチドッグ タイマが走行する時のウォッチドッグ タイマの前置分周を決めます。各種前置分周値と対応する計時完了 周期は**表19**.で示されます。

| 表19. ウォッチドッグ前置分周選択    |      |      |      |        |       |      |      |      |      |       |      |   |   |   |   |   |

|-----------------------|------|------|------|--------|-------|------|------|------|------|-------|------|---|---|---|---|---|

| WDP3                  |      | 0 1  |      |        |       |      |      |      |      |       |      |   |   |   |   |   |

| WDP2                  | 0    |      |      | 1      |       |      | 0    |      |      | 1     |      |   |   |   |   |   |

| WDP1                  | (    | )    |      | 1      | (     | )    |      | L    | (    | )     | -    | 1 | ( | ) | ] |   |

| WDP0                  | 0    | 1    | 0    | 1      | 0     | 1    | 0    | 1    | 0    | 1     | 0    | 1 | 0 | 1 | 0 | 1 |

| WDT発振周期数              | 2k   | 4k   | 8k   | 16k    | 32k   | 64k  | 128k | 256k | 512k | 1024k |      |   |   |   |   |   |

| 代表的計時完了<br>周期(VCC=5V) | 16ms | 32ms | 64ms | 0.125s | 0.25s | 0.5s | 1.0s | 2.0s | 4.0s | 8.0s  | (予約) |   |   |   |   |   |

# 割り込み

本章はATtiny2313によって実行される割り込み操作の詳細を記述します。AVR割り込み操作の一般説明については9頁の「リセットと割り込みの扱い」を参照してください。

# ATtiny2313の割り込みべかタ

表20. リセットと割り込みのべつタ

| ベクタ番号 | プログラム アドレス | 発生元                      | 備考                     |  |  |

|-------|------------|--------------------------|------------------------|--|--|

| 1     | \$0000     | リセット                     | 電源ON, WDT, BOD等の各種リセット |  |  |

| 2     | \$0001     | INT0                     | 外部割り込み要求0              |  |  |

| 3     | \$0002     | INT1                     | 外部割り込み要求1              |  |  |

| 4     | \$0003     | タイマ/カウンタ1 CAPT           | タイマ/カウンタ1捕獲発生          |  |  |

| 5     | \$0004     | タイマ/カウンタ1 COMPA          | タイマ/カウンタ1比較A一致         |  |  |

| 6     | \$0005     | タイマ/カウンタ1 OVF1           | タイマ/カウンタ1溢れ            |  |  |

| 7     | \$0006     | タイマ/カウンタ0 OVF0           | タイマ/カウンタ0 溢れ           |  |  |

| 8     | \$0007     | USART RX                 | USART 受信完了             |  |  |

| 9     | \$0008     | USART UDRE               | USART 送信緩衝部空き          |  |  |

| 10    | \$0009     | USART TX                 | USART 送信完了             |  |  |

| 11    | \$000A     | アナログ比較器 ANA_COMP         | アナログ比較器出力遷移            |  |  |

| 12    | \$000B     | PCINT (PCI)              | ピン変化割り込み要求             |  |  |

| 13    | \$000C     | タイマ/カウンタ1 COMPB          | タイマ/カウンタ1比較B一致         |  |  |

| 14    | \$000D     | タイマ/カウンタ0 COMPA          | タイマ/カウンタ0比較A一致         |  |  |

| 15    | \$000E     | タイマ/カウンタ0 COMPB          | タイマ/カウンタ0比較B一致         |  |  |

| 16    | \$000F     | USI START                | USI 開始条件検出             |  |  |

| 17    | \$0010     | USI OVF                  | USI 計数器溢れ              |  |  |

| 18    | \$0011     | EEPROM EE_RDY EEPROM 操作可 |                        |  |  |

| 19    | \$0012     | ウォッチドック゛ WDT             | ウォッチドッグ計時完了            |  |  |

プログラムが決して割り込み元を許可しないなら、割り込みへ、クタは使われず、これらの位置に通常のプログラムコードが配置できます(訳注:共通性から本行追加)。ATtiny2313での最も代表的且つ一般的なリセットと割り込みのヘ、クタアドレス用設定を次に示します。

| アト・レス  | ラヘ゛ル   | 命令   |                   | 注釈                 |

|--------|--------|------|-------------------|--------------------|

| \$0000 |        | RJMP | RESET             | ;各種リセット            |

| \$0001 |        | RJMP | EXT_INTO          | ;外部割り込み要求0         |

| \$0002 |        | RJMP | EXT_INT1          | ;外部割り込み要求1         |

| \$0003 |        | RJMP | TIM1_CAPT         | ;タイマ/カウンタ1捕獲発生     |

| \$0004 |        | RJMP | TIM1_COMPA        | ;タイマ/カウンタ1比較A一致    |

| \$0005 |        | RJMP | TIM1_OVF          | ;タイマ/カウンタ1溢れ       |

| \$0006 |        | RJMP | TIMO_OVF          | ;タイマ/カウンタ0溢れ       |

| \$0007 |        | RJMP | USART_RXC         | ;USART 受信完了        |

| \$0008 |        | RJMP | USART_UDRE        | ;USART 送信緩衝部空き     |

| \$0009 |        | RJMP | USART_TX          | ;USART 送信完了        |

| \$000A |        | RJMP | ANA_COMP          | ;アナログ比較器出力遷移       |

| \$000B |        | RJMP | PCINT             | ;ピン変化割り込み要求        |

| \$000C |        | RJMP | TIM1_COMPB        | ;タイマ/カウンタ1 比較B一致   |

| \$000D |        | RJMP | TIMO_COMPA        | ;タイマ/カウンタ0 比較A一致   |

| \$000E |        | RJMP | TIMO_COMPB        | ;タイマ/カウンタ0 比較B一致   |

| \$000F |        | RJMP | USI_STRT          | ;USI 開始条件検出        |

| \$0010 |        | RJMP | USI_OVF           | ;USI 計数器溢れ         |

| \$0011 |        | RJMP | EE_RDY            | ;EEPROM操作可         |

| \$0012 |        | RJMP | WDT_OVF           | ;ウォッチドッグ計時完了       |

| ;      |        |      |                   |                    |

| \$0013 | RESET: | LDI  | R16, LOW (RAMEND) | ;RAM最終アドレス下位を取得    |

| \$0014 |        | OUT  | SPL, R16          | ;スタック ポインタ(下位)を初期化 |

|        |        | }    |                   | ;以下、I/O初期化など       |

# 入出力ポート

# 序説

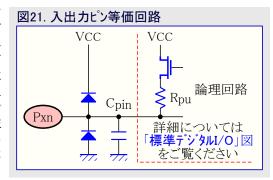

全てのAVRのポートは標準デジタルI/Oポートとして使われる時に真の読み-変更-書き(リート、モディファイライト)を機能的に持ちます。これはSBIとCBI命令で他のどのピンの方向をも無意識に変更することなく、1つのポートピンの方向を変更できることを意味します。(出力として設定されていれば)駆動値を変更、または(入力として設定されていれば)アルアップ抵抗を許可/禁止する時にも同じく適用されます。各出力緩衝部は高い吐き出し(ソース)と吸い込み(シンケ)の両能力で対称的な駆動特性を持ちます。このピン駆動部はLED(表示器)を直接駆動するのに充分な強さです。全てのポートピンは個別に選択可能な、供給電圧で抵抗値が変化しないプルアップ抵抗を持っています。全てのI/Oピンは図21.で示されるようにVCCとGNDの両方に保護ダイオートを持っています。各値の完全な一覧については118頁の「電気的特性」を参照してください。

本項内の全てのレシ、スタとビットの参照は一般形で記されます。小文字の'x'はポート番号文字、小文字の'n'はビット番号を表します。けれどもプログラム内でレシ、スタやビット定義に使うとき、正確な形式(例えば、ここで一般に記されたPORTxnがポートBのビット3に対してはPORT B3)が使われなければなりません。物理的なI/Oレジスタとビット位置は39頁の「I/Oポート用レジスタ」で一覧されます。

各々1つの出力レジスタ(PORTx)、方向レジスタ(DDRx)、入力レジスタ(PINx)の各ポートに対して、3つI/Oメモリアドレス位置が割り当てられます。入力レジスタのI/O位置は読むだけで、一方出力レジスタと方向レジスタは読み書き(両方)です。けれどもPINxレジスタのビットへの論理1書き込みは、出力レジスタの対応ビット値を(1/0)反転する結果になります。加えてMCU制御レジスタ(MCUCR)のプルアップ禁止(PUD)ビットが設定(1)されると、全ポートで全ビットに対してプルアップ機能を禁止します。

標準デジタルI/OとしてのI/Oポートの使用は次の「標準デジタル入出力としてのポート」で記述されます。多くのポート ピンはデバイスの周辺機能用の交換機能と多重化されます。ポート ピンとの各交換機能のインターフェース法は33頁の「交換ポート機能」で記述されます。交換機能の完全な記述については個別機能部項を参照してください。

ポート ピンのいくつかの交換機能の許可は、そのポート内の他のピンの標準デジタル入出力としての使用に影響しないことに注意してください。

# 標準デジタル入出力としてのポート

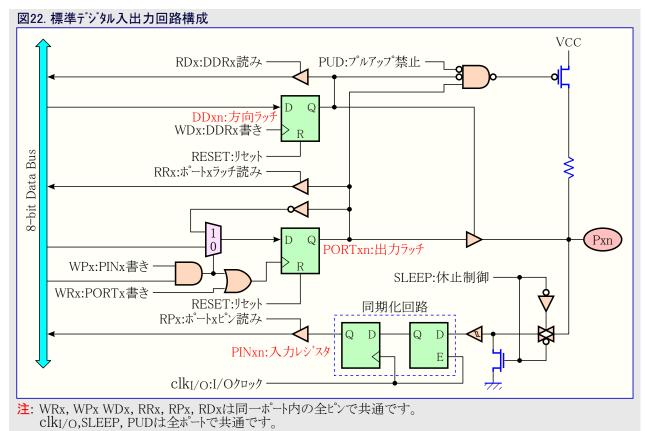

このポートは任意の内部プルアップ付き双方向I/Oポートです。図22.はここで属にPxnと呼ばれるI/Oポート ピンの1つの機能説明を示します。

## ピンの設定

各ポート ピンは3つのレシブスタ ビットDDxn、PORTxn、PINxnから成ります。39頁の「I/Oホート用レジスタ」で示されるように、DDxnビットはDDRx I/Oアドレス、PORTxnビットはPORTx I/Oアドレス、PINxビットはPINx I/Oアドレスでアクセスされます。

DDRxレジスタ内のDDxnビットはそのピンの方向を選択します。DDxnが論理1を書かれるとPxnは出力ピンとして設定されます。DDxnが論 理0を書かれるとPxnは入力ピンとして設定されます。

そのピンが入力ピンとして設定される時にPORTxnが論理lを書かれると、プルアップ抵抗が活性(有効)にされます。 プルアップ抵抗をOFF に切り替えるにはPORTxnが論理0を書かれるか、またはそのピンが出力ピンとして設定されなければなりません。ポート ピンは例えクロック が動いていなくても、リセット条件が活性(有効)になるとHi-Zにされます。

そのピンが出力ピンとして設定される時にPORTxnが論理1を書かれると、そのポート ピンはHigh(1)に駆動されます。そのピンが出力ピンと して設定される時にPORTxnが論理0を書かれると、そのポートピンはLow(0)に駆動されます。

#### ピンの出力交互切り替え

PINxnへの論理1書き込みはDDRxnの値に拘らず、PORTxnの値を反転切り替えします。SBI命令がポート内の1ビットの反転切り替えに 使えることに注目してください。

# 入出力間の切り替え

耒21 ポート ピンの設定

Hi-Z入力(DDxn=0, PORTxn=0)とHigh出力(DDxn=1, PORTxn=1)間の切り替え時、プルアップ許可入力(DDxn=0, PORTxn=1)または Low出力(DDxn=1, PORTxn=0)のどちらかの中間状態が生じるに違いありません。通常、高インピーダンス環境は強力なHigh(吐き出し) 駆動部とプルアップ間の違いに気付かないので、プルアップが許可された状態は十分受け入れられます。この事例でないなら、全ポートの 全プルアップを禁止するために、MCU制御レシ、スタ(MCUCR)のプルアップ、禁止(PUD)ビットが設定(1)できます。

プルアップ入力とLow出力間の切り替えは同じ問題を発生します。使用者は中間状態としてHi-Z入力(DDxn=0, PORTxn=0)またはHigh 出力(DDxn=1, PORTxn=1)のどちらかを使わなければなりません。

表21.はピン値に対する制御信号の一覧を示します。

| 我Z1. パート こ200設と |        |             |     |         |                               |  |  |  |  |  |

|-----------------|--------|-------------|-----|---------|-------------------------------|--|--|--|--|--|

| DDxn            | PORTxn | PUD (MCUCR) | 入出力 | プルアップ抵抗 | 備考                            |  |  |  |  |  |

| 0               | 0      | X           | 入力  | なし      | 高インピーダンス (Hi-Z)               |  |  |  |  |  |

| 0               | 1      | 0           | 入力  | あり      | Pxnに外部からLowを入力すると吐き出し電流が流れます。 |  |  |  |  |  |

| 0               | 1      | 1           | 入力  | なし      | 高インピーダンス (Hi-Z)               |  |  |  |  |  |

# なし 出力 Low (吸い込み)出力 出力 なし High (吐き出し)出力

## ピン値の読み込み

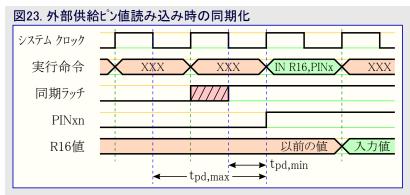

DDxn方向ビットの設定に関係なく、ポート ピンはPINxnレジス タビットを通して読めます。図22.で示されるようにPINxnレ ジスタ ビットと先行するラッチは同期化回路を構成します。 こ れは物理ピンが内部クロックのエッジ付近で値を変える場合 の未定義状態(メタ ステーブル)を避けるために必要とされま すが、それは遅延も持ち込みます。図23.は外部的に加 えられたピン値を読む時の同期化タイミング図を示します。 伝播遅延の最小と最大は各々tpd,minとtpd,maxで示され ます。

(図23.で)システム クロックの最初の下降端の直後から始まるク ロック周期を考察してください。このラッチはクロックがLowの時 に閉じ、クロックがHighの時に同期ラッチ信号の斜線部分で 示されるように通過(トランスペアレント)となります。この信号値 はシステム クロックがLowになる時に保持(ラッチ)されます。そ れが続くクロックの上昇端でPINxnレシブスタに取り込まれま す。2つの矢印tpd,minとtpd,maxによって示されるように、ピ ン上の単一信号遷移は出現時点に依存して0.5~1.5シス テムクロック周期遅らされます。

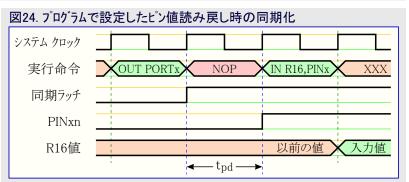

ソフトウェアが指定したピン値を読み戻す時は、図24.で示さ れるようにNOP命令が挿入されなければなりません。 OUT命令はシステムクロックの上昇端で同期ラッチを設定しま す。この場合、同期化回路を通過する遅延時間(tpd)は1 システムクロック周期です。

次のコート・例はポートBピンの0と1をHigh出力、2と3をLow出力、6と7をプルアップ指定として4~7を入力に設定する方法を示します。結果のピン値が再び読み戻されますが、前記で検討されたように、いくつかのピンへ直前に指定された値を読み戻すことができるようにNOP命令が挿入されます。

```

アセンブリ言語プログラム例

LDI

R16, (1<<PB7) | (1<<PB6) | (1<<PB1) | (1<<PB0)

;プルアップとHigh値を取得

R17, (1<<DDB3) | (1<<DDB2) | (1<<DDB1) | (1<<DDB0)

;出力ビット値を取得

LDI

PORTB, R16

;プルアップとHigh値を設定

OUT

OUT

DDRB, R17

;入出力方向を設定

NOP

;同期化遅延対処

;ピン値読み戻し

IN

R16, PINB

C言語プログラム例

unsigned char i;

/* */

PORTB = (1 << PB7) | (1 << PB6) | (1 << PB1) | (1 << PB0);

/* プルアップとHigh値を設定 */

DDRB = (1 << DDB3) | (1 << DDB2) | (1 << DDB1) | (1 << DDB0);

/* 入出力方向を設定 */

/* 同期化遅延対処 */

__no_operation();

i = PINB;

/* ピン値読み戻し */

```

**注**: アセンブリ言語プログラムについてはプルアップがピン0,1,6,7に設定されてから、ビット0と1の強力なHigh駆動部としての再定義、ビット2と3のLow駆動部としての定義、方向ビットが正しく設定されるまでの時間を最小とするために2つの一時レジスタが使われます。

## デジタル入力許可と休止形態

図22.で示されるようにデジタル入力信号はシュミットトリカの入力をGNDにクランプできます。この図でSLEEPと印された信号は入力信号のいくつかが開放のまま、またはVCC/2付近のアナログ信号電圧を持つ場合の高消費電力を避けるため、パワーダウン動作とスタンバイ動作でMCU休止制御器によって設定(1)されます。

SLEEPは外部割り込みピンとして許可されたポート ピンに対しては無視されます。外部割り込み要求が許可されないなら、SLEEPは他のピンについてと同様に有効です。SLEEPは33頁の「**交換ポート機能**」で記載されるように様々な他の交換機能によっても無視されます。

外部割り込みが許可されていない"上昇端、下降端または論理変化(両端)割り込み"として設定された非同期外部割り込みピンに論理1が存在すると、上で言及した休止形態から(復帰)再開する時に、これらの休止形態に於けるクランプが要求された論理変化を生ずるので、対応する外部割り込み要求フラグが設定(=1)されます。

#### 未接続ピン (訳注:共通性のため本項追加)

いくつかのピンが未使用にされる場合、それらのピンが定義されたレベルを持つのを保証することが推奨されます。例え上記のような深い休止形態で多くのデジタル入力が禁止されるとしても、デジタル入力が許可される他の全ての動作(リセット、活動動作、アイドル動作)で消費電流削減のため、浮き状態入力は避けられるべきです。

未使用ピンの定義されたレベルを保証する最も簡単な方法は内部プルアップを許可することです。この場合、リセット中のプルアップは禁止されます。 リセット中の低消費電力が重要なら、外部プルアップまたはプルダウンを使うことが推奨されます。 未使用ピンを直接GNDまたはVCCに接続することは、ピンが偶然に出力として設定されると過電流を引き起こす可能性があるため推奨されません。

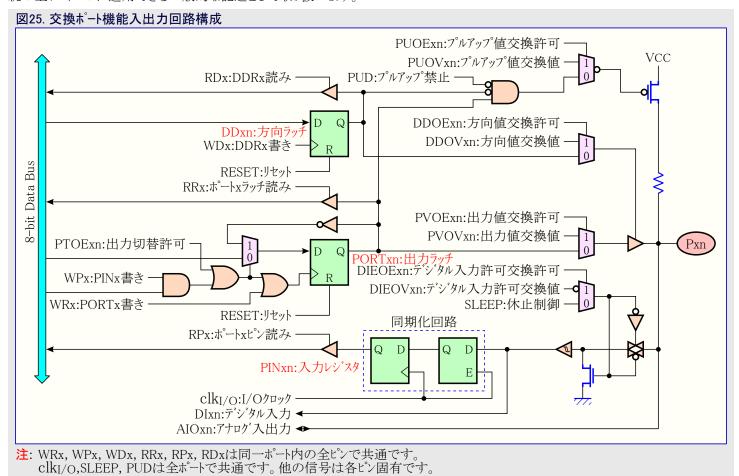

# 交換ポート機能

多くのポート ピンには標準デジタル入出力に加え交換機能があります。図25.は単純化された図22.でのポート ピン制御信号が交換機能によってどう重複できるかを示します。この重複信号は全てのポート ピンに存在する訳ではありませんが、この図はAVR マイクロコントローラ系統の全ポート ピンに適用できる一般的な記述として取り扱います。

表22.は重複(交換)信号の機能一覧を示します。図25.で示すピンとポートは次表で示されません。重複(交換)信号は交換機能を持つ機能部で内部的に生成されます。

|         | XHEAD CYTHDATIC LINCAVERY |                                                                                                    |  |  |  |  |  |  |

|---------|---------------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 表22. 交換 | 機能用交換信号の一般定義              |                                                                                                    |  |  |  |  |  |  |

| 信号略名    | 信号名                       | 意味                                                                                                 |  |  |  |  |  |  |

| PUOE    | プルアップ値交換許可                | 1で、プルアップ許可はPUOV信号で制御され、0の場合、DDxn=0, PORTxn=1, PUD=0でプルアップが許可されます。                                  |  |  |  |  |  |  |

| PUOV    | プルアップ値交換値                 | PUOE=1時、DDxn, PORTxn, PUDの値に関係なく、プルアップの有(1)/無(0)を指定します。                                            |  |  |  |  |  |  |

| DDOE    | 方向値交換許可                   | 1で、出力駆動部はDDOV信号で制御され、0の場合、DDxnレジスタ値で制御されます。                                                        |  |  |  |  |  |  |

| DDOV    | 方向値交換値                    | DDOE=1時、DDxnレジスタ値に関係なく、出力駆動部のON(1)/OFF(0)を制御します。                                                   |  |  |  |  |  |  |

| PVOE    | 出力値交換許可                   | 1で出力駆動部がONなら、ポート値はPVOV信号で制御されます。出力駆動部がONで0の場合、ポート値はPORTxnレジスタ値で制御されます。                             |  |  |  |  |  |  |

| PVOV    | 出力値交換値                    | PVOE=1時、PORTxnレジスタ値に関係なく、ポート値を制御(1/0)します。                                                          |  |  |  |  |  |  |

| PTOE    | 出力切替許可                    | PTOE=1時、PORTxnレジスタ値が反転します。                                                                         |  |  |  |  |  |  |

| DIEOE   | デジタル入力許可交換許可              | 1で、デジタル入力許可はDIEOV信号で制御され、0の場合、MCUの状態(活動動作、休止<br>形態)によって決定されます。                                     |  |  |  |  |  |  |

| OIEOV   | デジタル入力許可交換値               | DIEOE=1時、MCUの状態(活動動作、休止形態)に関係なく、デジタル入力を許可(1)/禁止(0)します。                                             |  |  |  |  |  |  |

| DI      | デジタル入力                    | 交換機能用デジタル入力です。この信号は図上でシュミットトリガ出力に接続されていますが、<br>これは同期化前となります。この信号はクロックとしての使用を除き、各交換機能自身が同<br>期化します。 |  |  |  |  |  |  |

| AIO     | アナログ入出力                   | 交換機能用アナログ入出力です。この信号はピンに直接接続され、双方向使用ができます。                                                          |  |  |  |  |  |  |

次節は交換機能に関連する重複(交換)信号と各ポートの交換機能を簡単に記述します。更に先の詳細については交換機能の記述を参照してください。

# ■ MCU制御レジスタ (MCU Control Register) MCUCR

| ピット         | 7   | 6   | 5   | 4   | 3     | 2     | 1     | 0     |       |

|-------------|-----|-----|-----|-----|-------|-------|-------|-------|-------|

| \$35 (\$55) | PUD | SM1 | SE  | SM0 | ISC11 | ISC10 | ISC01 | ISC00 | MCUCR |

| Read/Write  | R/W | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |       |

| 初期値         | 0   | 0   | 0   | 0   | 0     | 0     | 0     | 0     |       |

#### ■ ビット7 - PUD: プルアップ 禁止 (Pull-up Disable)

このビットが1を書かれると、例えDDxnとPORTxnレジスタがプルアップを許可(DDxn=0, PORTxn=1)に設定されていても、I/Oポートのプルアップは禁止されます。この特徴についてより多くの詳細に関しては31頁の「ピンの設定」をご覧ください。

## ポートAの交換機能

ポートAピンの交換機能は表23.で示されます。

| 表23. ポートAピンの交換機能 |                                        |  |  |  |  |  |  |  |  |

|------------------|----------------------------------------|--|--|--|--|--|--|--|--|

| ポ−ト ピン           | 交換機能                                   |  |  |  |  |  |  |  |  |

| PA2              | RESET (外部リセット入力)<br>dW (デンブッグWIRE入出力)  |  |  |  |  |  |  |  |  |

| PA1              | XTAL2 (システム クロック用発振増幅器出力)              |  |  |  |  |  |  |  |  |

| PA0              | XTAL1 (システム クロック用発振増幅器入力または外部クロック信号入力) |  |  |  |  |  |  |  |  |

交換ピンの設定は次のとおりです。(訳注:共通性のため本項追加)

#### • RESET - ポートA ビット2 : PA2

RESET: リセット ピン。RSTDISBLヒューズがプログラム(0)されると、このピンは通常のI/Oピンとして機能し、デバイスはリセット元として電源ONリセットと低電圧リセットに頼らなければなりません。RSTDISBLヒューズが非プログラム(1)にされると、このピンにリセット回路が接続され、このピンはI/Oピンとして使えません。

PA2がリセット ピンとして使われると、PORTA2, DDA2, PINA2は全て0を読みます。

dW: デバッグWIRE双方向通信ピン。デバッグWIREによる内蔵デバッグ時の双方向通信に使います。dWピンとして使われると、このピン は他の機能ピンとして使えません。

#### • XTAL2 - ポートA ビット1 : PA1

XTAL2: チップ(システム) クロック発振器ピン2。 クリスタル用発振器クロック ピンとして使われます。 クロック ピンとして使われると、このピンルはI/Oピンとして使えません。

PA1がクロック ピンとして使われると、PORTA1, DDA1, PINA1は全て0を読みます。

#### • XTAL1 - ポートA ビット0 : PA0

XTAL1: チップ(システム) クロック発振器ピン1。 クリスタル用発振器クロック ピンまたは外部クロック入力ピンとして使われます。これらのピンとして使われると、このピンはI/Oピンとして使えません。

PAOがクロック ピンとして使われると、PORTAO, DDAO, PINAOは全てOを読みます。

## ポートBの交換機能

ポートBピンの交換機能は表24.で示されます。

#### 表24 ポートBピンの交換機能

|        | ロビノの文法版化                                                                  |        |                                                      |

|--------|---------------------------------------------------------------------------|--------|------------------------------------------------------|

| ポート ピン | 交換機能                                                                      | ポート ピン | 交換機能                                                 |

| PB7    | USCK (3線動作USIクロック入出力)<br>SCL (2線動作USI(TWI)クロック入出力)<br>PCINT7(ピン変化割り込み7入力) | PB3    | OC1A (タイマ/カウンタ1 比較A一致/PWM出力)<br>PCINT3 (ピン変化割り込み3入力) |

| PB6    | DO (3線動作USIデータ出力)<br>PCINT6 (ピン変化割り込み6入力)                                 | PB2    | OC0A (タイマ/カウンタ0 比較A一致/PWM出力)<br>PCINT2 (ピン変化割り込み2入力) |

| PB5    | DI (3線動作USIデータ入力)<br>SDA (2線動作USI(TWI)データ入出力)<br>PCINT5 (ピン変化割り込み5入力)     | PB1    | AIN1 (アナログ比較器反転入力)<br>PCINT1 (ピン変化割り込み1入力)           |

| PB4    | OC1B (タイマ/カウンタ1 比較B一致/PWM出力)<br>PCINT4 (ピン変化割り込み4入力)                      | PB0    | AIN0 (アナログ比較器非反転入力)<br>PCINT0 (ピン変化割り込み0入力)          |

交換ピンの設定は次のとおりです。

• USCK/SCL/PCINT4 - ホートB ビット7: PB7

USCK: 3線動作USIのクロック入出力。 SCL: 2線動作USI(TWI)のクロック入出力。

PCINT7: ピン変化割り込み7入力。PB7ピンは外部割り込み元としても扱えます。

• DO/PCINT6 - ホ°ートB ビット6: PB6

DO: 3線動作USIのデータ出力。

PCINT6: ピン変化割り込み6入力。PB6ピンは外部割り込み元としても扱えます。

• DI/SDA/PCINT5 - ホートB ビット5: PB5

DI: 3線動作USIのデータ入力。3線動作USIは標準ポート機能を無効にしないので、ピンは入力として設定されなければなりません。

SDA: 2線動作USI(TWI)のデータ入出力。

PCINT5: ピン変化割り込み5入力。PB5ピンは外部割り込み元としても扱えます。

• OC1B/PCINT4 - ポートB ビット4 : PB4

OC1B: タイマ/カウンタ1の比較B一致出力。PB4ピンはタイマ/カウンタ1の比較B一致用外部出力として扱えます。この機能を扱うにはこのピンが出力として設定(DDB4=1)されなければなりません。このOC1Bピンはタイマ機能のPWM動作用出力ピンでもあります。

PCINT4: ピン変化割り込み4入力。PB4ピンは外部割り込み元としても扱えます。

• OC1A/PCINT3 - ポートB ビット3 : PB3

OC1A: タイマ/カウンタ1の比較A一致出力。PB3ピンはタイマ/カウンタ1の比較A一致用外部出力として扱えます。この機能を扱うにはこの ピンが出力として設定(DDB3=1)されなければなりません。このOC1Aピンはタイマ機能のPWM動作用出力ピンでもあります。

PCINT3: ピン変化割り込み3入力。PB3ピンは外部割り込み元としても扱えます。

• OC0A/PCINT2 - ポートB ビット2 : PB2

OCOA: タイマ/カウンタ0の比較A一致出力。PB2ピンはタイマ/カウンタ0の比較A一致用外部出力として扱えます。この機能を扱うにはこの ピンが出力として設定(DDB2=1)されなければなりません。このOC0Aピンはタイマ機能のPWM動作用出力ピンでもあります。

PCINT2: ピン変化割り込み2入力。PB2ピンは外部割り込み元としても扱えます。

• AIN1/PCINT1 - ポートB ビット1 : PB1

AIN1: アナログ比較器の反転入力。アナログ比較器の機能を妨げるデジタル ポート機能を避けるため、内部プルアップをOFFにした入力としてポート ピンを設定してください。

PCINT1: ピン変化割り込み1入力。PB1ピンは外部割り込み元としても扱えます。

• AIN0/PCINT0 - ホートB ビット0 : PB0

AINO: アナログ比較器の非反転入力。アナログ比較器の機能を妨げるデジタルポート機能を避けるため、内部プルアップをOFFにした入力としてポート ピンを設定してください。

PCINTO: ピン変化割り込み0入力。PB0ピンは外部割り込み元としても扱えます。

表25.と表26.はポートBの交換機能を33頁の図25.で示される交換信号に関連付けます。(訳注:原書無効行削除)

# 表25. ポートB7~4の交換機能用交換信号

| 信号名   | PB7/USCK/SCL/PCINT7  | PB6/DO/PCINT6 | PB5/DI/SDA/PCINT5    | PB4/OC1B/PCINT4 |

|-------|----------------------|---------------|----------------------|-----------------|

| PUOE  | 2線USI                | 0             | 0                    | 0               |

| PUOV  | 0                    | 0             | 0                    | 0               |

| DDOE  | 2線USI                | 0             | 2線USI                | 0               |

| DDOV  | (SCL保持+PORTB7)+DDB7  | 0             | (SDA+PORTB5)•DDB5    | 0               |

| PVOE  | 2線USI·DDB7           | 3線USI         | 2線USI·DDB5           | OC1B許可          |

| PVOV  | 0                    | DO            | 0                    | OC1B            |

| PTOE  | USI許可                | 0             | 0                    | 0               |

| DIEOE | (PCIE•PCINT7)+USISIE | PCIE•PCINT6   | (PCIE•PCINT5)+USISIE | PCIE•PCINT4     |

| DIEOV | 1                    | 1             | 1                    | 1               |

| DI    | USCK/SCL/PCINT7入力    | PCINT6入力      | DI/SDA/PCINT5入力      | PCINT4入力        |

| AIO   | _                    | -             | _                    | -               |

# 表26. ポートB3~0の交換機能用交換信号(訳注:矛盾点を一部修正)

| 信号名   | PB3/OC1A/PCINT3 | PB2/OC0A/PCINT2 | PB1/AIN1/PCINT1     | PB0/AIN0/PCINT0     |

|-------|-----------------|-----------------|---------------------|---------------------|

| PUOE  | 0               | 0               | 0                   | 0                   |

| PUOV  | 0               | 0               | 0                   | 0                   |

| DDOE  | 0               | 0               | 0                   | 0                   |

| DDOV  | 0               | 0               | 0                   | 0                   |

| PVOE  | OC1A許可          | OC0A許可          | 0                   | 0                   |

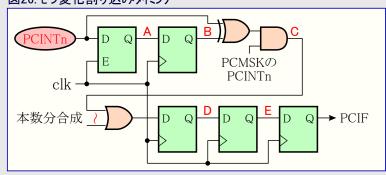

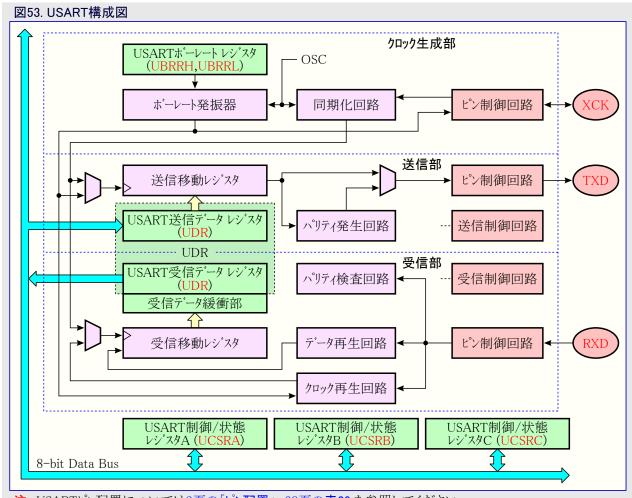

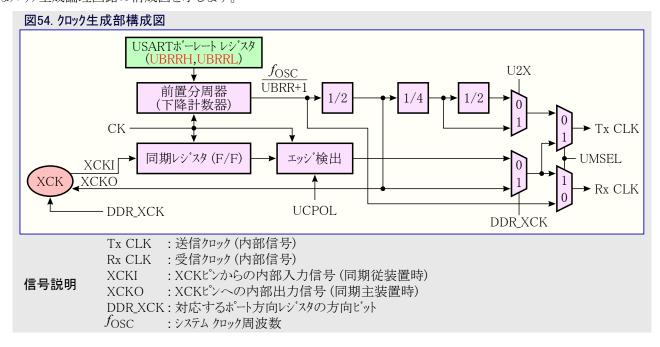

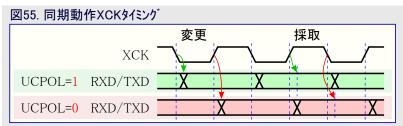

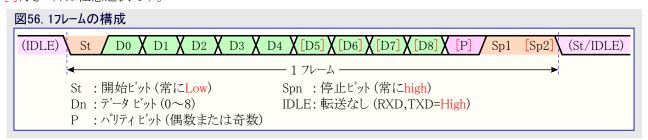

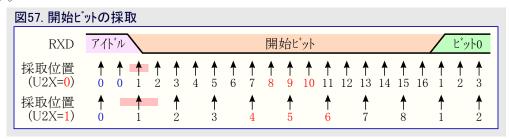

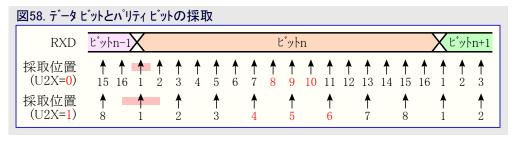

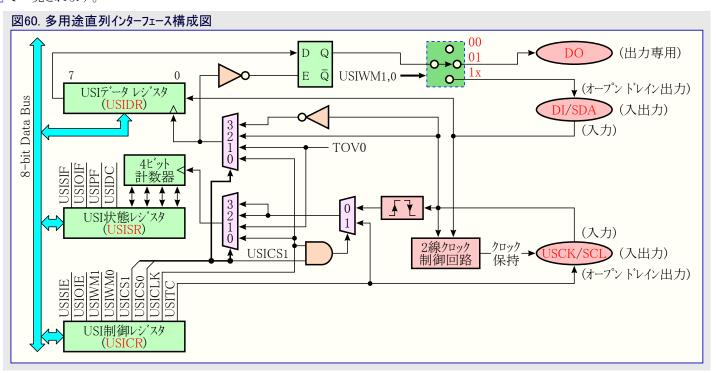

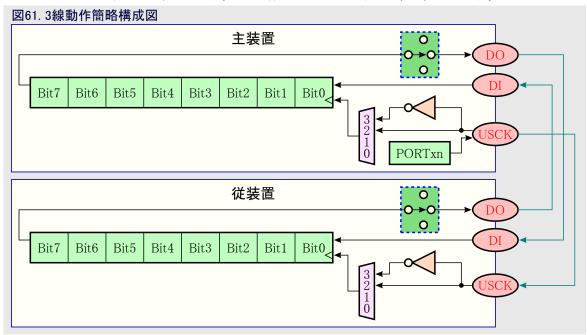

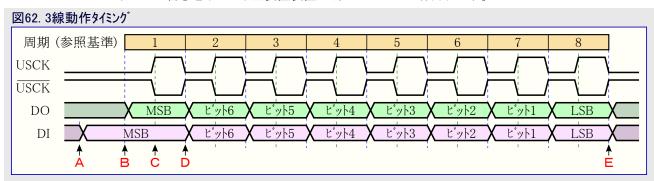

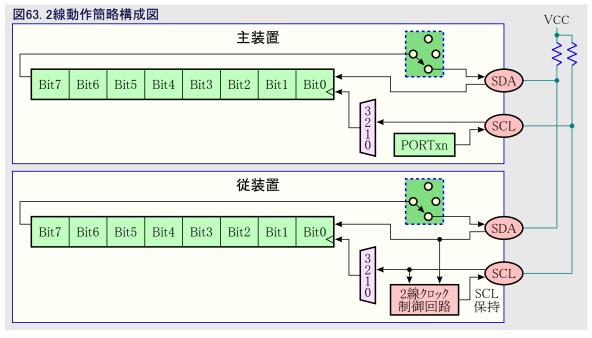

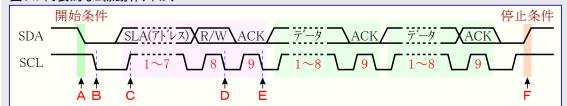

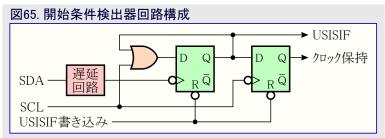

| PVOV  | OC1A            | OC0A            | 0                   | 0                   |