# 特徴

- 高性能、低消費AVR® 8ビット マイクロ コントローラ

- 進化したRISC構造

- ・強力な123命令(多くは1周期で実行)

- 32個の1バイト長汎用レジスタ

- ・完全なスタティック動作

- ・20MHz時、20MIPSに達する高速動作

## ■ データ メモリと不揮発性プログラム メモリ

- 実装自己書き換え(ISP)可能な2K/4Kバイト(1K/2K語)フラッシュ メモリ内蔵

- ・10,000回の書き換え可能

- 実装書き換え可能な128/256バイトのEEPROM

- ・100,000回の書き換え可能

- 128/256バイトの内蔵SRAM

- プログラム用フラッシュ メモリとデータ用EEPROM保護用の設定可能な施錠機能

#### ■ 内蔵周辺機能

- ・分離された前置分周器と比較動作付き1つの8ビットタイマ/カウンタ

- ・分離された前置分周器と比較、捕獲動作付き1つの16ビットタイマ/カウンタ

- 4つのPWM出力

- ・アナログ比較器

- ・設定可能な専用発振器付きウォッチドッグ、タイマ

- ・多用途直列インターフェース(USI)

- · 全二重USART

#### ■ 特殊マイクロ コントローラ機能

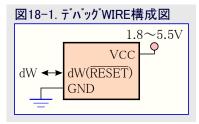

- ・デバッグWIRE内蔵デバッグ機能

- ・SPIポート経由の実装書き込み

- ・外部及び内部の割り込み

- ・アイドル、パワーダウン、スタンバイの3つの低消費動作

- ・強化した電源ONJセット回路

- ・設定可能な低電圧検出器(BOD)回路

- ・校正付き内蔵RC発振器

### ■ I/Oと外囲器

- 18ビットの設定可能なI/O

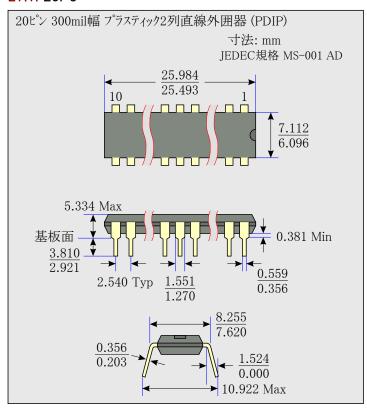

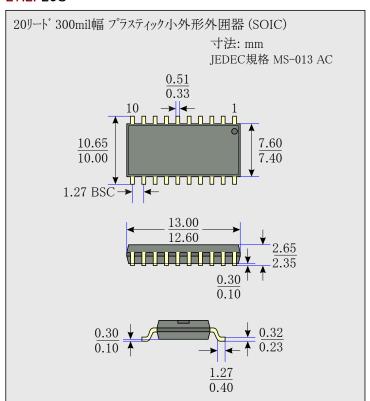

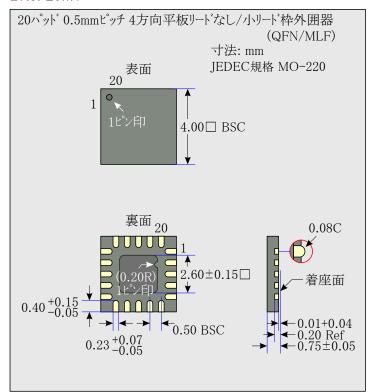

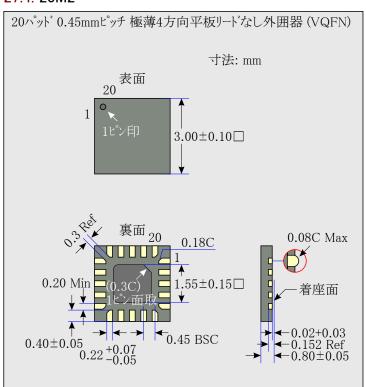

- ・20ピンPDIP、20リードSOIC、20パッドMLF/VQFN

#### ■ 動作電圧

· 1.8∼5.5V

#### ■ 動作速度

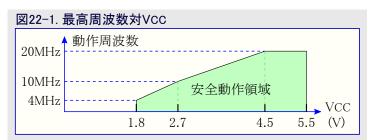

- $0\sim4 \text{MHz}/1.8\sim5.5 \text{V}$

- $0 \sim 10 \text{MHz} / 2.7 \sim 5.5 \text{V}$

- $0\sim20\text{MHz}/4.5\sim5.5\text{V}$

### ■ 工業用温度範囲

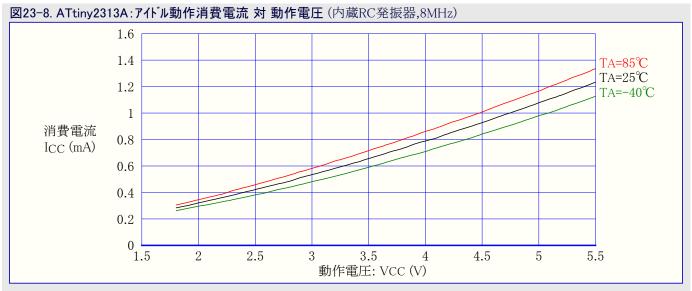

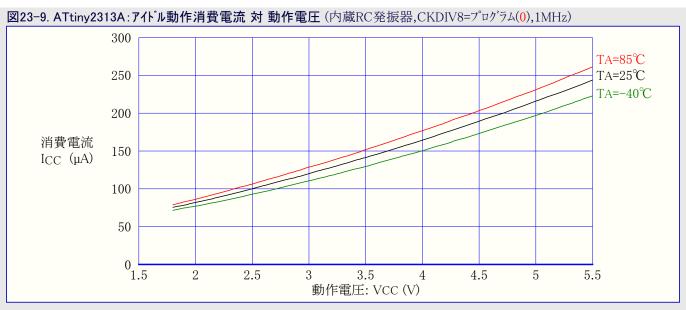

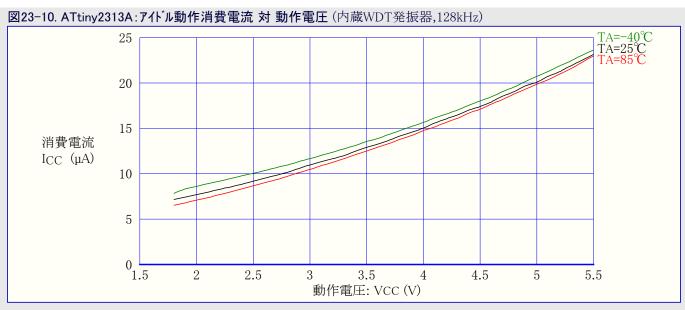

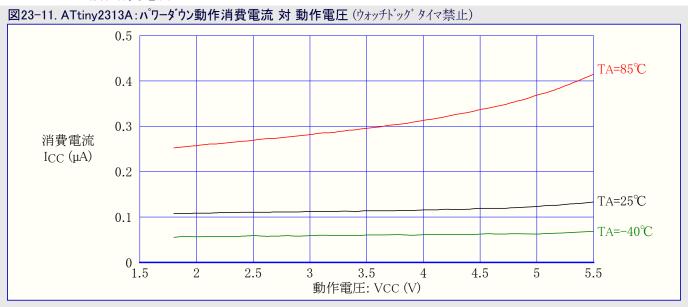

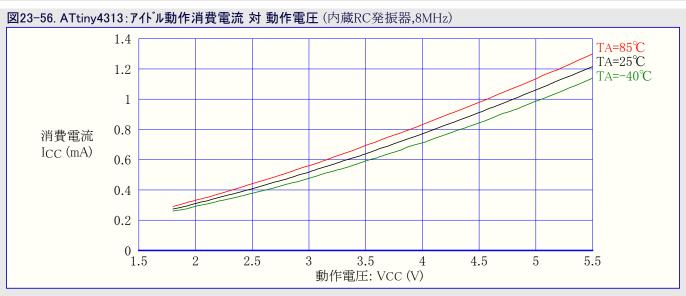

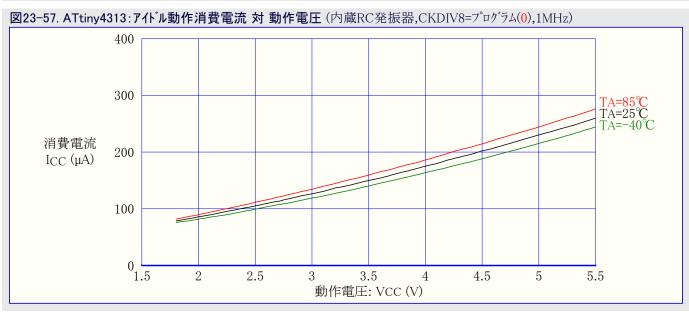

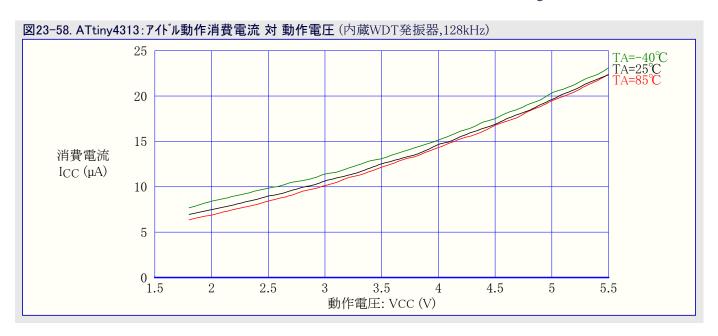

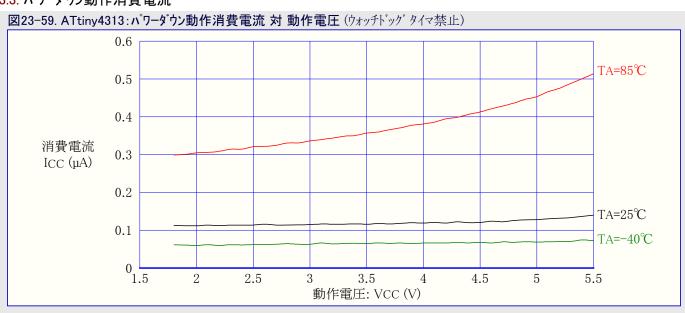

#### ■ 代表消費電力

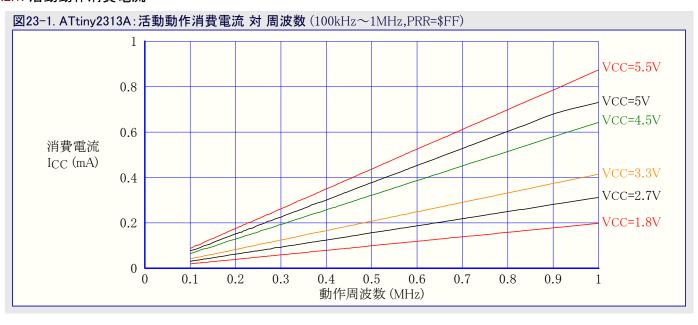

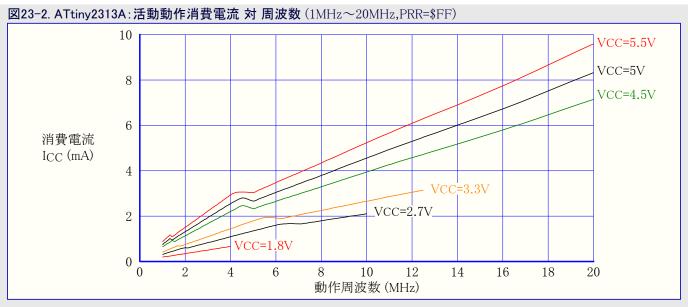

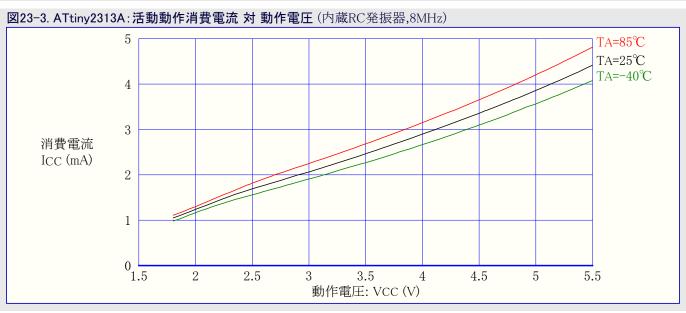

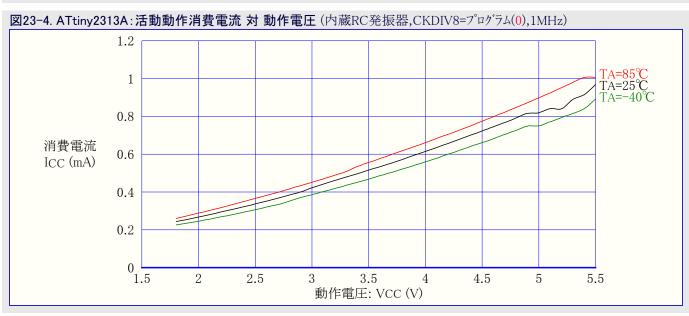

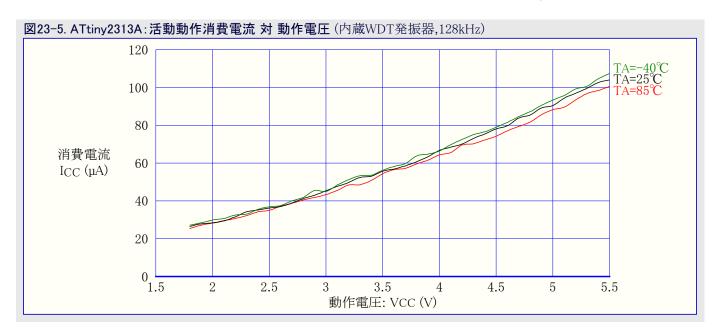

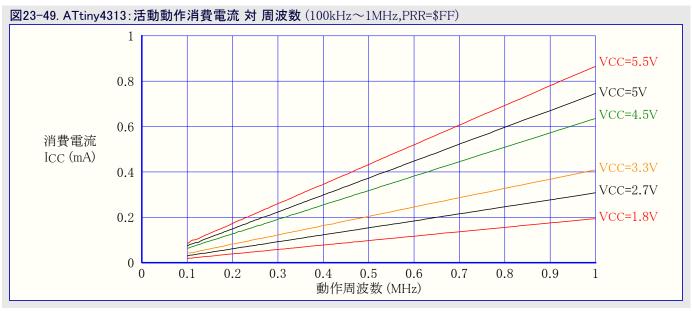

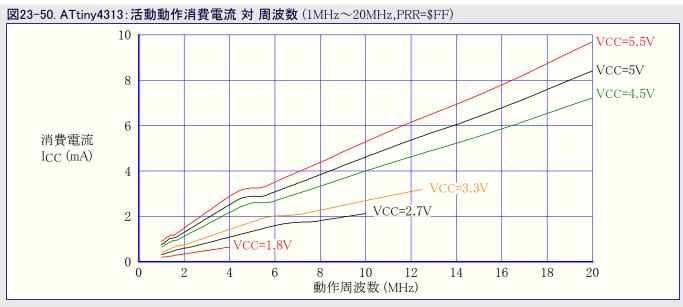

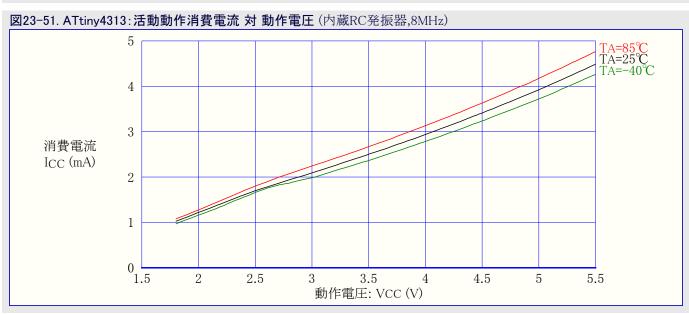

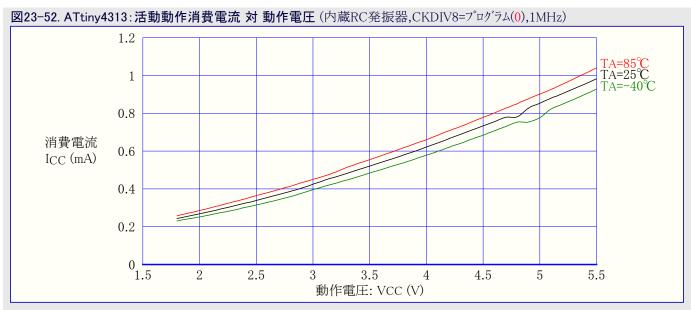

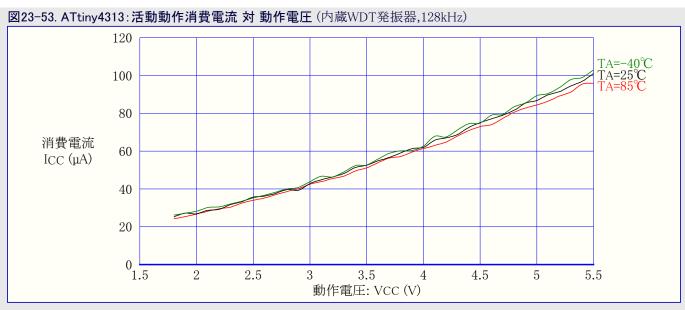

活動動作 : 190µA (1.8V,1MHz)

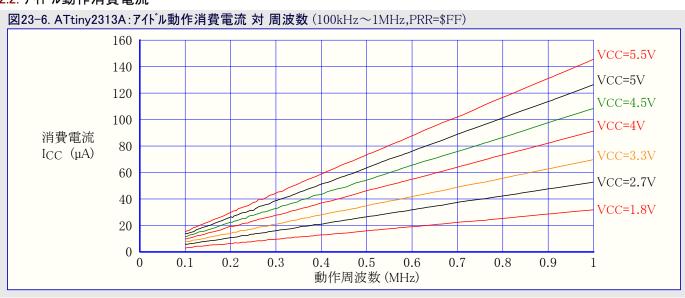

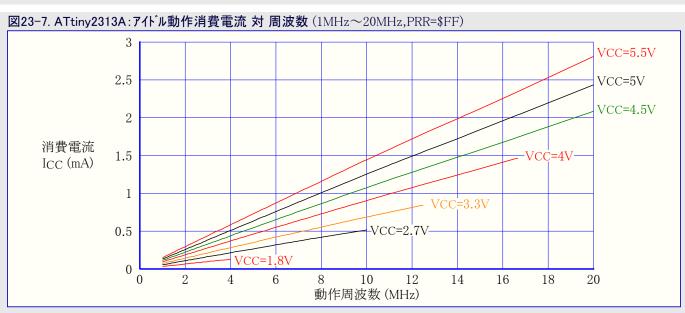

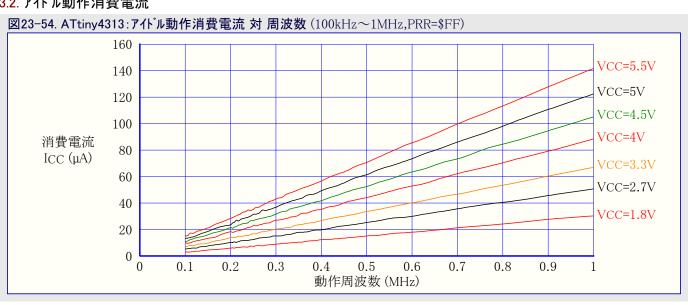

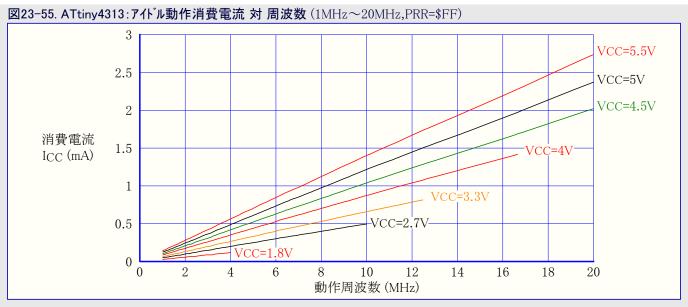

・アイトル動作 : 24µA (1.8V,1MHz)

・パワータウン動作: 0.1µA (1.8V,25℃)

本書は一般の方々の便宜のため有志により作成されたもので、Atmel社とは無関係であることを御承知ください。しおりの[はじめに]での内容にご注意ください。

ATtiny2313A ATtiny4313

Rev. 8246B-09/11, 8246BJ4-06/22

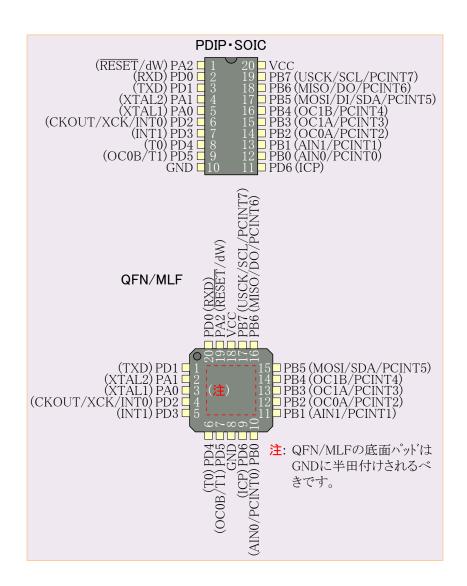

# 1. ピン配置

## 1.1. ピン概要

#### 1.1.1. VCC

電源ピン。

#### 1.1.2. GND

接地ピン。

#### 1.1.3. PA2~PA0 (本°-トA)

ポートAは(ビット単位で選択される)内蔵プルアップ抵抗付きの3ビット双方向入出力ポートです。ポートA出力緩衝部はRESET能力を持つ PA2を除いて、共に高い吐き出し/吸い込み能力の対称駆動特性を持ちます。PA2をRESETピンの代わりに入出力ピンとして使うには RSTDISBLヒューズをプログラム(0)してください。入力の時にプルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートAピンには吐き出し電流が流れます。 リセット条件が有効になると、クロックが走行していなくても、ポートAピンはHi-Zにされます。

ポートAは40頁で示されるATtiny2313A/4313の様々な特殊機能も扱います。

#### 1.1.4. PB7~PB0 (ホートB)

ポートBは(ビット単位で選択される)内蔵プルアップ抵抗付きの8ビット双方向入出力ポートです。ポートB出力緩衝部は共に高い吐き出し/吸い込み能力の対称駆動特性です。入力の時にプルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートBピンには吐き出し電流が流れます。リセット条件が有効になると、クロックが走行していなくても、ポートBピンはHi-Zにされます。

ポートBは41頁で示されるATtiny2313A/4313の様々な特殊機能も扱います。

#### 1.1.5. PD6~PD0 (ホートD)

ポートDは(ビット単位で選択される)内蔵プルアップ抵抗付きの7ビット双方向入出力ポートです。ポートD出力緩衝部は共に高い吐き出し/吸い込み能力の対称駆動特性です。入力の時にプルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートDピンには吐き出し電流が流れます。 リセット条件が有効になると、クロックが走行していなくても、ポートDピンはHi-Zにされます。

ポートDは43頁で示されるATtiny2313A/4313の様々な特殊機能も扱います。

# 1.1.6. RESET

リセット入力。リセット ピンが禁止されていない場合に例えクロックが走行していなくても、最小パルス幅より長いこのピンのLowレヘールはリセットを生成します。最小パルス幅は134頁の表22-3.で与えられます。より短いパルスはリセットの生成が保証されません。リセット入力はPA2及びdW(デバックWIRE)との切り替え機能です。

リセット ピンは(弱い)入出力ピンとしても使えます。

## 1.1.7. XTAL1

発振器反転増幅器への入力と内部クロック操作回路への入力。XTAL1はPA0との切り替え機能です。

### 1.1.8. XTAL2

発振器反転増幅器からの出力。XTAL2はPA1との切り替え機能です。

# 2. 概要

ATtiny2313A/4313はAVR強化RISC構造を基にした低消費CMOS 8ビットマイクロコントローラです。1周期での強力な命令の実行によって、ATtiny2313A/4313はMHzあたり1MIPSに達する単位処理量を成し遂げ、処理速度対消費電力の最適化を設計者に許します。

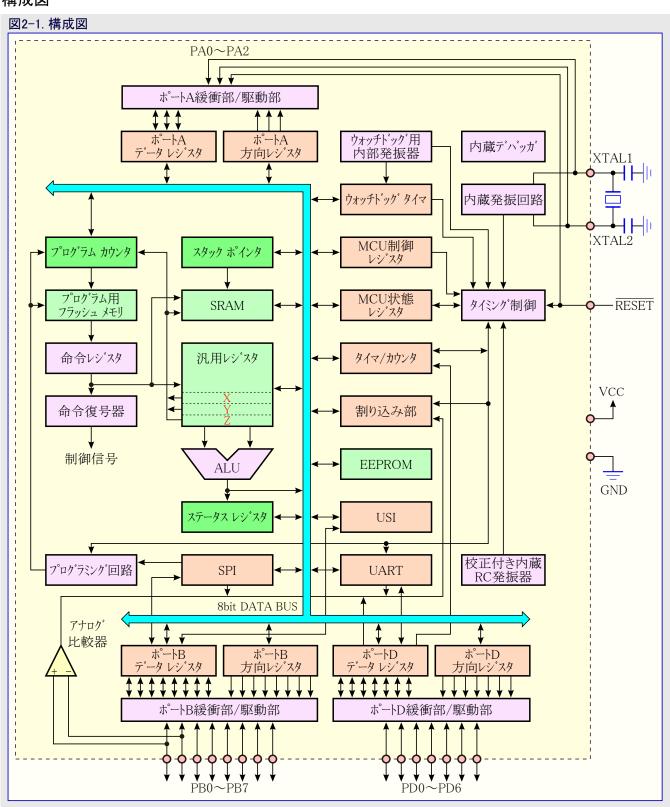

## 2.1. 構成図

AVRコアは32個の汎用作業レジスタと豊富な命令群の組み合わせです。32個の全レジスタはALU(Arithmetic Logic Unit)に直結され、レジスタ間命令は1クロック周期で実行されます。AVR構造は現状のCISC型マイクロコントローラに対して最大10倍の単位処理量向上効果があります。

ATtiny2313A/4313は2K/4Kバトの実装書き込み可能なフラッシュメモリ、128/256バトのEEPROM、128/256バトのSRAM、18本の汎用入出力線、32個の汎用作業レジスタ、内蔵デバッケ用の単線インターフェース、比較動作付きの2つの柔軟なタイマ/カウンタ、内部及び外部割り込み、設定変更可能な直列USART、開始条件検出器付き多用途直列インターフェース(USI)、内蔵発振器付きの設定変更可能なウオッチドッケ・タイマ、ソフトウェアで選択できる3つの低消費動作を提供します。アイドル動作はCPUを停止し、一方SRAM、タイマ/カウンタ、割り込み機構に機能の継続を許します。パワーダウン動作は発振器を停止しますがレジスタの内容を保護し、以降のハードウェアリセットか外部割り込みまで他の全機能を禁止します。スタンバイ動作ではクリスタル発振子/セラミック振動子用発振器が動作する一方で、デバイスのその他は休止します。これは低消費電力と非常に速い起動の組み合わせを許します。

本デバイスはAtmelの高密度不揮発性メモリ技術を使って製造されています。内蔵の実装書き換え(ISP)可能なフラッシュメモリはプログラムメモリに使え、規定の不揮発性メモリ書き込み器かSPI直列インターフェース経由によって再書き込みができます。モノリシックチップ上の実装書き換え可能なフラッシュメモリと拡張された8ビットRISC型CPUの組み合わせによるATtiny2313A/4313は、多くの組み込み制御の応用に対して高度な柔軟性と対費用効果をもたらす強力なマイクロコントローラです。

ATtiny2313A/4313 AVRはCコンハペイラ、マクロ アセンフ・ラ、デ・バッカ・、シミュレータ、インサーキット エミューレータ、評価キットを含む完全なプログラム及びシステム開発ツールで支援されます。

# 2.2. ATtiny2313AとATtiny4313間の違い

ATtiny2313AとATtiny4313はメモリ容量だけが異なります。表2-1.は2つのデバイスについてメモリ容量の違いを要約します。

| 表2-1. メモリ量要約 |           |        |        |  |  |  |  |

|--------------|-----------|--------|--------|--|--|--|--|

| デバイス名        | フラッシュ メモリ | EEPROM | SRAM   |  |  |  |  |

| ATtiny2313A  | 2Kバイト     | 128バイト | 128バイト |  |  |  |  |

| ATtiny4313   | 4Kバイト     | 256バイト | 256バイト |  |  |  |  |

# 3. 諸注意

## 3.1. 資料

包括的なデータシート、応用記述、開発ツール群はhttp://www.atmel.com/avrでのダウンロードで利用可能です。

# 3.2. コート 例

この資料はデバイスの様々な部分の使用法を手短に示す簡単なコート・例を含みます。これらのコート・例はアセンブルまたはコンパイルに先立ってデバイス定義へッタ・ファイルがインクルートされると仮定します。全てのCコンパイラ製造業者がヘッタ・ファイル内にヒット定義を含めるとは限らず、またCでの割り込みの扱いがコンパイラに依存することに注意してください。より多くの詳細についてはCコンパイラの資料で確認してください。

拡張I/O領域に配置したI/Oレジスタに対し、IN, OUT, SBIS, SBIC, CBI, SBI命令は拡張I/O領域へのアクセスを許す命令に置き換えられなければなりません。代表的にはSBRS, SBRC, SBR, CBR命令と組み合わせたLDS, STS命令です。全てのAVRデバイスが拡張I/O領域を含む訳でないことに注意してください(訳補:本デバイスに拡張I/O領域はありません)。

### 3.3. データ保持力

信頼性証明結果はデータ保持誤り率の反映を示し、20年以上/85℃または100年以上/25℃で1PPMよりずっと小さな値です。

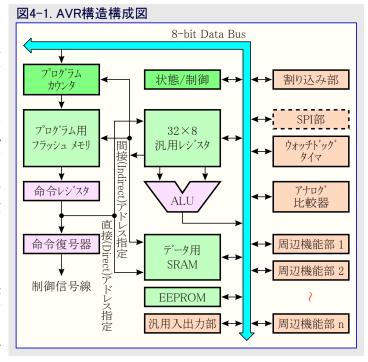

## 4. CPU コア

本項はAVRコア構造を一般的に説明します。このCPUコアの主な機能は正しいプログラム実行を保証することです。従ってCPUはメモリアクセス、計算実行、周辺制御、割り込み操作ができなければなりません。

# 4.1. 構造概要

最大効率と平行処理のため、AVRはプログラムとデータに対してメモリとハンスを分離するハーハート・構造を使います。プログラムメモリ内の命令は単一段のハプイプラインで実行されます。1命令の実行中に次の命令がプログラムメモリから事前取得されます。この概念は全部のクロック周期で命令実行を可能にします。プログラムメモリは実装書き換え可能なフラッシュメモリです。

高速レジスタファイルは1クロック周期アクセスの32個の8ビット長汎用レジスタを含みます。これは1クロック周期ALU(Arithmetic Logic Unit)操作を許します。代表的なALU操作では2つのオペラントがレジスタファイルからの出力で、1クロック周期内でその操作が実行され、その結果がレジスタファイルに書き戻されます。

32個中の6つのレシ、スタは効率的なアト・レス計算ができるデータ空間アト・レス指定用に3つの16ビット長間接アト・レスポーインタ用レシ、スタとして使われます。これらアト・レスポーインタの1つはプログラム用フラッシュメモリ内の定数表参照用アト・レスポーインタとしても使えます。これら16ビット長付加機能レシ、スタはX,Y,Zレシ、スタで、本項内で後述されます。

ALUはレシ、スタ間またはレシ、スタと定数間の算術及び論理操作を支援します。単一レシ、スタ操作もALUで実行できます。算術演算操作後、操作結果についての情報を反映するために、ステータスレジ、スタ (SREG)が更新されます。

プログラムの流れは条件/無条件分岐や呼び出し命令によって提供され、全アドレス空間を直接アドレス指定できます。AVR命令の多くは

16ビット語(ワード)形式です。全てのプログラム メモリのアドレスは(<mark>訳注</mark>:定数のみを除き)16または32ビット長命令を含みます。

割り込みやサブルーチン呼び出し中、戻りアドレスを示すプログラム カウンタ(PC)はスタックに保存されます。スタックは一般的なデータ用SRAM上に実際には割り当てられ、従ってスタック容量は全SRAM容量とSRAM使用量でのみ制限されます。全ての使用者プログラムはリセット処理ルーチンで(サブルーチン呼び出しや割り込みが実行される前に)、スタック ポインタ(SP)を初期化しなければなりません。SPはI/O空間で読み書きアクセスが可能です。データ用SRAMはAVR構造で支援される5つの異なるアドレス指定種別を通して容易にアクセスできます。

AVR構造に於けるメモリ空間は全て直線的な普通のメモリ配置です。

柔軟な割り込み部にはI/O空間の各制御レシ、スタとステータスレシ、スタ(SREG)の特別な全割り込み許可(I)ビットがあります。全ての割り込みは割り込みへ、クタ表に個別の割り込みへ、クタを持ちます。割り込みには割り込みへ、クタ表の位置に従う優先順があります。下位側割り込みへ、クタアドレスが高い優先順位です。

I/Oメモリ空間は制御レジスタや他のI/O機能としてCPU周辺機能用の64アドレスを含みます。I/Oメモリは直接またはレジスタ ファイルの次のデータ空間位置\$20~\$5Fとしてアクセスできます。

## **4.2. ALU** (Arithmetic Logic Unit)

高性能なAVRのALUは32個の全汎用レジスタに直接接続され動作します。汎用レジスタ間または汎用レジスタと即値間の演算操作は単一クロック周期内で実行されます。ALU操作は算術演算、論理演算、ビット操作の3つの主な種類に大別されます。符号付きと符号なし両方の乗算と固定小数点形式を支援する乗算器(乗算命令)も提供する構造の実装(製品)もあります。詳細記述については「命令要約」章をご覧ください。

# 4.3. ステータス レジスタ (Status Register) SREG

ステータスレジスタは最も直前に実行した演算命令の結果についての情報を含みます。この情報は条件処理を行うためのプログラムの流れ変更に使えます。ステータスレジスタは「命令一式手引書」で詳述したように、全てのALU操作後、更新されることに注目してください。これは多くの場合でそれ用の比較命令使用の必要をなくし、高速でより少ないコードに帰着します。

ステータス レシ スタは割り込み処理ルーチン移行時の保存と割り込みからの復帰時の回復(復帰)が自動的に行われません。これはソフトウェアによって扱われなければなりません。

AVRのステータス レシ、スタ(SREG)は次のように定義されます。

| ピット         | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |      |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$3F (\$5F) | I   | T   | Н   | S   | V   | N   | Z   | С   | SREG |

| Read/Write  | R/W |      |

| 初期値         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

### ■ ビット7 - I: 全割り込み許可 (Global Interrupt Enable)

全割り込み許可ビットは割り込みが許可されるために設定(1)されなければなりません。その時の個別割り込み許可制御は独立した制御レジスタで行われます。全割り込み許可ビットが解除(0)されると、個別割り込み許可設定に拘らず、どの割り込みも許可されません。I ビットは割り込みが起こった後にハードウェアによって解除(0)され、後続の割り込みを許可するために、RETI命令によって設定(1)されます。Iビットは「命令一式手引書」で記述されるようにSEIやCLI命令で応用(プログラム)によって設定(1)や解除(0)もできます。

#### ■ L'yh6 - T: L'yh変数 (Bit Copy Storage)

ビット複写命令、BLD(Bit LoaD)とBST(Bit STore)は操作したビットの転送元または転送先として、このTビットを使います。レジスタ ファイルのレジスタからのビットはBST命令によってTに複写でき、TのビットはBLD命令によってレジスタ ファイルのレジスタ内のビットに複写できます。

#### **■ ビット5 - H** : **ハーフキャリー フラク** (Half Carry Flag)

ハーフキャリー(H)フラグはいくつかの算術操作でのハーフキャリーを示します。ハーフキャリーはBCD演算に有用です。詳細情報については「<mark>命令</mark> 要約」記述をご覧ください。

#### ■ ビット4 - S: 符号 (Sign Bit, S= N Ex-OR V)

Sフラグは常に負(N)フラグと2の補数溢れ(V)フラグの排他的論理和です。詳細情報については「命令要約」記述をご覧ください。

#### ■ ビット3 - V: 2の補数溢れフラグ(2's Complement Overflow Flag)

2の補数溢れ(V)フラグは2の補数算術演算を支援します。詳細情報については「命令要約」記述をご覧ください。

#### **■ Ľット2 - N**: **負フラク** (Negative Flag)

負(N)フラグは算術及び論理操作での負の結果(MSB=1)を示します。詳細情報については「命令要約」記述をご覧ください。

#### **■ L**"y**h1** - **Z** : **t**"**D 750**" (Zero Flag)

ゼロ(Z)フラグは算術及び論理操作でのゼロ(0)の結果を示します。詳細情報については「命令要約」記述をご覧ください。

#### **■ L** \* **vl O O** : **キャリー フラク** \* (Carry Flag)

キャリー(C)フラグは算術及び論理操作でのキャリー(またはボロー)を示します。詳細情報については「**命令要約**」記述をご覧ください。

## 4.4. 汎用レジスタファイル

このレシ、スタファイルはAVRの増強したRISC命令群用に最適化されています。必要な効率と柔軟性を達成するために、次の入出力機構がレシ、スタファイルによって支援されます。

- ・1つの8ビット出力オペラントと1つの8ビットの結果入力

- ・2つの8ビット出力オペラントと1つの8ビットの結果入力

- ・2つの8ビット出力オペラントと1つの16ビットの結果入力

- ・1つの16ビット出力オペランドと1つの16ビットの結果入力

図4-2.はCPU内の32個の汎用作業レジスタの構造を示します。 レジスタファイルを操作する殆どの命令は全てのレジスタに直接アクセスし、それらの殆どは単一周期命令です。

図4-2.で示されるように各レジスタは使用者データ空間の最初の32位置へ直接的に配置することで、それらはデータメモリアトレスも割り当てられます。例え物理的にSRAM位置として実装されていなくてもX,Y,Zレジスタ(ポインタ)がレジスタファイル内のどのレジスタの指示にも設定できるように、このメモリ構成は非常に柔軟なレジスタのアクセスを提供します。

| <u> </u>    | AVR CPU 汎用レジスタヤ | 構成凶  |              |

|-------------|-----------------|------|--------------|

|             | 7 0             | アトレス |              |

|             | R0              | \$00 |              |

|             | R1              | \$01 |              |

|             | R2              | \$02 |              |

|             | }               |      |              |

|             | R13             | \$0D |              |

|             | R14             | \$0E |              |

| >n ⊞        | R15             | \$0F |              |

| 汎用<br>レシ゛スタ | R16             | \$10 |              |

| ファイル        | R17             | \$11 |              |

| . , (,,     | }               |      |              |

|             | R26             | \$1A | Xレジスター・下位バイト |

|             | R27             | \$1B | 上位ハイト        |

|             | R28             | \$1C | Yレジスタ 下位バイト  |

|             | R29             | \$1D | 上位ハイト        |

|             | R30             | \$1E | フレシブスタ 下位バイト |

|             | R31             | \$1F | 上位バイ         |

#### 4.4.1. Xレシ、スタ、 Yレシ、スタ、 Zレシ、スタ

R26~R31レジスタには通常用途の使用にいくつかの追加機能があります。これらのレジスタはデータ空間の間接アトンス指定用の16ビットアトンスポインタです。3つのX,Y,Z間接アトンスレジスタは図4-3.で記載したように定義されます。

種々のアドレス指定種別で、これらのアドレス レジスタは固定変位、 自動増加、自動減少としての機能を持ちます(詳細については 「命令一式手引書」をご覧ください)。

| 図4-3. X,Y,Z | レジス | <b>Þ構成図</b> |     |            |   |

|-------------|-----|-------------|-----|------------|---|

|             | 15  | XH (上位)     |     | XL (下位)    | 0 |

| X レジスタ      | 7   | R27 (\$1B)  | 0 7 | R26 (\$1A) | 0 |

|             | 15  | YH (上位)     |     | YL (下位)    | 0 |

| Yレジスタ       | 7   | R29 (\$1D)  | 0 7 | R28 (\$1C) | 0 |

|             | 15  | ZH (上位)     |     | ZL (下位)    | 0 |

| Z レジスタ      | 7   | R31 (\$1F)  | 0 7 | R30 (\$1E) | 0 |

|             |     |             |     |            |   |

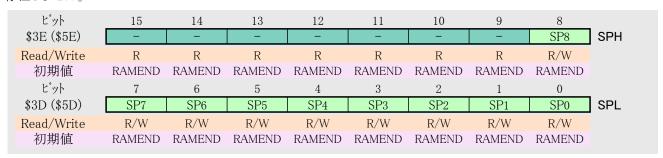

## 4.5. スタック ホ°インタ (Stack Pointer) SPL (SP)

スタックは主に一時データの保存、局所変数の保存、割り込みとサブルーチン呼び出し後の戻りアドレスの保存に使われます。スタック ポインタ レジスタは常にこのスタックの先頭(<mark>訳注</mark>:次に使われるべき位置)を指し示します。スタックが高位メモリから低位メモリへ伸長するように実行されることに注意してください。これはスタックへのPUSH命令はスタック ポインタを減少するという意味です。

スタック ポインタはサブルーチンや割り込みのスタックが配置されるデータSRAMのスタック領域を指し示します。データSRAM内のスタック空間はサブルーチン呼び出しの実行や割り込みの許可の何れにも先立ってプログラムによって定義されなければなりません。スタック ポインタは、60以上を指示するように設定されなければなりません。スタック ポインタはPUSH命令でデータがスタックに格納されると-1され、サブルーチン呼び出しや割り込みで戻りアドレスがスタックに格納されると-2されます。スタック ポインタはPOP命令でデータがスタックから引き出されると+1され、サブルーチンからの復帰(RET)命令や割り込みからの復帰(RETI)命令でアドレスがスタックから引き出されると+2されます。

AVRのスタック ポインタはI/O空間内の2つの8ビット レジスタとして実装されます。実際に使われるビット数は(そのデバイス)実装に依存します。SPLだけが必要とされる程に小さいAVR構造の実装(デバイス)のデータ空間もあることに注意してください。その場合、SPHレジスタは存在しません。

(<mark>訳補</mark>) 内蔵SRAMはATtiny2313Aが128バイト(\$0060~\$00DF)、ATtiny4313が256バイト(\$0060~\$015F)です。従って、ATtiny2313AではSP8が利用できません。RAMENDはATtiny2313Aが\$00DF(0000 0000 1101 1111)、ATtiny4313が\$015F(0000 0001 0101 1111)になります。

## 4.6. 命令実行タイミング

本項は命令実行の一般的なアクセス タイミング の概念を記述します。AVR CPUはチップ(デバイス)用に選択したクロック元から直接的に生成したCPUクロック(clk<sub>CPU</sub>)によって駆動されます。内部クロック分周は使われません。

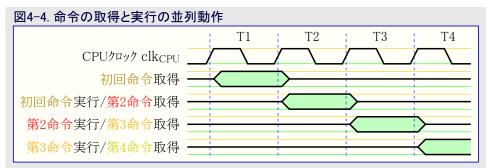

図4-4.はハーハート、構造と高速アクセスレジスタファイルの概念によって可能とされる並列の命令取得と命令実行を示します。これは機能対費用、機能対クロック、機能対電源部に関する好結果と対応するMHzあたり1MIPSを達成するための基本的なパイプラインの概念です。

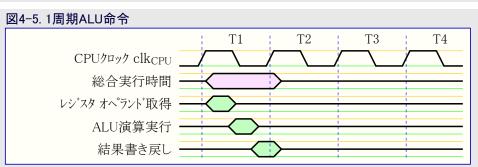

図4-5.はレシ、スタファイルに対する内部タイミングの概念を示します。単一クロック周期で2つのレシ、スタオペラント、を使うALU操作が実行され、その結果が転送先レジ、スタへ書き戻されます。

## 4.7. リセットと割り込みの扱い

AVRは多くの異なる割り込み元を提供します。これらの割り込みと独立したリセット ベクタ各々はプログラム メモリ空間内に独立したプログラム ベクタを持ちます。全ての割り込みは割り込みを許可するため、ステータス レジスタ(SREG)の全割り込み許可(I)ビットと共に論理1が書かれなければならない個別の許可ビットを割り当てられます。

プログラム メモリ空間の最下位アドレスは既定でリセットと割り込みへクタとして定義されます。 へクタの完全な一覧は31頁の「**割り込み**」で示されます。この一覧は各種割り込みの優先順位も決めます。 下位側アドレスがより高い優先順位です。 リセットが最高優先順位で、次が外部割り込み要求の(INTO)です。 より多くの情報については31頁の「割り込み」を参照してください。

割り込みが起こると全割り込み許可(I)ビットが解除(0)され、全ての割り込みは禁止されます。使用者ソフトウェアは多重割り込みを許可するため、全割り込み許可(I)ビットへ論理1を書けます。その後全ての許可した割り込みが現在の割り込みルーチンで割り込めます。全割り込み許可(I)ビットは割り込みからの復帰(RETI)命令が実行されると、自動的に設定(1)されます。

根本的に2つの割り込み形式があります。1つ目の形式は割り込み要求フラグを設定(1)する事象によって起動されます。これらの割り込みでは割り込み処理ルーチンを実行するために、プログラム カウンタは対応する現実の割り込みへ、クタを指示し、ハートウェアが対応する割り込み要求フラグを解除(0)します。割り込み要求フラグは解除(0)されるべきフラグのビット位置へ論理1を書くことによっても解除(0)できます。対応する割り込み許可ビットが解除(0)されている間に割り込み条件が起こると、割り込み要求フラグが設定(1)され、割り込みが許可されるか、またはこのフラグがソフトウェアによって解除(0)されるまで記憶(保持)されます。同様に、全割り込み許可(1)ビットが解除(0)されている間に1つまたはより多くの割り込み条件が起こると、対応する割り込み要求フラグが設定(1)されて全割り込み許可(1)ビットが設定(1)されるまで記憶され、その(I=1)後で優先順に従って実行されます。

2つ目の割り込み形式は割り込み条件が存在する限り起動し(続け)ます。これらの割り込みは必ずしも割り込み要求フラグを持っているとは限りません。割り込みが許可される前に割り込み条件が消滅すると、この割り込みは起動されません。

AVRが割り込みから抜け出すと常に主プログラムへ戻り、何れかの保留割り込みが扱われる前に1つ以上の命令を実行します。

ステータス レジスタ(SREG)は割り込みルーチンへ移行時の保存も、復帰時の再設定も自動的に行われないことに注意してください。これはソフトウェアによって扱われなければなりません。

割り込みを禁止するためにCLI命令を使うと、割り込みは直ちに禁止されます。CLI命令と同時に割り込みが起こっても、CLI命令後に割り込みは実行されません。次例は時間制限EEPROM書き込み手順中に割り込みを無効とするために、これがどう使えるかを示します。

| アセンブリ言語プログラム例                  |                                                                                                                    |                                                                                                                                    |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| IN<br>CLI<br>SBI<br>SBI<br>OUT | R16, SREG  EECR, EEMPE EECR, EEPE SREG, R16                                                                        | ;ステータス レジスタを保存<br>;EEPROM書き込み手順中割り込み禁止<br>;EEPROM主書き込み許可<br>;EEPROM書き込み開始<br>;ステータス レジスタを復帰                                        |

| C言語プログラム例                      |                                                                                                                    |                                                                                                                                    |

| cSREG<br>dis<br>EECR<br>EECR   | cSREG;<br>= SREG;<br>able_interrupt();<br> = (1< <eempe);<br> = (1&lt;<eepe);<br>= cSREG:</eepe);<br></eempe);<br> | /* ステータス レジ スタ保存変数定義 */ /* ステータス レジ スタを保存 */ /* EEPROM書き込み手順中割り込み禁止 */ /* EEPROM主書き込み許可 */ /* EEPROM書き込み開始 */ /* ステータス レジ スタを復帰 */ |

割り込みを許可するためにSEI命令を使うと、次例で示されるようにどの保留割り込みにも先立ってSEI命令の次の命令が実行されます。

| アセンブリ言語プログラム例                   |                                        |

|---------------------------------|----------------------------------------|

| SEI<br>SLEEP                    | ;全割り込み許可;休止形態移行(割り込み待ち)                |

| C言語プログラム例                       |                                        |

| enable_interrupt();<br>sleep(); | /* 全割り込み許可 */<br>/* 休止形態移行 (割り込み待ち) */ |

注: SLEEP命令までは割り込み禁止、保留割り込み実行前に休止形態へ移行します。

### 4.7.1. 割り込み応答時間

許可した全てのAVR割り込みに対する割り込み実行応答は最小4クロック周期です。4クロック周期後、実際の割り込み処理ルーチンに対するプログラム ベクタ アドレスが実行されます。この4クロック周期時間中にプログラム カウンタ(PC)がスタック上に保存(プッシュ)されます。このベクタは標準的に割り込み処理ルーチンへの無条件分岐で、この分岐は2クロック周期(記主:原文は3(JMP命令=3を想定、実際はRJMP命令=2))要します。複数周期命令実行中に割り込みが起こると、その割り込みが扱われる前に、この命令が完了されます。MCUが休止形態の時に割り込みが起こると、割り込み実行応答時間は4クロック周期増やされます。この増加は選択した休止形態からの起動時間に加えてです。

割り込み処理ルーチンからの復帰は4クロック周期要します。これらの4クロック周期中、プログラム カウンタ(PC:2バイト)がスタックから取り戻され(ポッ プ)、スタック ポインタは増加され(+2)、ステータス レシ、スタ(SREG)の全割り込み許可(I)ビットが設定(1)されます。

## 5. メモリ

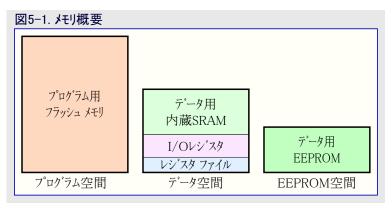

AVR構造は独立したアドレス空間に各々のメモリ形式を配置し、 プログラム メモリとデータ メモリを区別します。実行可能コートは不揮 発性プログラムメモリ(フラッシュ)に配置され、一方データは揮発性 (SRAM)または不揮発性(EEPROM)のメモリに置くことができま す。右の図5-1.をご覧ください。

全てのメモリ空間は直線的で規則的です。

## 5.1. プログラム用フラッシュ メモリ

ATtiny2313A/4313はプログラム保存のための実装書き換え可能なチップ上の2/4Kバイトのフラッシュ メモリを含みます。 フラッシュ メモリは不揮 発性、換言するとそれらは例え給電されない時でも格納された情報を保ちます。

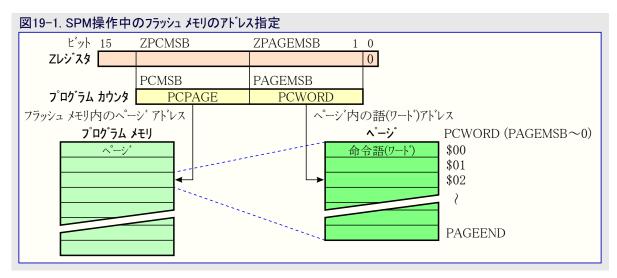

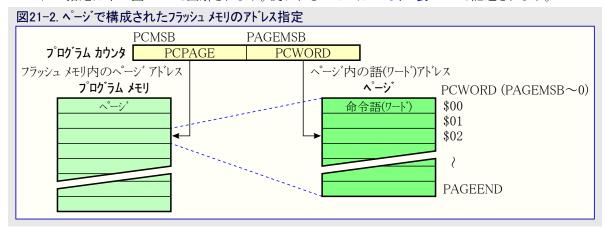

全てのAVR命令が16または32ビット幅のため、フラッシュ メモリは1024/2048×16ビットとして構成されます。プログラム カウンタ(PC)は10/11ビッ ト幅、故に下の表5-1.で説明されるようにプログラム メモリの1024/2048位置全てのアトレス指定能力があります。

定数表はプログラムメモリのアトレス空間全体内に割り当てることができます。 171頁の「命令要約」内のLPM(プログラム用メモリから取得)とSPM(プログラム用 メモリへの格納)の命令をご覧ください。122頁の「外部プログラミング」で記述さ れるように、外部装置からプログラム用フラッシュメモリをプログラミングすることもで きます。

| 表5-1. プログラム用フラッシュ メモリの容量 |       |       |               |  |  |  |  |

|--------------------------|-------|-------|---------------|--|--|--|--|

| デバイス名                    | フラッシュ | ける。   | アドレス範囲        |  |  |  |  |

| ATtiny2313A              | 2Kバイト | 1024語 | \$0000~\$03FF |  |  |  |  |

| ATtiny4313               | 4Kバイト | 2048語 | \$0000~\$07FF |  |  |  |  |

命令の取得と実行のタイミング図は9頁の「**命令実行タイミング**」で示されます。 フラッシュ メモリは最低10,000回の消去/書き込み回数の耐久性があります。

## 5.2. データ メモリ (SRAM) とレシ スタ ファイル

表5-2.はATtiny2313A/4313のデータ メモリとレジスタ ファイルがどう構成されるかを示します。これらのメモリ領域は揮発性、換言するとそれ らは電力が取り去られた時に情報を保持しません。

| 表5-2. ァーダメモリ | とレジスタの領域の配直        |  |

|--------------|--------------------|--|

| ニ゛ぃ゛ノっタ      | J 〒 II ♪ 古 ↓ + + + |  |

| デバイス名       | メモリ領域         | 容量     | 長アドレス (注1)    | 短アドレス ( <mark>注2</mark> ) |

|-------------|---------------|--------|---------------|---------------------------|

|             | 汎用レジスタファイル    | 32バイト  | \$0000~\$001F | (利用不可)                    |

| ATtiny2313A | I/Oレシ スタ ファイル | 64バイト  | \$0020~\$005F | \$00∼\$3F                 |

|             | データ用SRAM      | 128バイト | \$0060~\$00DF | (利用不可)                    |

|             | 汎用レジスタファイル    | 32バイト  | \$0000~\$001F | (利用不可)                    |

| ATtiny4313  | I/Oレシ スタ ファイル | 64バイト  | \$0020~\$005F | \$00∼\$3F                 |

|             | データ用SRAM      | 256バイト | \$0060~\$015F | (利用不可)                    |

注1: データ アトレスとしても知られます。このアトレス指定形態はデータ メモリ(SRAM)とレシ、スタ領域の全 体を網羅します。このアトンスは2語命令内の16ビット(アトンス指示)領域に含まれます。

注2: 直接I/Oアドレスとしても知られます。このアドレス指定形態はレジスタ領域の一部だけを網羅しま す。これはアドレスが命令語内に組み込まれる命令によって使われます。

224/352データ メモリ位置は汎用レジスタ ファイル、I/Oレジスタ ファイル、内蔵SRAMデータ用メモリを含みます。

将来のデバイスとの両立性のため、アクセスされる場合、予約されたビットはOを書かれるべきです。予約されたI/Oメモリ アドレスは決して書 かれるべきではありません。

## 5.2.1. 汎用レジスタ ファイル

最初の32位置は汎用レジスタファイル用に予約されます。これらのレジスタは8頁の「汎用レジスタファイル」で詳細に記述されます。

#### 5.2.2. I/Oレシ スタ ファイル

汎用レシ`スタ ファイルに後続する、次の64位置はI/Oレシ`スタ用に予約されます。この領域内のレシ`スタは主にテ`ハ`イスの入出力と周辺機能 部との通信に使われます。データはIN,OUT,LD,STとそれらの派生のような命令を用いてI/O空間と汎用レジスタ ファイル間で転送するこ とができます。

この領域内の全てのレジスタはINとOUTの命令でアクセスすることができます。これらのI/O特定命令はI/Oレジスタ領域の最初の位置を \$00、最後を\$3Fとしてアドレス指定します。

下位32個(アドレス範囲\$00~\$1F)のレジスタはいくつかのビット特定命令によってアクセス可能です。これらのレジスタでは、SBIとCBIを用いてビットが容易に設定(1)と解除(0)され、一方ビット条件分岐はSBIC,SBIS,SBRC,SBRS命令を用いて容易く作成されます。

この領域内のレジスタはLD/LDD/LDI/LDSとST/STD/STSの命令でアクセスすることもできます。これらの命令は揮発性メモリ全体を1つのデータ空間として扱い、従ってI/Oレジスタのアドレスは\$20で始まります。

#### 171頁の「命令要約」をご覧ください。

ATtiny2313A/4313はどの情報の格納にも使うことができる3つの汎用I/Oレシ、スタも含みます。170頁の「レシ、スタ要約」でGPIOR0, GPIOR1,GPIOR2をご覧ください。これらの汎用I/Oレシ、スタはそれらがSBI,CBI,SBIC,SBIS,SBRC,SBRSのようなビット特定命令でアクセス可能なので、特に全体変数や状態フラケの格納に有用です。

#### 5.2.3. データ メモリ (SRAM)

汎用レジスタファイルとI/Oレジスタファイルに後続する、残りの128/256位置はデータ用内蔵SRAM用に予約されます。 以下のように利用可能な5つのアドレス指定形態があります。

- 直接:このアドレス指定の形態はデータ空間全体に届きます。

- 間接:

- ・変位付き間接:このアドレス指定の形態はYまたはZレジスタによって与えられる基準アドレスから63アドレス位置に届きます。

- ・事前減少付き間接:この形態ではアクセスに先立ってアトレスレジスタが自動的に減少(-1)されます。アトレスポインタレジスタ(X,Y,Z)は汎用レジスタファイルのR26~R31に配置されます。8頁の「汎用レジスタファイル」をご覧ください。

- ・事後増加付き間接:この形態ではアクセス後にアトレス レジスタが自動的に増加(+1)されます。アトレス ポインタ レジスタ(X,Y,Z)は汎用レジ スタ ファイルのR26~R31に配置されます。8頁の「汎用レジスタ ファイル」をご覧ください。

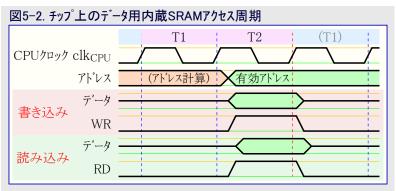

全てのアドレス指定形態は汎用レシ、スタファイル、I/Oレシ、スタファイル、データメモリを含み、揮発性メモリ全体に使うことができます。 内蔵SRAMは下の図5-2.で図解されるように2clk<sub>CPU</sub>周期でアクセスされます。

## 5.3. データ メモリ (EEPROM)

ATtiny2313A/4313は128バイトの不揮発性データメモリを含みます。このEEPROMは単一バイトを読み書きできる独立したデータ空間として構成されます。全てのアクセス レジスタはI/O空間に配置されます。

EEPROMの配置は下の表5-3.で要約されます。

EEPROM操作の時間に内蔵8MHz発振器が使われます。この発振器の周波数は20頁の「OSCCAL - 校正付き内蔵RC発振器」で記述される必要条件内でなければなりません。

厳重に濾波された電源によって給電される時に、供給電圧(VCC)は電源 投入と電源切断に於いて緩やかに上昇または下降しそうです。緩やかな 上昇や下降の時間はデバイスを指定よりも低い供給電圧で走行する状態に

| 表5-3. 不揮発性データ メモリ(EEPROM)の容量 |                       |           |  |  |  |  |  |

|------------------------------|-----------------------|-----------|--|--|--|--|--|

| デバイス名                        | Nida EEPROM容量 アトiレス範囲 |           |  |  |  |  |  |

| ATtiny2313A                  | 128バイト                | \$00∼\$7F |  |  |  |  |  |

| ATtiny4313                   | 256バイト                | \$00∼\$FF |  |  |  |  |  |

置くかもしれません。このような状況での問題を避けるには、14頁の「EEPROM化けの防止」をご覧ください。

EEPROMは最低100,000回の消去/書き込み耐久性があります。

## 5.3.1. プログラミング法

EEPROMプログラミングには以下のように2つの方法があります。

- ・非分離バイト プログラミング: これは単一操作で目標位置が消去されて書かれる、単純なプログラミング形態です。この操作形態では書く前に目標が常に消去されることが保証されますが、プログラミング時間がより長くなります。

- ・分離バイトプログラミング: 2つの異なる操作で消去と書き込みの周期を分けることが可能です。これは短いアクセス時間が必要とされるとき、例えば供給電圧が降下する時に有用です。この方法を利用するために、目標位置はそれらへ書く前に消去されなければなりません。

プログラミング法はEEPROM制御レンブスタ(EECR)のEEPROMプログラミング種別(EEPM1とEEPM0)ビットを用いて選択されます。15頁の**表5-4**. をご覧ください。書き込みと消去の時間が同じ表で与えられます。

EEPROMプログラミングが或る程度の時間がかかるため、応用は次の(操作)を開始する前に現在の操作の完了を待たなければなりません。これはEEPROM制御レジスタ(EECR)のEEPROMプログラム許可(EEPE)ビットのポーリング、またはEEPROM操作可割り込み経由のどちらかによって行うことができます。EEPROM割り込みはEECRのEEPROM操作可割り込み許可(EERIE)ビットによって制御されます。

#### 5.3.2. 読み込み

EEPROM位置を読むには以下の手順に従ってください。

- ・他のEEPROM操作が進行中でないのを確実にするためにEEPROM制御レジスタ(EECR)のEEPROMプログラム許可(EEPE)ビットをポー リングしてください。 設定(1)ならば解除(0)を待ってください。

- ・ 目的アドレスをEEPROMアトレス レジスタ(EEARH/EEARL)に書いてください。

- ・EEPROM制御レジスタ(EECR)のEEPROM読み込み許可(EERE)ピットを設定(1)することによって読み込み操作を開始してください。 読み込み動作中、CPUは次の命令を実行する前に4クロック周期間停止されます。

- ・ EEPROMデータ レシブスタ(EEDR)からデータを読んでください。

#### 5.3.3. 消去

予期せぬEEPROM書き込みを防ぐために、メモリ位置を消去するのに特別な手順に従わなければなりません。EEPROM位置を消去するには以下の手順に従ってください。

- ・他のEEPROM操作が進行中でないのを確実にするためにEEPROM制御レジスタ(EECR)のEEPROMプログラム許可(EEPE)ビットをポー リングしてください。設定(1)ならば解除(0)を待ってください。

- ・EEPROM制御レジ゙スタ(EECR)のEEPROMプログラミング種別(EEPM1とEEPM0)ビットを書くことによってプログラミング動作形態を消去に設定してください。

- ・ 目的アトレスをEEPROMアトレス レシ スタ(EEARH/EEARL)に書いてください。

- ・EEPROM制御レジネタ(EECR)のEEPROM主プログラム許可(EEMPE)を設定(1)することによって消去を許可してください。4クロック周期内にEEPROM制御レジネタ(EECR)のEEPROMプログラム許可(EEPE)ビットを設定(1)することによって消去動作を開始してください。消去動作中、CPUは次の命令を実行する前に2クロック周期間停止されます。

EEPEL'ットは消去動作が完了されるまで設定(1)に留まります。デバイスがプログラミング多忙の間、他のどんなEEPROM操作の実行も不可能です。

#### 5.3.4. 書き込み

予期せぬEEPROM書き込みを防ぐために、メモリ位置を書くのに特別な手順に従わなければなりません。

EERPOMにデータを書く前に目的位置が消去されなければなりません。これは同一操作で、または分離操作の一部としてのどちらかで行うことができます。未消去EEPROM位置への書き込みは不正なデータに帰着します。

EEPROM位置を書くには以下の手順に従ってください。

- ・他のEEPROM操作が進行中でないのを確実にするためにEEPROM制御レン、スタ(EECR)のEEPROMプログラム許可(EEPE)ヒットをポーリングしてください。設定(1)ならば解除(0)を待ってください。

- ・EEPROM制御レジスタ(EECR)のEEPROMプログラミング種別(EEPM1とEEPM0)ビットを書くことによってプログラミング動作形態を設定してください。2者選択として、1操作でのデータ書き込みか、または消去のみと書き込みのみに分離する書き込み手順にできます。

- ・目的アドレスをEEPROMアトレスレジ、スタ(EEARH/EEARL)に書いてください。

- ・目的データをEEPROMデータレジスタ(EEDR)に書いてください。

- ・EEPROM制御レジスタ(EECR)のEEPROM主プログラム許可(EEMPE)を設定(1)することによって書き込みを許可してください。4クロック 周期内にEEPROM制御レジスタ(EECR)のEEPROMプログラム許可(EEPE)ヒットを設定(1)することによって書き込み動作を開始してく ださい。書き込み動作中、CPUは次の命令を実行する前に2クロック周期間停止されます。

EEPEビットは書き込み動作が完了されるまで設定(1)に留まります。デバイスがプログラミング多忙の間、他のどんなEEPROM操作の実行も不可能です。

## 5.3.5. EEPROMデータ化けの防止

低VCCの期間中、正しく動作するための供給電圧がCPUとEEPROMに対して低すぎるためにEEPROMデータが化け得ます。これらの問題はEEPROMを使う基板段階の装置と同じで、同じ設計上の解決策が適用されるべきです。

低供給電圧に於いてEEPROMのデータは以下の2つのように不正にされ得ます。

- その他正当なEEPROMプログラミング手順の正しい操作を維持するために供給電圧が低すぎます。

- ・CPUに対して供給電圧が低すぎで、命令が不正に実行されるかもしれません。

EEPROMデータ化けは不充分な供給電源電圧の期間中、デバイスをリセットに保つことによって避けられます。これは内蔵低電圧検出器 (BOD)を許可することによって容易に行えます。BOD検出レヘルが設計に対して充分でなければ、低VCCに対する外部リセット回路を使うことができます。

供給電圧が充分ならば、例えリセットが起きる時でも、EEPROM書き込み動作は完了されます。

#### 5.3.6. プログラム例

次のコート・例はアセンブリ言語とC言語でのEEPROM消去、書き込み、または非分離書き込み関数を示します。本例は(例えば全割り込み禁止によって)割り込みが制御され、これらの関数実行中に割り込みが起きない前提です。

```

アセンブリ言語プログラム例

;EEPROMプログラミング、完了ならばスキップ

EEPROM_WR:

SBIC

EECR, EEPE

;以前のEEPROMプログラミング完了まで待機

RJMP

EEPROM_WR

LDI

R18, (0<<EEPM1) | (0<<EEPM0)

;プログラミング種別値取得(本例は非分離)

OUT

EECR, R18

;対応プログラミング 種別設定

EEAR, R17

;EEPROMアドレス下位バイト設定

OUT

OUT

EEDR, R16

;EEPROM書き込み値を設定

;EEPROM主プログラム許可ビット設定

SBI

EECR, EEMPE

;EEPROMプログラミング開始(プログラム許可ビット設定)

SBI

EECR, EEPE

;呼び出し元へ復帰

RET

C言語プログラム例

void EEPROM_write(unsigned char ucAddress, unsigned char ucData)

while (EECR & (1<<EPE));

/* 以前のEEPROMプログラミング完了まで待機 */

EECR = (0 < \langle EEPM1 \rangle | (0 < \langle EEPM0 \rangle ;

/* 対応プログラミング種別設定 */

EEAR = ucAddress;

/* EEPROMアドレス設定*/

EEDR = ucData;

/* EEPROM書き込み値を設定 */

/* EEPROM主プログラム許可*/

EECR = (1 < EEMPE);

EECR = (1 << EEPE);

/* EEPROMプログラミング開始*/

```

### **注**: 5頁の「**コート** 例」をご覧ください。

次のコード例はアセンブリ言語とC言語でのEEPROM読み込み関数を示します。本例は割り込みが制御され、これらの関数実行中に割り込みが起きない前提です。

```

アセンブリ言語プログラム例

;EEPROMプログラミング完了ならばスキップ

EEPROM_RD:

SBIC

EECR, EEPE

;以前のEEPROMプログラミング。完了まで待機

RJMP

EEPROM_RD

;EEPROMアドレス下位バイト設定

OUT

EEAR, R17

EECR, EERE

;EEPROM読み出し開始(読み込み許可ビット設定)

SBI

IN

R16, EEDR

;EEPROM読み出し値を取得

RET

;呼び出し元へ復帰

C言語プログラム例

unsigned char EEPROM_read(unsigned char ucAddress)

while (EECR & (1<<EPE));

/* 以前のEEPROMプログラミング完了まで待機 */

EEAR = ucAddress;

/* EEPROMアドレス設定 */

EECR |= (1<<EERE);

/* EEPROM読み出し開始 */

/* EEPROM読み出し値を取得,復帰 */

return EEDR;

注: 5頁の「コート'例」をご覧ください。

```

# 5.4. メモリ関係レジスタ

# 5.4.1. EEAR - EEPROMアドレス レジスタ (EEPROM Address Register)

| ピット         | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |      |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| \$1E (\$3E) | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEAR |

| Read/Write  | R/W   |      |

| 初期値         | 不定    |      |

#### ■ ビット7 - EEAR7 : EEPROMアドレス7 (EEPROM Address)

これはATtiny4313の最上位EEPROMアドレス ビットです。より少ないEEPROMのデバイス、例えばATtiny2313Aでのこのビットは予約されており、常に0として読まれます。EEPROMアドレス レジスタ(EEAR)の初期値は未定義で、従ってEEPROMがアクセスされる前に正しい値が書かれなければなりません。

#### ■ ビット6~0 - EEAR6~0: EEPROM7ドレス6~0 (EEPROM Address)

これらはEEPROMアドレスレジスタの(下位)ビットです。EEPROMのデータ バイトは0~(128/256)-1の範囲で直線的にアドレス指定されます。 EEARの初期値は未定義で、従ってEEPROMがアクセスされ得る前に正しい値が書かれなければなりません。

#### 5.4.2. EEDR - EEPROMデータレジスタ (EEPROM Data Register)

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |      |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|------|

| \$1D (\$3D) | (MSB) |     |     |     |     |     |     | (LSB) | EEDR |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |      |

| 初期値         | 不定    | 不定  | 不定  | 不定  | 不定  | 不定  | 不定  | 不定    |      |

#### ■ ビット7~0 - EEDR7~0: EEPROMデータ (EEPROM Data)

EEPROM書き込み操作に対してEEDRはEEPROMアドレス レジスタ(EEAR)で与えたアドレスのEEPROMへ書かれるべきデータを含みます。 EEPROM読み込み操作に対してEEDRはEEARで与えたアドレスのEEPROMから読み出したデータを含みます。

## 5.4.3. EECR - EEPROM制御レジスタ (EEPROM Control Register)

| ピット         | 7 | 6 | 5     | 4     | 3     | 2     | 1    | 0    |      |

|-------------|---|---|-------|-------|-------|-------|------|------|------|

| \$1C (\$3C) | _ | - | EEPM1 | EEPM0 | EERIE | EEMPE | EEPE | EERE | EECR |

| Read/Write  | R | R | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  |      |

| 初期値         | 0 | 0 | 不定    | 不定    | 0     | 0     | 不定   | 0    |      |

## ■ ビット7 - Res: 予約 (Reserved)

このビットは将来の使用に予約されており、常に0として読まれます。将来のAVRデバイスとの共通性のため、常に本ビットへ0を書いてください。読み込み後、本ビットを遮蔽排除してください。

## ■ ビット7,6 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

#### ■ ビット5,4 - EEPM1,0: EEPROMプログラミング種別 (EEPROM Programing Mode Bits)

EEPROMプログラミング種別にかト設定はEEPROMプログログラミング種別グラミング許可(EEPE)書き込み時にどのプログラミング 動作が起動されるかを定義します。1つの非分離操作(旧値消去と新値書き込み)、または2つの異なる操作として消去と書き込み操作を分離してデータをプログラムする(書く)ことが可能です。各動作に対するプログラミング時間は表5-4、で示されます。

| 表5-4. EEPROM7 ロクラミンク 種別 |       |           |                     |  |  |  |

|-------------------------|-------|-----------|---------------------|--|--|--|

| EEPM1                   | EEPM0 | プログラミング時間 | 動作                  |  |  |  |

| 0                       | 0     | 3.4ms     | 1操作での消去と書き込み(非分離操作) |  |  |  |

| 0                       | 1     | 1.8ms     | 消去のみ                |  |  |  |

| 1                       | 0     | 1.8ms     | 書き込みのみ              |  |  |  |

| 1                       | 1     | -         | 将来使用に予約             |  |  |  |

EEPEが設定(1)されている間はEEPMnへのどの書

き込みも無視されます。リセット中、EEPMnビットはEEPROMがプログラミング作業中を除いて'00'にリセットされます。

#### ■ ビット3 - EERIE: EEPROM操作可割り込み許可(EEPROM Ready Interrupt Enable)

EERIEの1書き込みはステータス レジ、スタ(SREG)の全割り込み許可(I)ヒットが設定(1)されているなら、EEPROM操作可割り込みを許可します。EERIEの0書き込みは、この割り込みを禁止します。EEPROM操作可割り込みは不揮発性メモリ(フラッシュ メモリとEEPROM)がプログラミングの準備可ならば継続する割り込みを発生します。

#### ■ ビット2 - EEMPE: EEPROM主プログラム許可 (EEPROM Master Program Enable)

EEMPEt'ットはEEPROMプログラム許可(EEPE)t'ットの1書き込みが有効か無効かどちらかを決めます。

EEMPEが設定(1)されると、4クロック周期内のEEPE設定(1)は選択したアドレスのEEPROMをプログラムします。EEMPEが0なら、EEPE設定(1)は無効です。EEMPEがソフトウェアによって設定(1)されてしまうと、4クロック周期後にハードウェアがこのビットを0に解除します。

## ■ ビット1 - EEPE: EEPROMプログラム許可 (EEPROM Program Enable)

これはEEPROMのプログラミング許可信号です。EEPROM主プログラム許可(EEMPE)ビットはEEPEが書かれる前に設定(1)されなければならず、さもなくばEEPROM書き込み(消去)は行われません。

EEPEが(1を)書かれると、EEPROMはEEPMnビット設定に従ってプロケラミンケされます。EEPEが設定(1)されてしまうと、次の命令が実行される前にCPUは2周期停止されます。書き込み(プロケラミンケ)アクセス時間経過後、EEPEビットはハードウェアによって解除(0)されます。 EEPROM書き込み操作がフラッシュ メモリ、ヒュース゛ビット、施錠ビットの全てのソフトウェア プロケラミンケを妨げることに注意してください。

#### ■ ビット0 - EERE: EEPROM読み込み許可(EEPROM Read Enable)

これはEEPROMの読み込みストローブです。EEARに目標アドレスが設定されると、EEPROM読み込み操作を起動するためにEEREビットは1を書かれなければなりません。

EEPROM読み込みアクセスは(その)1命令かかり、要求したデータが直ちに利用できます。EEPROMが読まれる時に、次の命令が実行される前にCPUが4周期停止されます。

使用者は読み込み操作を始める前にEEPEビットをポーリングすべきです。書き込み(プログラム)操作実行中の場合、EEPROMアドレス レジスタ(EEAR)の変更もEEPROM読み込みもできません。

# 5.4.4. GPIOR2 - 汎用I/Oレジスタ2 (General Purpose I/O Register 2)

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     | _      |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$15 (\$35) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR2 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

### 5.4.5. GPIOR1 - 汎用I/Oレジスタ1 (General Purpose I/O Register 1)

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     | _      |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$14 (\$34) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR1 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

### 5.4.6. GPIORO - 汎用I/OレジスタO (General Purpose I/O Register 0)

| ヒ゛ット           | 7 6    | 5     | 4   | 3   | 2   | 1   | 0     |        |

|----------------|--------|-------|-----|-----|-----|-----|-------|--------|

| \$13 (\$33) (M | ISB)   |       |     |     |     |     | (LSB) | GPIOR0 |

| Read/Write R   | /W R/W | / R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値            | 0 0    | 0     | 0   | 0   | 0   | 0   | 0     |        |

# 6. クロック体系

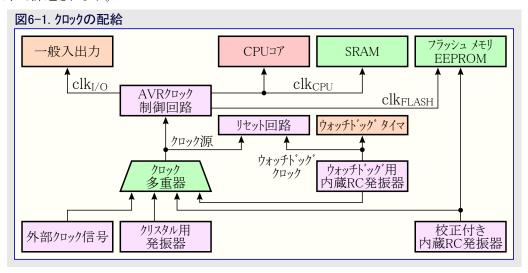

図6-1.はAVR内の主要なクロック系統とその配給を示します。全てのクロックが与えられた時間有効である必要はありません。消費電力低減のため、22頁の「電力管理と休止形態」で記述される各種休止形態の使用によって、使われていない部分のクロックが停止できます。クロック系統は以下で詳述されます。

# 6.1. クロック副系統

#### 6.1.1. CPU クロック - clkcpu

CPUクロックはAVRコアの動作と関係する系統の部分に配給されます。このような部分の例は汎用レジスタ ファイル、ステータス レジスタ、スタック ポインタを保持するデータ メモリです。CPUクロックの停止はコアが一般的な操作や計算を実行することを禁止します。

#### 6.1.2. I/O クロック - clk<sub>I/O</sub>

I/Oクロックはタイマ/カウンタやUSARTのようなI/O部の大部分で使われます。I/Oクロックは外部割り込み部でも使われますが、いくつかの外部割り込みは例えI/Oクロックが停止されても検出されることをこのような割り込みに許す非同期論理回路によって検出されることに注意してください。多用途直列(USI)部の開始条件検出はclk<sub>I/O</sub>が停止される時に非同期に実行され、全休止形態でUSI開始条件検出を可能とすることにも注意してください。

## 6.1.3. フラッシュ クロック - clk<sub>FLASH</sub>

フラッシュ クロックはフラッシュ メモリ インターフェースの動作を制御します。このフラッシュ クロックは常にCPUクロックと同時に活動します。

#### 6.2. クロック元

このデバイスには右で示されるようにフラッシュ ヒューズ ビットによって選択可能な後続のクロック元選択があります。選択したクロック元からのクロックはAVRクロック発生器への入力で、適切な単位部へ配給されます。

各クロック選択に対する様々な選択は次項で得られます。CPUがハ<sup>°</sup>ワーダウンから起動するとき、選択したクロック元は命令実行開始前に安定な発振器動作を保証する起動時間に使われます。CPUがリセットから始まるとき、これらは通常動作開始前に安定電圧へ達するのを電源に許す付加遅延です。ウォッチト<sup>°</sup>ック・発振器は、この起動時間の実時間部のタイシングに使われます。

| 表6-1. クロック種別選択         |                                              |  |  |  |  |  |

|------------------------|----------------------------------------------|--|--|--|--|--|

| クロック種別                 | CKSEL3~0                                     |  |  |  |  |  |

| 外部クリスタル/セラミック発振子       | 1111~1000                                    |  |  |  |  |  |

| 128kHz内部(WDT)発振器       | 0110                                         |  |  |  |  |  |

| 8MHz校正付き内蔵RC発振器        | 0100                                         |  |  |  |  |  |

| 4MHz校正付き内蔵RC発振器        | 0010                                         |  |  |  |  |  |

| 外部クロック信号               | 0000                                         |  |  |  |  |  |

| (予約)                   | 0xx1                                         |  |  |  |  |  |

| 注: 1=非プログラム、0=プログラム、x= | <b>注</b> : 1=非プログラム、0=プログラム、x=0また <i>は</i> 1 |  |  |  |  |  |

## 6.2.1. 既定のクロック元

このデバイスはCKSEL=0100, SUT=10, CKDIV8=プログラム(0)で出荷されます。従って既定クロック元設定は最長起動時間の8MHzで走行する内蔵RC発振器を8で前置分周し、結果として1MHzに帰着する初期システム クロックです。この既定設定は全ての使用者が実装または並列書き込み器を使って、それらを希望したクロック元設定にできることを保証します。

低電圧のデバイスに関してはCKDIV8ヒュースでの非プログラム(1)がオーバークロックに帰着するかもしれないことに注意すべきです。低電圧 (2.7V以下)に於けるデバイスは最大4MHz動作と評価されますが(133頁の「速度」項をご覧ください)、内部発振器からのクロック信号を直接システム クロック線へ配線することはデバイスを8MHzで動かすでしょう。

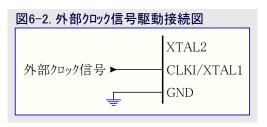

## 6.2.2. 外部クロック信号

外部クロック元からデバイスを駆動するためにXTAL1は図6-2.で示されるように駆動され るべきです。外部クロックでデバイスを走行するためにはCKSELヒューズが'0000'にプログラ ム(設定)されなければなりません。

このクロック元が選択されると、起動時間は表6-2.で示されるようにSUTヒューズによって 決定されます。

表6-2 外部クロック信号駆動用起動遅延時間選択表

| SUT1,0 | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法            |  |

|--------|---------------------|------------------------------|------------------|--|

| 0 0    | 6×CK                | 14×CK                        | 低電圧検出(BOD)リセット許可 |  |

| 0 1    | 6×CK                | 14×CK+4.1ms                  | 高速上昇電源           |  |

| 1 0    | 6×CK                | 14×CK+65ms                   | 低速上昇電源           |  |

| 1 1    | (予約)                |                              |                  |  |

外部クロックを供給するとき、MCUの安定な動作を保証するために供給したクロック周波数の急な変化を避けることが必要とされます。或 るクロック周期から次への2%より大きな周波数変化は予測されない事態を引き起こします。このようなクロック周波数での変化中、MCUは リセットに保たれるのを保証することが必要とされます。

システム クロック前置分周器が安定な動作を保証しながら、内部クロック周波数の実行時変更の実現に使えることに注意してください。詳 細については20頁の「システム クロック前置分周器」を参照してください。

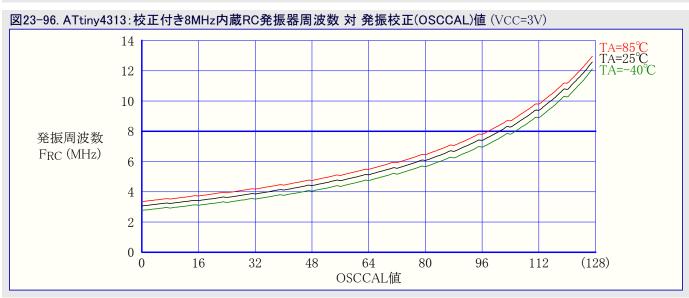

#### 6.2.3. 校正付き内蔵RC発振器

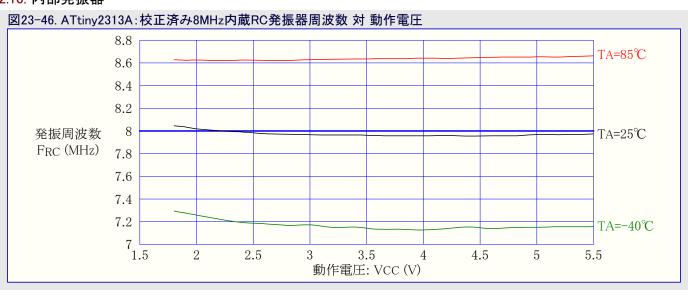

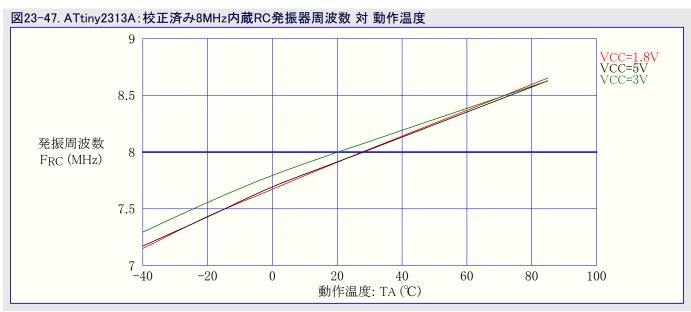

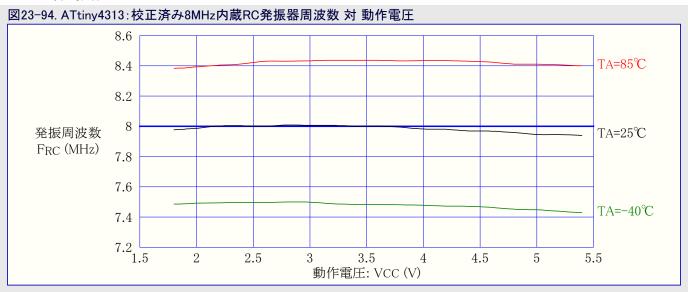

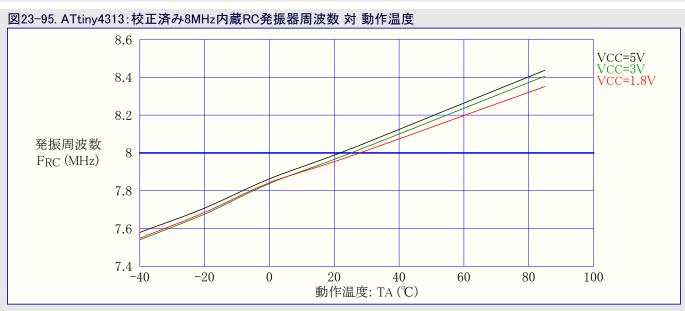

校正された内蔵RC発振器は8MHzまたは4MHzクロックを供給します。この周波数は 3V,25℃での公称値です。この周波数が(VCCに依存して)デバイスの速度仕様を越え る場合、起動中に内部周波数を8分周するためにCKDIV8ヒューズがプログラム(0)されな ければなりません。より多くの詳細については20頁の「システム クロック前置分周器」をご 覧ください。このクロックは表6-3.で示されるようにCKSELヒュース、のプログラミングによってシ ステム クロックとして選択できます。選択したなら、外部部品なしで動作します。リセット中、 <mark>注1</mark>: デバイスはこの選択で出荷されます。

表6-3. 校正付き内蔵RC発振器動作

| CKSEL3~0 | <b>公称周波数</b> (MHz) |

|----------|--------------------|

| 0 1 0 0  | 8.0 (注1)           |

| 0 0 1 0  | 4.0                |

ハードウュアが発振校正レジスタ(OSCCAL)に校正値バイトを設定し、これによってRC発振器を自動的に校正します。 3V,25℃でこの校正 は公称周波数±10%以内の周波数を与えます。atmel.com/avrで利用可能な応用記述に記載された実行時校正法の使用で、与えら れたどのVCCと温度でも±2%の精度を達成することができます。この発振器がチップ(システム)クロックとして使われるとき、ウォッチドック・発振 器は未だウォッチドッグタイマとリセット付加遅延タイマに使われます。予め設定された校正値のより多くの情報については、120頁の「校正バ 小 項をご覧ください。

この発振器が選択されると、起動時間は表6-4.で示されるようにSUTヒューズによって決定されます。

表6-4. 校正付き内蔵RC発振器用起動遅延時間選択表

| SUT1,0            | パワーダウンからの<br>起動遅延時間 | リセットからの<br>付加遅延時間   | 推奨使用法            |  |  |

|-------------------|---------------------|---------------------|------------------|--|--|

| 0 0               | 6×CK                | 14×CK ( <b>注1</b> ) | 低電圧検出(BOD)リセット許可 |  |  |

| 0 1               | 6×CK                | 14×CK+4.1ms         | 高速上昇電源           |  |  |

| 1 0 ( <b>注2</b> ) | 6×CK                | 14×CK+65ms          | 低速上昇電源           |  |  |

| 1 1               | (予約)                |                     |                  |  |  |

注1: RSTDISBLヒューズがプログラム(0)されると、プログラミング動作への移行可を保証するため、付加遅延時間は14×CK+4msに増や されます。

注2: デバイスはこの選択で出荷されます。

#### 6.2.4. 128kHz内部発振器

128kHz内部発振器は128kHzのクロックを供給する低電力発振器です。この周波数は3V,25℃での公称値です。このクロックはCKSEL ヒューズを'0110'にプログラミング(設定)することによってシステム クロックとして選択できます。

このクロック元が選択されると、起動時間は表6-5.で示されるようにSUTヒューズによって決定されます。

表6-5. 128kHz内部発振器用起動遅延時間選択表

| SUT1,0 | パワーダウンからの<br>起動遅延時間 | リセットからの<br>付加遅延時間   | 推奨使用法            |  |

|--------|---------------------|---------------------|------------------|--|

| 0 0    | 6×CK                | 14×CK ( <b>注1</b> ) | 低電圧検出(BOD)リセット許可 |  |

| 0 1    | 6×CK                | 14×CK+4ms           | 高速上昇電源           |  |

| 1 0    | 6×CK                | 14×CK+64ms          | 低速上昇電源           |  |

| 11     | (予約)                |                     |                  |  |

注1: RSTDISBLヒューズがプログラム(0)されると、プログラミング動作への移行可を保証するため、付加遅延時間は14×CK+4msに増やされます。

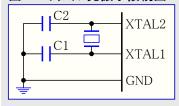

## 6.2.5. クリスタル用発振器

XTAL1とXTAL2は**図6-3**.で示されるように、チップ上の発振器としての使用に設定できる反転増幅器の各々、入力と出力です。クリスタル発振子またはセラミック振動子のどちらでも使えます。

C1とC2はクリスタル発振子とセラミック振動子の両方について常に等しくすべきです。このコンデンサの最適値は使うクリスタル発振子やセラミック振動子、浮遊容量の量、その環境の電磁雑音に依存します。クリスタル発振子使用に対するコンデンサ選択について初期の指針のいくつかは表6-6.で与えられます。セラミック振動子については製造業者によって与えられたコンデンサ値が使われるべきです。

発振器は示された周波数範囲で最適化された4つの異なる動作ができます。この動作は、表6-6.で示されたCKSEL3~1ヒュースによって選択されます。

図6-3. クリスタル発振子接続図

| CKSEL3~1 | 周波数範囲      | 推奨C1,2容量 |

|----------|------------|----------|

| 100 (注1) | 0.4~0.9MHz | -        |

| 101      | 0.9~3.0MHz | 12∼22pF  |

| 110      | 3.0~8.0MHz | 12∼22pF  |

| 111      | 8.0∼ MHz   | 12~22pF  |

**注1**: この選択はクリスタル発振子ではなく、セラミック 振動子でのみ使われるべきです。

CKSEL0ヒューズはSUT1,0ヒューズと共に、表6-7.で示される起動遅延時間を選択します。

#### 表6-7 加7如晚年子/セラミック振動子田起動遅延時間選択表

| 衣0-7. ソリハ | 反0-7. クウヘタル光振士/でフミツク振到士用起到建処時间選択衣 |                      |                              |                             |  |  |  |  |  |  |

|-----------|-----------------------------------|----------------------|------------------------------|-----------------------------|--|--|--|--|--|--|

| CKSEL0    | SUT1,0                            | パワーダウンからの<br>起動遅延時間  | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法                       |  |  |  |  |  |  |

|           | 0 0                               | 258×CK ( <b>注1</b> ) | $14 \times \text{CK+4ms}$    | 外部セラミック振動子、高速上昇電源           |  |  |  |  |  |  |

| 0         | 0 1                               | 258×CK ( <b>注1</b> ) | $14 \times \text{CK+64ms}$   | 外部セラミック振動子、低速上昇電源           |  |  |  |  |  |  |

| U         | 1 0                               | 1K×CK ( <b>注2</b> )  | 14×CK                        | 外部セラミック振動子、低電圧検出(BOD)リセット許可 |  |  |  |  |  |  |

|           | 1 1                               | 1K×CK ( <b>注2</b> )  | $14 \times \text{CK+4ms}$    | 外部セラミック振動子、高速上昇電源           |  |  |  |  |  |  |

|           | 0 0                               | 1K×CK ( <b>注2</b> )  | $14 \times \text{CK+64ms}$   | 外部セラミック振動子、低速上昇電源           |  |  |  |  |  |  |

| 1         | 0 1                               | 16K×CK               | 14×CK                        | 外部クリスタル発振子、低電圧検出(BOD)リセット許可 |  |  |  |  |  |  |

| 1         | 1 0                               | 16K×CK               | 14×CK+4ms                    | 外部クリスタル発振子、高速上昇電源           |  |  |  |  |  |  |

|           | 1 1                               | 16K×CK               | 14×CK+64ms                   | 外部クリスタル発振子、低速上昇電源           |  |  |  |  |  |  |

**注1**: これらの選択はデバイスの最高周波数付近での動作でないとき、応用にとって起動での周波数安定性が重要でない場合だけ使われるべきです。これらの選択はクリスタル発振子用ではありません。

**注2**: これらの選択はセラミック振動子での使用を意図され、起動での周波数安定性を保証します。デバイスの最高周波数付近での動作でないとき、応用にとって起動での周波数安定性が重要でない場合はクリスタル発振子も使えます。

## 6.3. システム クロック前置分周器

ATtiny2313A/4313のシステム クロックはクロック前置分周レシ、スタ(CLKPR)の設定によって分周できます。この特徴(機能)は必要とされる処理能力が低い時の消費電力削減に使えます。これは全クロック種別で使え、CPUと全同期周辺機能のクロック周波数に影響を及ぼします。 clk<sub>CPU</sub>、clk<sub>FLASH</sub>、clk<sub>I/O</sub>は表6-8.で示された値によって分周されます。

#### 6.3.1. 切り替え時間

前置分周器設定間を切り替えるとき、システム クロック前置分周器は中間(経過途中)の周波数が直前の設定に対応するクロック周波数または新規設定に対応するクロック周波数のどちらよりも高くなく、クロック系で不具合が起きないことを保証します。

前置分周器として実行するリプル カウンタは分周されないクロック周波数で走行し、CPUのクロック周波数より速いかもしれません。従って例え(カウンタ値が)読めるとしても、前置分周器の状態を決めることはできず、1から他へのクロック分周値切り替えを行う正確な時間は必ずしも予測できません。CLKPS値が書かれる時から新規クロック周波数が活性(有効)になる前にT1+T2~T1+2×T2間かかります。この間で2つの有効なクロック端が生成されます。ここでのT1は直前のクロック周期、T2は新規前置分周器設定に対応する周期です。

## 6.4. クロック出力緩衝部(外部クロック出力)

このデバイスはシステム クロックをCKOUTピンに出力することができます。これを許可するにはCKOUTヒュース、がプログラム(0)されなければなりません。この動作形態はチップのクロックがシステム内の他の回路の駆動を必要とされる時に有用です。

このヒューズがプログラム(0)された時にI/Oピンの標準動作が無視され、このクロックがリセット中に出力されないことに注意してください。クロックがCKOUTピンで出力される時に、校正付き内蔵RC発振器を含むどのクロック元も選択することができます。

システム クロック前置分周器が使われる場合、出力されるのは分周されたシステム クロックです。

## 6.5. クロック関係レジスタ

## 6.5.1. OSCCAL - 発振校正レジスタ (Oscillator Calibration Register)

| <u> ビット</u> | 7 | 6    | 5    | 4    | 3      | 2    | 1    | 0    |        |

|-------------|---|------|------|------|--------|------|------|------|--------|

| \$31 (\$51) | - | CAL6 | CAL5 | CAL4 | CAL3   | CAL2 | CAL1 | CAL0 | OSCCAL |

| Read/Write  | R | R/W  | R/W  | R/W  | R/W    | R/W  | R/W  | R/W  |        |

| 初期値         | 0 |      |      | デハ゛  | イス固有の校 | 正値   |      |      |        |

#### ■ ビット7 - Res: 予約 (Reserved)

このビットは予約されており、常に0として読まれます。

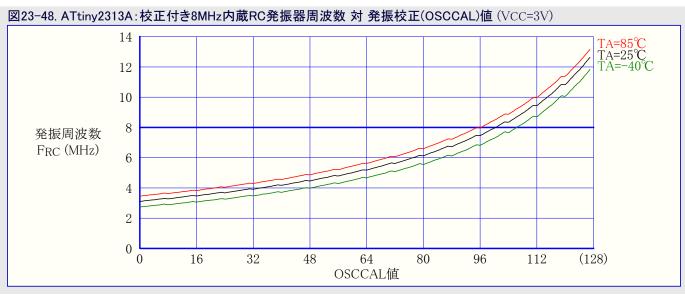

#### ■ ビット6~0 - CAL6~0:発振校正値 (Oscillator Calibration Value)

このアドレスへの校正バイ書き込みは発振器周波数の偏差処理を省くために内蔵発振器を調整します。これはチップ リセット中、自動的に行われます。OSCCALが0の時に最低利用可能周波数が選択されます。このレジスタへの以外の値を書くことは内蔵発振器の周波数を増加します。このレジスタへの\$7F書き込みは最高使用可能周波数にします。

校正付き発振器はフラッシュメモリとEEPROMのアクセス時間に使われます。フラッシュメモリやEEPROMが書かれる場合、公称周波数より上へ10%を越えて校正してはいけません。そうでなければフラッシュメモリやEEPROM書き込みは失敗するかもしれません。この発振器は8MHzまたは4MHzへの校正を意図したものであることに注意してください。(訳注:削除漏れのため原書本位置のI行を削除)

校正付き内蔵RC発振器を校正するとき、MCUの安定な動作を保証するために大きな段階での校正値変更を避けてください。或るクロック周期から次への2%より大きな周波数変化は予測されない事態を引き起こします。OSCCAL変更は各校正について\$20を越えるべきではありません。このようなクロック周波数での変化中、MCUはリセットに保たれるのを保証することが必要とされます。

# 6.5.2. CLKPR - クロック前置分周レジスタ (Clock Prescale Register)

| ピット         | 7      | 6 | 5 | 4 | 3      | 2      | 1      | 0      |       |

|-------------|--------|---|---|---|--------|--------|--------|--------|-------|

| \$26 (\$46) | CLKPCE | - | - | - | CLKPS3 | CLKPS2 | CLKPS1 | CLKPS0 | CLKPR |

| Read/Write  | R/W    | R | R | R | R/W    | R/W    | R/W    | R/W    |       |

| 初期値         | 0      | 0 | 0 | 0 | 内容参照   | 内容参照   | 内容参照   | 内容参照   |       |

#### ■ ビット7 - CLKPCE: クロック分周値変更許可 (Clock Prescaler Change Enable)

CLKPSビットの変更を許可するためにCLKPCEビットは論理1を書かれなければなりません。CLKPCEビットは同時にCLKPRの他の全ビットが0を書かれる時だけ更新されます。CLKPCEは書き込み後4クロック周期またはCLKPSビット書き込み時、ハードウェアによって解除(0)されます。この制限時間(4クロック周期)内のCLKPCEビット再書き込みは制限時間の延長もCLKPCEビットの解除(0)も行いません。

#### ■ ビット6~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

#### ■ ビット3~0 - CLKPS3~0: クロック分周値選択 (Clock Prescaler Select Bits 3~0)

これらのビットは選択したクロック元と内部システム クロック間の分周値を定義します。これらのビットは応用の必要条件に合わせた各種クロック周波数を実行時に書けます。分周値が使われると、分周器はMCUへの主クロックを分周し、全ての同期周辺機能の速度が減じられます。分周値は表6-8.で与えられます。

予期せぬクロック周波数の変更を防ぐため、CLKPSビットの変更は次の特別な書き込み手順に従わなければなりません。

- 1. クロック分周値変更許可(CLKPCE)ビットに1、CLKPR内の他の全ビットに0を書きます。

- 2. (次からの)4周期以内にCLKPCEビットをOとする欲したCLKPS値を書きます。

前置分周器設定変更時、書き込み手続きが割り込まれないことを保証するため、割り込みは禁止されなければなりません。応用ソフトウェアは現在の動作条件でデバイスの最高周波数より高い周波数のクロック元を選択した場合、充分な分周値が選択されることを保証しなければなりません。本デバイスはCKDIV8ヒュースがブログラム(0)で出荷されます。

表6-8. クロック前置分周器選択 CLKPS3 0 CLKPS2 CLKPS1 0 0 CLKPS0 0 0 0 0 0 分周値(数) 64 128 (予約) 1 2 4 8 16 32 256

# 7. 電力管理と休止形態

高機能と産業的に先行するコート、効率は低電力の応用に対してAVRマイクロコントローラを理想的に選択させます。加えて、休止形態は応用でMCU内の未使用部を一時停止することを可能にし、それによって節電します。AVRは応用で必要な消費電力に仕立てることを使用者に許す様々な休止形態を提供します。

## 7.1. 休止形態種別

17頁の図6-1.はATtiny2313A/4313に於ける各種クロック系統とその配給を示します。この図は適切な休止形態選択を手助けします。 表7-1.は各種休止形態とそれらの起動元を示します。

表7-1. 各休止形態に於ける動作クロック範囲と復帰起動要因

| ſ |                                    | 動          | 作クロック範       | 囲         | 発振器動作        |                   | 復帰起重          | 加要因(割り込み)         |               |            |

|---|------------------------------------|------------|--------------|-----------|--------------|-------------------|---------------|-------------------|---------------|------------|

|   | 休止種別                               | clk<br>CPU | clk<br>FLASH | clk<br>10 | 主クロック<br>供給元 | INT0,INT1<br>ピン変化 | USI開始条件<br>検出 | SPM/EEPROM<br>操作可 | ウォッチ<br>ト゛ック゛ | その他<br>I/O |

| ı | アイドル                               |            |              | 0         | 0            | 0                 | 0             | 0                 | 0             | 0          |

|   | ハ <sup>°</sup> ワータ <sup>*</sup> ウン |            |              |           |              | 1                 | 0             |                   | 0             |            |

|   | スタンバイ                              |            |              |           | 0            | 1                 | 0             |                   | 0             |            |

① INT0とINT1についてはレベル割り込みのみです。

3つの休止形態の何れかへ移行するにはMCU制御レシ、スタ(MCUCR)の休止。許可(SE)ヒットが論理1を書かれ、SLEEP命令が実行されなければなりません。MCUCRの休止種別選択(SM1,0)ヒットはSLEEP命令によって活性(有効)にされる休止形態(アイト・ル,ハ・ワータ・ウン、スタンハ・イ)のどれかを選びます。一覧については表7-2.をご覧ください。MCUが休止形態中に許可した割り込みが起こると、MCUは起動します。その時にMCUは起動時間に加えて4周期停止され、割り込みルーチンを実行し、そしてSLEEP命令の次の命令から実行を再開します。デハ・イスが休止から起動するとき、レシ・スタファイルとSRAMの内容は変えられません。休止形態中にリセットが起こると、MCUは起動し、リセット ヘ・クタから実行します。

レベルで起動した割り込みが起動復帰に使われる場合、MCUを起動(とMCUがその割り込み処理ルーチンへ移行)するには、変更したレベルが一定時間保持されなければならないことに注意してください。詳細については32頁の「外部割り込み」を参照してください。

#### 7.1.1. アイドル動作

休止種別選択(SM1,0)ビットが'00'を書かれると、SLEEP命令はMCUをアイドル動作へ移行させ、CPUを停止しますが、アナロケ、比較器、多用途直列インターフェース(USI)、タイマ/カウンタ、ウォッチドッケ、、割り込み機構の継続動作を許します。この休止形態は基本的にclkCPUとclkFLASHを停止する一方、他のクロックに走行を許します。

アイドル動作はMCUにタイマ溢れのような内部割り込みだけでなく、外部で起動された割り込みからの起動も許します。アナロケ比較器割り込みからの起動が必要とされないなら、アナロケ比較器制御/状態レジスタ(ACSR)のアナロケ比較器禁止(ACD)ビットを設定(1)することによってアナロケ比較器を電源断にできます。これはアイドル動作での消費電力を削減します。

## 7.1.2. パワーダウン動作

SM1,0ビットが'01'または'11'を書かれると、SLEEP命令はMCUをパワーダウン動作へ移行させます。この動作では外部発振器が停止される一方で、外部割り込みとウォッチドッケ、機能は(許可ならば)継続して動作します。外部リセット、ウォッチドッケ、リセット、低電圧検出(BOD)リセット、NT0またはINT1の外部レヘブル割り込み、ピン変化割り込みだけがMCUを起動できます。この休止形態は基本的に生成した全てのクロックを停止し、非同期部の動作だけを許します。

#### 7.1.3. スタンバイ動作

外部クリスタル発振子/セラミック振動子クロック種別が選択され、SM1,0ビットが'10'の時に、SLEEP命令はMCUをスタンバイ動作へ移行させます。この動作は(外部クリスタル用)発振器が走行(動作)を保たれる例外を除いてパワーダウン動作と同じです。デバイスはスタンバイ動作から6クロック周期で起動します。

# 7.2. ソフトウェア低電圧検出(BOD)禁止

低電圧検出器(BOD)がBODLEVELヒュース'(119頁の表20-4.参照)によって許可されていると、BODは休止期間中に電源電圧を活発に監視します。いくつかのデバイスはパワータウンとスタンバイの休止形態でソフトウェアでBODを禁止することによる節電が可能です。この休止形態電力消費はBODがヒュース'によって全面的に禁止される時と同じ水準になるでしょう。

BODがソフトウェアで禁止される場合、BOD機能は休止形態移行後、直ちにOFFされます。休止からの起動復帰で、BODは再び自動的に許可されます。これは休止期間中にVCCレベルが落ちた場合の安全な動作を保証します。

BODが禁止されてしまうと、MCUが命令コードの実行を継続する前にBODが正しく動作するのを保証するために、休止形態からの起動時間は概ね60usになります。

BOD禁止はBOD制御レジスタ(BODCR)のBOD休止(BODS)ビットによって制御されます。25頁の「BODCR - BOD制御レジスタ」をご覧ください。このビットへの1書き込みはパワーダウン動作とスタンバイ動作でのBODをOFFにし、一方このビットの0はBOD活動(有効)を保ちます。既定設定は0、換言するとBOD活動(有効)です。

BODSビットへの書き込みは許可ビットと時間制限手順によって制御されます。25頁の「BODCR - BOD制御レジスタ」をご覧ください。

# 7.3. 電力削減レジスタ

電力削減レジスタ(24頁の「PRR - 電力削減レジスタ」参照)は個別周辺機能へのクロックを停止することにより、消費電力を削減方法を提供します。周辺機能へのクロックが停止される、以下のようになります。

- 周辺機能の現在の状態が固定化されます。

- 関連するレジスタは読み書きすることができません。

- ・周辺機能によって使われる資源は専有されたままに留まります。

周辺機能は殆どの場合に於いてクロックを停止する前に禁止されるべきです。電力削減レジスタ(PRR)のビットを解除(0)することが周辺機能部を起し、停止前と同じ状態にします。

周辺機能停止は全体に亘る重要な消費電力の削減のために活動動作とアイドル動作で使えます。例については137頁の「**電力削減の効果**」をご覧ください。その他の休止形態ではクロックが予め停止されます。

## 7.4. 消費電力の最小化

これらはAVRコアが制御するシステムで消費電力の最小化を試みる時に考慮するためのそれぞれの検討点です。一般的に休止形態動作は可能な限り多く使われるべきで、休止形態種別は動作するデバイスの機能が可能な限り少なくなるように選択されるべきです。必要とされない全ての機能は禁止されるべきです。特に次の機能部は最低可能消費電力の達成を試みるとき、特別な考慮を必要とするでしょう。

### 7.4.1. アナログ比較器

アナログ比較器が使われないなら、アイブル動作へ移行する時に禁止されるべきです。その他の休止形態ではアナログ比較器が自動的に禁止されます。しかし、アナログ比較器が入力として内部基準電圧を使う設定の場合、全休止形態でアナログ比較器が禁止されるべきです。さもなくば内部基準電圧は休止形態と無関係に許可されます。アナログ比較器設定法の詳細については111頁の「アナログ比較器」を参照してください。

## 7.4.2. 内部基準電圧

内部基準電圧は低電圧検出器(BOD)とアナログ比較器によって必要とされる時に許可されます。これら単位部が上の項目で記述されたように禁止されると、内部基準電圧は禁止され、電力を消費しません。再び許可する場合、この出力が使われる前に使用者は基準電圧へ起動(安定時間)を与えなければなりません。基準電圧が休止形態でON保持される場合、この出力は直ちに使えます。起動時間の詳細については28頁の「内部基準電圧」を参照してください。

## 7.4.3. 低電圧検出器 (BOD)

低電圧検出器(BOD)が応用で必要とされないなら、この単位部はOFFされるべきです。低電圧検出器がBODLEVELヒューズによって許可されていると全休止形態で許可され、故に常に電力を消費します。これはより深い休止形態での総消費電流にとって重要な一因になります。低電圧検出器(BOD)設定法の詳細については27頁の「低電圧検出(BOD)」と22頁の「ソフトウェア低電圧検出(BOD)禁止」を参照してください。

### 7.4.4. ウォッチトック タイマ

ウォッチト、ッケ、タイマが応用で必要とされないなら、この単位部はOFFにされるべきです。ウォッチト、ッケ、タイマが許可されていると全休止形態で許可され、故に常時電力を消費します。これはより深い休止形態での総消費電流にとって重要な一因になります。ウォッチト、ッケ、タイマ 設定法の詳細については28頁の「ウォッチト、ッケ、タイマ」を参照してください(訳注:原書に対して参照先修正)。

#### 7.4.5. ホートピン

休止形態へ移行するとき、全てのポート ピンは最小電力使用に設定されるべきです。最も重要なことはその時にピンが抵抗性負荷を駆動しないのを保証することです。I/Oクロック(clkɪ/O)が停止される休止形態ではデバイスの入力緩衝部が禁止されます。これは必要とされない時に入力論理回路によって電力が消費されないことを保証します。いくつかの場合で入力論理回路は起動条件を検出するために必要とされ、その時は許可されます。どのピンが許可されるかの詳細については38頁の「デジタル入力許可と休止形態」を参照してください。入力緩衝部が許可され、入力信号が浮いている状態のままか、またはアナログ信号電圧がVCC/2付近の場合、入力緩衝部は過大な電力を消費するでしょう。

アナログ入力ピンに対するデジタル入力緩衝部は常に禁止されるべきです。入力ピンでのVCC/2付近のアナログ信号入力は活動動作でも 重要な電流を引き起こし得ます。デジタル入力緩衝部はデジタル入力禁止レジスタ(DIDR)の書き込みによって禁止できます。詳細については112頁の「DIDR - デジタル入力禁止レジスタ」を参照してください。

## 7.5. 電力管理用レジスタ

### 7.5.1. MCUCR - MCU制御レジスタ (MCU Control Register)

このMCU制御レジスタは電力管理用の制御ビットを含みます。

| ピット         | 7   | 6   | 5   | 4   | 3     | 2     | 1     | 0     |       |

|-------------|-----|-----|-----|-----|-------|-------|-------|-------|-------|

| \$35 (\$55) | PUD | SM1 | SE  | SM0 | ISC11 | ISC10 | ISC01 | ISC00 | MCUCR |

| Read/Write  | R/W | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |       |

| 初期値         | 0   | 0   | 0   | 0   | 0     | 0     | 0     | 0     |       |

#### ■ ビット5 - SE:休止許可(Sleep Enable)

SLEEP命令が実行される時にMCUを休止形態へ移行させるには、休止許可(SE)ビットが論理1を書かれなければなりません。MCUの目的外休止形態移行を避けるため、SLEEP命令実行直前に休止許可(SE)ビットを設定(1)し、起動後直ちに解除(0)することが推奨されます。

■ ビット6,4 - SM1,0: 休止種別選択 (Sleep Mode Select Bits 1 and 0)

これらのビットは表7-2.で示される利用可能な3つの休止形態の1つを選択します。

| 表7-2. 休止形態種別選択 |     |          |  |  |  |  |  |

|----------------|-----|----------|--|--|--|--|--|

| SM1            | SM0 | 0 休止形態種別 |  |  |  |  |  |

| 0              | 0   | アイドル動作   |  |  |  |  |  |

| 0              | 1   | パプーダウン動作 |  |  |  |  |  |

| 1              | 0   | スタンバイ動作  |  |  |  |  |  |

| 1              | 1   | パワーダウン動作 |  |  |  |  |  |

注: スタンハーイ動作は外部クリスタル発振子またはセラミック振動子での使用に対してだけ推奨されます。

## 7.5.2. PRR - 電力削減レジスタ (Power Reduction Register)

電力削減レジスタは周辺機能のクロック信号の禁止を許すことによって消費電力削減の方法を提供します。

| ピット         | 7 | 6 | 5 | 4 | 3      | 2      | 1     | 0       |     |

|-------------|---|---|---|---|--------|--------|-------|---------|-----|

| \$36 (\$56) | - | - | - | - | PRTIM1 | PRTIM0 | PRUSI | PRUSART | PRF |

| Read/Write  | R | R | R | R | R/W    | R/W    | R/W   | R/W     |     |

| 初期値         | 0 | 0 | 0 | 0 | 0      | 0      | 0     | 0       |     |

### ■ L\*ット7~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

■ ビット3 - PRTIM1: タイマ/カウンタ1電力削減 (Power Reduction Timer/Counter1)

このビットへの1書き込みはタイマ/カウンタ1部を停止します。タイマ/カウンタ1が許可されると、停止前と同様に動作は継続します。

■ ビット2 - PRTIM0: タイマ/カウンタ0電力削減 (Power Reduction Timer/Counter0)

このビットへの1書き込みはタイマ/カウンタ0部を停止します。タイマ/カウンタ0が許可されると、停止前と同様に動作は継続します。

■ ビット1 - PRUSI: 多用途直列インターフェース電力削減 (Power Reduction USI)

このビットへの1書き込みはその部分へのクロック停止によって多用途直列インターフェース(USI)を停止します。USIの再起動時、USIは正しい動作を保証するために再初期化されるべきです。

■ ビット0 - PRUSART: USART電力削減 (Power Reduction USART)

このビットへの1書き込みはその部分へのクロック停止によってUSARTを停止します。USARTの再起動時、USARTは正しい動作を保証するために再初期化されるべきです。

# 7.5.3. BODCR - BOD制御レジスタ (Brown-Out Detector Control Register)

BOD制御レジスタはソフトウェアによって低電圧検出(BOD)を禁止するための制御ビットを含みます。

| ヒ゛ット        | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0     |       |

|-------------|---|---|---|---|---|---|------|-------|-------|

| \$07 (\$27) | - | - | - | - | - | - | BODS | BODSE | BODCR |

| Read/Write  | R | R | R | R | R | R | R/W  | R/W   |       |

| 初期値         | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0     |       |

## ■ ビット7~2 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

### ■ ビット1 - BODS: BOD休止 (BOD Sleep)

休止間でBODを禁止するにはBODSビットが論理1を書かれなければなりません。これはMCUCRのBOD休止許可(BODSE)ビットと時間制限手順によって制御されます。最初にBODSとBODSEの両方が1に設定されなければなりません。次に4クロック周期内にBODSが1に設定され、BODSEが0に設定されなければなりません。BODSビットはそれが設定された後の3クロック周期間活性(有効)です。SLEEP命令は実際の休止敬愛に対してBODをOFFにするために、BODSが活性(有効)の間に実行されなければなりません。BODSビットは3クロック周期後、自動的に解除(0)されます。

#### ■ ビット0 - BODSE: BOD休止許可 (BOD Sleep Enable)

BODSEビットはBOD休止(BODS)ビット記述で説明されるように、BODS制御ビットの設定を許可します。このBOD禁止は時間制限手順によって制御されます。

# 8. システム制御とリセット

## 8.1. AVRのリセット

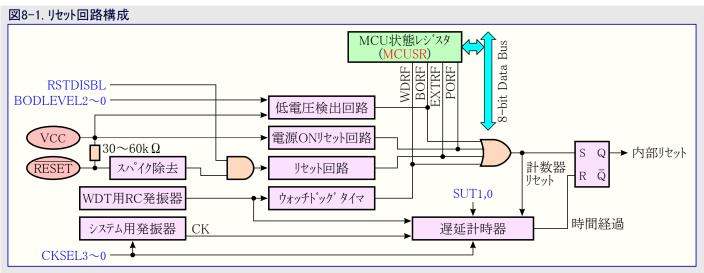

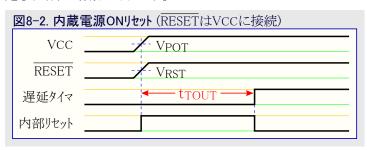

リセット中、全てのI/Oレジスタはそれらの初期値に設定され、プログラムはリセット ベクタから実行を開始します。リセット ベクタに配置される命令は、きっとリセット処理ルーチンへの無条件相対分岐(RJMP)命令でしょう。プログラムが決して割り込み元を許可しないなら、割り込みペクタは使われず、これらの位置に通常のプログラム コードが配置できます。図8-1.の回路構成図はリセット論理回路を示します。リセット回路の電気的特性は134頁の表22-3.で与えられます。

AVRのI/Oポートはリセット元が有効になると直ちにそれらの初期状態にリセットされます。これはどのクロック元の走行も必要ありません。全てのリセット元が無効にされてしまった後、遅延計数器(タイマ)が始動され、内部リセットを引き伸ばします。これは通常動作開始前に安定電圧へ達することを電源に許します。遅延タイマの遅延時間はSUTヒューズとCKSELヒューズを通して使用者によって定義されます。この遅延時間についての各種選択は17頁の「クロック元」で示されます。

#### 8.2. リセット元

ATtiny2313A/4313には次の4つのリセット元があります。

- ・電源ONJセット・・・・・供給電圧が電源ONJセット閾値電圧(VPOA)以下でMCUがJセットされます。

- ・外部リセット・・・・・・・RESETピンが最小パルス幅以上Lowレベルに保たれると、MCUがリセットされます。

- ・ウォッチドッグリセット・・・ウォッチドッグシステム リセット動作が許可され、ウォッチドッグタイマが終了すると、MCUがリセットされます。

- ・低電圧リセット・・・・・低電圧検出器(BOD)が許可され、供給電圧(VCC)が低電圧検出電圧(VBOT)以下でMCUがリセットされます。

## 8.2.1. 電源ONリセット

電源ONリセット(POR)パルスはチップ上の検出回路によって生成されます。検出電圧は134頁の「システムとリセットの特性」で定義されます。 POR信号はVCCが検出電圧以下の時は必ず活性(有効)にされます。 POR回路は供給電圧異常検出は勿論、始動リセットの起動にも使えます。

電源ONJセット回路はデバイスが電源投入でリセットされることを保証します。電源ONJセット閾値電圧への到達はVCCの上昇後にデバイスがどのくらいリセットを保つかを決める遅延計数器(タイマ)を起動します。VCCがこの検出電圧以下に低下すると、リセット信号はどんな遅延もなく再び有効にされます。

#### 8.2.2. 外部リセット

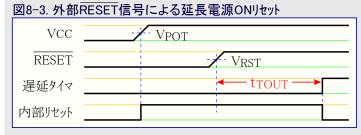

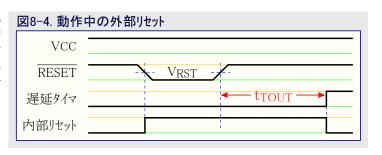

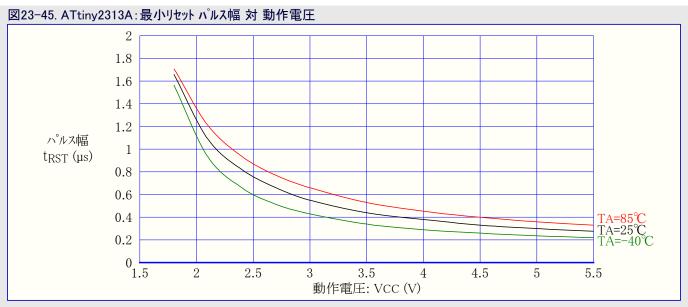

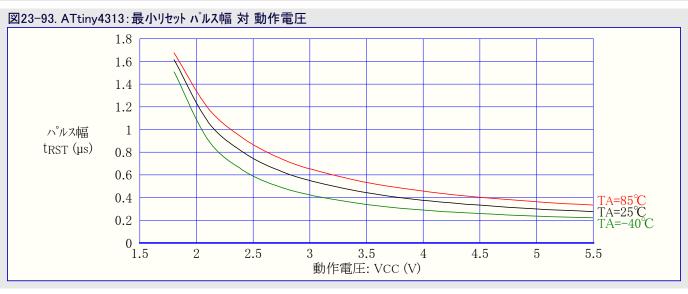

外部リセットは許可ならば、RESETt°ンのLowレヘブルによって生成されます。クロックが動いていなくても、最小ハプルス幅(134頁の「システムとリセットの特性」参照)以上のリセットハプルスはリセットを生成します。短すぎるハプルスはリセット生成が保証されません。印加された信号の上昇がリセット閾値電圧(VRST)に達すると(遅延タイマを起動し)、遅延タイマは遅延時間(t<sub>TOUT</sub>)経過後にMCUを始動します。

### 8.2.3. 低電圧(ブラウンアウト)検出リセット

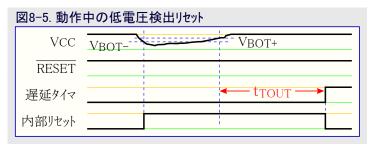

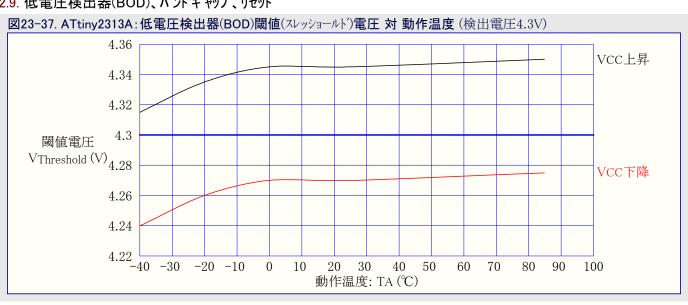

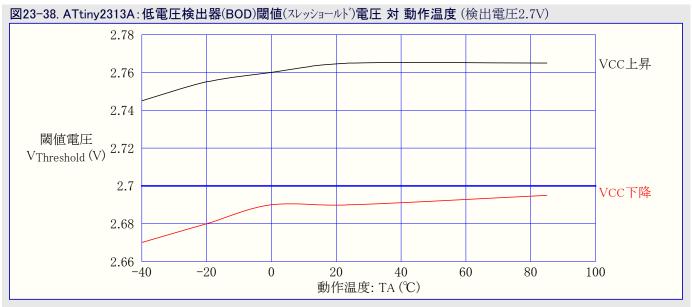

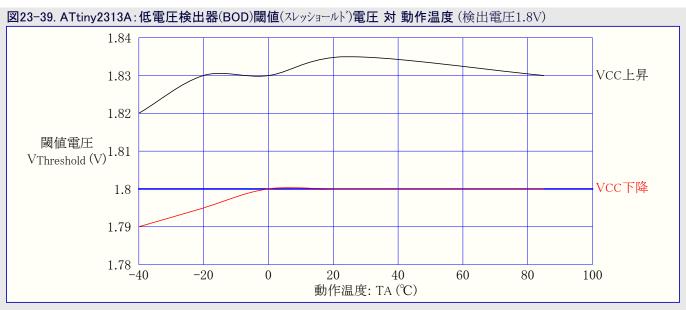

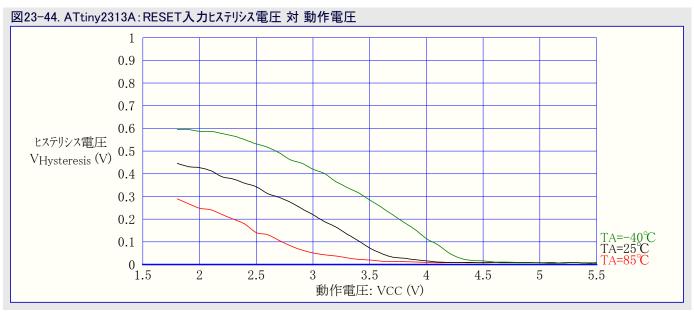

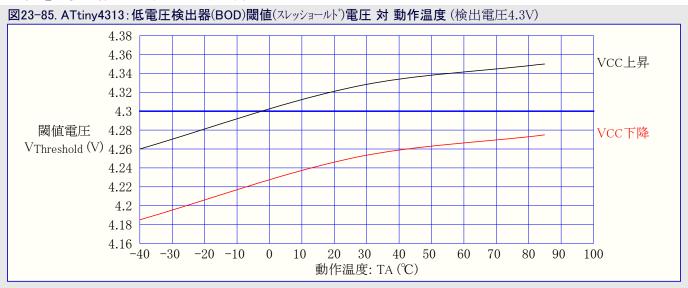

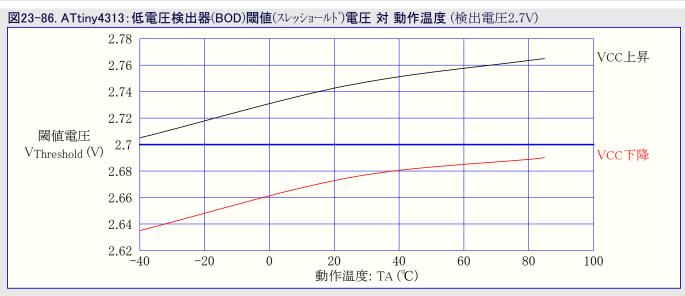

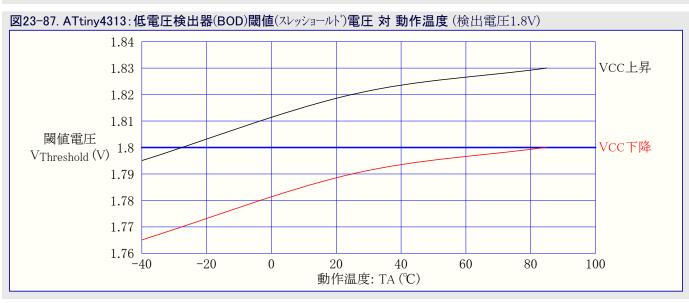

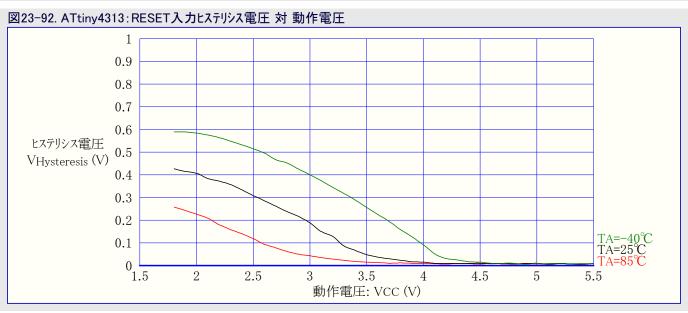

ATtiny2313A/4313には固定化された起動(検出)電圧と比較することによって動作中のVCCを監視するチップ。上の低電圧検出(BOD)回路があります。BODの起動電圧はBODLEVELtューズによって選択できます。この起動電圧はスパイク対策BODを保証するためにヒステリシスを持ちます。検出電圧のヒステリシスはVBOT+=VBOT+VHYST/2、VBOT-=VBOT-VHYST/2と解釈されるべきです。

BODが許可され、VCCが起動電圧以下に下降すると(図8-5.の  $V_{BOT}$ -)、低電圧 $J_{tot}$ -)が直ちに有効とされます。 $V_{CC}$ が起動電圧以上に上昇すると(図8-5.の $V_{BOT}$ -)、(遅延 $J_{tot}$ -)が起動され)遅延 $J_{tot}$ -のは遅延時間( $J_{tot}$ -)経過後にMCUを始動します。

BOD回路は電圧が134頁の「システムとリセットの特性」で与えられるtBOD時間より長く起動電圧以下に留まる場合のみ、VCCでの低下を検出します。

### 8.2.4. ウォッチト・ック・リセット

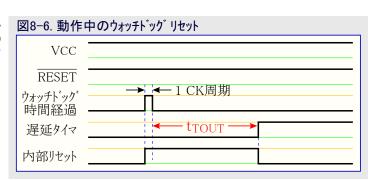

ウォッチト、ック・時間経過時、(内部的に)1CK周期幅の短いリセット パルスを生成します。このパルスの下降端で遅延タイマは遅延時間(t<sub>TOUT</sub>)の計時を始めます。ウォッチト、ック・タイマ操作の詳細については28頁の「ウォッチト、ック・タイマ」を参照してください。

## 8.3. 内部基準電圧

ATtiny2313A/4313は内部基準電圧が特徴です。この基準電圧は低電圧検出(BOD)に使われ、アナログ比較器入力としても使えます。

## 8.3.1. 基準電圧許可信号と起動時間

この基準電圧には使われるべき方法に影響を及ぼすかもしれない起動時間があります。この起動時間は134頁の「システムとリセットの特性」で与えられます。節電のために、この基準電圧は常にONではありません。この基準電圧は次の状態中ONです。

- 1. 低電圧検出リセット許可時 (BODLEVEL2~0ヒューズ、のプ゚ログ゙ラム(0)により)

- 2. アナログ比較器基準電圧接続時 (アナログ比較器制御/状態レジスタ(ACSR)の基準電圧入力選択(ACBG)=1)

従って低電圧検出(BOD)が許可されていないと、ACBGの設定(=1)後、使用者はアナログ比較器出力が使われる前に、基準電圧へ起動時間を与えなければなりません。パワーダウン動作での消費電力を減らすため、使用者はパワーダウン動作へ移行する前に基準電圧がOFFされるのを保証することで上の2つの状態を避けられます。

## 8.4. ウォッチト・ック・タイマ

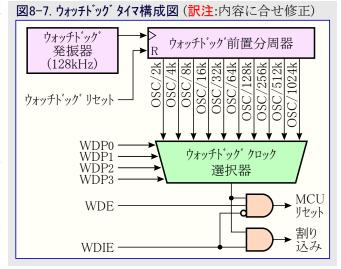

ウォッチト、ック、タイマは128kHzで動く独立したチップ上の発振器からクロック駆動されます。ウォッチト、ック、タイマ前置分周器の制御により、ウォッチト、ック、リセット間隔は30頁の表8-3.で示されるように調整できます。ウォッチト、ック、リセット(WDR)命令はウォッチト、ック、タイマをリセットします。ウォッチト、ック、タイマはそれが禁止される時とチップ。リセットが起こる時もリセットされます。10種の異なるクロック周期がこのリセット周期を決めるために選択できます。別のウォッチト、ック、リセットなしにリセット周期が経過すると、ATtiny2313A/4313はリセットしてリセット、ベクタから実行します。ウォッチト、ック、リセットの詳細タイミングについては30頁の表8-3.を参照してください。

ウォッチドッグ タイマはリセットの代わりに割り込みを生成する設定にもできます。これはパワーダウン動作から起動するのにウォッチドッグを使う時に大変有用となり得ます。

予期せぬウォッチト、ッグ禁止や予期せぬ計時終了周期変更を防ぐため、2つの異なる安全レベルが表8-1.で示されるWDTONヒューズによって選択されます。詳細については次の「ウォッチト、ッグ、タイマ設定変更の時間制限手順」を参照してください。

表8-1. WDTONヒュース、設定によるウォッチト、ック、機能設定

| WDTON t1-7, | 安全レベル | WDT初期状態 | WDT禁止方法  | 計時完了時間変更方法 |

|-------------|-------|---------|----------|------------|

| 非プログラム(1)   | 1     | 禁止      | 時間制限     | なし(常時可)    |

| プログラム(0)    | 2     | 許可      | なし(常時許可) | 時間制限       |

### 8.4.1. ウォッチト、ック、タイマ設定変更の時間制限手順

ウォッチドッグ設定変更手順は安全レベル間で僅かに異なります。各レベルに対して独立した手順が記述されます。

#### • 安全レベル1

この動作種別ではウォッチドッグタイマが初めに禁止されますが、どんな制限もなくウォッチドッグ許可(WDE)ビットに1を書くことにより許可できます。許可したウォッチドッグタイマを禁止する時に時間制限手順が必要とされます。許可したウォッチドッグタイマを禁止するには次の手順に従わなければなりません。

- 1. 同じ操作(命令)でウォッチト、ッグ変更許可(WDCE)とウォッチト、ッグ許可(WDE)に論理1を書きます。WDEビットの直前の値に拘らず、論理1がWDEに書かれなければなりません。

- 2. 次からの4クロック周期内に同じ操作(命令)で欲したWDEとウォッチドッグタイマ前置分周選択(WDP3~0)ビットを書きますが、WDCE ビットは解除(0)されてです。

#### • 安全レベル2

この動作種別ではウォッチドッグタイマが常に許可され、WDEビットは常に1として読めます。時間制限手順はウォッチドッグ計時完了周期を変更する時に必要とされます。ウォッチドッグ計時完了周期を変更するには次の手順に従わなければなりません。

- 1. 同じ操作(命令)でWDCEとWDEに論理1を書きます。WDEビットが常に設定(1)されていても、WDEは時間制限手順を開始するために1を書かれなければなりません。

- 2. 次からの4クロック周期内に同じ操作(命令)で欲したWDP2~0ビットを書きますが、WDCEビットは解除(0)されてです。WDEビットに書かれた値は無関係です。

#### 8.4.2. コート 例

次のコート・例はウォッチト、ッグ(WDT)をOFFに切り替えるアセンブリ言語とC言語の関数を示します。本例は(例えば全割り込み禁止によって)割り込みが制御され、それ故これらの関数実行中に割り込みが起きない前提です。

```

アセンブリ言語プログラム例

WDT OFF:

;ウォッチトック タイマ リセット

WDR

R16, (0<<WDRF)

;WDRF=0値を取得

LDI

OUT

MCUSR, R16

;MCUSRのWDRFを解除(0)

IN

R16, WDTCSR

;現WDTCSR値を取得

ORI

R16, (1<<WDCE) | (1<<WDE)

;WDCEとWDE論理1値を設定

WDTSCR, R16

;WDCEとWDEに論理1書き込み

OUT

R16, (0<<WDE)

;WDE論理0値を取得

LDI

OUT

WDTSCR, R16

;ウォッチトッグ禁止

;呼び出し元へ復帰

RET

C言語プログラム例

void WDT_off(void)

/* ウォッチトック タイマ リセット */

_WDR();

MCUSR = 0x00;

/* MCUSRのWDRFを解除(0)*/

WDTCSR \mid = (1 << WDCE) \mid (1 << WDE);

/* WDCEとWDEに論理1書き込み */

WDTCSR = 0x00;

/* ウォッチト・ック 禁止 */

}

注: 5頁の「コート「例」をご覧ください。

```

# 8.5. リセット関係レジスタ

# 8.5.1. MCUSR - MCU状態レジスタ (MCU Status Register)

MCU状態レジスタはどのリセット元がMCUリセットを起こしたかの情報を提供します。

| ピット         | 7 | 6 | 5 | 4 | 3    | 2    | 1     | 0    | _     |

|-------------|---|---|---|---|------|------|-------|------|-------|

| \$34 (\$54) | _ | - | - | - | WDRF | BORF | EXTRF | PORF | MCUSR |

| Read/Write  | R | R | R | R | R/W  | R/W  | R/W   | R/W  |       |

| 初期値         | 0 | 0 | 0 | 0 | 内容参照 | 内容参照 | 内容参照  | 内容参照 |       |

■ L'ット7~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

■ ビット3 - WDRF: ウォッチドック゛リセット フラク゛(Watchdog Reset Flag)

このビットはウォッチドッグ リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

■ ビット2 - BORF: 低電圧リセット フラク (Brown-Out Reset Flag)

このビットは低電圧リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

■ Ľット1 – EXTRF:外部リセット フラク (External Reset Flag)

このビットは外部リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

■ ビット0 - PORF: 電源ONリセット フラク (Power-on Reset Flag)

このビットは電源ONリセットが起こると設定(1)されます。このビットはこのフラグへの論理0書き込みによってのみリセット(0)されます。

リセット条件の確認にリセット フラグを使うため、使用者はプログラム内で可能な限り早くMCUSRを読み、そして解除(0)すべきです。別のリセットが起こる前にこのレジスタが解除(0)されると、そのリセット元はリセットフラグを調べることによって得られます。

## 8.5.2. WDTCSR - ウォッチトック タイマ制御/状態レジスタ (Watchdog Timer Control and Status Register)

| ピット         | 7    | 6    | 5    | 4    | 3   | 2    | 1    | 0    |        |

|-------------|------|------|------|------|-----|------|------|------|--------|

| \$21 (\$41) | WDIF | WDIE | WDP3 | WDCE | WDE | WDP2 | WDP1 | WDP0 | WDTCSR |

| Read/Write  | R/W  | R/W  | R/W  | R/W  | R/W | R/W  | R/W  | R/W  |        |

| 初期値         | 0    | 0    | 0    | 0    | 不定  | 0    | 0    | 0    |        |

#### ■ ビット7 - WDIF: ウォッチドッグ割り込み要求フラグ (Watchdog Interrupt Flag)

ウォッチト、ック、タイマが割り込みに設定され、ウォッチト、ック、タイマで計時完了が起こると、本ヒ、ットが設定(1)されます。対応する割り込み処理へクタを実行すると、WDIFはハート・ウェアによって解除(0)されます。代わりにWDIFはこのフラグへの論理1書き込みによっても解除(0)されます。ステータスレシ、スタ(SREG)の全割り込み許可(I)ビットとウォッチト、ック・割り込み許可(WDIE)が設定(1)されていれば、ウォッチト、ック・計時完了割り込みが実行されます。

#### ■ ビット6 - WDIE: ウォッチドッグ割り込み許可 (Watchdog Interrupt Enable)

このビットが1を書かれ、ステータス レジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されると、ウォッチドッグ割り込みが許可されます。この動作ではウォッチドッグタイマで計時完了が起きる場合、リセットに代わって対応する割り込みが実行されます。

WDEが設定(1)されると、WDIEは計時完了が起きるとき、ハートウェアによって自動的に解除(0)されます。これは割り込みを使う間のウォッチトッグ リセット保護を維持するのに有用です。WDIEビットが解除(0)された後、次の計時完了はリセットを生成するでしょう。このウォッチトッグ リセットを避けるには、各割り込み後にWDIEが設定(1)されなければなりません。

| 表8-2. | 表8-2. ウォッチドッグタイマ設定 |      |          |  |  |  |  |  |  |  |

|-------|--------------------|------|----------|--|--|--|--|--|--|--|

| WDE   | WDIE               | 動作状態 | 計時完了での動作 |  |  |  |  |  |  |  |

| 0     | 0                  | 停止   | なし       |  |  |  |  |  |  |  |

| 0     | 1                  | 走行   | 割り込み     |  |  |  |  |  |  |  |

| 1     | 0                  | 走行   | リセット     |  |  |  |  |  |  |  |

| 1     | 1                  | 走行   | 割り込み     |  |  |  |  |  |  |  |

#### ■ ビット4 - WDCE: ウォッチドッグ変更許可 (Watchdog Change Enable)

ウォッチト、ック、許可(WDE)ビットが論理0を書かれるとき、このビットは設定(1)されなければなりません。さもなければ、ウォッチト、ック、は禁止されません。一旦1を書かれると、ハート・ウェアが4クロック周期後、このビットを解除(0)します。ウォッチト、ック、禁止手順についてはWDEビットの記述を参照してください。このビットは前置分周ビットを変更する時も設定(1)されなければなりません。28頁の「ウォッチト、ック、タイマ設定変更の時間制限手順」をご覧ください。

#### ■ ビット3 - WDE: ウォッチドッグ許可 (Watchdog Enable)

ウォッチト、ック・許可(WDE)が論理1を書かれるとウォッチト、ック、タイマが許可され、WDEが論理0を書かれるとウォッチト、ック、タイマ機能が禁止されます。WDEはウォッチト、ック、変更許可(WDCE)と、ットが論理レヘ、ル1を持つ場合だけ解除(0)できます。許可されているウォッチト、ック、タイマを禁止するには次の手順に従わなければなりません。

- 1. 同じ操作(命令)内で、ウォッチト、ック、変更許可(WDCE)ヒ、ットとウォッチト、ック、許可(WDE)ヒ、ットに論理1を書きます。例え禁止操作を始める前のWDEが1に設定されていても、論理1がWDEに書かれなければなりません。

- 2. 次からの4クロック周期内で、論理0をWDEに書きます。これがウォッチト、ッグを禁止します。

安全レヘブル2では上記の手順でもウォッチドック゛タイマを禁止することができません。28頁の「**ウォッチドック゛タイマ設定変更の時間制限手順**」をご覧ください。

安全レヘ・ル1ではWDEがMCUSRのウォッチト・ック・リセット フラク・(WDRF)によって無効にされます。WDRFの説明については28頁の「MCUSR - MCU状態レシ・スタ」をご覧ください。これはWDRFが設定(1)されていると、WDEが常に設定(1)されることを意味します。WDEを解除(0)するには上記手順でウォッチトック・を禁止する前にWDRFが解除(0)されなければなりません。この特徴は失敗を引き起こす状態中の複数リセットと失敗後の安全な起動を保証します。

注: ウォッチドッグ タイマが応用で使われないなら、デバイス初期化でウォッチドッグ禁止手順を全て行なうことが重要です。ウォッチドッグが偶然に許可されると(例えばポインタの逸脱や低電圧(ブラウンアウト)状態)、デバイスはリセットし、その転化が次のウォッチドッグ リセットを引き起こすでしょう。この状態を避けるため、応用ソフトウェアは初期化ルーチンでWDRFフラグとWDE制御ビットを常に解除(0)すべきです。

#### ■ ビット5,2~0 - WDP3~0: ウォッチドッグ タイマ前置分周選択(Watchdog Timer Prescaler 3,2,1 and 0)

このWDP3~0ビットはウォッチドッグタイマが許可される時のウォッチドッグタイマの前置分周を決めます。異なる前置分周値と対応する計時完了周期は**表8-3**.で示されます。

| 表8-3. ウォッチト゛ック゛前       | 長8-3. ウォッチドッグ前置分周器選択 |      |      |             |       |      |      |      |      |       |                        |  |   |   |  |  |

|------------------------|----------------------|------|------|-------------|-------|------|------|------|------|-------|------------------------|--|---|---|--|--|

| WDP3                   |                      |      |      | (           | )     |      |      | 1    |      |       |                        |  |   |   |  |  |

| WDP2                   |                      | (    | )    |             | 1     |      |      |      | 0    |       |                        |  | 1 |   |  |  |

| WDP1                   | (                    | 0 1  |      | 1           | 0 1   |      |      | 0 1  |      |       | 0                      |  |   |   |  |  |

| WDP0                   | 0                    | 1    | 0    | 1           | 0     | 1    | 0    | 1    | 0    | 1     | 0 1 0 1 0 1            |  |   | 1 |  |  |

| WDT発振周期数               | 2k                   | 4k   | 8k   | 16k         | 32k   | 64k  | 128k | 256k | 512k | 1024k |                        |  |   |   |  |  |

| 代表的計時完了<br>周期 (VCC=5V) | 16ms                 | 32ms | 64ms | 0.125s      | 0.25s | 0.5s | 1.0s | 2.0s | 4.0s | 8.0s  | (予約)( <mark>注</mark> ) |  |   |   |  |  |

| 注・選択したから               | 010未                 | 滞の有  |      | <u>つ</u> 1つ | が使わ   | れます  |      |      |      |       |                        |  |   |   |  |  |

# 9. 割り込み

この項はATtiny2313A/4313によって実行される割り込み操作の詳細を記述します。AVR割り込み操作の一般説明については9頁の「リセットと割り込みの扱い」を参照してください。

# 9.1. 割り込みべかり

表9-1. リセットと割り込みのべりタ

| ベクタ番号 | プログラム アドレス | 発生元              | 備考                     |

|-------|------------|------------------|------------------------|

| 1     | \$0000     | リセット             | 電源ON, WDT, BOD等の各種リセット |

| 2     | \$0001     | INT0             | 外部割り込み要求0              |

| 3     | \$0002     | INT1             | 外部割り込み要求1              |

| 4     | \$0003     | タイマ/カウンタ1 CAPT   | タイマ/カウンタ1捕獲発生          |

| 5     | \$0004     | タイマ/カウンタ1 COMPA  | タイマ/カウンタ1比較A一致         |

| 6     | \$0005     | タイマ/カウンタ1 OVF1   | タイマ/カウンタ1溢れ            |

| 7     | \$0006     | タイマ/カウンタ0 OVF0   | タイマ/カウンタ0 溢れ           |

| 8     | \$0007     | USART RX         | USART 受信完了             |

| 9     | \$0008     | USART UDRE       | USART 送信緩衝部空き          |

| 10    | \$0009     | USART TX         | USART 送信完了             |

| 11    | \$000A     | アナログ比較器 ANA_COMP | アナログ比較器出力遷移            |

| 12    | \$000B     | PCINTO (PCIO)    | ピン変化0群割り込み要求           |

| 13    | \$000C     | タイマ/カウンタ1 COMPB  | タイマ/カウンタ1比較B一致         |

| 14    | \$000D     | タイマ/カウンタ0 COMPA  | タイマ/カウンタ0比較A一致         |

| 15    | \$000E     | タイマ/カウンタ0 COMPB  | タイマ/カウンタ0比較B一致         |

| 16    | \$000F     | USI START        | USI 開始条件検出             |

| 17    | \$0010     | USI OVF          | USI 計数器溢れ              |

| 18    | \$0011     | EEPROM EE_RDY    | EEPROM 操作可             |

| 19    | \$0012     | ウォッチト`ック` WDT    | ウォッチドッグ計時完了            |

| 20    | \$0013     | PCINT1 (PCI1)    | ピン変化1群割り込み要求           |

| 21    | \$0014     | PCINT2 (PCI2)    | ピン変化2群割り込み要求           |

プログラムが決して割り込み元を許可しないなら、割り込みへ、クタは使われず、これらの位置に通常のプログラムコードを配置できます。 ATtiny2313A/4313での最も代表的且つ一般的なリセットと割り込みのへ、クタアドレス用設定を次に示します。

| アト・レス  | ラヘ゛ル   | 命令   |                   | 注釈                 |

|--------|--------|------|-------------------|--------------------|

| \$0000 |        | RJMP | RESET             | ;各種Jセット            |

| \$0001 |        | RJMP | EXT_INTO          | ;外部割り込み要求0         |

| \$0002 |        | RJMP | EXT_INT1          | ;外部割り込み要求1         |

| \$0003 |        | RJMP | TIM1_CAPT         | ;タイマ/カウンタ1捕獲発生     |

| \$0004 |        | RJMP | TIM1_COMPA        | ;8/マ/カウン81比較A一致    |

| \$0005 |        | RJMP | TIM1 OVF          | ;タイマ/カウンタ1溢れ       |

| \$0006 |        | RJMP | TIMO_OVF          | ;タイマ/カウンタ0溢れ       |

| \$0007 |        | RJMP | USART_RXC         | ;USART 受信完了        |

| \$0008 |        | RJMP | USART_UDRE        | ;USART 送信緩衝部空き     |

| \$0009 |        | RJMP | USART_TX          | ;USART 送信完了        |

| \$000A |        | RJMP | ANA_COMP          | ;アナログ比較器出力遷移       |

| \$000B |        | RJMP | PCINTO            | ;ピン変化0群割り込み要求      |

| \$000C |        | RJMP | TIM1_COMPB        | ;タイマ/カウンタ1 比較B一致   |

| \$000D |        | RJMP | TIMO_COMPA        | ;タイマ/カウンタ0 比較A一致   |

| \$000E |        | RJMP | TIMO_COMPB        | ;タイマ/カウンタ0 比較B一致   |

| \$000F |        | RJMP | USI_STRT          | ;USI 開始条件検出        |

| \$0010 |        | RJMP | USI_OVF           | ;USI 計数器溢れ         |

| \$0011 |        | RJMP | EE_RDY            | ;EEPROM操作可         |

| \$0012 |        | RJMP | WDT_OVF           | ;ウォッチドッグ計時完了       |

| \$0013 |        | RJMP | PCINT1            | ;ピン変化1群割り込み要求      |

| \$0014 |        | RJMP | PCINT2            | ;ピン変化2群割り込み要求      |

| ;      |        |      |                   |                    |

| \$0015 | RESET: | LDI  | R16, LOW (RAMEND) | ;RAM最終アドレス下位を取得    |

| \$0016 |        | OUT  | SPL, R16          | ;スタック ポインタ(下位)を初期化 |

|        |        | }    |                   | ;以下、I/O初期化など       |

## 9.2. 外部割り込み

外部割り込みはINT0,INT1ピンまたはPCINT0~17ピンの何れかによって起動されます。許可したなら、例えINT0,1またはPCINT0~17 ピンが出力として設定されても、割り込みが起動することに注目してください。この特徴はソフトウェア割り込みを生成する方法を提供します。ピン変化0群割り込みPCI0は許可したPCINT0~7の何れかが切り替わると起動します。ピン変化1群割り込みPCI1は許可したPCINT8~10の何れかが切り替わると起動します。ピン変化2群割り込みPCI2は許可したPCINT11~17の何れかが切り替わると起動します。ピン変化割り込み許可レジスタn(PCMSK0,PCMSK1,PCMSK2)は、どのピンがピン変化割り込み要因となるかを制御します。PCINT 0~17でのピン変化割り込みは非同期に検知されます。これはそれらの割り込みがアイドル動作以外の休止形態からもデバイスを起動するのに使えることを意味します。

INT0とINT1割り込みは上昇端または下降端(含む両端)、またはLowレヘルによって起動できます。これはMCU制御レジスタ(MCUCR)で示されるように構成設定されます。INT0またはINT1割り込みがレヘル起動として設定、且つ許可されると、そのピンがLowに保持される限り、割り込みは(継続的に)起動します。INT0やINT1の上昇端または下降端割り込みの認知は17頁の「クロック副系統」で記述されるI/Oクロックの存在を必要とすることに注意してください。

### 9.2.1. Lowレベル割り込み

INTOやINT1のLowレベル割り込みは非同期に検知されます。これはそれらの割り込みがアイドル動作以外の休止形態からもデバイスを起動するのに使えることを意味します。I/Oクロックはアイドル動作を除く全休止形態で停止されます。

レヘル起動割り込みがハプワーダウン動作からの起動に使われる場合、この必要としたレヘルはレヘル割り込みを起動する完全な起動復帰のため、MCUに対して充分長く保持されなければならないことに注意してください。このレヘルが起動時間の最後に先立って消滅すると、MCUは今までどおり起動しますが、割り込みが生成されません。起動時間は17頁の「クロック体系」で示されるようにSUTヒュースとCKSELヒュースで定義されます。

デバイスが起動復帰する前に割り込みピン上のLowレヘブルが取り去られると、プログラム実行は割り込み処理ルーチンへ転換されませんが、 SLEEP命令に続く命令から継続します。

## 9.2.2. ピン変化割り込みタイミング

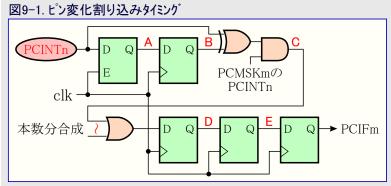

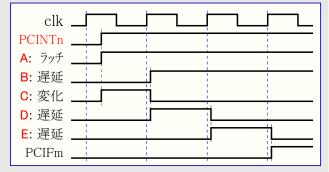

ピン変化割り込みの例は図9-1.で示されます。

### 9.3. 外部割り込み用レジスタ

### 9.3.1. MCUCR - MCU制御レジスタ (MCU Control Register)

MCU制御レジスタは割り込み条件制御ビットを含みます。

| ピット         | 7   | 6   | 5   | 4   | 3     | 2     | 1     | 0     | _     |

|-------------|-----|-----|-----|-----|-------|-------|-------|-------|-------|

| \$35 (\$55) | PUD | SM1 | SE  | SM0 | ISC11 | ISC10 | ISC01 | ISC00 | MCUCR |

| Read/Write  | R/W | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |       |

| 初期値         | 0   | 0   | 0   | 0   | 0     | 0     | 0     | 0     |       |

# ■ ビット3,2 - ISC11,0:外部割り込み1条件制御 (Interrupt Sense Control 1 bit1 and 0)

外部割り込み1はステータスレジスタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レジスタ(GIMSK)の外部割り込み1許可(INT1)ビットが設定(1)される場合のINT 1外部ピッレによって活性(有効)にされます。割り込みを活性にする外部INT1ピッのエッジとレベルは表9-2.で定義されます。INT1ピッの値はエッジ検出に先立って採取さます。エッジまたは論理変化割り込みが選択される場合、1クロック周期よりも長く留まるパルスは割り込みを生成します。より短レハパルスは割り込み発生が保証されません。Lowレベル割り込みが選択される場合、そのLowレベルは割り込みを生成するために現在実行している命令の完了まで保たれなければなりません。

| 表9-2. 外部割り込み1(INT1)割り込み条件 |   |                 |  |  |  |  |  |  |  |  |

|---------------------------|---|-----------------|--|--|--|--|--|--|--|--|

| ISC11 ISC10 割り込み発生条件      |   |                 |  |  |  |  |  |  |  |  |

| 0                         | 0 | INT1ピンのLowレベル   |  |  |  |  |  |  |  |  |

| 0                         | 1 | INT1ピンの論理変化(両端) |  |  |  |  |  |  |  |  |

| 1                         | 0 | INT1ピンの下降端      |  |  |  |  |  |  |  |  |

| 1                         | 1 | INT1ピンの上昇端      |  |  |  |  |  |  |  |  |

## ■ ビット1,0 - ISC01,0: 外部割り込み0条件制御 (Interrupt Sense Control 0 bit1 and 0)

外部割り込みのはステータスレジスタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レジスタ(GIMSK)の外部割り込み0許可(INTO)ビットが設定(1)される場合のINT 0外部ピンによって活性(有効)にされます。割り込みを活性にする外部INTのピンのエッジとレヘルは表9-3.で定義されます。INTのピンの値はエッジ検出に先立って採取されます。エッジまたは論理変化割り込みが選択される場合、1クロック周期よりも長く留まるパルスは割り込みを生成します。より短いパルスは割り込み発生が保証されません。Lowレヘル割り込みが選択される場合、そのLowレヘルは割り込みを生成するために現在実行している命令の完了まで保たれなければなりません。

| 表9-3. タ              | 表9-3. 外部割り込み <b>0</b> (INT0)割り込み条件 |                 |  |  |  |  |  |  |  |  |  |

|----------------------|------------------------------------|-----------------|--|--|--|--|--|--|--|--|--|

| ISC01 ISC00 割り込み発生条件 |                                    |                 |  |  |  |  |  |  |  |  |  |

| 0                    | 0                                  | INT0ピンがLowレヘブル  |  |  |  |  |  |  |  |  |  |

| 0                    | 1                                  | INT0ピンの論理変化(両端) |  |  |  |  |  |  |  |  |  |

| 1                    | 0                                  | INT0ピンの下降端      |  |  |  |  |  |  |  |  |  |

| 1                    | 1                                  | INT0ピンの上昇端      |  |  |  |  |  |  |  |  |  |

## 9.3.2. GIMSK - 一般割り込み許可レジスタ (General Interrupt Mask Register)

| ピット         | 7    | 6    | 5     | 4     | 3     | 2 | 1 | 0 | _     |

|-------------|------|------|-------|-------|-------|---|---|---|-------|

| \$3B (\$5B) | INT1 | INT0 | PCIE0 | PCIE2 | PCIE1 | - | - | - | GIMSK |

| Read/Write  | R/W  | R/W  | R/W   | R/W   | R/W   | R | R | R |       |

| 初期値         | 0    | 0    | 0     | 0     | 0     | 0 | 0 | 0 |       |

### ■ ビット7 - INT1:外部割り込み1許可 (External Interrupt Request 1 Enable)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットが設定(1)され、INT1ビットが設定(1)されると、INT1外部ピン割り込みが許可されます。MCU制御レジスタ(MCUCR)の割り込み条件制御1のビット1と0(ISC11,ISC10)はこの外部割り込みがINT1ピンの上昇端、下降端、両端、またはLowレベルのどれで活性(有効)にされるかを定義します。例えINT1ピンが出力として設定されても、このピンの動きは割り込み要求を引き起こします。外部割り込み要求1に対応する割り込みはINT1割り込みベクタから実行されます。

# ■ ビット6 - INTO: 外部割り込み0許可 (External Interrupt Request 0 Enable)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットが設定(1)され、INT0ビットが設定(1)されると、INT0外部ピン割り込みが許可されます。MCU制御レジスタ(MCUCR)の割り込み条件制御0のビット1と0(ISC01,ISC00)はこの外部割り込みがINT0ピンの上昇端、下降端、両端、またはLowレベルのどれで活性(有効)にされるかを定義します。例えINT0ピンが出力として設定されても、このピンの動きは割り込み要求を引き起こします。外部割り込み要求のに対応する割り込みはINT0割り込みへブタから実行されます。

#### ■ ビット5 - PCIEO: ピン変化0群割り込み許可 (Pin Change Interrupt Enable 0)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットが設定(1)され、PCIE0ビットが設定(1)されると、ピン変化0群割り込みが許可されます。 許可したPCINT0~7ピンの何れかの変化が割り込みを起こします。このピン変化割り込み要求に対応する割り込みはPCI0割り込みへプタから実行されます。PCINT0~7ピンはピン変化割り込み許可レジスタの(PCMSKO)によって個別に許可されます。

#### ■ ビット4 - PCIE2: ピン変化2群割り込み許可 (Pin Change Interrupt Enable 2)

ステータス レジ スタ(SREG)の全割り込み許可(I)ビットが設定(1)され、PCIE2ビットが設定(1)されると、ピン変化2群割り込みが許可されます。 許可したPCINT11~17ピンの何れかの変化が割り込みを起こします。このピン変化割り込み要求に対応する割り込みはPCI2割り込み ^ ブタから実行されます。PCINT11~17ピンはピン変化割り込み許可レジスタ2(PCMSK2)によって個別に許可されます。

## ■ ビット3 - PCIE1: ピン変化1群割り込み許可 (Pin Change Interrupt Enable 1)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットが設定(1)され、PCIE1ビットが設定(1)されると、ピン変化1群割り込みが許可されます。 許可したPCINT8~10ピンの何れかの変化が割り込みを起こします。このピン変化割り込み要求に対応する割り込みはPCI1割り込みへ、クタから実行されます。PCINT8~10ピンはピン変化割り込み許可レジスタ1(PCMSK1)によって個別に許可されます。

#### ■ ビット2~0 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

## 9.3.3. GIFR - 一般割り込み要求フラグレジスタ (General Interrupt Flag Register)

| ピット         | 7     | 6     | 5     | 4     | 3     | 2 | 1 | 0 | _    |

|-------------|-------|-------|-------|-------|-------|---|---|---|------|

| \$3A (\$5A) | INTF1 | INTF0 | PCIF0 | PCIF2 | PCIF1 | - | - | - | GIFR |

| Read/Write  | R/W   | R/W   | R/W   | R/W   | R/W   | R | R | R |      |

| 初期値         | 0     | 0     | 0     | 0     | 0     | 0 | 0 | 0 |      |

## ■ ビット7 - INTF1:外部割り込み1要求フラク (External Interrupt Flag 1)

INT1ピン上のエッシ`または論理変化が割り込み要求を起動すると、INTF1が設定(1)になります。ステータスレシ`スタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レシ`スタ(GIMSK)の外部割り込み1許可(INT1)ビットが設定(1)なら、MCUは対応する割り込みへ、クタへ飛びます。このフラク゛は割り込みルーチンが実行されると解除(0)されます。代わりにこのフラク゛は論理1を書くことによっても解除(0)できます。INT1がレヘル割り込みとして設定されると、このフラク゛は常に解除(0)されます。

#### ■ ビット6 - INTFO:外部割り込み0要求フラグ(External Interrupt Flag 0)

INTOピン上のエッジまたは論理変化が割り込み要求を起動すると、INTFOが設定(1)になります。ステータスレジスタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レジスタ(GIMSK)の外部割り込み0許可(INTO)ビットが設定(1)なら、MCUは対応する割り込みへ、クタへ飛びます。このフラク゛は割り込みルーチンが実行されると解除(0)されます。代わりにこのフラク゛は論理1を書くことによっても解除(0)できます。INTOがレヘル割り込みとして設定されると、このフラク゛は常に解除(0)されます。

## ■ ビット5 - PCIF0: ピン変化0群割り込み要求フラグ (Pin Change Interrupt Flag 0)

PCINT0~7ピンの何れかの論理変化が割り込み要求を起動すると、PCIF0が設定(1)になります。ステータス レジスタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レシ、スタ(GIMSK)のピン変化0群割り込み許可(PCIE0)ビットが設定(1)なら、MCUは対応する割り込みへ、クタへ飛びます。このフラグは割り込みルーチンが実行されると解除(0)されます。代わりにこのフラグは論理1を書くことによっても解除(0)できます。

#### ■ ビット4 - PCIF2: ピン変化2群割り込み要求フラグ (Pin Change Interrupt Flag 2)

PCINT11~17ピンの何れかの論理変化が割り込み要求を起動すると、PCIF2が設定(1)になります。ステータスレシ、スタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レシ、スタ(GIMSK)のピン変化2群割り込み許可(PCIE2)ビットが設定(1)なら、MCUは対応する割り込み ^ クタへ飛びます。このフラグは割り込みルーチンが実行されると解除(0)されます。代わりにこのフラグは論理1を書くことによっても解除(0)できます。

#### ■ ビット3 - PCIF1: ピン変化1群割り込み要求フラグ (Pin Change Interrupt Flag 1)

PCINT8~10ピンの何れかの論理変化が割り込み要求を起動すると、PCIF1が設定(1)になります。ステータスレジ、スタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レシ、スタ(GIMSK)のピン変化1群割り込み許可(PCIE1)ビットが設定(1)なら、MCUは対応する割り込み ^ クタへ飛びます。このフラグは割り込みルーチンが実行されると解除(0)されます。代わりにこのフラグは論理1を書くことによっても解除(0)できます。

## ■ ビット2~0 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

# 9.3.4. PCMSK2 - ピン変化割り込み許可レジスタ2 (Pin Change Mask 2)

| ピット         | 7 | 6       | 5       | 4       | 3       | 2       | 1       | 0       |        |

|-------------|---|---------|---------|---------|---------|---------|---------|---------|--------|

| \$05 (\$25) | _ | PCINT17 | PCINT16 | PCINT15 | PCINT14 | PCINT13 | PCINT12 | PCINT11 | PCMSK2 |

| Read/Write  | R | R/W     |        |

| 初期値         | 0 | 0       | 0       | 0       | 0       | 0       | 0       | 0       |        |

# ■ ビット7 - Res: 予約 (Reserved)

このビットは予約されており、常に0として読まれます。

#### ■ ビット6~0 - PCINT17~PCINT11: ピン変化割り込み17~11許可 (Pin Change Enable Mask 17~11)

各PCINT11~17ピットは対応するI/Oピンでピン変化割り込みが許可されるかどうかを選びます。PCINT11~17と一般割り込み許可レジスタ(GIMSK)のPCIE2が設定(1)なら、対応するI/Oピンのピン変化割り込みが許可されます。PCINT11~17が解除(0)されると、対応するI/Oピンのピン変化割り込みは禁止されます。

# 9.3.5. PCMSK1 - ピン変化割り込み許可レジスタ1 (Pin Change Mask 1)

| ピット<br>\$04 (\$24) | 7 | 6 | 5 | 4 | 3 | 2<br>DCINT10 | 1<br>PCINT9 | 0<br>PCINT8 | DOMSK1 |

|--------------------|---|---|---|---|---|--------------|-------------|-------------|--------|

| Read/Write         | R | R | R | R | R | R/W          | R/W         | R/W         | PCMSK1 |

| 初期値                | 0 | 0 | 0 | 0 | 0 | 0            | 0           | 0           |        |

#### ■ ビット7~3 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

## ■ ビット2~0 - PCINT10~PCINT8: ピン変化割り込み10~8許可 (Pin Change Enable Mask 10~8)

各PCINT8~10ピットは対応するI/Oピンでピン変化割り込みが許可されるかどうかを選びます。PCINT8~10と一般割り込み許可レジスタ (GIMSK)のPCIE1が設定(1)なら、対応するI/Oピンのピン変化割り込みが許可されます。PCINT8~10が解除( $\frac{0}{0}$ )されると、対応するI/O ピンのピン変化割り込みは禁止されます。

## 9.3.6. PCMSKO - ピン変化割り込み許可レジスタO (Pin Change Mask 0)

| ピット         | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |        |

|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| \$20 (\$40) | PCINT7 | PCINT6 | PCINT5 | PCINT4 | PCINT3 | PCINT2 | PCINT1 | PCINT0 | PCMSK0 |

| Read/Write  | R/W    |        |

| 初期値         | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |        |

## ■ ビット7~0 - PCINT7~PCINT0: ピン変化割り込み7~0許可 (Pin Change Enable Mask 7~0)

各PCINT0~7ビットは対応するI/Oピンでピン変化割り込みが許可されるかどうかを選びます。PCINT0~7と一般割り込み許可レジスタ (GIMSK)のPCIE0が設定(1)なら、対応するI/Oピンのピン変化割り込みが許可されます。PCINT0~7が解除(0)されると、対応するI/Oピンのピン変化割り込みは禁止されます。

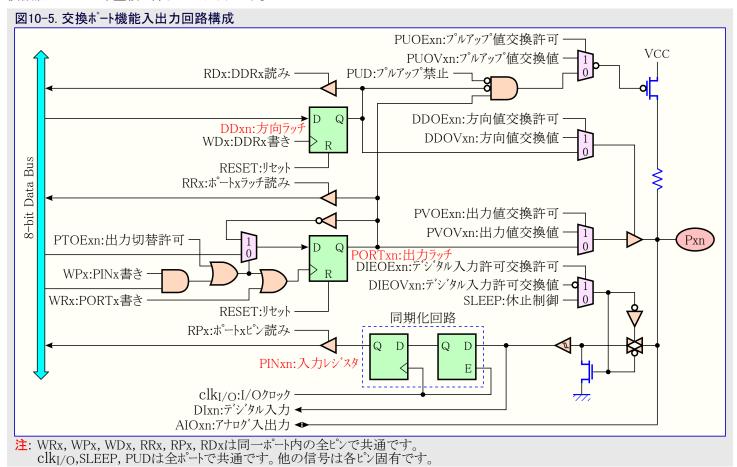

# 10. 入出力ポート