# 特徴

- 高性能、低消費AVR® 8ビット マイクロ コントローラ

- RISC構造

- ・強力な119命令(多くは1周期で実行)

- 32個の1バイト長汎用レジスタ

- ・完全なスタティック動作

16MHz時、16MIPSに達する高速動作

[はじめに]での内容にご注意ください。

本書は一般の方々の便宜のため有志に より作成されたもので、Atmel社とは無関

係であることを御承知ください。しおりの

### ■ データ メモリと不揮発性プログラム メモリ

- ・ 実装書き換え(ISP)可能な2Kバイト(1K語)フラッシュ メモリ内蔵 (10,000回の書き換え可能)

- ・ 実装書き換え可能な128 / 「小のEEPROM (100,000回の書き換え可能)

- 128バイの内蔵SRAM

- ・プログラム用フラッシュメモリとデータ用EEPROM保護用の設定可能な施錠機能

#### ■ 内蔵周辺機能

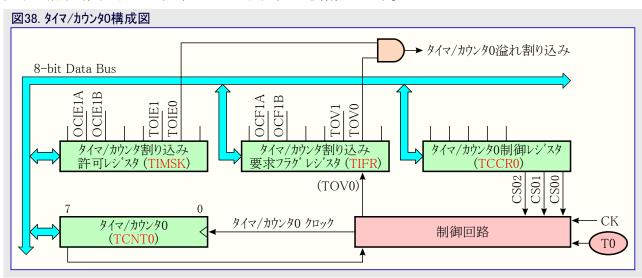

- ・独立した前置分周器付き8ビット タイマ/カウンタ

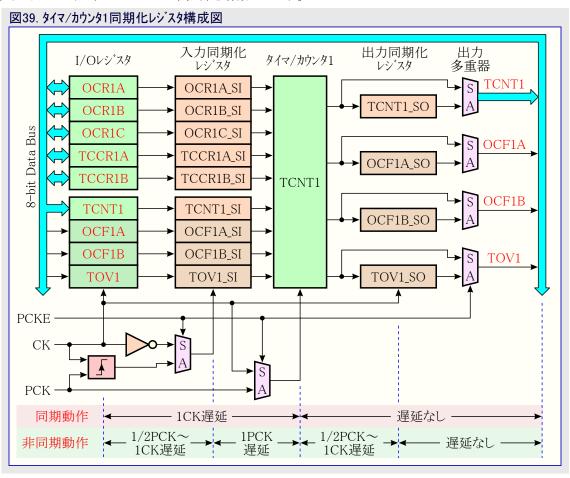

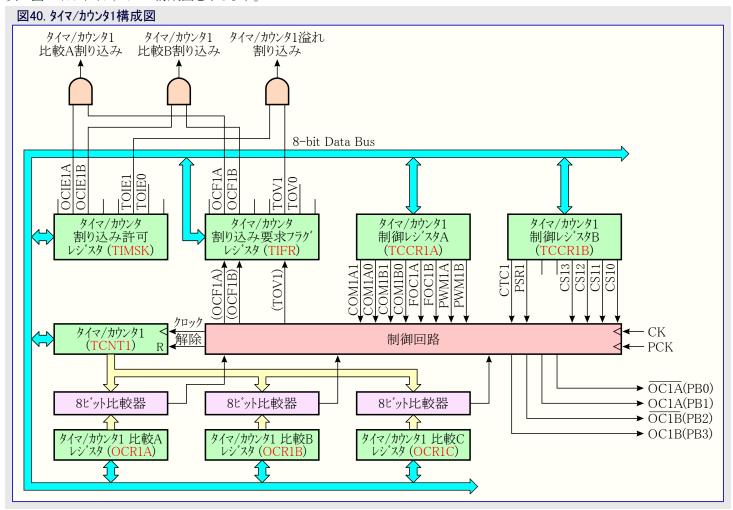

- ・独立した前置分周器付き 独立した比較レジスタでの2つの高周波数PWM出力 高速8ビット タイマ/カウンタ 非重複反転PWM出力ピン

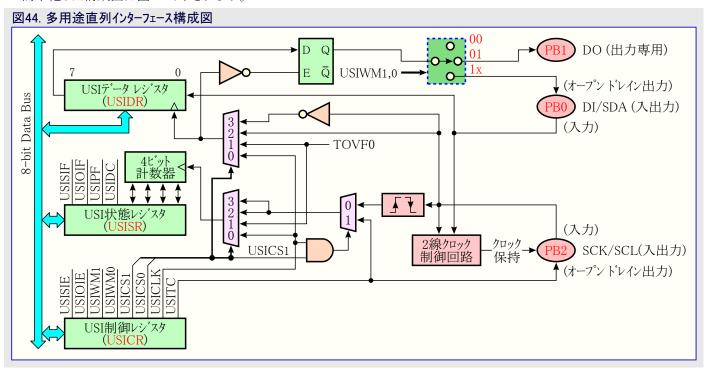

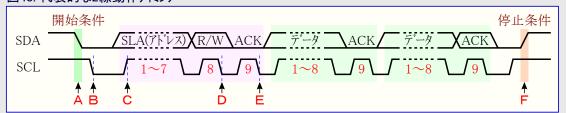

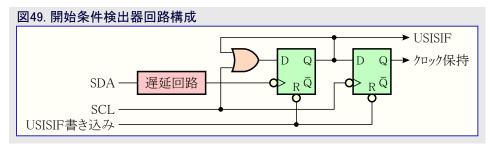

- ・ 開始条件検出器付き多用途直列インターフェース

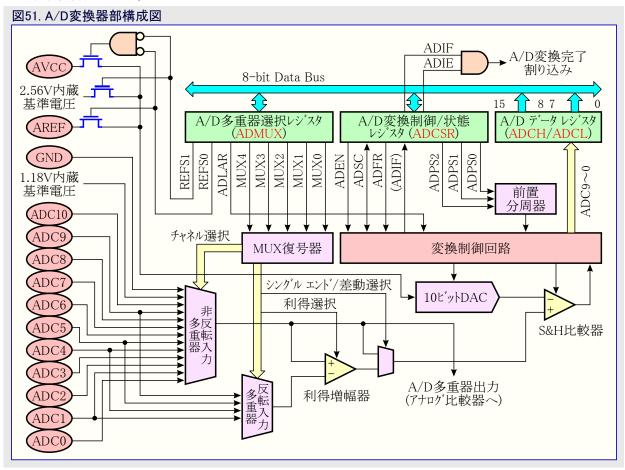

- ・10ビット A/D変換器 / 11のシングル エンド 入力チャネル

8つの差動入力チャネル

可変増幅(×1,×20)付き7つの差動入力チャネル

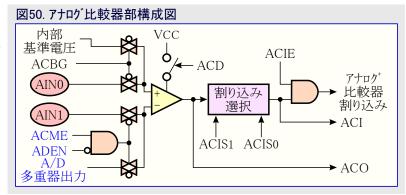

- ・アナログ比較器

- ・ 外部割り込み

- ・11ピンでのピン変化割り込み

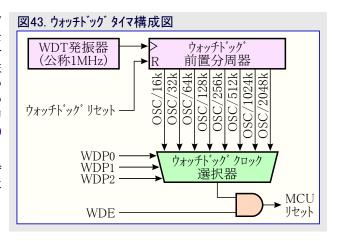

- ・設定可能な専用発振器付きウォッチトック、タイマ

#### ■ 特殊マイクロ コントローラ機能

- ・アイト・ル、A/D変換雑音低減、パワータ・ウン、スタンバイの4つの低消費動作

- ・電源ONJセット回路と設定可能な 低電圧検出器(BOD)

- ・外部及び内部の割り込み

- ・SPIポート経由の実装書き込み

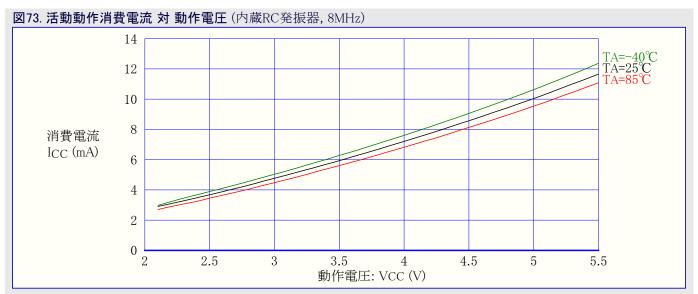

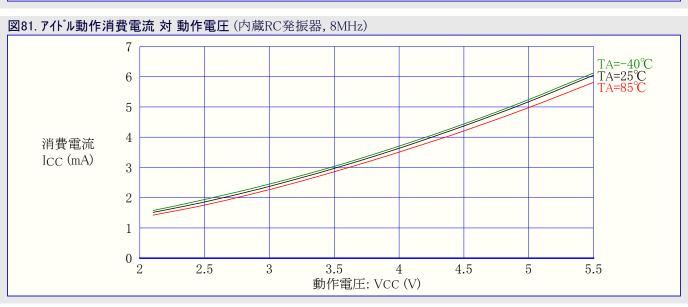

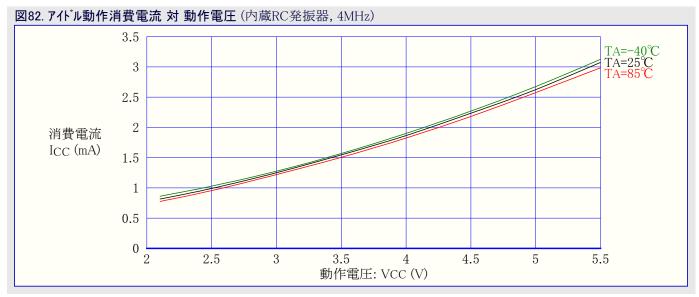

- ・校正付き内蔵RC発振器

#### ■ I/Oと外囲器

- 16ビットの設定可能なI/O

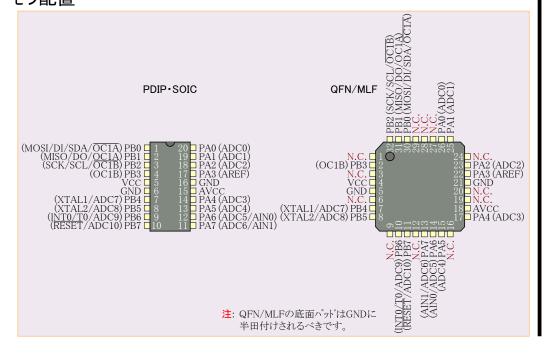

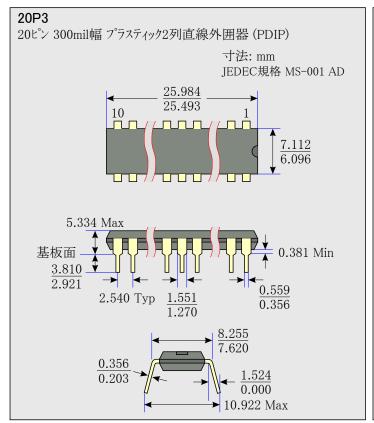

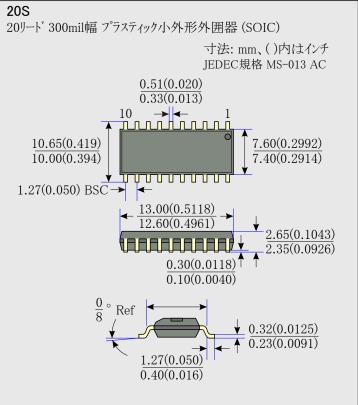

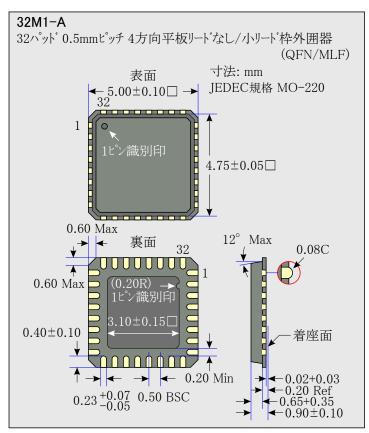

- 20ピンPDIP、20リートSOIC、 32パットQFN/MLF

#### タイマ ■ 動作電圧

- 2.7~5.5V (ATtiny26L)

- 4.5~5.5V (ATtiny26)

#### ■ 動作速度

- 0~8MHz (ATtiny26L)

- 0∼16MHz (ATtiny26)

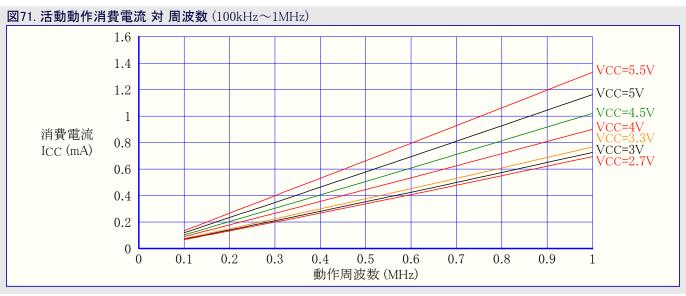

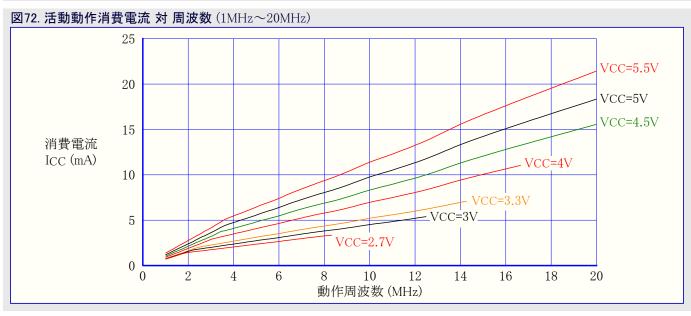

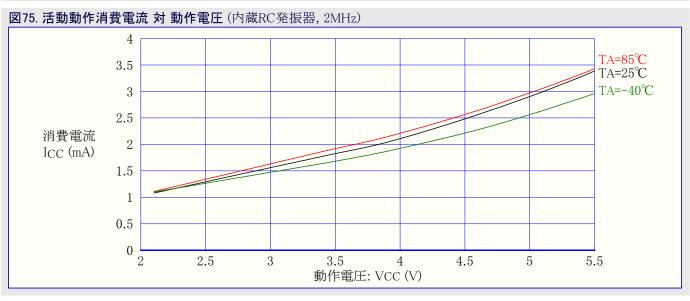

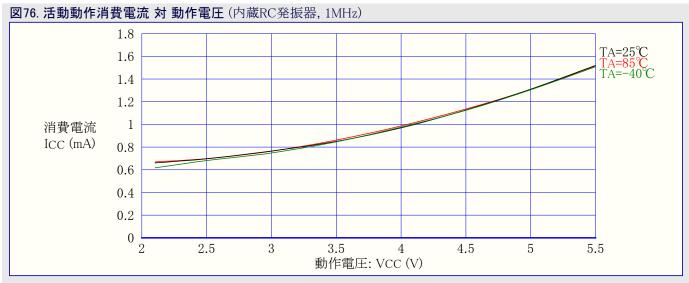

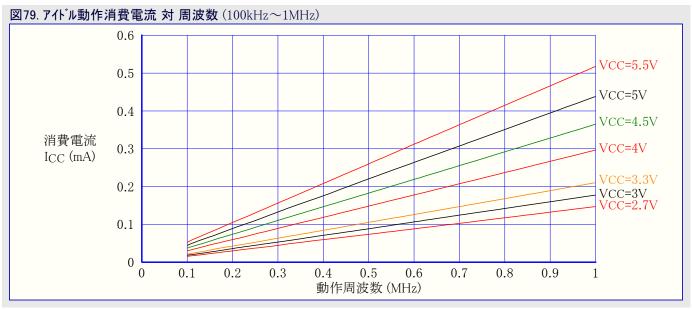

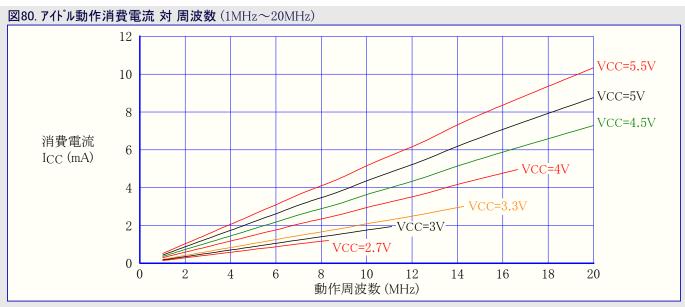

# ■ 消費電力 (25°C,代表値)

- 16MHz,5V,活動動作: 15mA (ATtiny26)

- 1MHz,3V,活動動作: 0.70mA (ATtiny26L)

- 1MHz,3V,アイドル動作: 0.18mA (ATtiny26L)

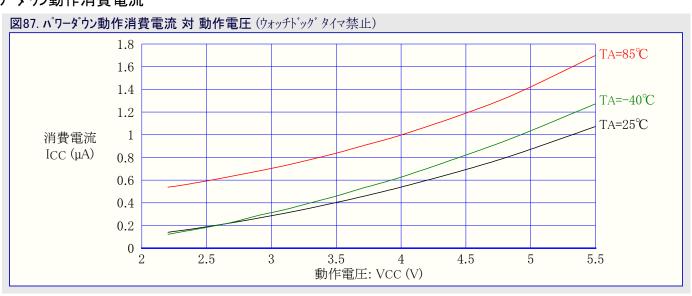

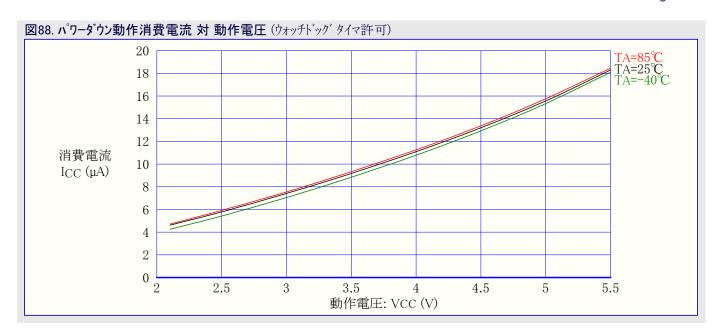

- パワーダウン動作:1µA未満

8ビット **AV** (2) マイクロ コントローラ 実装書き換え可能な 2 K / ごイト フラッシュ メモリ内蔵

ATtiny26 ATtiny26L

# ピン配置

Rev. 1477K-08/10, 1477KJ4-04/22

# 概要

ATtiny26/LはAVR RISC構造の低消費CMOS 8ビット マイクロ コントローラです。1周期で実行する強力な命令はMHzあたり1MIPSに達し、実行速度対電力消費の最適化が容易に行えます。

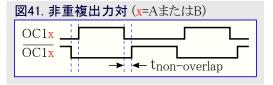

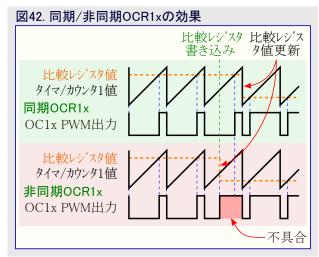

AVRは32個の汎用レジスタと豊富な命令群を兼ね備えています。32個の全レジスタはALU(Arithmetic Logic Unit)に直結され、レジスタ間命令は1クロック周期で実行されます。この構造の結果は現状のCISC型マイクロコントローラよりも10倍速い単位処理量向上を成し遂げる更に優れたコート、効率です。ATtiny26/Lには11のシングルエント、チャネルと8つの差動チャネルまでの高精度A/D変換器があります。7つの差動チャネルには選択的な20倍利得があります。この7つ中の4つの差動チャネルが選択的な利得を持ち、(両入力として)同時に使えます。ATtiny26/Lには2つの独立した出力の高周波数8ビットPWMもあります。この2つのPWM出力には同期整流に理想的な非重複反転出力ピンがあります。ATtiny26/Lの多用途直列インターフェース(USI)はTWI(2線直列インターフェース)やSMバスインターフェースの効率的なソフトウェア実装を許します。これらの特徴は高度な統合型蓄電池充電器や調光器への応用、数ある応用の中で、低価格帯温度調節器、炎検出器を許します。

ATmega26/Lは2Kバイトのフラッシュメモリ、128バイトEEPROM、128バイトSRAM、16本までの汎用入出力線、32個の汎用作業レジスタ、2つの8ビット タイマ/カウンタ(内1つはPWM出力付き)、内部と外部の発振器、内部及び外部割り込み、設定変更可能なウォッチドッグタイマ、2つの差動電圧入力利得段付き11チャネルの10ビット A/D変換器、ソフトウェア選択可能な4つの低消費動作機能を提供します。アイドル動作では動作を停止しますが、タイマ/カウンタと割り込みシステムに継続機能(動作)を許します。ATtiny26/LにはA/D変換雑音低減専用のA/D変換雑音低減動作もあります。この休止形態ではA/D変換部だけが機能します。パワーダウン動作はレジスタ内容を保護しますが、発振器を停止して、以降のハードウェア リセットか外部割り込みまでチップのその他全機能を禁止します。スタンバイ動作はパワーダウン動作と同様ですが、外部発振器が許可されます。ピン変化特性(機能)はパワーダウン動作での最低消費電力の特徴を保ちつつ、外部事象に対する高速応答性をATtiny26/Lで可能にします。

本ディイスはAtmelの高密度不揮発性メモリ技術を使って製造されています。モノリシック チップ 上のフラッシュ メモリと強化した8ビットRISC型 CPUの組み合わせにより、ATtiny26/Lは多くの組み込み制御の応用に対して高度な柔軟性と対費用効果をもたらす強力なマイクロコントローラです。

ATtiny26/L AVRはマクロアセンブラ、ディッカブ、シミュレータ、インサーキットエミューレータ、評価キットを含む完全な専用のプログラム及びシステム開発ツールで支援されます。

#### ピン概要

#### VCC

デジタル電源ピン。

#### **GND**

接地ピン。

#### **AVCC**

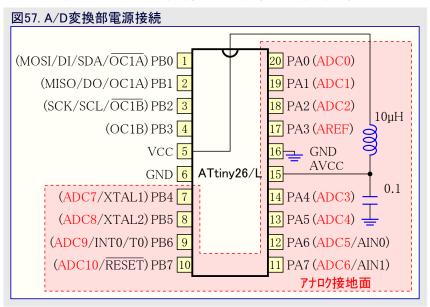

AVCCはポートAとA/D変換器用供給電圧(電源)ピンです。例えA/D変換が使われなくても、外部的にVCCへ接続されるべきです。A/D変換が使われる場合、VCCから低域通過濾波器を通して接続されるべきです。A/D変換操作の詳細については59頁をご覧ください。

#### **PA7~PA0** (ポートA)

ポートAは8ビット汎用入出力ポートです。PA7~0は(ビット毎に選択される)内蔵プルアップ抵抗を提供できます。ポートAには28頁の「ポートAの交換機能」で記述されるように、A/D変換やアナログ比較器のアナログ入力、ピン変化割り込みとしての交換機能があります。

#### PB7~PB0 (ポートB)

ポートBは8ビット汎用入出力ポートです。PB6~0は(ビット毎に選択される)内蔵プルアップ抵抗を提供できます。PB7はリセットとして使われないなら、入出力ピンです。PB7をリセットに替え入出力ピンとして使うにはRSTDISBLヒューズをプログラム(0)してください。ポートBには30頁の「ポートBの交換機能」で記述されるように、A/D変換器、クロック、タイマ/カウンタ、USI、SPIプログラミング、ピン変化割り込みとしての交換機能があります。

外部リセットはPB7/RESETt°ンのLowレヘールにより生成されます。例えクロックが走行(動作)していなくても500ns/5V(**訳注**:修正、原文は50ns/5V)より長いリセット ハールスはリセットを生成します。より短いハールスはリセットの生成が保証されません。

#### XTAL1

発振器反転増幅器への入力と内部クロック操作回路への入力。

#### XTAL2

発振器反転増幅器からの出力。

#### 一般情報

#### 資料

包括的なデータシート、応用記述、開発ツール群はhttp://www.atmel.com/avrでのダウンロートで利用可能です。

#### コート・例

この資料はデバイスの様々な部分の使用法を手短に示す簡単なコート・例を含みます。これらのコート・例はアセンブルまたはコンパイルに先立って、デバイス定義へッタ・ファイルがインクルートされると仮定します。全てのCコンパイラ製造業者がヘッタ・ファイル内にビット定義を含めるとは限らず、またCでの割り込みの扱いがコンパイラに依存することに注意してください。より多くの詳細についてはCコンパイラの資料で確認してください。

#### AVR CPU 17

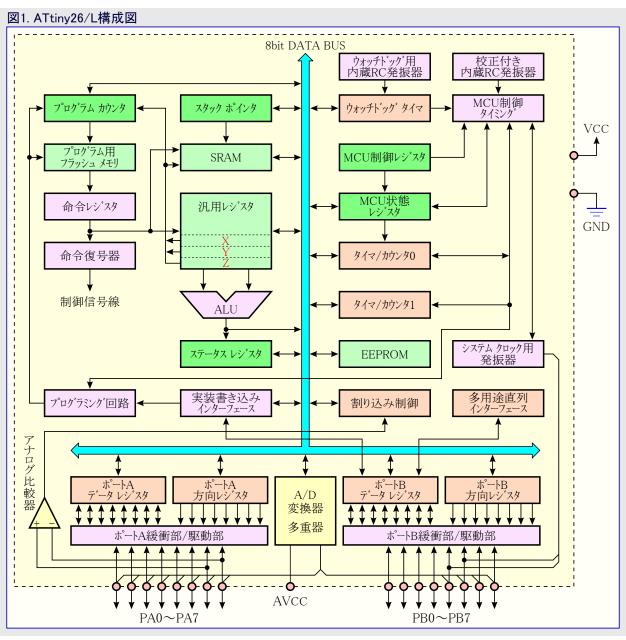

# 構造概要

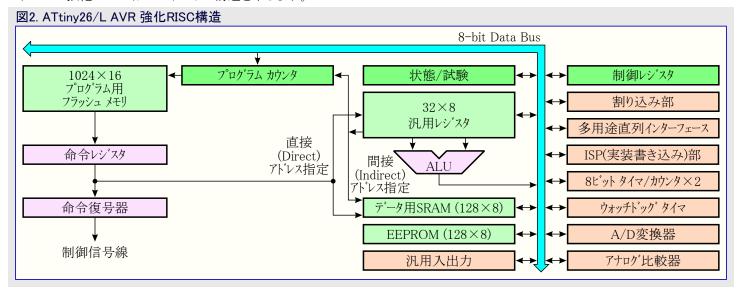

高速レジスタファイルの概念は1クロック周期アクセス時間の32個の8ビット長汎用レジスタを含みます。これは1クロック周期中に1つのALU(Arithm etic Logic Unit)命令が実行されることを意味します。1クロック周期で、2つのオペランドはレジスタファイルから出力されて、命令が実行され、その結果がレジスタファイルに書き戻されます。

32個中の6つのレシ、スタはデータ空間についてアドレス計算が効率的に行える、3つの16ビット長間接アドレスポインタとして使えます。3つのアドレスポインタの1つは定数表参照用アドレスポインタとしても使われます。これらの付加機能レシ、スタは16ビット長のXレシ、スタ、Yレシ、スタ、Zレシ、スタです。

ALUはレジスタ間、レジスタと定数間の算術及び論理操作を行います。単一レジスタ操作も同様にALUで実行されます。図2.はATtiny 26/L AVR強化RISCマイクロコントローラの構造を示します。

付加的なレシ、スタ操作として、通常のメモリアト、レス指定をレシ、スタファイルにも使えます。実際にはレシ、スタファイルがデータ空間の最下位32バイト(\$00~\$1F)に割り当てられ、通常のメモリ位置としてのアクセスができることによって行えます。

I/Oメモリ空間は制御レジスタ、タイマ/カウンタ、A/D変換器、その他I/O機能など、CPU周辺機能用の64アドレスを含みます。I/Oメモリは直接またはレジスタ ファイルに後続するデータ空間位置\$20~\$5Fとしてアクセスできます。

AVRのメモリとハ、スはプログラム用とデータ用に各々分離されたハーハ・ート・構造で構成されています。プログラムメモリは2段のパイプ。ラインでアクセスされます。1命令の実行中に次の命令をプログラムメモリから事前取得します。この概念は全てのクロック周期で命令が実行されるのを可能にします。プログラムメモリは実装書き換え可能なフラッシュメモリです。

プログラム カウンタ(PC)相対の無条件分岐(RJMP)命令と呼び出し(RCALL)命令で1Kアトンス空間全てがアクセスされます。AVRの多くの命令は16ビット1語の形式です。全てのプログラム メモリのアトンスに16または32ビット命令を配置できます。

割り込みやサブルーチン呼び出しでの戻りアドレスを示すプログラム カウンタ(PC)はスタックに保存されます。スタックは一般的なデータ用SRAMへ効果的に割り当てられ、スタック容量はSRAM容量とSRAM使用量でのみ制限されます。プログラムではリセット時の初期化ルーチンで(サブルーチンや割り込みが実行される前に)、スタックポインタ(SP)を初期化しなければなりません。8ビットのSPはI/O空間にあり、読み書き可能です。C言語で書かれたプログラムについてはスタック容量がリンカファイルで宣言されなければなりません。より多くの情報についてはC使用者の手引きを参照してください。

128バイトのデータSRAMはAVR構造で支援される5つの異なるアドレス指定種別で容易にアクセスできます。

AVR構造に於けるメモリ空間は全て直線的な普通のメモリ配置です。

I/Oメモリ空間は制御レジスタ、タイマ/カウンタ、その他I/O機能としてのCPU周辺機能用の64アドレスを含みます。AVR構造のメモリ空間は全て直線的な普通のメモリ配置です。

柔軟な割り込み部にはI/O空間の各制御レシ、スタとステータスレシ、スタ(SREG)の全割り込み許可(I)ビットがあります。全ての割り込み要因はプログラムメモリの先頭に割り込みへ、クタ表として、個別の割り込みへ、クタがあります。各割り込みはこの割り込みへ、クタ表の位置に従った優先順です。下位側割り込みへ、クタアドレスが高い優先順位です。

# 汎用レジスタファイル

図3.は32個の汎用レジスタの構成を示します。

全てのレシ、スタに対するレシ、スタ操作命令はレシ、スタ直接指定ができ、1周期でアクセスします。SBCI,SUBI,CPI,ANDI,ORIの5つの算術、論理定数演算命令と、定数をレシ、スタに設定するLDI命令だけは例外です。これらの命令はレシ、スタファイル後半のR16~R31に対してだけ適用されます。通常のSBC,SUB,CP,AND,ORや他の全てのレシ、スタ間、単一レシ、スタ操作命令はレシ、スタファイルの全レシ、スタに適用されます。

図3.で示されるように、各レシ、スタはデータメモリ領域の先頭からの32アトレスに配置されています。レシ、スタファイルは物理的にSRAMのような配置構成ではなく、この特別な構成のため、X,Y,Zレジ、スタを指標とする任意のレシ、スタ指定のような、非常に柔軟なアクセスができます。

| 図3. AVR CPU 汎用レジスタ構成図 |     |      |                               |                |  |  |  |  |

|-----------------------|-----|------|-------------------------------|----------------|--|--|--|--|

|                       | 7 0 | アドレス |                               |                |  |  |  |  |

|                       | R0  | \$00 |                               |                |  |  |  |  |

|                       | >   |      |                               |                |  |  |  |  |

|                       | R15 | \$0F |                               |                |  |  |  |  |

| 汎用                    | R16 | \$10 |                               |                |  |  |  |  |

| レジスタ                  | ~   |      |                               |                |  |  |  |  |

| ファイル                  | R26 | \$1A | VISごフタ                        | 下位バイト<br>上位バイト |  |  |  |  |

|                       | R27 | \$1B | $\Delta V \neq \Delta \gamma$ | 上位バイト          |  |  |  |  |

|                       | R28 | \$1C | Yレジスタ                         | 下位バイト          |  |  |  |  |

|                       | R29 | \$1D | !                             | 上位バイト          |  |  |  |  |

|                       | R30 | \$1E | フレジブスタ                        | 下位バイト<br>上位バイト |  |  |  |  |

|                       | R31 | \$1F |                               | 上位バイト          |  |  |  |  |

#### Xレシ、スタ、Yレシ、スタ、Zレシ、スタ

レシ、スタR26~R31には通常の汎用用途以外にいくつかの付加機能があります。これらのレシ、スタはデータ空間の間接アト、レス指定ポインタにもなります。この3つの間接アト、レス用レシ、スタX,Y,Zは図4.で定義されます。

これらのアドレスレジスタは定数変位付き、自動増加/減少付きのアドレス指定が行えます(これらの概要は個別命令を参照してください)。

| 図4. X,Y,Zレジスタ構成図     |    |            |   |   |            |   |  |  |

|----------------------|----|------------|---|---|------------|---|--|--|

|                      | 15 | (上位)       |   |   | (下位)       | 0 |  |  |

| X レシ <sup>*</sup> スタ | 7  | R27 (\$1B) | 0 | 7 | R26 (\$1A) | 0 |  |  |

| Y レジスタ               | 7  | R29 (\$1D) | 0 | 7 | R28 (\$1C) | 0 |  |  |

| Z レジスタ               | 7  | R31 (\$1F) | 0 | 7 | R30 (\$1E) | 0 |  |  |

#### **ALU** (Arithmetic Logic Unit)

高性能なAVRのALUは32個の全汎用レシ、スタに直接接続され、動作します。レジ、スタファイル内のレジ、スタ間ALU操作は1クロック周期内で実行されます。ALU操作は算術演算、論理演算、ビット操作の3つの主な種類に大別されます。

# ■ ステータス レシ スタ (Status Register) SREG

AVRのステータス レシ、スタ(SREG)は、I/O領域の\$3F(\$5F)で、次のように定義されます。

| ピット         | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _    |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$3F (\$5F) | I   | Т   | Н   | S   | V   | N   | Z   | С   | SREG |

| Read/Write  | R/W |      |

| 初期値         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

#### ■ ビット7 - I: 全割り込み許可 (Global Interrupt Enable)

この全割り込み許可ビットは許可されるべき割り込みに対して設定(1)されなければなりません。そして個別割り込み許可制御は一般割り込み許可レジスタ(GIMSK)とタイマ/カウンタ割り込み許可レジスタ(TIMSK)の割り込み許可レジスタで行われます。全割り込み許可ビットが解除(0)されると、GIMSKとTIMSK値と無関係にどの割り込みも許可されません。このIビットは割り込みが起きてしまった後、ハードウェアによって解除(0)され、後続の割り込みを許可するため、割り込み処理のRETI命令によって設定(1)されます。Iビットは「命令一式参考書」で記述されるようにSEIやCLI命令で応用(プログラム)によって設定(1)や解除(0)もできます。

#### ■ L'yh6 - T: L'yh変数 (Bit Copy Storage)

このTビットはBLD(Bit LoaD)命令とBST(Bit STore)命令の転送元または転送先として使われます。BLD命令はTをレジスタ ファイルのレジ スタのビットに複写し、BST命令はレジスタ ファイルのレジスタからビットをTに複写します。

#### **■ L**\*ット5 - **H**: **ハ**ーフキャリー フラク\* (Half Carry Flag)

このHフラグはいくつかの算術演算命令でのハーフキャリーを示します。ハーフキャリーはBCD演算に有用です。詳細情報については命令要約を参照してください。

#### ■ ビット4 - S: 符号 (Sign Bit, S= N Ex-OR V)

このSフラグは常に負(N)フラグと2の補数溢れ(V)フラグの排他的論理和です。詳細情報については命令要約を参照してください。

#### ■ ビット3 - V: 2の補数溢れフラグ(2's Complement Overflow Flag)

この2の補数溢れ(V)フラグは2の補数算術演算を補助します。詳細情報については命令要約を参照してください。

#### **■ Ľット2 - N**: **負フラク** (Negative Flag)

このNフラグは算術及び論理演算の結果が負であること(MSB=1)を示します。詳細情報については命令要約を参照してください。

#### **■ L**'y**\1** - **Z** : **t**'**D 750**' (Zero Flag)

このZフラグは算術及び論理演算の結果がゼロ(0)であることを示します。詳細情報については命令要約を参照してください。

#### **■ L** \* **v l O C** : **キャリー フラク** \* (Carry Flag)

このCフラグは算術及び論理演算でキャリーが発生したことを示します。詳細情報については命令要約を参照してください。

ステータス レシ スタは割り込み処理ルーチン移行時の保存と、割り込み処理ルーチンから復帰時の再設定が、自動的に行われないことに注意してください。これはソフトウェアにより操作しなければなりません。(<mark>訳注</mark>:共通性のため本注意追加)

#### ■ スタック ポインタ (Stack Pointer) SP

ATtiny26/Lのスタック ポインタはI/O空間位置\$3D(\$5D)で8ビット レジスタとして実装されます。ATtiny26/Lが224(\$E0)位置を持つため、8 ビットが使われます。

| ビット _       | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |      |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$3D (\$5D) | SP7 | SP6 | SP5 | SP4 | SP3 | SP2 | SP1 | SP0 | ] SF |

| Read/Write  | R/W |      |

| 初期値         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

スタック ポインタはサブルーチンと割り込みのスタックが配置されるデータSRAMのスタック領域を指し示します。データSRAM内のスタック領域は、割り込みの許可や、何れかのサブルーチン呼び出しが実行される前にプログラムによって定義されなければなりません。スタック ポインタは\$60以上を指示するために設定されなければなりません。スタック ポインタは、PUSH命令でデータがスタック上に格納されるときー1され、サブルーチン呼び出しや割り込みでアドレスがスタック上に格納されるときー2されます。POP命令でデータをスタックから引き出すとき+1され、サブルーチンからの復帰(RET命令)や割り込みからの復帰(RETI命令)でアドレスをスタックから引き出すとき+2されます。

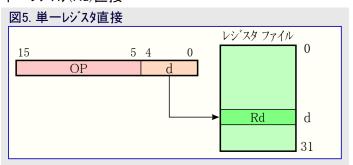

# プログラム及びデータ空間に対するアドレス指定種別

ATtiny26/L AVR強化RISCマイクロコントローラはプログラムフラッシュメモリ、SRAM、レジスタファイル、I/Oデータメモリのアクセス用に強力で効率的なアトレス指定種別を支援します。本項はAVR構造によって支援される各アトレス指定種別を記述します。図内のOPは命令語の動作コート、部を意味します。単純化のため、全ての図がアトレス指定ビットの正確な位置を示すとは限りません。

#### 単一レジスタ(Rd)直接

オペランドはレジスタd(Rd)を示します。

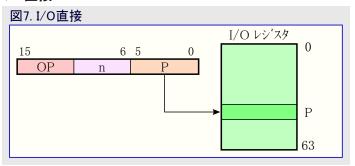

#### I/O直接

オヘ<sup>°</sup>ラント゛はI/Oアト゛レスPと、転送元または転送先となるレシ、スタn(Rn)を示します。

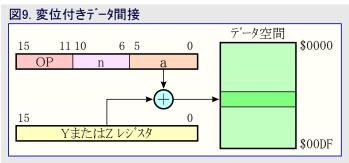

#### 変位付きデータ間接

オペラント、アト・レスは、YまたはZレジ、スタの内容と命令語内の6ビット値aを加算した値となり、他方が転送元または転送先となるレジスタn(Rn)を示します。

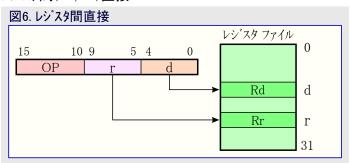

#### レジスタ間(Rd. Rr)直接

オペラント、はレジスタr(Rr)とd(Rd)を示し、結果はレジスタd(Rd)に格納されます。

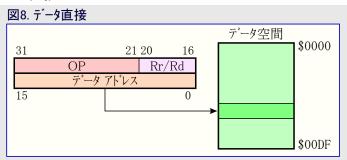

# データ直接

オペラント、は2語命令の下位16ビットでデータ空間のアドレス位置を示し、Rr/Rdは転送元または転送先となるレジスタを示します。

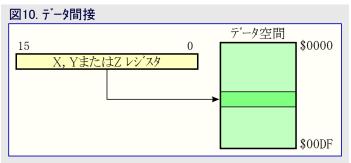

#### データ間接

オペラント、アトンスは、X, YまたはZレジスタの内容となります。

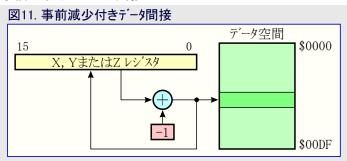

#### 事前減少付きデータ間接

X,YまたはZレジ、スタはアクセス動作前に内容が減少されます。オヘ。 ランド、アドレスは減少されたX,YまたはZレジ、スタの内容となります。

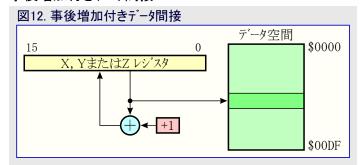

# 事後増加付きデータ間接

X,YまたはZレジスタはアクセス動作後に内容が増加されます。オペラント、アト、レスは増加される前のX,YまたはZレジスタの内容となります。

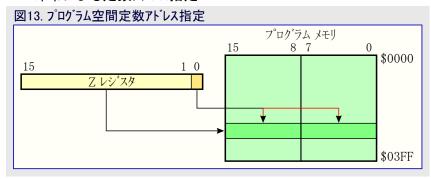

#### LPM命令による定数アドレス指定

ハイト定数のアトレスはZレジスタの内容で示されます。上位15ビットが0~1Kの語(ワート)アトレスを指示し、最下位ビットがハイト位置を表し、LSB=0で下位ハイト、LSB=1で上位ハイトを示します。

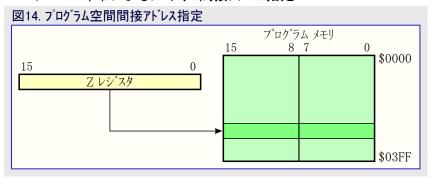

#### IJMP. ICALL命令によるプログラム間接アドレス指定

プログラムはZレシ、スタの内容のアト・レスから実行が継続されます。(PCにZレシ、スタの内容を設定します。)

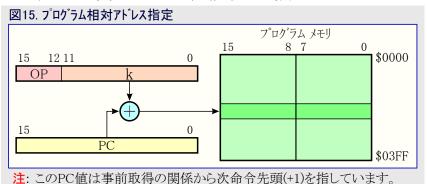

# RJMP, RCALL命令によるプログラム相対アドレス指定

プログラムはPC+k+1のアドレスから継続実行されます。相対値kは符号付きで、-2048~2047です。

# メモリ

AVR CPUはチップ(デバイス)用に選択したクロック元から直接的に生成したCPUクロック(clkCPU)により駆動されます。内部クロック分周は使われません。

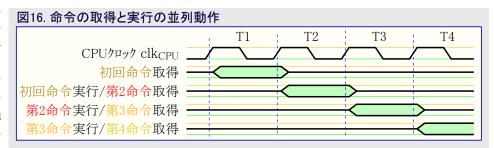

図16.はハーハート・構造と高速アクセスレジスタファイルの概念によって可能とされる並列の命令取得と命令実行を示します。これは機能対費用、機能対クロック、機能対電源部についての好結果と対応するMHzあたり1MIPSを達成するための基本的なパイプラインの概念です。

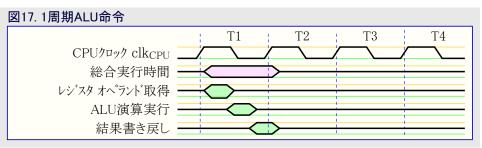

図17.はレジスタファイルに対する内部タイミングの概念を示します。単一クロック周期で、2つのレジスタオペランドを使うALU操作が実行され、その結果が転送先レジスタへ書き戻されます。

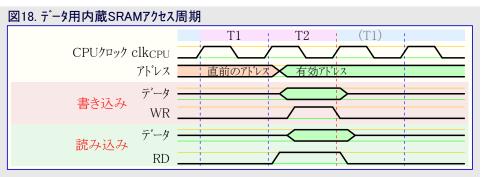

データ用内蔵SRAMアクセスは図18.で記載されるように2clkcpu周期で実行されます。

(訳注) 内蔵SRAMのアクセスを含む代表的な命令はT1,T2の2周期で実行され、T1で対象アトレスを取得/(算出)/確定して、T2で実際のアクセスが行われます。次の(T1)は次の命令のT1です。

# 実装書き換え(ISP: In-System Program)可能なプログラム用フラッシュ メモリ

ATtiny26/Lはプログラム格納用に実装書き換え可能な2Kハイトのフラッシュメモリをチップ上に含みます。全ての命令が16または32ビット語のため、フラッシュメモリは1K×16ビットとして構成されています。フラッシュメモリは少なくても10,000回再書き込みの耐久性があります。ATtiny 26/Lのプログラム カウンタ(PC)は10ビット幅で、従ってプログラムメモリ内の1024アドレスを指定します。フラッシュメモリ書き込みの詳細記述については67頁の「メモリプログラミング」をご覧ください。各種プログラムメモリアドレス指定種別については7頁の「プログラム及びデータ空間に対するアトレス指定種別」をご覧ください。

#### データ用SRAM

図19.はATtiny26/Lのデータメモリの構成を示します。

下位224データ メモリ位置は汎用レジスタファイル、I/Oレジスタ、内蔵データSRAMを指定します。最初の96位置はレジスタファイルとI/Oレジスタ、次の128位置がデータ用内蔵SRAMを指定します。

直接、間接、変位付き間接、事前減少付き間接、事後増加付き間接の5つのアトレス指定種別がデータメモリ空間を網羅します。レジスタファイル内のレジスタR26~R31が間接アトレス指定時のポインタレジスタです。

直接アドレス指定は全てのデータアドレス空間に届きます。変位付き間接アドレス指定はYまたはZレジスタで与えられる基準アドレスから届く63アドレス位置が特徴です。

事前減少付き間接、事後増加付き間接アドレス指定を使う時はアドレス レジスタX,YまたはZが使われ、自動的に減少または増加されます。

ATtiny26/Lの32個の汎用レジスタ、64個のI/Oレジスタ、128バイトのデータ用内蔵SRAMはこれら全てのアドレス指定種別を通して全て直接的にアクセス可能です。

各アト・レス指定種別の詳細記述については7頁の「プログラム及びデータ空間に対するアト・レス指定種別」をご覧ください。

| 図19. データ   | 図19. データ空間とSRAMの配置 |        |  |  |  |  |  |  |

|------------|--------------------|--------|--|--|--|--|--|--|

| アト・レス      |                    |        |  |  |  |  |  |  |

|            | R0                 | \$0000 |  |  |  |  |  |  |

| 12374      | R1                 | \$0001 |  |  |  |  |  |  |

| レジスタファイル   | }                  |        |  |  |  |  |  |  |

| 7711       | R30                | \$001E |  |  |  |  |  |  |

|            | R31                | \$001F |  |  |  |  |  |  |

| I/O        | \$00               | \$0020 |  |  |  |  |  |  |

| レジスタ       | \$01               | \$0021 |  |  |  |  |  |  |

| (赤字は       | }                  |        |  |  |  |  |  |  |

| I/O        | \$3E               | \$005E |  |  |  |  |  |  |

| アドレス)      | \$3F               | \$005F |  |  |  |  |  |  |

|            | \$0060             | \$0060 |  |  |  |  |  |  |

| 中华         | \$0061             | \$0061 |  |  |  |  |  |  |

| 内蔵<br>SRAM | }                  |        |  |  |  |  |  |  |

| SIVAM      | \$00DE             | \$00DE |  |  |  |  |  |  |

|            | \$00DF             | \$00DF |  |  |  |  |  |  |

#### **EEPROMアクセス**

EEPROMをアクセスするレジスタはI/O空間でアクセスできます。

代表的な書き込み(<mark>訳注</mark>:原書はアクセス)時間は8.3msです。(書き込みは)自己タイシグ機能ですが、使用者ソフトウェアは次バイトが書ける時を検知してください。EEPROMが新規データを受け入れる準備ができているときに起動するために、特別なEEPROM操作可割り込みが設定できます。

実行中のEEPROM書き込み動作は例えリセット条件が起きても完了(最後まで実行)します。

不測のEEPROM書き込みを防ぐため、2段階の手順に従わなければなりません。この詳細については「EEPROM制御レジスタ(EECR)」の記述を参照してください。

EEPROMが書かれるとき、CPUは次の命令が実行される前に2クロック周期停止されます。

EEPROMが読まれるとき、CPUは次の命令が実行される前に4クロック周期停止されます。

#### ■ EEPROM7トレスレジスタ (EEPROM Address Register) EEAR

| ピット         | 7 | 6     | 5     | 4     | 3     | 2     | 1     | 0     |      |

|-------------|---|-------|-------|-------|-------|-------|-------|-------|------|

| \$1E (\$3E) | _ | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEAR |

| Read/Write  | R | R/W   |      |

| 初期値         | 0 | 不定    |      |

#### ■ ビット7 - Res: 予約 (Reserved)

このビットは予約されており、常に0として読めます。

#### ■ ビット6~0 - EEAR6~0: EEPROMアドレス (EEPROM Address)

EEPROMアドレス レジスタ(EEAR)は128バイトEEPROM空間のEEPROMアドレスを指定します。EEPROMデータ バイトは0~127間で直線的に配されます。EEARの初期値は不定です。EEPROMがアクセスされるであろう前に適切な値が書かれなければなりません。

#### ■ EEPROMデータレジスタ (EEPROM Data Register) EEDR

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     | _    |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|------|

| \$1D (\$3D) | (MSB) |     |     |     |     |     |     | (LSB) | EEDR |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |      |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |      |

#### ■ ビット7~0 - EEDR7~0: EEPROMデータ (EEPROM Data)

EEPROM書き込み操作に対してEEDRはEEPROMアドレス レジスタ(EEAR)で与えたアドレスのEEPROMへ書かれるべきデータを含みます。 EEPROM読み込み操作に対してEEDRはEEARで与えたアドレスのEEPROMから読み出したデータを含みます。

#### ■ EEPROM制御レジスタ (EEPROM Control Register) EECR

| ピット         | 7 | 6 | 5 | 4 | 3     | 2     | 1    | 0    | _    |

|-------------|---|---|---|---|-------|-------|------|------|------|

| \$1C (\$3C) | _ | - | - | - | EERIE | EEMWE | EEWE | EERE | EECR |

| Read/Write  | R | R | R | R | R/W   | R/W   | R/W  | R/W  |      |

| 初期値         | 0 | 0 | 0 | 0 | 0     | 0     | 不定   | 0    |      |

#### ■ ビット7~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読めます。

#### ■ ビット3 - EERIE: EEPROM操作可割り込み許可 (EEPROM Ready Interrupt Enable)

EERIEの1書き込みはステータス レジ、スタ(SREG)の全割り込み許可(I)ヒットが設定(1)されているなら、EEPROM操作可割り込みを許可します。EERIEの0書き込みは、この割り込みを禁止します。EEPROM操作可割り込みはEEWEが解除(0)されていると継続する割り込みを発生します。

#### ■ ビット2 - EEMWE: EEPROM主書き込み許可(EEPROM Master Write Enable)

EEMWEL'ットはEEPROM書き込み許可(EEWE)ヒットの1設定がEEPROM書き込みの原因となるかどうかを決めます。EEMWEが設定 (1)されるとき、EEWEの1設定は選択されたアトレスのEEPROMにデータを書きます。EEMWEが0の場合、EEWEの1設定は無効です。 EEMWEがソフトウェアによって設定(1)されてしまうと、4クロック周期後にハートウェアがこのヒットを0に解除します。EEPROM書き込み手順については「書き込み許可(EEWE)ヒット」の記述をご覧ください。

#### ■ ビット1 - EEWE: EEPROM書き込み許可(EEPROM Write Enable)

このEEPROM書き込み許可信号(EEWE)はEEPROMへの書き込みストローブです。 アドレスとデータが適切に設定されると、 EEPROMへこ の値を書き込むために、このEEWEピットを設定(1)しなければなりません。論理1がEEWEに書かれるとき、EEPROM主書き込み許可 (EEMWE)ビットは設定(1)されなければならず、そうしないと、EEPROM書き込みは行われません。EEPROMを書く時は次の手順に従う べきです(手順2.と3.の順番は重要ではありません)。

- 1. EEPROM書き込み許可(EEWE)ビットがのになるまで待機します。

- 2. 今回のEEPROMアドレスをEEPROMアドレス レジスタ(EEAR)に書きます。(任意、省略可)

- 3. 今回のEEPROMデータをEEPROMデータレジ、スタ(EEDR)に書きます。(任意、省略可)

- 4. EEPROM制御レジスタ(EECR)のEEPROM主書き込み許可(EEMWE)ビットに論理1を書きます。(EEMWEビットに論理1が書けるため には、同一周期内でEEWEL ットは0が書かれなければなりません。)

- 5. EEMWE設定後4クロック周期内に、EEPROM書き込み許可(EEWE)ビットへ論理1を書きます。

警告: 手順4.と5.間の割り込みは、EEPROM主書き込み許可が時間超過となるため、書き込み周期失敗になります。EEPROMをアクセ スする割り込み処理ルーチンが他のEEPROMアクセスで割り込み、EEARまたはEEDRを変更すると、割り込まれたEEPROMアクセスが 失敗する原因になります。これらの問題を防ぐため、手順2.~5.の間中、ステータスレシ、スタ(SREG)の全割り込み許可(I)ビットは解 除(0)されていることが推奨されます。

書き込み時間(代表値8.3ms)が経過してしまうと、EEWEビットは自動的に解除(0)されます。次のバイトを書く前に、このビットをポーリングし て0まで待機できます。EEWEが設定(1)されてしまうと、次の命令が実行される前に、CPUは2周期停止されます。

#### ■ ビット0 - EERE: EEPROM読み込み許可(EEPROM Read Enable)

このEEPROM読み込み許可信号(EERE)はEEPROMへの読み込みストローブです。 EEARに適切なアドレスが設定されると、このEEREビッ トを設定(1)しなければなりません。EEREビットが自動的に解除(0)されると、求められたデータがEEDR内にあります。EEPROM読み込み アクセスは1命令で行われるので、EEREビットのポーリングは必要ありません。EEREが設定(1)されてしまうと、次の命令が実行される前に CPUは4周期停止されます。

読み込み操作を始める前に使用者はEEWEビットをポーリングすべきです。 新規データまたはアドレスがEEPROM I/Oレジスタに書かれるとき に書き込み動作が実行中の場合、書き込み動作は阻止され、結果が不定にされます。

EEPROMアクセスの時間に校正済み内蔵RC発振器が使われま 表1. EEPROM書き込み時間 す。表1.はCPUからのEEPROMアクセスに対する代表的な書き込 み時間を示します。(訳注:共通性のため本文章追加)

(訳注) 表1.内のtyp値(8.5ms)と文章内の代表値(8.3ms)が矛盾 しています。

| 項目              | 校正付き内蔵RC<br>発振器周期数 (注) | Тур   |

|-----------------|------------------------|-------|

| EEPROM書き込み(CPU) | 8448                   | 8.5ms |

注: CKSELヒューズ設定と無関係に1MHzが使われます。

# パワーダウン休止動作中のEEPROM書き込み

EEPROM書き込み動作が活動中にパワーダウン休止動作へ移行すると、EEPROM書き込み動作が継続し、EEPROM書き込み時間が 過ぎ去ってしまう前に完了します。しかし、書き込み動作が完了されると、発振器が動作を継続し、結果としてデバイスはパワーダウン動 作へ完全に移行しません。従ってパワーダウンへ移行する前に、EEPROM書き込み動作が完了される(EEWE=0)ことの確認が推奨され ます。(<mark>訳補</mark>: パワーダウン移行後もEPROM書き込みは正常に完了するが、その後発振器が止まらないことの注意)

#### EEPROMデータ化けの防止

電源電圧が低すぎる時のCPUやEEPROMの動作特性により、低VCCの期間中、EEPROMデータが化けてしまいます。これらは EEPROMを使った基板レベルの問題と同じで、同じ設計上の解決法が適用されるべきです。

EEPROMデータ化けが発生する低電源電圧は、2つの場合が想定できます。1つ目は、EEPROM書き込み動作に必要な最低電圧以 下の場合で、2つ目は、CPUが命令を実行するのに必要な最低電圧以下の場合です。

次の推奨設計(内の1つで充分)により、EEPROMのデータ化けは容易に避けることができます。

- ・不充分な供給電源電圧の期間中、AVRのRESETを活性(Low)に保ってください。これは動作電圧が検出電圧と一致するなら、内 蔵低電圧検出器(BOD)を許可することにより行えます。一致しない場合、外部低VCCリセット保護回路が適用できます。

- ・低VCCの時間中、AVRコアをパワーダウン休止動作に保ちます。これはCPUを命令の復号と実行を試みないように防ぎ、不測の書き 込みからEEPROMレジスタを保護する効果があります。

- ・ソフトウェアからメモリ内容を変更できることが必要とされない場合、フラッシュメモリに定数を格納します。フラッシュメモリはCPUにより更新さ れることができないので、データ化けの問題はありません。

#### I/Oメモリ (レシ、スタ)

ATtiny26/LのI/O領域定義は表2.で示されます。

#### 表2. ATtiny26/L I/Oレジスタ

| アト・レス       | レジスタ名  |                        | 機能                                            |

|-------------|--------|------------------------|-----------------------------------------------|

| \$3F (\$5F) | SREG   | ステータス レシ スタ            | Status Register                               |

| \$3D (\$5D) | SP     | スタック ホ゜インタ             | Stack Pointer Low                             |

| \$3B (\$5B) | GIMSK  | 一般割り込み許可レジスタ           | General Interrupt MaSK register               |

| \$3A (\$5A) | GIFR   | 一般割り込み要求フラク・レシブスタ      | General Interrupt Flag register               |

| \$39 (\$59) | TIMSK  | タイマ/カウンタ割り込み許可レジスタ     | Timer/Counter Interrupt MaSK register         |

| \$38 (\$58) | TIFR   | タイマ/カウンタ割り込み要求フラグ レジスタ | Timer/Counter Interrupt Flag register         |

| \$35 (\$55) | MCUCR  | MCU制御レシブスタ             | MCU Control Register                          |

| \$34 (\$54) | MCUSR  | MCU状態レシブスタ             | MCU Status Register                           |

| \$33 (\$53) | TCCR0  | タイマ/カウンタ0制御レシ、スタ       | Timer/Counter 0 Control Register              |

| \$32 (\$52) | TCNT0  | タイマ/カウンタ0 カウンタ         | Timer/CouNTer 0 (8bit)                        |

| \$31 (\$51) | OSCCAL | 発振校正レジスタ               | OSCillator CALibration Register               |

| \$30 (\$50) | TCCR1A | タイマ/カウンタ1制御レジスタA       | Timer/Counter 1 Control Register A            |

| \$2F (\$4F) | TCCR1B | タイマ/カウンタ1制御レジスタB       | Timer/Counter 1 Control Register B            |

| \$2E (\$4E) | TCNT1  | タイマ/カウンタ1 カウンタ         | Timer/CouNTer 1 (8bit)                        |

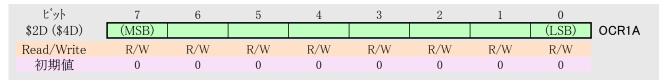

| \$2D (\$4D) | OCR1A  | タイマ/カウンタ1比較Aレシ、スタ      | Timer/Counter 1 Oouput Compare Register A     |

| \$2C (\$4C) | OCR1B  | タイマ/カウンタ1比較Bレシ、スタ      | Timer/Counter 1 Oouput Compare Register B     |

| \$2B (\$4B) | OCR1C  | タイマ/カウンタ1比較Cレジスタ       | Timer/Counter 1 Oouput Compare Register C     |

| \$29 (\$49) | PLLCSR | PLL制御/状態レジスタ           | PLL Control and Status Register               |

| \$21 (\$41) | WDTCR  | ウォッチト゛ック゛タイマ制御レシ゛スタ    | WatchDog Timer Control Register               |

| \$1E (\$3E) | EEAR   | EEPROMアトレス レシ スタ       | EEPROM Address Register                       |

| \$1D (\$3D) | EEDR   | EEPROMデータ レシ、スタ        | EEPROM Data Register                          |

| \$1C (\$3C) | EECR   | EEPROM制御レジスタ           | EEPROM Control Register                       |

| \$1B (\$3B) | PORTA  | ポートA出力データ レジスタ         | Data Register, Port A                         |

| \$1A (\$3A) | DDRA   | ポートA方向レジスタ             | Data Direction Register, Port A               |

| \$19 (\$39) | PINA   | ポートA入力データレジスタ          | Input Pins, Port A                            |

| \$18 (\$38) | PORTB  | ポートB出力データ レジスタ         | Data Register, Port B                         |

| \$17 (\$37) | DDRB   | ポートB方向レジスタ             | Data Direction Register, Port B               |

| \$16 (\$36) | PINB   | ポートB入力データ レジスタ         | Input Pins, Port B                            |

| \$0F (\$2F) | USIDR  | 多用途直列インターフェース データ レジスタ | Universal Serial Interface Data Register      |

| \$0E (\$2E) | USISR  | 多用途直列インターフェース 状態レジスタ   | Universal Serial Interface Status Register    |

| \$0D (\$2D) | USICR  | 多用途直列インターフェース 制御レジスタ   | Universal Serial Interface Control Register   |

| \$08 (\$28) | ACSR   | アナログ比較器制御/状態レジスタ       | Analog Comparator Control and Status Register |

| \$07 (\$27) | ADMUX  | A/D多重器選択レジブスタ          | ADC Multiplexer Select Register               |

| \$06 (\$26) | ADCSR  | A/D変換制御/状態レジスタ         | ADC Contro and Status Register                |

| \$05 (\$25) | ADCH   | A/D変換データ レジスタ上位バイト     | ADC Data Register High                        |

| \$04 (\$24) | ADCL   | A/D変換データ レジスタ下位バイト     | ADC Data Register Low                         |

注: 予約と未使用の位置は、この表で示されていません。()内のアドレスはデータ空間の一部としてアクセスする場合のアドレスです。

ATtiny26/Lの全てのI/Oと周辺部はI/O空間に配置されています。各I/O位置は、I/O空間と32個の汎用レジスタ間のデータ移動を行う IN命令とOUT命令によりアクセスされます。アドレス\$00~\$1F範囲内のI/Oレジスタは、SBIとCBI命令を使う直接ビットアクセスが可能です。これらのレジスタでは、SBISとSBIC命令の使用により、単一ビット値の検査ができます。より詳細な内容は命令要約を参照してください。将来のデバイスとの共通性を保つため、予約ビットに書く場合は0を書くべきです。予約済みI/Oアドレスは決して書かれるべきではありません。

# システム クロックとクロック選択

#### クロック系統とその配給

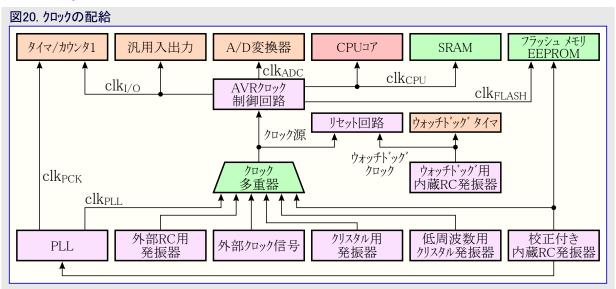

**図20**.はAVR内の主要なクロック系統とその配給を示します。全てのクロックが与えられた時間有効である必要はありません。消費電力低減のため、21頁の「**電力管理と休止形態**」で記述される各種休止形態使用により、使わない部分のクロックが停止できます。クロック系統は以下で詳述されます。

#### CPU クロック - clkcpu

CPUクロックはAVRコアの動作と関係する系統の部分に配給されます。このような部分の例は汎用レジスタ ファイル、ステータス レジスタ、スタック ポインタを保持するデータ メモリです。CPUクロックの停止はコアが一般的な操作や計算を実行することを禁止します。

#### I/O クロック - clk<sub>I/O</sub>

I/Oクロックはタイマ/カウンタ、USIのようなI/O部の大部分で使われます。I/Oクロックは外部割り込み部でも使われますが、いくつかの外部割り込みは例えI/Oクロックが停止されても検出されることをこのような割り込みに許す非同期論理回路により検出されることに注意してください。

# フラッシュ クロック - clk<sub>FLASH</sub>

フラッシュ クロックはフラッシュ メモリ インターフェースの動作を制御します。このフラッシュ クロックは常にCPUクロックと同時に活動します。

#### A/D変換クロック - clkadc

A/D変換器には専用のクロック範囲が提供されます。これはデジタル回路により生成される雑音を低減するためにCPUとI/Oクロックの停止を許します。これはより正確なA/D変換結果を与えます。

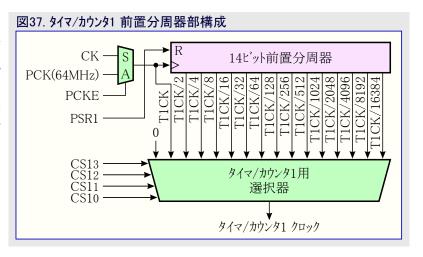

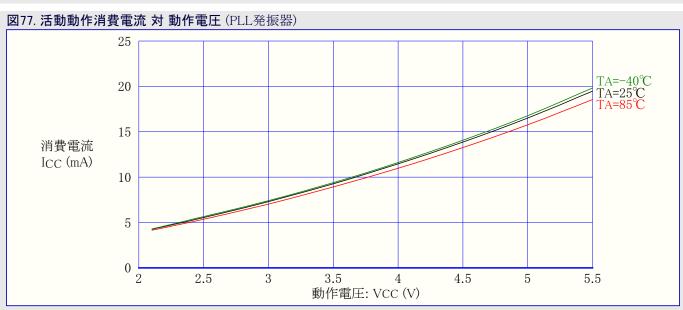

#### 高速周辺機能クロック - clkpck

ATtiny26/Lの内部PLLは公称1MHz入力から64倍したクロック周波数を発生します。この1MHz PLL入力は必要としたなら1MHzへ自動的に分周される内蔵RC発振器の出力です。図21.をご覧ください。PLL基準周波数が公称1MHzのとき、高速周辺機能クロックは64MHzです。高速周辺機能クロックまたはそれから分周したクロックはタイマ/カウンタ1に対するクロック元として選択できます。

PLLはこのRC発振器に固定化し、発振校正レジスタ(OSCCAL)経由のRC発振器調整は同時に高速周辺機能クロックも調整します。けれども分周したRC発振器が1MHzより高い周波数にされるのが可能でも、高速周辺機能クロックは(最悪の場合)70MHzで飽和し、最高周波数での発振に留まります。この場合のPLLがRC発振器クロックのどれにも固定化されないことに注意されるべきです。

従ってPLLの正しい動作範囲を保つため、1MHzよ高い周波数にOSCCAL補正をしないことが推奨されます。内部PLLはPLL制御/ 状態レジスタ(PLLCSR)のPLL許可(PLLE)ビットが設定(1)またはPLLCKヒューズがプログラム(0)される時だけ許可されます。PLLCSRのPLL 固定(PLOCK)ビットはPLLが固定化されている時に設定(1)されます。

内部1MHz RC発振器とPLLはパワーダウンとスタンバイの休止形態でOFFへ切り替えられます。

#### 図21. 高速周辺機能クロック(PCK)構成図

#### クロック元

このデバイスには右で示されるようにフラッシュ ヒューズ ビットにより選択可能な後続のクロック元選択があります。選択したクロック元からのクロックはAVRクロック発生器への入力で適切な単位部へ配給されます。表4.で示されるようにPB4(XTAL1)とPB5(XTAL2)ピンのI/Oピンとしての使用はクロック設定に依存して制限されます。

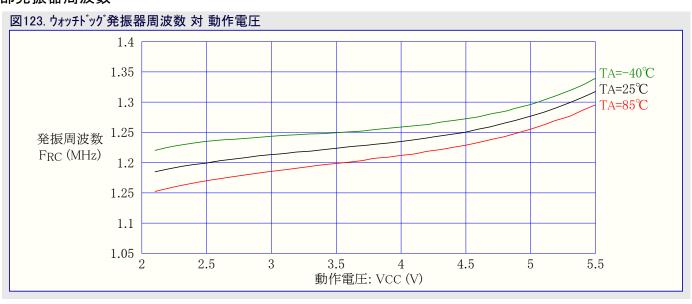

各クロック選択に対する様々な選択は次項で得られます。CP Uがハプータウンから起動するとき、選択したクロック元は命令実行開始前に安定な発振器動作を保証する起動時間に使われます。CPUがリセットから始まるとき、これらは通常動作開始前に安定電圧へ達するのを電源に許す付加遅延です。ウォッチトッグ発振器はこの起動時間の実時間部のタイシングに使われます。各計時完了に使われるウォッチトック(WD T)発振器の周期数は表5.で示されます。ウォッチトックが発振器の周波数は「代表特性」で示されるように電圧依存です。

表5. ウォッチト・ック・発振器の代表的計時完了値と周期数

| VCC=3.0V | VCC=5.0V | 周期数         |

|----------|----------|-------------|

| 4.3ms    | 4.1ms    | 4K (4096)   |

| 69ms     | 65ms     | 64K (65536) |

#### 既定のクロック元

このデバイスはCKSEL=0001, SUT=10, PLLCK非プログラム (1)で出荷されます。従って既定クロック元設定は最長起動時間の1MHz内蔵RC発振器です。この既定設定は全ての使用者が実装または並列書き込み器を使用して、それらを希望したクロック元設定にできることを保証します。

#### 表3. クロック種別選択

| クロック種別                | PLLCK | CKSEL3~0  |

|-----------------------|-------|-----------|

| 外部クリスタル発振子/セラミック振動子   | 1     | 1111~1010 |

| 外部低周波数クリスタル発振子        | 1     | 1001      |

| 外部RC発振                | 1     | 1000~0101 |

| 校正付き内蔵RC発振器           | 1     | 0100~0001 |

| 外部クロック信号              | 1     | 0000      |

| PLLクロック (PCK/4=16MHz) | 0     | 0001      |

注: 1=非プログラム、0=プログラム

#### 表4. クロック種別対PB4,PB5の機能

| クロック種別                | PLLCK | CKSEL3~0 | PB4   | PB5   |  |

|-----------------------|-------|----------|-------|-------|--|

| 外部クロック信号              | 1     | 0000     | XTAL1 | I/O   |  |

|                       |       | 0001     |       |       |  |

| 校正付き内蔵RC発振器           | 1     | 0010     | I/O   | I/O   |  |

| 1又正円で円成八し先1水台         | 1     | 0011     | 1/ 0  | 1/ () |  |

|                       |       | 0100     |       |       |  |

|                       |       | 0101     |       | I/O   |  |

| 外部RC発振                | 1     | 0110     | XTAL1 |       |  |

|                       |       | 0111     |       |       |  |

|                       |       | 1000     |       |       |  |

| 外部低周波数クリスタル発振子        | 1     | 1001     | XTAL1 | XTAL2 |  |

|                       |       | 1010     |       | XTAL2 |  |

|                       |       | 1011     |       |       |  |

| 外部クリスタル/セラミック発振子      | 1     | 1100     | VTAL1 |       |  |

| ノトロレノソハアル/ ヒノベソノデエル   | 1     | 1101     | ATALI |       |  |

|                       |       | 1110     |       |       |  |

|                       |       | 1111     |       |       |  |

| PLLクロック (PCK/4=16MHz) | 0     | 0001     | I/O   | I/O   |  |

注: 1=非プログラム、0=プログラム

# クリスタル用発振器

XTAL1とXTAL2は**図22**.で示されるように、チップ上の発振器としての使用に設定できる反転増幅器の各々、入力と出力です。クリスタル発振子またはセラミック振動子のどちらでも使えます。セラミック振動子の最高周波数は12MHzです。このクロック種別を使うとき、CKOPT ヒューズは常に非プログラム(1)にされるべきです。C1とC2は常に等しくすべきです。このコンデンサの最適値は使うクリスタル発振子やセラミック振動子、浮遊容量の量、その環境の電磁雑音に依存します。クリスタル発振子使用に対するコンデンサ選択について初期の指針のいくつかは表6.で与えられます。セラミック振動子については、製造業者により与えられたコンデンサ値が使われるべきです。

発振器は示された周波数範囲で最適化された3つの異なる動作ができます。この動作は表6.で示されたCKSEL3~1ヒューズにより選択されます。

# 図22. クリスタル発振子接続図 C2 XTAL2 XTAL1 GND

| 表6. クリスタル発振器動作 |             |          |  |  |  |

|----------------|-------------|----------|--|--|--|

| CKSEL3~1       | 周波数範囲       | 推奨C1,2容量 |  |  |  |

| 101 (注1)       | 0.4~0.9MHz  | -        |  |  |  |

| 110            | 0.9∼3.0MHz  | 12∼22pF  |  |  |  |

| 111            | 3.0~16.0MHz | 12∼22pF  |  |  |  |

| 111            | 16.0∼ MHz   | 12∼15pF  |  |  |  |

**注1**: この選択はクリスタル発振子ではなく、セラミック振動子でだけ使われるべきです。

CKSEL0ヒュースiはSUT1,0ヒュースiと共に、表7.で示される起動遅延時間を選択します。

#### 表7. クリスタル発振子/セラミック振動子用起動遅延時間選択表

| <u> </u> | (1.7)人が光派士/でスク派到丁州起到廷延时间送扒衣 |                      |                              |                             |  |  |

|----------|-----------------------------|----------------------|------------------------------|-----------------------------|--|--|

| CKSEL0   | SUT1,0                      | パワーダウンからの<br>起動遅延時間  | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法                       |  |  |

|          | 0 0                         | 258×CK ( <b>注1</b> ) | 4.1ms                        | 外部セラミック振動子、高速上昇電源           |  |  |

| 0        | 0 1                         | 258×CK ( <b>注1</b> ) | 65ms                         | 外部セラミック振動子、低速上昇電源           |  |  |

| U        | 1 0                         | 1K×CK ( <b>注2</b> )  | -                            | 外部セラミック振動子、低電圧検出リセット(BOD)許可 |  |  |

|          | 1 1                         | 1K×CK ( <b>注2</b> )  | 4.1ms                        | 外部セラミック振動子、高速上昇電源           |  |  |

|          | 0 0                         | 1K×CK ( <b>注2</b> )  | 65ms                         | 外部セラミック振動子、低速上昇電源           |  |  |

| 1        | 0 1                         | 16K×CK               | -                            | 外部クリスタル発振子、低電圧検出リセット(BOD)許可 |  |  |

| 1        | 1 0                         | 16K×CK               | 4.1ms                        | 外部クリスタル発振子、高速上昇電源           |  |  |

|          | 1 1                         | 16K×CK               | 65ms                         | 外部クリスタル発振子、低速上昇電源           |  |  |

**注1**: これらの選択はデバイスの最高周波数付近での動作でないとき、応用にとって起動での周波数安定性が重要でない場合だけ使われるべきです。これらの選択はクリスタル発振子用ではありません。

**注2**: これらの選択はセラミック振動子での使用を意図され、起動での周波数安定性を保証します。デバイスの最高周波数付近での動作でないとき、応用にとって起動での周波数安定性が重要でない場合はクリスタル発振子も使えます。

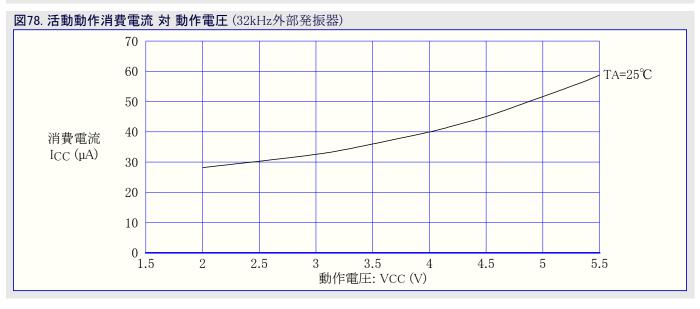

#### 低周波数クリスタル用発振器

デバイスに対するクロック元として時計用32.768kHzクリスタルを使うには、PLLCKヒューズ=1、CKSEL3~0ヒューズを'1001'に設定することにより低周波数クリスタル発振器が選択されなければなりません。クリスタルは図22.で示されるように接続されるべきです。CKOPTヒューズのプログラム(0)により、使用者はXTAL1とXTAL2の内部容量(コンデンサ)を許可でき、それにより外部コンデンサの必要がなくなります。内部容量は36pFの公称値です。

この発振器が選択されると、起動時間は表8.で示されるようにSUTヒューズにより決定されます。

#### 表8. 低周波数クリスタル発振器用起動遅延時間選択表

| SUT1,0 | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法                     |  |

|--------|---------------------|------------------------------|---------------------------|--|

| 0 0    | 1K×CK ( <b>注1</b> ) | 4.1ms                        | 高速上昇電源または低電圧検出リセット(BOD)許可 |  |

| 0 1    | 1K×CK ( <b>注1</b> ) | 65ms                         | 低速上昇電源                    |  |

| 1 0    | 32K×CK              | 65ms                         | 起動時周波数の安定重視               |  |

| 1 1    | (予約)                |                              |                           |  |

**注1**: これらの選択は応用にとって起動での周波数安定性が重要でない場合だけ使われるべきです。

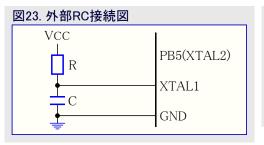

#### 外部RC発振器

タイミングに鈍感な応用に対しては**図23**.で示される外部RC設定が使えます。周波数は式f=1/(3RC)により大まかに推測されます。Cは最低22pFであるべきです。CKOPTヒュース、のプログラム(0)により、使用者はXTAL1とGND間の36pF内部容量を許可でき、それにより外部コンデンサの必要がなくなります。

この発振器は示された周波数範囲で各々最適化された4つの異なる種別で動作できます。この動作は表9.で示されるようにCKSEL3~0ヒュース、により選択されます。

この発振器が選択されると起動時間は表10.で示されるようにSUTヒュースにより決定されます。

| 表9. 外部RC発振器動作 |             |  |  |  |

|---------------|-------------|--|--|--|

| CKSEL3~0      | 周波数範囲 (MHz) |  |  |  |

| 0 1 0 1       | 0.1~0.9     |  |  |  |

| 0 1 1 0       | 0.9~3.0     |  |  |  |

| 0 1 1 1       | 3.0~8.0     |  |  |  |

| 1 0 0 0       | 8.0~12.0    |  |  |  |

|               |             |  |  |  |

表10. 外部RC発振器用起動遅延時間選択表

| SUT1,0 | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法                     |

|--------|---------------------|------------------------------|---------------------------|

| 0 0    | 18×CK               | -                            | 低電圧検出(BOD)リセット許可          |

| 0 1    | 18×CK               | 4.1ms                        | 高速上昇電源                    |

| 1 0    | 18×CK               | 65ms                         | 低速上昇電源                    |

| 1 1    | 6×CK ( <b>注1</b> )  | 4.1ms                        | 高速上昇電源または低電圧検出(BOD)リセット許可 |

**注1**: この選択はデバイスの最高周波数付近で動作するときに使われるべきではありません。

# 校正付き内蔵RC発振器

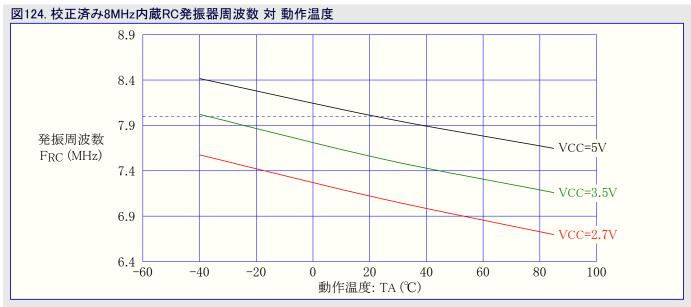

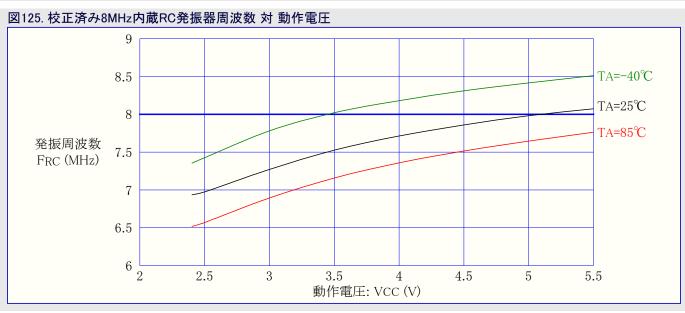

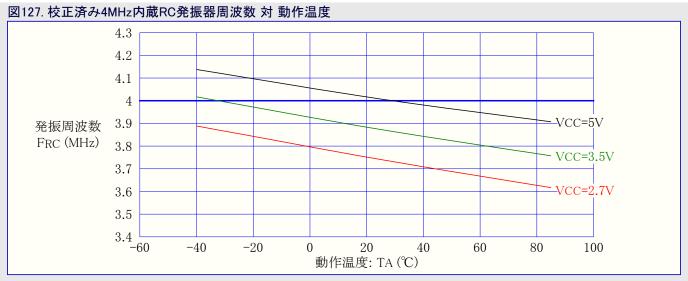

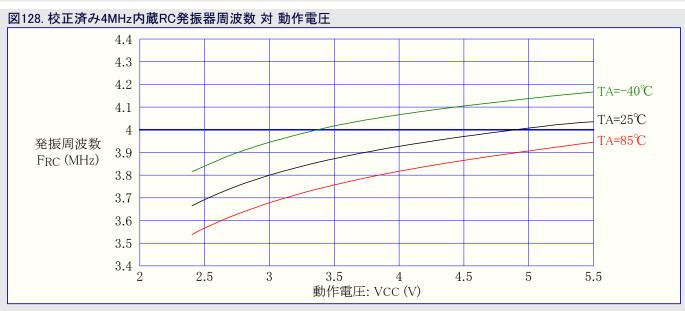

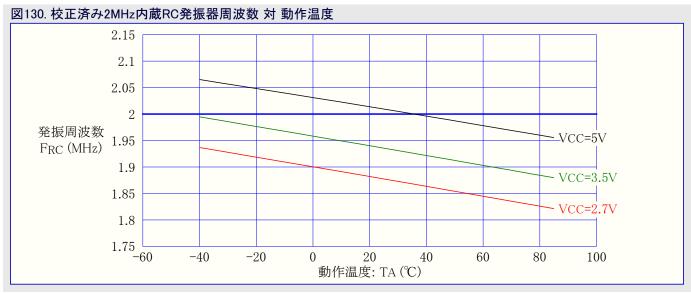

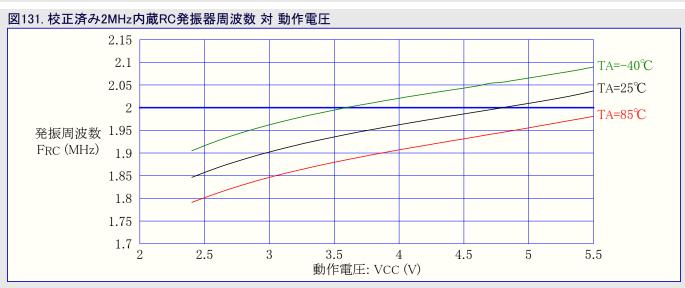

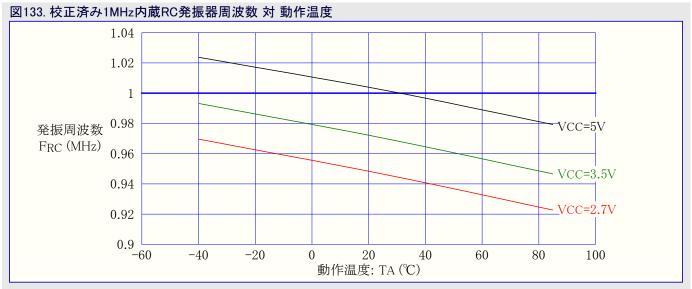

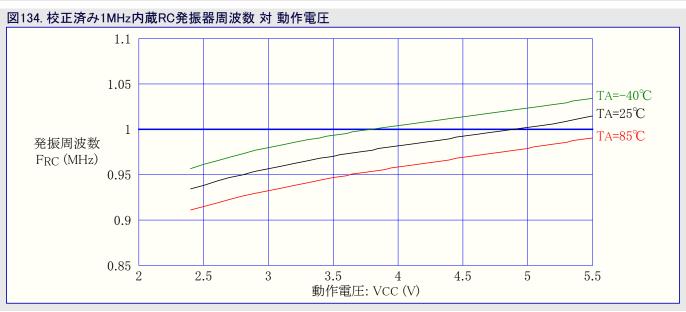

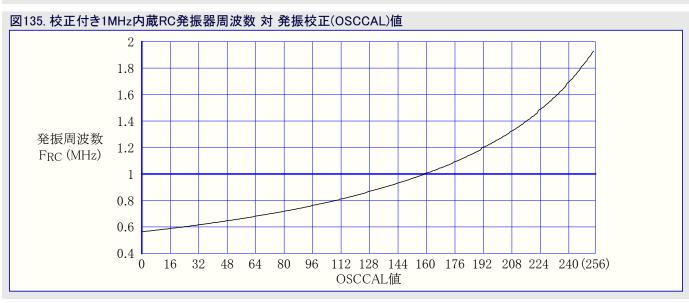

校正された内蔵RC発振器は決められた1.0, 2.0, 4.0, 8.0MHz/ロックを供給します。全ての周波数は5V,25℃での公称値です。このクロックは表11.で示されるようにCKSEL ヒュース・のプログラミングによりシステム クロックとして選択できます。選択したならば、外部部品なしで動作します。このクロック選択を使うとき、CKOPTヒュース・は常に非プログラム(1)にされるべきです。リセット中、ハート・ウェアが発振校正レジスタ(OSCCAL)に校正値バイトを設定し、これによりRC発振器を自動的に校正します。5V,25℃で1.0MHz発振器周波数が選択され、この校正は公称周波数±3%以内の周波数を与えます。atmel.com/avrで利用可能な応用記述に記載された実行時校正法の使用で、与えられたどのVCCと温度でも±1%の精度を達成することができます。この発振器がチップ(システム)クロックと

表11. 校正付き内蔵RC発振器動作

| CKSEL3~0 | 公称周波数 (MHz) |

|----------|-------------|

| 0001(注1) | 1.0         |

| 0 0 1 0  | 2.0         |

| 0 0 1 1  | 4.0         |

| 0 1 0 0  | 8.0         |

注1: デバイスはこの選択で出荷されます。

して使われるとき、ウォッチ ドッグ発振器は未だウォッチ ドッグ タイマとリセット付加遅延タイマに使われます。予め設定された校正値のより多くの情報については67頁の「校正バイト」項をご覧ください。

この発振器が選択されると、起動時間は**表12**.で示されるようにSUTヒュース により決定されます。PB4(XTAL1)とPB5(XTAL2)は標準I/O ポートとして使えます。

表12. 校正付き内蔵RC発振器用起動遅延時間選択表

| SUT1,0  | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法            |  |

|---------|---------------------|------------------------------|------------------|--|

| 0 0     | 6×CK                | -                            | 低電圧検出リセット(BOD)許可 |  |

| 0 1     | 6×CK                | 4.1ms                        | 高速上昇電源           |  |

| 10 (注1) | 6×CK                | 65ms                         | 低速上昇電源           |  |

| 1 1     | (予約)                |                              |                  |  |

注1: デバイスはこの選択で出荷されます。

# ■ 発振校正レジスタ (Oscillator Calibration Register) OSCCAL

| ピット         | 7    | 6    | 5    | 4      | 3     | 2    | 1    | 0    |        |

|-------------|------|------|------|--------|-------|------|------|------|--------|

| \$31 (\$51) | CAL7 | CAL6 | CAL5 | CAL4   | CAL3  | CAL2 | CAL1 | CAL0 | OSCCAL |

| Read/Write  | R/W  | R/W  | R/W  | R/W    | R/W   | R/W  | R/W  | R/W  |        |

| 初期値         |      |      |      | デバイス固ィ | 有の校正値 |      |      |      |        |

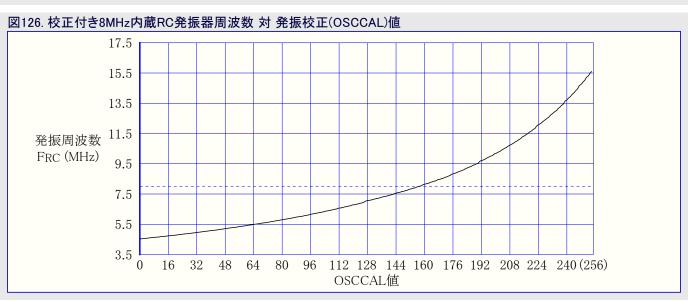

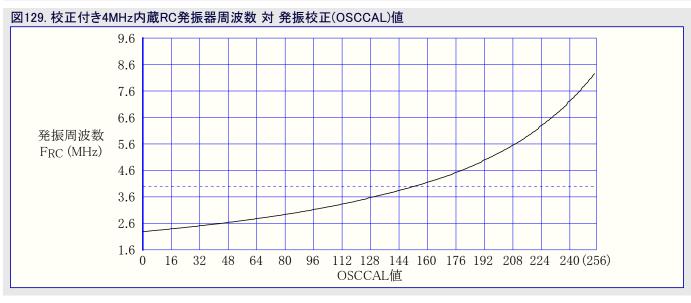

#### ■ ビット7~0 - CAL7~0:発振校正値 (Oscillator Calibration Value)

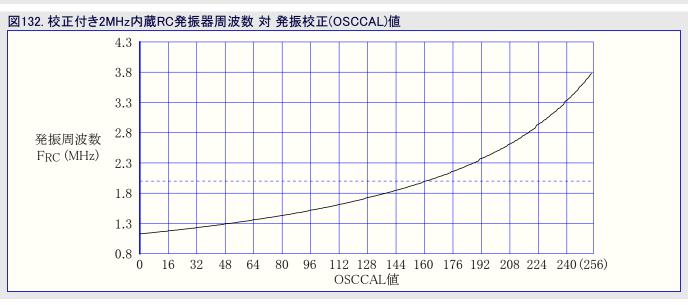

0の時に最低利用可能周波数が選択されます。このレジスタへの以外の値を書くことは内蔵発振器の周波数を増加します。このレジスタへの\$FF書き込みは最高使用可能周波数にします。校正付き発振器はフラッシュメモリとEEPROMのアクセス時間に使われます。フラッシュメモリまたはEEPROMが書かれる場合、公称周波数より上へ10%を越えて校正してはいけません。そうでなければ、フラッシュメモリまたはEEPROM書き込みは失敗するかもしれません。この発振器は1.0、2.0、4.0、8.0MHzへの校正が意図されることに注意してください。表13.で示されるような他の値への調整は保証されません。

| 表13. 内蔵RC発振器周波数範囲   |       |       |  |  |

|---------------------|-------|-------|--|--|

| OSCCAL値 公称周波数に対する割合 |       |       |  |  |

| USUCALill           | 最小    | 最大    |  |  |

| \$00                | 50 %  | 100 % |  |  |

| \$7F                | 75 %  | 150 % |  |  |

| \$FF                | 100 % | 200 % |  |  |

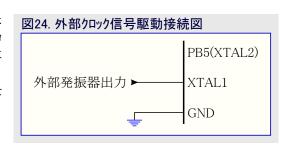

#### 外部クロック信号

外部クロック元からデバイスを駆動するためにXTAL1は**図24**.で示されるように駆動されるべきです。外部クロックでデバイスを走行するためにCKSELヒューズは'0000'にプログラム(設定)されなければなりません。CKOPTヒューズのプログラム(0)により、使用者はXTAL1とGND間の36pF内部容量を許可できます。

このクロック元が選択されると、起動時間は表14.で示されるようにSUTヒューズにより決定されます。

#### 表14. 外部クロック信号駆動用起動遅延時間選択表

| SUT1,0 | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法            |  |

|--------|---------------------|------------------------------|------------------|--|

| 0 0    | 6×CK                | -                            | 低電圧検出(BOD)リセット許可 |  |

| 0 1    | 6×CK                | 4.1ms                        | 高速上昇電源           |  |

| 1 0    | 6×CK                | 65ms                         | 低速上昇電源           |  |

| 1 1    | (予約)                |                              |                  |  |

外部クロックを供給するとき、MCUの安定な動作を保証するために供給したクロック周波数の急な変化を避けることが必要とされます。或るクロック周期から次への2%より大きな周波数変化は予測されない事態を引き起こします。このようなクロック周波数での変化中、MCUはリセットに保たれることを保証することが必要とされます。

#### 高速PLLクロック (PLLCLK)

周辺(機能)タイマ/カウンタ1の使用に対してとシステム クロック元に関し、(校正付き内蔵)RC発振器にロックした公称64MHzクロック速度を供給する内部PLLです。PLLCKヒュース、のプログラム(0)によりシステム クロック元として選択されると、4分周されます。このクロック種別が使われるとき、CKSEL3~0ヒュース、は、0001、に設定されなければなりません。このクロック種別は安全な動作を保証するため4.5~5.5V動作時だけ使えます。システム クロック周波数は16MHz(64MHz/4)です。このクロック種別を使うとき、起動遅延時間は表15.で示されるようにSUTヒュース、により決定されます。14頁の図21.「高速周辺機能クロック(PCK)構成図」もご覧ください。

#### 表15. 高速PLLクロック(PLLCK=0)用起動遅延時間選択表

| SUT1,0 | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法            |

|--------|---------------------|------------------------------|------------------|

| 0 0    | 1K×CK               | -                            | 低電圧検出リセット(BOD)許可 |

| 0 1    | 1K×CK               | 4.1ms                        | 高速上昇電源           |

| 1 0    | 1K×CK               | 65ms                         | 低速上昇電源           |

| 1 1    | 16K×CK              | -                            | 似. 压工升电源         |

# システム制御とリセット

ATtiny26/Lは4つのリセット元を提供します。

- ・電源ONリセット・・・・・・・・・・供給電圧が電源ONリセット閾値電圧(VPOT)以下のとき、MCUはリセットされます。

- ・ウォッチドック゛リセット・・・・・・・・・ウォッチト、ック゛が許可され、ウォッチト、ック゛タイマ時間が経過すると、MCUはリセットされます。

- ・低電圧検出(BOD)リセット・・・供給電圧(VCC)が低電圧リセット閾値電圧(VBOT)以下のとき、MCUはリセットされます。

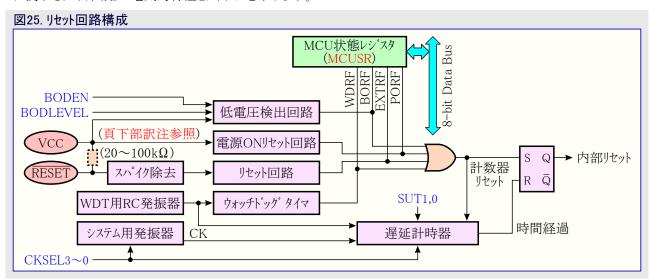

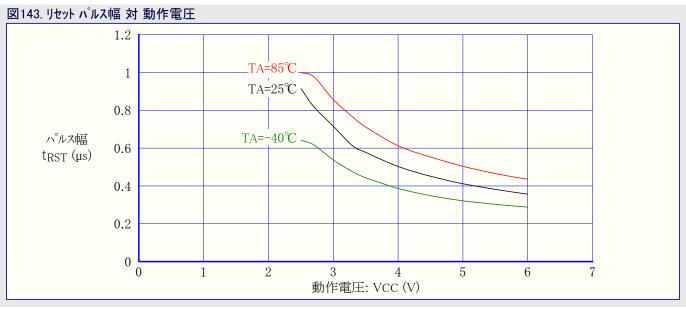

リセット中、全てのI/Oレシ、スタはそれらの初期値に設定され、その後にアトレス\$0000からプログラム実行が始まります。アトレス\$0000に配置される命令は、きっとリセット処理ルーチンへの無条件相対分岐(RJMP)命令でしょう。プログラムで決して割り込みを許可しないならば、割り込みへ、クタが使われず、これらの位置に通常のプログラムを配置できます。図25.はATtiny26/Lに関するリセット論理を示します。表16.はATtiny26/Lに関するリセット回路の電気的特性とタイミングを示します。

#### 表16. リセット電気的特性

| シンホ゛ル              | 項                   | 目                  | 最小     | 代表  | 最大     | 単位  |

|--------------------|---------------------|--------------------|--------|-----|--------|-----|

| V <sub>POT</sub>   | 上昇時電源ONJセット閾値電      | 圧                  |        | 1.4 | 2.3    |     |

| VPOT               | 下降時電源ONリセット閾値電圧(注1) |                    |        | 1.3 | 2.3    | V   |

| V <sub>RST</sub>   | RESETt°ン閾値電圧        |                    | 0.2VCC |     | 0.9VCC |     |

| $t_{RST}$          | リセット ハ°ルス幅          |                    | 1.5    |     |        | μs  |

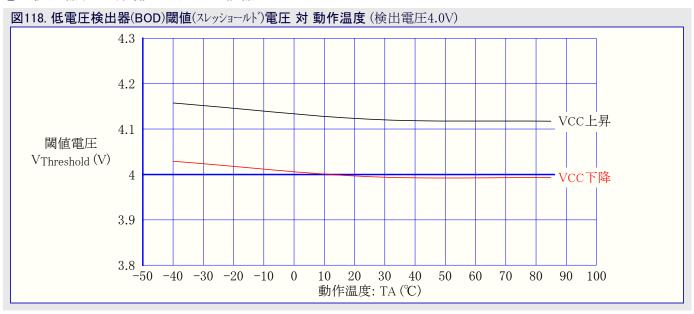

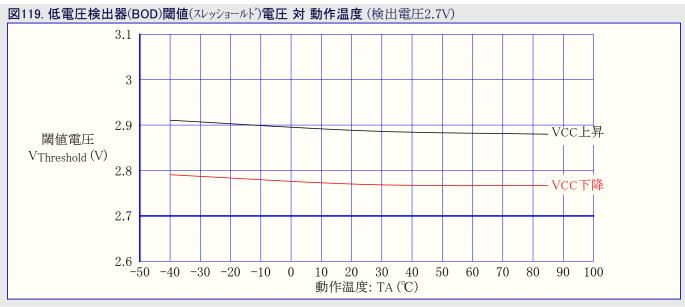

| $V_{\mathrm{BOT}}$ | 低電圧検出 (注2)          | BODLEVEL=非プログラム(1) | 2.4    | 2.7 | 2.9    | V   |

| VBOT               | スレッショールド電圧          | BODLEVEL=プログラム(0)  | 3.7    | 4.0 | 4.5    | V   |

| tnom               | 最小低電圧検出時間           | BODLEVEL=非プログラム(1) |        | 2   |        | 110 |

| t <sub>BOT</sub>   | 取小心电压快山时间           | BODLEVEL=プログラム(0)  |        | 2   |        | μs  |

| V <sub>HYST</sub>  | 低電圧検出ヒステリシス電圧       |                    |        | 130 |        | mV  |

注1: 供給電圧がこの電圧以下にならないと、上昇時の電源ONJセットは動作しません。

注2: VBOTはいくつかのデバイスについて公称最小動作電圧以下かもしれません。この状態のデバイスについて、そのデバイスは製造検査中にVCC=VBOTへ落として検査されます。これはVCCがマイクロコントローラの正しい動作がもはや保証されない電圧へ落ちる前に低電圧(BOD)リセットが起きることを保証します。この検査はATtiny26LについてはBODLEVEL=1、ATtiny26についてはBODLEVEL=1、ATtiny26についてはBODLEVEL=1、ATtiny26についてはBODLEVEL=1を使って実行されます。ATtiny26に対してBODLEVEL=1は適用できません。

13頁の「システム クロックとクロック選択」からリセットからの起動時間をご覧ください。 CPUがパワーダウン動作から起動するとき、起動時間のクロック計数(CK)部だけが使われます。 ウォッチトッグ発振器は起動時間の実時間部のタイミングに使われます。

(<mark>訳注</mark>) 図25.でRESETピンのプルアップは原書の同図には存在しませんが、原書の「電気的特性」にその値が記載されています。これは常時有り、またはRSTDISBLヒュースで有無切り替えの2つが予測されます。

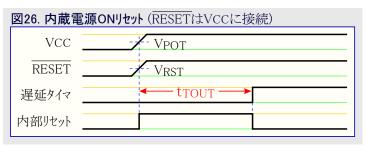

#### 電源ONリセット

電源ONJセット(POR)パルスはチップ上の検出回路によって生成されます。検出電圧は表16.で定義されます。POR信号はVCCが検出電圧以下の時は必ず活性(有効)にされます。POR回路は供給電圧異常検出は勿論、始動リセットの起動にも使えます。

ハ<sup>°</sup>ワーONリセット回路はデハ<sup>°</sup>イスが電源投入でリセットされることを保証します。電源ONリセット閾値電圧(VPOT)への到達はVCC上昇後にデハ<sup>°</sup>イスがどのくらいリセットを保つかを決める遅延カウンタ(タイマ)を起動します。遅延カウンタの計時完了時間はCKSELヒュース<sup>°</sup>を通して使用者によって定義できます。遅延時間についての各種選択は13頁の「システム クロックとクロック選択」で示されます。VCCがこの検出電圧以下に低下すると、リセット信号はどんな遅延もなく再び有効にされます。

#### 外部リセット

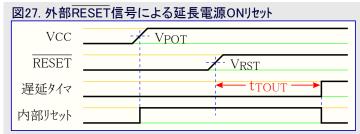

外部リセットはRESETt°ンのLowレヘルによって生成されます。例えクロックが動いていなくても、最小ハペルス幅(表16.参照)以上のリセットハペルスはリセットを生成します。短すぎるハペルスはリセットの生成が保証されません。印加された信号の上昇がリセット閾値電圧(VRST)に達すると(遅延タイマが起動され)、遅延タイマは遅延時間(t<sub>TOUT</sub>)経過後にMCUを始動します。

#### 低電圧(ブラウンアウト)検出

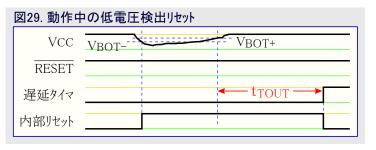

ATtiny26/Lには固定化された起動(検出)電圧と比較することによって動作中のVCCを監視するチップ。上の低電圧検出(BOD)回路があります。BOD回路はBODENtューズによって許可/禁止ができます。BODが許可(BODEN=プログラム(0))され、VCCが起動電圧以下の値に下降すると(図29.のVBOT-)、低電圧リセットが直ちに有効とされます。VCCが起動電圧以上に上昇すると(図29.のVBOT+)、低電圧リセットは遅延後に非活性(無効)にされます。この遅延はPOR信号の遅延と同じ方法で使用者によって定義されます。BODの起動電圧はBODLEVELtューズによって2.7V(非プログラム(1))ま

たは4.0V(プログラム(0))を選択できます。起動電圧はスパイク対策BODを保証するために130mVのヒステリシスを持ちます。検出電圧のヒステ リシスはVBOT+=VBOT+VHYST/2、VBOT-=VBOT-VHYST/2と解釈すべきです。(<mark>訳注</mark>:共通性のため本行追加)

BOD回路は電圧が表16.で与えられるtBOD時間より長く起動電圧以下に留まる場合のみ、VCCでの低下を検出します。

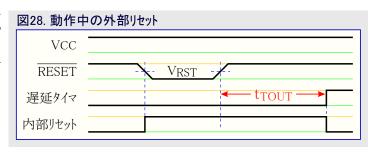

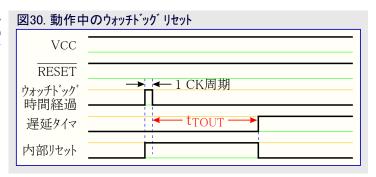

# ウォッチト゛ック゛リセット

ウォッチト、ック・時間経過時、(内部的に)1CK周期幅の短いリセット パルスを生成します。このパルスの下降端で遅延タイマは遅延時間(t<sub>TOUT</sub>)の計時を始めます。ウォッチト、ック・タイマ操作の詳細については48頁を参照してください。

# ■ MCU状態レジスタ (MCU Status Register) MCUSR

MCU状態レシブスタはどのリセット元がMCUリセットを起こしたかの情報を提供します。

| ピット         | 7 | 6 | 5 | 4 | 3    | 2    | 1     | 0    |       |

|-------------|---|---|---|---|------|------|-------|------|-------|

| \$34 (\$54) | - | - | - | - | WDRF | BORF | EXTRF | PORF | MCUSR |

| Read/Write  | R | R | R | R | R/W  | R/W  | R/W   | R/W  |       |

| 初期値         | 0 | 0 | 0 | 0 | 内容参照 | 内容参照 | 内容参照  | 内容参照 |       |

#### ■ ビット7~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

#### ■ ビット3 - WDRF: ウォッチドック゛リセット フラク゛(Watchdog Reset Flag)

このビットはウォッチドッグ リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

#### ■ ビット2 - BORF: 低電圧リセット フラク (Brown-Out Reset Flag)

このビットは低電圧リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

#### ■ ビット1 - EXTRF: 外部リセット フラク (External Reset Flag)

このビットは外部リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

#### ■ ビット0 - PORF: 電源ONリセット フラク (Power-on Reset Flag)

このビットは電源ONリセットが起こると設定(1)されます。このビットはこのフラグへの論理0書き込みによってのみリセット(0)されます。

リセット条件の確認にリセット フラグを使うには、使用者はプログラム内で可能な限り早くMCUSRを読み、そして解除(0)すべきです。別のリセットが起こる前にこのレジスタが解除(0)されると、リセット元はリセット フラグを調べることにより得られます。

# 電力管理と休止形態

休止形態は応用でMCU内の未使用部を一時停止することを可能にし、これによって節電します。AVRは応用で必要な消費電力に 仕立てることを使用者に許す様々な休止形態を提供します。

4つの休止形態の何れかに移行するにはMCU制御レシ、スタ(MCUCR)の休止許可(SE)ヒットが論理1を書かれ、SLEEP命令が実行されなければなりません。MCUCRの休止種別選択(SM1,0)ヒットはSLEEP命令によって活性(有効)にされる休止形態(アイト・ル、A/D変換雑音低減、パワータ・ウン、スタンハ・イ)のどれかを選びます。一覧については表17.をご覧ください。MCUが休止形態中に許可した割り込みが起こるとMCUは起動します。その時にMCUは起動時間に加えて4周期停止され、割り込みルーチンを実行し、そしてSLEEP命令の次の命令から実行を再開します。ディバイスが休止から起動するとき、レジスタファイルとSRAMの内容は変えられません。休止形態中にリセットが起こると、MCUは起動し、リセット ベクタから実行します。

22頁の表19.はATtiny26/Lの各種クロック系統とその配給を示します。この図は適切な休止形態を選択する助けになります。

#### ■ MCU制御レジスタ (MCU Control Register) MCUCR

MCU制御レシブスタは一般的なMCU機能に関する制御ビットを含みます。

| ピット         | 7 | 6   | 5   | 4   | 3   | 2 | 1     | 0     | _     |

|-------------|---|-----|-----|-----|-----|---|-------|-------|-------|

| \$35 (\$55) | - | PUD | SE  | SM1 | SM0 | - | ISC01 | ISC00 | MCUCR |

| Read/Write  | R | R/W | R/W | R/W | R/W | R | R/W   | R/W   |       |

| 初期値         | 0 | 0   | 0   | 0   | 0   | 0 | 0     | 0     |       |

■ ビット7 - Res: 予約 (Reserved)

このビットは予約されており、常に0として読めます。

#### ■ ビット6 - PUD: プルアップ 禁止 (Pull-up Disable)

このビットが設定(1)されると、例えDDxnとPORTxnレジスタがプルアップを許可することに設定(DDxn=0, PORTxn=1)されても、I/Oポートの(全)プルアップは禁止されます。この機能についてより多くの詳細に関しては25頁の「ピンの設定」をご覧ください。

#### ■ ビット5 - SE: 休止許可 (Sleep Enable)

SLEEP命令が実行される時にMCUを休止形態へ移行させるため、休止許可(SE)ビットは設定(1)されなければなりません。プログラムの書き手の目的外でMCUが休止形態へ移行するのを避けるため、SLEEP命令の実行直前に休止許可(SE)ビットを設定(1)することが推奨されます。

#### ■ ビット4,3 - SM1,0: 休止種別 (Sleep Mode Bits 1,0)

これらのビットは右表で示されるように4つの利用可能な休止形態の 1つを選択します。

| 表17. 休止形態種別選択 |             |  |  |  |  |  |

|---------------|-------------|--|--|--|--|--|

| SM0           | 休止形態種別      |  |  |  |  |  |

| 0             | ア仆ル動作       |  |  |  |  |  |

| 1             | A/D変換雜音低減動作 |  |  |  |  |  |

| 0             | パワーダウン動作    |  |  |  |  |  |

| 1             | スタンハーイ動作    |  |  |  |  |  |

|               |             |  |  |  |  |  |

詳細については以降の各休止動作を参照してください。

# ■ ビット2 - Res: 予約 (Reserved)

このビットは予約されており、常に0として読めます。

#### ■ ビット1,0 - ISC01,0:外部割り込み0条件制御 (Interrupt Sense Control 0 bit1 and 0)

外部割り込み0はステータスレジ、スタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レジ、スタ(GIMSK)の外部割り込み0許可(INTO)ビットが設定(1)なら、INTO外部ピンによって活性(有効)にされます。割り込みを活性(有効)にするINTO外部ピンの動きは右表で定義されます。

#### 表18. 外部割り込み0(INT0)割り込み条件

| ISC01 | ISC00 | 割り込み発生条件          |

|-------|-------|-------------------|

| 0     | 0     | INT0ピンがLowレベルで発生。 |

| 0     | 1     | INTOピンのレベル変化で発生。  |

| 1     | 0     | INTOピンの下降端で発生。    |

| 1     | 1     | INTOピンの上昇端で発生。    |

注: ISC01,00ビットの変更時、INT0はGIMSKで割り込み許可 ビットの解除(0)によって禁止されなければなりません。さも なければこれらのビット変更時に割り込みが起き得ます。

#### アイドル動作

休止種別選択(SM1,0)ビットが'00'を書かれるとき、SLEEP命令はMCUをアイドル動作へ移行させ、CPUを停止しますが、アナロケ比較器、A/D変換器、多用途直列インターフェース(USI)、タイマ/カウンタ、ウォッチドッグ、割り込み機構の継続動作を許します。この休止形態は基本的にclkCPUとclkFLASHを停止する一方、他のクロックに走行を許します。

アイドル動作はMCUにタイマ溢れやUSIの開始条件検出や溢れなどの内部割り込みだけでなく、外部で起動された割り込みからの起動も可能にします。アナログ比較器割り込みからの起動が必要とされないなら、アナログ比較器制御/状態レジスタ(ACSR)のアナログ比較器禁止(ACD)ビットを設定(1)することによってアナログ比較器を電源断にできます。これはアイドル動作での消費電力を削減します。A/D変換が許可されるなら、この動作に移行すると変換が自動的に始まります。

# A/D変換雜音低減動作

SM1,0ビットが'01'を書かれるとき、SLEEP命令はMCUをA/D変換雑音低減動作へ移行させ、CPUを停止しますが、A/D変換器、外部割り込み、USIの開始条件検出、ウォッチドック、の(許可されていれば)継続動作を許します。この休止形態は基本的にclk<sub>I/O</sub>, clk<sub>CPU</sub>, clk<sub>FLASH</sub>を停止する一方、他のクロックに走行を許します。

これはA/D変換に対する雑音環境を改善し、より高い分解能の測定を可能にします。A/D変換器が許可されている場合、この動作に移行すると、変換が自動的に始まります。A/D変換完了割り込みからの他、外部リセット、ウォッチトック・リセット、低電圧検出(BOD)リセット、USI開始条件検出割り込み、EEPROM操作可割り込み、INTOの外部レベル割り込み、ピン変化割り込みだけがA/D変換雑音低減動作からMCUを起動できます。

### パワーダウン動作

SM1,0ビットが、10'を書かれると、SLEEP命令はMCUをパワーダウン動作へ移行させます。この動作で外部発振器が停止される一方、外部割り込み、USI開始条件検出、ウォッチドッグ機能は(許可されていれば)継続して動作します。外部リセット、ウォッチドッグリセット、低電圧検出(BOD)リセット、USI開始条件検出割り込み、INTOの外部レベル割り込み、ピン変化割り込みだけがMCUを起動できます。この休止形態は基本的に生成した全てのクロックを停止し、非同期部の動作だけを許します。

パワーダウン動作から起動するとき、起動条件が起きてから起動の効果が現れるまで遅延があります。これは停止されてしまっている後の再始動と安定になることをクロックに許します。この起動(遅延)時間は14頁の「クロック元」で記述されるように、リセット遅延時間を定義するのと同じCKSELヒュース、によって定義されます。

パワーダウン動作からの復帰にレベルで起動された割り込みが使われる場合、MCUを起動するため、変更されたレベルは一定時間保持されなければならないことに注意してください。これはMCUの雑音不安定性を減らします。

MCUが起動して実行を始める前に起動復帰条件が消滅すると、例えばINT0のLowレベルが充分長く保持されないと、起動復帰の原因となる割り込みは実行されません。

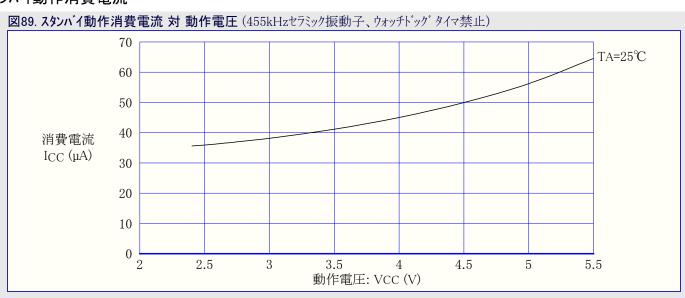

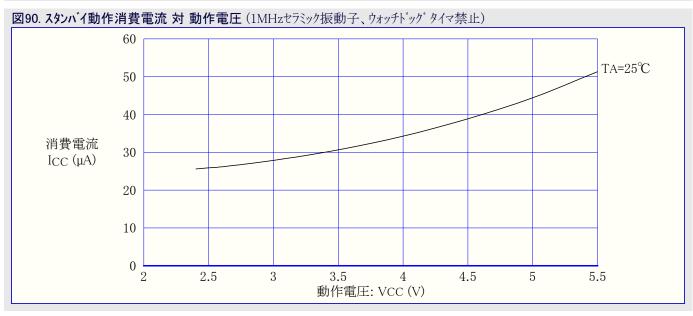

#### スタンバイ動作

外部クリスタル発振子/セラミック振動子クロック種別が選択され、且つSM1,0ビットが'11'のとき、SLEEP命令はMCUをスタンバイ動作へ移行させます。この動作は(外部クリスタル用)発振器が走行(動作)を保たれる例外を除いてパワーダウン動作と同じです。デバイスはスタンバイ動作から6クロック周期で起動します。

| 耒10     | 各休止形態に於け              | ス動作カロッカ箭田       | シャではいる |

|---------|-----------------------|-----------------|--------|

| বছ । স. | <b>イイルトロ ルク思してルこし</b> | る) 半川1 Fフロフフ里川井 |        |

|            | 動作クロック範囲   |              |           | 動作発振器 復帰起動要因(害 |              |              | 助要因 (割り       | (割り込み)        |             |            |

|------------|------------|--------------|-----------|----------------|--------------|--------------|---------------|---------------|-------------|------------|

| 休止種別<br>   | clk<br>CPU | clk<br>FLASH | clk<br>10 | clk<br>ADC     | 主クロック<br>供給元 | INT0<br>ピン変化 | USI開始<br>条件検出 | EEPROM<br>操作可 | A/D変換<br>完了 | その他<br>I/O |

| アイドル       |            |              | 0         | 0              | 0            | 0            | 0             | 0             | 0           | 0          |

| A/D変換雑音低減  |            |              |           | 0              | 0            | ○ (注2)       | 0             | 0             | 0           |            |

| ハ゜ワータ゛ウン   |            |              |           |                |              | ○ (注2)       | 0             |               |             |            |

| スタンバイ (注1) |            |              |           |                | 0            | ○ (注2)       | 0             |               |             |            |

注1: クロック元として外部クリスタル発振子またはセラミック振動子が選択された場合にだけ推奨されます。

注2: INTOはレベル割り込みだけです。

#### 消費電力の最小化

これらはAVRが制御するシステムで消費電力の最小化を試みるときに考慮するためのそれぞれの検討点です。一般的に休止形態は可能な限り多く使われるべきで、休止種別は動作するデバイスの機能が可能な限り少なくなるために選択されるべきです。必要とされない全ての機能は禁止されるべきです。特に次の機能部は最低可能消費電力の達成を試みるとき、特別な考慮を必要とするでしょう。

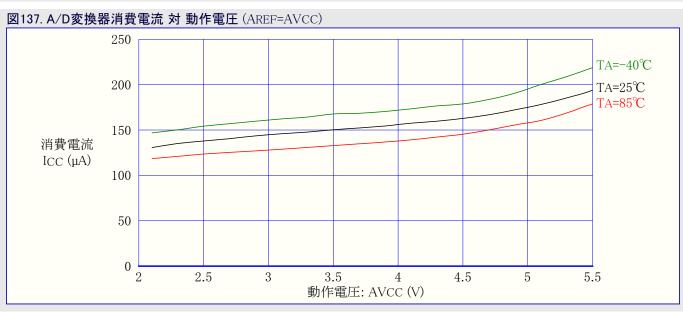

#### A/D変換器 (ADC)

許可したなら、A/D変換器は全休止形態で許可されます。節電のため休止形態の何れかへ移行する前に、A/D変換器は禁止されるべきです。A/D変換器がOFFそして再びONに切り替えられると、次の(最初の)変換は延長された(初回)変換になります。A/D変換器操作の詳細については59頁の「A/D変換器」を参照してください。

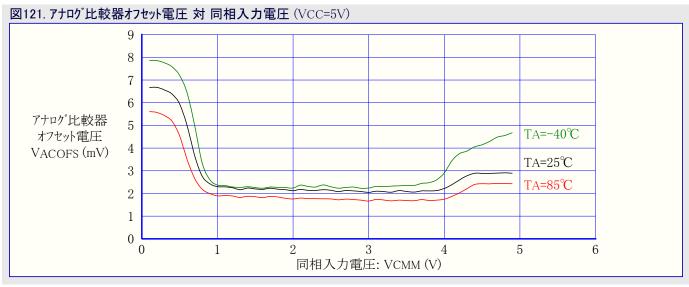

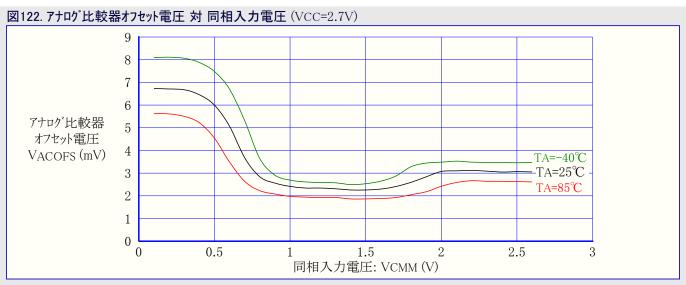

#### アナログ比較器

アイドル動作へ移行するとき、アナロゲ比較器は使われないならば禁止されるべきです。A/D変換雑音削減動作へ移行するとき、アナロゲ比較器は禁止されるべきです。その他の休止形態でのアナロゲ比較器は自動的に禁止されます。しかしアナロゲ比較器が入力として内部基準電圧を使う設定の場合、全休止形態でアナロゲ比較器は禁止されるべきです。さもなければ内部基準電圧は休止形態と無関係に許可されます。アナロゲ比較器設定法の詳細については57頁の「アナロゲ比較器」を参照してください。

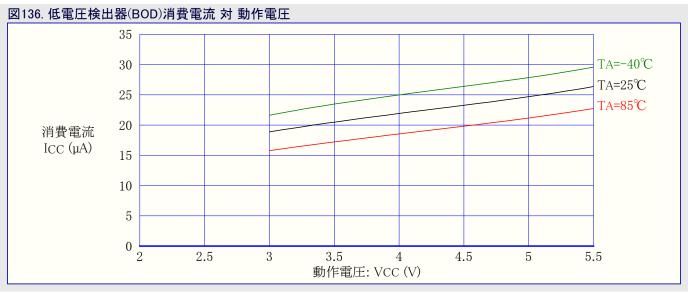

#### 低電圧検出器 (BOD)

低電圧検出器(BOD)が応用で必要とされないなら、この単位部はOFFにされるべきです。低電圧検出器がBODENヒューズにより許可されていると全休止形態で許可され、故に常時電力を消費します。これはより深い休止形態での総消費電流にとって重要な一因になります。低電圧検出器(BOD)設定法の詳細については19頁の「低電圧検出(BOD)」を参照してください。

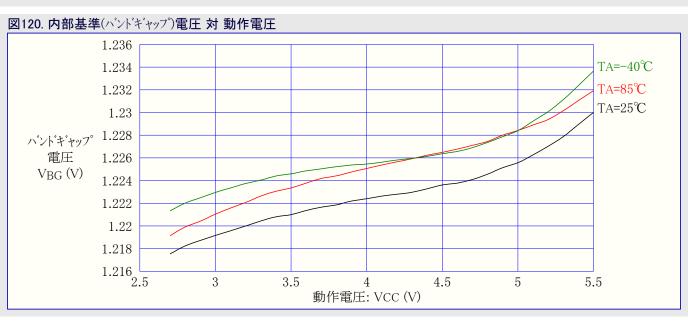

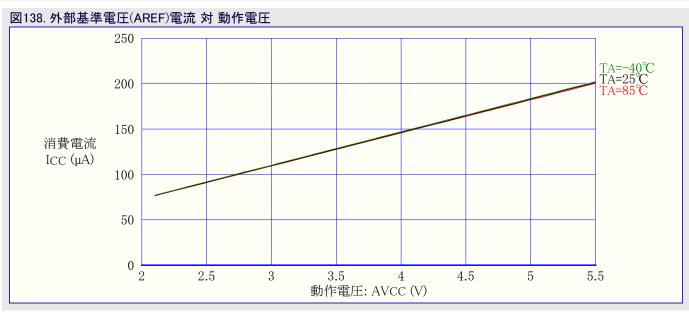

#### 内部基準雷圧

内部基準電圧(表20.参照)は低電圧検出器(BOD)、アナログ比較器、A/D変換器により必要とされる時に許可されます。これら単位部が上の項目で記述されたように禁止されると、内部基準電圧は禁止され、電力を消費しません。再び許可する場合、この出力が使われる前に、使用者は基準電圧へ起動(安定時間)を与えなければなりません。基準電圧が休止形態でON保持される場合、この出力は直ちに使えます。

| 表20. 内部基準電圧特性     |      |      |      |      |    |  |

|-------------------|------|------|------|------|----|--|

| シンボル              | 項目   | 最小   | 代表   | 最大   | 単位 |  |

| $V_{\mathrm{BG}}$ | 基準電圧 | 1.15 | 1.18 | 1.40 | V  |  |

| $t_{\mathrm{BG}}$ | 起動時間 |      | 40   | 70   | μs |  |

| $I_{BG}$          | 消費電流 |      | 10   |      | μA |  |

#### ウォッチト゛ック゛タイマ

ウォッチト、ック、タイマが応用で必要とされないならば、この単位部はOFFにされるべきです。ウォッチト、ック、タイマが許可されていると全休止形態で許可され、故に常時電力を消費します。これはより深い休止形態での総消費電流にとって重要な一因になります。ウォッチト、ック、タイマ設定法の詳細については48頁の「ウォッチト、ック、タイマ」を参照してください。

#### ホ<sup>°</sup>ート ヒ<sup>°</sup>ン

休止形態へ移行するとき、全てのポートピンは最小電力使用に設定されるべきです。最も重要なことはその時にピンが抵抗性負荷を駆動しないことを保証することです。I/Oクロック(clk<sub>I</sub>/O)とA/D変換クロック(clk<sub>ADC</sub>)の両方が停止される休止形態ではデバイスの入力緩衝部が禁止されます。これは必要とされない時に入力論理回路により電力が消費されないことを保証します。いくつかの場合で入力論理回路は起動条件を検出するために必要とされ、その時は許可されます。どのピンが許可されるかの詳細については26頁の「デジタル入力許可と休止形態」を参照してください。入力緩衝部が許可され、入力信号が浮いている状態のままか、またはアナログ信号電圧がVCC/2付近の場合、入力緩衝部は過大な電力を使うでしょう。

# 入出力ポート

#### 序説

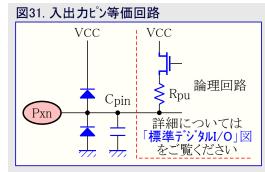

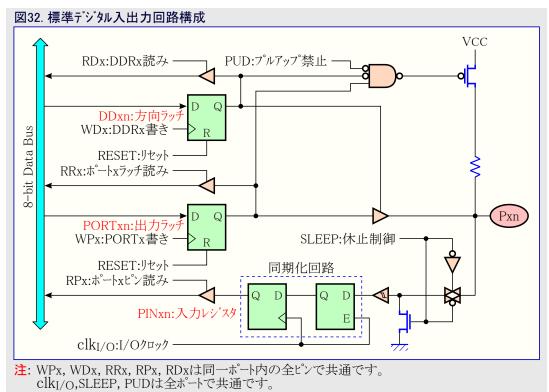

全てのAVRのポートは標準デジタルI/Oポートとして使われる時に真の読み-変更-書き(リート、モディファイライト)を機能的に持ちます。これはSBIとCBI命令で他のどのピッの方向をも無意識に変更することなく、1つのポートピッの方向を変更できることを意味します。(出力として設定されていれば)駆動値を変更、または(入力として設定されていれば)が動値を変更、または(入力として設定されていれば)がルアップ抵抗を許可/禁止するときにも同じく適用されます。各出力緩衝部は高い吐き出し(ソース)と吸い込み(シンケ)能力の両方で対称的な駆動特性を持ちます。このピッレ駆動部はLED(表示器)を直接駆動するのに充分な強さです。全てのポートピッは個別に選択可能な、供給電圧で抵抗値が変化しないプルアップ抵抗を持っています。全てのI/Oピッは図31.で示されるようにVCCとGNDの両方に保護ダイオート、を持っています。

本項内の全てのレジスタとビットの参照は一般形で記されます。小文字の'x'はポート番

号文字、小文字の'n'はビット番号を表します。けれどもプログラム内でレジスタやビット定義に使うとき、正確な形式(例えば、ここで一般に記されたPORTxnがポートBのビット3に対してはPORTB3)が使われなければなりません。物理的なI/Oレジスタとビット位置は33頁の「I/O ポート用レジスタ」で一覧されます。

各々1つの出力レシ、スタ(PORTx)、方向レシ、スタ(DDRx)、入力レシ、スタ(PINx)の各ポートに対して、3つI/Oメモリアト・レス位置が割り当てられます。入力レシ、スタのI/O位置は読むだけで、一方出力レシ、スタと方向レシ、スタは読み書き(両方)です。加えてMCU制御レシ、スタ(MCUCR)のプルアップ、禁止(PUD)ビットは設定(1)されると、全ポートで全ビットに対してプルアップ機能を禁止します。

標準デジタルI/OとしてのI/Oポートの使用は次の「**標準デジタル入出力としてのポート**」で記述されます。多くのポート ピンはデバイスの周辺機能用の交換機能と多重化されます。ポート ピンとの各交換機能のインターフェース法は27頁の「**交換ポート機能**」で記述されます。交換機能の完全な記述については個別機能部項目を参照してください。

ポート ピンのいくつかの交換機能の許可は、そのポート内の他のピンの標準デジタル入出力としての使用に影響しないことに注意してください。

#### 標準デジタル入出力としてのポート

このポートは任意の内部プルアップ付き双方向I/Oポートです。図32.は、ここで属にPxnと呼ばれるI/Oポートピンの1つの機能説明を示します。

#### ピンの設定

各ポート ピンは3つのレジスタ ビット、DDxn、PORTxn、PINxnから成ります。33頁の「I/Oポート用レジスタ」で示されるようにDDxnビットはDDRx I/Oアドレス、PORTxnビットはPORTx I/Oアドレス、PINxビットはPINx I/Oアドレスでアクセスされます。

DDRxレジスタ内のDDxnビットは、そのピンの方向を選択します。DDxnが論理1を書かれるとPxnは出力ピンとして設定されます。DDxnが論理0を書かれるとPxnは入力ピンとして設定されます。

そのピンが入力ピンとして設定されるとき、PORTxnが論理1を書かれると、プルアップ抵抗が活性(有効)にされます。プルアップ抵抗をOFF に切り替えるには、PORTxnが論理0を書かれるか、またはそのピンが出力ピンとして設定されなければなりません。ポートピンは例えクロックが動いていなくても、リセット条件が活性(有効)になるとHi-Zにされます。

そのピンが出力ピンとして設定されるとき、PORTxnが論理1を書かれると、そのポート ピンはHigh(1)に駆動されます。そのピンが出力ピンとして設定されるとき、PORTxnが論理0を書かれると、そのポート ピンはLow(0)に駆動されます。

Hi-Z入力(DDxn=0, PORTxn=0)とHigh出力(DDxn=1, PORTxn=1)間の切り替え時、プルアップ許可入力(DDxn=0, PORTxn=1)または Low出力(DDxn=1, PORTxn=0)のどちらかの中間状態が生じるに違いありません。通常、高インピーダンス環境は強力なHigh(吐き出し) 駆動部とプルアップ間の違いに気付かないので、プルアップが許可された状態は十分受け入れられます。この事例でないならば、全ポートの全プルアップを禁止するために、MCU制御レシ、スタ(MCUCR)のプルアップを禁止(PUD)ビットが設定(1)できます。

プルアップ入力とLow出力間の切り替えは同じ問題を発生します。使用者は中間状態としてHi-Z入力(DDxn=0, PORTxn=0)またはHigh 出力(DDxn=1, PORTxn=1)のどちらかを使わなければなりません。

表21.はピン値に対する制御信号の一覧を示します。

| 表21. | ボー | トピンの | り設定 |

|------|----|------|-----|

|------|----|------|-----|

| DDxn | PORTxn | PUD (MCUCR) | 入出力 | プルアップ抵抗 | 備考                            |

|------|--------|-------------|-----|---------|-------------------------------|

| 0    | 0      | X           | 入力  | なし      | 高インヒ゜ーダンス (Hi-Z)              |

| 0    | 1      | 0           | 入力  | あり      | Pxnに外部からLowを入力すると吐き出し電流が流れます。 |

| 0    | 1      | 1           | 入力  | なし      | 高インピーダンス (Hi-Z)               |

| 1    | 0      | X           | 出力  | なし      | Low (吸い込み)出力                  |

| 1    | 1      | X           | 出力  | なし      | High (吐き出し)出力                 |

#### ピン値の読み込み

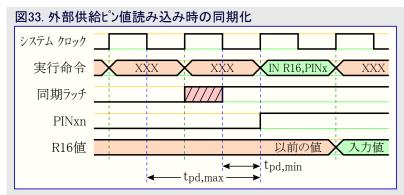

DDxn方向ビットの設定に関係なく、ポートピンはPINxnレジスタビットを通して読めます。図32.で示されるようにPINxnレジスタビットを先行するラッチは同期化回路を構成します。これは物理ピンが内部クロック端付近で値を変える場合の未定義状態(メタ ステーブル)を避けるために必要とされますが、それは遅延も持ち込みます。図33.は外部的に加えられたピン値を読む時の同期化タイミング図を示します。伝播遅延の最小と最大は各々tpd,minとtpd,maxで示されます。

(図33.で)システム クロックの最初の下降端の直ぐ後から始まる クロック周期を考察してください。このラッチはクロックがLowの時に閉じ、クロックがHighの時に同期ラッチ信号の斜線部分で示されるように通過(トランスペアレント)となります。この信号値はシステム クロックがLowになる時に保持(ラッチ)されます。それが続くクロックの上昇端でPINxnレシ、スタに取り込まれます。2つの矢印tpd,minとtpd,maxによって示されるように、ピン上の単一信号遷移は、出現時点に依存して0.5~1.5システム クロック周期遅らされます。

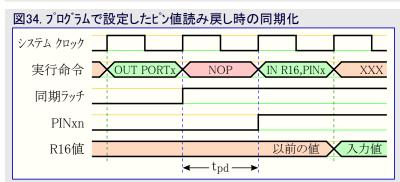

ソフトウェアが指定したピン値を読み戻すとき、図34.で示されるようにNOP命令が挿入されなければなりません。OUT命令はシステムクロックの上昇端で同期ラッチを設定します。この場合、同期化回路を通過する遅延時間(tpd)は1システムクロック周期です。

次のコート例はポートBピンの0と1をHigh出力、2と3をLow出力、6と7をプルアップ指定として4~7を入力に設定する方法を示します。結果のピン値が再び読み戻されますが、前記で検討されたように、いくつかのピンへ直前に指定された値を読み戻すことができるようにNOP命令が挿入されます。

```

アセンブリ言語プログラム例

LDI

R16, (1<<PB7) | (1<<PB6) | (1<<PB1) | (1<<PB0)

;プルアップとHigh値を取得

R17, (1<<DDB3) | (1<<DDB2) | (1<<DDB1) | (1<<DDB0)

;出力ビット値を取得

LDI

PORTB, R16

;プルアップとHigh値を設定

OUT

;入出力方向を設定

OUT

DDRB, R17

NOP

;同期化遅延対処

;ピン値読み戻し

IN

R16, PINB

C言語プログラム例

unsigned char i;

/* */

PORTB = (1 << PB7) | (1 << PB6) | (1 << PB1) | (1 << PB0);

/* プルアップとHigh値を設定 */

DDRB = (1<<DDB3) | (1<<DDB2) | (1<<DDB1) | (1<<DDB0);

/* 入出力方向を設定 */

_NOP();

/* 同期化遅延対処 */

i = PINB;

/* ピン値読み戻し */

```

注: アセンブリ言語プログラムについてはプルアップがピン0,1,6,7に設定されてから、ビット0と1の強力なHigh駆動部としての再定義、ビット2と3のLow駆動部としての定義、方向ビットが正しく設定されるまでの時間を最小とするために2つの一時レジスタが使われます。

#### デジタル入力許可と休止形態

図32.で示されるように、デジタル入力信号はシュミットトリカの入力をGNDにクランプできます。この図でSLEEPと印された信号は、入力信号のいくつかが開放のまま、またはVCC/2付近のアナログ信号電圧を持つ場合の高消費電力を避けるため、パワーダウン動作、スタンバイ動作、A/D雑音低減動作でMCU休止制御器によって設定(1)されます。

SLEEPは外部割り込みピンとして許可されたポート ピンに対しては無視されます。外部割り込み要求が許可されないならば、SLEEPは他のピンについてと同様に有効です。SLEEPは27頁の「**交換ポート機能**」で記載されるように様々な他の交換機能によっても無視されます。

外部割り込みが許可されていない"上昇端、下降端、または論理変化(両端)割り込み"として設定された非同期外部割り込みピンに論理1が存在すると、上で言及した休止形態から(復帰)再開するとき、これら休止形態でのクランプが要求された論理変化を生ずるので、対応する外部割り込み要求フラグが設定されます。

#### 未接続ピン

いくつかのピンが未使用にされる場合、それらのピンが定義されたレベルを持つのを保証することが推奨されます。例え上記のような深い休止形態で多くのデジタル入力が禁止されるとしても、デジタル入力が許可される他の全ての動作(リセット、活動動作、アイドル動作)で消費電流削減のため、浮き入力は避けられるべきです。

未使用ピンの定義されたレベルを保証する最も簡単な方法は内部プルアップを許可することです。この場合、リセット中のプルアップは禁止されます。リセット中の低消費電力が重要ならば、外部プルアップまたはプルダウンを使うことが推奨されます。未使用ピンを直接GNDまたはVCCに接続することは、ピンが偶然に出力として設定されると過電流を引き起こす可能性があるため推奨されません。

# 交換ポート機能

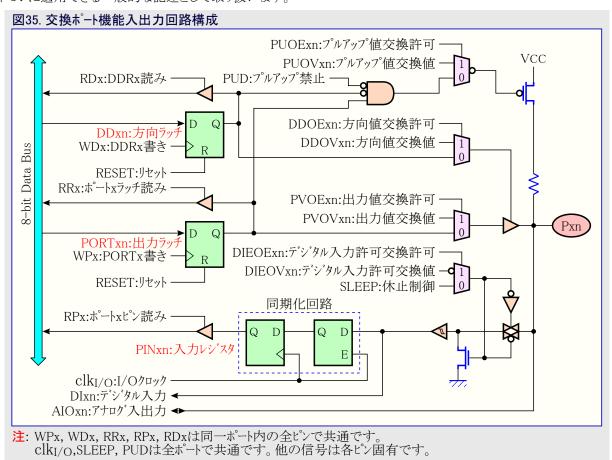

多くのポート ピンには標準デ゙ジタル入出力に加え交換機能があります。図35.は単純化された図32.でのポート ピン制御信号が交換機能により、どう重複できるかを示します。この重複信号は全てのポート ピンに存在する訳ではありませんが、この図はAVRマイクロ コントローラ系統の全ポート ピンに適用できる一般的な記述として取り扱います。

表22.は重複(交換)信号の機能一覧を示します。図35.で示すピンとポートは次表で示されません。重複(交換)信号は交換機能を持つ機能部で内部的に生成されます。

| 機能用交換信号の一般定義 | Š |

|--------------|---|

|              |   |

|       | 機能用交換信号の一般定  |                                                                                                     |

|-------|--------------|-----------------------------------------------------------------------------------------------------|

| 信号略名  | 信号名          | 意味                                                                                                  |

| PUOE  | プルアップ値交換許可   | 1で、プルアップ許可はPUOV信号で制御され、0の場合、DDxn=0, PORTxn=1, PUD=0でプルアップが許可されます。                                   |

| PUOV  | プルアップ値交換値    | PUOE=1時、DDxn, PORTxn, PUDの値に関係なく、プルアップの有(1)/無(0)を指定します。                                             |

| DDOE  | 方向値交換許可      | 1で、出力駆動部はDDOV信号で制御され、0の場合、DDxnレジスタ値で制御されます。                                                         |

| DDOV  | 方向値交換値       | DDOE=1時、DDxnレジスタ値に関係なく、出力駆動部のON(1)/OFF(0)を制御します。                                                    |

| PVOE  | 出力値交換許可      | 1で出力駆動部がONならば、ポート値はPVOV信号で制御されます。出力駆動部がONで0の場合、ポート値はPORTxnレジスタ値で制御されます。                             |

| PVOV  | 出力値交換値       | PVOE=1時、PORTxnレシブスタ値に関係なく、ポート値を制御(1/0)します。                                                          |

| DIEOE | デジタル入力許可交換許可 | 1で、デジタル入力許可はDIEOV信号で制御され、0の場合、MCUの状態(活動動作、休止<br>形態)によって決定されます。                                      |

| OIEOV | デジタル入力許可交換値  | DIEOE=1時、MCUの状態(活動動作、休止形態)に関係なく、デジタル入力を許可(1)/禁止(0)します。                                              |

| DI    | デジタル入力       | 交換機能用デジタル入力です。この信号は図上でシュミット トリガ出力に接続されていますが、<br>これは同期化前となります。この信号はクロックとしての使用を除き、各交換機能自身が同<br>期化します。 |

| AIO   | アナログ入出力      | 交換機能用アナログ入出力です。この信号はピンに直接接続され、双方向使用ができます。                                                           |

次節は交換機能に関連する重複(交換)信号と各ポートの交換機能を簡単に記述します。さらに先の詳細については交換機能の記述を参照してください。

# ■ MCU制御レジスタ (MCU Control Register) MCUCR

MCU制御レジスタは一般的なMCU機能に対する制御ビットを含みます。

| ピット         | 7 | 6   | 5   | 4   | 3   | 2 | 1     | 0     | _     |

|-------------|---|-----|-----|-----|-----|---|-------|-------|-------|

| \$35 (\$55) | _ | PUD | SE  | SM1 | SM0 | - | ISC01 | ISC00 | MCUCR |

| Read/Write  | R | R/W | R/W | R/W | R/W | R | R/W   | R/W   |       |

| 初期値         | 0 | 0   | 0   | 0   | 0   | 0 | 0     | 0     |       |

#### ■ ビット2 - PUD: プルアップ。禁止 (Pull-up Disable)

このビットが設定(1)されると、例えDDxnとPORTxnレジスタがプルアップを許可(DDxn=0, PORTxn=1)に設定されても、I/Oポートのプルアップは禁止されます。この特徴についてより多くの詳細に関しては25頁の「ピンの設定」をご覧ください。

#### ポートAの交換機能

ポートAには表23.で示されるようにA/D変換器とアナログ比較器用のアナログ入力、ピン変化割り込みとしての交換機能があります。いくつかのポートAピンが出力として設定される場合、(A/D)変換が進行中の時にそれらを切り替えないことが重要です。これは変換の結果を誤らせるかもしれません。A/D変換器は59頁の「A/D変換器」で記述されます。アナログ比較器は57頁の「アナログ比較器」で記述されます。ピン変化割り込みは例えそのピンが出力として設定されても、割り込みが許可され、それが交換機能によって遮蔽(マスク)されなければ、PA7,PA6,PA3ピンで起動します。38頁の「ピン変化割り込み」での詳細をご覧ください。

#### 表23. ポートAピンの交換機能

| ポート ピン | 交換機能                                        | ホ <sup>°</sup> ート ヒ <sup>°</sup> ン | 交換機能                                        |  |  |  |

|--------|---------------------------------------------|------------------------------------|---------------------------------------------|--|--|--|

|        | ADC6 (A/D変換チャネル6入力)                         | PA4                                | ADC3 (A/D変換チャネル3入力)                         |  |  |  |

| PA7    | AIN1 (アナログ比較器反転入力)<br>PCINT1 (ピン変化1群割り込み)   | PA3                                | AREF (A/D変換外部基準電圧入力)<br>PCINT1 (ピン変化1群割り込み) |  |  |  |

| PA6    | ADC5 (A/D変換チャネル5入力)<br>AIN0 (アナロケ)比較器非反転入力) | PA2                                | ADC2 (A/D変換チャネル2入力)                         |  |  |  |

| 1 A0   | PCINT1 (ピン変化1群割り込み)                         | PA1                                | ADC1 (A/D変換チャネル1入力)                         |  |  |  |

| PA5    | ADC4 (A/D変換チャネル4入力)                         | PA0                                | ADC0 (A/D変換チャネル0入力)                         |  |  |  |

#### ・ ADC6/AIN1/(PCINT1) - ポートA ビット7 : PA7

ADC6,AIN1: A/D変換チャネル6入力、アナログ・比較器反転入力。A/D変換器またはアナログ・比較器の機能を妨げるデジタルポート機能を 避けるため、内部プルアップをOFFにした入力としてポート ピンを設定してください。

PCINT1: ピン変化1群割り込みピン。ピン変化割り込みは全割り込み(I)が許可され、ピン変化割り込みが許可され、交換機能がこの割り込みを遮蔽しない時のピンで許可されます。交換機能の遮蔽はアナログ比較器です。ピン変化割り込みが許可され、交換機能によって遮蔽されなければ、休止形態でもデ゙ジタル入力はPA7ピンで許可されます。

#### ・ ADC5/AIN0/(PCINT1) - ポートA ビット6 : PA6

ADC5,AINO: A/D変換チャネル5入力、アナログ比較器非反転入力。A/D変換器またはアナログ比較器の機能を妨げるデジタル ポート機能を避けるため、内部プルアップをOFFにした入力としてポート ピンを設定してください。

PCINT1: ピン変化1群割り込みピン。ピン変化割り込みは全割り込み(I)が許可され、ピン変化割り込みが許可され、交換機能がこの割り込みを遮蔽しない時のピンで許可されます。交換機能の遮蔽はアナログ比較器です。ピン変化割り込みが許可され、交換機能によって遮蔽されなければ、休止形態でもデジタル入力はPA6ピンで許可されます。

#### • ADC4 - ホートA ビット5: PA5

ADC4: A/D変換チャネル4入力。A/D変換器の機能を妨げるデジタル ポート機能を避けるため、内部プルアップをOFFにした入力としてポート ピンを設定してください。

#### • ADC3 - ホートA ビット4: PA4

ADC3: A/D変換チャネル3入力。A/D変換器の機能を妨げるデジタル ポート機能を避けるため、内部プルアップをOFFにした入力としてポート ピンを設定してください。

#### • AREF/(PCINT1) - ポートA ビット3 : PA3

AREF: A/D変換用外部基準電圧。このピンがA/D多重器選択レシ、スタ(ADMUX)のREFSのピットの設定(1)により、外部基準電圧または AREFピンでの外部コンデンサとの内部基準電圧(2.56V)として使われると、プルアップと出力駆動部はPA3で禁止されます。

PCINT1: ピン変化1群割り込みピン。ピン変化割り込みは全割り込み(I)が許可され、ピン変化割り込みが許可され、交換機能がこの割り込みを遮蔽しない時のピンで許可されます。交換機能の遮蔽はA/D変換器用基準電圧としてのピン使用です。ピン変化割り込みが許可され、交換機能によって遮蔽されなければ、休止形態でもデン゙タル入力はPA3ピンで許可されます。

• ADC2 - ホートA ビット2: PA2

ADC2: A/D変換チャネル2入力。A/D変換器の機能を妨げるデジタル ポート機能を避けるため、内部プルアップをOFFにした入力としてポート ピンを設定してください。

• ADC1 - ポートA ビット1 : PA1

ADC1: A/D変換チャネル1入力。A/D変換器の機能を妨げるデジタル ポート機能を避けるため、内部プルアップをOFFにした入力としてポート ピンを設定してください。

• ADC0 - ポートA ビット0 : PA0

ADC0: A/D変換チャネル0入力。A/D変換器の機能を妨げるデジタル ポート機能を避けるため、内部プルアップをOFFにした入力としてポート ピンを設定してください。

表24.と表25.はポートAの交換機能を27頁の図35.で示される交換信号に関連付けます。これらはPA7, PA6, PA3でデジタル入力を変更します。PA3の出力とプルアップ駆動部も無効にされます。

|                | - 0                |           |            |                     |

|----------------|--------------------|-----------|------------|---------------------|

| 主り4            | + ` L ^ 7 ~        | . 4の六幅:   | 機能用交換      | & /=                |

| <i>7</i> 0 / 4 | 小 <b>一</b> P A / C | マサロノングを担じ | 100 HI V 4 | 41 = <del>7 =</del> |

| 信号名   | PA7/ADC6/AIN1/PCINT1 | PA6/ADC5/AIN0/PCINT1 | PA5/ADC4 | PA4/ADC3 |

|-------|----------------------|----------------------|----------|----------|

| PUOE  | 0                    | 0                    | 0        | 0        |

| PUOV  | 0                    | 0                    | 0        | 0        |

| DDOE  | 0                    | 0                    | 0        | 0        |

| DDOV  | 0                    | 0                    | 0        | 0        |

| PVOE  | 0                    | 0                    | 0        | 0        |

| PVOV  | 0                    | 0                    | 0        | 0        |

| DIEOE | ACSR[ACD]·PCINT1許可   | ACSR[ACD] · PCINT1許可 | 0        | 0        |

| DIEOV | 1                    | 1                    | 0        | 0        |

| DI    | PCINT1入力             | PCINT1入力             | _        | _        |

| AIO   | ADDC6入力/AIN1入力       | ADDC5入力/AIN0入力       | ADDC4入力  | ADDC3入力  |

#### 表25. ポートA3~0の交換機能用交換信号

| 信号名   | PA3/AREF/PCINT1           | PA2/ADC2 | PA1/ADC1 | PA0/ADC0 |

|-------|---------------------------|----------|----------|----------|

| PUOE  | ADMUX[REFS0]              | 0        | 0        | 0        |

| PUOV  | 0                         | 0        | 0        | 0        |

| DDOE  | ADMUX[REFS0]              | 0        | 0        | 0        |

| DDOV  | 0                         | 0        | 0        | 0        |

| PVOE  | 0                         | 0        | 0        | 0        |

| PVOV  | 0                         | 0        | 0        | 0        |

| DIEOE | ADMUX[REFS0]・<br>PCINT1許可 | 0        | 0        | 0        |

| DIEOV | 1                         | 0        | 0        | 0        |

| DI    | PCINT1入力                  | _        | -        | _        |

| AIO   | A/D基準電圧入力                 | ADDC2入力  | ADDC1入力  | ADDC0入力  |

注: PCINT1割り込みは38頁の「ピン変化割り込み」で記述されるように全割り込み許可(I)ビットが許可され、GIMSKでPCIE1ビットが設定(1)され、そのピンの交換機能が禁止される場合にだけ許可されます。

(訳注) 論理反転は赤色のバーで示しました。

#### ポートBの交換機能

ポートBにはA/D変換器、クロック、タイマ/カウンタ、USI、SPIプログラミング、ピン変化割り込みについての交換機能があります。A/D変換器は59頁の「A/D変換器」で、クロックは13頁の「システム クロックとクロック選択」で、タイマ/カウンタは39頁の「タイマ/カウンタ」で、USIは49頁の「多用途直列インターフェース (USI)」で記述されます。ピン変化割り込みは例えそのピンが出力として設定されても、割り込みが許可され、それが交換機能で遮蔽されなければ、PB7~0ピンで起動します。38頁の「ピン変化割り込み」での詳細をご覧ください。プログラミング動作でのピン機能は67頁の「メモリプログラミング」で記述されます。交換機能は表26.で示されます。

#### 表26. ポートBピンの交換機能

| ホ <sup>°</sup> ート ヒ <sup>°</sup> ン | 交換機能                                                                            | ポート ピン | 交換機能                                                                                              |

|------------------------------------|---------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------|

| PB7                                | ADC10 (A/D変換チャネル10入力)<br>RESET (外部リセット入力)<br>PCINT1 (ピン変化1群割り込み)                | PB3    | OC1B (タイマ/カウンタ1 PWM-B非反転出力,<br>比較B一致出力)<br>PCINT0 (ピン変化0群割り込み)                                    |

| PB6                                | ADC9 (A/D変換チャネル9入力) INT0 (外部割り込み0入力) T0 (タイマ/カウンタ0外部クロック入力) PCINT1 (ピン変化1群割り込み) | PB2    | SCK (3線動作USI 直列クロック入出力) SCL (2線動作USI 直列クロック入出力(注)) OC1B (タイマ/カウンタ1 PWM-B反転出力) PCINTO (ピン変化0群割り込み) |

| PB5                                | ADC8 (A/D変換チャネル8入力)<br>XTAL2 (システム クロック発振器出力)<br>PCINT1 (ピン変化1群割り込み)            | PB1    | DO (3線動作USI 直列データ出力)<br>OC1A (タイマ/カウンタ1 PWM-A非反転出力,<br>比較A一致出力)<br>PCINTO (ピン変化0群割り込み)            |

| PB4                                | ADC7 (A/D変換チャネル7入力)<br>XTAL1 (システム クロック発振器(外部)入力)<br>PCINT1 (ピン変化1群割り込み)        | PB0    | DI (3線動作USI 直列データ入力) SDA (2線動作USI 直列データ 入出力(注)) OC1A (タイマ/カウンタ1 PWM-A反転出力) PCINTO (ピン変化0群割り込み)    |

注: オープントレイン出力

交換ピン設定は次のとおりです。

• ADC10/RESET/(PCINT1) - ホートB ビット7: PB7

ADC10: A/D変換チャネル10入力。A/D変換器の機能を妨げるデジタル ポート機能を避けるため、内部プルアップをOFFにした入力としてポート ピンを設定してください。

RESET:外部リセット入力はLow活性(有効)で、RSTDISBLヒュース、の非プログラム(1)によって許可されます。このピンがRESETピンとして使われると、プルアップが活性(有効)にされ、出力駆動部とデジタル入力は非活性(無効)にされます。

PCINT1: ピン変化1群割り込みピン。ピン変化割り込みは全割り込み(I)が許可され、ピン変化割り込みが許可され、交換機能がこの割り込みを遮蔽しない時のピンで許可されます。交換機能の遮蔽はRESETとしてのピン使用です。ピン変化割り込みが許可され、交換機能によって遮蔽されなければ、休止形態でもデ゙ジタル入力はPB7ピンで許可されます。

• ADC9/INT0/T0/(PCINT1) - ホ°ートB ビット6 : PB6

ADC9: A/D変換チャネル9入力。A/D変換器の機能を妨げるデジタル ポート機能を避けるため、内部プルアップをOFFにした入力としてポート ピンを設定してください。

INTO:外部割り込み0入力。外部割り込み元として扱えるPB6ピンは一般割り込み許可レジスタ(GIMSK)のINTOビットを設定(1)することによって許可されます。

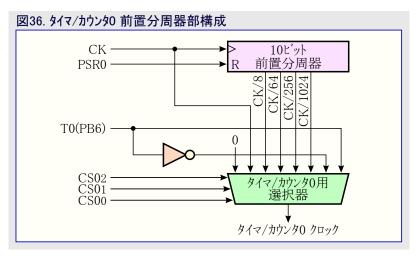

TO: タイマ/カウンタ0外部クロック入力はタイマ/カウンタ0制御レシ、スタ(TCCR0)のCS02とCS01ビットを設定(1)することによって許可されます。

PCINT1: ピン変化1群割り込みピン。ピン変化割り込みは全割り込み(I)が許可され、ピン変化割り込みが許可され、交換機能がこの割り込みを遮蔽しない時のピンで許可されます。交換機能の遮蔽は、外部Lowレヘル割り込み元0(INT0)とタイマ/カウンタ0外部クロック入力(T0)です。ピン変化割り込みが許可され、交換機能によって遮蔽されなければ、休止形態でもデジタル入力はPB6ピンで許可されます。

• ADC8/XTAL2/(PCINT1) - ホ°-トB ビット5 : PB5

ADC8: A/D変換チャネル8入力。A/D変換器の機能を妨げるデジタル ポート機能を避けるため、内部プルアップをOFFにした入力としてポート ピンを設定してください。

XTAL2: システム クロック発振器ピン2。内蔵校正可能RC発振器、外部クロック、PLLクロックを除く全てのチップ クロック元用クロック ピンとして使われると、このピンはI/Oピンとして使えません。チップ クロック元として内蔵校正可能RC発振器、外部クロック、またはPLLクロックを使うと、PB5は通常のI/Oピンとして取り扱います。

PCINT1: ピン変化1群割り込みピン。ピン変化割り込みは全割り込み(I)が許可され、ピン変化割り込みが許可され、交換機能がこの割り込みを遮蔽しない時のピンで許可されます。交換機能の遮蔽は、XTAL2出力です。ピン変化割り込みが許可され、交換機能によって遮蔽されなければ、休止形態でもデジタル入力はPB5ピンで許可されます。

#### • ADC7/XTAL1/(PCINT1) - ホートB ビット4: PB4

- ADC7: A/D変換チャネル7入力。A/D変換器の機能を妨げるデジタル ポート機能を避けるため、内部プルアップをOFFにした入力としてポート ピンを設定してください。

- XTAL1: システム クロック発振器ピン1。内蔵校正可能RC発振器とPLLクロックを除く全てのチップ クロック元用クロック ピンとして使われます。ク ロック ピンとして使われると、このピンはI/Oピンとして使えません。チップ クロック元として内蔵校正可能RC発振器またはPLLクロッ クを使うと、PB4は通常のI/Oピンとして取り扱います。

- PCINT1: ピン変化1群割り込みピン。ピン変化割り込みは全割り込み(I)が許可され、ピン変化割り込みが許可され、交換機能がこの割り込みを遮蔽しない時のピンで許可されます。交換機能の遮蔽はXTAL1入力です。ピン変化割り込みが許可され、交換機能によって遮蔽されなければ、休止形態でもデジタル入力はPB4ピンで許可されます。

- OC1B/(PCINT0) ホートB ビット3: PB3

- OC1B: タイマ/カウンタ1の比較B一致出力。PB3ピンはタイマ/カウンタ1の比較B一致用出力として扱えます。PB3ピンはこの機能を扱うために出力として設定(DDB3=1)されなければなりません。このOC1BピンはPWM動作用出力ピンでもあります。

- PCINTO: ピン変化0群割り込みピン。ピン変化割り込みは全割り込み(I)が許可され、ピン変化割り込みが許可され、交換機能がこの割り込みを遮蔽しない時のピンで許可されます。交換機能の遮蔽は比較一致出力OC1Bです。ピン変化割り込みが許可され、交換機能によって遮蔽されなければ、休止形態でもデン゙タル入力はPB3ピンで許可されます。

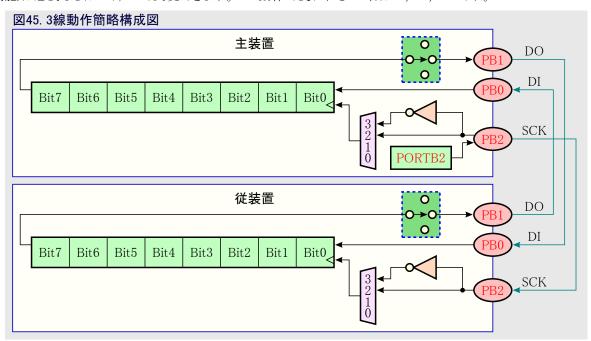

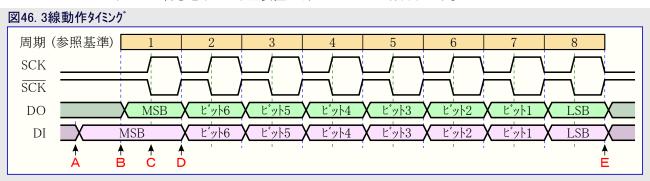

- ・SCK/SCL/OC1B/(PCINT0) ホートB ピット2: PB2

- SCK: 3線動作USIのクロック入出力。SPIが許可されると、このピンは入力として設定されます。3線動作USIでのDDB2ビットは主装置動作に対して出力、従装置動作に対して入力と、ピンの方向を制御します。

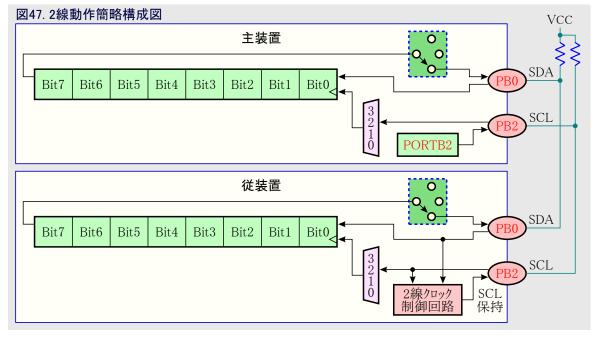

- SCL: 2線動作USIのクロック入出力(オープントレイン出力)。SCLピンはDDB2が設定(1)され且つ、PORTB2が解除(0)されるか、または開始条件が検出されるとLowに引き込まれます。プルアップは2線動作USIで禁止されます。

- OC1B: タイマ/カウンタ1のPWM-B反転出力。PB2ピンはUSIが許可されなければ、タイマ/カウンタ1 PWM動作用反転出力として扱えます。 PB2ピンはこの機能を扱うために出力として設定(DDB2=1)されなければなりません。

- PCINTO: ピン変化0群割り込みピン。ピン変化割り込みは全割り込み(I)が許可され、ピン変化割り込みが許可され、交換機能がこの割り込みを遮蔽しない時のピンで許可されます。交換機能の遮蔽は反転比較一致出力OC1BとUSIクロックSCK,SCLです。ピン変化割り込みが許可され、交換機能により遮蔽されなければ、休止形態でもデジタル入力はPB2ピンで許可されます。

- DO/OC1A/(PCINT0) ポートB ビット1 : PB1

- DO: 3線動作USIのデータ出力。データ出力(DO)はPORTB1値を無効にし、データ方向(DDB1)ビットが設定(1)されると、ポートが駆動されます。 けれどもPORTB1ビットは未だプルアップを制御し、方向が入力でPORTB1が設定(1)されるなら、プルアップを許可します。

- OC1A: タイマ/カウンタ1の比較A一致出力。PB1ピンはタイマ/カウンタ1の比較A一致用出力として扱えます。PB1ピンはこの機能を扱うために出力として設定(DDB1=1)されなければなりません。このOC1AピンはプログラミングまたはUSIで使われないなら、タイマ/カウンタ機能のPWM動作用出力ピンでもあります。

- PCINTO: ピン変化0群割り込みピン。ピン変化割り込みは全割り込み(I)が許可されて、ピン変化割り込みが許可され、交換機能がこの割り込みを遮蔽しない時のピンで許可されます。交換機能の遮蔽は比較一致出力OC1Aと3線動作USIでのデータ出力(DO)です。ピン変化割り込みが許可され、交換機能によって遮蔽されなければ、休止形態でもデジタル入力はPB1ピンで許可されます。

- DI/SDA/OC1A/(PCINT0) ホートB ビット0 : PB0

- DI: 3線動作USIのデータ入力。3線動作USIは標準ポート機能を無効にしませんので、ピンは入力として設定しなければなりません。

- SDA: 2線動作USIのデータ入出力(オープント・レイン出力)。直列データ ピンは双方向でオープント・レイン出力を使います。SDAピンは出力としてこのピンを設定することにより許可されます。このピンはDDB0が設定(1)される時にPORTB0またはUSI移動レシ、スタ(出力)が0のとき、Lowに引き込まれます。プルアップは2線動作USIで禁止されます。

- OC1A: タイマ/カウンタ1のPWM-A反転出力。PB0ピンはプログラミングまたはUSIで使われないなら、タイマ/カウンタ1 PWM動作用反転出力として扱えます。PB0ピンはこの機能を扱うために出力として設定(DDB0=1)されなければなりません。

- PCINTO: ピン変化0群割り込みピン。ピン変化割り込みは全割り込み(I)が許可され、ピン変化割り込みが許可され、交換機能がこの割り込みを遮蔽しない時のピンで許可されます。交換機能の遮蔽は反転比較一致出力OC1AとUSIデータDI,SDAです。ピン変化割り込みが許可され、交換機能によって遮蔽されなければ、休止形態でもデジタル入力はPB0ピンで許可されます。

表27.と表28.はポートBの交換機能を27頁の図35.で示される交換信号に関連付けます。

#### 表27. ポートB7~4の交換機能用交換信号

| <u> </u> | 「の人民版配加入民間の                |                             |                           |                                     |  |

|----------|----------------------------|-----------------------------|---------------------------|-------------------------------------|--|

| 信号名      | PB7/ADC10/<br>RESET/PCINT1 | PB6/ADC9/INT0/<br>T0/PCINT1 | PB5/ADC8/<br>XTAL2/PCINT1 | PB4/ADC7/XTAL1                      |  |

| PUOE     | RSTDISBL                   | 0                           | PB5 I/O許可                 | PB4 I/O許可                           |  |

| PUOV     | 1                          | 0                           | 0                         | 0                                   |  |

| DDOE     | RSTDISBL                   | 0                           | PB5 I/O許可                 | PB4 I/O許可                           |  |

| DDOV     | 0                          | 0                           | 0                         | 0                                   |  |

| PVOE     | 0                          | 0                           | 0                         | 0                                   |  |

| PVOV     | 0                          | 0                           | 0                         | 0                                   |  |

| DIEOE    | RSTDISBL PCINT1許可          | T0外部クロック・INT0許可<br>PCINT1許可 | PB5 I/O許可<br>PCINT1許可     | PCINT1許可 <br>PB4 I/O許可 <br>外部クロック許可 |  |

| DIEOV    | RSTDISBL•PCINT1許可          | 0                           | PB5 I/O許可・<br>PCINT1許可    | PCINT1許可・<br>PB4 I/O許可<br>外部クロック許可  |  |

| DI       | PCINT1入力                   | INT0, T0, PCINT1入力          | PCINT1入力                  | 外部クロック, PCINT1入力                    |  |

| AIO      | ADC10入力/リセット入力             | ADC9入力                      | ADC8入力/XTAL2出力            | ADC7入力/XTAL1入力                      |  |

- **注**:・RSTDISBLヒュース'(Low有効)は18頁の「システム制御とリセット」章で記述されます。

- ・PCINT1割り込みは38頁の「ピン変化割り込み」で記述されるように全割り込み許可(I)ビットが許可され、GIMSKでPCIE1ビットが 設定(1)され、そのピンの交換機能が禁止される場合にだけ許可されます。

- ・PB4 I/O許可、PB5 I/O許可、外部クロック許可は14頁の「クロック元」で記述されるようにPLLCKとCKSELヒュースで与えられます。

- ・INTO(外部Lowレヘル割り込み)許可は38頁の「外部割り込み」で記述されるように全割り込み許可(I)が許可され、且つGIMSKでINTOビットが設定(1)される場合に許可されます。

- ・外部クロック(T0外部クロック)禁止でのタイマ/カウンタ0の操作は40頁の「8ビット タイマ/カウンタ0」で記述されます。

(訳注) 論理反転は赤色のバーで示しました。

#### 表28. ポートB3~0の交換機能用交換信号

| 信号名   | PB3/OC1B/PCINT0 | PB2/SCK/SCL/<br>OC1B/PCINT0                      | PB1/DO/OC1A/PCINTO          | PB0/DI/SDA/OC1A                                 |

|-------|-----------------|--------------------------------------------------|-----------------------------|-------------------------------------------------|

| PUOE  | 0               | 2線USI                                            | 0                           | 2線USI                                           |

| PUOV  | 0               | 0                                                | 0                           | 0                                               |

| DDOE  | 0               | 2線USI                                            | 0                           | 2線USI                                           |

| DDOV  | 0               | (USI SCL保持 PORTB2)・<br>DDB2                      | 0                           | (SDA PORTB0)•DDB0                               |

| PVOE  | OC1B許可          | 2線USI·DDB2 OC1B許可                                | 3線USI OC1A許可                | 2線USI·DDB0 OC1A許可                               |

| PVOV  | OC1B            | (2線USI•DDB2)•OC1B                                | 3線USI·DO 3線USI·OC1A許可·OC1A  | (2線USI·DDB0)·<br>OC1A許可·OC1A                    |

| DIEOE | OC1B許可・PCINT0許可 | (2線USI 3線USI <br>OC1B許可)・PCINT0許可<br>USI開始割り込み許可 | (3線USI OC1A許可)・<br>PCINT0許可 | (2線USI 3線USI<br>OC1A許可)・PCINT0許可<br>USI開始割り込み許可 |

| DIEOV | 1               | 1                                                | 1                           | 1                                               |

| DI    | PCINT0入力        | SCK, SCL, PCINT0入力                               | PCINT0入力                    | SDA, PCINT0入力                                   |

| AIO   | -               | _                                                | _                           | -                                               |

- 注:・タイマ/カウンタ1比較一致出力の許可とタイマ/カウンタ1 PWM出力OC1A/OC1BとOC1A/OC1Bは41頁の「8ビット タイマ/カウンタ1」で記述されます。

- ・PCINT0割り込みは38頁の「ピン変化割り込み」で記述されるように全割り込み許可(I)ビットが許可され、GIMSKでPCIE0ビットが 設定(1)され、そのピンの交換機能が禁止される場合にだけ許可されます。

- 2線と3線のUSI動作は49頁の「多用途直列インターフェース (USI)」で記述されます。

- ・USIに関する移動クロック(SCL)保持は49頁の「**多用途直列インターフェース (USI)**」で記述されます。

- ・USI開始割り込みは49頁の「**多用途直列インターフェース** (USI)」で記述されるように全割り込み許可(I)ビットが許可され、USICRで USISIEビットが設定(1)される場合に許可されます。

- ・データ出力(DO)は3線動作USIで有効で、その操作は49頁の「**多用途直列インターフェース (USI)**」で記述されます。

- ・2線動作USIでのSDAと3線動作USIでのDIデータ ピンの操作は49頁の「**多用途直列インターフェース (USI)**」で記述されます。

(訳注) 論理反転は赤色のバーで示しました。

# I/Oポート用レジスタ

# ■ ポートA出力レジスタ (Port A Data Register) PORTA

| ピット         | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|-------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

| \$1B (\$3B) | PORTA7 | PORTA6 | PORTA5 | PORTA4 | PORTA3 | PORTA2 | PORTA1 | PORTA0 | PORTA |

| Read/Write  | R/W    |       |

| 初期値         | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

# ■ ポートA方向レジスタ (Port A Data Direction Register) DDRA

| ピット         | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |      |

|-------------|------|------|------|------|------|------|------|------|------|

| \$1A (\$3A) | DDA7 | DDA6 | DDA5 | DDA4 | DDA3 | DDA2 | DDA1 | DDA0 | DDRA |

| Read/Write  | R/W  |      |

| 初期値         | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

# ■ ポートA入力レジスタ (Port A Input Address) PINA

| ピット         | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _    |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| \$19 (\$39) | PINA7 | PINA6 | PINA5 | PINA4 | PINA3 | PINA2 | PINA1 | PINA0 | PINA |

| Read/Write  | R     | R     | R     | R     | R     | R     | R     | R     |      |

| 初期値         | 不定    |      |

# ■ ポートB出力レジスタ (Port B Data Register) PORTB

| ピット         | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|-------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

| \$18 (\$38) | PORTB7 | PORTB6 | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 | PORTB |

| Read/Write  | R/W    |       |

| 初期値         | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

# ■ ポートB方向レジスタ (Port B Data Direction Register) DDRB

| ピット         | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    | _    |

|-------------|------|------|------|------|------|------|------|------|------|

| \$17 (\$37) | DDB7 | DDB6 | DDB5 | DDB4 | DDB3 | DDB2 | DDB1 | DDB0 | DDRB |

| Read/Write  | R/W  |      |

| 初期値         | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

# ■ ポートB入力レジスタ (Port B Input Address) PINB

| ピット         | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |      |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| \$16 (\$36) | PINB7 | PINB6 | PINB5 | PINB4 | PINB3 | PINB2 | PINB1 | PINB0 | PINB |

| Read/Write  | R     | R     | R     | R     | R     | R     | R     | R     |      |

| 初期値         | 不定    |      |

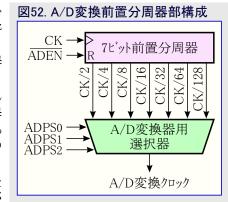

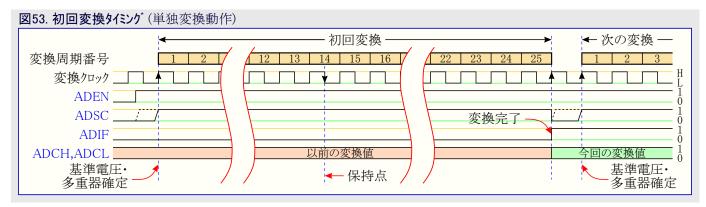

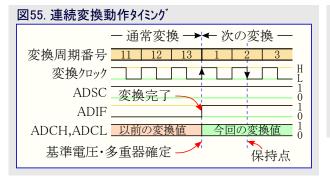

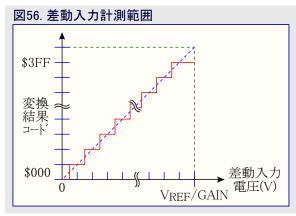

# 割り込み