# 4Kバイト実装書き込み可能フラッシュ メモリ付き Atmel 8ビット tinyAVR マイクロ コントローラ

データシート

# 特徴

- 高性能、低消費AVR® 8ビット マイクロ コントローラ

- 進化したRISC構造

- 強力な112命令(多くは1クロック周期実行)

- 16個の1バイト長汎用レジスタ

- 完全なスタティック動作

- 12MHz時、12MIPSに達する高速動作

- データ用メモリとプログラム用不揮発性メモリ

- 実装書き換え可能な4Kバイト(2K語)フラッシュ メモリ内蔵

- 256バ仆の内蔵SRAM

- フラッシュ書き込み/消去回数: 10,000

- データ保持力: 20年/85℃, 100年/25℃

- 内蔵周辺機能

- 2つのPWM出力を持つ1つの8ビット タイマ/カウンタ

- 1つの8/16ビットタイマ/カウンタ

- 10ビット A/D変換器

- ・12のシングル エント チャネル

- 独立したチップ。上発振器を持つウォッチト、ッグ、タイマ

- アナログ比較器

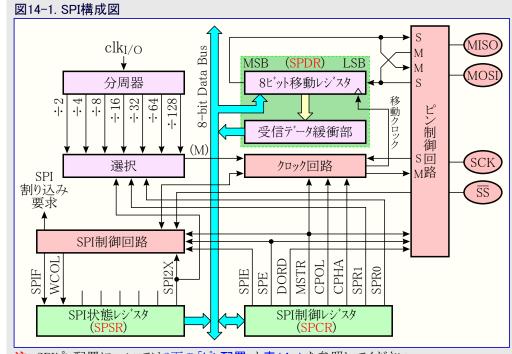

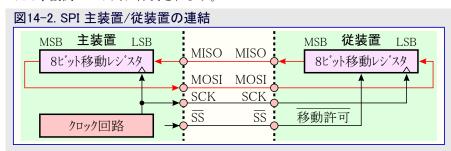

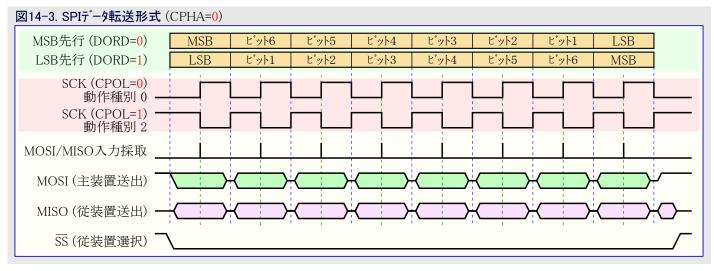

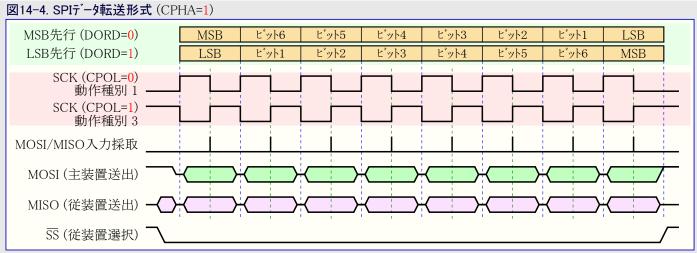

- 主装置/従装置動作SPI直列インターフェース

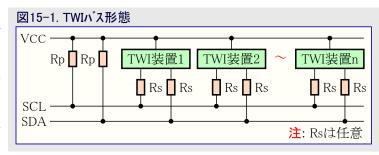

- 従装置動作TWI直列インターフェース

- 特殊マイクロ コントローラ機能

- 実装書き込み可能

- 内部及び外部の割り込み

- アイドル、A/D変換雑音低減、スタンバイ、パワーダウンの4つの低消費動作

- 強化した電源ONJセット回路

- 校正付き内蔵RC発振器

- I/Oと外囲器

- 18ビットの設定変更可能なI/O

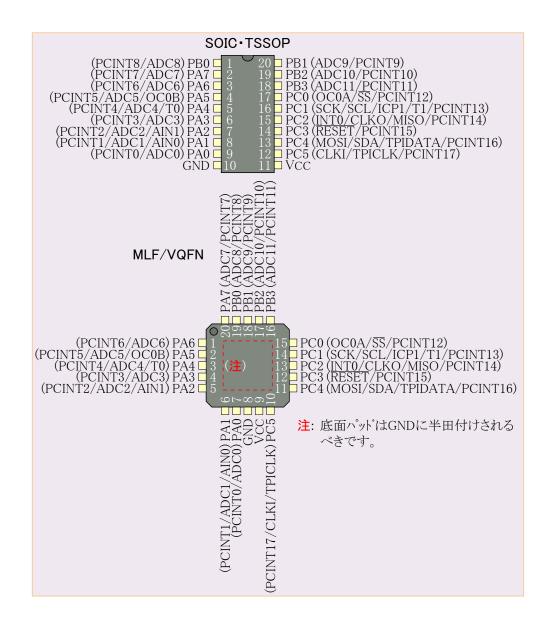

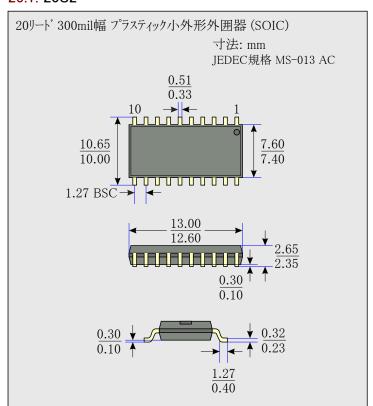

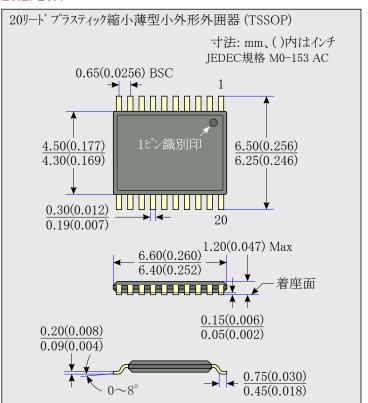

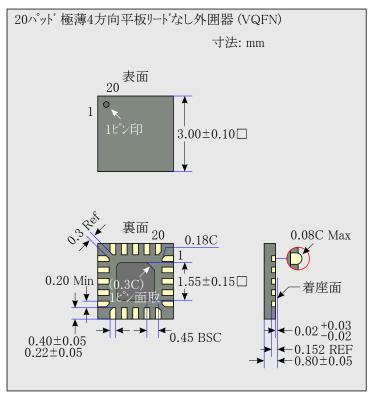

- 20ピンSOIC/TSSOP、20パットVQFN/MLF

- 動作電圧

- -1.8~5.5V

- 動作速度

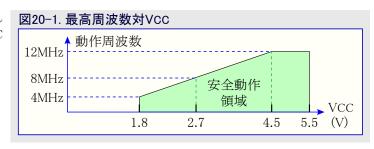

- $-0\sim4 MHz/1.8\sim5.5 V$

- $-0 \sim 8 MHz/2.7 \sim 5.5 V$

- $-0\sim12MHz/4.5\sim5.5V$

- 工業用温度範囲: -40~+85℃

- 低消費電力

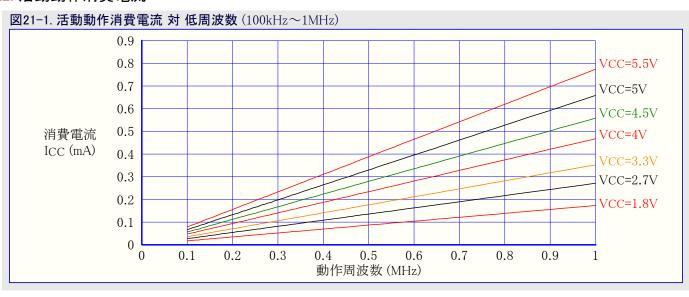

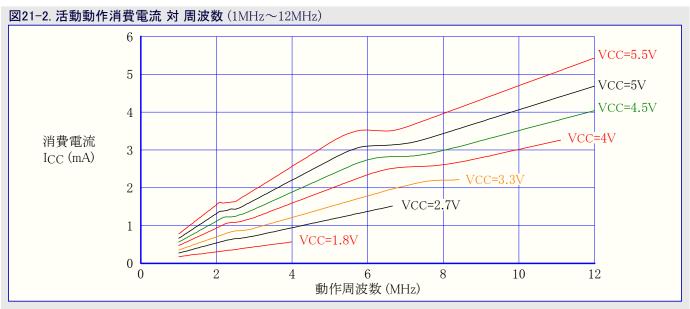

- 活動動作: 200μA (1MHz,1.8V)アイトル動作: 25μA (1MHz,1.8V)ハプワータヴン動作: <0.1μA (1.8V)</li>

本書は一般の方々の便宜のため有志により作成されたもので、Atmel社とは無関係であることを御承知ください。しおりの[はじめに]での内容にご注意ください。

# 1. ピン配置

### 1.1. ピン概要

#### 111 VCC

電源ピン。

#### 1.1.2. GND

接地ピン。

#### 1.1.3. RESET

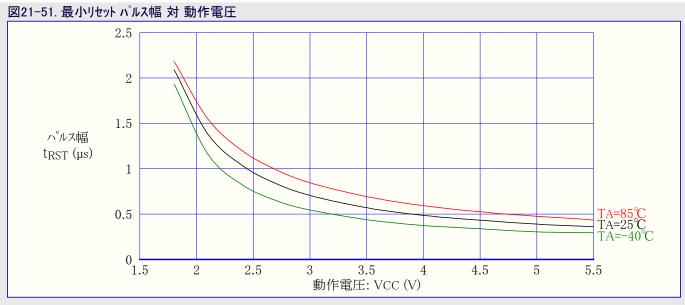

リセット入力。RESETピンが禁止されていなければ、例えクロックが走行していなくても、最小パルス幅より長いこのピンのLowレヘブルはリセットを生成します。最小パルス幅は109頁の表20-4.で与えられます。より短いパルスはリセットの生成が保証されません。

RESETピンは((駆動能力の)弱い)入出力ピンとしても使えます。

### 1.1.4. PA7~PA0 (ホ°ートA)

ポートAは(ビット単位で選択される)内蔵プルアップ抵抗付きの8ビット双方向入出力ポートです。ポートA出力緩衝部は共に高い吐き出し/吸い込み能力の対称駆動特性です。入力のとき、プルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートAピンには吐き出し電流が流れます。 リセット条件が有効になると、クロックが走行していなくても、ポートAピンはHi-Zにされます。

ポートAには34頁の「**交換ポート機能**」で示されるようにA/D変換器とアナログ比較器用のアナログ入力とピン変化割り込みとしての交換機能があります。

### **1.1.5**. PB3~PB0 (本°一トB)

ポートBは(ビット単位で選択される)内蔵プルアップ抵抗付きの4ビット双方向入出力ポートです。ポートB出力緩衝部は共に高い吐き出し/吸い込み能力の対称駆動特性です。入力のとき、プルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートBピンには吐き出し電流が流れます。リセット条件が有効になると、クロックが走行していなくても、ポートBピンはHi-Zにされます。

ポートBには34頁の「交換ポート機能」で示されるようにA/D変換器用のアナロゲ入力とピン変化割り込みとしての交換機能があります(記主:整合性から本行追加)。

ポートBは38頁で一覧されるように、ATtiny40の様々な特殊機能も扱います。

#### **1.1.6. PC5~PC0** (ホートC)

ポートCは(ビット単位で選択される)内蔵プルアップ抵抗付きの6ビット双方向入出力ポートです。RESET能力を持つPC3を除いて、ポートC出力緩衝部は共に高い吐き出し/吸い込み能力の対称駆動特性です。PC3ピンをRESETの代わりにI/Oピンとして使うには、RSTDISBL ヒュース'をプログラム(0)にしてください。入力のとき、プルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートCピンには吐き出し電流が流れます。リセット条件が有効になると、クロックが走行していなくても、ポートCピンはHi-Zにされます。

ポートCには34頁の「**交換ポート機能**」で示されるようにピン変化割り込みとしての交換機能があります(<mark>訳注</mark>:整合性から本行修正)。 ポートCは39頁で一覧されるように、ATtiny40の様々な特殊機能も扱います。

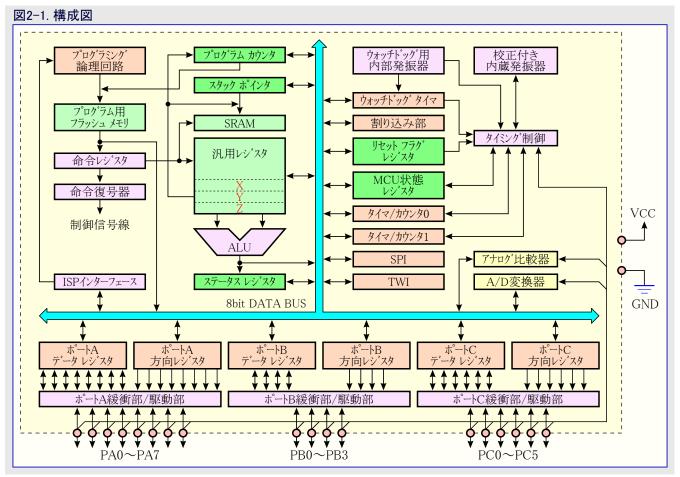

# 2. 概要

ATtiny40はAVR強化RISC構造を基にした低消費CMOS 8ビットマイクロコントローラです。1周期での強力な命令の実行によってATtiny40はMHzあたり1MIPSに達する単位処理量を成し遂げ、処理速度対消費電力の最適化を設計者に許します。

AVRコアは16個の汎用作業レジスタを伴う豊富な命令群とシステム レジスタを結合します。全レジスタはALU(Arithmetic Logic Unit)に直結され、1クロック周期で実行される単一命令でのアクセスを2つの独立したレジスタに許します。その結果としての基本構造は簡潔且つコート、効率的で、同時に伝統的なCISC型マイクロコントローラに対して10倍程度までの処理量を達成します。

ATtiny40は4Kハ、イトの実装書き込み可能なフラッシュメモリ、256ハ、イトのSRAM、18本の汎用入出力線、16個の汎用作業レシ、スタ、2つのPWMチャネルを持つ8ビットタイマ/カウンタ、8/16ビットタイマ/カウンタ、内部及び外部割り込み、8チャネルの10ビットA/D変換器、内蔵発振器付きの設定変更可能なウォッチドッグ。タイマ、従装置2線インターフェース、主装置/従装置の直列周辺インターフェース、校正付き内蔵発振器、ソフトウェアで選択できる4つの低消費動作を提供します。

アイドル動作はCPUを停止し、一方、タイマ/カウンタ、A/D変換器、アナログ比較器、割り込み機構に機能の継続を許します。A/D変換雑音低減動作はA/D変換器を除く全I/O部とCPUを停止することによってA/D変換中の切り替え雑音を最小にします。パワーダウン動作ではレジ、スタがそれらの内容を保ち、次の割り込みかハードウェアリセットまで、全てのチップ機能が禁止されます。スタンハイ動作ではデバイスの残りが休止する一方で発振器が走行し、低消費電力と組み合わされた非常に速い始動を許します。

本ディーイスはAtmelの高密度不揮発性メモリ技術を使って製造されます。チップ上の実装書き換え可能なフラッシュメモリは伝統的な不揮発性メモリ書き込み器による実装書き換えをプログラム用メモリに許します。

ATtiny40 AVRはマクロ アセンフ・ラと評価キットを含む完全なプログラム及びシステム開発ツールの1式によって支援されます。

# 3. 一般情報

# 3.1. 資料

包括的なデータシート、応用記述、トライハ、群と開発ツールの説明はhttp://www.atmel.com/avrでのダウンロートで利用可能です。

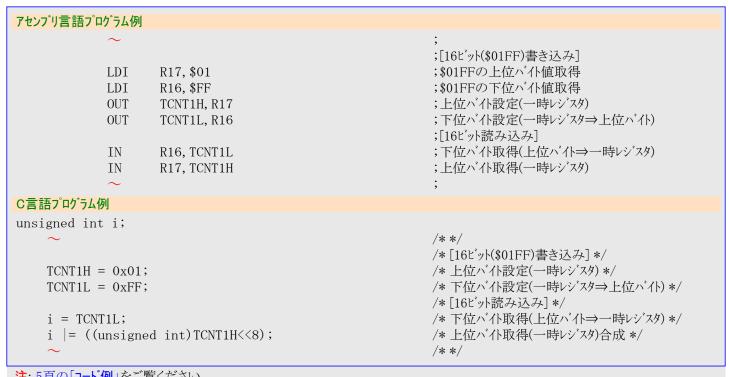

# 3.2. コート 例

この資料はデバイスの様々な部分の使用法を手短に示す簡単なコート・例を含みます。これらのコート・例はアセンブルまたはコンパイルに先立って、デバイス定義へッタ・ファイルがインクルートされると仮定します。全てのCコンパイラ製造業者がヘッタ・ファイル内にヒット定義を含めるとは限らず、またCでの割り込みの扱いがコンパイラに依存することに注意してください。より多くの詳細についてはCコンパイラの資料で確認してください。

# 3.3. 容量性接触感知

Atmel QTouchライブラリはAtmel AVRマイクロコントローラ上の接触感知インターフェースのための使い易い解決策を提供します。QTouchライブラリはQTouch®とQMatrix®採取法用の支援を含みます。

接触感知は接触チャネルと感知器を定義することで応用プログラミングインターフェース(API)を用いてQTouchライブラリをリンクすることによってどの応用にも容易に追加されます。そして応用はチャネル情報を取得して接触感知器の状態を決めるためにAPIを呼び出します。

QTouchライフ・ラリは無料でAtmelのウェフ・サイトからダウンロート・することができます。より多くの情報と実装の詳細についてはAtmelのウェフ・サイトからも入手可能なQTouchライフ・ラリ使用者の手引きを参照してください。

# 3.4. データ保持力

信頼性証明結果はデータ保持誤り率の反映を示し、20年以上/85℃または100年以上/25℃で1PPMよりずっと小さな値です。

# 3.5. お断り

本データシート内に含まれる代表値はシミュレーションと同じ製法技術で製造された他のAVRマイクロ コントローラの特性を基にしています。

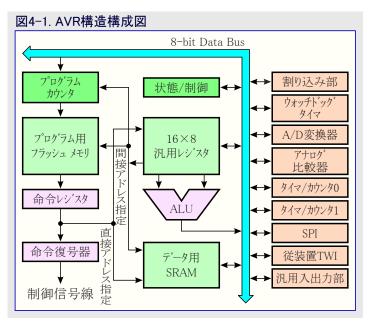

# 4. CPU コア

本項はAVRコア構造を一般的に説明します。このCPUコアの主な機能は正しいプログラム実行を保証することです。従ってCPUはメモリアクセス、計算実行、周辺制御、割り込み操作ができなければなりません。

# 4.1. 構造概要

最大効率と平行処理のため、AVRはプログラムとデータに対してメモリとハンスを分離するハーハート・構造を使います。プログラムメモリ内の命令は単一段のハーイプラインで実行されます。1命令の実行中に次の命令がプログラムメモリから事前取得されます。この概念は全部のクロック周期で命令実行を可能にします。プログラムメモリは実装書き換え可能なフラッシュメモリです。

高速レジスタファイルは1クロック周期アクセスの16個の8ビット長汎用レジスタを含みます。これは1クロック周期ALU(Arithmetic Logic Unit)操作を許します。代表的なALU操作では2つのオペラントがレジスタファイルからの出力で、1クロック周期内でその操作が実行されてその結果がレジスタファイルに書き戻されます。

16個中の6つのレジスタは効率的なアトレス計算ができるデータ空間アトレス指定用に3つの16ビット長間接アトレスポインタ用レジスタとして使われます。これらの16ビット長付加機能レジスタはX,Y,Zレジスタで、本項内で後述されます。

ALUはレシ、スタ間またはレシ、スタと定数間の算術及び論理操作を支援します。単一レシ、スタ操作もALUで実行できます。算術演算操作後、操作結果についての情報を反映するために、ステータスレジ、スタ (SREG)が更新されます。

プログラムの流れは条件/無条件分岐や呼び出し命令によって提供され、全アトンス空間を直接アトンス指定する能力があります。 殆どの AVR命令は単一16ビット語(ワード)形式ですが、32ビット幅の命令も存在します。 実際の命令一式はいくつかのデバイスが(全)命令一式の 部分だけを実装するように変わります。

割り込みやサブルーチン呼び出し中、戻りアトレスを示すプログラム カウンタ(PC)はスタックに保存されます。スタックは一般的なデータ用SRAM上に実際には割り当てられ、従ってスタック容量はSRAM容量とSRAM使用量でのみ制限されます。全ての使用者プログラムはリセット処理ルーチンで(サブルーチン呼び出しや割り込みが実行される前に)、スタック ポインタ(SP)を初期化しなければなりません。SPはI/O空間で読み書きアクセスが可能です。データ用SRAMはAVR構造で支援される4つの異なるアトレス指定種別を通して容易にアクセスできます。

AVR構造に於けるメモリ空間は全て直線的な普通のメモリ配置です。

柔軟な割り込み部にはI/O空間の各制御レシ、スタとステータスレシ、スタ(SREG)の特別な全割り込み許可(I)ビットがあります。全ての割り込みは割り込みへ、クタ表に個別の割り込みへ、クタを持ちます。割り込みには割り込みへ、クタ表の位置に従う優先順があります。下位側割り込みへ、クタアドレスが高い優先順位です。

I/Oメモリ空間は制御レジスタや他のI/O機能としてCPU周辺機能用の64アドレスを含みます。I/Oメモリはデータ空間位置\$0000~\$003Fとしてアクセスできます。

### **4.2. ALU** (Arithmetic Logic Unit)

高性能なAVRのALUは16個全ての汎用レシ、スタに直接接続され動作します。汎用レジ、スタ間または汎用レシ、スタと即値間の演算操作は単一クロック周期内で実行されます。ALU操作は算術演算、論理演算、ビット操作の3つの主な種類に大別されます。符号付きと符号なし両方の乗算と固定小数点形式を支援する乗算器(乗算命令)も提供する構造の実装(製品)もあります。詳細記述については「AVR命令1式」資料と133頁の「命令要約」章をご覧ください。

#### 4.3. ステータス レジスタ

ステータス レジスタは最も直前に実行した演算命令の結果についての情報を含みます。この情報は条件処理を行うためのプログラムの流れ変更に使えます。ステータス レジスタは「AVR命令一式」資料と133頁の「命令要約」章で詳述したように、全てのALU操作後、更新されることに注目してください。これは多くの場合でそれ用の比較命令使用の必要をなくし、高速でより少ないコードに帰着します。

ステータス レシ、スタは割り込み処理ルーチン移行時の保存と割り込みからの復帰時の回復(復帰)が自動的に行われません。これはソフトウェアによって扱われなければなりません。

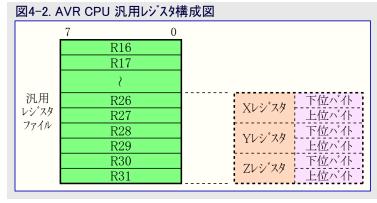

# 4.4. 汎用レジスタファイル

このレジスタファイルはAVRの増強したRISC命令群用に最適化されています。必要な効率と柔軟性を達成するために、次の入出力機構がレシ、スタファイルによって支援されます。

- ・1つの8ビット出力オペランドと1つの8ビットの結果入力

- ・2つの8ビット出力オペランドと1つの8ビットの結果入力

- ・1つの16ビット出力オペラントと1つの16ビットの結果入力

右の図4-2.はCPUに於ける16個の汎用作業レジスタ構造を示します。

注: AVRレシ、スタファイルの代表的な実装は32個の汎用レシ、スタを含みますが、ATtiny40は16個のレシ、スタだけを実装します。 互換性のため、レシ、スタはR0~R15ではなく、R16~R31で番号付けされます。

レジスタファイルを操作する殆どの命令は全てのレジスタに直接アクセスし、それらの殆どは単一クロック周期命令です。

## 4.4.1. Xレシ、スタ、Yレシ、スタ、Zレシ、スタ

R26~R31レジスタには通常用途の使用にいくつかの追加機能があります。これらのレジスタはデータ空間の間接アドス指定用の16 ビットアドレス ホーインタです。3つのX,Y,Z間接アドレス レジスタは図4-3.で記載したように定義されます。

種々のアドレス指定種別で、これらのアドレスレジスタは自動増加、 自動減少としての機能を持ちます(詳細については「AVR命令 一式」資料と133頁の「命令要約」章をご覧ください)。

| 図4-3. X,Y,Z | 図4−3. X,Y,Zレジスタ構成図 |            |     |            |    |  |  |  |  |

|-------------|--------------------|------------|-----|------------|----|--|--|--|--|

|             | 15                 | XH (上位)    |     | XL (下位)    | 0_ |  |  |  |  |

| X レジスタ      | 7                  | R27 (\$1B) | 0 7 | R26 (\$1A) | 0  |  |  |  |  |

|             | 15                 | YH (上位)    |     | YL (下位)    | 0_ |  |  |  |  |

| Y レジスタ      | 7                  | R29 (\$1D) | 0 7 | R28 (\$1C) | 0  |  |  |  |  |

|             | 15                 | ZH (上位)    |     | ZL (下位)    | 0  |  |  |  |  |

| Z レジスタ      | 7                  | R31 (\$1F) | 0 7 | R30 (\$1E) | 0  |  |  |  |  |

# 4.5. スタック ホペインタ

スタックは主に一時データの保存、局所変数の保存、割り込みとサブルーチン呼び出し後の戻りアドレスの保存に使われます。スタック ポインタ レジスタ(SPHとSPL)は常にこのスタックの先頭(<mark>訳注</mark>:次に使われるべき位置)を指し示します。スタックが高位メモリから低位メモリへ伸びることに注意してください。これはPUSH命令がスタック ポインタ値を減らし、POP命令が増すという意味です。

スタック ポインタはサブルーチンや割り込みのスタックが配置されるデータ メモリの領域を指し示します。このスタック空間はサブルーチン呼び出しの実行や割り込みの許可の何れにも先立って、プログラムによって定義されなければなりません。

このポインタはPUSH命令でデータがスタックに置かれる時に-1され、POP命令でデータが取得される時に+1されれます。これはサブルーチン呼び出しや割り込み処理ルーチンへ飛ぶことによって戻りアトレスがスタックに置かれる時に-2され、サブルーチンからの復帰(RET命令)や割り込みからの復帰(RETI命令)によって戻りアトレスががスタックから取得される時に+2されます。

AVRのスタック ポインタは代表的にI/O空間内の2つの8ビット レジ スタとして実装されます。 スタック ポインタの幅と実装されるビット数はデバイス 依存です。 いくつかのAVRデバイスではSPLだけを用いて全てのデータ メモリをアドレス指定することができます。 その場合、SPHレジ スタは 実装されません。

スタック ポインタはI/Oレジスタ領域(SRAMの最低アドレスである最小値)以上を指示するように設定されなければなりません。11頁の**図5-1**. をご覧ください。

# 4.6. 命令実行タイミング

本項は命令実行の一般的なアクセス タイミング の概念を記述します。AVR CPUはチップ(デバイス)用に選択したクロック元から直接的に生成したCPUクロック(clkCPU)によって駆動されます。内部クロック分周は使われません。

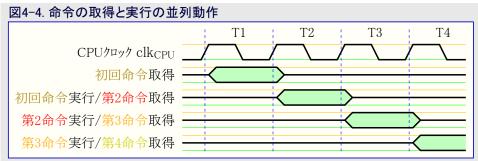

図4-4.はハーハート・構造と高速アクセスレジスタファイルの概念によって可能とされる並列の命令取得と命令実行を示します。これは機能対費用、機能対クロック、機能対電源部に関する好結果と対応するMHzあたり1MIPSを達成するための基本的なパイプラインの概念です。

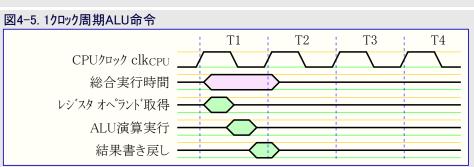

図4-5.はレシ、スタファイルに対する内部タイミングの概念を示します。単一クロック周期で2つのレシ、スタオペ。ラント、を使うALU操作が実行され、その結果が転送先レジ、スタへ書き戻されます。

# 4.7. リセットと割り込みの扱い

AVRは多くの異なる割り込み元を提供します。これらの割り込みと独立したリセット ベクタ各々はプログラム メモリ空間内に独立したプログラム ベクタを持ちます。全ての割り込みは割り込みを許可するために、ステータス レジスタ(SREG)の全割り込み許可(I)ビットと共に論理1が書かれなければならない個別の許可ビットを割り当てられます。

既定でのプログラムメモリ空間の最下位アトンスはリセットと割り込みのベクタとして定義されます。ベクタの完全な一覧は27頁の「割り込み」で示されます。この一覧は各種割り込みの優先順位も決めます。下位側アトンスがより高い優先順位です。リセットが最高優先順位で、次が外部割り込み要求の(INTO)です。

割り込みが起こると全割り込み許可(I)ビットが解除(0)され、全ての割り込みは禁止されます。使用者ソフトウェアは多重割り込みを許可するため、全割り込み許可(I)ビットへ論理1を書けます。その後全ての許可した割り込みが現在の割り込みルーチンで割り込めます。全割り込み許可(I)ビットは割り込みからの復帰(RETI)命令が実行されると、自動的に設定(1)されます。

根本的に2つの割り込み形式があります。1つ目の形式は割り込み要求フラグを設定(I)する事象によって起動されます。これらの割り込みでは割り込み処理ルーチンを実行するために、プログラム カウンタは対応する現実の割り込みへ、クタを指示し、ハートウェアが対応する割り込み要求フラグを解除(0)します。割り込み要求フラグは解除(0)されるべきフラグのビット位置へ論理1を書くことによっても解除(0)できます。対応する割り込み許可ビットが解除(0)されている間に割り込み条件が起こると、割り込み要求フラグが設定(1)されて割り込みが許可されるか、またはこのフラグがソフトウェアによって解除(0)されるまで記憶(保持)されます。同様に、全割り込み許可(I)ビットが解除(0)されている間に1つまたはより多くの割り込み条件が起こると、対応する割り込み要求フラグが設定(1)されて全割り込み許可(I)ビットが設定(1)されるまで記憶され、その(I=1)後で優先順に従って実行されます。

2つ目の割り込み形式は割り込み条件が存在する限り起動し(続け)ます。これらの割り込みは必ずしも割り込み要求フラグを持っているとは限りません。割り込みが許可される前に割り込み条件が消滅すると、この割り込みは起動されません。

AVRが割り込みから抜け出すと常に主プログラムへ戻り、何れかの保留割り込みが扱われる前に1つ以上の命令を実行します。

ステータス レジスタ(SREG)は割り込みルーチンへ移行時の保存も、復帰時の再設定も自動的に行われないことに注意してください。これはソフトウェアによって扱われなければなりません。

割り込みを禁止するためにCLI命令を使うと、割り込みは直ちに禁止されます。CLI命令と同時に割り込みが起こっても、CLI命令後に割り込みは実行されません。

割り込みを許可するためにSEI命令を使うと、次例で示されるようにどの保留割り込みにも先立ってSEI命令の次の命令が実行されます。

### アセンブリ言語プログラム例

SEI ;全割り込み許可

SLEEP ;休止形態動作移行(移行後に割り込み待ち)

**注**: 5頁の「**コート** 例」をご覧ください。

#### 4.7.1. 割り込み応答時間

許可した全てのAVR割り込みに対する割り込み実行応答は最小4クロック周期です。4クロック周期後、実際の割り込み処理ルーチンに対するプログラム ベクタ アドレスが実行されます。この4クロック周期間にプログラム カウンタ(PC)がスタック上に保存(プッシュ)されます。このベクタは標準的に割り込み処理ルーチンへの無条件分岐で、この分岐は2クロック周期(訳注:原文は3(JMP命令=3を想定、実際はRJMP命令=2))要します。複数周期命令実行中に割り込みが起こると、その割り込みが扱われる前に、この命令が完了されます。MCUが休止形態動作の時に割り込みが起こると、割り込み実行応答時間は4クロック周期、増やされます。この増加は選択した休止形態動作からの起動時間に加えてです。

割り込み処理ルーチンからの復帰は4クロック周期要します。これらの4クロック周期中、プログラムカウンタ(PC:2バイト)がスタックから取り戻され(ポッ プ)、スタック ポインタは増加され(+2)、ステータス レシ、スタ(SREG)の全割り込み許可(I)ビットが設定(1)されます。

# 4.8. コア関係レジスタ

# 4.8.1. CCP - 構成設定変更保護レジスタ (Configuration Change Protection Register)

| ピット        | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0     |     |

|------------|-------|---|---|---|---|---|---|-------|-----|

| \$3C       | (MSB) |   |   |   |   |   |   | (LSB) | CCP |

| Read/Write | W     | W | W | W | W | W | W | R/W   |     |

| 初期値        | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |     |

### ● ビット7~0 - CCP7~0:構成設定変更保護 (Configuration Change Protenction)

保護されたI/Oレジスタの内容を変更するため、CCPレジスタは最初に正しい識票を書かれなければなりません。CCPが書かれた後、保護されたI/Oレジスタは次からの4CPU命令周期中に書けます。これらの周期中は全ての割り込みが無視されます。これらの周期後に割り込みはCPUによって自動的に再び取り扱われて、どの保留割り込みもそれらの優先権に従って実行されます。

保護されたI/Oレジスタの識票が書かれると、CCP0は保護機能が許可されている限り1として読めます。CCP7~1は常に0として読めます。

表4-1.は認証に於ける識票を示します。

### 表4-1. 構成設定変更保護レジスタによって認証される識票

| ĺ | 識票   | 適用群                                            | 説明           |

|---|------|------------------------------------------------|--------------|

|   | \$D8 | IOREG: CLKMSR, CLKPSR, WDTCSR (注1), MCUCR (注2) | 保護されたI/Oレジスタ |

注1: WDTCSRではWDEとWDP3~0のビットだけが保護されます。

注2: MCUCRではBODSビットだけが保護されます。

# 4.8.2. SPL (SP) - スタック ホーインタ (Stack Pointer)

| ピット        | 15     | 14     | 13     | 12     | 11     | 10     | 9      | 8      |     |

|------------|--------|--------|--------|--------|--------|--------|--------|--------|-----|

| \$3E       | -      | -      | -      | -      | -      | -      | -      | -      | SPH |

| Read/Write | R      | R      | R      | R      | R      | R      | R      | R      |     |

| 初期値        | RAMEND |     |

| ピット        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |     |

| \$3D       | SP7    | SP6    | SP5    | SP4    | SP3    | SP2    | SP1    | SP0    | SPL |

| Read/Write | R/W    |     |

| 初期値        | RAMEND |     |

|            |        |        |        |        |        |        |        |        |     |

### • ビット7~0 - SP7~0: スタック ポインタ (Stack Pointer)

スタック ポインタ レジ スタは上位メモリ位置から下位メモリ位置へ大きくなるように実装されるスタックの先頭を指示します。従って、スタックPUSH 命令はスタック ポインタを減少(-1)します。SRAM内のスタック空間はどのサブルーチン呼び出しの実行や割り込みが許可されるのにも先立ってプログラムによって定義されなければなりません。

ATtiny40のスタック ポーインタはI/O空間内の2つの8ビット レジスタとして実装されています。

## 4.8.3. SREG - ステータス レジスタ (Status Register

| ピット        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _    |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$3F       | I   | Т   | Н   | S   | V   | N   | Z   | С   | SREG |

| Read/Write | R/W |      |

| 初期値        | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

### ● ビット7 - I: 全割り込み許可 (Global Interrupt Enable)

割り込みが許可されるには全割り込み許可ビットが設定(1)されなければなりません。その時の個別割り込み許可制御は独立した制御レジスタで行われます。全割り込み許可ビットが解除(0)されると、個別割り込み許可設定に拘らず、どの割り込みも許可されません。Iビットは割り込みが起こった後にハートウェアによって解除(0)され、後続の割り込みを許可するため、RETI命令によって設定(1)されます。Iビットは「AVR命令一式」資料と133頁の「命令要約」章で記述されるようにSEIやCLI命令で応用(プログラム)によって設定(1)や解除(0)もできます。

### ● ビット6 - T: ビット変数 (Bit Copy Storage)

ビット複写命令、BLD(Bit LoaD)とBST(Bit STore)は操作したビットの転送元または転送先として、このTビットを使います。レジスタ ファイルのレジスタからのビットはBST命令によってTに複写でき、TのビットはBLD命令によってレジスタ ファイルのレジスタ内のビットに複写できます。

#### • ビット5 - H: ハーフキャリー フラク (Half Carry Flag)

ハーフキャリー(H)フラグはいくつかの算術操作でのハーフキャリーを示します。ハーフキャリーはBCD演算に有用です。詳細情報については「AVR 命令一式」資料と100頁の「命令要約」項をご覧ください。

# ● ビット4 - S: 符号 (Sign Bit, S= N Ex-OR V)

Sフラグは常に負(N)フラグと2の補数溢れ(V)フラグの排他的論理和です。詳細情報については、「AVR命令一式」資料と100頁の「命令要約」項をご覧ください。

## ● ビット3 - V: 2の補数溢れフラグ(2's Complement Overflow Flag)

2の補数溢れ(V)フラグは2の補数算術演算を支援します。詳細情報については「AVR命令一式」資料と100頁の「命令要約」項をご覧ください。

#### ビット2 - N: 負フラク (Negative Flag)

負(N)フラケ は算術及び論理操作での負の結果(MSB=1)を示します。詳細情報については「AVR命令一式」資料と100頁の「命令要約」項をご覧ください。

#### ヒット1 - Z: セロフラケ (Zero Flag)

ゼロ(Z)フラグは算術及び論理操作でのゼロ(0)の結果を示します。詳細情報については「AVR命令一式」資料と100頁の「命令要約」項をご覧ください。

#### ヒット0 - C: キャリー フラク゛(Carry Flag)

キャリー(C)フラグは算術及び論理操作でのキャリー(またはボロー)を示します。詳細情報については「AVR命令一式」資料と100頁の「命令要約」項をご覧ください。

# 5. メモリ

この項はATtiny40の各種メモリを記述します。本デバイスにはプログラム メモリ空間とデータ メモリ空間の2つの主なメモリ空間があります。

# 5.1. 実装書き換え可能なプログラム用フラッシュ メモリ

ATtiny40はプログラム保存用に実装書き換え可能な4Kバイトのフラッシュメモリをチップ上に含みます。全てのAVR命令が16または32ビット幅のため、このフラッシュメモリは2048×16ビットとして構成されます。

フラッシュ メモリは最低10,000回の消去/書き込み周回の耐久性があります。ATtiny40のプログラム カウンタ(PC)は11ビット幅、従って\$0000から始まる2048プログラム メモリ位置をアトレス指定する能力があります。102頁の「メモリプログラミング」はフラッシュ メモリの(TPI)直列プログラミングの詳細な記述を含みます。

定数表は全てのプログラム メモリ アトレス空間に配置できます。プログラム メモリが直接アクセスできないため、これはデータ メモリに割り当てられています。割り当てられたプログラム メモリはデータ メモリのハイト アトレス\$4000から始まります(図5-1.をご覧ください)。

プログラム用フラッシュ メモリへの内部的な書き込みは禁止され、従ってプログラム メモリはファームウェアに対して読み込み専用として見えます。フラッシュ メモリは未だ外部的に書けますが、プログラム用メモリ空間に対する内部的な書き込み操作は成功しません。

命令の取得と実行のタイミング図は8頁の「命令実行タイミング」で示されます。

# 5.2. データ メモリ

データ メモリはI/Oメモリ、内部SRAM、不揮発性メモリ施錠ビット、フラッシュ メモリを含みます。 ATtiny40のメモリ空間がどう構成されるかの図解については図5-1.をご覧ください。

最初の64位置はI/Oメモリ用に予約され、一方後続する256データ メモリ位置(\$0040~\$01 3F)はデータ用内部SRAMをアドレス指定します。

不揮発性メモリ施錠ビットと全てのフラッシュ メモリ領域がデータ メモリ空間に割り当てられています。これらの位置はデバイスのファームウェアに関して読み込み専用として見えます。

データ メモリ用の4つの異なるアトンス指定形態は、直接、間接、事前減少付き間接、事後増加付き間接です。レジスタ ファイル内のレジスタR26~R31は間接アトンス指定ポインタ用レジスタとして機能します。

INとOUTの命令はI/Oメモリの64位置全てをアクセスできます。LDSとSTSの命令を用いる直接アドレス指定は\$0040~\$00BF間の最下位128位置に届きます。

間接アトンス指定はデータ空間全体に届きます。自動の事前減少付きと事後増加付きのレシ、スタ間接アトンス指定動作を使う時に(使われた)X,Y,Zアトンスレシ、スタが減少(-1)または増加(+1)されます。

# 5.2.1. データ メモリ アクセス タイミング

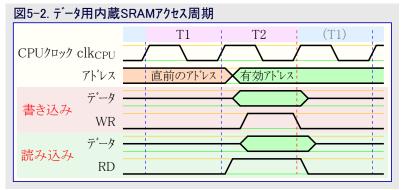

この項は内部メモリ アクセスに対する一般的なアクセス タイミングの概念を記述します。 データ用内蔵SRAMアクセスは**図5-2**.で記載されるように2clk<sub>CPU</sub>周期で実行されます。

(訳注) 内蔵SRAMのアクセスを含む代表的な命令はT1,T2の 2周期で実行され、T1で対象アトレスを取得/(算出)/ 確定し、T2で実際のアクセスが行われます。後続する (T1)は次の命令のT1です。

#### 5.2.2. 内部SRAM

内部SRAMはアドレス\$0040から始まるデータメモリ空間に配置されます。SRAMは直接アドレス指定、またはRAMインターフェースを用いることによってCPUからアクセスされます。レジスタのR26~R31は間接アドレス指定に対するポインタレジスタとして機能します。間接アドレス指定に関連してポインタの事前減少(-1)と事後増加(+1)も支援されます。LDSとSTSの命令を用いる直接アドレス指定は\$0040~\$00BF間の最下位128位置にだけ届きます。先頭の128小、仆を超える\$00C0~\$013F間の位置は間接アドレス指定形態(LDとSTの命令)またはRAMインターフェース経由のどちらかを用いてアクセスされなければなりません。

\*\*00FE\*\*\*

使用者はRAMインターフェース使用時にRAMのアドレス指定に特段の注意を払わなければなりません。直接と間接のアドレス指定形態は仮想RAMアドレスを使いますが、RAMインターフェースは物理RAMアドレスを用います。仮想RAMアドレス空間の物理アドレスへの配置は表5-1.で記載されます。

例えば、仮想RAMアトンス \$0100(STSまたはST命令)を用いてRAMにデータが書かれる場合に、それは物理RAMアトンス \$0000に割り当てられます。従ってRAMインターフェース経由で同じデータ位置が読み戻される時に、RAMアトンス レジスタ(RAMAR)へ物理アトンス \$0000が書かれなければなりません。他方、直接または間接のアトンス指定形態(LDSまたはLD命令)を用いて同じデータ位置が読み戻されるなら、同じ仮想RAMアトンス \$0100が用いられます。

| 表5-1. SRAW/アレス | (全间       |

|----------------|-----------|

| 仮想RAMアドレス      | 物理RAMアドレス |

| \$0040         | \$0040    |

| \$0041         | \$0041    |

| }              | >         |

| \$00FE         | \$00FE    |

| \$00FF         | \$00FF    |

| \$0100         | \$0000    |

| \$0101         | \$0001    |

| }              | >         |

| \$013E         | \$003E    |

| \$013F         | \$003F    |

#### 5.2.3. RAMインターフェース

RAMインターフェースはRAMアト・レス レン・スタ(RAMAR)とRAMデータ レシ・スタ(RAMDR)の2つのレン・スタから成ります。これらのレシ・スタはI/O空間でアクセス可能です。

或る位置を書くために、使用者は最初にRAMアドレスをRAMARに、その後にデータをRAMDRに書かなければなりません。RAMDRへのデータ書き込みが書き込み動作を起動し、同じ命令周期内でRAMARによって与えられたアドレスのRAMに転送元レジスタからのデータが書かれます。

或る位置を読むために、使用者は最初にRAM7ドレスをRAMARに、その後にRAMDRからデータを読まなければなりません。RAMDRからのデータ読み込みが読み込み動作を起動し、同じ命令周期内でRAMARによって与えられたアドレスのRAMからのデータが取得されて転送先レジスタに書かれます。

```

アセンブリ言語プログラム例

RAM_WR:

OUT

RAMAR, R17

;RAMアトレスレシ、スタにアトレス(R17)設定

OUT

RAMDR, R16

;RAMデータレシ、スタにデータ(R16)設定

RET

;呼び出し元へ復帰

;RAMアドレスレシ、スタにアドレス(R17)設定

OUT

RAM RD:

RAMAR, R17

;RAMデータレシ、スタからデータ(R16)取得

ΙN

R16, RAMDR

RET

;呼び出し元へ復帰

C言語プログラム例

void RAM_write( unsigned char ucAddress, unsigned char ucData )

/* RAMアドレス レジスタにアドレス設定 */

RAMAR = ucAddress;

RAMDR = ucData;

/* RAMデータ レシ スタにデータ設定 */

void RAM_read( unsigned char ucAddress, unsigned char ucData )

RAMAR = ucAddress;

/* RAMアトレス レシ スタにアトレス設定 */

ucData = RAMDR;

/* RAMデータレジスタからデータ取得 */

```

# 5.3. I/O メモリ (レシ スタ)

ATtiny40のI/O空間定義は132頁の「レジスタ要約」で示されます。

ATtiny40の全てのI/Oと周辺機能はI/O空間に配置されます。全てのI/O位置はI/O空間と16個の汎用作業レジスタ間のデータ転送を行うLDとSTの命令によってアクセスできます。アドレス範囲\$00~\$1F内のI/OレジスタはSBI命令とCBI命令を使って直接的にビットアクセスが可能です。これらのレジスタではSBISとSBIC命令の使用によって単一ビット値が検査できます。より多くの詳細については「AVR命令一式」資料と133頁の「命令要約」章をご覧ください。I/O指定命令INとOUTを使う時はI/Oアドレス\$00~\$3Fが使われなければなりません。

将来のデバイスとの共通性を保つため、アクセスされる場合、予約ビットはOが書かれるべきです。予約済みI/Oメモリ アドレスは決して書かれるべきではありません。

状態フラグのいくつかはそれらへ論理1を書くことによって解除(0)されます。CBIとSBI命令は指定ビットだけを操作し、従って状態フラグのようなものを含むレジスタに使えることに注意してください。CBIとSBI命令は(I/Oアドレス)\$00~\$1Fのレジスタでのみ動作します。 I/Oと周辺制御レジスタは以降の項で説明されます。

# 5.4. RAMインターフェース用レジスタ

## 5.4.1. RAMAR - RAMアトレス レシ スタ (RAM Address Register)

| ピット        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

| \$20       | RAMAR7 | RAMAR6 | RAMAR5 | RAMAR4 | RAMAR3 | RAMAR2 | RAMAR1 | RAMAR0 | RAMAR |

| Read/Write | R/W    |       |

| 初期値        | 不定     |       |

#### ヒット7~0 - RAMAR7~0: RAMプトレス (RAM Address)

RAMARレシ、スタはRAMアト、レス ヒットを含みます。RAMデータ ハ・イトは0~255の範囲で一直線にアトンス指定されます。RAMARの初期値は不定で、従ってRAMがアクセスされ得る前に正しい値が書かれなければなりません。

# 5.4.2. RAMDR - RAMデータレジスタ (RAM Data Register)

| ピット        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

| \$1F       | RAMDR7 | RAMDR6 | RAMDR5 | RAMDR4 | RAMDR3 | RAMDR2 | RAMDR1 | RAMDR0 | RAMDR |

| Read/Write | R/W    |       |

| 初期値        | 不定     |       |

#### ヒット7~0 - RAMDR7~0: RAMデータ (RAM Data)

RAM書き込み操作に関し、RAMDRレシ、スタはRAMARレシ、スタによって与えられたアドレスのRAMに書かれるべきRAMデータを含みます。 RAM読み込み操作について、RAMDRはRAMARレシ、スタによって与えられたアドレスのRAMから読み出したデータを含みます。

# 6. クロック体系

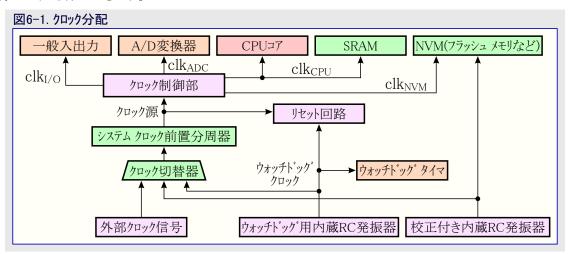

図6-1.はATtiny40に於ける主要なクロック系統とその配給を示します。全てのクロックが与えられた時間有効である必要はありません。消費電力低減のため、18頁の「電力管理と休止形態動作」で記述される各種休止形態動作と電力削減レジスタ ビットの使用により、使われていない部分のクロックを停止できます。

## 6.1. クロック副系統

クロック副系統が以下の項目で詳述されます。

# 6.1.1. CPU クロック - clk<sub>CPU</sub>

CPUクロックはAVRコアの動作と関係する系統部分に配給されます。このような部分の例はシステムレジスタとデータ用SRAMメモリです。CPUクロックの停止はコアが一般的な操作や計算を実行することを禁止します。

### 6.1.2. I/O クロック - clk<sub>I/O</sub>

I/Oクロックはタイマ/カウンタのようなI/O部の大部分で使われます。I/Oクロックは外部割り込み部でも使われますが、いくつかの外部割り込みは例えI/Oクロックが停止されても検出されることをこのような割り込みに許す非同期論理回路によって検出されることに注意してください。

#### 6.1.3. NVMクロック - clk<sub>NVM</sub>

NVMクロックは不揮発性メモリ(NVM)制御部の動作を制御します。NVMクロックは通常CPUクロックと同時に活動します。

### 6.1.4. A/D変換クロック - clk<sub>ADC</sub>

A/D変換器には専用のクロック範囲が提供されます。これはデジタル回路によって生成される雑音を低減するためにCPUとI/Oクロックの停止を許します。これはより正確なA/D変換結果を与えます。

### 6.2. クロック元

全ての同期クロック信号は主クロックから配給されます。デバイスは主クロックに関して次のような3つの切り替え供給元を持ちます。

- ・校正付き8MHz内蔵発振器

- ・ 外部クロック信号

- ・128kHz内部発振器 (15頁をご覧ください。)

活動するクロック元を変更して選択する方法は16頁の表6-3.をご覧ください。

# 6.2.1. 校正付き8MHz内蔵発振器

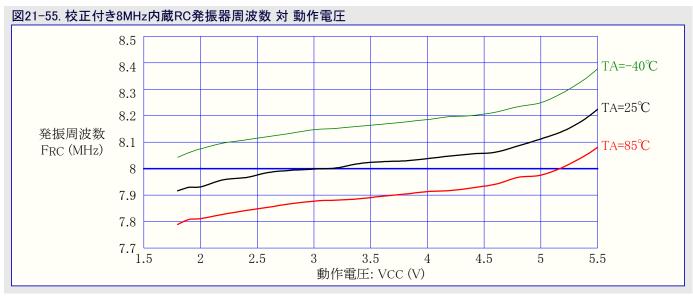

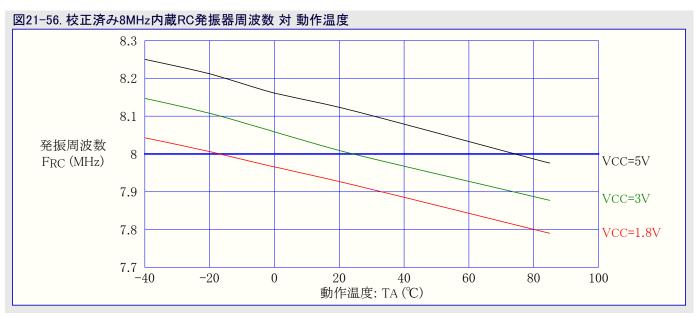

校正された内蔵RC発振器は概ね8MHzのクロック信号を提供します。電圧と温度に依存しますが、このクロックは使用者によって高精度な校正ができます。より多くの詳細については109頁の表20-2.と130頁の「内部発振器周波数」をご覧ください。

このクロックはクロック主設定レシ、スタ(CLKMSR)のクロック主選択(CLKMS1,0)ピットを00に設定することによって主クロックとして選択できます。一旦許可されると、発振器は外部部品なしで動作します。リセット中、ハードウェアが発振校正(OSCCAL)レジ、スタに校正値バイトを設定し、これによって発振器を自動的に校正します。この校正の精度は表21-2.で工場校正として示されます。

この発振器が主クロックとして使われる時に未だウォッチドッグ発振器がウォッチドッグタイマとリセット時間経過に使われます。予め設定された校正値のより多くの情報については104頁の「校正領域」項をご覧ください。

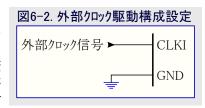

#### 6.2.2. 外部クロック信号

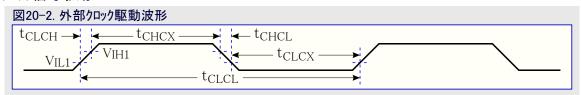

外部クロック元からデバイスを駆動するには、CLKIが**図6-2**.で示されるように駆動されるべきです。 外部クロックはクロック主設定レジスタ(CLKMSR)のクロック主選択(CLKMS1,0)ビットを10に設定することによって主クロックとして選択できます。

外部クロックを印加する時にMCUの安定な動作を保証するため、印加したクロック周波数の急な変化を避けることが必要とされます。或るクロック周期から次への2%より大きな周波数変化は予測されない事態を引き起こします。このようなクロック周波数での変化中、MCUはリセットに保たれるのを保証することが必要とされます。

# 6.2.3. 128kHz内部発振器

128kHz内部発振器は128kHzのクロックを提供する低電力発振器です。周波数は供給電圧、温度、1群の変量に依存します。このクロッ クはクロックはクロック主設定レジスタ(CLKMSR)のクロック主選択(CLKMS1,0)ビットを01に設定することによって主クロックとして選択できます。

#### 6.2.4. クロック元切り替え

主クロック元は16頁の「CLKMSR - クロック主設定レジスタ」を使って走行時に切り替えることができます。どのクロック元を切り替える時にもクロックシステムは主クロックに異常が起きないことを保証します。

# 6.2.5. 既定のクロック元

デバイスが電源投入またはリセットされる時に、主クロックとして常に校正付き8MHz内蔵発振器が選択されます。 同期システム クロックはシステム クロック前置分周器によって8分周に制御された主クロックです。 クロック前置分周選択ビットは後でシステム クロック周波数を変更するために書くことができます。 「システム クロック前置分周器」をご覧ください。

# 6.3. システム クロック前置分周器

システム クロックはシステム クロック前置分周器経由で主クロックから配給されます。システム クロックは16頁の「CLKPSR - クロック前置分周レジスタ」を設定することによって分周できます。システム クロック前置分周器は処理能力に対する必要条件が低い時の消費電力低減、またはシステム クロックを最大周波数の制限内に持って来るのに使うことができます。前置分周器は全ての主クロック元任意選択で使うことができ、CPUと全ての同期周辺機能のクロック周波数に影響を及ぼします。

システム クロック前置分周器は未だ安定動作を保証すると同時に内部クロック周波数の走行時変更の実行に使うことができます。

# 6.3.1. 切り替え時間

前置分周器設定を切り替える時に、システム クロック前置分周器は中間(経過途中)の周波数が直前の設定に対応するクロック周波数または新規設定に対応するクロック周波数のどちらよりも高くなく、システム クロックで異常が起きないことを保証します。

前置分周器として実行するリプル カウンタは主クロックの周波数で動き、それはCPUのクロック周波数よりも速いかもしれません。従って例え (カウンタ値が)読めるとしても、前置分周器の状態を決めることはできず、1から他へのクロック分周値切り替えを行う正確な時間は必ずしも予測できません。

CLKPS値が書かれる時から新規クロック周波数が活性(有効)になる前にT1+T2~T1+2×T2間かかります。この間で2つの有効なクロック端が生成されます。ここでのT1は直前のクロック周期、T2は新規前置分周器設定に対応する周期です。

## 6.4. 始動

#### 6.4.1. リセットからの始動

リセット元が活性(有効)になる時に内部リセットは直ちに有効設定にされます。内部リセットはリセット下が開放されて始動手順が完了されるまで有効設定にされ続けます。始動手順は次のような3つの段階を含みます。

- 1. リセット元が開放された後の最初の段階はリセット始動時間を計数するデバイスから成ります。このリセット始動時間の目的は供給電圧が充分な水準に達するのを保証することです。リセット始動時間は128KHz内部発振器を使って計数されます。リセット始動時間の詳細については表6-1.をご覧ください。

- 始動回路によって実際の供給電圧が監視されないことに注意してください。例えデバイスが早くに充分な供給電圧水準へ達したとしても、デバイスはリセット始動時間まで計数します。

- 2. 2つ目の段階は発振器始動時間を計数することで、これは校正付き内蔵発振器がシステムの他の部分によって使われる前にそれが安定状態に達することを保証します。校正付き内蔵発振器はそれが安定と見做され得る前に最低周期数の発振が必要です。発振器始動時間の詳細については表6-1.をご覧ください。

- 3. 内部リセットを開放する前の最後段階はデバイスを正しく構成設定するために不揮発性メモリから校正値と構成設定値を設定することです。構成設定時間は表6-1.で一覧にされます。

### 表6-1. 校正付き内蔵発振器使用時の始動時間

| リセット | 発振器 | 構成設定 | 総始動時間                         |

|------|-----|------|-------------------------------|

| 64ms | 6周期 | 21周期 | 64ms+6発振器周期+21システム クロック周期 (注) |

注:・デバイスの電源投入後やリセット後のシステム クロックは自動的に8分周された校正付き8MHz内蔵発振器に設定されます。

・低電圧検出器(BOD)許可時、リセット始動時間はデバイス通電後の128msです。

#### 6.4.2. パワーダウン動作からの始動

ハ°ワーダウン休止動作からの起動時、供給電圧は充分な水準であると仮定され、発振器の安定動作を保証するために発振器始動時間だけが計数されます。発振器始動時間は選択されている主クロックで計数され、始動時間はその選択されたクロックに依存します。詳細については表6-2.をご覧ください。

# 表6-2 パワーダウン休止動作からの始動時間

| 氏。こハケケルドエ助下の500円助利用 |                           |  |  |  |  |  |  |

|---------------------|---------------------------|--|--|--|--|--|--|

| 発振器始動時間             | 総始動時間                     |  |  |  |  |  |  |

| 6周期                 | 6発振器周期 ( <mark>注</mark> ) |  |  |  |  |  |  |

注:・始動時間は主クロック発振器周期で測定されます。

・ソフトウェアBOD禁止使用時、休止動作からの起動は概ね60µsです。

# 6.4.3. アイト・ル,A/D変換雑音低減,スタンハ・イ動作からの始動

アイドル、A/D変換雑音低減、スタンバイ動作からの起動時、発振器は既に動いており、発振器始動時間は全く持ち込まれません。

# 6.5. クロック関係レジスタ

## 6.5.1. CLKMSR - クロック主設定レシ、スタ (Clock Main Settings Register)

| ピット        | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0      |        |

|------------|---|---|---|---|---|---|--------|--------|--------|

| \$37       | - | - | - | - | - | - | CLKMS1 | CLKMS0 | CLKMSR |

| Read/Write | R | R | R | R | R | R | R/W    | R/W    |        |

| 初期値        | 0 | 0 | 0 | 0 | 0 | 0 | 0      | 0      |        |

ヒット7~2 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

● ビット1,0 - CLKMS1,0: クロック主選択 (Clock Main Select Bits)

これらのビットはシステムの主クロック元を選びます。このビットは主クロックの供給元を切り替えるために走行時に書くことができます。クロック システムは不具合なしでの主クロック元切り替えを保証します。

主クロック切り替えは表6-3.で示されます。

主クロック元の予期せぬ切り替えを避けるため、CLKMSビットを変更するには次のような保護された変更手順に従わなければなりません。

- 1. 保護されたI/Oレジスタの変更許可用の識票を構成設定変更保護 (CCP)レジスタに書いてください。

- 2.4命令周期内に望む値でCLKMSビットを書いてください。

| 表6-3. 主ク | 表6-3. 主クロックの選択 |                     |  |  |  |  |  |  |  |

|----------|----------------|---------------------|--|--|--|--|--|--|--|

| CLKMS1   | CLKMS0         | 主クロック元              |  |  |  |  |  |  |  |

| 0        | 0              | 校正付き8MHz内蔵発振器       |  |  |  |  |  |  |  |

| 0        | 1              | 128kHz内部発振器(WDT発振器) |  |  |  |  |  |  |  |

| 1        | 0              | 外部クロック信号            |  |  |  |  |  |  |  |

| 1        | 1              | (予約)                |  |  |  |  |  |  |  |

# 6.5.2. CLKPSR - クロック前置分周レジスタ (Clock Prescale Register)

| ピット        | 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      |        |

|------------|---|---|---|---|--------|--------|--------|--------|--------|

| \$36       | _ | - | - | - | CLKPS3 | CLKPS2 | CLKPS1 | CLKPS0 | CLKPSR |

| Read/Write | R | R | R | R | R/W    | R/W    | R/W    | R/W    |        |

| 初期値        | 0 | 0 | 0 | 0 | 0      | 0      | 1      | 1      |        |

ヒット7~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

● ビット3~0 - CLKPS3~0: クロック分周値選択 (Clock Prescaler Select Bits 3~0)

これらのビットは選択したクロック元と内部システム クロック間の分周係数を定義します。これらのビットは応用の必要条件に合わせてクロック周波数を変えるために走行時に書くことができます。前置分周器はMCUへの主クロック入力を分周するため、これによって全ての同期周辺機能の速度が減じられます。分周係数は表6-4.で与えられます。

表6-4. クロック前置分周器選択(注:既定値)

| 及。      | 7-3 HH 7- | - " ' ''- | · · // L / C | <u> </u> |    |    |    |     |     |      |   |   |   |   |   |   |

|---------|-----------|-----------|--------------|----------|----|----|----|-----|-----|------|---|---|---|---|---|---|

| CLKPS3  |           |           |              | (        | )  |    |    |     |     |      |   | ] | 1 |   |   |   |

| CLKPS2  |           | (         | )            |          | 1  |    |    |     | 0   |      |   |   | 1 |   |   |   |

| CLKPS1  | 0         |           | 1            |          | 0  |    | 1  |     | 0   |      | 1 |   | 0 |   | 1 |   |

| CLKPS0  | 0         | 1         | 0            | 1        | 0  | 1  | 0  | 1   | 0   | 1    | 0 | 1 | 0 | 1 | 0 | 1 |

| 分周係数(数) | 1         | 2         | 4            | 8(注)     | 16 | 32 | 64 | 128 | 256 | (予約) |   |   |   |   |   |   |

予期せぬクロック周波数の変更を防ぐため、CLKPSビットの変更するには保護された変更手順に従わなければなりません。

- 1. 保護されたI/Oレジスタの変更許可用の識票を構成設定変更保護(CCP)レジスタに書いてください。

- 2. (次からの)4命令周期内に望む値でCLKPSビットを書いてください。

始動でクロック分周係数8を選択するためにCLKPSビットは0011にリセットされます。応用ソフトウェアは選択したクロック元が現在の動作条件に於いてデバイスの最大周波数よりも高い周波数を持つ場合に、充分な分周係数が使われるのを保証しなければなりません。

# 6.5.3. OSCCAL - 発振校正レジスタ (Oscillator Calibration Register)

| ピット        | 7          | 6    | 5    | 4    | 3    | 2    | 1    | 0    | _      |  |  |

|------------|------------|------|------|------|------|------|------|------|--------|--|--|

| \$39       | CAL7       | CAL6 | CAL5 | CAL4 | CAL3 | CAL2 | CAL1 | CAL0 | OSCCAL |  |  |

| Read/Write | R/W        | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |        |  |  |

| 初期値        | デバイス固有の校正値 |      |      |      |      |      |      |      |        |  |  |

# ● ビット7~0 - CAL7~0 : 発振校正値 (Oscillator Calibration Value)

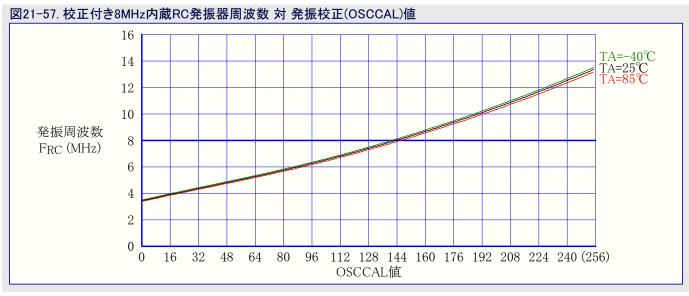

発振校正レジスタは発振器周波数の偏差処理を省くための内蔵発振器の調整に使われます。チップのリセット中に予めプログラムされた値が自動的にこのレジスタへ書かれ、109頁の「表20-2. 内蔵RC発振器の校正精度」で指定されるように工場校正された周波数を与えます。

応用ソフトウェアは発振器周波数を変更するために、このレシ、スタに書くことができます。この発振器は**表21-2**.で指定されるように周波数を校正することができます。この範囲外への校正は保証されません。

$CAL7\sim0$ L ットは発振器の周波数を調整するのに使われます。\$00の設定は最低周波数を生じ、\$FFの設定は最高周波数を生成します。

# 7. 電力管理と休止形態動作

高機能と産業的に先行するコード効率は低電力の応用に対してAVRマイクロ コントローラを理想的に選択させます。加えて休止形態動作は応用でMCU内の未使用部を一時停止することを可能にし、それによって節電します。AVRは応用で必要な消費電力に仕立てることを使用者に許す様々な休止形態動作を提供します。

# 7.1. 休止形態動作種別

14頁の図6-1.はATtiny40の各種クロック系統とその配給を示します。この図は適切な休止形態動作選択の助けになります。表7-1.は異なる休止形態動作とそれらの起動元を示します。

表7-1. 各休止形態動作に於ける動作クロック範囲と復帰起動要因

|   |           |            | 動作クロッ      | ク範囲 |     | 発振器動作        |              | 復         | 原帰起動要因( | 割り込み)   |        |

|---|-----------|------------|------------|-----|-----|--------------|--------------|-----------|---------|---------|--------|

|   | 休止形態種別    | clk<br>CPU | clk<br>NVM | clk | clk | 主クロック<br>供給元 | INT0<br>ピン変化 | ウォッチト゛ック゛ | 従装置TWI  | A/D変換完了 | その他I/O |

| ı | アイドル      |            |            | 0   | 0   | 0            | 0            | 0         | 0       | 0       | 0      |

|   | A/D変換雜音低減 |            |            |     | 0   | 0            | 1            | 0         | 2       | 0       |        |

|   | スタンバイ     |            |            |     |     | 0            | 1            | 0         | 2       |         |        |

|   | パワーダウン    |            |            |     |     |              | 1            | 0         | 2       |         |        |

- ①: INT0についてはレベル割り込みのみです。

- ②: TWIアドレス一致割り込みのみです。

4つの休止形態動作の何れかへ移行するにはMCU制御レジスタ(MCUCR)の休止許可(SE)ビットが論理1を書かれ、SLEEP命令が実行されなければなりません。MCUCRの休止形態種別選択(SM2~0)ビットはSLEEP命令によって活性(有効)にされる休止形態(アイドル、A/D変換雑音低減、スタンハイ、パワータ・ウン)のどれかを選びます。一覧については表7-2.をご覧ください。

MCUが休止形態動作中に許可した割り込みが起こると、MCUは起動します。その時にMCUは起動時間に加えて4周期停止され、割り込みルーチンを実行し、そしてSLEEP命令の次の命令から実行を再開します。デバイスが休止状態から起動するとき、レジスタファイルとSRAMの内容は変えられません。休止形態動作中にリセットが起こると、MCUは起動し、リセット ベクタから実行します。

レヘールで起動した割り込みが起動復帰に使われる場合、MCUを起動(とMCUがその割り込み処理ルーチンへ移行)するには、変更したレヘールが一定時間保持されなければならないことに注意してください。詳細については28頁の「外部割り込み」を参照してください。

#### 7.1.1. アイドル動作

休止形態種別選択(SM2~0)ビットが'000'を書かれると、SLEEP命令はMCUをアイドル動作へ移行させ、CPUを停止しますが、アナロケ比較器、A/D変換器、タイマ/カウンタ、TWI、SPI、ウォッチトック、割り込み機構の継続動作を許します。この休止形態は基本的にclkCPUとclk NVMを停止する一方、他のクロックに走行を許します。

アイドル動作はMCUにタイマ溢れなどの内部割り込みだけでなく、外部で起動された割り込みからの起動も可能にします。アナロゲ比較器割り込みからの起動が必要とされないなら、アナロゲ比較器制御/状態レジスタA(ACSRA)のアナロゲ比較器禁止(ACD)ビットを設定(1)することにより、アナロゲ比較器を電源断にできます。これはアイドル動作での消費電力を削減します。A/D変換が許可されるなら、この動作に移行すると変換が自動的に始まります。

# 7.1.2. A/D変換雑音低減動作

SM2~0ビットが'001'を書かれると、SLEEP命令はMCUをA/D変換雑音低減動作へ移行させ、CPUを停止しますが、A/D変換器、外部割り込み、ウォッチドッグの(許可されていれば)継続動作を許します。この休止形態は基本的にclk<sub>I/O</sub>, clk<sub>CPU</sub>, clk<sub>NVM</sub>を停止する一方、他のクロックに走行を許します。

これはA/D変換に対する雑音環境を改善し、より高い分解能の測定を可能にします。A/D変換器が許可されている場合、この動作に移行すると、変換が自動的に始まります。A/D変換完了割り込みからの他、外部リセット、ウォッチト、ッグ・リセット、INTOの外部レヘル割り込み、ピン変化割り込みだけが、A/D変換雑音低減動作からMCUを起動できます(訳注:本行追加)。

### 7.1.3. パワーダウン動作

SM2~0ビットが'010'を書かれると、SLEEP命令はMCUをパワーダウン動作へ移行させます。この動作では発振器が停止される一方、外部割り込み、TWI、ウォッチドッグ機能は(許可されていれば)継続して動作します。外部リセット、ウォッチドッグリセット、INT0の外部レヘル割り込み、ピン変化割り込み、従装置TWI割り込みだけがMCUを起動できます。この休止形態は生成した全てのクロックを停止し、非同期部の動作だけを許します。

### 7.1.4. スタンバイ動作

SM2~0ビットが'100'を書かれると、SLEEP命令はMCUをスタンバイ動作へ移行させます。この動作は発振器が走行(動作)を保たれる例外を除いてパワーダウン動作と同じです。発振器が既に走行していて始動が必要ないので、これは起動時間を減らします。

# 7.2. ソフトウェア低電圧検出(BOD)禁止

低電圧検出器(BOD)がBODLEVELヒュース'(103頁の表19-5.参照)によって許可されていると、BODは休止期間中に電源電圧を活発に監視します。いくつかのデバイスはパプワーダウンとスタンバイの休止動作でソフトウェアでBODを禁止することによる節電が可能です。この休止動作電力消費はBODがヒュース'によって全面的に禁止される時と同じ水準になるでしょう。

BODがソフトウェアで禁止される場合、BOD機能は休止動作移行後、直ちにOFFされます。休止からの起動復帰で、BODは再び自動的に許可されます。これは休止期間中にVCCレベルが落ちた場合の安全な動作を保証します。

BODが禁止されてしまうと、MCUが命令コードの実行を継続する前にBODが正しく動作するのを保証するために、休止動作からの起動時間は概ね60usになります。

BOD禁止はMCU制御レジスタ(MCUCR)のBOD休止(BODS)ビットによって制御されます。20頁の「MCUCR - MCU制御レジスタ」をご覧ください。このビットへの1書き込みはパワーダウン動作とスタンハイ動作でのBODをOFFにし、一方このビットの0はBOD活動(有効)を維持します。既定設定は0、換言するとBOD活動(有効)です。

BODSビットへの書き込みは許可ビットと時間制限手順によって制御されます。20頁の「MCUCR - MCU制御レジスタ」をご覧ください。

# 7.3. 電力削減レジスタ

電力削減レジスタ(20頁の「PRR - 電力削減レジスタ」参照)は個別周辺機能へのクロックを停止することにより、消費電力を削減方法を提供します。周辺機能へのクロックが停止される、以下のようになります。

- ・周辺機能の現在の状態が固定化されます。

- 関連するレシ、スタは読み書きすることができません。

- ・周辺機能によって使われる資源は専有されたままに留まります。

周辺機能は殆どの場合に於いてクロックを停止する前に禁止されるべきです。電力削減レジスタ(PRR)のビットを解除(0)することが周辺機能部を起し、停止前と同じ状態にします。

周辺機能停止は全体に亘る重要な消費電力の削減のために活動動作とアイドル動作で使えます。例については112頁の「**周辺機能部供給電流**」をご覧ください。その他の休止形態動作ではクロックが予め停止されます。

# 7.4. 消費電力の最小化

これらはAVRコアが制御するシステムで消費電力の最小化を試みる時に考慮するためのそれぞれの検討点です。一般的に休止形態動作は可能な限り多く使われるべきで、休止形態種別は動作するデバイスの機能が可能な限り少なくなるように選択されるべきです。必要とされない全ての機能は禁止されるべきです。特に次の機能部は最低可能消費電力の達成を試みるとき、特別な考慮を必要とするでしょう。

## 7.4.1. アナログ比較器

アイドル動作またはA/D変換雑音削減動作へ移行するとき、アナログ比較器は使われないなら、禁止されるべきです。その他の休止形態動作でのアナログ比較器は自動的に禁止されます。更なる詳細については83頁の「アナログ比較器」をご覧ください。

# 7.4.2. A/D変換器 (ADC)

許可したなら、A/D変換器は全ての休止形態動作で許可されます。節電するため、休止形態動作の何れかへ移行する前にA/D変換器は禁止されるべきです。A/D変換器がOFFそして再びONに切り替えられると、次の(最初の)変換は延長された(初回)変換になります。A/D変換器操作の詳細については86頁の「A/D変換器」をご覧ください。

# 7.4.3. ウォッチト・ック・タイマ

ウォッチト、ック、タイマが応用で必要とされないなら、この単位部はOFFされるべきです。ウォッチト、ック、タイマが許可されていると全休止形態動作で許可され、故に常時電力を消費します。これはより深い休止形態動作での総消費電流にとって重要な一因になります。ウォッチト、ック、タイマ設定法の詳細については24頁の「ウォッチト、ック、タイマ」をご覧ください。

# 7.4.4. 低電圧検出器 (BOD)

低電圧検出器(BOD)が応用で必要とされないなら、この単位部はOFFにされるべきです。低電圧検出器がBODLEVELヒューズによって許可されていると全休止形態動作で許可され、故に常時電力を消費します。これはより深い休止形態動作での総消費電流にとって重要な一因になります。低電圧検出器(BOD)設定法の詳細については23頁の「低電圧検出(BOD)」と「ソフトウェア低電圧検出器(BOD)禁止」をご覧ください。

### 7.4.5. ホート ピン

休止形態動作へ移行するとき、全てのポートピンは最小電力使用に設定されるべきです。最も重要なことはその時にピンが抵抗性負荷を駆動しないのを保証することです。I/Oクロック(clkɪ/O)が停止される休止形態動作ではデバイスの入力緩衝部が禁止されます。これは必要とされない時に入力論理回路によって電力が消費されないことを保証します。いくつかの場合で入力論理回路は起動条件を検出するために必要とされ、その時は許可されます。どのピンが許可されるかの詳細については33頁の「デジタル入力許可と休止形態動作」を参照してください。入力緩衝部が許可され、入力信号が浮いている状態のままか、またはアナログ信号電圧がVCC/2付近の場合、入力緩衝部は過大な電力を消費するでしょう。

アナログ、入力ピンに対するデジタル入力緩衝部は常に禁止されるべきです。入力ピンでVCC/2付近のアナログ信号入力は活動動作でも重要な電流を引き起こし得ます。デジタル入力緩衝部はデジタル入力禁止レジスタの(DIDRO)とポート制御レジスタ(PORTCR)の書き込みによって禁止できます。詳細については85頁と94頁の「DIDRO - デジタル入力禁止レジスタの」と「PORTCR - ポート制御レジスタ」をご覧ください。

# 7.5. 電力管理用レジスタ

### 7.5.1. MCUCR - MCU制御レジスタ (MCU Control Register)

このMCU制御レジスタは条件制御と電力管理用の制御ビットを含みます。

| ピット        | 7     | 6     | 5 | 4    | 3   | 2   | 1   | 0   | _     |

|------------|-------|-------|---|------|-----|-----|-----|-----|-------|

| \$3A       | ISC01 | ISC00 | - | BODS | SM2 | SM1 | SM0 | SE  | MCUCR |

| Read/Write | R/W   | R/W   | R | R/W  | R/W | R/W | R/W | R/W |       |

| 初期値        | 0     | 0     | 0 | 0    | 0   | 0   | 0   | 0   |       |

● ビット5 - Res: 予約 (Reserved)

このビットは予約されており、常に0として読まれます。

● ビット4 - BODS : BOD休止 (BOD Sleep)

休止中(18頁の表7-1.参照)にBODを禁止するために、BODSビットは論理lを書かれなければなりません。これは以下のように、保護された変更手順によって制御されます。

- 1. 構成設定変更保護(CCP)レジスタに保護されたI/Oレジスタの変更許可用の識票を書いてください。

- 2.4命令周期内にBODSビットを書いてください。

実際の休止動作に対してBODをOFFにするために、SLEEP命令はBODSが活性(有効)の間に実行されなければなりません。 BODSビットはデバイス起き上がり時に自動的に解除(0)されます。代わりに、BODSビットはそれに論理0を書くことによっても解除(0)することができます。これは保護された手順の必要がありません。

● ビット3~1 - SM2~0: 休止形態種別選択 (Sleep Mode Select Bit 2, 1 and 0)

これらのビットは表7-2.で示される利用可能な4つの休止形態動作の1つを選択します。

| 表7-2 | . 休止 | 形態 | 動作種 | 別選択         |

|------|------|----|-----|-------------|

| SM2  | 2 SI | M1 | SM0 | 休止形態動作種別    |

| 0    |      | 0  | 0   | アイドル動作      |

| 0    |      | 0  | 1   | A/D変換雑音低減動作 |

| 0    |      | 1  | 0   | パプーダウン動作    |

| 0    |      | 1  | 1   | (予約)        |

| 1    |      | 0  | 0   | スタンバイ動作     |

| 1    |      | 0  | 1   | (予約)        |

| 1    |      | 1  | 0   | (予約)        |

| 1    |      | 1  | 1   | (予約)        |

### ● ビット0 - SE: 休止許可 (Sleep Enable)

SLEEP命令が実行される時にMCUを休止形態動作へ移行させるには、休止許可(SE)ビットが論理1を書かれなければなりません。MCUの目的外休止形態動作移行を避けるため、SLEEP命令実行直前に休止許可(SE)ビットを設定(1)し、起動後直ちに解除(0)することが推奨されます。

# 7.5.2. PRR - 電力削減レジスタ (Power Reduction Register)

| ピット        | 7 | 6 | 5 | 4     | 3     | 2      | 1      | 0     |     |

|------------|---|---|---|-------|-------|--------|--------|-------|-----|

| \$35       | _ | - | - | PRTWI | PRSPI | PRTIM1 | PRTIM0 | PRADC | PRR |

| Read/Write | R | R | R | R/W   | R/W   | R/W    | R/W    | R/W   |     |

| 初期値        | 0 | 0 | 0 | 0     | 0     | 0      | 0      | 0     |     |

ビット7~5 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

● ビット4 - PRTWI: TWI電力削減 (Power Reduction Two-Wire Interface)

このビットへの1書き込みは2線インターフェース(TWI)部を停止します。

● ビット3 - PRSPI: SPI電力削減 (Power Reduction Serial Peripheral Interface)

このビットへの1書き込みは直列周辺インターフェース(SPI)部を停止します。

- ビット2 PRTIM1: タイマ/カウンタ1電力削減 (Power Reduction Timer/Counter1)

このビットへの1書き込みはタイマ/カウンタ1部を停止します。タイマ/カウンタ1が許可されると、停止前と同様に動作は継続します。

- ビット1 PRTIM0 : タイマ/カウンタ0電力削減 (Power Reduction Timer/Counter0) このビットへの1書き込みはタイマ/カウンタ0部を停止します。 タイマ/カウンタ0が許可されると、停止前と同様に動作は継続します。

時、アナログ比較器はADC入力切替器を使えません。

- ビット0 PRADC: A/D変換器電力削減 (Power Reduction ADC) このピットへの1書き込みはA/D変換器(ADC)を停止します。A/D変換器は停止前に禁止されなければなりません。A/D変換器停止

- 注: アナログ 比較器は83頁の「ACSRA アナログ 比較器制御/状態レジ スタA」のアナログ 比較器禁止(ACD)ビットを使うことで禁止されます。 (訳注:共通性から本注追加)

# 8. システム制御とリセット

### 8.1. AVRのリセット

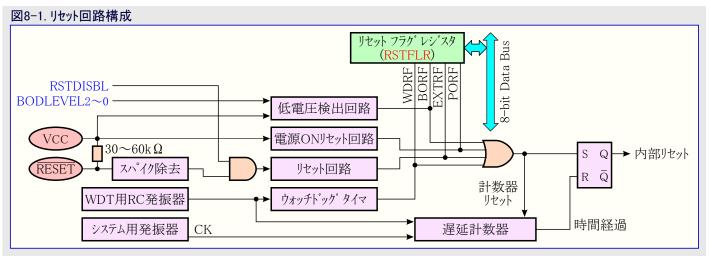

リセット中、全てのI/Oレシ、スタはそれらの初期値に設定され、プログラムはリセット、ブクタから実行を開始します。リセット、ブクタに配置される命令は、きっとリセット処理ルーチンへの無条件相対分岐(RJMP)命令でしょう。プログラムが決して割り込み元を許可しないなら、割り込み、ブクタは使われず、これらの位置に通常のプログラムコートが配置できます。図8-1.の回路構成図はリセット論理回路を示します。リセット回路の電気的特性は109頁の「システムとリセットの特性」項で定義されます。

AVRのI/Oポートはリセット元が有効になると直ちにそれらの初期状態にリセットされます。これはどのクロック元の走行も必要ありません。 全てのリセット元が無効にされてしまった後、遅延計数器(タイマ)が始動され、内部リセットを引き伸ばします。これは通常動作開始前に安定電圧へ達することを電源に許します。始動手順は15頁の「リセットからの始動」で記述されます。

## 8.2. リセット元

ATtinv40には次の4つのリセット元があります。

- ・電源ONJセット・・・・・供給電圧が電源ONJセット閾値電圧(VPOA)以下でMCUがJセットされます。

- ・外部リセット・・・・・・・ RESETピンが最小パルス幅以上Lowレベルに保たれると、MCUがリセットされます。

- ・ウォッチト、ック、リセット・・・ウォッチト、ック、リセット動作が許可され、ウォッチト、ック、タイマが終了すると、MCUがリセットされます。

- ・低電圧リセット・・・・・・ 低電圧検出器(BOD)が許可され、供給電圧(VCC)が低電圧検出電圧(VBOT)以下でMCUがリセットされます。

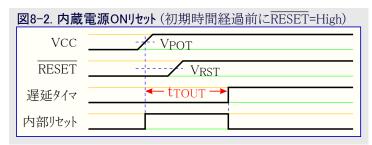

# 8.2.1. 電源ONリセット

電源ONJセット(POR)パルスはチップ上の検出回路により、生成されます。検出電圧は109頁の「システムとリセットの特性」項で定義されます。POR信号はVCCが検出電圧以下の時は必ず活性(有効)にされます。POR回路は供給電圧異常検出は勿論、始動リセットの起動にも使えます。

電源ONJセット回路はデバイスが電源投入でリセットされることを保証します。電源ONJセット閾値電圧(VPOR)への到達はVCCの上昇後にデバイスがどのくらいリセットを保つかを決める遅延計数器(タイマ)を起動します。VCCがこの検出電圧以下に低下すると、リセット信号はどんな遅延もなく再び有効にされます。

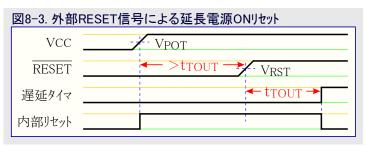

#### 8.2.2. 外部リセット

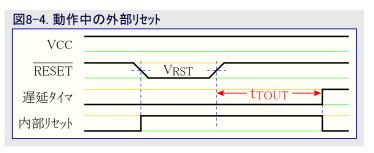

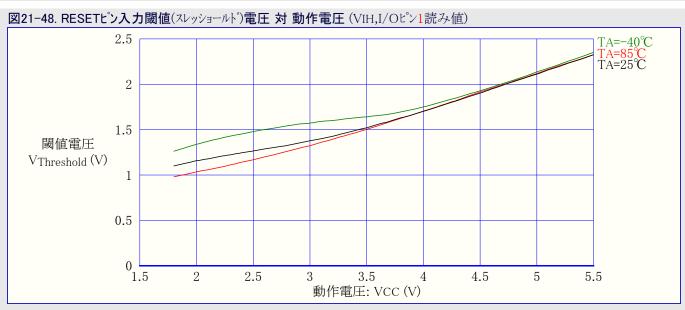

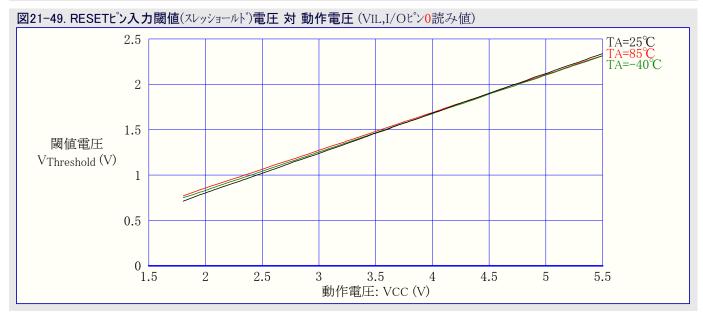

外部リセットはRESETピンのLowレヘルによって生成されます。クロックが動いていなくても、最小ハルス幅(109頁の「システムとリセットの特性」項参照)以上のリセットハルスはリセットを生成します。短すぎるハルスはリセット生成が保証されません。印加された信号の上昇がリセット閾値電圧(VRST)に達すると(遅延タイマを起動し)、遅延タイマは遅延時間(tTOUT)経過後にMCUを始動します。電源ON始動計数中は外部リセットが無視されます。内部電源ON遅延計数完了時にRESETピンがLowの場合にだけ、電源ONリセット後に内部リセットが延長されます。22頁の図8-2.と図8-3.をご覧ください。

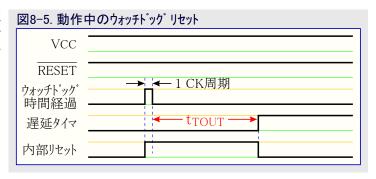

### 8.2.3. ウォッチト・ック・リセット

ウォッチト、ック、時間経過時、(内部的に)短いリセット ハ°ルスを生成します。遅延タイマはこのハ°ルスの下降端で遅延時間(t<sub>TOUT</sub>)の計時を始めます。ウォッチト、ック、タイマ操作の詳細については24頁を、リセット遅延時間については109頁の表20-4。をご覧ください。

## 8.2.4. 低電圧(ブラウンアウト)検出リセット

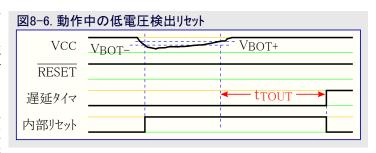

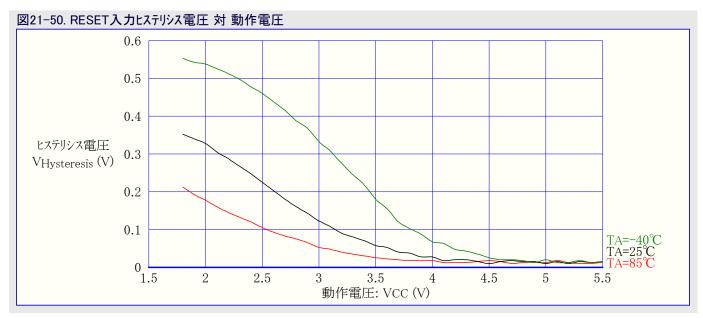

ATtiny40は固定化された起動(検出)電圧と比較することによって動作中のVCCを監視するチップ上の低電圧検出(BOD)回路を持ちます。BODの起動電圧はBODLEVELtュース。によって選択できます。この起動電圧はスパイク対策BODを保証するためにヒステリシスを持ちます。検出電圧のヒステリシスはVBOT+=VBOT+VHYST/2、VBOT-=VBOT-VHYST/2と解釈されるべきです。

BODが許可され、VCCが起動電圧以下に下降すると(図8-6.の VBOT-)、低電圧リセットが直ちに有効とされます。VCCが起動電圧以上に上昇すると(図8-6.のVBOT+)、(遅延タイマが起動され)遅延タイマは遅延時間(tTOUT)経過後にMCUを始動します。

BOD回路は電圧が109頁の「システムとリセットの特性」で与えられるtBOD時間より長く起動電圧以下に留まる場合のみ、VCCでの低下を検出します。

### 8.3. 内部基準電圧

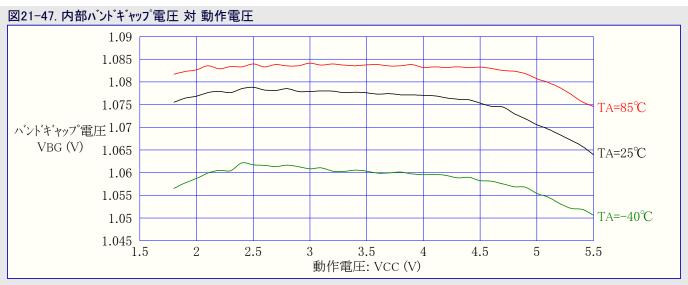

ATtiny40は内部基準電圧が特徴です。この基準電圧は低電圧検出(BOD)に使われ、A/D変換やアナログ比較器の入力としても使えます。 ハント・ギャップ 電圧は供給電圧と温度で変化します。

# 8.3.1. 基準電圧許可信号と起動時間

基準電圧には使われるべき方法に影響を及ぼすかもしれない起動時間があります。この起動時間は、109頁の「システムとリセットの特性」で与えられます。節電のために、この基準電圧は常にONではありません。この基準電圧は次の状態中ONです。

- 1. 低電圧検出リセット許可時 (BODLEVELヒュース、のプログラム(0)により)

- 2. アナログ比較器内部基準電圧接続時 (アナログ比較器制御/状態レジスタA(ACSRA)の基準電圧入力選択(ACBG)=1)

- 3. A/D変換部動作許可時 (A/D変換制御/状態レジスタA(ADCSRA)のA/D動作許可(ADEN)=1)

従って低電圧検出(BOD)が許可されていないと、ACBGの設定(=1)またはA/D変換部許可(ADEN=1)後、使用者はアナログ比較器またはA/D変換器出力が使われる前に基準電圧へ起動時間を与えなければなりません。ハプーダウン動作での消費電力を減らすため、使用者はパワーダウン動作へ移行する前に基準電圧がOFFされるのを保証することで上の3つの状態を避けられます。

# 8.4. ウォッチト・ック タイマ

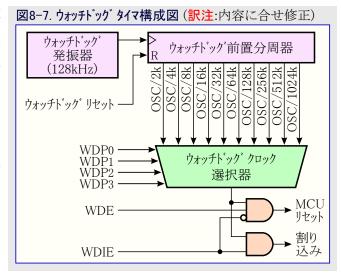

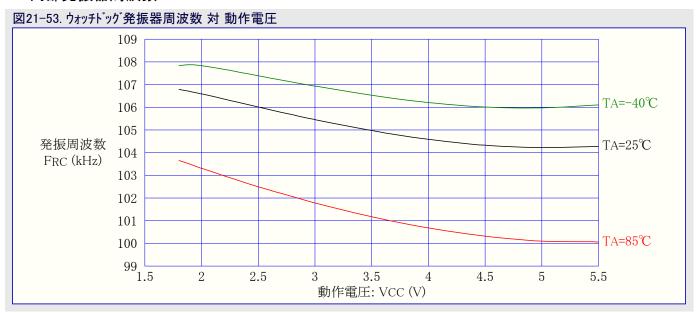

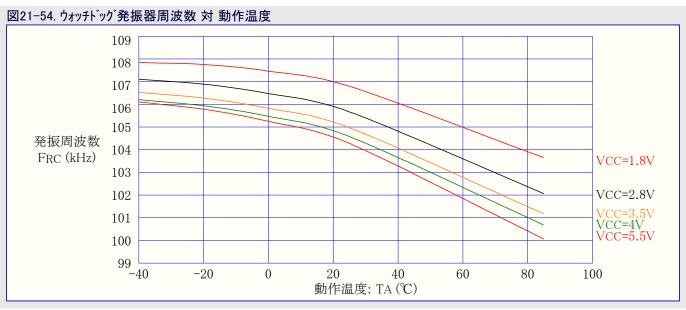

ウォッチト、ッケ、タイマは128kHzで動く独立したチップ、上の発振器からクロック駆動されます。図8-7.をご覧ください。ウォッチト、ッケ、タイマ前置分周器の制御により、ウォッチト、ッケ、リセット間隔は25頁の表8-3.で示されるように調整できます。ウォッチト、ッケ、リセット(WDR)命令はウォッチト、ッケ、タイマをリセットします。ウォッチト、ッケ、タイマはそれが禁止される時とデバイスリセットが起こる時もリセットされます。10種の異なるクロック周期時間がこのリセット周期を決めるために選択できます。別のウォッチト、ッケ、リセットなしにリセット周期が経過すると、ATtiny40はリセットしてリセット、ベクタから実行します。ウォッチト、ッケ、リセットの詳細タイミンケ、については25頁の表8-3.を参照してください。

ウォッチドッグ タイマはリセットの代わりに割り込みを生成する設定にもできます。これはパワーダウン動作から起動するのにウォッチドッグを使う時に大変有用となり得ます。

予期せぬウォッチト、ック禁止や予期せぬ計時終了周期変更を防ぐため、2つの異なる安全レヘルが表8-1.で示されるWDTON構成設定ビットによって選択されます。詳細については次の「ウォッチト、ック、タイマ構成設定変更用手順」を参照してください。

表8-1. WDTON構成設定ビットの設定によるウォッチトック、機能設定

| WDTON構成設定ビット                                        | 安全レベル | WDT初期状態 | WDT禁止方法   | 計時完了時間変更方法 |

|-----------------------------------------------------|-------|---------|-----------|------------|

| 非プログラム(1)                                           | 1     | 禁止      | 保護された変更手順 | なし(常時可)    |

| プ <sup>°</sup> ログ <sup>*</sup> ラム( <mark>0</mark> ) | 2     | 許可      | なし(常時許可)  | 保護された変更手順  |

### 8.4.1. ウォッチト、ック、タイマ構成設定変更用手順

ウォッチドック、構成設定変更手順は安全レヘブル間で異なります。

#### 8.4.1.1. 安全レベル1

この動作種別ではウォッチドッグ タイマが初めに禁止されますが、どんな制限もなくウォッチドッグ許可(WDE)ビットに1を書くことによって許可できます。許可したウォッチドッグ タイマを禁止する時に特別な手順が必要とされます。許可したウォッチドッグ タイマを禁止するには次の手順に従わなければなりません。

- 1. 保護されたI/Oレジスタの変更許可用の識票を構成設定変更保護(CCP)レジスタに書いてください。

- 2. (次からの)4命令周期内に同じ操作(命令)で欲したWDEとウォッチトック、タイマ前置分周選択(WDP3~0)ビットを書いてください。

#### 8.4.1.2. 安全レベル2

この動作種別ではウォッチドッグタイマが常に許可され、WDEビットは常に1として読めます。ウォッチドッグ計時完了周期を変更する時に保護された変更が必要とされます。ウォッチドッグ計時完了周期を変更するには次の手順に従わなければなりません。

- 1. 保護されたI/Oレジスタの変更許可用の識票を構成設定変更保護(CCP)レジスタに書いてください。

- 2. (次からの)4命令周期内に同じ操作(命令)でWDP2~0ビットを書いてください。WDEビットに書かれた値は無関係です。

#### 8.4.2. コート 例

次のコート・例はウォッチト、ック、(WDT)をOFFに切り替える方法を示します。本例は(例えば全割り込み禁止によって)割り込みが制御され、それ故この関数実行中に割り込みが起きない前提です。

| WDT OFF: | WDR  |                                                                         | ;ウォッチト゛ック゛ タイマ リセット            |

|----------|------|-------------------------------------------------------------------------|--------------------------------|

| _        | IN   | R16, RSTFLR                                                             | ;現RSTFLR値を取得                   |

|          | ANDI | R16, ~ (1< <wdrf)< td=""><td>;WDRFビットのみ<mark>0</mark>値を取得</td></wdrf)<> | ;WDRFビットのみ <mark>0</mark> 値を取得 |

|          | OUT  | RSTFLR, R16                                                             | ;RSTFLRのWDRFを解除(0)             |

|          | LDI  | R16, \$D8                                                               | ;変更許可識票値を取得                    |

|          | OUT  | CCP, R16                                                                | ;構成設定変更許可手順開始                  |

|          | LDI  | R16, (0< <wde)< td=""><td>;WDE論理<mark>0</mark>値を取得</td></wde)<>         | ;WDE論理 <mark>0</mark> 値を取得     |

|          | OUT  | WDTCSR, R16                                                             | ;ウォッチドック゛禁止                    |

|          | RET  |                                                                         | ;呼び出し元へ復帰                      |

# 8.5. リセット関係レジスタ

### 8.5.1. WDTCSR - ウォッチトック、タイマ制御/状態レジスタ (Watchdog Timer Control and Status Register)

| ピット        | 7    | 6    | 5    | 4 | 3   | 2    | 1    | 0    | _      |

|------------|------|------|------|---|-----|------|------|------|--------|

| \$31       | WDIF | WDIE | WDP3 | - | WDE | WDP2 | WDP1 | WDP0 | WDTCSR |

| Read/Write | R/W  | R/W  | R/W  | R | R/W | R/W  | R/W  | R/W  |        |

| 初期値        | 0    | 0    | 0    | 0 | 不定  | 0    | 0    | 0    |        |

# ● ビット7 - WDIF: ウォッチドッグ割り込み要求フラグ (Watchdog Timer Interrupt Flag)

ウォッチト、ック、タイマが割り込みに設定され、ウォッチト、ック、タイマで計時完了が起こると、本ヒ、ットが設定(1)されます。対応する割り込み処理へ、クタを実行すると、WDIFはハート、ウェアによって解除(0)されます。代わりにWDIFはこのフラグへの論理1書き込みによっても解除(0)されます。ウォッチト、ック、割り込み許可(WDIE)が設定(1)されていると、ウォッチト、ック、計時完了割り込みが要求されます。

#### ● ビット6 - WDIE: ウォッチトック・割り込み許可 (Watchdog Timer Interrupt Enable)

このビットが1を書かれると、ウォッチドッグ割り込みが許可されます。この設定(1)との組み合わせでウォッチドッグリセット許可(WDE)ビットが解除(0)されると、ウォッチドッグ タイマは割り込み動作形態で、ウォッチドッグ タイマで計時完了が起こると、対応する割り込みが要求されます。

WDEが設定(1)されると、ウォッチト、ッグ タイマは割り込み及びシステム リセット動作形態です。ウォッチト、ッグ タイマでの最初の計時完了がウォッチト、ッグ割り込み要求(WDIF)フラグを設定(1)します。対応する割り込みへ、クタの実行はハート、ウェアによってWDIEとWDIFを自動的に解除(0)します(ウォッチト、ッグ はシステム リセット動作形態になります)。これは割り込みを使うのと同時にウォッチト、ッグ タイマ保護を維持するのに有用です。割り込み及びシステム リセット動作形態に留まるには、各割り込み後にWDIEが設定(1)されなければなりません。然しながら、これがウォッチト、ッグ システム リセット動作形態の安全機能を危険に晒すかもしれないため、これは割り込み処理ルーチン自身内で行われるべきではありません。次の計時完了に先立って割り込みが実行されない場合、システム リセットが適用(実行)されます。

表8-2. ウォッチト・ック タイマ構成設定

| WDTON | WDE | WDIE | 動作種別           | 計時完了での動作             |

|-------|-----|------|----------------|----------------------|

| 1     | 0   | 0    | 停止             | なし                   |

| 1     | 0   | 1    | 割り込み           | 割り込み                 |

| 1     | 1   | 0    | システム リセット      | リセット                 |

| 1     | 1   | 1    | 割り込み及びシステムリセット | 割り込み、その後システムリセット動作種別 |

| 0     | X   | X    | システム リセット      | リセット                 |

注: WDTON構成設定ビットは0でプログラム、1で非プログラムに設定です。

#### ● ビット4 - Res: 予約 (Reserved)

このビットは予約されており、常に0として読まれます。

#### ビット3 - WDE: ウォッチト・ック・システム リセット許可 (Watchdog System Reset Enable)

WDEはリセット フラグ レシ スタ(RSTFLR)のウォッチト ッグ リセット フラグ (WDRF)によって無効にされます。これはWDRFが設定(1)されると、WDE が常に設定(1)されることを意味します。WDEを解除(0)するにはWDRFが先に解除(0)されなければなりません。この特徴は失敗を引き起こす状態中の複数リセットと失敗後の安全な起動を保証します。

#### ビット5,2~0 - WDP3~0: ウォッチトック、タイマ前置分周選択 (Watchdog Timer Prescaler 3,2,1 and 0)

このWDP3~0ビットはウォッチドッグ タイマが走行する時のウォッチドッグ タイマの前置分周を決めます。各種前置分周値と対応する計時完了周期は**表8-3**.で示されます。

表8-3. ウォッチトック前置分周選択

| 1 1 1                 |      | 77 FAZIV |      |                |       |      |      |      |      |       |      |   |   |   |   |   |  |

|-----------------------|------|----------|------|----------------|-------|------|------|------|------|-------|------|---|---|---|---|---|--|

| WDP3                  |      |          |      | (              | )     |      |      |      |      |       |      | 1 |   |   |   |   |  |

| WDP2                  |      | (        | )    |                | 1     |      |      |      |      | C     | )    |   |   | 1 |   |   |  |

| WDP1                  | (    | )        |      | 1              | (     | )    |      |      | (    | )     | 1    |   | 0 |   | 1 |   |  |

| WDP0                  | 0    | 1        | 0    | 1              | 0     | 1    | 0    | 1    | 0    | 1     | 0    | 1 | 0 | 1 | 0 | 1 |  |

| WDT発振周期数              | 2k   | 4k       | 8k   | 16k            | 32k   | 64k  | 128k | 256k | 512k | 1024k |      |   |   |   |   |   |  |

| 代表的計時完了<br>周期(VCC=5V) | 16ms | 32ms     | 64ms | <b>0.</b> 125s | 0.25s | 0.5s | 1.0s | 2.0s | 4.0s | 8.0s  | (予約) |   |   |   |   |   |  |

# 8.5.2. RSTFLR - リセット フラク・レシ スタ (Reset Flag Register)

リセット フラグ レジスタどのリセット元がMCUリセットを起こしたかの情報を提供します。

| ピット        | 7 | 6 | 5 | 4 | 3    | 2    | 1     | 0    |        |

|------------|---|---|---|---|------|------|-------|------|--------|

| \$3B       | - | - | - | - | WDRF | BORF | EXTRF | PORF | RSTFLR |

| Read/Write | R | R | R | R | R/W  | R/W  | R/W   | R/W  |        |

| 初期値        | 0 | 0 | 0 | 0 | 内容参照 | 内容参照 | 内容参照  | 内容参照 |        |

# ヒット7~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

• ビット3 - WDRF: ウォッチドック゛リセット フラク゛(Watchdog Reset Flag)

このビットはウォッチドッグ リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

● ビット2 - BORF: 低電圧リセット フラク (Brown-Out Reset Flag)

このビットは低電圧リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

● ビット1 - EXTRF:外部リセット フラク (External Reset Flag)

このビットは外部リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

ビット0 - PORF: 電源ONリセット フラク (Power-on Reset Flag)

このビットは電源ONリセットが起こると設定(1)されます。このビットはこのフラグへの論理0書き込みによってのみリセット(0)されます。

リセット条件の確認にリセット フラグを使うため、使用者はプログラム内で可能な限り早くRSTFLRを読み、そして解除(0)すべきです。別のリセットが起こる前にこのレジスタが解除(0)されると、そのリセット元はリセットフラグを調べることによって得られます。

# 9. 割り込み

本項はATtiny40によって実行されるような割り込み操作の詳細を記述します。AVR割り込み操作の一般説明については8頁の「リセットと割り込みの扱い」をご覧ください。

# 9.1. 割り込みべかり

ATtiny40の割り込みベクタは下の表9-1.で記述されます。

表9-1. リセットと割り込みのベクタ

| ベクタ番号 | プログラム アトレス | ラベル表記                    | 割り込み元                  |

|-------|------------|--------------------------|------------------------|

| 1     | \$0000     | RESET                    | 電源ON, WDT, BOD等の各種リセット |

| 2     | \$0001     | INT0                     | 外部割り込み要求0              |

| 3     | \$0002     | PCINTO (PCIO)            | ピン変化0群割り込み要求           |

| 4     | \$0003     | PCINT1 (PCI1)            | ピン変化1群割り込み要求           |

| 5     | \$0004     | PCINT2 (PCI2)            | ピン変化2群割り込み要求           |

| 6     | \$0005     | WDT                      | ウォッチドッグ計時完了            |

| 7     | \$0006     | TIM1_CAPT                | タイマ/カウンタ1捕獲発生          |

| 8     | \$0007     | TIM1_COMPA               | タイマ/カウンタ1比較A一致         |

| 9     | \$0008     | TIM1_COMPB               | タイマ/カウンタ1比較B一致         |

| 10    | \$0009     | TIM1_OVF                 | タイマ/カウンタ1溢れ            |

| 11    | \$000A     | TIM0_COMPA               | タイマ/カウンタ0比較A一致         |

| 12    | \$000B     | TIM0_COMPB               | タイマ/カウンタ0比較B一致         |

| 13    | \$000C     | TIM0_OVF                 | タイマ/カウンタ0溢れ            |

| 14    | \$000D     | ANA_COMP                 | アナログ比較器出力遷移            |

| 15    | \$000E     | ADC                      | A/D変換完了                |

| 16    | \$000F     | TWI_SLAVE                | 2線インターフェース             |

| 17    | \$0010     | SPI                      | 直列周辺インターフェース           |

| 18    | \$0011     | QTRIP ( <mark>注</mark> ) | 接触感知                   |

注:接触感知割り込み元はQTouchライブラリ支援に関連します。

プログラムが決して割り込み元を許可しない条件では、割り込みへ、クタは使われず、結果としてこれらの位置に通常のプログラム コードを配置することができます。

ATtiny40での最も代表的且つ一般的なリセットと割り込みのベクタ アドレス用設定は下のプログラム例で示されます。

| アセンブリ言語プログラ  | ム例     |            |                      |

|--------------|--------|------------|----------------------|

| \$0000       | ORG    | \$0000     | ;プログラム用フラッシュ メモリ先頭位置 |

| Ф0000        | D TMD  | DECEM      | · ይደብ ከ 1            |

| \$0000       | RJMP   | RESET      | ;各種リセット              |

| \$0001       | RJMP   | INTO       | ;外部割9込み要求0           |

| \$0002       | RJMP   | PCINTO     | ;ピン変化0群割り込み要求        |

| \$0003       | RJMP   | PCINT1     | ;ピン変化1群割り込み要求        |

| \$0004       | RJMP   | PCINT2     | ;ピン変化2群割り込み要求        |

| \$0005       | RJMP   | WDT        | ;ウォッチドッグ計時完了         |

| \$0006       | RJMP   | TIM1_CAPT  | ;タイマ/カウンタ1捕獲発生       |

| \$0007       | RJMP   | TIM1_COMPA | ;タイマ/カウンタ1比較A一致      |

| \$0008       | RJMP   | TIM1_COMPB | ;タイマ/カウンタ1比較B一致      |

| \$0009       | RJMP   | TIM1_OVF   | ;タイマ/カウンタ1溢れ         |

| \$000A       | RJMP   | TIMO_COMPA | ;タイマ/カウンタ0比較A一致      |

| \$000B       | RJMP   | TIMO_COMPB | ;タイマ/カウンタ0比較B一致      |

| \$000C       | RJMP   | TIMO_OVF   | ;タイマ/カウンタ0溢れ         |

| \$000D       | RJMP   | ANA_COMP   | ;アナログ比較器出力遷移         |

| \$000E       | RJMP   | ADC        | ;A/D変換完了             |

| \$000F       | RJMP   | TWI_SLAVE  | ;2線インターフェース          |

| \$0010       | RJMP   | SPI        | ;直列周辺インターフェース        |

| \$0011       | RJMP   | QTRIP      | ;接触感知                |

| •            | · ·    | •          |                      |

| \$0012 RESET | : "命令" |            | ;主プログラム開始            |

注: 5頁の「**コード例**」をご覧ください。

# 9.2. 外部割り込み

外部割り込みはINT0ピンまたはPCINT0~17ピンの何れかによって起動されます。許可したなら、例えINT0またはPCINT0~17ピンが出力として設定されても、割り込みが起動することに注目してください。この特徴はソフトウェア割り込みを生成する方法を提供します。

ピン変化割り込みPCIOは許可したPCINTO~7の何れかが切り替わると起動します。ピン変化割り込みPCIIは許可したPCINT8~11の何れかが切り替わると起動します。ピン変化割り込みPCI2は許可したPCINT12~17の何れかが切り替わると起動します。ピン変化割り込み許可レジスタn(PCMSKO,PCMSK1,PCMSK2)は、どのピンがピン変化割り込み要因となるかを制御します。PCINTO~17でのピン変化割り込みは非同期に検知され、そしてそれはそれらの割り込みがアイドル動作以外の休止形態動作からもデバイスを起動するのに使えることを意味します。

INT0割り込みは上昇端または下降端(含む両端)またはLowレヘルによって起動できます。これはMCU制御レジスタ(MCUCR)で示されるように設定されます。INT0割り込みがレヘル起動として設定、且つ許可されると、そのピンがLowに保持される限り、割り込みは(継続的に)起動します。INT0の上昇端または下降端割り込みの認知は14頁の「クロック体系」で記述されるI/Oクロックの存在を必要とすることに注意してください。

# 9.2.1. Lowレベル割り込み

INT0のLowレヘル割り込みは非同期に検知されます。これはそれらの割り込みがアイル動作以外の休止形態動作からもデバイスを起動するのに使えることを意味します。I/Oクロックはアイル動作を除く全休止形態動作で停止されます。

レヘル起動割り込みがハプーダウン動作からの起動に使われる場合、この必要としたレヘルはレヘル割り込みを起動する完全な起動復帰のため、MCUに対して充分長く保持されなければならないことに注意してください。このレヘルが起動時間の最後に先立って消滅すると、MCUは今までどおり起動しますが、割り込みが生成されません。起動時間は14頁の「クロック体系」で示されるように定義されます。デバイスが起動復帰する前に割り込みピン上のLowレヘルが取り去られると、プログラム実行は割り込み処理ルーチンへ転換されませんが、SLEEP命令に続く命令から継続します。

# 9.2.2. ピン変化割り込みタイミング

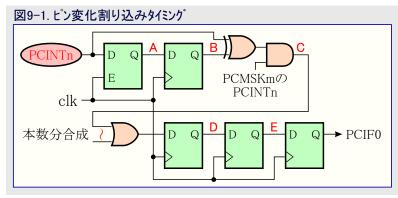

ピン変化割り込みのタイシンが例は図9-1.で示されます。

### 9.3. 割り込み用レジスタ

### 9.3.1. MCUCR - MCU制御レジスタ (MCU Control Register)

このMCU制御レジスタは条件制御と電力管理用の制御ビットを含みます。

| ピット        | 7     | 6     | 5 | 4    | 3   | 2   | 1   | 0   | _     |

|------------|-------|-------|---|------|-----|-----|-----|-----|-------|

| \$3A       | ISC01 | ISC00 | - | BODS | SM2 | SM1 | SM0 | SE  | MCUCR |

| Read/Write | R/W   | R/W   | R | R/W  | R/W | R/W | R/W | R/W |       |

| 初期値        | 0     | 0     | 0 | 0    | 0   | 0   | 0   | 0   |       |

#### ● ビット1,0 - ISC01,0:外部割り込み0条件制御 (Interrupt Sense Control 0 bit1 and 0)

外部割り込み0はステータスレジスタ(SREG)の全割り込み許可(I)ビットと外部割り込み許可レジスタ(EIMSK)の外部割り込み0許可(INTO)ビットが設定(1)される場合のINT 0外部ピッレによって活性(有効)にされます。割り込みを活性にする外部INTOピックのエッジとレベルは表9-2.で定義されます。INTOピッの値はエッジ検出に先立って採取されます。エッジまたは論理変化割り込みが選択される場合、1クロック周期よりも長く留まるパルスは割り込みを生成します。より短いパルスは割り込み発生が保証されません。Lowレベル割り込みが選択される場合、そのLowレベルは割り込みを生成するのに現在実行している命令の完了まで保たれなければなりません。

| 表9-2. 外部割り込み0(INTO)割り込み条件 |       |                 |  |  |  |  |

|---------------------------|-------|-----------------|--|--|--|--|

| ISC01                     | ISC00 | 割り込み発生条件        |  |  |  |  |

| 0                         | 0     | INT0ピンのLowレヘブル  |  |  |  |  |

| 0                         | 1     | INT0ピンの論理変化(両端) |  |  |  |  |

| 1                         | 0     | INT0ピンの下降端      |  |  |  |  |

| 1                         | 1     | INT0ピンの上昇端      |  |  |  |  |

# 9.3.2. GIMSK - 一般割り込み許可レジスタ (General Interrupt Mask Register)

| ピット           | 7  | 6      | 5      | 4      | 3   | 2  | 1  | 0      |       |

|---------------|----|--------|--------|--------|-----|----|----|--------|-------|

| \$0C          | _  | PCIE2  | PCIE1  | PCIE0  | -   | -  | -  | INT0   | GIMSK |

| Read/Write    | R  | R/W    | R/W    | R/W    | R   | R  | R  | R/W    |       |

| 10000/ 111100 | 11 | 14/ ** | 10, 11 | 14, 11 | 1 ( | 11 | 11 | 11/ 11 |       |

#### ● ビット7 - Res: 予約 (Reserved)

このビットは予約されており、常に0として読まれます。

#### ● ビット6 - PCIE2: ピン変化2群割り込み許可 (Pin Change Interrupt Enable 2)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットが設定(1)され、PCIE2ビットが設定(1)されると、ピン変化割り込み2が許可されます。許可したPCINT12~17ピンの何れかの変化が割り込みを起こします。このピン変化割り込み要求に対応する割り込みはPCI2割り込みへクタから実行されます。PCINT12~17ピンはピン変化割り込み許可レジスタ2(PCMSK2)によって個別に許可されます。

### ● ビット5 - PCIE1: ピン変化1群割り込み許可 (Pin Change Interrupt Enable 1)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットが設定(1)され、PCIE1ビットが設定(1)されると、ピン変化割り込み1が許可されます。許可したPCINT8~11ピンの何れかの変化が割り込みを起こします。このピン変化割り込み要求に対応する割り込みはPCI1割り込みへりタから実行されます。PCINT8~11ピンはピン変化割り込み許可レジスタ1(PCMSK1)によって個別に許可されます。

#### ● ビット4 - PCIE0: ピン変化0群割り込み許可 (Pin Change Interrupt Enable 0)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットが設定(1)され、PCIE0ビットが設定(1)されると、ピン変化割り込み0が許可されます。許可したPCINT0~7ピンの何れかの変化が割り込みを起こします。このピン変化割り込み要求に対応する割り込みはPCI0割り込みへ、クタから実行されます。PCINT0~7ピンはピン変化割り込み許可レジスタの(PCMSKO)によって個別に許可されます。

### ヒット3~1 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

### ● ビット0 - INTO:外部割り込み0許可(External Interrupt Request 0 Enable)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットが設定(1)され、INT0ビットが設定(1)されると、INT0外部ピン割り込みが許可されます。MCU制御レジスタ(MCUCR)の割り込み条件制御0のビット(ISC01,ISC00)は、この外部割り込みがINT0ピンの上昇端、下降端、両端、またはLowレベルのどれで活性(有効)にされるかを定義します。例えINT0ピンが出力として設定されても、このピンの動きは割り込み要求を引き起こします。外部割り込み要求0に対応する割り込みはINT0割り込みへブタから実行されます。

# 9.3.3. GIFR - 一般割り込み要求フラク・レシズタ (General Interrupt Flag Register)

| ピット        | 7 | 6     | 5     | 4     | 3 | 2 | 1 | 0     | _   |

|------------|---|-------|-------|-------|---|---|---|-------|-----|

| \$0B       | _ | PCIF2 | PCIF1 | PCIF0 | - | - | - | INTF0 | GIF |

| Read/Write | R | R/W   | R/W   | R/W   | R | R | R | R/W   |     |

| 初期値        | 0 | 0     | 0     | 0     | 0 | 0 | 0 | 0     |     |

# ● ビット7 - Res: 予約 (Reserved)

このビットは予約されており、常に0として読まれます。

## ● ビット6 - PCIF2: ピン変化2群割り込み要求フラグ(Pin Change Interrupt Flag 2)

PCINT12~17t°ンの何れかの論理変化が割り込み要求を起動すると、PCIF2が設定(1)になります。ステータスレシ、スタ(SREG)の全割り込み許可(I)t'ットと一般割り込み許可レシ、スタ(GIMSK)のt°ン変化2群割り込み許可(PCIE2)t'ットが設定(1)なら、MCUは対応する割り込み へクタへ飛びます。このフラク、は割り込み処理ルーチンが開始されると解除(0)されます。代わりにこのフラク、は論理1を書くことによっても解除(0)できます。

#### ● ビット5 - PCIF1 : ピン変化1群割り込み要求フラグ (Pin Change Interrupt Flag 1)

PCINT8~11  $\mathfrak L^2$ ンの何れかの論理変化が割り込み要求を起動すると、PCIF1が設定(1)になります。ステータスレジスタ(SREG)の全割り込み許可(I)  $\mathfrak L^2$  大学の何れかの論理変化が割り込み要求を起動すると、PCIF1が設定(1) になります。ステータスレジスタ(SREG)の全割り込み 共計の表決には、MCUは対応する割り込み、かりな一般では、このフラグは割り込み処理ルーチンが開始されると解除(0)されます。代わりにこのフラグは論理1を書くことによっても解除(0)できます。

# ● ビット4 - PCIFO: ピン変化0群割り込み要求フラグ (Pin Change Interrupt Flag 0)

PCINT0~7ピンの何れかの論理変化が割り込み要求を起動すると、PCIF0が設定(1)になります。ステータスレジスタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レジスタ(GIMSK)のピン変化0群割り込み許可(PCIE0)ビットが設定(1)なら、MCUは対応する割り込みへ,クタへ飛びます。このフラグは割り込み処理ルーチンが開始されると解除(0)されます。代わりにこのフラグは論理1を書くことによっても解除(0)できます。

#### ビット3~1 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

#### ● ビット0 - INTF0:外部割り込み0要求フラグ(External Interrupt Flag 0)

INTOピン上のエッジまたは論理変化が割り込み要求を起動すると、INTFOが設定(1)になります。ステータスレシ、スタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レシ、ス(GIMSK)の外部割り込み0許可(INTO)ビットが設定(1)なら、MCUは対応する割り込みへ、クタへ飛びます。このフラク、は割り込みルーチンが実行されると解除(0)されます。代わりにこのフラク、は論理1を書くことによっても解除(0)できます。INTOがレヘル割り込みとして設定されると、このフラク、は継続的に解除(0)されます。

# 9.3.4. PCMSK2 - ピン変化割り込み許可レジスタ2 (Pin Change Mask Register 2)

| ピット        | 7 | 6 | 5       | 4       | 3       | 2       | 1       | 0       |        |

|------------|---|---|---------|---------|---------|---------|---------|---------|--------|

| \$1A       | _ | - | PCINT17 | PCINT16 | PCINT15 | PCINT14 | PCINT13 | PCINT12 | PCMSK2 |

| Read/Write | R | R | R/W     | R/W     | R/W     | R/W     | R/W     | R/W     |        |

| 初期値        | 0 | 0 | 0       | 0       | 0       | 0       | 0       | 0       |        |

### ビット7,6 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

# ● ビット5~0 - PCINT17~PCINT12: ピン変化割り込み17~12許可 (Pin Change Enable Mask 17~12)

各PCINT12~17ビットは対応するI/Oピンでピン変化割り込みが許可されるかどうかを選びます。PCINT12~17と一般割り込み許可レジスタ(GIMSK)のPCIE2が設定(1)なら、対応するI/Oピンのピン変化割り込みが許可されます。PCINT12~17が解除(0)されると、対応するI/Oピンのピン変化割り込みは禁止されます。

## 9.3.5. PCMSK1 - ピン変化割り込み許可レジスタ1 (Pin Change Mask Register 1)

| ピット        | 7 | 6 | 5 | 4 | 3       | 2       | 1      | 0      |        |

|------------|---|---|---|---|---------|---------|--------|--------|--------|

| \$0A       | - | - | - | - | PCINT11 | PCINT10 | PCINT9 | PCINT8 | PCMSK1 |

| Read/Write | R | R | R | R | R/W     | R/W     | R/W    | R/W    |        |

| 初期値        | 0 | 0 | 0 | 0 | 0       | 0       | 0      | 0      |        |

### ヒット7~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

#### ● ビット3~0 - PCINT11~PCINT8 : ピン変化割り込み11~8許可 (Pin Change Enable Mask 11~8)

各PCINT8~11ビットは対応するI/Oピンでピン変化割り込みが許可されるかどうかを選びます。PCINT8~11と一般割り込み許可レジスタ (GIMSK)のPCIE1が設定(1)なら、対応するI/Oピンのピン変化割り込みが許可されます。PCINT8~11が解除(0)されると、対応するI/O ピンのピン変化割り込みは禁止されます。

### 9.3.6. PCMSKO - ピン変化割り込み許可レジスタO (Pin Change Mask Register 0)

| ピット        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |        |

|------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| \$09       | PCINT7 | PCINT6 | PCINT5 | PCINT4 | PCINT3 | PCINT2 | PCINT1 | PCINT0 | PCMSK0 |

| Read/Write | R/W    |        |

| 初期値        | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |        |

#### ● ビット7~0 - PCINT7~PCINT0 : ピン変化割り込み7~0許可 (Pin Change Enable Mask 7~0)

各PCINT0~7ビットは対応するI/Oピンでピン変化割り込みが許可されるかどうかを選びます。PCINT0~7と一般割り込み許可レジスタ (GIMSK)のPCIE0が設定(1)なら、対応するI/Oピンのピン変化割り込みが許可されます。PCINT0~7が解除(0)されると、対応するI/Oピンのピン変化割り込みは禁止されます。

# 10. 入出力ポート

## 10.1. 概要

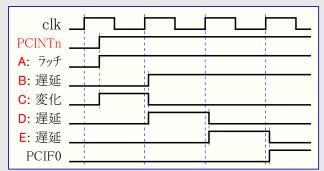

全てのAVRのポートは標準デジタルI/Oポートとして使われる時に真の読み-変更-書き (リート、モディファイライト)を機能的に持ちます。これはSBIとCBI命令で他のどのピンの方 向をも無意識に変更することなく、1つのポートピンの方向を変更できることを意味し ます。(出力として設定されていれば)駆動値を変更、またはプルアップ抵抗を許可/禁 止する時にも同じく適用されます。各出力緩衝部は高い吐き出し(ソース)と吸い込み (シンケ)の両能力で対称的な駆動特性を持ちます。このピン駆動部はLED(表示器)を 直接駆動するのに充分な強さです。全てのポートピンは個別に選択可能な、供給電 圧で抵抗値が変化しないプルアップ抵抗を持っています。全てのI/Oピンは図10-1.で 示されるようにVCCとGNDの両方に保護ダイオードがあります。各値の完全な一覧に ついては108頁の「電気的特性」を参照してください。

本項内の全てのレシ、スタとビットの参照は一般形で記されます。小文字の'x'はポート番

号文字、小文字の'n'はビット番号を表します。けれどもプログラム内でレジスタやビット定義に使うとき、正確な形式(例えば、ここで一般に 記されたPORTxnがポートBのビット3に対してはPORTB3)が使われなければなりません。物理的なI/Oレジスタとビット位置は41頁の「I/O ポート用レジスタ」で一覧されます。

各々1つの出力レジスタ(PORTx)、方向レシ、スタ(DDRx)、プルアップ許可レシ、スタ(PUEx)、入力レシ、スタ(PINx)の各ポートに対して、4つI/Oメモリ アドレス位置が割り当てられます。入力レジスタのI/O位置は読むだけで、一方出力レジスタ、方向レジスタ、プルアップ許可レジスタは読み書き (両方)です。けれどもPINxレジスタのビットへの論理1書き込みは、出力レジスタの対応ビット値を(1/0)反転する結果になります。

標準デンタルI/OとしてのI/Oポートの使用は次の「標準デンタル入出力としてのポート」で記述されます。多くのポート ピンはデバイスの周辺 機能用の交換機能と多重化されます。 ポート ピンとの各交換機能のインターフェース法は34頁の「<mark>交換ポート機能</mark>」で記述されます。 交換機 能の完全な記述については個別機能部項目を参照してください。

ポートピンのいくつかの交換機能の許可は、そのポート内の他のピンの標準デジタル入出力としての使用に影響しないことに注意してくだ さい。

# 10.2. 標準デジタル入出力としてのポート

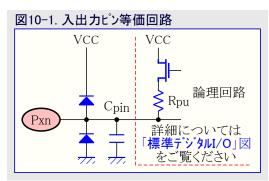

このポートは任意の内部プルアップ付き双方向I/Oポートです。 図10-2.はここで属にPxnと呼ばれるI/Oポート ピンの1つの機能説明を示し ます。

注: WEx, WRx, WPx WDx, REx, RRx, RPx, RDxは同一ポート内の全ピンで共通です。 clk<sub>I</sub>/OとSLEEPは全ポートで共通です。

#### 10.2.1. ピンの構成設定

各ポート ピンはDDxn、PUExn、PORTxn、PINxnの4つのレジスタ ビットから成ります。41頁の「I/Oポート用レジスタ」で示されるように、DDxn ビットはDDRx I/O位置、PUExnビットはPUEx I/O位置、PORTxnビットはPORTx I/O位置、PINxビットはPINx I/O位置でアクセスされます。

DDRxレジスタ内のDDxnビットはそのピンの方向を選択します。DDxnが論理1を書かれるとPxnは出力ピンとして設定されます。DDxnが論理0を書かれるとPxnは入力ピンとして設定されます。

そのピンが出力ピンとして設定される時にPORTxnが論理1を書かれると、そのポート ピンはHigh(1)に駆動されます。そのピンが出力ピンとして設定される時にPORTxnが論理0を書かれると、そのポート ピンはLow(0)に駆動されます。

PUExnが論理1を書かれた場合にプルアップ抵抗が活性(有効)にされます。プルアップ抵抗をOFFに切り替えるにはPUExnが論理0を書かれなければなりません。

表10-1.はピン値に対する制御信号を要約します。

表10-1. ポート ピンの設定

| DDxn | PORTxn | PUExn | 入出力 | プルアップ抵抗 | 備考                                                                  |

|------|--------|-------|-----|---------|---------------------------------------------------------------------|

| 0    | X      | 0     | 入力  | なし      | 高インピーダンス (Hi-Z)                                                     |

| 0    | X      | 1     | 入力  | あり      | 外部的にLowへ引かれた場合に電流を吐き出します。                                           |

| 1    | 0      | 0     | 出力  | なし      | Low (吸い込み)出力                                                        |

| 1    | 0      | 1     | 出力  | あり      | 非推奨: Low (吸い込み)出力、内部プルアップ活性(有効)<br>内部プルアップ抵抗を通して電流を吐き出し、常に電力を消費します。 |

| 1    | 1      | 0     | 出力  | なし      | High (吐き出し)出力                                                       |

| 1    | 1      | 1     | 出力  | あり      | High (吐き出し)出力、内部プルアップ活性(有効)                                         |

ポート ピンは例えクロックが動いていなくても、リセット条件が活性(有効)になるとHi-Zにされます。

### 10.2.2. ピンの出力交互切り替え

PINxnへの論理1書き込みはDDRxnの値に拘らず、PORTxnの値を反転切り替えします。SBI命令がポート内の1ビットの反転切り替えに使えることに注目してください。

#### 10.2.3. 接続前切断(Break-Before-Make)切り替え

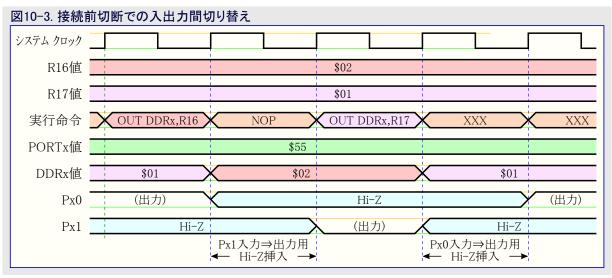

接続前切断動作ではDDRxnを入力から出力へ切り換える時に1システム クロック持続する隣接Hi-Z区間が**図10-3**.で示されるように導入されます。例えば、システム クロックが4MHzでDDRxnが出力にするように書かれた場合、PORTxnの値がポート ピンで見える前に250nsの隣接Hi-Z区間が導入されます。

異常を避けるため、DDRxn最大切り替え周波数は2システム クロックが推奨されます。この接続前切断はポート単位動作で、ポート単位の接続前切断許可(BBMx)ビットによって活性(有効)にされます。BBMxビットの詳細については41頁の「PORTCR - ホート制御レジスタ」をご覧ください。

DDRxnt ットを出力から入力に切り替える時に隣接Hi-Z区間は導入されません。

### 10.2.4. ピン値の読み込み

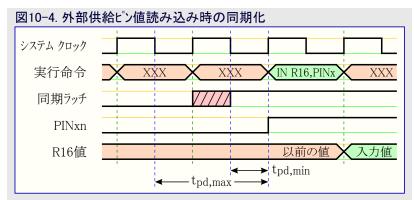

DDxn方向ビットの設定に関係なく、ポート ピンはPINxnレジスタ ビットを通して読めます。図10-2.で示されるようにPINxn レジスタ ビットと先行するラッチは同期化回路を構成します。これは物理ピンが内部クロックのエッジ付近で値を変える場合の未定義状態(メタ ステーブル)を避けるために必要とされますが、それは遅延も持ち込みます。図10-4.は外部的に加えられたピン値を読む時の同期化タイミング図を示します。伝播遅延の最小と最大は各々tpd,minとtpd,maxで示されます。

(図10-4.で)システム クロックの最初の下降端直後から始まるクロック周期を考察してください。このラッチはクロックがLowの時に閉じ、クロックがHighの時に同期ラッチ信号の斜線部分で示されるように通過(トランスペアレント)となります。この信号値はシステム クロックがLowになる時に保持(ラッチ)されます。それが続くクロックの上昇端でPINxnレジスタに取り込まれます。2つの矢印tpd,minとtpd,maxによって示されるように、ピン上の単一信号遷移は出現時点に依存して0.5~1.5システムクロック周期遅らされます。

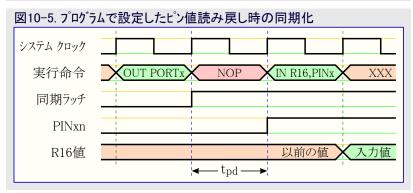

ソフトウェアが指定したピン値を読み戻す時は、図10-5.で示されるようにNOP命令が挿入されなければなりません。OUT命令はシステムクロックの上昇端で同期ラッチを設定します。この場合、同期化回路を通過する遅延時間(tpd)は1システムクロック周期です。

# 10.2.5. デジタル入力許可と休止形態動作

図10-2.で示されるようにデジタル入力信号はシュミット トリガの入力をGNDにクランプできます。この図でSLEEPと印された信号は入力信号のいくつかが開放のまま、またはVCC/2付近のアナログ信号電圧を持つ場合の高消費電力を避けるため、パワーダウン動作とスタンバイ動作でMCU休止制御器によって設定(1)されます。

SLEEPは外部割り込みピンとして許可されたポートピンに対して無視されます。外部割り込み要求が許可されないなら、SLEEPは他のピンについてと同様に有効です。SLEEPは34頁の「交換ポート機能」で記載されるように様々な他の交換機能によっても無視されます。

外部割り込みが許可されていない"上昇端、下降端または論理変化(両端)割り込み"として設定された非同期外部割り込みピンに論理1が存在すると、上で言及した休止形態動作から(復帰)再開する時に、これらの休止形態動作に於けるクランプが要求された論理変化を生ずるので、対応する外部割り込み要求フラグが設定(=1)されます。

#### 10.2.6. 未接続ピン

いくつかのピンが未使用にされる場合、それらのピンが定義されたレベルを持つことの保証が推奨されます。例え上記のような深い休止 形態動作で多くのデンダル入力が禁止されるとしても、デンダル入力が許可される他の全ての動作(リセット、活動動作、アイドル動作)で消費電流削減のため、浮き状態入力は避けられるべきです。

未使用ピンの定義されたレベルを保証する最も簡単な方法は内部プルアップを許可することです。この場合、リセット中のプルアップは禁止されます。リセット中の低消費電力が重要なら、外部のプルアップまたはプルダウンを使うことが推奨されます。未使用ピンを直接GNDまたはVCCに接続することは、ピンが偶然に出力として設定されると過電流を引き起こす可能性があるため推奨されません。

# 10.2.7. プログラム例

次のコート・例はポートBピンの0をHigh出力、1をLow出力、2をプルアップ指定として2と3を入力に設定する方法を示します。結果のピン値が再び読み戻されますが、前記で検討されたように、いくつかのピンへ直前に指定された値を読み戻すことができるようにNOP命令が挿入されます。

| -1*:                              |                                                                      |              |

|-----------------------------------|----------------------------------------------------------------------|--------------|

| アセンブリ言語プログラム例                     |                                                                      |              |

| LDI                               | R16, (1< <pueb2)< th=""><th>;プルアップ許可値を取得</th></pueb2)<>              | ;プルアップ許可値を取得 |

| OUT                               | PUEB, R16                                                            | ;プルアップを設定    |

| LDI                               | R16, (1< <pb0)< th=""><th>;High値を取得</th></pb0)<>                     | ;High値を取得    |

| OUT                               | PORTB, R16                                                           | ;High値を設定    |

| LDI                               | R16, (1< <ddb1) (1<<ddb0)<="" th=""  =""><th>;出力ビット値を取得</th></ddb1)> | ;出力ビット値を取得   |

| OUT                               | DDRB, R16                                                            | ;入出力方向を設定    |

| NOP                               |                                                                      | ;同期化遅延対処     |

| IN                                | R16, PINB                                                            | ;ピン値読み戻し     |

| <b>注</b> : 5頁の「 <b>コート</b> ・例」をご覧 | <b>管ください。</b>                                                        |              |

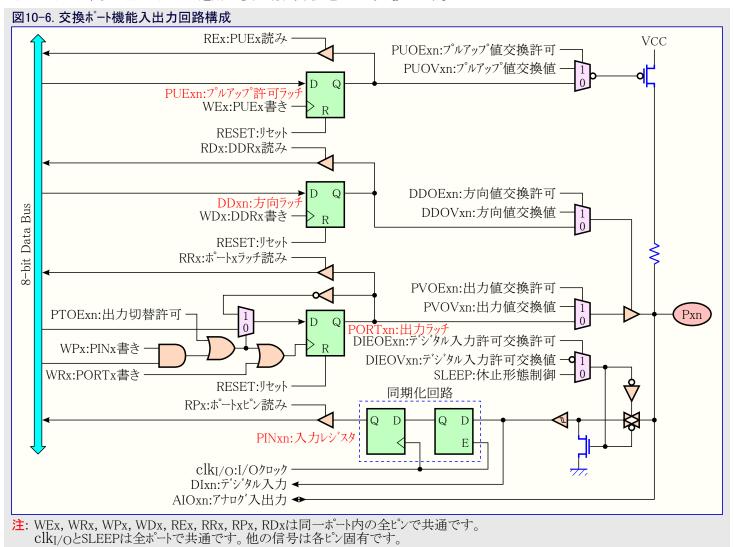

# 10.3. 交換ポート機能

多くのポート ピンには標準デジタル入出力に加え交換機能があります。下の図10-6.は単純化された31頁の図10-2.でのポート ピン制御信号が交換機能によってどう重複できるかを示します。この重複信号は全てのポート ピンに存在する訳ではありませんが、この図はAVRマイクロコントローラ系統の全ポート ピンに適用できる一般的な記述として取り扱います。

上の図の図解はAVRマイクロ コントローラ系統の全ポート ピンに適用できる一般的な記述として取り扱います。いくつかの重複信号は全てのポート ピンに存在しないかもしれません。

表10-2.は重複(交換)信号の機能一覧を示します。図10-6.で示すピンとポートは次表で示されません。重複(交換)信号は交換機能を持つ機能部で内部的に生成されます。

表10-2. 交換機能用交換信号の一般定義

| 信号略名  | 信号名              | 意味                                                                                         |  |  |

|-------|------------------|--------------------------------------------------------------------------------------------|--|--|

| PUOE  | プルアップ値交換許可       | 1で、プルアップ許可はPUOV信号で制御され、Oの場合、PUExn=1でプルアップが許可されます。                                          |  |  |

| PUOV  | プルアップ値交換値        | PUOE=1時、PUExnレシ、スタ ビット設定に関係なく、プルアップの有(1)/無(0)を指定します。                                       |  |  |

| DDOE  | 方向値交換許可          | 1で、出力駆動部はDDOV信号で制御され、0の場合、DDxnレジスタ値で制御されます。                                                |  |  |

| DDOV  | 方向値交換値           | DDOE=1時、DDxnレシ、スタ値に関係なく、出力駆動部のON(1)/OFF(0)を制御します。                                          |  |  |

| PVOE  | 出力値交換許可          | 1で出力駆動部がONなら、ポート値はPVOV信号で制御されます。出力駆動部がONで0なら、ポート値はPORTxnレジスタ値で制御されます。                      |  |  |

| PVOV  | 出力値交換値           | PVOE=1時、PORTxnレシ、スタ値に関係なく、ポート値を制御(1/0)します。                                                 |  |  |

| PTOE  | 出力切替許可           | PTOE=1時、PORTxnレシブスタ値が反転します。                                                                |  |  |

| DIEOE | デジタル入力許可<br>交換許可 | 1で、デジタル入力許可はDIEOV信号で制御され、Oの場合、MCUの状態(活動動作、休止形態動作)によって決定されます。                               |  |  |

| OIEOV | デジタル入力許可<br>交換値  | DIEOE=1時、MCUの状態(活動動作、休止形態動作)に関係なく、デジタル入力を許可(1)/禁止(0)します。                                   |  |  |

| DI    | デジタル入力           | 交換機能用デジタル入力です。この信号は図上でシュミット トリガ出力に接続されていますが、これは同期化前となります。本信号はクロックとしての使用を除き、各交換機能自身が同期化します。 |  |  |

| AIO   | アナログ入出力          | 交換機能用アナログ入出力です。この信号はピンに直接接続され、双方向使用ができます。                                                  |  |  |

次節は交換機能に関連する重複(交換)信号と各ポートの交換機能を簡単に記述します。更に先の詳細については交換機能の記述 を参照してください。

# 10.3.1. ホートAの交換機能

ポートAピンの交換機能は表10-3.で示されます。

#### 表10-3 ポートAピンの交換機能

| 式10 5. ↑ TAC 200 大俣版化              |                                                                         |                     |                                                                    |  |  |

|------------------------------------|-------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------|--|--|

| ホ <sup>°</sup> ート ヒ <sup>°</sup> ン | 交換機能                                                                    | ポ <sup>ー</sup> ト ピン | 交換機能                                                               |  |  |

| PA7                                | ADC7 (A/D変換チャネル7入力)<br>PCINT7 (ピン変化割り込み7入力)                             | PA3                 | ADC3 (A/D変換チャネル3入力)<br>PCINT3 (ピン変化割り込み3入力)                        |  |  |

| PA6                                | ADC6 (A/D変換チャネル6入力)<br>PCINT6 (ピン変化割り込み6入力)                             | PA2                 | ADC2 (A/D変換チャネル2入力)<br>AIN1 (アナログ比較器反転入力)<br>PCINT2 (ピン変化割り込み2入力)  |  |  |

| PA5                                | ADC5 (A/D変換チャネル5入力)<br>OC0B (タイマ/カウンタ0 比較B一致出力)<br>PCINT5 (ピン変化割り込み5入力) | PA1                 | ADC1 (A/D変換チャネル1入力)<br>AIN0 (アナログ比較器非反転入力)<br>PCINT1 (ピン変化割り込み1入力) |  |  |

| PA4                                | ADC4 (A/D変換チャネル4入力)<br>T0 (タイマ/カウンタ0 外部クロック入力)<br>PCINT4 (ピン変化割り込み4入力)  | PA0                 | ADC0 (A/D変換チャネル0入力)<br>PCINT0 (ピン変化割り込み0入力)                        |  |  |

- ポートA ビット7 : PA7 ADC7/PCINT7

- ADC7: A/D変換器チャネル7入力。

- ・PCINT7: ピン変化割り込み元7入力。PA7ピンはピン変化0群割り込みに対する外部割り込み元として扱えます。

- ホートA ヒット6: PA6 ADC6/PCINT6

- ADC6: A/D変換器チャネル6入力。

- ・PCINT6: ピン変化割り込み元6入力。PA6ピンはピン変化0群割り込みに対する外部割り込み元として扱えます。

- π°-トΑ L"ット5 : PA5 ADC5/OC0B/PCINT5

- ・ADC5: A/D変換器チャネル5入力。

- ・OCOB: タイマ/カウンタ0の比較B一致出力。PA5ピンはタイマ/カウンタ0の比較B一致用外部出力として扱えます。この機能を扱うため、このピンは出力として構成設定(DDA5=1)されなければなりません。OCOBピンはタイマ機能のPWM動作用出力ピンでもあります。

- ・PCINT5: ピン変化割り込み元5入力。PA5ピンはピン変化0群割り込みに対する外部割り込み元として扱えます。

- - ・ADC4: A/D変換器チャネル4入力。

- **TO**: タイマ/カウンタ0の外部クロック入力。

- ・PCINT4: ピン変化割り込み元4入力。PA4ピンはピン変化0群割り込みに対する外部割り込み元として扱えます。

- ポ-トA ビット3 : PA3 ADC3/PCINT3

- ADC3: A/D変換器チャネル3入力。

- ・PCINT3: ピン変化割り込み元3入力。PA3ピンはピン変化0群割り込みに対する外部割り込み元として扱えます。

- π°-トA L"ット2 : PA2 ADC2/AIN1/PCINT2

- ・ **ADC2**: A/D変換器チャネル2入力。

- ・AIN1: アナログ比較器の反転入力。アナログ比較器の機能を妨げるデジタルポート機能を避けるため、内部プルアップをOFFにした入力としてポート ピンを構成設定してください。

- ・PCINT2: ピン変化割り込み元2入力。PA2ピンはピン変化0群割り込みに対する外部割り込み元として扱えます。

- ホ°ートA ビット1 : PA1 ADC1/AIN0/PCINT1

- ・ADC1: A/D変換器チャネル1入力。

- ・AINO:アナログ比較器の非反転入力。アナログ比較器の機能を妨げるデジタルポート機能を避けるため、内部プルアップをOFFにした入力としてポート ピンを構成設定してください。

- ・PCINT1: ピン変化割り込み元1入力。PA1ピンはピン変化0群割り込みに対する外部割り込み元として扱えます。

- π°-トΑ Ľット0 : PA0 ADC0/PCINT0

- ADC0: A/D変換器チャネル0入力。

- ・PCINTO: ピン変化割り込み元0入力。PAOピンはピン変化0群割り込みに対する外部割り込み元として扱えます。

表10-4.と表10-5.はポートAの交換機能を34頁の図10-6.で示される交換信号に関連付けます。

表10-4. ポートA7~4の交換機能用交換信号

| 信号名   | PA7/ADC7/PCINT7      | PA6/ADC6/PCINT6      | PA5/ADC5/OC0B/PCINT5 | PA4/ADC4/T0/PCINT4   |  |

|-------|----------------------|----------------------|----------------------|----------------------|--|

| PUOE  | 0                    | 0                    | 0                    | 0                    |  |

| PUOV  | 0                    | 0                    | 0                    | 0                    |  |

| DDOE  | 0                    | 0                    | 0                    | 0                    |  |

| DDOV  | 0                    | 0                    | 0                    | 0                    |  |

| PVOE  | 0                    | 0                    | OC0B許可               | 0                    |  |

| PVOV  | 0                    | 0                    | OC0B                 | 0                    |  |

| PTOE  | 0                    | 0                    | 0                    | 0                    |  |

| DIEOE | PCIE0 • PCINT7+ADC7D | PCIE0 • PCINT6+ADC6D | PCIE0 • PCINT5+ADC5D | PCIE0 • PCINT4+ADC4D |  |

| DIEOV | PCIE0 • PCINT7       | PCIE0 • PCINT6       | PCIE0 • PCINT5       | PCIE0 • PCINT4       |  |

| DI    | PCINT7入力             | PCINT6入力             | PCINT5入力             | T0/PCINT4入力          |  |

| AIO   | ADC7入力               | ADC6入力               | ADC5入力               | ADC4入力               |  |

## 表10-5. ポートA3~0の交換機能用交換信号

| 信号名   | PA3/ADC3/PCINT3      | PA2/ADC2/AIN1/PCINT2 | PA1/ADC1/AIN0/PCINT1  | PA0/ADC0/PCINT0      |  |

|-------|----------------------|----------------------|-----------------------|----------------------|--|

| PUOE  | 0                    | 0                    | 0                     | 0                    |  |

| PUOV  | 0                    | 0                    | 0                     | 0                    |  |

| DDOE  | 0                    | 0                    | 0                     | 0                    |  |

| DDOV  | 0                    | 0                    | 0                     | 0                    |  |

| PVOE  | 0                    | 0                    | 0                     | 0                    |  |

| PVOV  | 0                    | 0                    | 0                     | 0                    |  |

| PTOE  | 0                    | 0                    | 0                     | 0                    |  |

| DIEOE | PCIE0 • PCINT3+ADC3D | PCIE0 • PCINT2+ADC2D | PCIE0 • PCINT1+ADC1D  | PCIE0 • PCINT0+ADC0D |  |

| DIEOV | PCIE0 • PCINT3       | PCIE0 • PCINT2       | PCIE0 • PCINT1        | PCIE0 • PCINT0       |  |

| DI    | PCINT3入力             | PCINT2入力             | PCINT1入力              | PCINT0入力             |  |

| AIO   | ADC3入力               | アナログ比較器反転/<br>ADC2入力 | アナログ比較器非反転/<br>ADC1入力 | ADC0入力               |  |

(訳注) 原書の表10-4.~6.は表10-4.と表10-5.に再合成しました。

## 10.3.2. ホ°ートBの交換機能

ポートBピンの交換機能は表10-7.で示されます。

#### 表10-7 ポートBピンの交換機能

| ポートし | で 交換機能                                          | ポート ピン | 交換機能                                        |  |  |

|------|-------------------------------------------------|--------|---------------------------------------------|--|--|

| PB3  | ADC11 (A/D変換チャネル11入力)<br>PCINT11 (ピン変化割り込み11入力) | PB1    | ADC9 (A/D変換チャネル9入力)<br>PCINT9 (ピン変化割り込み9入力) |  |  |

| PB2  | ADC10 (A/D変換チャネル10入力)<br>PCINT10 (ピン変化割り込み10入力) | PB0    | ADC8 (A/D変換チャネル8入力)<br>PCINT8 (ピン変化割り込み8入力) |  |  |

• ポートB ビット3 : PB3 - ADC11/PCINT11

・ADC11: A/D変換器チャネル11入力。

・PCINT11: ピン変化割り込み元11入力。PB3ピンはピン変化1群割り込みに対する外部割り込み元として扱えます。

• π°-トΒ ビット2 : PB2 - ADC10/PCINT10

・ADC10: A/D変換器チャネル10入力。

・PCINT10: ピン変化割り込み元10入力。PB2ピンはピン変化1群割り込みに対する外部割り込み元として扱えます。

• ポートB ビット1 : PB1 - ADC9/PCINT9

ADC9: A/D変換器チャネル9入力。

・PCINT9: ピン変化割り込み元9入力。PB1ピンはピン変化1群割り込みに対する外部割り込み元として扱えます。

• ポ-トB ビット0 : PB0 - ADC8/PCINT8

・ ADC8: A/D変換器チャネル8入力。

・PCINT8: ピン変化割り込み元8入力。PB0ピンはピン変化1群割り込みに対する外部割り込み元として扱えます。

表10-8.はポートBの交換機能を34頁の図10-6.で示される交換信号に関連付けます。

表10-8. ポートB3~0の交換機能用交換信号

| 信号名   | PB3/ADC11/PCINT11      | PB2/ADC10/PCINT10      | PB1/ADC9/PCINT9      | PB0/ADC8/PCINT8      |  |

|-------|------------------------|------------------------|----------------------|----------------------|--|

| PUOE  | 0                      | 0                      | 0                    | 0                    |  |

| PUOV  | 0                      | 0                      | 0                    | 0                    |  |

| DDOE  | 0                      | 0                      | 0                    | 0                    |  |

| DDOV  | 0                      | 0                      | 0                    | 0                    |  |

| PVOE  | 0                      | 0                      | 0                    | 0                    |  |

| PVOV  | 0                      | 0                      | 0                    | 0                    |  |

| PTOE  | 0                      | 0                      | 0                    | 0                    |  |

| DIEOE | PCIE1 • PCINT11+ADC11D | PCIE1 • PCINT10+ADC10D | PCIE1 • PCINT9+ADC9D | PCIE1 • PCINT8+ADC8D |  |

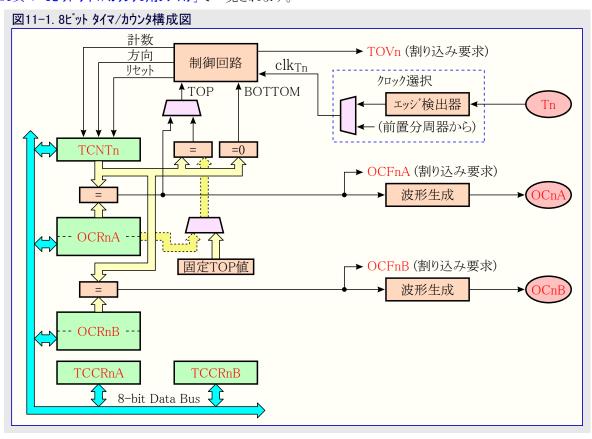

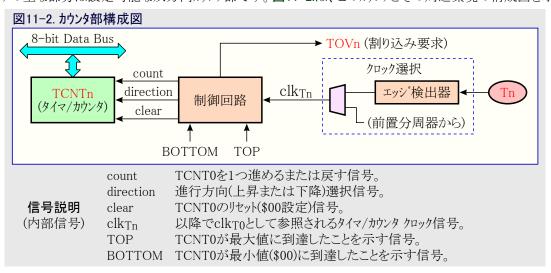

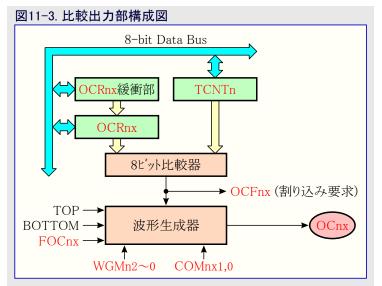

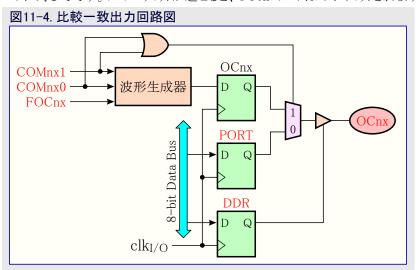

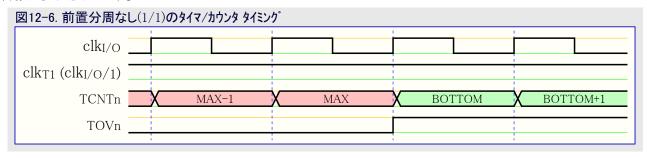

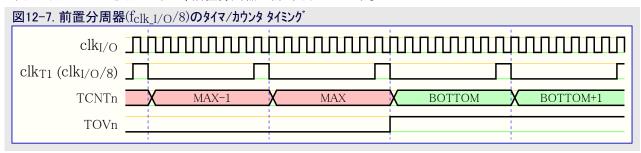

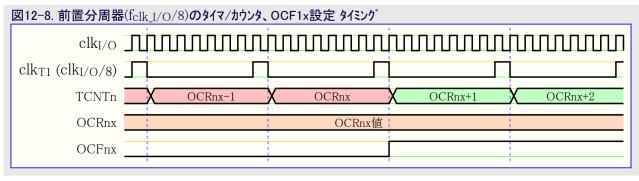

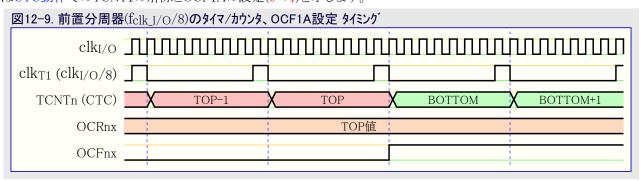

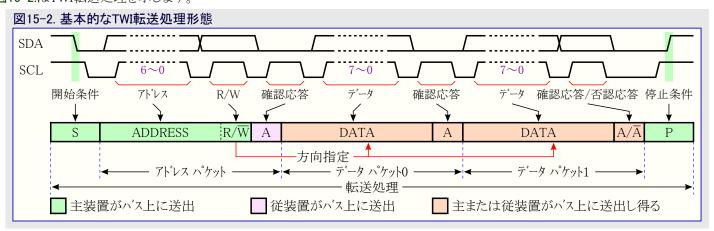

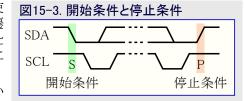

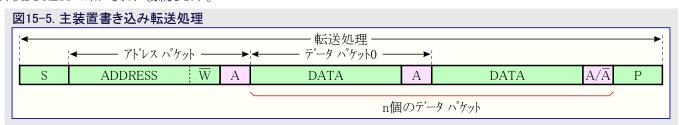

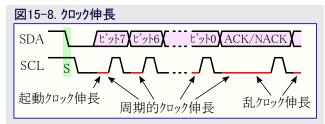

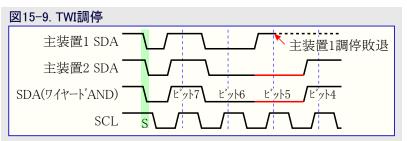

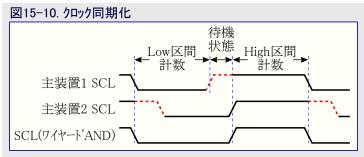

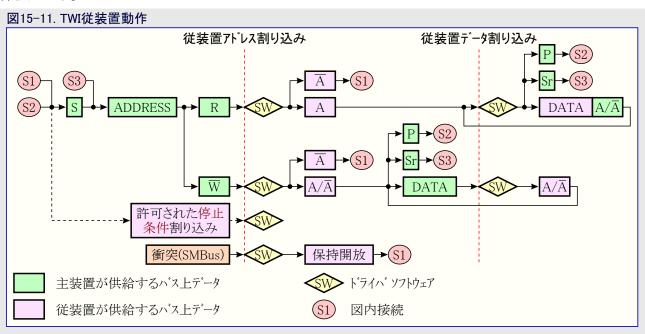

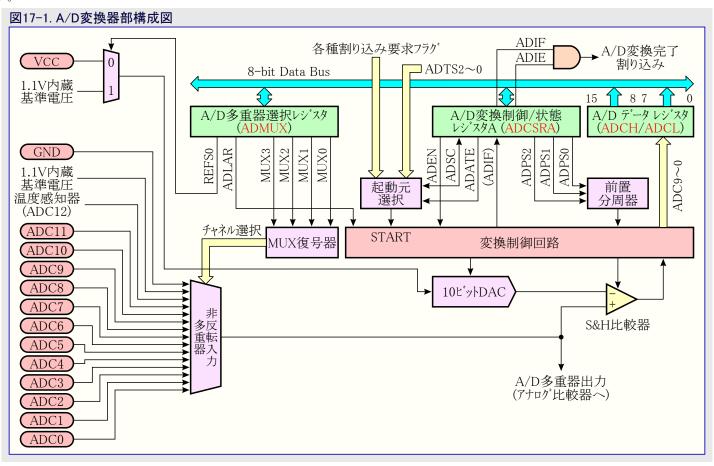

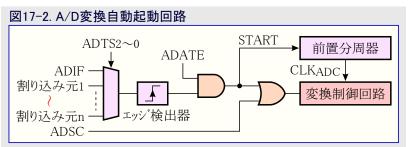

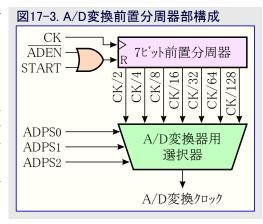

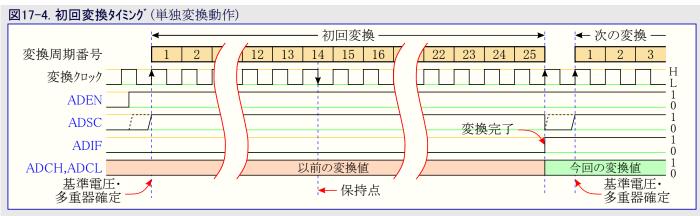

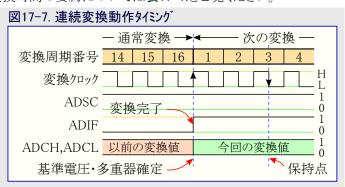

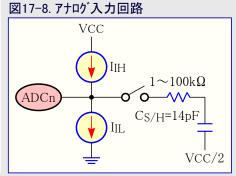

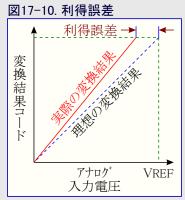

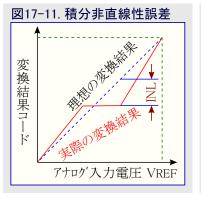

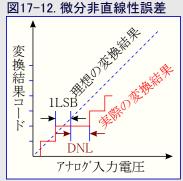

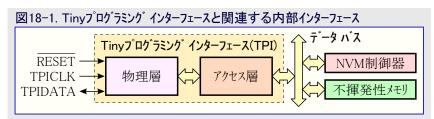

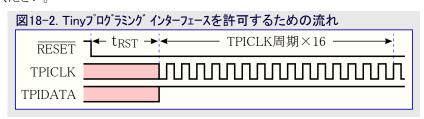

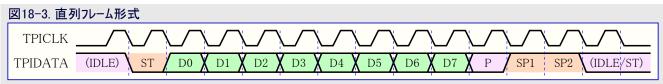

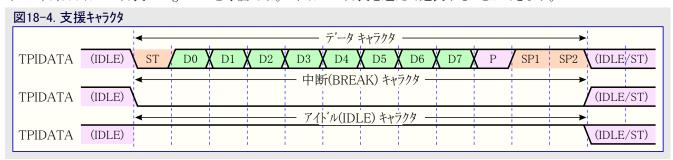

| DIEOV | PCIE1 • PCINT11        | PCIE1 • PCINT10        | PCIE1 • PCINT9       | PCIE1 • PCINT8       |  |