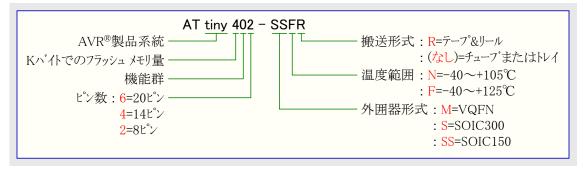

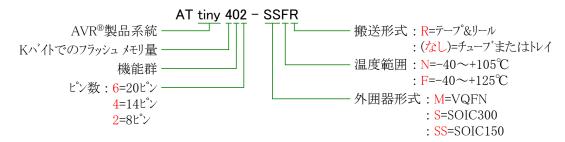

# ATtiny202/204/402/404/406

# tinyAVR® O系統

#### 序説

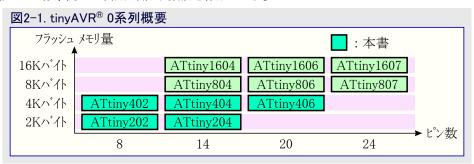

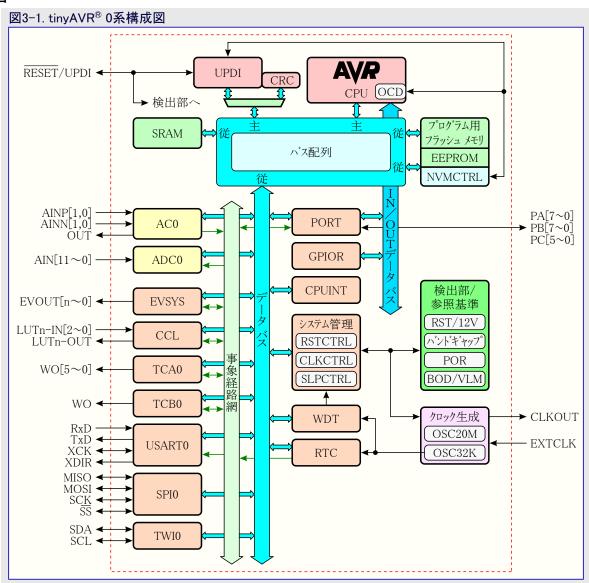

ATtiny202/204/402/404/406マイクロ コントローラはハート ウェア乗算器を持つAVR®プロセッサを使い、8、14、20ピン外囲器で 2/4Kハ イトのフラッシュ メモリ、128/256ハ イトのSRAM、64/128ハ イトのEEPROMを持ち、最大20MHzで動くtinyAVR® 0系統のマイクロ コントローラの一員です。tinyAVR® 0系統は事象システム、正確なアナログ機能、コアから独立した周辺機能を含む柔軟で低電力な基本構造を持つ最新技術を使います。

注意: このデータシートは工業に限定されたデバイスに対して有効です。

(<mark>訳注</mark>)・本書はATtiny202/204/402/404/406シリコン障害とデータシート説明(DS80000956B)の内容を含みます。

・原書に対して断りなく最新情報に更新している場合があります。

本書は一般の方々の便宜のため有志により作成されたもので、Microchip社とは無関係であることを御承知ください。しおりの[はじめに]での内容にご注意ください。

© 2021 Microchip Technology Inc. 完全データシート DS40002318A/J11 - 1頁

#### 特徴

- CPU

- AVR® CPU

- 最大20MHzで走行

- 単一周期I/Oアクセス

- 2段階の割り込み制御器

- 2周期ハート・ウェア乗算器

- メモリ

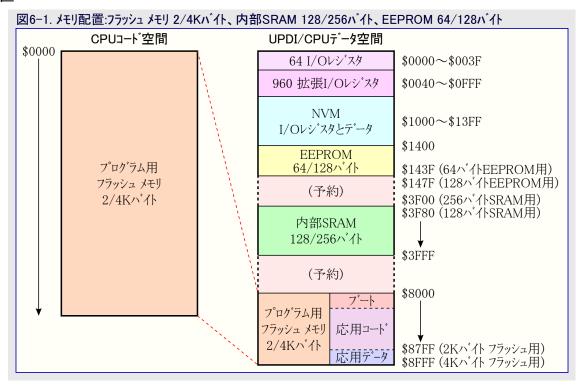

- 実装自己書き換え可能な2/4Kバイト(1/2K語)のフラッシュ メモリ

- 64/128 バイトのEEPROM

- 128/256バイトのSRAM

- 書き込み/消去寿命

- フラッシュ メモリ: 10,000回

- EEPROM: 100,000回

- データ保持力

- ·55℃で40年

- ・システム

- 電源ONリセット(POR)

- 低電圧検出器(BOD)

- クロック任意選択

- · 16/20MHz低電力内部RC発振器

- · 32.768kHz超低電力(ULP)内部RC発振器

- 外部クロック入力

- 単一ピンの統一プログラム/デバッグ インターフェース

- 3つの休止動作形態

- ・直ちに起き上がるために全ての周辺機能が動いているアイドル

- ・スタンバイ

- 選んだ周辺機能の構成設定可能な動作

- 完全なデータ保持を持つパワーダウン

- 周辺機能

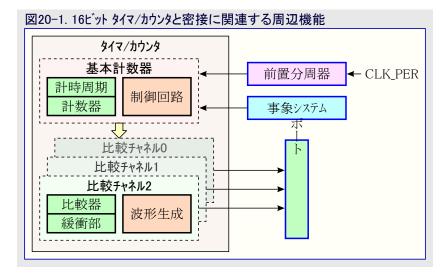

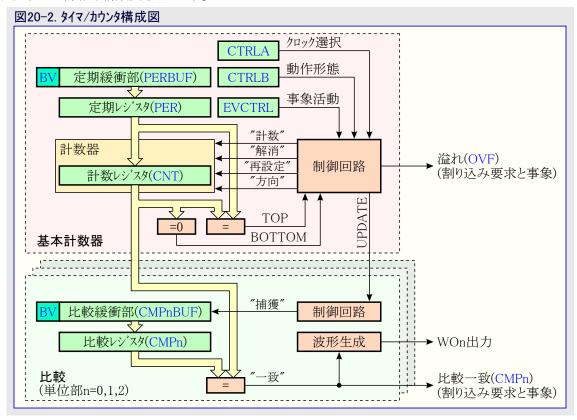

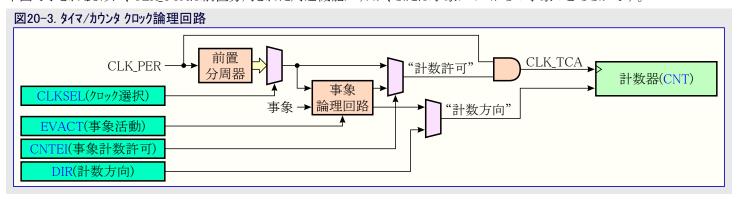

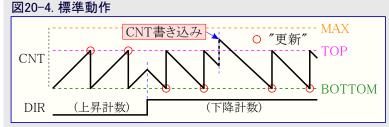

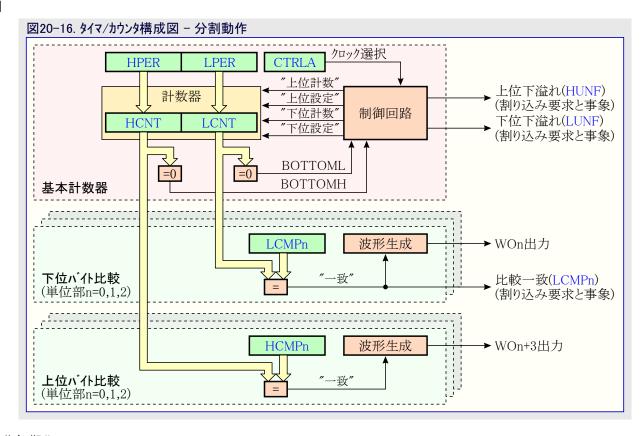

- 専用の定期レジスタと3つの比較チャネルを持つ1つの16ビット タイマ/カウンタA型 (TCA)

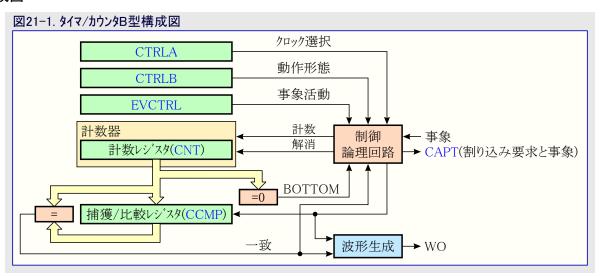

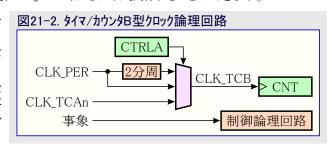

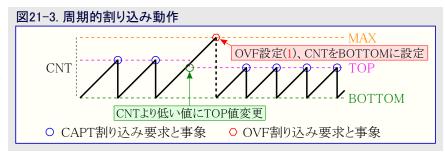

- 捕獲入力を持つ1つの16ビット タイマ/カウンタB型 (TCB)

- 外部クロックまたは内部RC発振器から走行する1つの16ビット実時間計数器 (RTC)

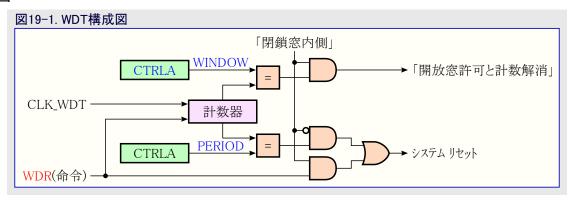

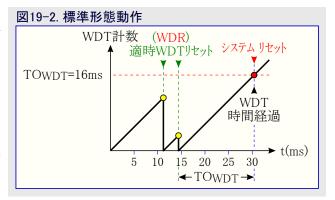

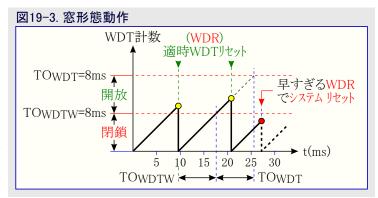

- 独立したチップ上の発振器を持ち、窓動作を持つウォッチドッグ タイマ (WDT)

- 分数ボーレート生成器、自動ボーレート、フレーム開始検出を持つ1つのUSART

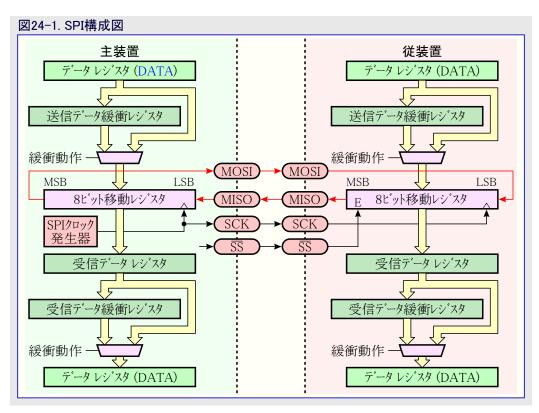

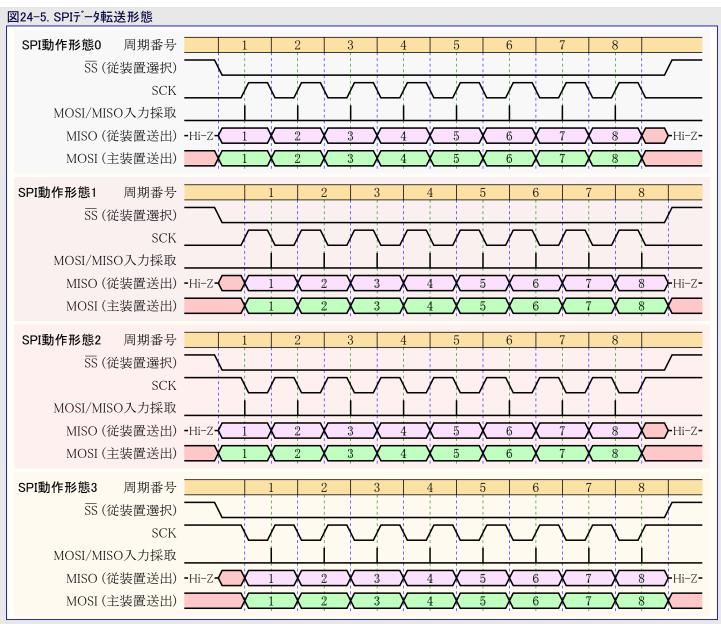

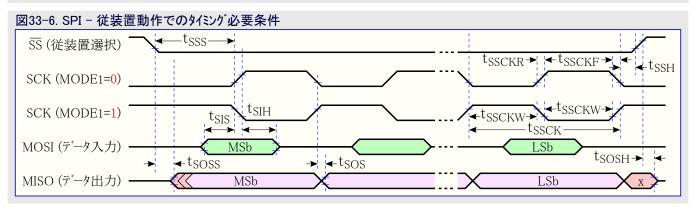

- 主装置/従装置直列周辺インターフェース (SPI)

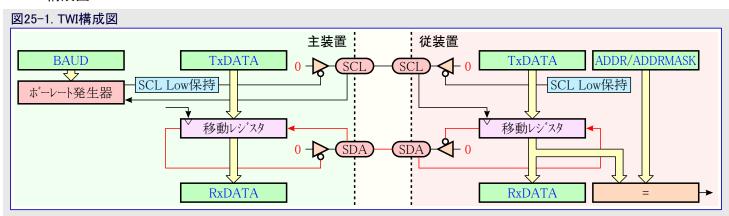

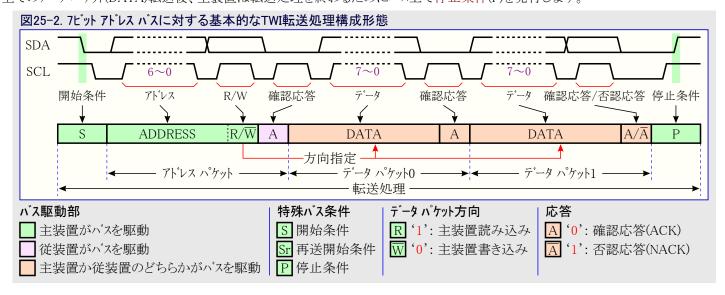

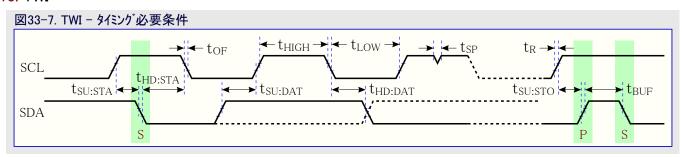

- 2重アドレス一致を持つ1つの2線インターフェース (TWI)

- Philips I<sup>2</sup>C互換

- ・標準動作 (Sm, 100kHz)

- ・高速動作 (Fm, 400kHz)

- ・高速動作プラス (Fm+, 1MHz)

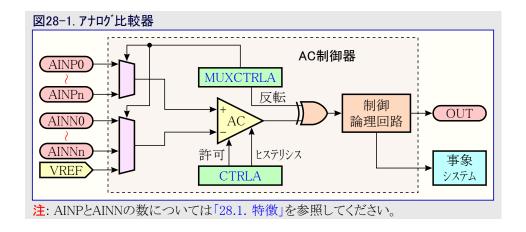

- 低伝搬遅延を持つ1つのアナログ比較器 (AC)

- 10ビット、115kspsの1つのA/D変換器 (ADC)

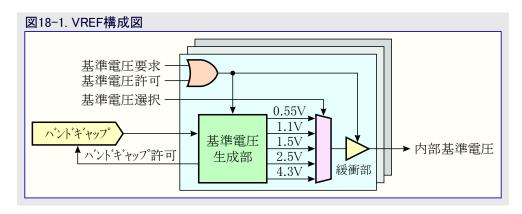

- 多数の参照基準電圧 (VREF)

- 1.1V

- 1.5V

- CPUから独立して予測可能な周辺機能相互合図のための事象システム (EVSYS)

• 2.5V

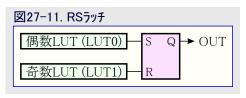

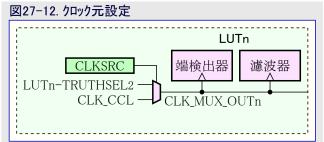

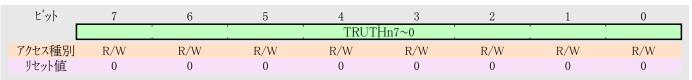

- 2つの設定可能な参照表(LUT)を持つ構成設定可能な注文論理回路 (CCL)

- 自動化されたCRCメモリ走査

- 全ての汎用ピンでの外部割り込み

- I/Oと外囲器

- 18本までの設定可能なI/O線

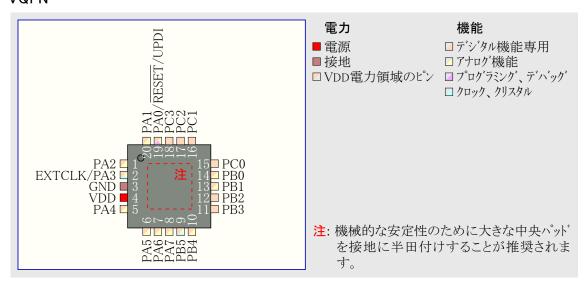

- 8リート、SOIC150、14リート、SOIC150、20リート、SOIC300、20ハット、VQFN 3×3mm

- 温度範囲

- --40~105°C

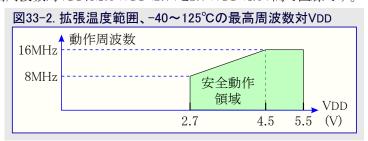

- --40~125°C

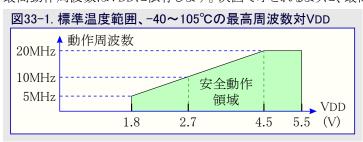

- ・速度評定

- $-0\sim5 MHz/1.8\sim5.5 V$

- $-0\sim10\text{MHz}/2.7\sim5.5\text{V}$

- $-0\sim20 MHz/4.5\sim5.5 V$

• 4.3V

# 目次

|            | 序説 ······ 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | 12.1. 特徴 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                |                |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------|----------------|

|            | <b>特徴 ······</b> 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | 12.2. 概要                                                    | 53             |

| 1.         | シリコン障害とデータシート説明文書 ・・・・・・・・・6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | 12.3. 機能的な説明 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・           | 53             |

|            | tinyAVR® 0系列概要 ·························6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | 12.4. レジスタ要約・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・            |                |

|            | 2.1. 製品形態要約                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | 12.5. レジスタ説明 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・           |                |

| 2          | 構成図・・・・・・・・・・・・ 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13. | CPUINT - CPU割り込み制御器 ······                                  | 58             |

|            | leが回 ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 13.1. 特徴                                                    | 58             |

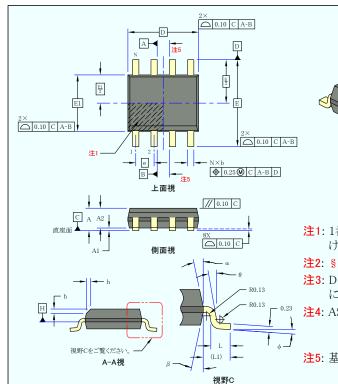

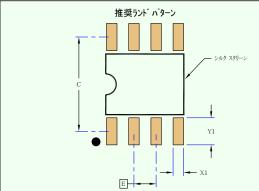

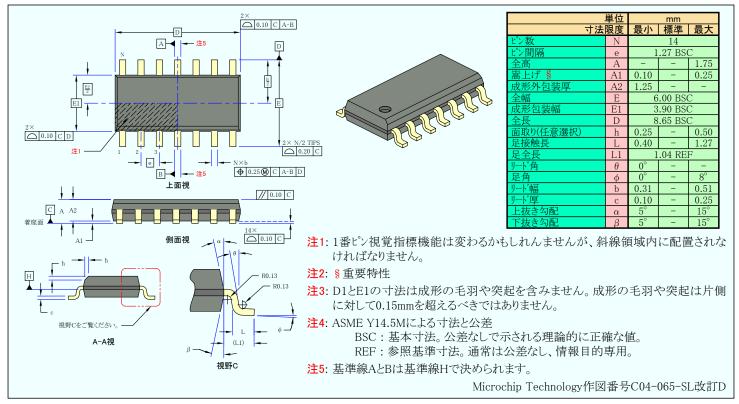

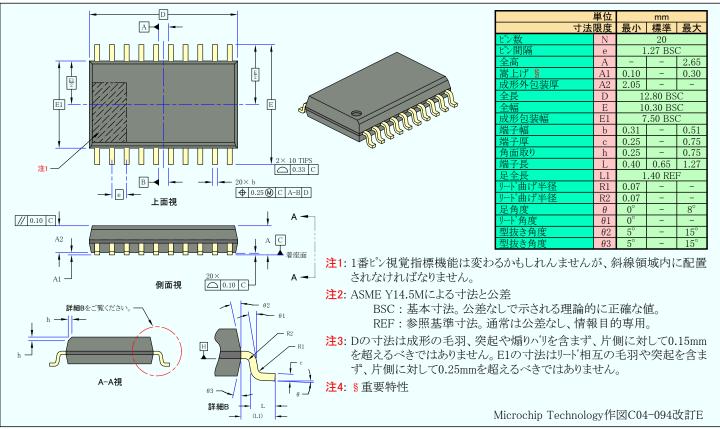

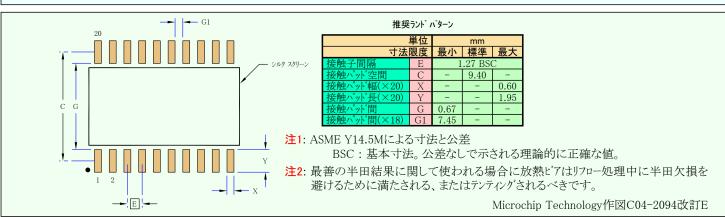

| 4.         | 4.1. 8リート*SOIC · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 13.2. 概要 · · · · · · · · · · · · · · · · · ·                |                |

|            | 4.1. 8')-  SOIC 4.2. 14'J-  SOIC 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | 13.3. 機能的な説明 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・           | 58             |

|            | 4.3. 20'J-\frac{1}{5}SOIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | 13.4. レジスタ要約・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・            |                |

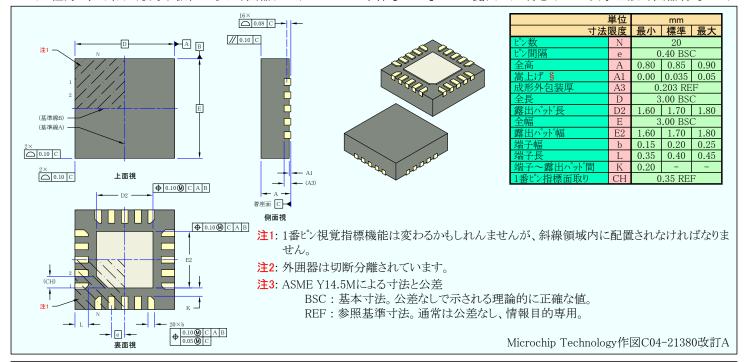

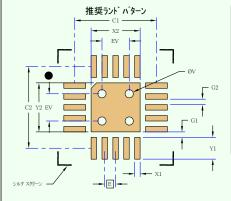

|            | 4.4. 20/\(\dagger^\gamma\) VQFN \(\dagger^\gamma\) 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 13.5. レジスタ説明 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・           |                |

| 5          | 入出力多重化と考察 ・・・・・・・・・・9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14. | EVSYS - 事象システム・・・・・・・・・・・・ (e                               |                |

| J.         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 14.1. 特徴 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                |                |

| 6          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 14.2. 概要(                                                   |                |

| <b>0</b> . |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 14.3. 機能的な説明 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・           |                |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 14.4. レジスタ要約 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・           |                |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-  |                                                             |                |

|            | 6.3. 実装書き換え可能なフラッシュ ブログラム メモリ・・・・・ 10<br>6.4. SRAMデータ メモリ ・・・・・・・・・・・・・・・ 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15. | PORTMUX - ポート多重化器・・・・・ 7                                    | 12             |

|            | 6.5. EEPROMデータメモリ・・・・・・・・・・11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | 15.1. 概要                                                    |                |

|            | 6.6. 使用者列····································                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | 15.2. レジスタ要約・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・            |                |

|            | 6.7. 識票列 · · · · · · · · · · · · · · · · 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | 15.3. レジスタ説明 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・           |                |

|            | 6.8. I/Oメモリ · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16. | PORT - I/Oピン構成設定 ・・・・・・ 7                                   |                |

|            | 6.0 施錠されたデバイスでの                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 16.1. 特徴 ・・・・・・・・・・・・・・・・・・・・・・・                            |                |

|            | CPUとUPDIからのメモリ領域アクセス                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 16.2. 概要                                                    |                |

|            | 6.10. 構成設定と使用者ヒュース (FUSE) ・・・・・・・・ 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | 16.3. 機能的な説明 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・           |                |

| 7          | 周辺機能と基本構造・・・・・・・・・・・・・・・・20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | 16.4. レジスタ要約 - PORTx ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・   |                |

| /.         | 7.1. 周辺機能単位部71・レス配置 ・・・・・・・・・ 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | 16.5. レジスタ説明 - PORTx · · · · · · · · · · · · · · · · · · ·  |                |

|            | 7.2. 割り込みへ、クタ配置・・・・・・・・・・・・20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | 16.6. レジスタ要約 - VPORTx · · · · · · · · · · · · · · · · · · · |                |

|            | 7.2. 司り込のペクトに直                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | 16.7. レジスタ説明 – VPORTx ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・  |                |

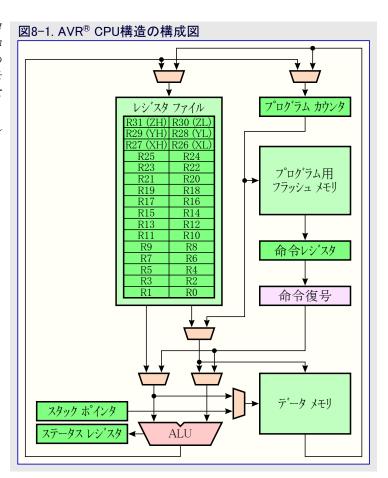

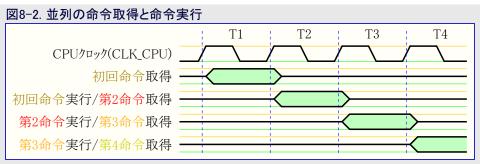

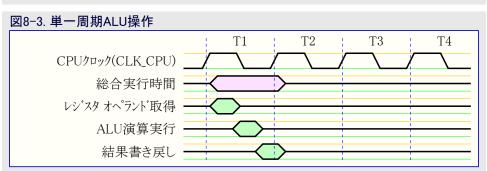

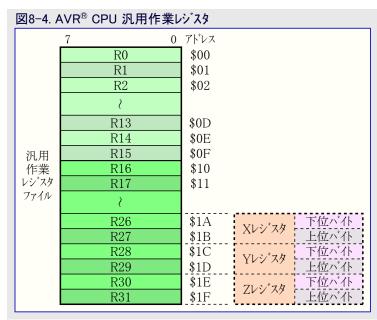

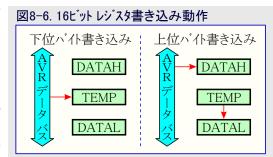

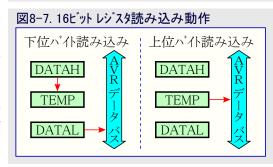

| 0          | AVR CPU · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17. | BOD - 低電圧検出器 · · · · · · · · · · · · · · · · · · ·          | 38             |

| Ö.         | and the state of t |     | 17.1. 特徴                                                    |                |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 17.2. 概要 · · · · · · · · · · · · · · · · · ·                |                |

|            | 1777                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 17.3. 機能的な説明 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・           |                |

|            | And the TA was not been done to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     | 17.4. レジスタ要約・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・            |                |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 17.5. レジスタ説明                                                |                |

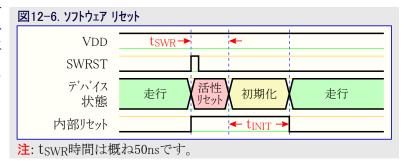

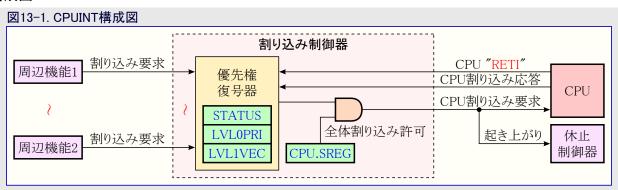

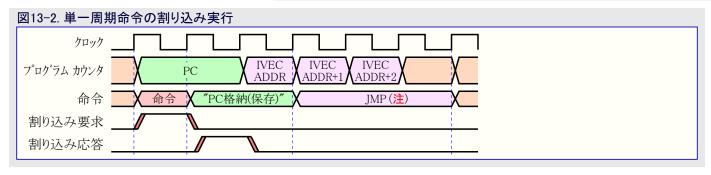

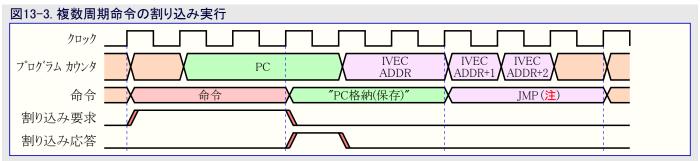

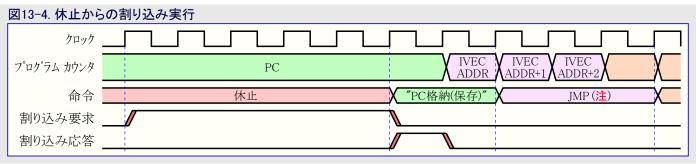

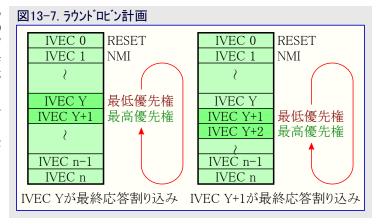

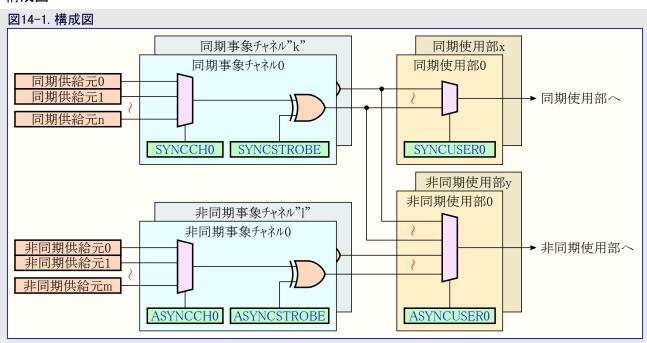

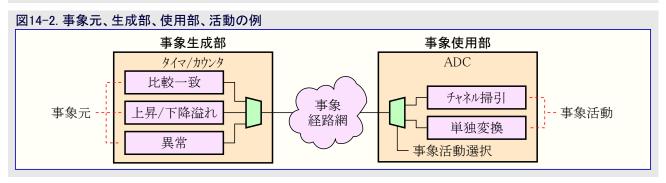

|            | 8.5. 機能的な説明・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18. | VREF - 基準電圧 •••••••• 9                                      | <del>)</del> 4 |