# 特徴

- 高性能、低消費AVR® 8ビット マイクロ コントローラ

- 進化したRISC構造

- ・強力な123命令(多くは1周期実行)

- ・32個の1バイト長汎用レジスタ

- ・完全なスタティック動作

- ・20MHz時、20MIPSに達する高速動作

# ■ 不揮発性プログラム用メモリとデータ用メモリ

- ・ 実装自己書き換え可能な2/4/8Kバイト(1/2/4K語)フラッシュ メモリ内蔵

- ・10,000回の書き換え耐久性

- 128/256/512バイトのEEPROM

- ・100,000回の書き換え耐久性

- ・128/256/512バイトの内蔵SRAM

- ・ データ保持力: 20年/85℃, 100年/25℃

- ソフトウェア保護用の設定可能な施錠機能

### ■ 内蔵周辺機能

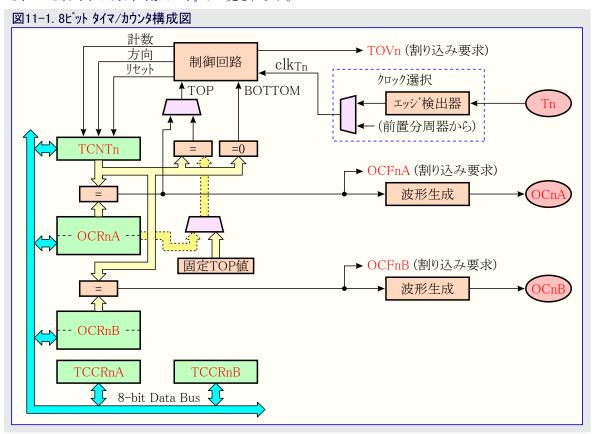

- 各々2つのPWM出力付き、1つの8ビットと1つの16ビットのタイマ/カウンタ

- 10ビット A/D変換器

- ・8つのシングルエント チャネル

- ・設定可能な利得(×1,×20)付き12種の差動ADCチャネル対

- ・設定可能な専用発振器付きウォッチドッグタイマ

- ・アナログ比較器

- ・多用途直列インターフェース(USI)

#### ■ 特殊マイクロ コントローラ機能

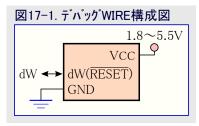

- ・デバッグWIRE内蔵デバッグ機能

- ・SPIポート経由の実装書き込み

- ・内部及び外部の割り込み:12ピンでのピン変化割り込み

- ・アイドハ、A/D変換雑音低減、スタンバイ、パワーダウンの4つの低消費動作

- ・強化した電源ONリセット回路

- ・設定可能な低電圧検出器(BOD)回路

- ・校正付き内蔵RC発振器

- ・チップ上の温度感知器

### ■ I/Oと外囲器

- ・12ビットの設定変更可能なI/O

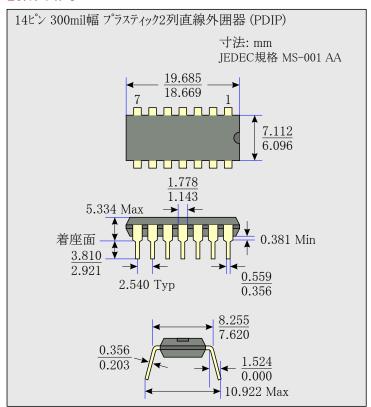

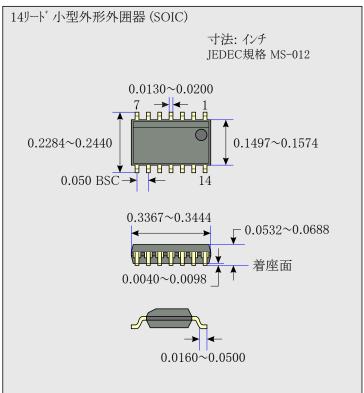

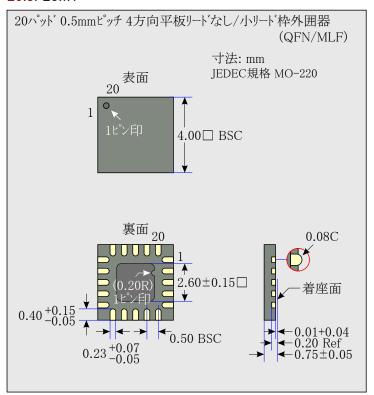

- 14ピンPDIP、14リートSOIC、20パットQFN/MLFが利用可能

#### ■ 動作電圧

ATtiny24/44/84V: 1.8~5.5V

ATtiny24/44/84 : 2.7~5.5V

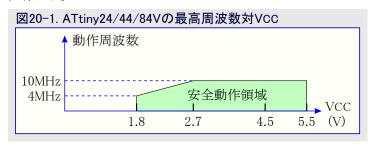

### ■ 動作速度

- · ATtiny24/44/84V

- $0\sim4 \text{MHz}/1.8\sim5.5 \text{V}$

- $0 \sim 10 MHz/2.7 \sim 5.5 V$

- ATtiny24/44/84

- $0\sim10\text{MHz}/2.7\sim5.5\text{V}$

- $0\sim20\text{MHz}/4.5\sim5.5\text{V}$

- 工業用温度範囲: -40~+85℃

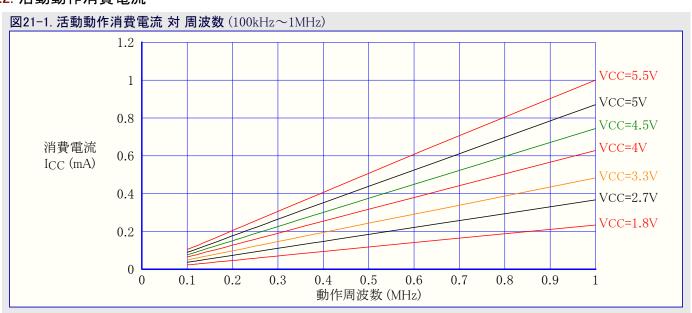

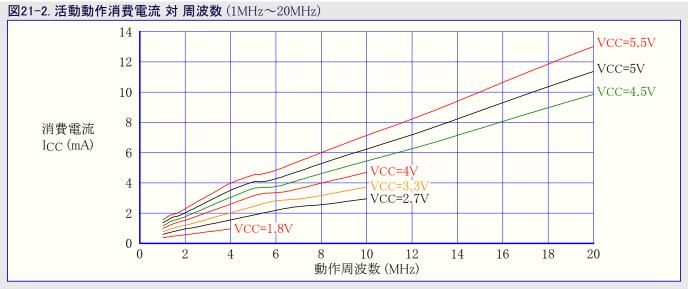

# ■ 低消費電力

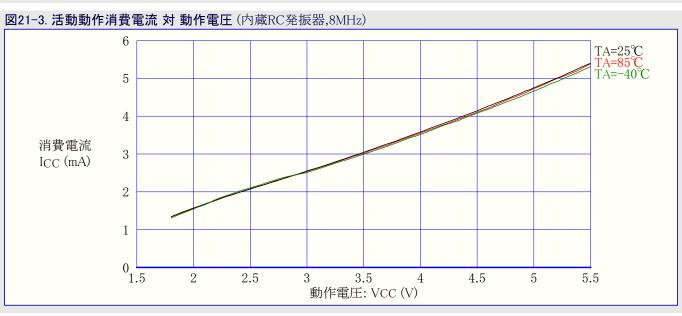

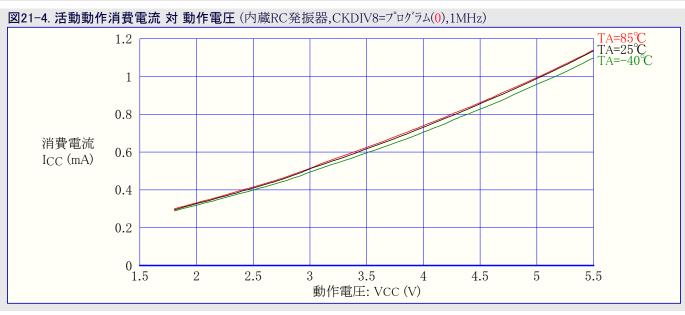

- ・300μA (1MHzシステム クロック,1.8V,活動動作)

- ・0.1μA (1.8V,パワータ ウン動作)

8ビット **AVA**® マイクロ コントローラ 実装書き換え可能な 2/4/8 Kバイトフラッシュ メモリ内蔵

ATtiny24

ATtiny24V

ATtiny44

ATtiny44V

ATtiny84

ATtiny84V

Rev. 8006K-10/10, 8006KJ6-04/22

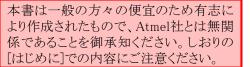

# 1. ピン配置

# 1.1. ピン概要

### 1.1.1. VCC

電源ピン。

### 1.1.2. GND

接地ピン。

### 1.1.3. PA7~PA0 (ホートA)

ポートAは(ビット単位で選択される)内蔵プルアップ抵抗付きの8ビット双方向入出力ポートです。ポートA出力緩衝部は共に高い吐き出し/吸い込み能力の対称駆動特性です。入力のとき、プルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートAピンには吐き出し電流が流れます。 リセット条件が有効になると、クロックが走行していなくても、ポートAピンはHi-Zにされます。

ポートAには38頁で示されるA/D変換器とアナログ比較器用のアナログ入力、SPIとピン変化割り込みとしての交換機能があります。

### 1.1.4. PB3~PB0 (ポートB)

ポートBは(ビット単位で選択される)内蔵プルアップ抵抗付きの4ビット双方向入出力ポートです。RESET能力を持つPB3を除いて、ポートB出力緩衝部は共に高い吐き出し/吸い込み能力の対称駆動特性です。PB3ピンをRESETの代わりにI/Oピンとして使うには、RSTDISBL ヒューズをプログラム(0)にしてください。入力のとき、プルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートBピンには吐き出し電流が流れます。リセット条件が有効になると、クロックが走行していなくても、ポートBピンはHi-Zにされます。

ポートBは41頁の「ホートBの交換機能」で示されるATtiny24/44/84の様々な特殊機能も扱います。

### 1.1.5. RESET

リセット入力。RESETピンが禁止されていなければ、例えクロックが走行していなくても、最小パルス幅より長いこのピンのLowレペールはリセットを生成します。最小パルス幅は116頁の表20-4.で与えられます。より短いパルスはリセットの生成が保証されません。 RESETピンは((駆動能力の)弱い)入出力ピンとしても使えます。

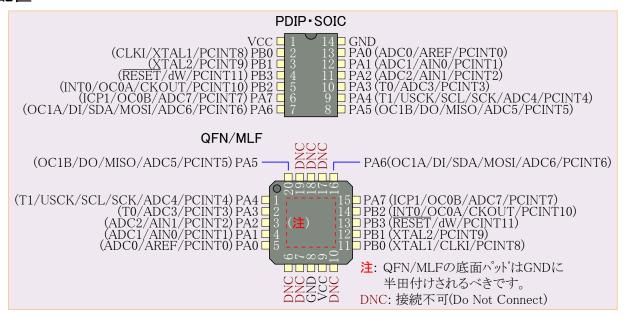

# 2. 概要

ATtiny24/44/84はAVR強化RISC構造を基にした低消費CMOS 8ビットマイクロコントローラです。1周期での強力な命令の実行によってATtiny24/44/84はMHzあたり1MIPSに達する他に処理量を成し遂げ、処理速度対消費電力の最適化を設計者に許します。

AVRコアは32個の汎用作業レジスタと豊富な命令群の組み合わせです。32個の全レジスタはALU(Arithmetic Logic Unit)に直結され、レジスタ間命令は1クロック周期で実行されます。AVR構造は現状のCISC型マイクロコントローラに対して最大10倍の単位処理量向上効果があります。

ATtiny24/44/84は2/4/8Kバ小の実装書き込み可能なフラッシュメモリ、128/256/512バ小のEEPROM、128/256/512バ小のSRAM、12本の汎用入出力線、32個の汎用作業レジスタ、2つのPWM出力付きの1つの8ビット タイマ/カウンタ、2つのPWM出力付きの1つの16ビット タイマ/カウンタ、多用途直列インターフェース(USI)、内部及び外部割り込み、12種のA/Dチャネル対用の設定可能な利得段(×1,×20)と8チャネルの10ビット A/D変換器、内蔵発振器付きの設定変更可能なウオッチドッグタイマ、校正付き内蔵RC発振器、ソフトウェアで選択できる4つの低消費動作を提供します。アイトル動作はCPUを停止し、一方SRAM、タイマ/カウンタ、A/D変換器、アナログ比較器、割り込み機構に機能の継続を許します。A/D変換雑音低減動作はA/D変換中の切り替え雑音を最小とするためにA/D変換器を除く全I/O部とCPUを停止します。パワータウン動作はレジスタの内容を保護し、発振器が停止するため、以降のハートヴェアリセットか外部割り込みまで、他の全機能を禁止します。スタンバイ動作ではクリスタル発振子/セラミック振動子用発振器が動作し、一方デバイスのその他は休止します。これは低消費電力と非常に速い起動の組み合わせを許します。

本デバイスはAtmelの高密度不揮発性メモリ技術を使って製造されます。チップ上のISPフラッシュメモリは通常の不揮発性メモリ書き込み器によるSPI直列インターフェースを通して、またはAVRコア上で走行するチップ。上のブートコート、による実装書き換えをプログラム用メモリに許します。 ATtiny24/44/84 AVRはCコンパイラ、マクロアセンブラ、プログラムデバッガ/シミュレータ、インサーキットエミューレータ、評価キットを含む完全なプログラム及びシステム開発ツールで支援されます。

# 3. 諸注意

# 3.1. 資料

包括的なデータシート、応用記述、ドライバ群と開発ツールの記述はhttp://www.atmel.com/avrでのダウンロードで利用可能です。

### 3.2. コート 例

この資料はデバイスの様々な部分の使用法を手短に示す簡単なコート・例を含みます。これらのコート・例はアセンブルまたはコンパイルに先立ってデバイス定義へッタ・ファイルがインクルートされると仮定します。全てのCコンパイラ製造業者がヘッタ・ファイル内にヒット定義を含めるとは限らず、またCでの割り込みの扱いがコンパイラに依存することに注意してください。より多くの詳細についてはCコンパイラの資料で確認してください。

拡張I/O領域に配置したI/Oレジスタに対し、IN, OUT, SBIS, SBIC, CBI, SBI命令は拡張I/O領域へのアクセスを許す命令に置き換えられなければなりません。これは代表的にSBRS, SBRC, SBR, CBR命令と組み合わせたLDS, STS命令を意味します。全てのAVRデバイスが拡張I/O領域を含むとは限らないことに注意してください。(訳補: 本デバイスに拡張I/O領域はありません。)

# 3.3. データ保持力

信頼性証明結果はデータ保持誤り率の反映を示し、20年以上/85℃または100年以上/25℃で1PPMよりずっと小さな値です。

### 3.4. お断り

本データシート内で示された代表値はシミュレーションと同じ製法技術で製造された他のAVRマイクロコントローラの特性を基にしています。

# 4. CPU 17

本項はAVRコア構造を一般的に説明します。このCPUコアの主な機能は正しいプログラム実行を保証することです。従ってCPUはメモリアクセス、計算実行、周辺制御、割り込み操作ができなければなりません。

# 4.1.構造概要

最大効率と平行処理のため、AVRはプログラムとデータに対してメモリとハスを分離するハーハート構造を使います。プログラムメモリ内の命令は単一段のハーイプラインで実行されます。1命令の実行中に次の命令がプログラムメモリから事前取得されます。この概念は全部のクロック周期で命令実行を可能にします。プログラムメモリは実装書き換え可能なフラッシュメモリです。

高速レジスタファイルは1クロック周期アクセスの32個の8ビット長汎用レジスタを含みます。これは1クロック周期ALU(Arithmetic Logic Unit)操作を許します。代表的なALU操作では2つのオペランドがレジスタファイルからの出力で、1クロック周期内でその操作が実行され、その結果がレジスタファイルに書き戻されます。

32個中の6つのレシ、スタは効率的なアト・レス計算ができるデータ空間アト・レス指定用に3つの16ビット長間接アト・レスポーインタ用レシ、スタとして使われます。これらアト・レスポーインタの1つはプログラム用フラッシュメモリ内の定数表参照用アト・レスポーインタとしても使えます。これら16ビット長付加機能レシ、スタはX,Y,Zレシ、スタで、本項内で後述されます。

ALUはレジスタ間またはレジスタと定数間の算術及び論理操作を支援します。単一レジスタ操作もALUで実行できます。算術演算操作後、操作結果についての情報を反映するために、ステータスレジスタ(SREG)が更新されます。

プログラムの流れは全アトレス空間を直接アトレス指定可能な条件/無条件分岐や呼び出し命令によって提供されます。 殆どのAVR命

図4-1. AVR構造構成図 8-bit Data Bus プログラム 状態/制御 割り込み部 カウンタ SPI部 プログラム用  $32\times8$ フラッシュ メモリ 間 汎用レジスタ ウォッチト゛ック 接 タイマ 命令レジスタ アナロク ALU 比較器 直 トレス指 接 命令復号器 ◆ 周辺機能部 1 データ用 定 **SRAM** → 周辺機能部2 アドレス指 制御信号線 **EEPROM** 汎用入出力部 ◆ 周辺機能部 n

令は16ビット語(ワード)形式ですが、32ビット命令もあります。いくつかのデバイスが部分的な命令一式だけを実装するため、実際の命令一式は変化します。

割り込みやサブルーチン呼び出し中、戻りアトレスを示すプログラムカウンタ(PC)はスタックに保存されます。スタックは一般的なデータ用SRAM上に実際には割り当てられ、従ってスタック容量は全SRAM容量とSRAM使用量でのみ制限されます。全ての使用者プログラムはリセット処理ルーチンで(サブルーチン呼び出しや割り込みが実行される前に)、スタックホーインタ(SP)を初期化しなければなりません。SPはI/O空間で読み書きアクセスが可能です。データ用SRAMはAVR構造で支援される5つの異なるアトレス指定種別を通して容易にアクセスできます。

AVR構造に於けるメモリ空間は全て直線的な普通のメモリ配置です。

柔軟な割り込み部にはI/O空間の各制御レシ、スタとステータスレシ、スタ(SREG)の特別な全割り込み許可(I)ビットがあります。全ての割り込みは割り込みへ、クタ表に個別の割り込みへ、クタを持ちます。割り込みには割り込みへ、クタ表の位置に従う優先順があります。下位側割り込みへ、クタアドレスが高い優先順位です。

I/Oメモリ空間は制御レジスタや他のI/O機能としてCPU周辺機能用の64アドレスを含みます。I/Oメモリは直接またはレジスタ ファイルの次のデータ空間位置\$20~\$5Fとしてアクセスできます。

### **4.2.ALU** (Arithmetic Logic Unit)

高性能なAVRのALUは32個の全汎用レジスタに直接接続され動作します。汎用レジスタ間または汎用レジスタと即値間の演算操作は単一クロック周期内で実行されます。ALU操作は算術演算、論理演算、ビット操作の3つの主な種類に大別されます。符号付きと符号なし両方の乗算と固定小数点形式を支援する乗算器(乗算命令)も提供する構造の実装(製品)もあります。詳細記述については、「命令要約」章をご覧ください。

### 4.3. ステータス レジスタ

ステータスレジスタは最も直前に実行した演算命令の結果についての情報を含みます。この情報は条件処理を行うためのプログラムの流れ変更に使えます。ステータスレジスタは「命令一式参考書」で詳述したように、全てのALU操作後、更新されることに注目してください。これは多くの場合でそれ用の比較命令使用の必要をなくし、高速でより少ないコードに帰着します。

ステータス レジスタは割り込み処理ルーチン移行時の保存と割り込みからの復帰時の回復(復帰)が自動的に行われません。これはソフトウェアによって扱われなければなりません。

### 4.3.1. ステータス レシ スタ (Status Register) SREG

| ピット         | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |      |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$3F (\$5F) | I   | T   | Н   | S   | V   | N   | Z   | С   | SREG |

| Read/Write  | R/W |      |

| 初期値         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

### ■ ビット7 - I: 全割り込み許可 (Global Interrupt Enable)

全割り込み許可ビットは割り込みが許可されるために設定(1)されなければなりません。その時の個別割り込み許可制御は独立した制御レシ、スタで行われます。全割り込み許可ビットが解除(0)されると、個別割り込み許可設定に拘らず、どの割り込みも許可されません。I ビットは割り込みが起こった後にハードウェアによって解除(0)され、後続の割り込みを許可するために、RETI命令によって設定(1)されます。Iビットは「命令一式参考書」で記述されるようにSEIやCLI命令で応用(プログラム)によって設定(1)や解除(0)もできます。

### ■ ビット6 - T: ビット変数 (Bit Copy Storage)

ビット複写命令、BLD(Bit LoaD)とBST(Bit STore)は操作したビットの転送元または転送先として、このTビットを使います。レジスタ ファイルのレジスタからのビットはBST命令によってTに複写でき、TのビットはBLD命令によってレジスタ ファイルのレジスタ内のビットに複写できます。

### **■ ビット5 - H**: **ハーフキャリー フラク** (Half Carry Flag)

ハーフキャリー(H)フラグはいくつかの算術操作でのハーフキャリーを示します。ハーフキャリーはBCD演算に有用です。詳細情報については「命令要約」記述をご覧ください。

### ■ ビット4 - S: 符号 (Sign Bit, S= N Ex-OR V)

Sフラケは常に負(N)フラケと2の補数溢れ(V)フラケの排他的論理和です。詳細情報については「命令要約」記述をご覧ください。

### ■ ビット3 - V: 2の補数溢れフラグ(2's Complement Overflow Flag)

2の補数溢れ(V)フラグは2の補数算術演算を支援します。詳細情報については「命令要約」記述をご覧ください。

### **■ Ľット2 - N**: **負フラク** (Negative Flag)

負(N)フラグは算術及び論理操作での負の結果(MSB=1)を示します。詳細情報については「命令要約」記述をご覧ください。

### **■ L** "y**h**1 - **Z** : **t** "**D** 7ラク" (Zero Flag)

セ<sup>i</sup>p(Z)フラグは算術及び論理操作でのセ<sup>i</sup>p(0)の結果を示します。詳細情報については「**命令要約**」記述をご覧ください。

###

キャリー(C)フラグは算術及び論理操作でのキャリー(またはボロー)を示します。詳細情報については「**命令要約**」記述をご覧ください。

# 4.4. 汎用レジスタファイル

このレシ、スタファイルはAVRの増強したRISC命令群用に最適化されています。必要な効率と柔軟性を達成するために、次の入出力機構がレシ、スタファイルによって支援されます。

- ・1つの8ビット出力オペラントと1つの8ビットの結果入力

- ・2つの8ビット出力オペラントと1つの8ビットの結果入力

- ・2つの8ビット出力オペランドと1つの16ビットの結果入力

- ・1つの16ビット出力オペラントと1つの16ビットの結果入力

**図4-2**.はCPU内の32個の汎用作業レジスタの構造を示します。 レジスタファイルを操作する殆どの命令は全てのレジスタに直接アクセスし、それらの殆どは単一周期命令です。

図4-2.で示されるように各レジスタは使用者データ空間の最初の32位置へ直接的に配置することで、それらはデータメモリアドレスも割り当てられます。例え物理的にSRAM位置として実装されていなくても、X,Y,Zレジスタ(ポインタ)がレジスタファイル内のどのレジスタの指示にも設定できるように、このメモリ構成は非常に柔軟なレジスタのアクセスを提供します。

| 図4-2./      | AVR CPU 汎用レジスタ | 構成図  |                               |

|-------------|----------------|------|-------------------------------|

|             | 7              | アドレス |                               |

|             | R0             | \$00 |                               |

|             | R1             | \$01 |                               |

|             | R2             | \$02 |                               |

|             | ?              |      |                               |

|             | R13            | \$0D |                               |

|             | R14            | \$0E |                               |

| >n ⊞        | R15            | \$0F |                               |

| 汎用<br>レシブスタ | R16            | \$10 |                               |

| ファイル        | R17            | \$11 |                               |

| 2 7 (7)     | ₹              |      |                               |

|             | R26            | \$1A | Xレジスタ       下位バ仆         上位バ仆 |

|             | R27            | \$1B | ト位バイト                         |

|             | R28            | \$1C | VICITE 下位バイト                  |

|             | R29            | \$1D | 上ルハル                          |

|             | R30            | \$1E | Zレジスター 下位バイト                  |

|             | R31            | \$1F | 上位バイト                         |

# 4.4.1. Xレシ、スタ、Yレシ、スタ、Zレシ、スタ

R26~R31レシ、スタには通常用途の使用にいくつかの追加機能があります。これらのレシ、スタはデータ空間の間接アトンス指定用の16 ビットアドンスポインタです。3つのX,Y,Z間接アドンスレシ、スタは**図4-3**.で記載したように定義されます。

種々のアドレス指定種別で、これらのアドレス レジスタは固定変位、 自動増加、自動減少としての機能を持ちます(詳細については 「命令一式参考書」をご覧ください)。

| 図4-3. X,Y,Zl         | シズスタ | 構成図        |     |            |    |

|----------------------|------|------------|-----|------------|----|

|                      | 15   | XH (上位)    |     | XL (下位)    | 0  |

| X レジスタ               | 7    | R27 (\$1B) | 0 7 | R26 (\$1A) | 0  |

|                      | 15   | YH (上位)    |     | YL (下位)    | 0_ |

| Y レシ <sup>*</sup> スタ | 7    | R29 (\$1D) | 0 7 | R28 (\$1C) | 0  |

|                      | 15   | ZH (上位)    |     | ZL (下位)    | 0_ |

| Ζ レジスタ               | 7    | R31 (\$1F) | 0 7 | R30 (\$1E) | 0  |

# 4.5. スタック ホ°インタ

スタックは主に一時データの保存、局所変数の保存、割り込みとサブルーチン呼び出し後の戻りアドレスの保存に使われます。スタック ポインタ レジスタは常にこのスタックの先頭(<mark>訳注</mark>:次に使われるべき位置)を指し示します。スタックが高位メモリから低位メモリへ伸長するように実行されることに注意してください。これはスタックへのPUSH命令はスタック ポインタを減少するという意味です。

スタック ポインタはサブルーチンや割り込みのスタックが配置されるデータSRAMのスタック領域を指し示します。データSRAM内のスタック空間はサブルーチン呼び出しの実行や割り込みの許可の何れにも先立ってプログラムによって定義されなければなりません。スタック ポインタは、60以上を指示するように設定されなければなりません。スタック ポインタはPUSH命令でデータがスタックに格納されると-1され、サブルーチン呼び出しや割り込みで戻りアドレスがスタックに格納されると-2されます。スタック ポインタはPOP命令でデータがスタックから引き出されると+1され、サブルーチンからの復帰(RET)命令や割り込みからの復帰(RETI)命令でアドレスがスタックから引き出されると+2されます。

AVRのスタック ポインタはI/O空間内の2つの8ビット レジスタとして実装されます。実際に使われるビット数は(そのデバイス)実装に依存します。SPLだけが必要とされる程に小さいAVR構造の実装(デバイス)のデータ空間もあることに注意してください。その場合、SPHレジスタは存在しません。

# 4.5.1. スタック ポインタ (Stack Pointer) SPH,SPL (SP)

|             | • `    |        | ,      | ,      |        |        |        |        |     |

|-------------|--------|--------|--------|--------|--------|--------|--------|--------|-----|

| ピット         | 15     | 14     | 13     | 12     | 11     | 10     | 9      | 8      |     |

| \$3E (\$5E) | -      | -      | -      | -      | -      | -      | (SP9)  | (SP8)  | SPH |

| Read/Write  | R      | R      | R      | R      | R      | R      | R/W    | R/W    |     |

| 初期値         | RAMEND |     |

| ピット         | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |     |

| \$3D (\$5D) | SP7    | SP6    | SP5    | SP4    | SP3    | SP2    | SP1    | SP0    | SPL |

| Read/Write  | R/W    |     |

| 初期値         | RAMEND |     |

|             |        |        |        |        |        |        |        |        |     |

(<mark>訳補</mark>) 内蔵SRAMはATtiny24が128バイト(\$0060~\$00DF)、ATtiny44が256バイト(\$0060~\$015F)、ATtiny84が512バイト(\$0060~\$025F)です。従って、ATtiny44ではSPHのSP9が、ATtiny24ではSP9,8が利用できません。SRAM最終位置はATtiny24が\$00DF (0000 0000 1101 1111)、ATtiny44が\$015F(0000 0001 0101 1111)、ATtiny84が\$025F(0000 0010 0101 1111)になります。

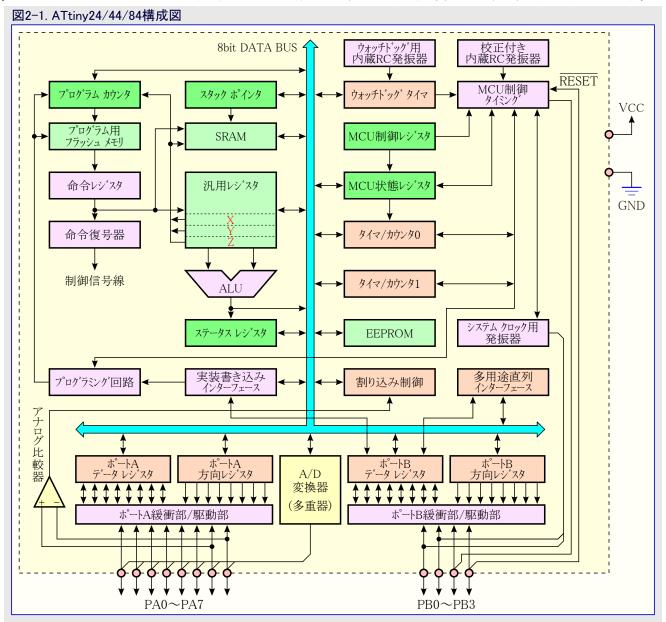

# 4.6. 命令実行タイミング

本項は命令実行の一般的なアクセス タイミング の概念を記述します。AVR CPUはチップ(デバイス)用に選択したクロック元から直接的に生成したCPUクロック(clk<sub>CPU</sub>)によって駆動されます。内部クロック分周は使われません。

図4-4.はハーハート、構造と高速アクセスレジスタファイルの概念によって可能とされる並列の命令取得と命令実行を示します。これは機能対費用、機能対クロック、機能対電源部に関する好結果と対応するMHzあたり1MIPSを達成するための基本的なパイプラインの概念です。

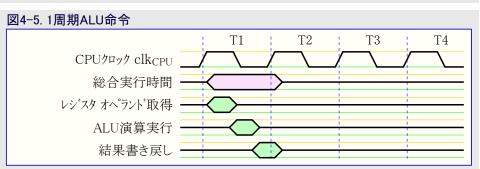

図4-5.はレシ、スタファイルに対する内部タイミングの概念を示します。単一クロック周期で2つのレシ、スタオペラント、を使うALU操作が実行され、その結果が転送先レジ、スタへ書き戻されます。

# 4.7. リセットと割り込みの扱い

AVRは多くの異なる割り込み元を提供します。これらの割り込みと独立したリセット ベクタ各々はプログラム メモリ空間内に独立したプログラム ベクタを持ちます。全ての割り込みは割り込みを許可するために、ステータス レジスタ(SREG)の全割り込み許可(I)ビットと共に論理1が書かれなければならない個別の許可ビットを割り当てられます。

プログラム メモリ空間の最下位アドレスは既定によってリセットと割り込みベクタとして定義されます。 ベクタの完全な一覧は30頁の「**割り込み**」で示されます。この一覧は各種割り込みの優先順位も決めます。下位側アドレスがより高い優先順位です。 リセットが最高優先順位で、次が外部割り込み要求の(INTO)です。

割り込みが起こると全割り込み許可(I)ビットが解除(0)され、全ての割り込みは禁止されます。使用者ソフトウェアは多重割り込みを許可するため、全割り込み許可(I)ビットへ論理1を書けます。その後全ての許可した割り込みが現在の割り込みルーチンで割り込めます。全割り込み許可(I)ビットは割り込みからの復帰(RETI)命令が実行されると、自動的に設定(1)されます。

根本的に2つの割り込み形式があります。1つ目の形式は割り込み要求フラグを設定(1)する事象によって起動されます。これらの割り込みでは割り込み処理ルーチンを実行するために、プログラム カウンタは対応する現実の割り込みへ、クタを指示し、ハートウェアが対応する割り込み要求フラグを解除(0)します。割り込み要求フラグは解除(0)されるべきフラグのビット位置へ論理1を書くことによっても解除(0)できます。対応する割り込み許可ビットが解除(0)されている間に割り込み条件が起こると、割り込み要求フラグが設定(1)され、割り込みが許可されるか、またはこのフラグがソフトウェアによって解除(0)されるまで記憶(保持)されます。同様に、全割り込み許可(1)ビットが解除(0)されている間に1つまたはより多くの割り込み条件が起こると、対応する割り込み要求フラグが設定(1)されて全割り込み許可(1)ビットが設定(1)されるまで記憶され、その(I=1)後で優先順に従って実行されます。

2つ目の割り込み形式は割り込み条件が存在する限り起動し(続け)ます。これらの割り込みは必ずしも割り込み要求フラグを持っているとは限りません。割り込みが許可される前に割り込み条件が消滅すると、この割り込みは起動されません。

AVRが割り込みから抜け出すと常に主プログラムへ戻り、何れかの保留割り込みが扱われる前に1つ以上の命令を実行します。

ステータス レジスタ(SREG)は割り込みルーチンへ移行時の保存も、復帰時の再設定も自動的に行われないことに注意してください。これはソフトウェアによって扱われなければなりません。

割り込みを禁止するためにCLI命令を使うと、割り込みは直ちに禁止されます。CLI命令と同時に割り込みが起こっても、CLI命令後に割り込みは実行されません。次例は時間制限EEPROM書き込み手順中に割り込みを無効とするために、これがどう使えるかを示します。

```

アセンブリ言語プログラム例

;ステータスレジスタを保存

IN

R16, SREG

CL.T

;EEPROM書き込み手順中割り込み禁止

EECR, EEMPE

;EEPROM主書き込み許可

SBT

SBI

EECR, EEPE

;EEPROM書き込み開始

OUT

SREG, R16

;ステータスレジスタを復帰

C言語プログラム例

/* ステータス レシ スタ保存変数定義 */

char cSREG;

cSREG = SREG;

/* ステータス レシ スタを保存 */

_CLI() ;

/* EEPROM書き込み手順中割り込み禁止 */

EECR \mid = (1 << EEMPE);

/* EEPROM主書き込み許可 */

EECR = (1 < EEPE);

/* EEPROM書き込み開始 */

SREG = cSREG:

/* ステータス レシ スタを復帰 */

注: 4頁の「コート・例」をご覧ください。

```

割り込みを許可するためにSEI命令を使うと、次例で示されるようにどの保留割り込みにも先立ってSEI命令の次の命令が実行されます。

| アセンブリ言語プログラム例 |                       |

|---------------|-----------------------|

| SEI           | ;全割り込み許可              |

| SLEEP         | ;休止形態移行(割り込み待ち)       |

| C言語プログラム例     |                       |

| _SEI();       | /* 全割り込み許可 */         |

| _SLEEP();     | /* 休止形態移行 (割り込み待ち) */ |

注: SLEEP命令までは割り込み禁止、保留割り込み実行前に休止形態へ移行します。

注: 4頁の「コート・例」をご覧ください。

### 4.7.1. 割り込み応答時間

許可した全てのAVR割り込みに対する割り込み実行応答は最小4クロック周期です。4クロック周期後、実際の割り込み処理ルーチンに対するプログラム ヘブタ アトレスが実行されます。この4クロック周期時間中にプログラム カウンタ(PC)がスタック上に保存(プッシュ)されます。このヘブタは標準的に割り込み処理ルーチンへの無条件分岐で、この分岐は2クロック周期(<mark>訳注</mark>:原文は3(JMP命令=3を想定、実際はRJMP命令=2))要します。複数周期命令実行中に割り込みが起こると、その割り込みが扱われる前に、この命令が完了されます。MCUが休止形態の時に割り込みが起こると、割り込み実行応答時間は4クロック周期増やされます。この増加は選択した休止形態からの起動時間に加えてです。

割り込み処理ルーチンからの復帰は4クロック周期要します。これらの4クロック周期中、プログラム カウンタ(PC:2バイト)がスタックから取り戻され(ポップ)、スタック ポインタは増加され(+2)、ステータス レジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されます。

# 5. メモリ

この項はATtiny24/44/84の各種メモリを記述します。 AVR構造にはプログラム メモリ空間とデータ メモリ空間の2つの主なメモリ空間がありま す。加えてATtiny24/44/84はデータ保存用EEPROMメモリが特徴です。3つのメモリ空間全ては一般的な直線的アドレスです。

# 5.1. 実装書き換え可能なプログラム用フラッシュ メモリ

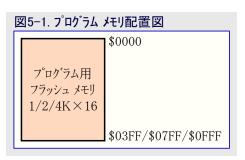

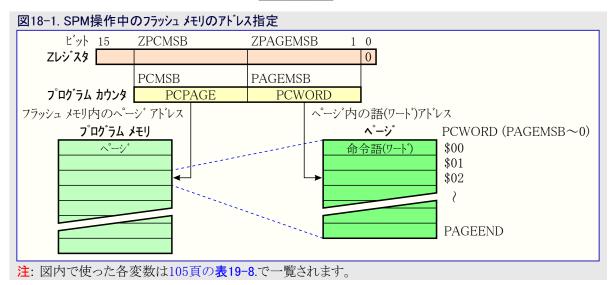

ATtiny24/44/84はプログラム保存用に実装書き換え可能な2/4/8Kバイトのフラッシュ メモリを チップ上に含みます。全てのAVR命令が16または32ビット幅のため、このフラッシュメモリは 1/2/4K×16ビットとして構成されます。

フラッシュ メモリは最低10,000回の消去/書き込み回数の耐久性があります。ATtinv24/44/ 84のプログラム カウンタ(PC)は10/11/12ビット幅で、従って1/2/4Kプログラム メモリ位置のアドレス 指定です。103頁の「メモリ プログラミング」はSPIピンを使うフラッシュ メモリの直列プログラミングの詳 細な記述を含みます。

定数表は全てのプログラムメモリアトレス空間に配置できます。(LPMとSPM命令記述参照) 命令の取得と実行のタイミング図は8頁の「**命令実行タイミング**」で示されます。

# 5.2. データ用SRAM メモリ

**図5-2**.はATtiny24/44/84のSRAMメモリ構成方法を示します。

下位データ メモリ位置はレシ、スタ ファイル、I/Oメモリ、データ用内蔵SRAMに充 てます。先頭の32位置はレジスタファイル、次の64位置は標準I/Oメモリ、そ して最後の128/256/512位置はデータ用内蔵SRAMに充てます。

直接、間接、変位付き間接、事前減少付き間接、事後増加付き間接の 5つの異なるアトレス指定種別でデータメモリ(空間)を網羅します。レシブスタ ファイル内のレシ、スタR26~R31は間接アト・レス指定ポインタ用レシ、スタが特徴で す。

直接アドレス指定はデータ空間全体に届きます。

変位付き間接動作はYまたはZレシ、スタで与えられる基準アト、レスからの63 アドレス位置に届きます。

図5-2. データ メモリ配置図 アト・レス R0 \$0000 レシブスタ ファイル  $(32\times8)$ \$001F R31 \$00 \$0020 I/Oレシ スタ  $(64 \times 8)$ \$3F \$005F \$0060 \$0060 内蔵SRAM  $(128/256/512 \times 8)$ \$0xxF \$00DF/\$015F/\$025F

注:赤字はI/Oアドレス

自動の事前減少付きと事後増加付きのレシ、スタ間接アト、レス指定動作を使う時に(使われる)X、Y、Zアト、レスン、スタは減少(-1)または増加 (+1)されます。

ATtiny24/44/84の32個の汎用レジスタ、64個のI/Oレジスタ、128/256/512バイトのデータ用内蔵SRAMは、これら全てのアドレス指定種別を 通して全部アクセスできます。レジスタファイルは7頁の「汎用レジスタファイル」で記述されます。

### 5.2.1. データ メモリ アクセス タイミング

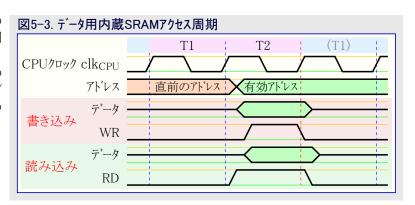

本節は内部メモリ アクセスに対する一般的なアクセス タイミングの 概念を記述します。データ用内蔵SRAMアクセスは図5-3.で図 解されるように2clkCPU周期で実行されます。

(訳注) 内蔵SRAMのアクセスを含む代表的な命令はT1,T2の 2周期で実行され、T1で対象アドレスを取得/(算出)/ 確定し、T2で実際のアクセスが行われます。後続する (T1)は次の命令のT1です。

# 5.3. データ用EEPROMメモリ

ATtiny24/44/84は128/256/512バイトのデータ用EEPROMを含みます。それは単一バイトが読み書きできる分離したデータ空間として構成されます。EEPROMは最低100,000回の消去/書き込み回数の耐久性があります。CPUとEEPROM間のアクセスは以降のEEPROMアドレス レジスタ、EEPROMデータ レジスタ、EEPROM制御レジスタで詳細に記述されます。EEPROMの直列プログラミングの詳細な記述については106頁の「低電圧直列プログラミング」をご覧ください。

### **5.3.1**. EEPROMアクセス

EEPROMアクセスレジスタはI/O空間でアクセス可能です。

EEPROMの消去/書き込み(<mark>訳注</mark>:原文はアクセス)時間は表5-1.で与えられます。(書き込みは)自己タイシンが機能ですが、使用者ソフトウェアは次ハーイが書ける時を検知してください。使用者コートがEEPROMに書く命令を含む場合、いくつかの予防処置が取られなければなりません。厳重に濾波した電源では電源の投入/切断でVCCが緩やかに上昇または下降しそうです。これはデハーイスが何周期かの時間、使われるクロック周波数に於いて最小として示されるより低い電圧で走行する原因になります。これらの状態で問題を避ける方法の詳細については12頁の「EEPROMデータ化けの防止」をご覧ください。

予期せぬEEPROM書き込みを防止するため特別な書き込み手順に従わなければなりません。この詳細についてはEEPROM制御レジスタの説明と以下の「非分離バイ書き込み」と「分離バイ書き込み」を参照してください。

EEPROMが読まれると、CPUは次の命令が実行される前に4クロック周期停止されます。EEPROMが書かれると、CPUは次の命令が実行される前に2クロック周期停止されます。

# 5.3.2. 非分離バイト プログラミング

非分離バイト プログラミングの使用は最も簡単な動作です。EEPROMにバイトを書くとき、使用者はEEARにアドレス、EEDRにデータを書かなければなりません。EEPMnビットが'00'ならば、(EEMPEが1を書かれる後の4周期内の)EEPEの1書き込みは消去/書き込み動作を起動します。消去と書き込みの両周期は1操作で行われ、総プログラミング時間は表5-1.で与えられます。EEPEビットは消去と書き込み動作が完了されるまで設定(1)に留まります。デバイスがプログラミング動作中、他のどのEEPROM操作の実行も不可能です。

### 5.3.3. 分離バイト プログラミング

2つの異なる操作として消去と書き込み周期を分離することが可能です。これは或る時間制限(代表的には電源電圧不足)に対してシステムが短いアクセス時間を必要とする場合に有用かもしれません。この方法の優位性を得るため、書かれるべき位置が書き込み操作前に消去されてしまっていることが必要とされます。しかし、消去と書き込みが分離されるため、時間が重大な操作の実行をシステムが許す時(代表的には電源投入後)に消去操作を行うことが可能です。

### 5.3.4. 消去

ハ'イトを消去するにはアドレスがEEARに書かれなければなりません。EEPMnビットが'01'なら、(EEMPEが1を書かれた後の4周期内の) EEPEの1書き込みは消去動作だけを起動します(プログラミング時間は表5-1.で与えられます)。EEPEビットは消去動作が完了されるまで設定(1)に留まります。デバイスがプログラミング動作中、他のどのEEPROM操作の実行も不可能です。

### 5.3.5. 書き込み

(特定)位置を書くため、使用者はEEARにアトンス、EEDRにデータを書かなければなりません。EEPMnビットが'10'なら、(EEMPEが1を書かれる後の4周期内の)EEPEの1書き込みは書き込み動作だけを起動します(プログラミング時間は表5-1.で与えられます)。EEPEビットは書き込み動作が完了されるまで設定(1)に留まります。書かれるべき位置が書き込み前に消去されてしまっていなければ、元の格納データは失ったとみなされなければなりません。デバイスがプログラミング動作中、他のどのEEPROM操作の実行も不可能です。

EEPROMアクセスの時間に校正済み内蔵RC発振器が使われます。発振器周波数が19頁の「**発振校正レジスタ**(OSCCAL)」で記述した必要条件内であることを確かめてください。

### 5.3.6. プログラム例

次のコート・例はアセンブリ言語とC言語でのEEPROM消去、書き込み、または非分離書き込み関数を示します。本例は(例えば全割り込み禁止によって)割り込みが制御され、これらの関数実行中に割り込みが起きない前提です。

```

アセンブリ言語プログラム例

;EEPROMプログラミング完了ならばスキップ

EEPROM WR:

SBIC

EECR, EEPE

;以前のEEPROMプログラミング完了まで待機

RJMP

EEPROM WR

R19, (0<<EEPM1) | (0<<EEPM0)

;プログラミング種別値取得(本例は非分離)

LDI

;対応プログラミング種別設定

OUT

EECR, R19

;EEPROMアドレス上位設定(注: ATtiny84のみ)

EEARH, R18

OUT

OUT

;EEPROMアドレス下位設定

EEARL, R17

;EEPROM書き込み値を設定

OUT

EEDR, R16

EECR, EEMPE

;EEPROM主プログラム許可ビット設定

SBI

SBI

EECR, EEPE

;EEPROMプログラミング開始(プログラム許可ビット設定)

RET

;呼び出し元へ復帰

C言語プログラム例

void EEPROM_write(unsigned int ucAddress, unsigned char ucData)

while (EECR & (1<<EPE));

/* 以前のEEPROMプログラミング完了まで待機 */

EECR = (0 << EEPM1) \mid (0 << EEPM0);

/* 対応プログラミング種別設定 */

/* EEPROMアトレス設定 */

EEAR = ucAddress;

EEDR = ucData;

/* EEPROM書き込み値を設定 */

EECR \mid = (1 << EEMPE);

/* EEPROM主プログラム許可*/

EECR = (1 \le EEPE);

/* EEPROMプログラミング開始*/

```

### **注**: 4頁の「**コート** 例」をご覧ください。

次のコート・例はアセンブリ言語とC言語でのEEPROM読み込み関数を示します。本例は割り込みが制御され、これらの関数実行中に割り込みが起きない前提です。

```

アセンブリ言語プログラム例

;EEPROMプログラミング完了ならばスキップ

EEPROM RD:

SBIC

EECR, EEPE

RJMP

EEPROM RD

;以前のEEPROMプログラミング完了まで待機

OUT

EEARH, R18

;EEPROMアドレス上位設定(注: ATtiny84のみ)

OUT

EEARL, R17

;EEPROMアドレス下位設定

;EEPROM読み出し開始(読み込み許可ビット設定)

SBI

EECR, EERE

IN

R16, EEDR

;EEPROM読み出し値を取得

;呼び出し元へ復帰

RET

C言語プログラム例

unsigned char EEPROM read(unsigned int ucAddress)

/* 以前のEEPROMプログラミング完了まで待機 */

while (EECR & (1<<EPE));

/* EEPROMアドレス設定 */

EEAR = ucAddress;

EECR |= (1<<EERE);

/* EEPROM読み出し開始 */

/* EEPROM読み出し値を取得,復帰 */

return EEDR;

注: 4頁の「コート 例」をご覧ください。

```

# 5.3.7. EEPROMデータ化けの防止

低VCCの期間中、正しく動作するための供給電圧がCPUとEEPROMに対して低すぎるためにEEPROMデータが化け得ます。これらの問題はEEPROMを使う基板段階の装置と同じで、同じ設計上の解決策が適用されるべきです。

EEPROMデータ化けは電圧が低すぎる時の2つの状態によって起こされ得ます。1つ目として、EEPROMへの通常の書き込み手順は正しく動作するための最低電圧が必要です。2つ目として、供給電圧が低すぎると、CPU自身が命令を間違って実行し得ます。

EEPROMデータ化けは次の推奨設計によって容易に避けられます。

不充分な供給電源電圧の期間中、AVRのRESETを活性(Low)に保ってください。これは内蔵低電圧検出器(BOD)を許可することによって行えます。内蔵BODの検出電圧が必要とした検出電圧と一致しない場合、外部低VCCリセット保護回路が使えます。書き込み動作実行中にリセットが起こると、この書き込み操作は供給電源電圧が充分ならば(継続)完了されます。

# 5.4. I/O メモリ (レジスタ)

ATtiny24/44/84のI/O空間定義は139頁の「レジスタ要約」で示されます。

ATtiny24/44/84の全てのI/Oと周辺機能はI/O空間に配置されます。全I/O位置はI/O空間と32個の汎用作業レジスタ間のデータ転送を行うLD/LDS/LDD命令とST/STS/STD命令によってアクセスされます。アドレス範囲\$00~\$1F内のI/OレジスタはSBI命令とCBI命令の使用で直接的にビットアクセス可能です。これらのレジスタではSBISとSBIC命令の使用によって単一ビット値が検査できます。より多くの詳細については「命令要約」章をご覧ください。I/O指定命令INとOUTを使う時はI/Oアドレス\$00~\$3Fが使われなければなりません。LD命令とST命令を使い、データ空間としてI/Oレジスタをアクセスする時はこれらのアドレスに\$20が加算されなければなりません。

将来のデバイスとの共通性を保つため、アクセスされる場合、予約ビットはOが書かれるべきです。予約済みI/Oメモリ アドレスは決して書かれるべきではありません。

状態フラグのいくつかはそれらへ論理1を書くことによって解除(0)されます。CBIとSBI命令は指定ビットだけを操作し、従って状態フラグのようなものを含むレジスタに使えることに留意してください。CBIとSBI命令は(I/Oアドレス)\$00~\$1Fのレジスタでのみ動作します。

I/Oと周辺制御レジスタは以降の項で説明されます。

### 5.4.1. 汎用I/Oレシ スタ

ATtiny24/44/84は3つの汎用I/Oレシ、スタを含みます。これらのレシ、スタはどの情報の格納にも使え、特に全体変数や状態フラケの格納に有用です。(I/O)アトレス範囲\$00~\$1Fの汎用I/Oレシ、スタはSBI,CBI,SBIS,SBIC命令の使用で直接ビットアクセスが可能です。

# 5.5. メモリ関係レジスタ

# 5.5.1. EEPROMアドレス レジスタ (EEPROM Address Register) EEARH,EEARL (EEAR) (訳注: EEARH/Lを纏めて記述)

| ピット         | 15      | 14    | 13    | 12    | 11    | 10    | 9     | 8       |       |

|-------------|---------|-------|-------|-------|-------|-------|-------|---------|-------|

| \$1F (\$3F) | _       | -     | -     | -     | -     | -     | -     | (EEAR8) | EEARH |

| Read/Write  | R       | R     | R     | R     | R     | R     | R     | R/W     |       |

| 初期値         | 0       | 0     | 0     | 0     | 0     | 0     | 0     | 不定      |       |

| ピット         | 7       | 6     | 5     | 4     | 3     | 2     | 1     | 0       |       |

| \$1E (\$3E) | (EEAR7) | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0   | EEARL |

| Read/Write  | R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W     |       |

| 初期値         | 不定      | 不定    | 不定    | 不定    | 不定    | 不定    | 不定    | 不定      |       |

### ■ L\*ット15~9 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

### ■ ビット8~0 - EEAR8~0: EEPROMアドレス (EEPROM Address)

EEAR8はATtiny84、EEAR7はATtiny44、EEAR6はATtiny24でのEEPROMの各々最上位アドレス ビットです。より小さなEEPROMを持つ デバイスでのこれらのビットは予約され、常に0を読みます。

EEAR5~0はEEPROMアドレス レジスタの下位側ビットです。EEPROMデータ バイトは0~127/255/511の範囲に直線的に配置されます。 EEARの初期値は不定で、従ってEEPROMが入出力される前に正しい値が書かれなければなりません。

# 5.5.2. EEPROMデータレジスタ (EEPROM Data Register) EEDR

| ビット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     | _    |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|------|

| \$1D (\$3D) | (MSB) |     |     |     |     |     |     | (LSB) | EEDR |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |      |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |      |

### ■ ビット7~0 - EEDR7~0: EEPROMデータ (EEPROM Data)

EEPROM書き込み操作に対してEEDRはEEPROMアドレスレジスタ(EEAR)で与えたアドレスのEEPROMへ書かれるべきデータを含みます。 EEPROM読み込み操作に対してEEDRはEEARで与えたアドレスのEEPROMから読み出したデータを含みます。

### 5.5.3. EEPROM制御レジスタ (EEPROM Control Register) EECR

| ピット         | 7 | 6 | 5     | 4     | 3     | 2     | 1    | 0    |      |

|-------------|---|---|-------|-------|-------|-------|------|------|------|

| \$1C (\$3C) | _ | - | EEPM1 | EEPM0 | EERIE | EEMPE | EEPE | EERE | EECR |

| Read/Write  | R | R | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  |      |

| 初期値         | 0 | 0 | 不定    | 不定    | 0     | 0     | 不定   | 0    |      |

### ■ ビット7 - Res: 予約 (Reserved)

このビットは将来の使用に予約されており、常に0として読まれます。将来のAVRデバイスとの共通性のため、常に本ビットへ0を書いてください。読み込み後、本ビットを遮蔽排除してください。

### ■ ビット6 - Res: 予約 (Reserved)

このビットは予約されており、常に0として読まれます。

### ■ ビット5,4 - EEPM1,0: EEPROM7゚ログラミング種別 (EEPROM Programing Mode Bits)

EEPROMプログラミング種別ビット設定はEEPROMプログラミング許可(EEPE)書き込み時にどのプログラミング動作が起動されるかを定義しま

す。1つの非分離操作(旧値消去と新値書き込み)、または2つの異なる操作として消去と書き込み操作を分離してデータをプログラムする(書く)ことが可能です。各動作に対するプログラミング時間は表5-1.で示されます。EEPEが設定(1)されていると、EEPMnへのどの書き込みも無視されます。リセット中、EEPMn とットはEEPROMがプログラミング作業中を除いて'00'にリセットされます。

| 衣5⁻1. E | EPROM | ノログラミング 悝別 |                     |

|---------|-------|------------|---------------------|

| EEPM1   | EEPM0 | プログラミング時間  | 動作                  |

| 0       | 0     | 3.4ms      | 1操作での消去と書き込み(非分離操作) |

| 0       | 1     | 1.8ms      | 消去のみ                |

| 1       | 0     | 1.8ms      | 書き込みのみ              |

| 1       | 1     | -          | 将来使用に予約             |

### ■ ビット3 - EERIE: EEPROM操作可割り込み許可(EEPROM Ready Interrupt Enable)

EERIEの1書き込みはステータスレジ、スタ(SREG)の全割り込み許可(I)ビットが設定(1)されているなら、EEPROM操作可割り込みを許可します。EERIEの0書き込みは、この割り込みを禁止します。EEPROM操作可割り込みは不揮発性メモリ(フラッシュ メモリとEEPROM)がプログラミングの準備可ならば継続する割り込みを発生します。

### ■ ビット2 - EEMPE: EEPROM主プログラム許可 (EEPROM Master Program Enable)

EEMPEL'ットはEEPROMプログラム許可(EEPE)ヒットの1書き込みが有効か無効かどちらかを決めます。

EEMPEが設定(1)されると、47ロック周期内のEEPE設定(1)は選択したアドレスのEEPROMをプログラムします。EEMPEが0なら、EEPE設定(1)は無効です。EEMPEがソフトウェアによって設定(1)されてしまうと、47ロック周期後にハードウェアがこのビットを0に解除します。

### ■ ビット1 - EEPE: EEPROMプログラム許可(EEPROM Program Enable)

EEPROMプログラム許可信号(EEPE)はEEPROMへのプログラミング許可信号です。EEPEが(1を)書かれると、EEPROMはEEPMnビット設定に従ってプログラムされます。論理1がEEPEへ書かれる前にEEPROM主プログラム許可(EEMPE)ビットは1を書かれねばならず、さもなければEEPROM書き込み(消去)は行われません。書き込み(プログラミング)アクセス時間が経過されると、EEPROMプログラム許可(EEPE)ビットはハートウェアによって解除(0)されます。EEPEが設定(1)されてしまうと、次の命令が実行される前にCPUは2周期停止されます。

### ■ ビット0 - EERE: EEPROM読み込み許可(EEPROM Read Enable)

EEPROM読み込み許可信号(EERE)はEEPROMへの読み込みストローブです。EEARに正しいアトレスが設定されると、EEPROM読み出しを起動するためにEEREビットは1を書かれなければなりません。EEPROM読み出しアクセスは(その)1命令で行われ、要求したデータは直ちに利用できます。EEPROMが読まれるとき、次の命令が実行される前にCPUは4周期停止されます。使用者は読み込み操作を始める前にEEPEビットをポーリングすべきです。書き込み(プログラム)操作実行中の場合、EEPROMアトレスレジスタ(EEAR)の変更もEEPROM読み込みもできません。

### 5.5.4. 汎用I/Oレジスタ2 (General Purpose I/O Register 2) GPIOR2

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     | _      |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$15 (\$35) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR2 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

### 5.5.5. 汎用I/Oレジスタ1 (General Purpose I/O Register 1) GPIOR1

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     | _      |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$14 (\$34) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR1 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

# 5.5.6. 汎用I/Oレジスタ0 (General Purpose I/O Register 0) GPIOR0

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |        |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$13 (\$33) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR0 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

# 6. クロック体系

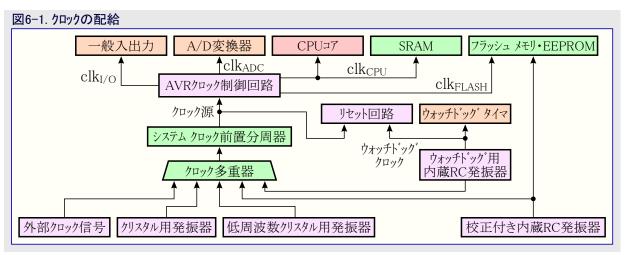

図6-1.はAVR内の主要なクロック系統とその配給を示します。全てのクロックが与えられた時間有効である必要はありません。消費電力低減のため、21頁の「電力管理と休止形態」で記述される各種休止形態の使用によって、使われていない部分のクロックが停止できます。

# 6.1. クロック副系統

クロック副系統が以下の項で詳述されます。

### 6.1.1. CPU クロック - clk<sub>CPU</sub>

CPUクロックはAVRコアの動作と関係する系統部分に配給されます。このような部分の例は汎用レジスタ ファイル、ステータス レジスタ、スタック ポイ ンタを保持するデータ メモリです。CPUクロックの停止はコアが一般的な操作や計算を実行することを禁止します。

### 6.1.2. I/O クロック - clk<sub>I/O</sub>

I/Oクロックはタイマ/カウンタのようなI/O部の大部分で使われます。I/Oクロックは外部割り込み部でも使われますが、いくつかの外部割り込みは例えI/Oクロックが停止されても検出されることをこのような割り込みに許す非同期論理回路によって検出されることに注意してください。

# 6.1.3. フラッシュ クロック - clk<sub>FLASH</sub>

フラッシュ クロックはフラッシュ メモリ インターフェースの動作を制御します。このフラッシュ クロックは常にCPUクロックと同時に活動します。

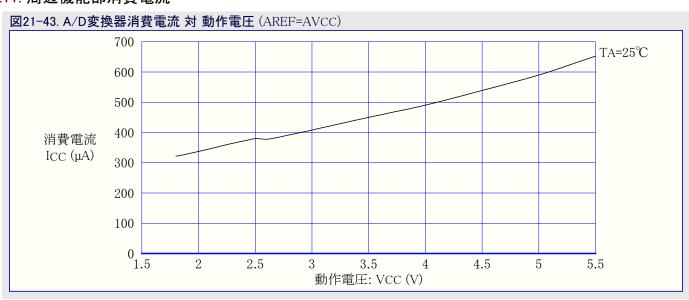

### 6.1.4. A/D変換クロック - clk<sub>ADC</sub>

A/D変換器には専用のクロック範囲が提供されます。これはデジタル回路によって生成される雑音を低減するためにCPUとI/Oクロックの停止を許します。これはより正確なA/D変換結果を与えます。

### 6.2. クロック元

このデバイスには右で示されるようにフラッシュ ヒューズ ビットによって選択可能な後続のクロック元選択があります。選択したクロック元からのクロックはAVRクロック発生器への入力で、適切な単位部へ配給されます。

各クロック選択に対する様々な選択は次項で得られます。CPUがパワーダウンから起動するとき、選択したクロック元は命令実行開始前に安定な発振器動作を保証する起動時間に使われます。CPUがリセットから始まるとき、これらは通常動作開始前に安定電圧へ達するのを電源に許す付加遅延です。ウォッチドッグ発振器はこの起動時間の実時間部のタイミングに使われます。各計時終了に使われるウォッチドッグ(WDT)発振器の各周期数は表6-2.で示されます。

| 表6-1. クロック種別選択   |           |  |  |  |  |  |

|------------------|-----------|--|--|--|--|--|

| クロック種別           | CKSEL3~0  |  |  |  |  |  |

| 外部クリスタル/セラミック発振子 | 1111~1000 |  |  |  |  |  |

| 外部低周波数クリスタル用発振器  | 0110      |  |  |  |  |  |

| 128kHz内部(WDT)発振器 | 0100      |  |  |  |  |  |

| 8MHz校正付き内蔵RC発振器  | 0010      |  |  |  |  |  |

| 外部クロック信号         | 0000      |  |  |  |  |  |

| (予約)             | 0xx1      |  |  |  |  |  |

注: 1=非ブログラム、0=プログラム、x=0または1

| 表6-2. WDT発振器の代表計時終了値、周期数 |  |  |  |  |

|--------------------------|--|--|--|--|

| 周期数                      |  |  |  |  |

| 512                      |  |  |  |  |

| 8K (8192)                |  |  |  |  |

|                          |  |  |  |  |

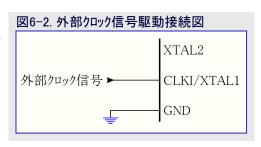

### 6.2.1. 外部クロック信号

外部クロック元からデバイスを駆動するには、CLKIが**図6-2**.で示されるように駆動されるべきです。外部クロックでデバイスを走行するためには、CKSELヒュースが'0000'にプログラム(設定)されなければなりません。

このクロック元が選択されると、起動時間は**表6-3**.で示されるようにSUTヒューズによって決定されます。

### 表6-3. 外部クロック信号駆動用起動遅延時間選択表

| SUT1,0 | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法            |  |  |  |

|--------|---------------------|------------------------------|------------------|--|--|--|

| 0 0    | 6×CK                | 14×CK                        | 低電圧検出(BOD)リセット許可 |  |  |  |

| 0 1    | 6×CK                | 14×CK+4ms                    | 高速上昇電源           |  |  |  |

| 1 0    | 6×CK                | 14×CK+64ms                   | 低速上昇電源           |  |  |  |

| 11     | (予約)                |                              |                  |  |  |  |

外部クロックを供給するとき、MCUの安定な動作を保証するために供給したクロック周波数の急な変化を避けることが必要とされます。或るクロック周期から次への2%より大きな周波数変化は予測されない事態を引き起こします。このようなクロック周波数での変化中、MCUはリセットに保たれるのを保証することが必要とされます。

システム クロック前置分周器が安定な動作を保証しながら、内部クロック周波数の実行時変更の実現に使えることに注意してください。詳細については18頁の「システム クロック前置分周器」を参照してください。

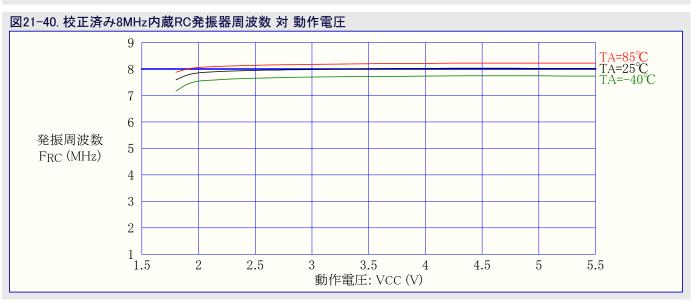

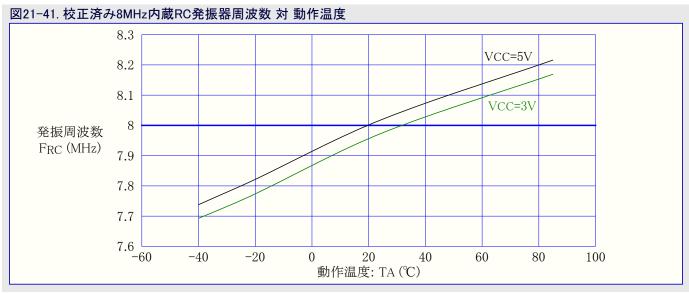

### 6.2.2. 校正付き内蔵RC発振器

既定で校正された内蔵RC発振器は概ね8MHzクロックを供給します。電圧と温度に依存しますが、このクロックは使用者によって高精度な校正ができます。より多くの詳細については115頁の表20-2.と133頁の「内部発振器周波数」をご覧ください。本デバイスはCKDIV8ヒューズがプログラム(0)で出荷されます。より多くの詳細については18頁の「システム クロック前置分周器」をご覧ください。

| 表6-4. 校正付き内蔵RC発振器動作  |            |  |  |  |  |  |

|----------------------|------------|--|--|--|--|--|

| CKSEL3~0 公称周波数 (MHz) |            |  |  |  |  |  |

| 0 0 1 0              | 8.0 (注1)   |  |  |  |  |  |

| 注1: デバイスはこの選         | 景択で出荷されます。 |  |  |  |  |  |

このクロックは表6-4.で示されるようにCKSELヒューズのプログラミングによってシステム クロックとして選択できます。選択したなら、外部部品なしで動作します。リセット中、ハードウェアが発振校正(OSCCAL)レジスタに予めプログラムされた校正値バイトを設定し、これによってRC発振器を自動的に校正します。この校正の精度は表20-2.で工場校正として示されます。

ソフトウェアからOSCCALレジスタを変更することによって(発振校正レジスタ(OSCCAL)参照)、工場校正を使うよりも高い精度を得ることができます。この校正の精度は表20-2.で使用者校正として示されます。

この発振器がチップ(システム)クロックとして使われるとき、ウォッチドック発振器は未だウォッチドック タイマとリセット付加遅延タイマに使われます。予め設定された校正値のより多くの情報については105頁の「校正バイ」項をご覧ください。

この発振器が選択されると、起動時間は表6-5.で示されるようにSUTヒュース」によって決定されます。

### 表6-5. 校正付き内蔵RC発振器用起動遅延時間選択表

| SUT1,0  | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法            |  |  |  |

|---------|---------------------|------------------------------|------------------|--|--|--|

| 0 0     | 6×CK                | 14×CK ( <b>注2</b> )          | 低電圧検出(BOD)リセット許可 |  |  |  |

| 0 1     | 6×CK                | 14×CK+4ms                    | 高速上昇電源           |  |  |  |

| 10 (注1) | 6×CK                | 14×CK+64ms                   | 低速上昇電源           |  |  |  |

| 1 1     | (予約)                |                              |                  |  |  |  |

注1: デバイスはこの選択で出荷されます。

**注2**: RSTDISBLヒューズがプログラム(0)されると、プログラミング動作への移行可を保証するため、付加遅延時間は14×CK+4.1msに増 やされます。

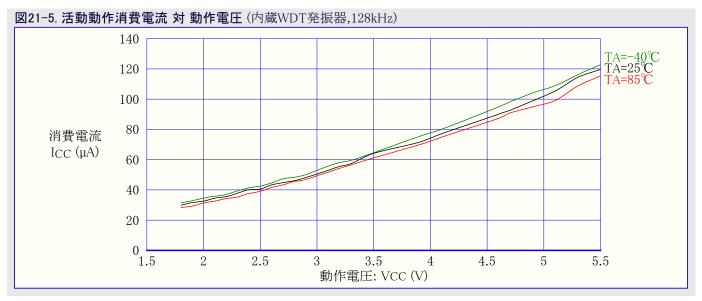

### 6.2.3. 128kHz内部発振器

128kHz内部発振器は128kHzのクロックを供給する低電力発振器です。この周波数は供給電圧、温度、1群の変量に依存します。本ク ロックはCKSELヒューズを'0100'にプログラミング(設定)することによってシステム クロックとして選択できます。

このクロック元が選択されると、起動時間は表6-6.で示されるようにSUTヒューズによって決定されます。

表6-6. 128kHz内部発振器用起動遅延時間選択表

| SUT1,0 | パワーダウンからの<br>起動遅延時間 | リセットからの<br>付加遅延時間   | 推奨使用法            |  |  |  |

|--------|---------------------|---------------------|------------------|--|--|--|

| 0 0    | 6×CK                | 14×CK ( <b>注1</b> ) | 低電圧検出(BOD)リセット許可 |  |  |  |

| 0 1    | 6×CK                | 14×CK+4ms           | 高速上昇電源           |  |  |  |

| 1 0    | 6×CK                | 14×CK+64ms          | 低速上昇電源           |  |  |  |

| 1 1    | (予約)                |                     |                  |  |  |  |

注1: RSTDISBLヒューズがプログラム(0)されると、プログラミング動作への移行可を保証するため、付加遅延時間は14×CK+4msに増やされます。

### 6.2.4. 低周波数クリスタル用発振器

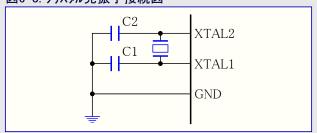

デバイスに対するクロック元として時計用32.768kHzクリスタルを使うには、CKSEL3~0ヒューズの'0110'設定によって低周波数クリスタル発振器が選択されなければなりません。クリスタルは図6-3.で示されるように接続されるべきです。 適切なコンデンサ値を得るには製造業者のデータシートを調べてください。

この発振器に対する起動遅延時間は表6-7.で示されるようにSUTヒューズで設定できます。

表6-7. 低周波数クリスタル用発振器起動遅延時間選択表

| SUT1,0 | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法                     |  |  |  |  |

|--------|---------------------|------------------------------|---------------------------|--|--|--|--|

| 0 0    | 1K×CK ( <b>注1</b> ) | 4ms                          | 高速上昇電源または低電圧検出(BOD)リセット許可 |  |  |  |  |

| 0 1    | 1K×CK ( <b>注1</b> ) | 64ms                         | 低速上昇電源                    |  |  |  |  |

| 1 0    | 32K×CK              | 64ms                         | 起動時の周波数安定                 |  |  |  |  |

| 1 1    |                     | (予約)                         |                           |  |  |  |  |

**注1**: これらの選択は応用にとって起動での周波数安定性が重要でない場合だけ使われるべきです。

低周波数クリスタル用発振器は各XTALピンに於いて表6-8.で見られる内部負荷容量を提供します。

表6-8. 低周波数クリスタル用発振器内部容量

| C 6. 内内////////////////////////////////// |                 |       |  |  |  |  |  |  |

|-------------------------------------------|-----------------|-------|--|--|--|--|--|--|

| 32kHz発振器形式                                | <b>容</b> 量 (pF) |       |  |  |  |  |  |  |

| 32KFI2光派品形式                               | XTAL1           | XTAL2 |  |  |  |  |  |  |

| システム クロック用発振器                             | 16              | 6     |  |  |  |  |  |  |

### 6.2.5. クリスタル/セラミック用発振器

XTAL1とXTAL2は図6-3.で示されるように、チップ上の発振器としての使用に設定できる反転増幅器の各々、入力と出力です。クリスタル発振子またはセラミック振動子のどちらでも使えます。

C1とC2はクリスタル発振子とセラミック振動子の両方について常に等しくすべきです。このコンデンサの最適値は使うクリスタル発振子やセラミック振動子、浮遊容量の量、その環境の電磁雑音に依存します。クリスタル発振子使用に対するコンデンサ選択について初期の指針のいくつかは下の表6-9.で与えられます。セラミック振動子については製造業者によって与えられたコンデンサ値が使われるべきです。

発振器は示された周波数範囲で各々最適化された4つの異なる動作ができます。この動作は**表6-9**.で示されるCKSEL3~1ヒューズによって選択されます。

図6-3. クリスタル発振子接続図

表6-9. クリスタル発振器動作

| CKSEL3~1 | 周波数範囲      | 推奨C1,2容量 |  |  |

|----------|------------|----------|--|--|

| 100 (注1) | 0.4~0.9MHz | -        |  |  |

| 101      | 0.9∼3.0MHz | 12∼22pF  |  |  |

| 110      | 3.0∼8.0MHz | 12∼22pF  |  |  |

| 111      | 8.0∼ MHz   | 12∼22pF  |  |  |

注1: この選択はクリスタル発振子ではなく、セラミック振動子でだけ使われるべきです。

CKSEL0ヒュース、はSUT1,0ヒュース、と共に、表6-10.で示されるように起動遅延時間を選択します。

表6-10. クリスタル発振子/セラミック振動子用起動遅延時間選択表

| CKSEL0 | SUT1,0 | パワーダウンからの<br>起動遅延時間( <mark>注1</mark> ) | リセットからの<br>付加遅延時間          | 推奨使用法                       |

|--------|--------|----------------------------------------|----------------------------|-----------------------------|

|        | 0 0    | 258×CK ( <b>注2</b> )                   | $14 \times \text{CK+4ms}$  | 外部セラミック振動子、高速上昇電源           |

| 0      | 0 1    | 258×CK ( <b>注2</b> )                   | $14 \times \text{CK+64ms}$ | 外部セラミック振動子、低速上昇電源           |

| U      | 1 0    | 1K×CK ( <b>注3</b> )                    | 14×CK                      | 外部セラミック振動子、低電圧検出(BOD)リセット許可 |

|        | 1 1    | 1K×CK ( <b>注3</b> )                    | 14×CK+4ms                  | 外部セラミック振動子、高速上昇電源           |

|        | 0 0    | 1K×CK ( <b>注3</b> )                    | $14 \times \text{CK+64ms}$ | 外部セラミック振動子、低速上昇電源           |

| 1      | 0 1    | 16K×CK                                 | 14×CK                      | 外部クリスタル発振子、低電圧検出(BOD)リセット許可 |

| 1      | 1 0    | 16K×CK                                 | 14×CK+4ms                  | 外部クリスタル発振子、高速上昇電源           |

|        | 1 1    | 16K×CK                                 | 14×CK+64ms                 | 外部クリスタル発振子、低速上昇電源           |

注1: 低電圧検出器(BOD)がソフトウェアによって禁止されていると、MCUが命令コードを実行する前にBODが正しく動作するのを保証するために、休止形態からの起動復帰時間は概ね60µsになります。

**注2**: これらの選択はデバイスの最高周波数付近での動作でないとき、応用にとって起動での周波数安定性が重要でない場合だけ使われるべきです。これらの選択はクリスタル発振子用ではありません。

**注3**: これらの選択はセラミック振動子での使用を意図され、起動での周波数安定性を保証します。デバイスの最高周波数付近での動作でないとき、応用にとって起動での周波数安定性が重要でない場合はクリスタル発振子も使えます。

### 6.2.6. 既定のクロック元

このデバイスはCKSEL=0010, SUT=10, CKDIV8=プログラム(0)で出荷されます。従って既定クロック元設定は最長起動時間の8MHzで走行する内蔵RC発振器、8で前置分周する初期システム クロックで、1MHzシステム クロックに帰着します。この既定設定は全ての使用者が実装または高電圧書き込み器を使って、それらを希望したクロック元設定にできることを保証します。

低電圧デバイス(ATtiny24V/44V/48V)に関し、CKDIV8ヒューズの非プログラム(1)が超過クロック駆動の結果になるかもしれないことに注意すべきです。低電圧(概ね2.4V以下)でのデバイスは最大8MHz動作と評価されます(115頁の「速度」をご覧ください)が、内蔵RC発振器からシステム クロック線への直接的なクロック信号経路はデバイスを8MHzで動かすでしょう。

### 6.3. システム クロック前置分周器

ATtiny24/44/84のシステム クロックはクロック前置分周レシ、スタ(CLKPR)の設定によって分周できます。この特徴(機能)は必要とされる処理能力が低い時の消費電力削減に使えます。これは全クロック種別で使え、CPUと全同期周辺機能のクロック周波数に影響を及ぼします。 clk<sub>CPU</sub>、clk<sub>FLASH</sub>、clk<sub>I/O</sub>、clk<sub>ADC</sub>は表6-11.で示された値によって分周されます。

### 6.3.1. 切り替え時間

前置分周器設定間を切り替えるとき、システム クロック前置分周器は中間(経過途中)の周波数が直前の設定に対応するクロック周波数または新規設定に対応するクロック周波数のどちらよりも高くなく、クロック系で不具合が起きないことを保証します。

前置分周器として実行するリプル カウンタは分周されないクロック周波数で走行し、CPUのクロック周波数より速いかもしれません。従って例え(カウンタ値が)読めるとしても、前置分周器の状態を決めることはできず、1から他へのクロック分周値切り替えを行う正確な時間は必ずしも予測できません。

CLKPS値が書かれる時から新規クロック周波数が活性(有効)になる前にT1+T2~T1+2×T2間かかります。この間で2つの有効なクロック端が生成されます。ここでのT1は直前のクロック周期、T2は新規前置分周器設定に対応する周期です。

### 6.4. クロック出力緩衝部(外部クロック出力)

本デバイスはシステム クロックをCKOUTピンに出力できます。この出力を許可するには、CKOUTヒューズがプログラム(0)されなければなりません。この動作はチップのクロックがシステム上の他の回路を駆動する時用です。このヒューズがプログラム(0)された時にI/Oピンの標準動作が無視され、このクロックがリセット間に出力されないことに注意してください。クロックがCKOUTに出力されるとき、校正付き内蔵RC発振器を含むどのクロック元も選択できます。システム クロック前置分周器が使われると、CKOUTヒューズがプログラム(0)された時の出力は分周されたシステム クロックです。

# 6.5. クロック関係レジスタ

### 6.5.1. 発振校正レジスタ (Oscillator Calibration Register) OSCCAL

| ピット         | 7    | 6    | 5    | 4      | 3     | 2    | 1    | 0    |        |

|-------------|------|------|------|--------|-------|------|------|------|--------|

| \$31 (\$51) | CAL7 | CAL6 | CAL5 | CAL4   | CAL3  | CAL2 | CAL1 | CAL0 | OSCCAL |

| Read/Write  | R/W  | R/W  | R/W  | R/W    | R/W   | R/W  | R/W  | R/W  |        |

| 初期値         |      |      |      | デバイス固ィ | 有の校正値 |      |      |      |        |

### ■ ビット7~0 - CAL7~0:発振校正値 (Oscillator Calibration Value)

発振校正レジスタは発振器周波数の偏差処理を省くための内蔵発振器の調整に使われます。チップのリセット中、115頁の表20-2.で指定されるように工場で校正された周波数を与える、予めプログラムされた値が本レジスタへ自動的に書かれます。応用ソフトウェアは発振器周波数を変更するために、このレジスタに書くことができます。この発振器は表20-2.で指定される周波数に校正できます。この範囲外への校正は推奨されません。

この発振器はフラッシュ メモリとEEPROMの書き込みアクセス時間に使われ、これらの書き込み時間はそれに応じて影響されることに注意してください。フラッシュ メモリまたはEEPROMが書かれる場合、8.8MHzより高く校正してはいけません。そうでなければ、フラッシュ メモリまたはEEPROM書き込みは失敗するかもしれません。

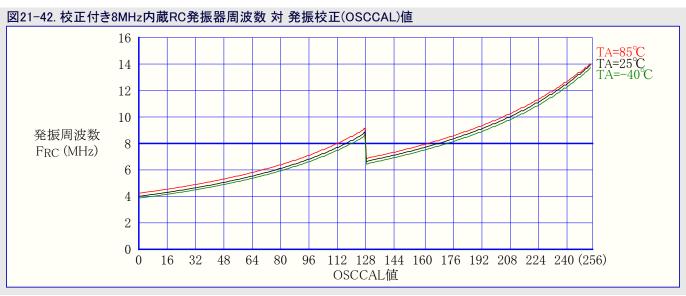

CAL7t'ットは発振器に対する操作範囲を決めます。このt'ットの(0)設定は低周波数範囲になり、(1)設定は高周波数範囲になります。この2つの周波数範囲は重複し、別の言葉では、OSCCAL=\$7F設定はOSCCAL=\$80設定より高い周波数になります。

CAL6~0ビットは選択した範囲内の周波数調整に使われます。\$00設定はその範囲の最低周波数になり、\$7F設定はその範囲の最高周波数になります。代表的な周波数については134頁の「図21-42. 校正付き8MHz内蔵RC発振器周波数 対 発振校正(OSCCAL)値」をご覧ください。

MCUの安定な動作を保証するために校正値は小さく変更されるべきです。或るクロック周期から次への2%より大きな周波数変化は予測されない事態を引き起こします。OSCCAL変更は各校正に対して\$20を越えるべきではありません。このようなクロック周波数変更の間、MCUはリセットに保たれるのを保証することが必要です。

### 6.5.2. クロック前置分周レシ、スタ (Clock Prescale Register) CLKPR

| ピット<br>\$26 (\$46) | 7<br>CLKPCE | 6 | 5<br>_ | 4 | 3<br>CLKPS3 | 2<br>CLKPS2 | 1<br>CLKPS1 | 0<br>CLKPS0 | CLKPR   |

|--------------------|-------------|---|--------|---|-------------|-------------|-------------|-------------|---------|

| Read/Write         | R/W         | R | R      | R | R/W         | R/W         | R/W         | R/W         | 0211111 |

| 初期値                | 0           | 0 | 0      | 0 | 内容参照        | 内容参照        | 内容参照        | 内容参照        |         |

# ■ ビット7 - CLKPCE: クロック分周値変更許可 (Clock Prescaler Change Enable)

CLKPSビットの変更を許可するためにCLKPCEビットは論理1を書かれなければなりません。CLKPCEビットは同時にCLKPRの他の全 ビットが0を書かれる時だけ更新されます。CLKPCEは書き込み後4クロック周期またはCLKPSビット書き込み時、ハードウェアによって解除(0)されます。この制限時間(4クロック周期ル)内のCLKPCEビット再書き込みは制限時間の延長もCLKPCEビットの解除(0)も行いません。

### ■ L'ット6~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

### ■ ビット3~0 - CLKPS3~0: クロック分周値選択 (Clock Prescaler Select Bits 3~0)

これらのビットは選択したクロック元と内部システム クロック間の分周値を定義します。これらのビットは応用の必要条件に合わせた各種クロック周波数を実行時に書けます。分周値が使われると、分周器はMCUへの主クロックを分周し、全ての同期周辺機能の速度が減じられます。分周値は表6-11.で与えられます。

予期せぬクロック周波数の変更を防ぐため、CLKPSビットの変更は次の特別な書き込み手順に従わなければなりません。

- 1. クロック分周値変更許可(CLKPCE)ビットに1、CLKPR内の他の全ビットに0を書きます。

- 2. (次からの)4周期以内にCLKPCEビットを0とする欲したCLKPS値を書きます。

前置分周器設定変更時、書き込み手続きが割り込まれないことを保証するため、割り込みは禁止されなければなりません。

CKDIV8tュース、がCLKPSt ットの初期値を決めます。CKDIV8が非プログラム(1)にされると、CLKPSt ットは、0000 にリセットされます。 CKDIV8がプログラム(0)されると、CLKPSt ットは起動時に8分周を与える、0011 にリセットされます。現在の動作条件でデバイスの最高周波数より高い周波数のクロック元を選択した場合、この機能が使われるべきです。CKDIV8tュース。設定に拘らず、どの値もCLKPSt ットへ書けることに注意してください。応用ソフトウェアは現在の動作条件でデバイスの最高周波数より高い周波数のクロック元を選択した場合、充分な分周値が選択されることを保証しなければなりません。このデバイスはCKDIV8tュースがプログラム(0)で出荷されます。

表6-11. クロック前置分周器選択

| (0 11.7877前巨刀向带医队 |   |     |   |   |    |     |    |     |     |   |   |     |      |   |   |   |  |

|-------------------|---|-----|---|---|----|-----|----|-----|-----|---|---|-----|------|---|---|---|--|

| CLKPS3            |   | 0   |   |   |    |     |    |     |     | 1 |   |     |      |   |   |   |  |

| CLKPS2            |   | (   | ) |   | 1  |     |    |     | 0   |   |   |     | 1    |   |   |   |  |

| CLKPS1            | ( | 0 1 |   |   |    | 0 1 |    |     | 0 1 |   |   | 0 1 |      |   | [ |   |  |

| CLKPS0            | 0 | 1   | 0 | 1 | 0  | 1   | 0  | 1   | 0   | 1 | 0 | 1   | 0    | 1 | 0 | 1 |  |

| 分周値(数)            | 1 | 2   | 4 | 8 | 16 | 32  | 64 | 128 | 256 |   |   |     | (予約) |   |   |   |  |

# 7. 電力管理と休止形態

高機能と産業的に先行するコート・効率は低電力の応用に対してAVRマイクロコントローラを理想的に選択させます。加えて休止形態は応用でMCU内の未使用部を一時停止することを可能にし、それによって節電します。AVRは応用で必要な消費電力に仕立てることを使用者に許す様々な休止形態を提供します。

# 7.1. 休止形態種別

15頁の図6-1.はATtiny24/44/84の各種クロック系統とその配給を示します。この図は適切な休止形態選択の助けになります。表7-1.は異なる休止形態とそれらの起動元を示します。

表7-1. 各休止形態に於ける動作クロック範囲と復帰起動要因

|   |           | 動作クロック範囲   |              |           |            | 発振器動作        | 復帰起動要因 (割り込み) |                   |         |            |           |  |  |  |

|---|-----------|------------|--------------|-----------|------------|--------------|---------------|-------------------|---------|------------|-----------|--|--|--|

|   | 休止種別      | clk<br>CPU | clk<br>FLASH | clk<br>10 | clk<br>ADC | 主クロック<br>供給元 | INT0<br>ピン変化  | SPM/EEPROM<br>操作可 | A/D変換完了 | その他<br>I/O | ウォッチト゛ック゛ |  |  |  |

| I | アイドル      |            |              | 0         | 0          | 0            | 0             | 0                 | 0       | 0          | 0         |  |  |  |

| ı | A/D変換雑音低減 |            |              |           | 0          | 0            | 1             | 0                 | 0       |            | 0         |  |  |  |

| I | ハ゜ワータ゛ウン  |            |              |           |            |              | 1             |                   |         |            | 0         |  |  |  |

| I | スタンバイ     |            |              |           |            | 0            | 1             |                   |         |            | 0         |  |  |  |

① INTOについてはレベル割り込みのみです。

4つの休止形態の何れかへ移行するにはMCU制御レシ、スタ(MCUCR)の休止許可(SE)ビットが論理1を書かれ、SLEEP命令が実行されなければなりません。MCUCRの休止種別選択(SM1,0)ビットはSLEEP命令によって活性(有効)にされる休止形態(アイドル、A/D変換雑音低減、パワータ、ウンハ´イ)のどれかを選びます。一覧については表7-2.をご覧ください。

MCUが休止形態中に許可した割り込みが起こると、MCUは起動します。その時にMCUは起動時間に加えて4周期停止され、割り込みルーチンを実行し、そしてSLEEP命令の次の命令から実行を再開します。デバイスが休止状態から起動するとき、レジスタファイルとSRAMの内容は変えられません。休止形態中にリセットが起こると、MCUは起動し、リセット ベクタから実行します。

レヘールで起動した割り込みが起動復帰に使われる場合、MCUを起動(とMCUがその割り込み処理ルーチンへ移行)するには、変更したレヘールが一定時間保持されなければならないことに注意してください。詳細については31頁の「外部割り込み」を参照してください。

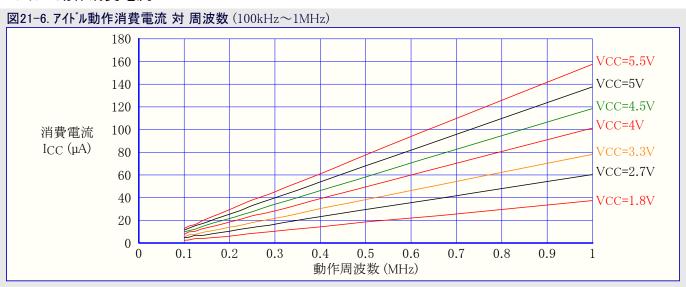

### 7.1.1. アイドル動作

休止種別選択(SM1,0)ビットが'00'を書かれるとき、SLEEP命令はMCUをアイドル動作へ移行させ、CPUを停止しますが、A/D変換器、アナログ比較器、タイマ/カウンタ、ウォッチドッグ、割り込み機構の継続動作を許します。この休止形態は基本的にclkCPUとclkFLASHを停止する一方、他のクロックに走行を許します。

アイドル動作はMCUにタイマ溢れなどの内部割り込みだけでなく、外部で起動された割り込みからの起動も可能にします。アナログ比較器割り込みからの起動が必要とされないなら、アナログ比較器制御/状態レジスタ(ACSR)のアナログ比較器禁止(ACD)ビットを設定(1)することによってアナログ比較器を電源断にできます。これはアイドル動作での消費電力を削減します。A/D変換が許可されるなら、この動作に移行すると変換が自動的に始まります。

### 7.1.2. A/D変換雑音低減動作

SM1,0ビットが'01'を書かれるとき、SLEEP命令はMCUをA/D変換雑音低減動作へ移行させ、CPUを停止しますが、A/D変換器、外部割り込み、ウォッチドック'の(許可されていれば)継続動作を許します。この休止形態は基本的にclk<sub>I/O</sub>, clk<sub>CPU</sub>, clk<sub>FLASH</sub>を停止する一方、他のクロックに走行を許します。

これはA/D変換に対する雑音環境を改善し、より高い分解能の測定を可能にします。A/D変換器が許可されている場合、この動作に移行すると、変換が自動的に始まります。A/D変換完了割り込みからの他、外部リセット、ウォッチトック・リセット、低電圧検出(BOD)リセット、SPM/EEPROM操作可割り込み、INTOの外部レヘル割り込み、ピン変化割り込みだけが、A/D変換雑音低減動作からMCUを起動できます。

### 7.1.3. パワーダウン動作

SM1,0ビットが'10'を書かれると、SLEEP命令はMCUをパワーダウン動作へ移行させます。この動作では発振器が停止される一方、外部割り込み、ウォッチドッグ機能は(許可されていれば)継続して動作します。外部リセット、ウォッチドッグ機能は(許可されていれば)継続して動作します。外部リセット、ウォッチドッグリセット、低電圧検出(BOD)リセット、INTOの外部レヘブル割り込み、ピン変化割り込みだけがMCUを起動できます。この休止形態は生成した全てのクロックを停止し、非同期部の動作だけを許します。

### 7.1.4. スタンバイ動作

外部クリスタル発振子/セラミック振動子用クロック種別が選択され、SM1,0ビットが'10'のとき、SLEEP命令はMCUをスタンバイ動作へ移行させます。この動作は(外部クリスタル用)発振器が走行(動作)を保たれる例外を除いてパワーダウン動作と同じです。デバイスはスタンバイ動作から6クロック周期で起動します。

# 7.2. ソフトウェア低電圧検出(BOD)禁止

低電圧検出器(BOD)がBODLEVELヒュース'(104頁の表19-4.参照)によって許可されていると、BODは休止期間中に電源電圧を活発に監視します。いくつかのデバイスはパプワーダウンとスタンバイの休止形態でソフトウェアでBODを禁止することによる節電が可能です。この休止形態電力消費はBODがヒュース'によって全面的に禁止される時と同じ水準になるでしょう。

BODがソフトウェアで禁止される場合、BOD機能は休止形態移行後、直ちにOFFされます。休止からの起動復帰で、BODは再び自動的に許可されます。これは休止期間中にVCCレベルが落ちた場合の安全な動作を保証します。

BODが禁止されてしまうと、MCUが命令コードの実行を継続する前にBODが正しく動作するのを保証するために、休止形態からの起動時間は概ね60µsになります。

BOD禁止はMCU制御レジスタ(MCUCR)のビット7、BOD休止(BODS)ビットによって制御されます。24頁の「**MCU制御レジスタ(MCUCR)**」をご覧ください。このビットへの1書き込みはパワーダウン動作とスタンバイ動作でのBODをOFFにし、一方このビットの0はBOD活動(有効)を保ちます。既定設定は0、換言するとBOD活動(有効)です。

BODSビットへの書き込みは許可ビットと時間制限手順によって制御されます。24頁の「MCU制御レジスタ(MCUCR)」をご覧ください。

#### 7.2.1. 制限

BOD禁止機能は以下のデバイスにだけ実装されています。

ATtiny24: 改訂Eとそれ以降ATtiny44: 改訂Dとそれ以降ATtiny84: 改訂Bとそれ以降

改訂はデバイス外囲器上に記され、以下のように配置され得ます。

- ・14P3と14S1外囲器の裏側

- ・20M1外囲器の表側

# 7.3. 電力削減

電力削減レシ、スタ(24頁の「電力削減レシ、スタ(PRR)」参照)は個別周辺機能へのクロックを停止することにより、消費電力を削減方法を提供します。周辺機能は現状で固定化され、I/Oレシ、スタは読み込みも書き込みもできません。クロックを停止している時に周辺機能によって使われていた資源は占有されたままなので、その周辺機能は殆どの場合、クロックを停止する前に禁止されるべきです。周辺機能部の起動は電力削減レシ、スタ(PRR)のビットを解除(0)することによって行い、その周辺機能部を停止前と同じ状態にします。

周辺機能部の停止は全体に亘る重要な消費電力の削減のために活動動作とアイドル動作で使えます。その他の休止形態ではクロックが予め停止されます。例については120頁の「**周辺機能部供給電流**」をご覧ください。

# 7.4. 消費電力の最小化

これらはAVRが制御するシステムで消費電力の最小化を試みる時に考慮するためのそれぞれの検討点です。一般的に休止形態は可能な限り多く使われるべきで、休止種別は動作するデバイスの機能が可能な限り少なくなるために選択されるべきです。必要とされない全ての機能は禁止されるべきです。特に次の機能部は最低可能消費電力の達成を試みるとき、特別な考慮を必要とするでしょう。

### 7.4.1. A/D変換器 (ADC)

許可したなら、A/D変換器は全休止形態で許可されます。節電するため、休止形態の何れかへ移行する前にA/D変換器は禁止されるべきです。A/D変換器がOFFそして再びONに切り替えられると、次の(最初の)変換は延長された(初回)変換になります。A/D変換器操作の詳細については87頁の「A/D変換器」をご覧ください。

### 7.4.2. アナログ比較器

アイドル動作へ移行するとき、アナログ比較器は使われないなら、禁止されるべきです。A/D変換雑音削減動作へ移行するとき、アナログ比較器は禁止されるべきです。その他の休止形態でのアナログ比較器は自動的に禁止されます。しかしアナログ比較器が入力として内部基準電圧を使う設定の場合、全休止形態でアナログ比較器は禁止されるべきです。さもなければ内部基準電圧は休止形態と無関係に許可されます。アナログ比較器設定法の詳細については85頁の「アナログ比較器」をご覧ください。

### 7.4.3. 低電圧検出器 (BOD)

低電圧検出器(BOD)が応用で必要とされないなら、この単位部はOFFにされるべきです。低電圧検出器がBODLEVELヒューズによって許可されていると全休止形態で許可され、故に常時電力を消費します。これはより深い休止形態での総消費電流にとって重要な一因になります。低電圧検出器(BOD)設定法の詳細については26頁の「低電圧検出(BOD)」と22頁の「ソフトウェア低電圧検出器(BOD)禁止」をご覧ください。

### 7.4.4. 内部基準電圧

内部基準電圧は低電圧検出器(BOD)、アナログ比較器、A/D変換器によって必要とされる時に許可されます。これら単位部が上の項で記述されたように禁止されると、内部基準電圧は禁止され、電力を消費しません。再び許可する場合、この出力が使われる前に使用者は基準電圧へ起動(安定時間)を与えなければなりません。基準電圧が休止形態でON保持される場合、この出力は直ちに使えます。起動時間の詳細については27頁の「内部基準電圧」をご覧ください。

### 7.4.5. ウォッチト゛ック゛タイマ

ウォッチト、ック、タイマが応用で必要とされないなら、この単位部はOFFにされるべきです。ウォッチト、ック、タイマが許可されていると全休止形態で許可され、故に常時電力を消費します。これはより深い休止形態での総消費電流にとって重要な一因になります。ウォッチト、ック、タイマ設定法の詳細については27頁の「ウォッチト、ック、タイマ」をご覧ください。

### 7.4.6. ホート ピン

休止形態へ移行するとき、全てのポートピンは最小電力使用に設定されるべきです。最も重要なことはその時にピンが抵抗性負荷を駆動しないのを保証することです。I/Oクロック(clk<sub>I/O</sub>)とA/D変換クロック(clk<sub>ADC</sub>)の両方が停止される休止形態ではデバイスの入力緩衝部が禁止されます。これは必要とされない時に入力論理回路によって電力が消費されないことを保証します。いくつかの場合で入力論理回路は起動条件を検出するために必要とされ、その時は許可されます。どのピンが許可されるかの詳細については36頁の「デジタル入力許可と休止形態」をご覧ください。入力緩衝部が許可され、入力信号が浮いている状態のままか、またはアナログ信号電圧がVCC/2付近の場合、入力緩衝部は過大な電力を消費するでしょう。

アナロケース力ピンに対するデジタル入力緩衝部は常に禁止されるべきです。入力ピンでのVCC/2付近のアナロケー信号入力は活動動作でも重要な電流を引き起こし得ます。デジタル入力緩衝部はデジタル入力禁止レジスタの(DIDRO)の書き込みによって禁止できます。詳細については86頁と97頁の「デジタル入力禁止レジスタの(DIDRO)」をご覧ください。

### 7.5. 電力管理用レジスタ

### 7.5.1. MCU制御レジスタ (MCU Control Register) MCUCR

このMCU制御レシブスタは電力管理用の制御ビットを含みます。

| ピット         | 7    | 6   | 5   | 4   | 3   | 2     | 1     | 0     |       |

|-------------|------|-----|-----|-----|-----|-------|-------|-------|-------|

| \$35 (\$55) | BODS | PUD | SE  | SM1 | SM0 | BODSE | ISC01 | ISC00 | MCUCR |

| Read/Write  | R/W  | R/W | R/W | R/W | R/W | R/W   | R/W   | R/W   |       |

| 初期値         | 0    | 0   | 0   | 0   | 0   | 0     | 0     | 0     |       |

### ■ ビット7 - BODS: BOD休止 (BOD Sleep)

低電圧検出器(BOD)休止機能はいくつかのデバイスでだけ利用可能です。22頁の「制限」をご覧ください。

休止間(21頁の表7-1.参照)にBODを禁止するために、BODSビットは論理1を書かれなければなりません。BODSビットの書き込みは MCUCRのBOD休止許可(BODSE)ピットと時間制限手順によって制御されます。最初にBODSとBODSEの両方が1に設定されなければなりません。次に4クロック周期内にBODSが1に設定され、BODSEが0に設定されなければなりません。BODSビットはそれが設定された後の3クロック周期間活性(有効)です。SLEEP命令は実際の休止形態に対してBODをOFFにするために、BODSが活性(有効)の間に 実行されなければなりません。BODSビットは3クロック周期後、自動的に解除(0)されます。

BOD休止が実装されていないデバイスでは、このビットが使われず、常に0として読めます。

### ■ ビット5 - SE:休止許可(Sleep Enable)

SLEEP命令が実行される時にMCUを休止形態へ移行させるには、休止許可(SE)ビットが論理1を書かれなければなりません。MCUの目的外休止形態移行を避けるため、SLEEP命令実行直前に休止許可(SE)ビットを設定(1)し、起動後直ちに解除(0)することが推奨されます。

### ■ ビット4,3 - SM1,0: 休止種別選択 (Sleep Mode Select Bits 1 and 0)

これらのビットは表7-2.で示される利用可能な4つの休止形態の1つを選択します。

### ■ ビット2 - BODSE: BOD休止許可 (BOD Sleep Enable)

BOD休止機能はいくつかのデバイスでだけ利用可能です。22頁の「制限」をご覧ください。

BODSEビットはBOD休止(BODS)ビット記述で説明されるように、BODS制御ビットの設定を許可します。このBOD禁止は時間制限手順によって制御されます。

このビットはソフトウェアBOD禁止が実装されていないデバイスで使われず、それらのデバイスで常に0として読めます。

| 表7-2. 休止形態種別選択 |     |             |  |  |  |  |  |  |  |  |

|----------------|-----|-------------|--|--|--|--|--|--|--|--|

| SM1            | SM0 | 休止形態種別      |  |  |  |  |  |  |  |  |

| 0              | 0   | アイドル動作      |  |  |  |  |  |  |  |  |

| 0              | 1   | A/D変換雑音低減動作 |  |  |  |  |  |  |  |  |

| 1              | 0   | パプーダウン動作    |  |  |  |  |  |  |  |  |

| 1              | 1   | スタンバイ動作(注)  |  |  |  |  |  |  |  |  |

**注**: クロック元として外部クリスタル発振子または セラミック振動子選択でだけ推奨されます。

# 7.5.2. 電力削減レジスタ (Power Reduction Register) PRR

電力削減レシ、スタは周辺機能のクロック信号の禁止を許すことによって消費電力削減の方法を提供します。

| ピット         | 7 | 6 | 5 | 4 | 3      | 2      | 1     | 0     |     |

|-------------|---|---|---|---|--------|--------|-------|-------|-----|

| \$00 (\$20) | _ | - | _ | _ | PRTIM1 | PRTIM0 | PRUSI | PRADC | PRR |

| Read/Write  | R | R | R | R | R/W    | R/W    | R/W   | R/W   |     |

| 初期値         | 0 | 0 | 0 | 0 | 0      | 0      | 0     | 0     |     |

### ■ L\*ット7~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

### ■ ビット3 - PRTIM1: タイマ/カウンタ1電力削減 (Power Reduction Timer/Counter1)

このビットへの1書き込みはタイマ/カウンタ1部を停止します。タイマ/カウンタ1が許可されると、停止前と同様に動作は継続します。

# ■ ビット2 - PRTIM0 : タイマ/カウンタ0電力削減 (Power Reduction Timer/Counter0)

このビットへの1書き込みはタイマ/カウンタ0部を停止します。タイマ/カウンタ0が許可されると、停止前と同様に動作は継続します。

### ■ ビット1 - PRUSI: 多用途直列インターフェース電力削減 (Power Reduction USI)

このビットへの1書き込みはその部分へのクロック停止によって多用途直列インターフェース(USI)を停止します。USIの再起動時、USIは正しい動作を保証するために再初期化されるべきです。

### ■ ビット0 - PRADC : A/D変換器電力削減 (Power Reduction ADC)

このビットへの1書き込みはA/D変換器(ADC)を停止します。A/D変換器は停止前に禁止されなければなりません。A/D変換器停止時、アナログ比較器はADC入力切替器を使えません。

注: アナログ・比較器は85頁の「アナログ・比較器制御/状態レジ、スタ(ACSR)」のアナログ・比較器禁止(ACD)ビットを使うことで禁止されます。 (訳注:共通性から本注追加)

# 8. システム制御とリセット

### 8.1. AVRのリセット

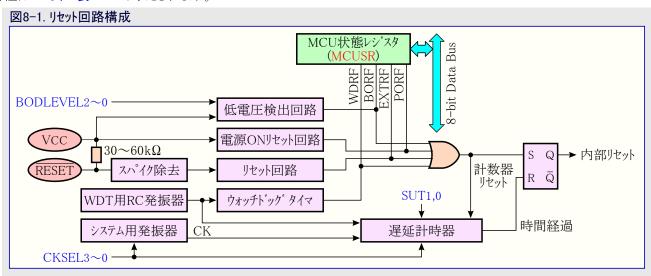

リセット中、全てのI/Oレシ、スタはそれらの初期値に設定され、プログラムはリセット、グタタから実行を開始します。 リセット、グタに配置される命令は、きっとリセット処理ルーチンへの無条件相対分岐(RJMP)命令でしょう。 プログラムが決して割り込み元を許可しないなら、割り込み、グタは使われず、これらの位置に通常のプログラムコードが配置できます。 図8-1.の回路構成図はリセット論理回路を示します。 リセット回路の電気的特性は116頁の表20-4.で与えられます。

AVRのI/Oポートはリセット元が有効になると直ちにそれらの初期状態にリセットされます。これはどのクロック元の走行も必要ありません。全てのリセット元が無効にされてしまった後、遅延計数器(タイマ)が始動され、内部リセットを引き伸ばします。これは通常動作開始前に安定電圧へ達することを電源に許します。遅延タイマの遅延時間はSUTヒュース、とCKSELヒュース、を通して使用者によって定義されます。この遅延時間についての各種選択は15頁の「クロック元」で示されます。

### 8.2. リセット元

ATtiny24/44/84には次の4つのリセット元があります。

- ・電源ONJセット・・・・・供給電圧が電源ONJセット閾値電圧(VPOA)以下でMCUがJセットされます。

- ・外部リセット・・・・・・RESETビンが最小ハッルス幅以上Lowレヘッルに保たれると、MCUがリセットされます。

- ・ウォッチドッグ リセット・・・ ウォッチト、ック リセット動作が許可され、ウォッチト、ック タイマが終了すると、MCUがリセットされます。

- ・低電圧リセット・・・・・ 低電圧検出器(BOD)が許可され、供給電圧(VCC)が低電圧検出電圧(VBOT)以下でMCUがリセットされます。

### 8.2.1. 電源ONリセット

電源ONJセット(POR)パルスはチップ上の検出回路によって生成されます。検出電圧は116頁の「システムとリセットの特性」で定義されます。 POR信号はVCCが検出電圧以下の時は必ず活性(有効)にされます。 POR回路は供給電圧異常検出は勿論、始動リセットの起動にも使えます。

電源ONJセット回路はデバイスが電源投入でJセットされることを保証します。電源ONJセット閾値電圧(VPOR)への到達はVCCの上昇後にデバイスがどのくらいJセットを保つかを決める遅延計数器(タイマ)を起動します。VCCがこの検出電圧以下に低下すると、Jセット信号はどんな遅延もなく再び有効にされます。

#### 8.2.2. 外部リセット

内部リセット

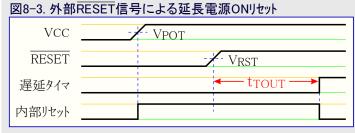

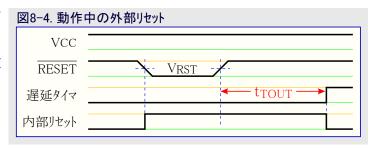

外部リセットはRESETt°ンのLowレヘールによって生成されます。クロックが動いていなくても、最小ハールス幅(116頁の「システムとリセットの特性」参照)以上のリセットハールスはリセットを生成します。短すぎるハールスはリセット生成が保証されません。印加された信号の上昇がリセット閾値電圧(VRST)に達すると(遅延タイマを起動し)、遅延タイマは遅延時間(tTOUT)経過後にMCUを始動します。

### 8.2.3. 低電圧(ブラウンアウト)検出リセット

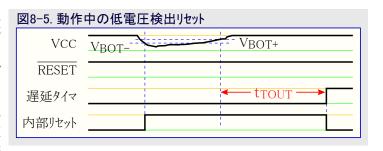

ATtiny24/44/84には固定化された起動(検出)電圧と比較することで動作中のVCCを監視するチップ上の低電圧検出(BOD)回路があります。BODの起動電圧はBODLEVELtューズによって選択できます。この起動電圧はスパイク対策BODを保証するためにヒステリシスを持ちます。検出電圧のヒステリシスはVBOT+=VBOT+VHYST/2、VBOT-=VBOT-VHYST/2と解釈されるべきです。

BODが許可され、VCCが起動電圧以下に下降すると(図8-5.の VBOT-)、低電圧Jセットが直ちに有効とされます。VCCが起動電圧以上に上昇すると(図8-5.のVBOT+)、(遅延J4インが起動され)遅延J4インは遅延時間(ITOUT)経過後にMCUを始動します。

BOD回路は電圧が116頁の「システムとリセットの特性」で与えられるtBOD時間より長く起動電圧以下に留まる場合のみ、VCCでの低下を検出します。

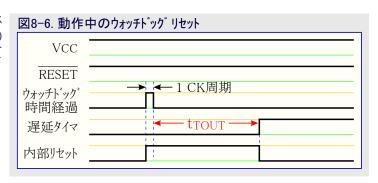

### 8.2.4. ウォッチト・ック・リセット

ウォッチトック・時間経過時、(内部的に)1CK周期幅の短いリセット パルスを生成します。このパルスの下降端で遅延タイマは遅延時間(t<sub>TOUT</sub>)の計時を始めます。ウォッチトック・タイマ操作の詳細については27頁の「ウォッチトック・タイマ」をご覧ください。

# 8.3. 内部基準電圧

ATtiny24/44/84は内部基準電圧が特徴です。この基準電圧は低電圧検出(BOD)に使われ、A/D変換やアナログ比較器の入力としても使えます。 バンドギャップ電圧は供給電圧と温度で変化します。

# 8.3.1. 基準電圧許可信号と起動時間

基準電圧には使われるべき方法に影響を及ぼすかもしれない起動時間があります。この起動時間は、116頁の「システムとリセットの特性」で与えられます。節電のために、この基準電圧は常にONではありません。この基準電圧は次の状態中ONです。

- 1. 低電圧検出リセット許可時 (BODLEVELヒュース、のプログラム(0)により)

- 2. アナログ比較器内部基準電圧接続時 (アナログ比較器制御/状態レジスタ(ACSR)の基準電圧入力選択(ACBG)=1)

- 3. A/D変換部動作許可時 (A/D変換制御/状態レジネタA(ADCSRA)のA/D動作許可(ADEN)=1)

従って低電圧検出(BOD)が許可されていないと、ACBGの設定(=1)またはA/D変換部許可(ADEN=1)後、使用者はアナログ比較器またはA/D変換器出力が使われる前に基準電圧へ起動時間を与えなければなりません。ハプーダウン動作での消費電力を減らすため、使用者はパワーダウン動作へ移行する前に基準電圧がOFFされるのを保証することで上の3つの状態を避けられます。

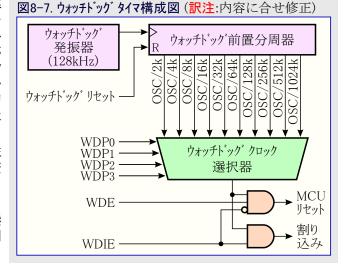

# 8.4. ウォッチトック タイマ

ウォッチト、ック、タイマは128kHzで動く独立したチップ、上の発振器からクロック駆動されます。ウォッチト、ック、タイマ前置分周器の制御により、ウォッチト、ック、リセット間隔は29頁の表8-3.で示されるように調整できます。ウォッチト、ック、リセット(WDR)命令はウォッチト、ック、タイマをリセットします。ウォッチト、ック、タイマはそれが禁止される時とチップ。リセットが起こる時もリセットされます。10種の異なるクロック周期がこのリセット周期を決めるために選択できます。別のウォッチト、ック、リセットなしにリセット周期が経過すると、ATtiny24/44/84はリセットしてリセットへ、クタから実行します。ウォッチト、ック、リセットの詳細タイミンク、については29頁の表8-3.を参照してください。

ウォッチドッグ タイマはリセットの代わりに割り込みを生成する設定にもできます。これはパワーダウン動作から起動するのにウォッチドッグを使う時に大変有用となり得ます。

予期せぬウォッチドッグ禁止や予期せぬ計時終了周期変更を防ぐため、2つの異なる安全レベルが表8-1.で示されるWDTONヒューズによって選択されます。詳細については次の「ウォッチドッグタイマ設定変更の時間制限手順」を参照してください。

表8-1. WDTONヒュース、設定によるウォッチト、ック、機能設定

| WDTON ヒューズ | 安全レベル | WDT初期状態 | WDT禁止方法  | 計時完了時間変更方法 |

|------------|-------|---------|----------|------------|

| 非プログラム(1)  | 1     | 禁止      | 時間制限     | なし(常時可)    |

| フ°ロクブラム(0) | 2     | 許可      | なし(常時許可) | 時間制限       |

### 8.4.1. ウォッチト、ック、タイマ設定変更の時間制限手順

ウォッチト、ック、設定変更手順は安全レベル間で僅かに異なります。各レベルに対して独立した手順が記述されます。

#### 8.4.1.1. 安全レベル1

この動作種別ではウォッチドッグタイマが初めに禁止されますが、どんな制限もなくウォッチドッグ許可(WDE)ビットに1を書くことにより許可できます。許可したウォッチドッグタイマを禁止する時に時間制限手順が必要とされます。許可したウォッチドッグタイマを禁止するには次の手順に従わなければなりません。

- 1. 同じ操作(命令)でウォッチトックで変更許可(WDCE)とウォッチトック許可(WDE)に論理1を書きます。WDEビットの直前の値に拘らず、論理1がWDEに書かれなければなりません。

- 2. 次からの4クロック周期内に同じ操作(命令)で欲したWDEとウォッチドッグタイマ前置分周選択(WDP3~0)ビットを書きますが、WDCEビットは解除(0)されてです。

# 8.4.1.2. 安全レベル2

この動作種別ではウォッチドッグ タイマが常に許可され、WDEビットは常に1として読めます。時間制限手順はウォッチドッグ計時完了周期を変更する時に必要とされます。ウォッチドッグ計時完了周期を変更するには次の手順に従わなければなりません。

- 1. 同じ操作(命令)でWDCEとWDEに論理1を書きます。WDEビットが常に設定(1)されていても、WDEは時間制限手順を開始するために1を書かれなければなりません。

- **2.** 次からの4クロック周期内に同じ操作(命令)で欲したWDP2~0ビットを書きますが、WDCEビットは解除( $\frac{0}{0}$ )されてです。WDEビットに書かれた値は無関係です。

#### 8.4.2. コート 例

次のコート・例はウォッチト、ッグ(WDT)をOFFに切り替えるアセンブリ言語とC言語の関数を示します。本例は(例えば全割り込み禁止によって)割り込みが制御され、それ故これらの関数実行中に割り込みが起きない前提です。

```

アセンブリ言語プログラム例

WDT OFF:

;ウォッチト、ック、タイマ リセット

WDR

R16, (0<<WDRF)

;WDRF=0値を取得

LDI

OUT

MCUSR, R16

;MCUSRのWDRFを解除(0)

IN

R16, WDTCSR

;現WDTCSR値を取得

ORI

R16, (1<<WDCE) | (1<<WDE)

;WDCEとWDE論理1値を設定

WDTCSR, R16

;WDCEとWDEに論理1書き込み

OUT

R16, (0<<WDE)

;WDE論理0値を取得

LDI

OUT

WDTCSR, R16

;ウォッチトックで禁止

;呼び出し元へ復帰

RET

C言語プログラム例

void WDT_off(void)

/* ウォッチト・ック・タイマ リセット */

_WDR();

MCUSR = 0x00;

/* MCUSRのWDRFを解除(0)*/

WDTCSR \mid = (1 << WDCE) \mid (1 << WDE);

/* WDCEとWDEに論理1書き込み */

WDTCSR = 0x00;

/* ウォッチト・ック 禁止 */

}

注: 4頁の「コート「例」をご覧ください。

```

# 8.5. リセット関係レジスタ

# 8.5.1. MCU状態レジスタ (MCU Status Register) MCUSR

MCU状態レジブタはどのリセット元がMCUリセットを起こしたかの情報を提供します。

| ピット         | 7 | 6 | 5 | 4 | 3    | 2    | 1     | 0    | _     |

|-------------|---|---|---|---|------|------|-------|------|-------|

| \$34 (\$54) | _ | - | _ | - | WDRF | BORF | EXTRF | PORF | MCUSR |

| Read/Write  | R | R | R | R | R/W  | R/W  | R/W   | R/W  |       |

| 初期値         | 0 | 0 | 0 | 0 | 内容参照 | 内容参照 | 内容参照  | 内容参照 |       |

■ L'ット7~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

■ ビット3 - WDRF: ウォッチドック゛リセット フラク゛(Watchdog Reset Flag)

このビットはウォッチドッグ リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

■ ビット2 - BORF: 低電圧リセット フラク (Brown-Out Reset Flag)

このビットは低電圧リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

■ Ľット1 – EXTRF:外部リセット フラク (External Reset Flag)

このビットは外部リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

■ ビット0 - PORF: 電源ONリセット フラク (Power-on Reset Flag)

このビットは電源ONリセットが起こると設定(1)されます。このビットはこのフラグへの論理0書き込みによってのみリセット(0)されます。

リセット条件の確認にリセット フラグを使うため、使用者はプログラム内で可能な限り早くMCUSRを読み、そして解除(0)すべきです。別のリセットが起こる前にこのレジスタが解除(0)されると、そのリセット元はリセットフラグを調べることによって得られます。

# 8.5.2. ウォッチト・ック タイマ制御/状態レシ、スタ (Watchdog Timer Control and Status Register) WDTCSR

| ピット         | 7    | 6    | 5    | 4    | 3   | 2    | 1    | 0    |        |

|-------------|------|------|------|------|-----|------|------|------|--------|

| \$21 (\$41) | WDIF | WDIE | WDP3 | WDCE | WDE | WDP2 | WDP1 | WDP0 | WDTCSR |

| Read/Write  | R/W  | R/W  | R/W  | R/W  | R/W | R/W  | R/W  | R/W  |        |

| 初期値         | 0    | 0    | 0    | 0    | 不定  | 0    | 0    | 0    |        |

### ■ ビット7 - WDIF: ウォッチドッグ割り込み要求フラグ (Watchdog Interrupt Flag)

ウォッチト、ック、タイマが割り込みに設定され、ウォッチト、ック、タイマで計時完了が起こると、本ヒ、ットが設定(1)されます。対応する割り込み処理へクタを実行すると、WDIFはハート・ウェアによって解除(0)されます。代わりにWDIFはこのフラグへの論理1書き込みによっても解除(0)されます。ステータスレシ、スタ(SREG)の全割り込み許可(I)ビットとウォッチト、ック・割り込み許可(WDIE)が設定(1)されていれば、ウォッチト、ック・計時完了割り込みが実行されます。

### ■ ビット6 - WDIE: ウォッチドッグ割り込み許可 (Watchdog Interrupt Enable)

このビットが1を書かれ、ステータス レジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されると、ウォッチドッグ割り込みが許可されます。この動作ではウォッチドッグタイマで計時完了が起きる場合、リセットに代わって対応する割り込みが実行されます。

WDEが設定(1)されると、WDIEは計時完了が起きるとき、ハートウェアによって自動的に解除(0)されます。これは割り込みを使う間のウォッチトッグ リセット保護を維持するのに有用です。WDIEビットが解除(0)された後、次の計時完了はリセットを生成するでしょう。このウォッチトッグ リセットを避けるには、各割り込み後にWDIEが設定(1)されなければなりません。

| 表8-2. ウォッチドッグ タイマ設定 |      |      |          |  |  |  |  |  |  |  |

|---------------------|------|------|----------|--|--|--|--|--|--|--|

| WDE                 | WDIE | 動作状態 | 計時完了での動作 |  |  |  |  |  |  |  |

| 0                   | 0    | 停止   | なし       |  |  |  |  |  |  |  |

| 0                   | 1    | 走行   | 割り込み     |  |  |  |  |  |  |  |

| 1                   | 0    | 走行   | リセット     |  |  |  |  |  |  |  |

| 1                   | 1    | 走行   | 割り込み     |  |  |  |  |  |  |  |

### ■ ビット4 - WDCE: ウォッチドッグ変更許可 (Watchdog Change Enable)

ウォッチト、ック、許可(WDE)と、ットが論理0を書かれるとき、このビットは設定(1)されなければなりません。さもなければ、ウォッチト、ック、は禁止されません。一旦1を書かれると、ハートウェアが4クロック周期後、このビットを解除(0)します。ウォッチト、ック、禁止手順についてはWDEビットの記述を参照してください。このビットは前置分周ビットを変更する時も設定(1)されなければなりません。27頁の「ウォッチト、ック、タイマ設定変更の時間制限手順」をご覧ください。

### ■ ビット3 - WDE: ウォッチドッグ許可 (Watchdog Enable)

ウォッチト、ック、許可(WDE)が論理1を書かれるとウォッチト、ック、タイマが許可され、WDEが論理0を書かれるとウォッチト、ック、タイマ機能が禁止されます。WDEはウォッチト、ック、変更許可(WDCE)と、ットが論理レヘ、ル1を持つ場合だけ解除(0)できます。許可されているウォッチト、ック、タイマを禁止するには次の手順に従わなければなりません。

- 1. 同じ操作(命令)内で、ウォッチト、ック・変更許可(WDCE)ヒ、ットとウォッチト、ック・許可(WDE)ヒ、ットに論理1を書きます。例え禁止操作を始める前のWDEが1に設定されていても、論理1がWDEに書かれなければなりません。

- 2. 次からの4クロック周期内で、論理0をWDEに書きます。これがウォッチト、ックを禁止します。

安全レヘブル2では上記の手順でもウォッチドック、タイマを禁止することができません。27頁の「ウォッチトック、タイマ設定変更の時間制限手順」をご覧ください。

安全レヘ・ル1ではWDEがMCUSRのウォッチト・ッグ リセット フラグ (WDRF)によって無効にされます。WDRFの説明については28頁の「MCU状態レジスタ(MCUSR)」をご覧ください。これはWDRFが設定(1)されていると、WDEが常に設定(1)されることを意味します。WDEを解除(0)するには上記手順でウォッチト・ッグを禁止する前にWDRFが解除(0)されなければなりません。この特徴は失敗を引き起こす状態中の複数リセットと失敗後の安全な起動を保証します。

注: ウォッチト・ック・タイマが応用で使われないなら、デバイス初期化でウォッチト・ック・禁止手順を全て行なうことが重要です。ウォッチト・ック・が偶然に許可されると(例えばポインタの逸脱や低電圧(ブラウンアウト)状態)、デバイスはリセットし、その転化が次のウォッチト・ック・リセットを引き起こすでしょう。この状態を避けるため、応用ソフトウェアは初期化ルーチンでWDRFフラグとWDE制御ビットを常に解除(0)すべきです。

### ■ ビット5,2~0 - WDP3~0: ウォッチドッグ タイマ前置分周選択(Watchdog Timer Prescaler 3,2,1 and 0)

このWDP3~0ビットはウォッチドッグタイマが許可される時のウォッチドッグタイマの前置分周を決めます。異なる前置分周値と対応する計時完了周期は**表8-3**.で示されます。

| . , . , ,             | 1777101240 01 117 24 0017 0 |      |      |        |       |      |      |      |      |       |                        |   |   |   |   |   |

|-----------------------|-----------------------------|------|------|--------|-------|------|------|------|------|-------|------------------------|---|---|---|---|---|

| 表8-3. ウォッチト゛ック゛前      | 表8−3. ウォッチドッグ前置分周器選択        |      |      |        |       |      |      |      |      |       |                        |   |   |   |   |   |

| WDP3                  |                             |      |      | (      | )     |      |      |      |      |       |                        |   | 1 |   |   |   |

| WDP2 0 1 0 1          |                             |      |      |        |       |      |      |      |      |       |                        |   |   |   |   |   |

| WDP1                  | WDP1 0 1                    |      |      |        |       | 0 1  |      |      | 0 1  |       | 1                      | 0 |   | 1 |   |   |

| WDP0                  | 0                           | 1    | 0    | 1      | 0     | 1    | 0    | 1    | 0    | 1     | 0                      | 1 | 0 | 1 | 0 | 1 |

| WDT発振周期数              | 2k                          | 4k   | 8k   | 16k    | 32k   | 64k  | 128k | 256k | 512k | 1024k |                        |   |   |   |   |   |

| 代表的計時完了<br>周期(VCC=5V) | 16ms                        | 32ms | 64ms | 0.125s | 0.25s | 0.5s | 1.0s | 2.0s | 4.0s | 8.0s  | (予約)( <mark>注</mark> ) |   |   |   |   |   |

| Value 1               |                             |      |      |        |       |      |      |      |      |       |                        |   |   |   |   |   |

注: 選択したなら、1010未満の有効設定の1つが使用されます。

# 9. 割り込み

本項はATtiny24/44/84によって実行される割り込み操作の詳細を記述します。AVR割り込み操作の一般説明については、8頁の「リセットと割り込みの扱い」をご覧ください。

# 9.1. ATtiny24/44/84の割り込みべか

ATtiny24/44/84の割り込み ごりをは下の表9-1. で記述されます。

表9-1. リセットと割り込みのベクタ

| ベクタ番号 | プログラム アドレス | 発生元              | 備考                     |

|-------|------------|------------------|------------------------|

| 1     | \$0000     | リセット             | 電源ON, WDT, BOD等の各種リセット |

| 2     | \$0001     | INT0             | 外部割り込み要求0              |

| 3     | \$0002     | PCINTO (PCIO)    | ピン変化0群割り込み要求           |

| 4     | \$0003     | PCINT1 (PCI1)    | ピン変化1群割り込み要求           |

| 5     | \$0004     | ウォッチドック゛WDT      | ウォッチドッグ計時完了            |

| 6     | \$0005     | タイマ/カウンタ1 CAPT   | タイマ/カウンタ1捕獲発生          |

| 7     | \$0006     | タイマ/カウンタ1 COMPA  | タイマ/カウンタ1比較A一致         |

| 8     | \$0007     | タイマ/カウンタ1 COMPB  | タイマ/カウンタ1比較B一致         |

| 9     | \$0008     | タイマ/カウンタ1 OVF1   | タイマ/カウンタ1溢れ            |

| 10    | \$0009     | タイマ/カウンタ0 COMPA  | タイマ/カウンタ0比較A一致         |

| 11    | \$000A     | タイマ/カウンタ0 COMPB  | タイマ/カウンタ0比較B一致         |

| 12    | \$000B     | タイマ/カウンタ0 OVF0   | タイマ/カウンタ0溢れ            |

| 13    | \$000C     | アナログ比較器 ANA_COMP | アナログ比較器出力遷移            |

| 14    | \$000D     | A/D変換器 ADC       | A/D変換完了                |

| 15    | \$000E     | EEPROM EE_RDY    | EEPROM 操作可             |

| 16    | \$000F     | USI START        | USI 開始条件検出             |

| 17    | \$0010     | USI OVF          | USI 計数器溢れ              |

プログラムが決して割り込み元を許可しないなら、割り込みへ、クタは使われず、これらの位置に通常のプログラムコート、を配置できます。 ATtiny24/44/84での最も代表的且つ一般的なリセットと割り込みのへ、クタアトレス用設定は下のプログラム例で示されます。

### 9.2. 外部割り込み

外部割り込みはINT0ピンまたはPCINT0~11ピンの何れかによって起動されます。許可したなら、例えINT0またはPCINT0~11ピンが出力として設定されても、割り込みが起動することに注目してください。この特徴はソフトウェア割り込みを生成する方法を提供します。ピン変化割り込みPCI1は許可したPCINT8~11の何れかが切り替わると起動します。ピン変化割り込みPCI0は許可したPCINT0~7の何れかが切り替わると起動します。ピン変化割り込み許可レジスタn(PCMSK0,PCMSK1)は、どのピンがピン変化割り込み要因となるかを制御します。PCINT0~11でのピン変化割り込みは非同期に検知されます。これはそれらの割り込みがアイドル動作以外の休止形態からもデバイスを起動するのに使えることを意味します。

INT0割り込みは上昇端または下降端(含む両端)またはLowレヘルによって起動できます。これはMCU制御レジスタ(MCUCR)の詳述で示される設定です。INT0割り込みがレヘル起動として設定、且つ許可されると、そのピンがLowに保持される限り、割り込みは(継続的に)起動します。INT0の上昇端または下降端割り込みの認知は15頁の「クロック体系」で記述されるI/Oクロックの存在を必要とすることに注意してください。

### 9.2.1. Lowレベル割り込み

INT0のLowレヘブル割り込みは非同期に検知されます。これはそれらの割り込みがアイブル動作以外の休止形態からもデブブイスを起動するのに使えることを意味します。I/Oクロックはアイブル動作を除く全休止形態で停止されます。

レヘル起動割り込みがハプワーダウン動作からの起動に使われる場合、この必要としたレヘルはレヘル割り込みを起動する完全な起動復帰のため、MCUに対して充分長く保持されなければならないことに注意してください。このレヘルが起動時間の最後に先立って消滅すると、MCUは今までどおり起動しますが、割り込みが生成されません。起動時間は15頁の「クロック元」で示されるようにSUTヒュースとCKSELヒュースで定義されます。

デバイスが起動復帰する前に割り込みピン上のLowレヘブルが取り去られると、プログラム実行は割り込み処理ルーチンへ転換されませんが、 SLEEP命令に続く命令から継続します。

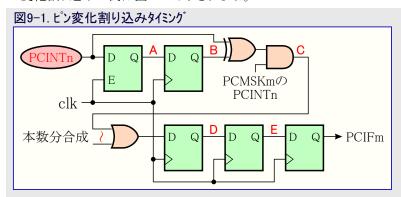

### 9.2.2. ピン変化割り込みタイミング

ピン変化割り込みの例は図9-1.で示されます。

# 9.3. 割り込み用レジスタ

### 9.3.1. MCU制御レジスタ (MCU Control Register) MCUCR

MCU制御レジスタは割り込み条件制御ビットを含みます。

| ピット         | 7    | 6   | 5   | 4   | 3   | 2     | 1     | 0     |       |

|-------------|------|-----|-----|-----|-----|-------|-------|-------|-------|

| \$35 (\$55) | BODS | PUD | SE  | SM1 | SM0 | BODSE | ISC01 | ISC00 | MCUCR |

| Read/Write  | R/W  | R/W | R/W | R/W | R/W | R/W   | R/W   | R/W   |       |

| 初期値         | 0    | 0   | 0   | 0   | 0   | 0     | 0     | 0     |       |

### ■ ビット1,0 - ISC01,0:外部割り込み0条件制御 (Interrupt Sense Control 0 bit1 and 0)

外部割り込みのはステータスレジスタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レジスタ(GIMSK)の外部割り込みの許可(INTO)ビットが設定(1)される場合のINT 0外部ピンによって活性(有効)にされます。割り込みを活性にする外部INTのピンのエッジとレベルは表9-2.で定義されます。INTOピンの値はエッジ検出に先立って採取されます。エッジまたは論理変化割り込みが選択される場合、1クロック周期よりも長く留まるパルスは割り込みを生成します。より短いパルスは割り込み発生が保証されません。Lowレベル割り込みが選択される場合、そのLowレベルは割り込みを生成するために現在実行している命令の完了まで保たれなければなりません。

| 表9-2. 5 | 表9-2. 外部割り込みO(INTO)割り込み条件 |                 |  |  |  |  |  |  |  |

|---------|---------------------------|-----------------|--|--|--|--|--|--|--|

| ISC01   | ISC00                     | ISC00 割り込み発生条件  |  |  |  |  |  |  |  |

| 0       | 0                         | INT0ピンのLowレヘ゛ル  |  |  |  |  |  |  |  |

| 0       | 1                         | INT0ピンの論理変化(両端) |  |  |  |  |  |  |  |

| 1       | 0                         | INT0ピンの下降端      |  |  |  |  |  |  |  |

| 1       | 1                         | INT0ピンの上昇端      |  |  |  |  |  |  |  |

# 9.3.2. 一般割り込み許可レジスタ (General Interrupt Mask Register) GIMSK

| ピット         | 7 | 6    | 5     | 4     | 3 | 2 | 1 | 0 |       |

|-------------|---|------|-------|-------|---|---|---|---|-------|

| \$3B (\$5B) | _ | INT0 | PCIE1 | PCIE0 | - | - | - | - | GIMSK |

| Read/Write  | R | R/W  | R/W   | R/W   | R | R | R | R |       |

| 初期値         | 0 | 0    | 0     | 0     | 0 | 0 | 0 | 0 |       |

### ■ ビット7,3~0 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

#### ■ ビット6 - INTO:外部割り込み0許可(External Interrupt Request 0 Enable)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットが設定(1)され、INT0ビットが設定(1)されると、INT0外部ピン割り込みが許可されます。 MCU制御レジスタ(MCUCR)の割り込み0条件制御(ISC01,0)ビットは、この外部割り込みがINT0ピンの上昇端、下降端、両端、またはLowレベルのどれで活性(有効)にされるかを定義します。例えINT0ピンが出力として設定されても、このピンの動きは割り込み要求を引き起こします。外部割り込み要求0に対応する割り込みはINT0割り込みへブタから実行されます。

### ■ ビット5 - PCIE1: ピン変化1群割り込み許可 (Pin Change Interrupt Enable 1)

ステータスレシ、スタ(SREG)の全割り込み許可(I)ビットが設定(1)され、PCIE1ビットが設定(1)されると、ピン変化1群割り込みが許可されます。 許可したPCINT8~11ピンの何れかの変化が割り込みを起こします。このピン変化割り込み要求に対応する割り込みはPCI1割り込みべ クタから実行されます。PCINT8~11ピンはピン変化割り込み許可レジスタ1(PCMSK1)によって個別に許可されます。

# ■ ビット4 - PCIEO: ピン変化O群割り込み許可 (Pin Change Interrupt Enable 0)

ステータスレジスタ(SREG)の全割り込み許可(I)ビットが設定(1)され、PCIE0ビットが設定(1)されると、ピン変化0群割り込みが許可されます。 許可したPCINT0~7ピンの何れかの変化が割り込みを起こします。このピン変化割り込み要求に対応する割り込みはPCI0割り込みへプタから実行されます。PCINT0~7ピンはピン変化割り込み許可レジスタの(PCMSKO)によって個別に許可されます。

### 9.3.3. 一般割り込み要求フラグレジスタ (General Interrupt Flag Register) GIFR

| ピット         | 7 | 6     | 5     | 4     | 3 | 2 | 1 | 0 |      |

|-------------|---|-------|-------|-------|---|---|---|---|------|

| \$3A (\$5A) | _ | INTF0 | PCIF1 | PCIF0 | - | - | - | - | GIFR |

| Read/Write  | R | R/W   | R/W   | R/W   | R | R | R | R |      |

| 初期値         | 0 | 0     | 0     | 0     | 0 | 0 | 0 | 0 |      |

### ■ L\*ット7.3~0 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

# ■ ビット6 - INTFO:外部割り込み0要求フラグ(External Interrupt Flag 0)

INT0ピン上のエッジまたは論理変化が割り込み要求を起動すると、INTF0が設定(1)になります。ステータスレジスタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レジスタ(GIMSK)の外部割り込み0許可(INT0)ビットが設定(1)なら、MCUは対応する割り込みへ、クタへ飛びます。このフラク゛は割り込みルーチンが実行されると解除(0)されます。代わりにこのフラク゛は論理1を書くことによっても解除(0)できます。INT0がレヘル割り込みとして設定されると、このフラク゛は常に解除(0)されます。

# ■ ビット5 - PCIF1: ピン変化1群割り込み要求フラグ(Pin Change Interrupt Flag 1)

PCINT8~11t°ンの何れかの論理変化が割り込み要求を起動すると、PCIF1が設定(1)になります。ステータスレジスタ(SREG)の全割り込み許可(I)t'ットと一般割り込み許可レジスタ(GIMSK)のt°ン変化1群割り込み許可(PCIE1)t'ットが設定(1)なら、MCUは対応する割り込み ^ ク タへ飛びます。このフラク は割り込みルーチンが実行されると解除(0)されます。代わりにこのフラク は論理1を書くことによっても解除(0)できます。

# ■ ビット4 - PCIF0: ピン変化0群割り込み要求フラグ(Pin Change Interrupt Flag 0)

PCINT0~7ピンの何れかの論理変化が割り込み要求を起動すると、PCIF0が設定(1)になります。ステータスレシ、スタ(SREG)の全割り込み許可(I)ビットと一般割り込み許可レシ、スタ(GIMSK)のピン変化0群割り込み許可(PCIE0)ビットが設定(1)なら、MCUは対応する割り込みへ、クタへ飛びます。このフラグは割り込みルーチンが実行されると解除(0)されます。代わりにこのフラグは論理1を書くことによっても解除(0)できます。

# 9.3.4. ピン変化割り込み許可レジスタ1 (Pin Change Enable Mask 8~11) PCMSK1

| ピット         | 7 | 6 | 5 | 4 | 3       | 2       | 1      | 0      |        |

|-------------|---|---|---|---|---------|---------|--------|--------|--------|

| \$20 (\$40) | _ | - | - | - | PCINT11 | PCINT10 | PCINT9 | PCINT8 | PCMSK1 |

| Read/Write  | R | R | R | R | R/W     | R/W     | R/W    | R/W    |        |

| 初期値         | 0 | 0 | 0 | 0 | 0       | 0       | 0      | 0      |        |

### ■ L\*ット7~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

### ■ ビット3~0 - PCINT11~PCINT8: ピン変化割り込み11~8許可 (Pin Change Enable Mask 11~8)

各PCINT8~11ビットは対応するI/Oピンでピン変化割り込みが許可されるかどうかを選びます。PCINT8~11と一般割り込み許可(GIMS K)レジスタのPCIE1が設定(1)なら、対応するI/Oピンのピン変化割り込みが許可されます。PCINT8~11が解除( $^{0}$ )されると、対応するI/O ピンのピン変化割り込みは禁止されます。

# 9.3.5. ピン変化割り込み許可レジスタO (Pin Change Enable Mask 0~7) PCMSKO

| ピット         | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |        |

|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| \$12 (\$32) | PCINT7 | PCINT6 | PCINT5 | PCINT4 | PCINT3 | PCINT2 | PCINT1 | PCINT0 | PCMSK0 |

| Read/Write  | R/W    |        |

| 初期値         | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |        |

### ■ ビット7~0 - PCINT7~PCINT0: ピン変化割り込み7~0許可(Pin Change Enable Mask 7~0)

# 10. 入出力ポート

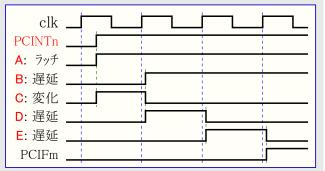

全てのAVRのポートは標準デジタルI/Oポートとして使われる時に真の読み-変更-書き (リート、モディファイライト)を機能的に持ちます。これはSBIとCBI命令で他のどのピンの方向をも無意識に変更することなく、1つのポートピンの方向を変更できることを意味します。(出力として設定されていれば)駆動値を変更、または(入力として設定されていれば)アルアップ抵抗を許可/禁止する時にも同じく適用されます。各出力緩衝部は高い吐き出し(ソース)と吸い込み(シンク)の両能力で対称的な駆動特性を持ちます。このピン駆動部はLED(表示器)を直接駆動するのに充分な強さです。全てのポートピンは個別に選択可能な、供給電圧で抵抗値が変化しないプルアップ抵抗を持っています。全てのI/Oピンは図10-1.で示されるようにVCCとGNDの両方に保護ダイオートがあります。各値の完全な一覧については114頁の「電気的特性」を参照してください。

本項内の全てのレシ、スタとビットの参照は一般形で記されます。小文字の'x'はポート番

号文字、小文字の'n'はビット番号を表します。けれどもプログラム内でレジスタやビット定義に使うとき、正確な形式(例えば、ここで一般に記されたPORTxnがポートBのビット3に対してはPORTB3)が使われなければなりません。物理的なI/Oレジスタとビット位置は43頁の「I/O ポート用レジスタ」で一覧されます。

各々1つの出力レジスタ(PORTx)、方向レジスタ(DDRx)、入力レジスタ(PINx)の各ポートに対して、3つI/Oメモリアトレス位置が割り当てられます。入力レジスタのI/O位置は読むだけで、一方出力レジスタと方向レジスタは読み書き(両方)です。けれどもPINxレジスタのビットへの論理1書き込みは、出力レジスタの対応ビット値を(1/0)反転する結果になります。加えてMCU制御レジスタ(MCUCR)のプルアップ禁止(PUD)ビットが設定(1)されると、全ポートで全ビットに対してプルアップ機能を禁止します。

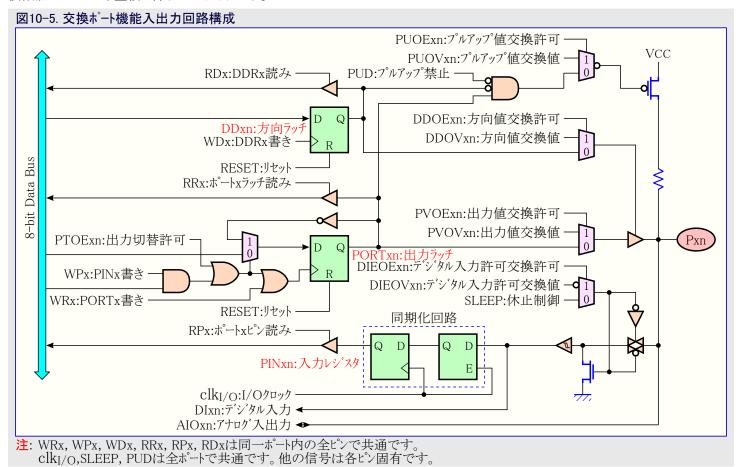

標準デジタルI/OとしてのI/Oポートの使用は次の「**標準デジタル入出力としてのポート**」で記述されます。多くのポート ピンはデバイスの周辺機能用の交換機能と多重化されます。ポート ピンとの各交換機能のインターフェース法は37頁の「**交換ポート機能**」で記述されます。交換機能の完全な記述については個別機能部項を参照してください。

ポート ピンのいくつかの交換機能の許可は、そのポート内の他のピンの標準デジタル入出力としての使用に影響しないことに注意してください。

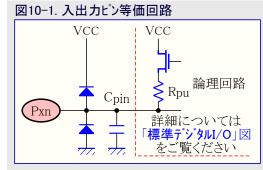

# 10.1. 標準デジタル入出力としてのポート

このポートは任意の内部プルアップ付き双方向I/Oポートです。図10-2.はここで属にPxnと呼ばれるI/Oポート ピンの1つの機能説明を示します。

### 10.1.1. ピンの設定

各ポート ピンは3つのレシ、スタ ビット、DDxn、PORTxn、PINxnから成ります。43頁の「I/Oポート用レシ、スタ」で示されるように、DDxnビットは DDRx I/Oアドレス、PORTxnビットはPORTx I/Oアドレス、PINxビットはPINx I/Oアドレスでアクセスされます。

DDRxレジスタ内のDDxnビットはそのピンの方向を選択します。DDxnが論理1を書かれるとPxnは出力ピンとして設定されます。DDxnが論理0を書かれるとPxnは入力ピンとして設定されます。

そのピンが入力ピンとして設定される時にPORTxnが論理1を書かれると、プルアップ抵抗が活性(有効)にされます。プルアップ抵抗をOFF に切り替えるにはPORTxnが論理0を書かれるか、またはそのピンが出力ピンとして設定されなければなりません。ポート ピンは例えクロックが動いていなくても、リセット条件が活性(有効)になるとHi-Zにされます。

そのピンが出力ピンとして設定される時にPORTxnが論理1を書かれると、そのポート ピンはHigh(1)に駆動されます。そのピンが出力ピンとして設定される時にPORTxnが論理0を書かれると、そのポート ピンはLow(0)に駆動されます。

### 10.1.2. ピンの出力交互切り替え

PINxnへの論理1書き込みはDDRxnの値に拘らず、PORTxnの値を反転切り替えします。SBI命令がポート内の1ビットの反転切り替えに使えることに注目してください。

### 10.1.3. 入出力間の切り替え

Hi-Z入力(DDxn=0, PORTxn=0)とHigh出力(DDxn=1, PORTxn=1)間の切り替え時、プルアップ許可入力(DDxn=0, PORTxn=1)または Low出力(DDxn=1, PORTxn=0)のどちらかの中間状態が生じるに違いありません。通常、高インピーダンス環境は強力なHigh(吐き出し) 駆動部とプルアップ間の違いに気付かないので、プルアップが許可された状態は十分受け入れられます。この事例でないなら、全ポートの全プルアップを禁止するために、MCU制御レジスタ(MCUCR)のプルアップ禁止(PUD)ピットが設定(1)できます。

プルアップ入力とLow出力間の切り替えは同じ問題を発生します。使用者は中間状態としてHi-Z入力(DDxn=0, PORTxn=0)またはHigh 出力(DDxn=1, PORTxn=1)のどちらかを使わなければなりません。

表10-1.はピン値に対する制御信号の一覧を示します。

| 表10-1. ボー | 表10-1. ボート ビンの設定 |             |     |         |                               |  |  |  |  |  |  |

|-----------|------------------|-------------|-----|---------|-------------------------------|--|--|--|--|--|--|

| DDxn      | PORTxn           | PUD (MCUCR) | 入出力 | プルアップ抵抗 | 備考                            |  |  |  |  |  |  |

| 0         | 0                | X           | 入力  | なし      | 高インピーダンス (Hi-Z)               |  |  |  |  |  |  |

| 0         | 1                | 0           | 入力  | あり      | Pxnに外部からLowを入力すると吐き出し電流が流れます。 |  |  |  |  |  |  |

| 0         | 1                | 1           | 入力  | なし      | 高インピーダンス (Hi-Z)               |  |  |  |  |  |  |

| 1         | 0                | X           | 出力  | 721.    | Low (吸い込み)出力                  |  |  |  |  |  |  |

High (吐き出し)出力

なし

出力

# 10.1.4. ピン値の読み込み

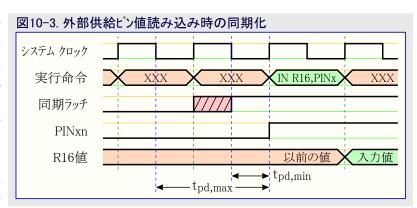

DDxn方向ビットの設定に関係なく、ポート ピンはPINxnレジスタ ビットを通して読めます。図10-2.で示されるようにPINxnレジスタ ビットと先行するラッチは同期化回路を構成します。これは物理ピンが内部クロックのエッジ付近で値を変える場合の未定義状態(メタ ステーブル)を避けるために必要とされますが、それは遅延も持ち込みます。図10-3.は外部的に加えられたピン値を読む時の同期化タイミング図を示します。伝播遅延の最小と最大は各々tpd,minとtpd,maxで示されます。

(図10-3.で)システム クロックの最初の下降端直後から始まるクロック周期を考察してください。このラッチはクロックがLowの時に閉じ、クロックがHighの時に同期ラッチ信号の斜線部分で示されるように通過(トランスペプレント)となります。この信号値はシステム クロックがLowになる時に保持(ラッチ)されます。それが続くクロックの上昇端でPINxnレジスタに取り込まれます。2つの矢印tpd,minとtpd,maxによって示されるように、ピン上の単一信号遷移は出現時点に依存して0.5~1.5システムクロック周期遅らされます。

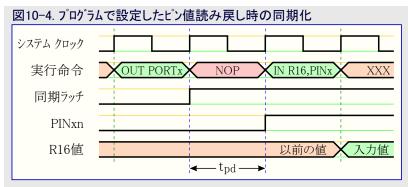

ソフトウェアが指定したピン値を読み戻す時は、図10-4.で示されるようにNOP命令が挿入されなければなりません。OUT命令はシステム クロックの上昇端で同期ラッチを設定します。この場合、同期化回路を通過する遅延時間(tpd)は1システム クロック周期です。

次のコート・例はポートAピンの0と1をHigh出力、2と3をLow出力、4をプルアップ指定として4と5を入力に設定する方法を示します。結果のピン値が再び読み戻されますが、前記で検討されたように、いくつかのピンへ直前に指定された値を読み戻すことができるようにNOP命令が挿入されます。

```

アセンブリ言語プログラム例

LDI

R16, (1<<PA4) | (1<<PA1) | (1<<PA0)

;プルアップとHigh値を取得

R17, (1<<DDA3) | (1<<DDA2) | (1<<DDA1) | (1<<DDA0) ;出力ビット値を取得

LDI

PORTA, R16

;プルアップとHigh値を設定

OUT

OUT

DDRA, R17

;入出力方向を設定

NOP

;同期化遅延対処

;ピン値読み戻し

IN

R16, PINA

C言語プログラム例

unsigned char i;

/* */

PORTA = (1 << PA4) | (1 << PA1) | (1 << PA0);

/* プルアップとHigh値を設定 */

DDRA = (1 << DDA3) | (1 << DDA2) | (1 << DDA1) | (1 << DDA0);

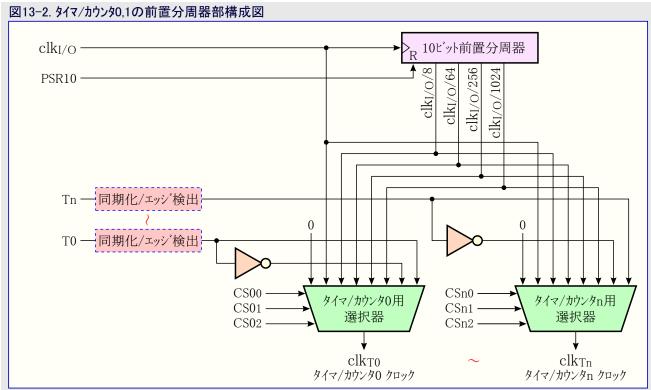

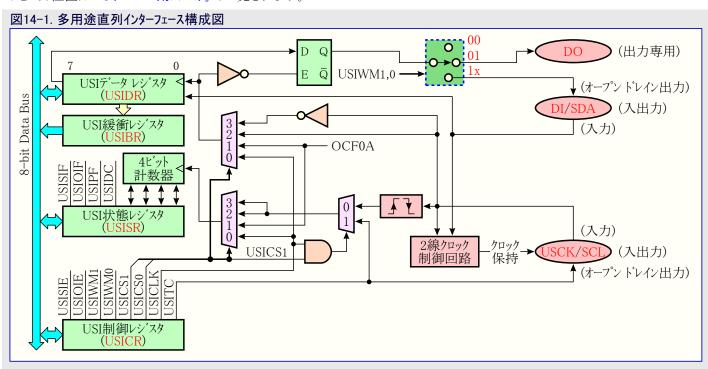

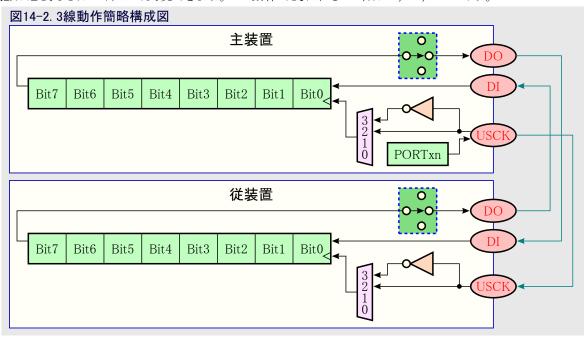

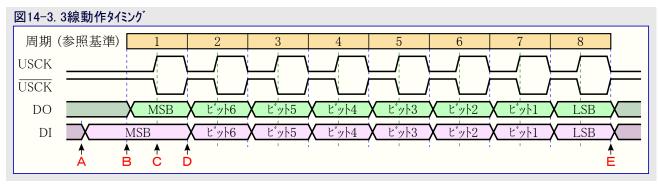

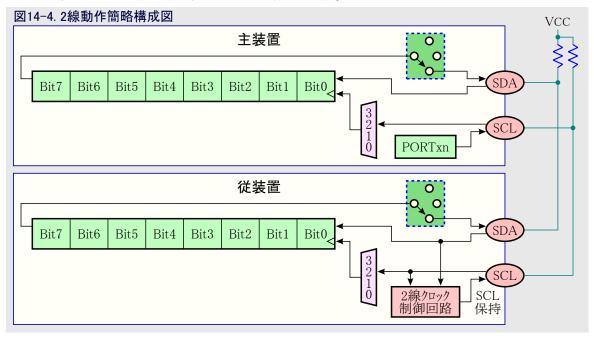

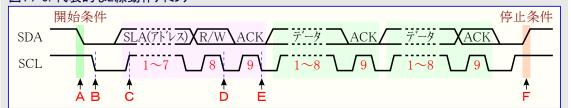

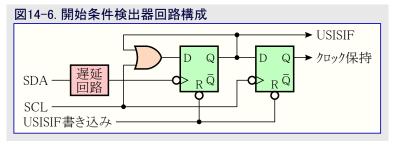

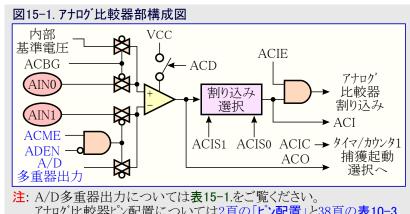

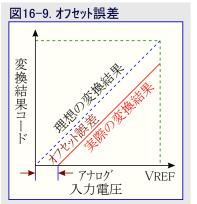

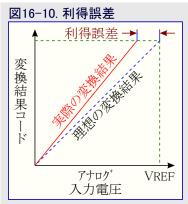

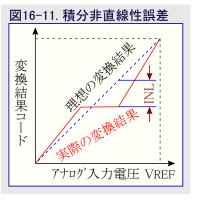

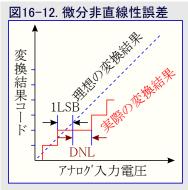

/* 入出力方向を設定 */