# 8Kバイト実装書き込み可能フラッシュ メモリ付き Atmel 8ビット AVR マイクロ コントローラ

テータシート

### 特徴

- 高性能、低消費Atmel® AVR® 8ビット マイクロ コントローラ

- 進化したRISC構造

- 強力な123命令(多くは1周期実行)

- 32個の1バイト長汎用レジスタ

- 完全なスタティック動作

- 20MHz時、20MIPSに達する高速動作

- データメモリと不揮発性プログラムメモリ

- 実装書き換え可能な8Kバイト(4K語)フラッシュ メモリ

- 耐久性: 10,000回の書き換え周回

- 実装書き換え可能な256小小のEEPROM

- 耐久性: 100,000回の書き換え周回

- 512バ仆の内蔵SRAM

- 個別施錠ビットを持つ任意のブート コード領域

- データ保持力: 20年/85℃, 100年/25℃

- 内蔵周辺機能

- 各々2つのPWMチャネルを持つ、1つの8ビットタイマ/カウンタと1つの16ビットタイマ/カウンタ

- 設定可能な超低電力ウォッチドッグ、タイマ

- チップ。上のアナログ比較器

- 10ビット A/D変換器

- 外部28と内部4のシングル エント 入力チャネル

- 開始フレーム検出を持つ全2重USART

- 主装置/従装置動作SPI直列インターフェース

- 従装置I2C直列インターフェース

- 特殊マイクロ コントローラ機能

- 低電力アイドル、A/D変換雑音低減、パワーダウンの低消費動作形態

- 強化した電源ONJセット回路

- 供給電圧採取での設定可能な低電圧検出器(BOD)回路

- 内部及び外部の割り込み元

- 28ピンでのピン変化割り込み

- 温度校正任意選択を持つ校正付き8MHz発振器

- 校正付き32kHz超低電力発振器

- ●8つの入出力ピンでの高電流駆動能力

- I/Oと外囲器

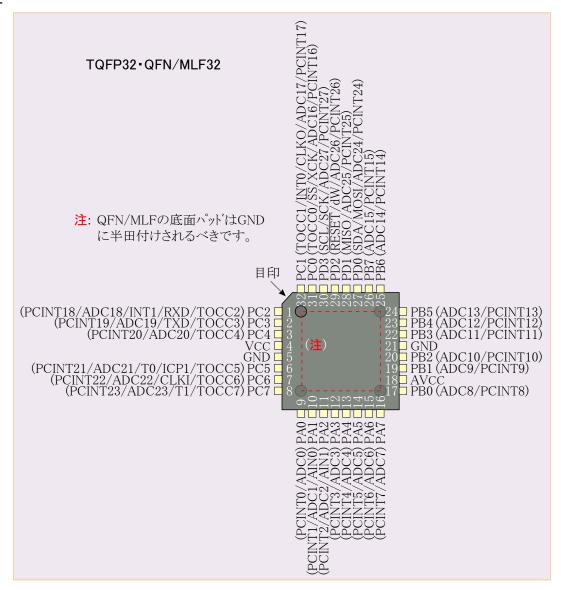

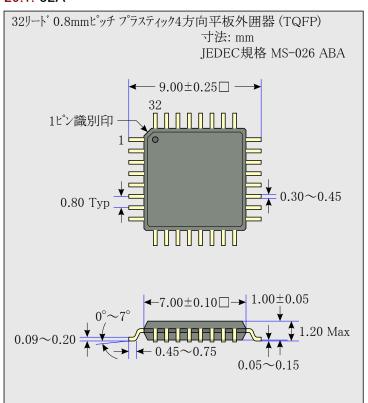

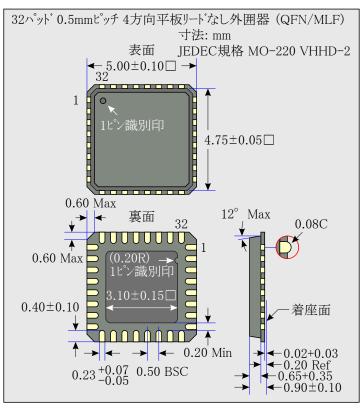

- 32リート、TQFP、32パット、QFN/MLF: 28本の設定可能なI/O線

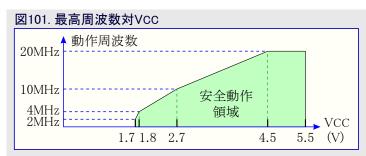

- 動作速度

- $0\sim2MHz/1.7\sim5.5V$

- $0\sim4\text{MHz}/1.8\sim5.5\text{V}$

- $0\sim10\text{MHz}/2.7\sim5.5\text{V}$

- $0\sim20\text{MHz}/4.5\sim5.5\text{V}$

- 代表消費電力 (1MHz,1.8V)

- 0.2mA (活動動作)

- 30µA (アイドル動作)

- 1µA (パワーダウン動作、WDT許可)

- 0.1µA (パワータ゛ウン動作,WDT禁止)

本書は一般の方々の便宜のため有志により作成されたもので、Atmel社とは無関係であることを御承知ください。しおりの[はじめに]での内容にご注意ください。

# 1. ピン配置

### 1.1. ピン説明

#### 1.1.1. VCC

デジタル電源ピン。

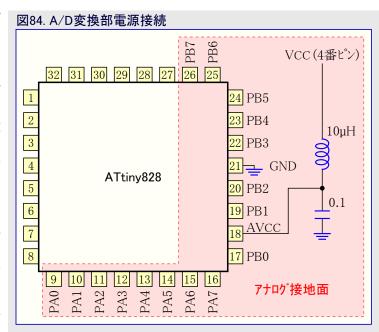

#### 1.1.2. AVCC

AVCCはA/D変換器と選択入出力ピン用の供給電圧(電源)ピンです。例えA/D変換が使われなくても、外部的にVCCへ接続されるべきです。A/D変換が使われる場合、このピンは137頁の「**雑音低減技術**」で記述されるように低域通過濾波器を通してVCCに接続されることが推奨されます。

ポートAとポートBの全てのピンはAVCCによって給電されます。他の全ての入出力ピンはそれらの供給電圧をVCCから取ります。

#### 1.1.3. GND

接地ピン。

#### 1.1.4. RESET

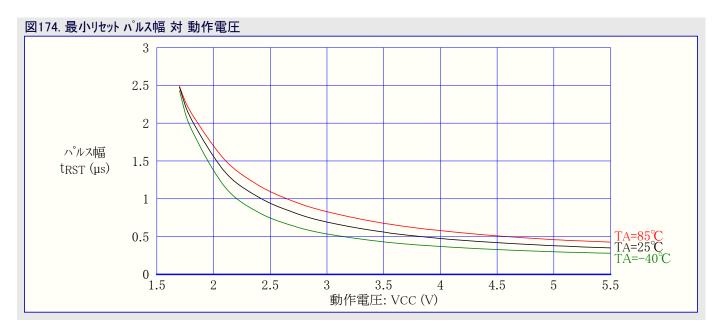

リセット入力。最小パルス幅より長いこのピンのLowレベルは、リセット ピンが禁止されていなければ、例えクロックが動作していなくてもリセットを生成します。最小パルス幅は168頁の**表107**.で与えられます。より短いパルスはリセットの生成が保証されません。

リセット ピンは(弱い)入出力ピンとしても使うことができます。

### **1.1.5**. **PA7~PA0** (本°一卜A)

ポートAは(ビット毎に選択される)内蔵プルアップ抵抗付きの8ビットの双方向入出力ポートです。出力緩衝部は高い吸い込みと標準の吐き出し能力を持ちます。ポート駆動能力については166頁の**表103**.をご覧ください。

入力の時にプルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポート ピンには吐き出し電流が流れます。リセット条件が有効になるとき、クロックが動作していなくても、ポート ピンはHi-Zになります。

このポートはピン変化割り込み、アナログ比較器、A/D変換器に関する交換ピン機能を持ちます。43頁の「交換ポート機能」をご覧ください。

### 1.1.6. PB7~PB0 (本°-トB)

ポートBは(ビット毎に選択される)内蔵プルアップ抵抗付きの8ビットの双方向入出力ポートです。出力緩衝部は高い吸い込みと標準の吐き出し能力を持ちます。ポート駆動能力については166頁の**表103**.をご覧ください。

入力の時にプルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポート ピンには吐き出し電流が流れます。リセット条件が有効になるとき、クロックが動作していなくても、ポート ピンはHi-Zになります。

このポートはピン変化割り込みとA/D変換器に関する交換ピン機能を持ちます。43頁の「交換ポート機能」をご覧ください。

#### 1.1.7. PC7~PC0 (ホ°ートC)

ポートCは(ビット毎に選択される)内蔵プルアップ抵抗付きの8ビットの双方向入出力ポートです。出力緩衝部は高い吸い込みと標準の吐き出し能力を持ちます。任意選択で、追加の高吸い込み能力を許可することができます。ポート駆動能力については166頁の表103.をご覧ください。

入力の時にプルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートピンには吐き出し電流が流れます。リセット条件が有効になるとき、クロックが動作していなくても、ポートピンはHi-Zになります。

このポートはピン変化割り込み、A/D変換器、タイマ/カウンタ、外部割り込み、直列インターフェースに関する交換ピン機能を持ちます。43頁の「**交換ポート機能**」をご覧ください。

#### 1.1.8. PD3~PD0 (ホートD)

ポートDは(ビット毎に選択される)内蔵プルアップ抵抗付きの4ビットの双方向入出力ポートです。PD0とPD3の出力緩衝部は吸い込みと吐き出しの両能力で対称的な駆動特性を持ちます。PD1の出力駆動部は高い吸い込みと標準の吐き出し能力を持ち、一方PD2はそれがリセット ピンとして使われるために弱い駆動特性を持ちます。ポート駆動能力については166頁の表103.をご覧ください。

入力の時にプルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポート ピンには吐き出し電流が流れます。リセット条件が有効になるとき、クロックが動作していなくても、ポート ピンはHi-Zになります。

このポートはピン変化割り込み、A/D変換器、直列インターフェース、デバッグWIREに関する交換ピン機能を持ちます。43頁の「**交換ポート機 能**」をご覧ください。

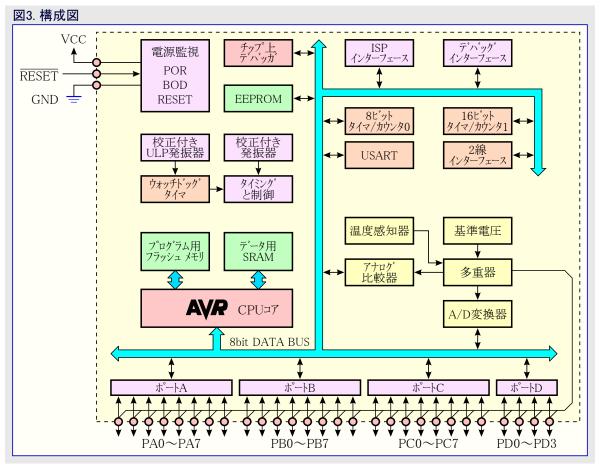

## 2. 概要

ATtiny828はAVR強化RISC構造を基にした低消費CMOS 8ビット マイクロ コントローラです。1周期での強力な命令の実行によってATtin y828はMHzあたり1MIPSに達する単位処理量を成し遂げ、処理速度対消費電力の最適化を設計者に許します。

AVRコアは32個の汎用作業レジスタと豊富な命令群の組み合わせです。32個の全レジスタはALU(Arithmetic Logic Unit)に直結され、1クロック周期で実行され、単一命令でアクセスされるべき2つの個別レジスタを許します。結果の構造は簡潔でコート効率的な一方で、現状のCISC型マイクロコントローラに対して最大10倍の単位処理量を達成します。

ATtiny828は以下の機能を提供します。

- 8Kバイトの実装書き込み可能なフラッシュ メモリ

- 512バイトのSRAMデータ メモリ

- 256ハ イトのEEPROMデータ メモリ

- 28本の汎用入出力線

- 32個の汎用作業レジスタ

- 2つのPWMチャネルを持つ1つの8ビット タイマ/カウンタ

- 2つのPWMチャネルを持つ1つの16ビット タイマ/カウンタ

- 内部及び外部の割り込み

- 4つの内部と28個の外部チャネルを持つ10ビット A/D変換器

- 内蔵発振器付き超低電力の設定可能なウォッチドッグタイマ

- 開始フレーム検出を持つ設定可能なUSART

- 従装置、I<sup>2</sup>C適合、2線インターフェース(TWI)

- 主装置/従装置直列周辺インターフェース(SPI)

- 校正付き8MHz発振器

- 校正付き32kHz超低電力発振器

- ソフトウェア選択可能な3つの節電動作形態

デバイスは節電用の以下の動作形態を含みます。

- アイ・ル動作: CPUを停止し、一方タイマ/カウンタ、A/D変換器、アナログ比較器、SPI、TWI、割り込み機構に機能の継続を許します。

- A/D変換雑音低減動作: A/D変換器を除く全I/O部とCPUを停止することによってA/D変換中の切り替え雑音を最小にします。

- パワーダウン動作:レシ、スタがそれらの内容を保ち、以降の割り込みまたはハートウェアリセットまで、全チップ機能が禁止されます。

本デバイスはAtmelの高密度不揮発性メモリ技術を使って製造されます。プログラム用フラッシュメモリは通常の不揮発性メモリ書き込み器による直列インターフェースを通して、またはAVRコアで走行するチップ上のブートコードによって実装書き換えすることができます。ブートプログラムは応用プログラムをフラッシュメモリに設定するのにどのインターフェースをも使うことができます。ブート領域フラッシュメモリ内のソフトウェアは応用領域フラッシュメモリ更新中に実行する、真の「書き込み中の読み出し可」動作を提供します。

ATtiny828 AVRはCコンパイラ、マクロ アセンブラ、プログラム デバッカブンミュレータ、評価キットを含む完全なプログラム及びシステム開発ツールで支援されます。

## 3. 一般情報

### 3.1. 資料

包括的なデータシート、応用記述、ドライバ群と開発ツールの説明はhttp://www.atmel.com/avrでのダウンロードで利用可能です。

### 3.2. コート 例

この文書はデバイスの様々な部分の使用法を手短に示す簡単なコート・例を含みます。これらのコート・例はアセンブルまたはコンパイルに先立って、デバイス定義へッタ・ファイルがインクルートされると仮定します。全てのCコンパイラ製造業者がヘッタ・ファイル内にヒット定義を含めるとは限らず、またCでの割り込みの扱いがコンパイラに依存することに注意してください。より多くの詳細についてはCコンパイラの資料で確認してください。

## 3.3. データ保持力

信頼性証明結果はデータ保持誤り率の反映を示し、20年以上/85℃または100年以上/25℃で1PPMよりずっと小さな値です。

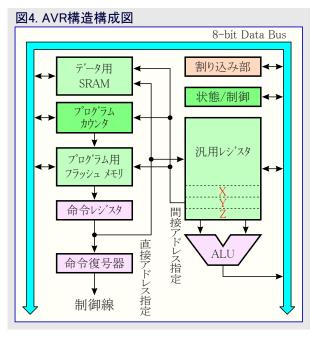

### 4. CPU コア

本項はAVRコア構造を一般的に説明します。このCPUコアの主な機能は正しいプログラム実行を保証することです。従ってCPUはメモリアクセス、計算実行、周辺制御、割り込み操作ができなければなりません。

### 4.1. 構造概要

最大効率と平行処理のため、AVRはプログラムとデータに対してメモリとハスを分離するハーハート、構造を使います。プログラムメモリ内の命令は単一段のハペイプラインで実行されます。1命令の実行中に次の命令がプログラムメモリから事前取得されます。この概念は全部のクロック周期で命令実行を可能にします。プログラムメモリは実装書き換え可能なフラッシュメモリです。

高速レジスタファイルは1クロック周期アクセスの16個の8ビット長汎用レジスタを含みます。これは1クロック周期ALU(Arithmetic Logic Unit)操作を許します。代表的なALU操作では2つのオペラントがレジスタファイルからの出力で、1クロック周期内でその操作が実行されてその結果がレジスタファイルに書き戻されます。

32個中の6つのレジスタは効率的なアトンス計算ができるデータ空間アトンス指定用に3つの16ビット長間接アトンスポインタ用レジスタとして使われます。これらアトンスポインタの1つはプログラム用フラッシュメモリ内の定数表参照用アトンスポインタとしても使えます。これら16ビット長付加機能レジスタはX,Y,Zレジスタで、本項内で後述されます。

ALUはレシ、スタ間またはレシ、スタと定数間の算術及び論理操作を支援します。 単一レシ、スタ操作もALUで実行できます。算術演算操作後、操作結果についての情報を反映するために、ステータスレシ、スタ(SREG)が更新されます。

プログラムの流れは条件/無条件分岐や呼び出し命令によって提供され、全アトレス空間を直接アトレス指定する能力があります。 殆どのAVR命令は単一16 ビット語(ワート)形式ですが、32ビット幅の命令も存在します。 実際の命令1式はいくつかのデバイスが(全)命令1式の部分だけを実装するように変わります。

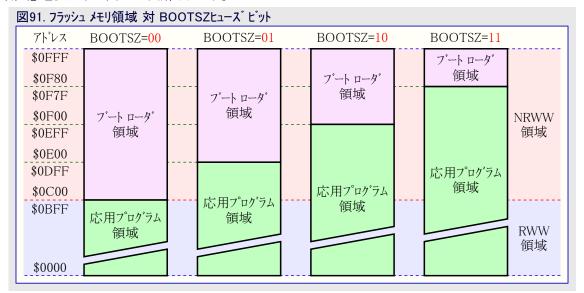

プログラム用フラッシュ メモリ空間はブート プログラム領域と応用プログラム領域の2つに分けられます。 どちらの領域にも書き込み禁止や読み書き防止用の専用施錠ビットがあります。 応用フラッシュ メモリ領域内に書き込むSPM命令はブート プログラム領域内に属さ(存在し)なければなりません。

割り込みやサブルーチン呼び出し中、戻りアトレスを示すプログラム カウンタ(PC)はスタックに保存されます。スタックは一般的なデータ用SRAM上に 実際には割り当てられ、従ってスタック容量はSRAM容量とSRAM使用量でのみ制限されます。全ての使用者プログラムはリセット処理ルーチンで(サブルーチン呼び出しや割り込みが実行される前に)、スタック ポインタ(SP)を初期化しなければなりません。SPはI/O空間で読み書きアクセスが可能です。データ用SRAMはAVR構造で支援される4つの異なるアトレス指定種別を通して容易にアクセスできます。

AVR構造に於けるメモリ空間は全て直線的な普通のメモリ配置です。

柔軟な割り込み部にはI/O空間の各制御レシ、スタとステータスレシ、スタ(SREG)の特別な全割り込み許可(I)ビットがあります。全ての割り込みは割り込みへ、クタ表に個別の割り込みへ、クタを持ちます。割り込みには割り込みへ、クタ表の位置に従う優先順があります。下位側割り込みへ、クタアドレスが高い優先順位です。

I/Oメモリ空間は制御レジスタや他のI/O機能としてCPU周辺機能用の64アドレスを含みます。I/Oメモリはデータ空間位置\$0000~\$003Fとしてアクセスできます。加えて、ATtiny828はST/STS/STDとLD/LDS/LDDの命令だけを使うことができる、データ空間内の\$0060~\$00FFの拡張I/O空間を持ちます。

## 4.2. ALU (Arithmetic Logic Unit)

高性能なAVRのALUは16個全ての汎用レジスタに直接接続され動作します。汎用レジスタ間または汎用レジスタと即値間の演算操作は単一クロック周期内で実行されます。ALU操作は算術演算、論理演算、ビット操作の3つの主な種類に大別されます。符号付きと符号なし両方の乗算と固定小数点形式を支援する乗算器(乗算命令)も提供する構造の実装(製品)もあります。より多くの情報については外部資料の「AVR命令一式」と204頁の「命令要約」項をご覧ください。

### 4.3. ステータス レジスタ

ステータス レジスタは最も直前に実行した演算命令の結果についての情報を含みます。この情報は条件処理を行うためのプログラムの流れ変更に使えます。ステータス レジスタは全てのALU操作後、更新されることに注目してください。これは多くの場合でそれ用の比較命令使用の必要をなくし、高速でより少ないコードに帰着します。より多くの情報については外部文書の「AVR命令一式」と204頁の「命令要約」章をご覧ください。

ステータス レジ スタは割り込み処理ルーチン移行時の保存と割り込みからの復帰時の回復(復帰)が自動的に行われません。これはソフトウェア によって扱われなければなりません。

### 4.4. 汎用レジスタファイル

このレシブスタファイルはAVRの増強したRISC命令群用に最適化されています。必要な効率と柔軟性を達成するために、次の入出力機構がレジスタファイルによって支援されます。

- 1つの8ビット出力オペランドと1つの8ビットの結果入力

- 2つの8ビット出力オペランドと1つの8ビットの結果入力

- 2つの8ビット出力オペランドと1つの16ビットの結果入力

- 1つの16ビット出力オペランドと1つの16ビットの結果入力

図5.はCPU内の32個の汎用作業レジスタの構造を示します。

レジスタファイルを操作する殆どの命令は全てのレジスタへの直接アクセスを持つ単一周期命令です。

図5.で示されるように各レジスタは使用者データ空間の最初の32位置へ直接的に配置することで、それらはデータメモリアドレスも割り当てられます。例え物理的にSRAM位置として実装されていなくてもX,Y,Zレジスタ(ポインタ)がレジスタファイル内のどのレジスタの指示にも設定できるように、このメモリ構成は非常に柔軟なレジスタのアクセスを提供します。

| 5. 汎用レジスタ構成圓 | 의      |              |

|--------------|--------|--------------|

| 7            | 0 アドレス | 特殊機能         |

| R0           | \$00   |              |

| R1           | \$01   |              |

| R2           | \$02   |              |

| >            |        |              |

| R13          | \$0D   |              |

| R14          | \$0E   |              |

| R15          | \$0F   |              |

| R16          | \$10   |              |

| R17          | \$11   |              |

| }            |        |              |

| R26          | \$1A   | Xレジスター・下位バイト |

| R27          | \$1B   |              |

| R28          | \$1C   | Yレジスタ 下位バイト  |

| R29          | \$1D   | 上位ハイト        |

| R30          | \$1E   | Zレジスター 下位バイト |

| R31          | \$1F   | 上位バイト        |

### 4.4.1. Xレシ、スタ、Yレシ、スタ、Zレシ、スタ

R26~R31レジスタには通常用途の使用にいくつかの追加機能があります。これらのレジスタはデータ空間の間接アトレス指定用の16 ビットアトレスポインタです。3つのX,Y,Z間接アトレスレジスタは図6.で記載したように定義されます。

種々のアドレス指定種別で、これらのアドレス レジスタは固定変位、 自動増加、自動減少としての機能を持ちます(詳細については 「命令一式手引書」をご覧ください)。

| 15     XH (上位)     XL (下位)     0       X レジスタ     7     R27 (\$1B)     0 7     R26 (\$1A)     0       15     YH (上位)     YL (下位)     0       Y レジスタ     7     R29 (\$1D)     0 7     R28 (\$1C)     0       15     ZH (上位)     ZL (下位)     0       7     R29 (\$1D)     0 7     R28 (\$1C)     0 | 図6. X,Y,Zレシ | バスタ精 | <b>请成</b> 図 |     |            |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|-------------|-----|------------|----|

| 15 YH (上位) YL (下位) 0<br>Y レジスタ 7 R29 (\$1D) 0 7 R28 (\$1C) 0<br>15 ZH (上位) ZL (下位) 0                                                                                                                                                                                                             |             | 15   | XH (上位)     |     | XL (下位)    | 0  |

| Y レジスタ     7     R29 (\$1D)     0 7     R28 (\$1C)     0       15     ZH (上位)     ZL (下位)     0                                                                                                                                                                                                  | X レジスタ      | 7    | R27 (\$1B)  | 0 7 | R26 (\$1A) | 0  |

| 15 ZH (上位) ZL (下位) 0                                                                                                                                                                                                                                                                             |             | 15   | YH (上位)     |     | YL (下位)    | 0_ |

|                                                                                                                                                                                                                                                                                                  | Y レジスタ      | 7    | R29 (\$1D)  | 0 7 | R28 (\$1C) | 0  |

|                                                                                                                                                                                                                                                                                                  |             | 15   | ZH (上位)     |     | ZL (下位)    | 0_ |

| Z V V X R31 (\$1F) 0 7 R30 (\$1E) 0                                                                                                                                                                                                                                                              | Z レジスタ      | 7    | R31 (\$1F)  | 0 7 | R30 (\$1E) | 0  |

### **4.5**. スタック ポインタ

スタックは主に一時データ、局所変数、割り込みとサブルーチン呼び出し後の戻りアドレスの保存に使われます。スタック ポインタ(SPHとSPL)レシスタは常にこのスタックの先頭(<mark>訳注</mark>:次に使われるべき位置)を指し示します。スタックが高位メモリへ伸長することに注意してください。これはPUSH命令がスタック ポインタ値を減少し、POP命令が増加することを意味します。

スタック ポインタはサブルーチンや割り込みのスタックが置かれるデータSRAMのスタック領域を指し示します。このスタック空間はどのサブルーチン呼び出しの実行や割り込みの許可にも先立ってプログラムによって定義されなければなりません。

このポインタはPUSH命令でデータがスタックに格納されると-1され、POP命令でデータがスタックから引き出されると+1されます。それはサブルーチン呼び出しや割り込みで戻りアトレスがスタックに格納されると-2され、サブルーチンからの復帰(RET)命令や割り込みからの復帰(RETI)命令でアトレスがスタックから引き出されると+2されます。

AVRのスタック ポインタはI/O空間内の2つの8ビット レシ、スタとして実装されます。スタック ポインタの幅と実装されるビット数はデバイス依存です。 いくつかのAVRデバイスでは全てのデータ メモリがSPLだけを使ってアドレス指定することができます。この場合、SPHレジスタは実装されません。

スタック ポインタはSRAMの最低アトレスである最低値、I/Oレジスタ領域の上の位置に設定されなければなりません。12頁の表3.をご覧ください。

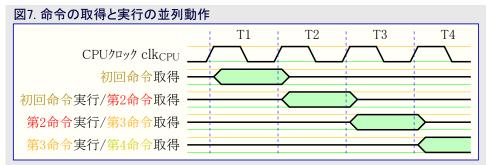

### 4.6. 命令実行タイミング

本項は命令実行の一般的なアクセス タイミング の概念を記述します。AVR CPUはチップ(デバイス)用に選択したクロック元から直接的に生成したCPUクロック(clkCPU)によって駆動されます。内部クロック分周は使われません。

図7.はハーハート・構造と高速アクセスレジスタファイルの概念によって可能とされる並列の命令取得と命令実行を示します。これは機能対費用、機能対クロック、機能対電源部に関する好結果と対応するMHzあたり1MIPSを達成するための基本的なパイプラインの概念です。

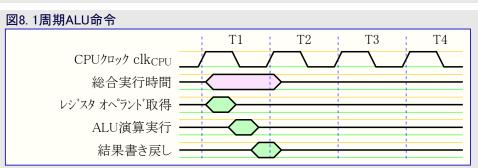

図8.はレジスタファイルに対する内部タイミングの概念を示します。単一クロック周期で2つのレジスタオペラントを使うALU操作が実行され、その結果が転送先レジスタへ書き戻されます。

## 4.7. リセットと割り込みの扱い

AVRは多くの異なる割り込み元を提供します。これらの割り込みと独立したリセット ベクタ各々はプログラム メモリ空間内に独立したプログラム ベクタを持ちます。全ての割り込みは割り込みを許可するために、ステータス レジスタ(SREG)の全割り込み許可(I)ビットと共に論理1が書かれなければならない個別の許可ビットを割り当てられます。

ブート施錠ビット(BLB02またはBLB12)がプログラム(0)されると、プログラム カウンタ値によっては割り込みが自動的に禁止されるかもしれません。この特質はソフトウェア保護を改善します。詳細については151頁の「施錠ビット」項をご覧ください。

既定でのプログラム メモリ空間の最下位アトンスはリセットと割り込みへクタとして定義されます。 へうタの完全な一覧は32頁の「**割り込み**」で示されます。この一覧は各種割り込みの優先順位も決めます。下位側アトンスがより高い優先順位です。 リセットが最高優先順位で次が外部割り込み要求の(INTO)です。

割り込みベクタ表はMCU制御レジスタ(MCUCR)の割り込みベクタ選択(IVSEL)ビットの設定(1)によってブート フラッシュ領域先頭へ移動することができます。より多くの情報については35頁の「MCUCR - MCU制御レジスタ」と32頁の「割り込み」を参照してください。リセット ベクタもBOOTRSTヒューズのプログラム(0)によってブート フラッシュ領域先頭へ移動できます。145頁の「ブート ローダ プログラムへの移行」をご覧ください。

割り込みが起こると全割り込み許可(I)ビットが解除(0)され、全ての割り込みは禁止されます。使用者ソフトウェアは多重割り込みを許可するため、全割り込み許可(I)ビットへ論理1を書けます。その後全ての許可した割り込みが現在の割り込みルーチンで割り込めます。全割り込み許可(I)ビットは割り込みからの復帰(RETI)命令が実行されると、自動的に設定(1)されます。

根本的に2つの割り込み形式があります。1つ目の形式は割り込み要求フラグを設定(I)する事象によって起動されます。これらの割り込みでは割り込み処理ルーチンを実行するために、プログラム カウンタは対応する現実の割り込みへ、クタを指示し、ハートウェアが対応する割り込み要求フラグをJ解除(0)します。割り込み要求フラグは解除(0)されるべきフラグのビット位置へ論理1を書くことによっても解除(0)できます。対応する割り込み許可ビットが解除(0)されている間に割り込み条件が起こると、割り込み要求フラグが設定(1)され、割り込みが許可されるか、またはこのフラグがソフトウェアによって解除(0)されるまで記憶(保持)されます。同様に、全割り込み許可(I)ビットが解除(0)されている間に1つまたはより多くの割り込み条件が起こると、対応する割り込み要求フラグが設定(1)されて全割り込み許可(I)ビットが設定(1)されるまで記憶され、その(I=1)後で優先順に従って実行されます。

2つ目の割り込み形式は割り込み条件が存在する限り起動し(続け)ます。これらの割り込みは必ずしも割り込み要求フラグを持っているとは限りません。割り込みが許可される前に割り込み条件が消滅すると、この割り込みは起動されません。

AVRが割り込みから抜け出すと常に主プログラムへ戻り、何れかの保留割り込みが扱われる前に1つ以上の命令を実行します。

ステータス レジスタ(SREG)は割り込みルーチンへ移行時の保存も、復帰時の再設定も自動的に行われないことに注意してください。これはソフトウェアによって扱われなければなりません。

割り込みを禁止するためにCLI命令を使うと、割り込みは直ちに禁止されます。CLI命令と同時に割り込みが起こっても、CLI命令後に割り込みは実行されません。次例は時間制限EEPROM書き込み手順中に割り込みを無効とするために、これがどう使えるかを示します。

```

アセンブリ言語プログラム例

;ステータスレジスタを保存

IN

R16, SREG

;EEPROM書き込み手順中割り込み禁止

CLI

EECR, EEMPE

;EEPROM主書き込み許可

SBI

EECR, EEPE

;EEPROM書き込み開始

SBI

OUT

SREG, R16

;ステータスレジスタを復帰

C言語プログラム例

/* ステータス レシ スタ保存変数定義 */

char cSREG;

/* ステータス レジ スタを保存 */

cSREG = SREG;

_CLI() ;

/* EEPROM書き込み手順中割り込み禁止*/

EECR \mid = (1 << EEMPE);

/* EEPROM主書き込み許可*/

/* EEPROM書き込み開始 */

EECR = (1 < EEPE);

/* ステータス レジ スタを復帰 */

SREG = cSREG:

注: 5頁の「コート・例」をご覧ください。

```

割り込みを許可するためにSEI命令を使うと、次例で示されるようにどの保留割り込みにも先立ってSEI命令の次の命令が実行されます。

| アセンブリ言語プログラム例 |                       |

|---------------|-----------------------|

| SEI           | ;全割り込み許可              |

| SLEEP         | ;休止形態移行(割り込み待ち)       |

| C言語プログラム例     |                       |

| _SEI();       | /* 全割り込み許可 */         |

| _SLEEP();     | /* 休止形態移行 (割り込み待ち) */ |

注: SLEEP命令までは割り込み禁止、保留割り込み実行前に休止形態へ移行します。

注: 5頁の「コート・例」をご覧ください。

### 4.7.1. 割り込み応答時間

許可した全てのAVR割り込みに対する割り込み実行応答は最小4クロック周期です。4クロック周期後、実際の割り込み処理ルーチンに対するプログラム ヘクタ アドレスが実行されます。この4クロック周期時間中にプログラム カウンタ(PC)がスタック上に保存(プッシュ)されます。このヘクタは標準的に割り込み処理ルーチンへの無条件分岐で、この分岐は3クロック周期要します。複数周期命令実行中に割り込みが起こると、その割り込みが扱われる前に、この命令が完了されます。MCUが休止形態の時に割り込みが起こると、割り込み実行応答時間は4クロック周期増やされます。この増加は選択した休止形態からの起動時間に加えてです。

割り込み処理ルーチンからの復帰は4クロック周期要します。これらの4クロック周期中、プログラム カウンタ(PC:2バイト)がスタックから取り戻され(ポップ)、スタック ポインタは増加され(+2)、ステータス レシ、スタ(SREG)の全割り込み許可(I)ビットが設定(1)されます。

### 4.8. コア関係レジスタ

### 4.8.1. CCP - 構成設定変更保護レジスタ (Configuration Change Protection Register)

| ピット         | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0     |     |

|-------------|-------|---|---|---|---|---|---|-------|-----|

| \$36 (\$56) | (MSB) |   |   |   |   |   |   | (LSB) | CCP |

| Read/Write  | W     | W | W | W | W | W | W | R/W   |     |

| 初期値         | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |     |

### ● ビット7~0 - CCP7~0: 構成設定変更保護 (Configuration Change Protenction)

保護されたI/Oレジスタの内容を変更するため、CCPレジスタは最初に正しい識票を書かれなければなりません。CCPが書かれた後、保護されたI/Oレジスタは次からの4CPU命令周期中に書けます。これらの周期中は全ての割り込みが無視されます。これらの周期後に割り込みはCPUによって自動的に再び取り扱われて、どの保留割り込みもそれらの優先権に従って実行されます。

保護されたI/Oレジスタの識票が書かれると、CCP0は保護機能が許可されている限り1として読めます。CCP7~1は常に0として読めます。

表1.は認証に於ける識票を示します。

#### 表1. 構成設定変更保護レジスタによって認証される識票

| 識票   | 適用群                      | 説明           |

|------|--------------------------|--------------|

| \$D8 | CLKPR, MCUCR, WDTCSR (注) | 保護されたI/Oレジスタ |

注: WDTCSRではWDEとWDP3~0のビットだけが保護されます。

### 4.8.2. SPH.SPL (SP) - スタック ポインタ (Stack Pointer)

| ピット         | 15     | 14     | 13     | 12     | 11     | 10     | 9      | 8      |     |

|-------------|--------|--------|--------|--------|--------|--------|--------|--------|-----|

| \$3E (\$5E) | _      | -      | -      | -      | -      | -      | SP9    | SP8    | SPH |

| Read/Write  | R      | R      | R      | R      | R      | R      | R/W    | R/W    |     |

| 初期値         | RAMEND |     |

| ピット         | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |     |

| \$3D (\$5D) | SP7    | SP6    | SP5    | SP4    | SP3    | SP2    | SP1    | SP0    | SPL |

| Read/Write  | R/W    |     |

| 初期値         | RAMEND |     |

### • ビット9~0 - SP9~0 : スタック ポインタ (Stack Pointer)

スタック ポインタ レジ スタは上位側メモリ位置から下位側目メモリ位置へ伸長するように実行されるスタックの先頭を指し示します。従ってスタックへのPUSH命令はスタック ポインタを減らします。

データSRAM内のスタック空間は、どのサブルーチン呼び出し実行や割り込み許可にも先立ってプログラムによって定義されなければなりません。

(<mark>訳補</mark>) ATtiny828の内蔵SRAMは512バイト(\$0100~\$02FF)です。従って、SRAM最終位置は\$02FF(<mark>0000 0010 1111 1111</mark>)です。

#### 4.8.3. SREG - ステータス レジスタ (Status Register)

| ピット         | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _    |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$3F (\$5F) | I   | T   | Н   | S   | V   | N   | Z   | С   | SREG |

| Read/Write  | R/W |      |

| 初期値         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

#### ● ビット7 - I: 全割り込み許可 (Global Interrupt Enable)

全割り込み許可ビットは割り込みが許可されるために設定(1)されなければなりません。その時の個別割り込み許可制御は独立した制御レジスタで行われます。全割り込み許可ビットが解除(0)されると、個別割り込み許可設定に拘らず、どの割り込みも許可されません。I ビットは割り込みが起こった後にハードウェアによって解除(0)され、後続の割り込みを許可するために、RETI命令によって設定(1)されます。Iビットは「命令一式参考書」で記述されるようにSEIやCLI命令で応用(プログラム)によって設定(1)や解除(0)もできます。

### ● ビット6 - T:ビット変数 (Bit Copy Storage)

ビット複写命令、BLD(Bit LoaD)とBST(Bit STore)は操作したビットの転送元または転送先として、このTビットを使います。レジスタ ファイルのレジスタからのビットはBST命令によってTに複写でき、TのビットはBLD命令によってレジスタ ファイルのレジスタ内のビットに複写できます。

### ビット5 − H : ハーフキャリー フラク゛(Half Carry Flag)

ハーフキャリー(H)フラグはいくつかの算術操作でのハーフキャリーを示します。ハーフキャリーはBCD演算に有用です。詳細情報については「命令ー式記述」をご覧ください。

#### ● ビット4 - S: 符号 (Sign Bit, S= N Ex-OR V)

Sフラグは常に負(N)フラグと2の補数溢れ(V)フラグの排他的論理和です。詳細情報については「命令一式記述」記述をご覧ください。

### ● ビット3 - V: 2の補数溢れフラグ(2's Complement Overflow Flag)

2の補数溢れ(V)フラグは2の補数算術演算を支援します。詳細情報については「命令一式記述」記述をご覧ください。

### ビット2 - N: 負フラク (Negative Flag)

負(N)フラグは算術及び論理操作での負の結果(MSB=1)を示します。詳細情報については「命令一式記述」記述をご覧ください。

#### ビット1 - Z: セロフラケ (Zero Flag)

ゼロ(Z)フラグは算術及び論理操作でのゼロ(0)の結果を示します。詳細情報については「命令一式記述」記述をご覧ください。

#### ヒット0 − C : キャリー フラク (Carry Flag)

キャリー(C)フラグは算術及び論理操作でのキャリー(またはボロー)を示します。詳細情報については「命令一式記述」記述をご覧ください。

## 5. メモリ

AVR構造は独立したアトンス空間に各メモリ形式を配置してプログラムメモリとデータメモリを区別します。 実行可能なコート、は不揮発性プログラムメモリ(フラッシュ)に置かれ、一方データは揮発性(SRAM)または不揮発性メモリ(EEPROM)のどちらにも置くことができます。右の図9.をご覧ください。

全てのメモリ空間は直線的で規則的です。

### 5.1. プログラム メモリ (フラッシュ)

ATtiny828はプログラム保存用に実装書き換え可能なチップ上の8Kバイのフラッシュ メモリを含みます。フラッシュ メモリは不揮発性、換言するとそれらは例え給電されない時でも格納された情報を維持します。

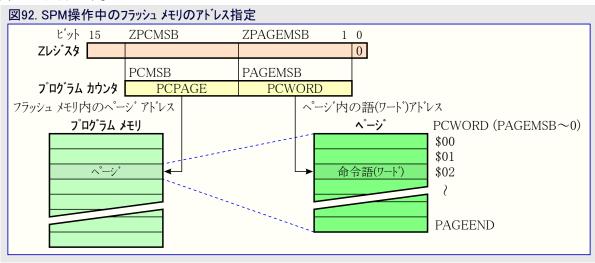

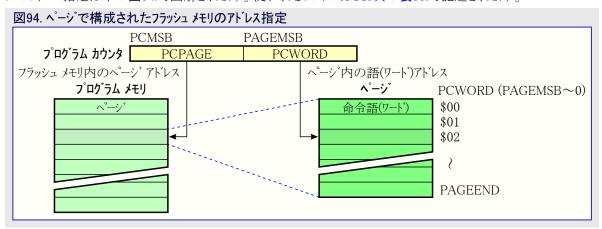

全てのAVR命令が16または32ビット幅のため、フラッシュ メモリは4096×16ビットとして構成されます。プログラム カウンタ(PC)は12ビット幅で、従って、下の表2.で説明されるように、プログラムの全4096位置をアトレス指定する能力があります。

ソフトウェア保護のため、フラッシュ プログラム メモリはブート プログラム領域と応用プログラム領域の2つに分けられます。より多くの詳細については147頁の「**フラッシュ メモリの自己プログラミング**」と144頁の「**応用とブート ローダのフラッシュ領域**」をご覧ください。

定数表はプログラム メモリのアトンス空間全体に置くことができます。204頁の「命令要約」でLPM(プログラム メモリ取得)とSPM(プログラム メモリ格納)の命令をご覧ください。プログラム用フラッシュ メモリは156頁の「外部プログラミング」で記述されるように、外部装置からもプログラミングすることができます。

命令の取得と実行のタイミング図は8頁の「**命令実行タイミング**」で示されます。

フラッシュ メモリは最低10,000回の消去/書き込み回数の耐久性を持ちます。

| 表2. プログラム メモ | 表2. プログラム メモリ(フラッシュ)の大きさ |       |               |  |  |  |  |  |  |  |

|--------------|--------------------------|-------|---------------|--|--|--|--|--|--|--|

| <b>デバイ</b> ス | フラッシュ                    | 容量    | アドレス範囲        |  |  |  |  |  |  |  |

| ATtiny828    | 8Kバイト                    | 4096語 | \$0000~\$0FFF |  |  |  |  |  |  |  |

### 5.2. データ メモリ(SRAM)とレシ、スタ ファイル

表3.はATtiny828のデータメモリとレシ、スタファイルがどう構成されるかを示します。これらのメモリ領域は揮発性、換言すると、それらは電力が取り去れる時に情報を維持しません。

| 丰っ           | =* h | JTIL | エンごフカ | 77/1 | の配置     |

|--------------|------|------|-------|------|---------|

| <i>オ</i> ▽.3 | エーツ  | メナリと | レン ムダ | ノアイル | (ノ) 四八百 |

| <b>デバイ</b> ス | メモリ領域         | 容量     | 長アドレス (注1)    | 短アドレス ( <mark>注2</mark> ) |

|--------------|---------------|--------|---------------|---------------------------|

|              | 汎用レジスタファイル    | 32バイト  | \$0000~\$001F | (利用不可)                    |

| Λ T+im-020   | I/Oレシ スタ ファイル | 64バイト  | \$0020~\$005F | \$00∼\$3F                 |

| ATtiny828    | 拡張I/Oレジスタファイル | 160バイト | \$0060~\$00FF | (利用不可)                    |

|              | データ用SRAM      | 512バイト | \$0100~\$02FF | (利用不可)                    |

注1: データ アドレスとしても知られます。このアドレス指定の形態はデータ メモリとレジスタ ファイル全体を網羅します。アドレスは2語命令の16ビット領域に含まれます。

**注2**: 直接I/Oアドレスとしても知られます。このアドレス指定の形態はI/Oレジスタ領域の一部だけを網羅します。これはアドレスが命令語に組み込まれた命令によって使われます。

768個のメモリ位置は汎用レジスタ ファイル、I/Oレジスタ、拡張I/Oレジスタ、内部データ メモリ(SRAM)を含みます。

将来のデバイスとの互換性のため、アクセスされる場合、予約ビットはOが書かれるべきです。予約されたI/Oメモリ アドレスは決して書かれるべきではありません。

### 5.2.1. 汎用レジスタ ファイル

最初の32位置は汎用レジスタ ファイル用に予約されます。これらのレジスタは7頁の「汎**用レジスタ ファイル**」で詳細に記述されます。

#### 5.2.2. I/Oレシ スタ ファイル

汎用レシ、スタファイルに後続する次の64位置はI/Oレシ、スタ用に予約されます。この領域内のレシ、スタは主にデバイスのI/Oと周辺機能部の通信に使われます。データはIN,OUT,LD,STとその派生のような命令を用いて、I/O空間とレシ、スタファイル間で転送することができます。この領域内の全てのI/Oレシ、スタはINとOUTの命令でアクセスすることができます。これらのI/O特有命令はI/Oレシ、スタ内の先頭位置を \$00とし、最後を\$3Fとしてアドレス指定します。

下位32個のレジスタ(アト・レス範囲\$00~\$1F)はいくつかのビット特有命令によってアクセス可能です。これらのレジスタではSBIとCBIを用いてビットが容易に設定(1)と解除(0)が行われ、一方ビット条件分岐はSBIC,SBIS,SBRC,SBRSの命令を用いて容易く作成されます。

この領域のレジスタはLD/LDD/LDS/(LDI)とST/STD/STSの命令でアクセスすることもできます。これらの命令は揮発性メモリ全体を1つのデータ空間として扱い、従ってI/Oレジスタを\$0020で始まるアドレスで指定します。

204頁の「命令要約」をご覧ください。

ATtiny828はどんな情報の格納にも使うことができる3つの汎用I/Oレジスタも含みます。200頁の「レジスタ要約」でGPIOR0、GPIOR1、GPIOR2をご覧ください。これらの汎用I/OレジスタはそれらがSBI,CBI,SBIC,SBIS,SBRC,SBRSのようなビット特有命令でアクセス可能なため、全域変数や状態フラグの格納に著しく有用です。

#### 5.2.3. 拡張I/Oレシ スタ ファイル

標準I/Oレジスタファイルに後続する次の160位置は拡張I/Oレジスタ用に予約されます。ATtiny828はINとOUTの命令でアドレス指定することができるよりも多くの周辺機能部を持つ複合マイクロコントローラです。拡張I/O領域内のレジスタはLD/LDD/LDSとST/STD/STSの命令を用いてアクセスされなければなりません。204頁の「命令要約」をご覧ください。

I/Oレジスタの一覧については200頁の「レジスタ要約」をご覧ください。

### 5.2.4. データ メモリ (SRAM)

汎用レジスタファイルとI/Oレジスタファイルに後続する残りの512位置は内部データSRAM用に予約されます。

5つの利用可能なアドレス指定形態があります。

- 直接:このアドレス指定形態はデータ空間全体に届きます。

- 間接

- 変位付き間接:このアドレス指定形態はYまたはZのレジスタによって与えられる基本アドレスから63アドレス位置に届きます。

- 事前減少付き間接:この形態ではアクセス前にアト・レス レシ、スタが自動的に減少(-1)されます。アト・レス ポインタ レシ、スタ(X,Y,Z)は汎用レシ、スタ ファイルでレシ、スタR26~R31内に置かれます。7頁の「汎用レシ、スタ ファイル」をご覧ください。

- 事後増加付き間接:この形態ではアクセス後にアトレスレジスタが自動的に増加(+1)されます。アトレスポインタレジスタ(X,Y,Z)は汎用レジスタファイルでレジスタR26~R31内に置かれます。7頁の「汎用レジスタファイル」をご覧ください。

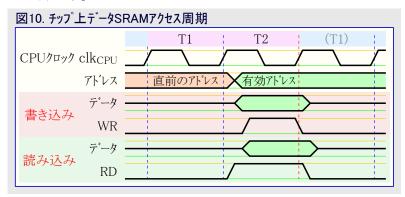

全てのアドレス指定形態は汎用レジスタ ファイル、I/Oレジスタ ファイル、データ メモリを含む揮発性メモリ全体で使うことができます。 内部SRAMは下の図10.で図解されるように、2clkcpu周期でアクセスされます。

(<mark>訳補</mark>) 内蔵SRAMのアクセスを含む代表的な命令はT1,T2の 2周期で実行され、T1で対象アドレスを取得/(算出)/ 確定し、T2で実際のアクセスが行われます。後続する (T1)は次の命令のT1です。

### 5.3. データ メモリ (EEPROM)

ATtiny828は256パイトの不揮発性データメモリを含みます。このEEPROMは単一パイトで読み書きすることができる独立したデータ空間として構成されます。全てのアクセスレジスタはI/O空間に置かれます。

EEPROM配置は下の表4.で要約されます。

EEPROM操作計時に内部8MHz発振器が使われます。この発振器の周波数は21頁の「OSCCALO - 発振器0校正レジスタ」で記述される必要条件内でなければなりません。

激しく濾波した供給によって給電される時に供給電圧(VCC)は電力上昇と電力下降で緩やかに上昇または下降しそうです。緩やか

な上昇と下降の時間は指定されるよりも低い供給電圧で走る状態にデバイスを置くかもしれません。このような状況での問題を避けるために15頁の「EEPROM化けの防止」をご覧ください。

EEPROMは最低100,000回の消去/書き込み回数の耐久性を持ちます。

| 表4. 不揮発性データ メモリ(EEROM)の大きさ |           |  |  |  |  |  |  |  |  |

|----------------------------|-----------|--|--|--|--|--|--|--|--|

| デバイス EEPROM容量 アトレス範囲       |           |  |  |  |  |  |  |  |  |

| 256バイト                     | \$00~\$FF |  |  |  |  |  |  |  |  |

|                            | EEPROM容量  |  |  |  |  |  |  |  |  |

### 5.3.1. プログラミング方法

EEPROMプログラミングには以下のように2つの方法があります。

- 非分離バイト プログラミング。これは単一操作で目標位置が消去されて書かれる単純なプログラミング動作形態です。この動作形態では常に目標が書き込み前に消去されることを保証されますが、プログラミング時間がより長くなります。

- 分離バ・トプログラミング。2つの違う操作で消去と書き込みを分けることが可能です。これは短いアクセス時間が必要とされる、例えば供給電圧が降下する時に有用です。この方法を利用するために、目標位置はそれらへ書く前に消去されなければなりません。これはシステムが時間に重要な操作を許す、代表的に始動と初期化時に時々行うことができます。

プログラミング方法はEEPROM制御レシ、スタ(EECR)のEEPROMプログラミング種別(EEPM1,0)ビットを用いて選択されます。表5.をご覧ください。書き込みと消去の時間はこの同じ表で与えられます。

EEPROMプログラミングは幾許かの時間がかかるため、応用は次を開始する前に1つの操作の完了を待たなければなりません。これは EEPROM制御レジスタ(EECR)のEPROMプログラム許可(EEPE)ビットのポーリング、またはEEPROM操作可割り込み経由のどちらによって行うことができます。 EEPROM割り込みはEECRのEEPROM操作可割り込み許可(EERIE)ビットによって制御されます。

### 5.3.2. 読み込み

EEPROM位置を読むには下の手続きに従ってください。

- 他のEEPROM操作が進行中でないことを確実にするためにEEPROM制御レジスタ(EECR)のEEPROMプログラム許可(EEPE)ビットをポーリングしてください。

- EEPROMアドレス レジスタ(EEARL)に目的アドレスを書いてください。

- EEPROM制御レシ、スタ(EECR)のEEPRO読み込み許可(EERE)じットを設定(1)することによって読み込み操作を開始してください。読み込み操作中、CPUは次の命令を実行する前に4クロック周期間停止されます。

- EEPROMデータレシ、スタ(EEDR)からデータを読んでください。

#### 5.3.3. 消去

予期せぬEEPROM書き込みを防ぐため、メモリ位置を消去するのに特別な手続きに従わなければなりません。EEPROM位置を消去するには下の手続きに従ってください。

- 他のEEPROM操作が進行中でないことを確実にするためにEEPROM制御レジスタ(EECR)のEEPROMプログラム許可(EEPE)ビットをポーリングしてください。 設定(1)の場合、解除(0)を待ってください。

- 自己プログラミング操作が進行中でないことを保証するためにSPM制御/状態レジスタ(SPMCSR)のSPM操作許可(SPMEN)ビットをポーリ ングしてください。設定(1)の場合、解除(0)を待ってください。この段階は応用がフラッシュ メモリをプログラミングするブート ローダを含む場 合にだけ関連します、そうでなければ、この段階を省略することができます。

- EEPROM制御レジスタ(EECR)のEEPROMプログラミング種別(EEPM1,0)ビットを書くことによって消去のためのプログラミング・形態を設定してください。

- EEPROMアドレスレシ、スタ(EEARL)に目的アドレスを書いてください。

- EEPROM制御レジ、スタ(EECR)のEEPROM主プログラム許可(EEMPE)を設定(1)することによって消去を許可してください。4クロック周期内に、EEPROM制御レジ、スタ(EECR)のEEPROMプログラム許可(EEPE)に、小を設定(1)することによって消去操作を開始してください。消去操作中、CPUは次の命令を実行する前に2クロック周期間停止されます。

EEPEビットは消去操作が完了されるまで設定(1)に留まります。デバイスがプログラミングで多忙の間、他のどのEEPROM操作を実行することも不可能です。

### 5.3.4. 書き込み

予期せぬEEPROM書き込みを防ぐため、メモリ位置を書くのに特別な手続きに従わなければなりません。

EEPROMにデータを書く前に目的位置は消去されなければなりません。このは同じ操作で、または分離操作の一部としてのどちらかで行うことができます。未消去EEPROM位置への書き込みは不正なデータに終わるでしょう。

EEPROM位置を書くには下の手続きに従ってください。

- 他のEEPROM操作が進行中でないことを確実にするためにEEPROM制御レジスタ(EECR)のEEPROMプログラム許可(EEPE)ビットをポーリングしてください。 設定(1)の場合、解除(0)を待ってください。

- 自己プログラミング操作が進行中でないことを保証するためにSPM制御/状態レジスタ(SPMCSR)のSPM操作許可(SPMEN)ビットをポーリングしてください。設定(1)の場合、解除(0)を待ってください。この段階は応用がフラッシュ メモリをプログラミング するフート ローダを含む場合にだけ関連します、そうでなければ、この段階を省略することができます。

- EEPROM制御レジスタ(EECR)のEEPROMプログラミング種別(EEPM1,0)ビットを書くことによって書き込みのためのプログラミング形態を設定してください。二者選択で、データは1操作で書くことができるか、または書き込み手続きを消去のみと書き込みのみに分割することができます。

- EEPROMアトレスレシ、スタ(EEARL)に目的アトレスを書いてください。

- EEPROMデータレジスタ(EEDR)に目的データを書いてください。

- EEPROM制御レシ、スタ(EECR)のEEPROM主プログラム許可(EEMPE)を設定(1)することによって書き込みを許可してください。4クロック 周期内に、EEPROM制御レシ、スタ(EECR)のEEPROMプログラム許可(EEPE)ピットを設定(1)することによって書き込み操作を開始してください。書き込み操作中、CPUは次の命令を実行する前に2クロック周期間停止されます。

EEPEビットは書き込み操作が完了されるまで設定(1)に留まります。デバイスがプログラミングで多忙の間、他のどのEEPROM操作も行うことが不可能です。

#### 5.3.5. EEPROM化けの防止

低VCCの間中、正しく動作するための供給電圧がCPUとEEPROMに対して低すぎるためにEEPROMデータが化け得ます。これらの問題はEEPROMを使う基板段階の装置と同じで、同じ設計上の解決策が適用されるべきです。

低供給電圧でEEPROM内のデータは以下の2つの点で不正にされ得ます。

- その他正当なEEPROMプログラミング手順の正しい動作を維持するのに供給電圧が低すぎます。

- CPUに対して供給電圧が低すぎて、命令が不正に実行されるかもしれません。

EEPROMデータ化けは不充分な供給電源電圧の期間中、デバイスをリセットに保つことによって避けられます。これは内部低電圧検出器 (BOD)を許可することによって容易に行えます。BOD検出電圧が設計に対して不充分な場合、外部低VCCリセット回路を使うことができます。

供給電圧が充分なら、例えリセットが起きても、EEPROM書き込み操作は完了されます。

#### 5.3.6. プログラム例

次のコート・例はアセンブリ言語とC言語でのEEPROM消去、書き込み、または非分離書き込み関数を示します。本例は(例えば全割り込み禁止によって)割り込みが制御され、これらの関数実行中に割り込みが起きない前提です。

本例はソフトウェア内にフラッシュブートローダが無い前提でもあります。そのようなコードが存在する場合、EEPROM書き込み関数は何れかが実行するSPM命令の完了も待たねばなりません。

```

アセンブリ言語プログラム例

EEPROM_WR:

SBIC

EECR, EEPE

;EEPROMプログラミング完了ならばスキップ

RJMP

EEPROM_WR

;以前のEEPROMプログラミング。完了まで待機

;プログラミング種別値取得(本例は非分離)

R19, (0<<EEPM1) | (0<<EEPM0)

LDI

OUT

EECR, R19

;対応プログラミング種別設定

OUT

EEARH, R18

;EEPROMアドレス上位設定(訳注:無効)

OUT

EEARL, R17

;EEPROMアトレス下位設定

OUT

EEDR, R16

;EEPROM書き込み値を設定

EECR, EEMPE

;EEPROM主プログラム許可ビット設定

SBI

SBI

EECR, EEPE

;EEPROMプログラミング開始(プログラム許可ビット設定)

RET

;呼び出し元へ復帰

C言語プログラム例

void EEPROM_write(unsigned int ucAddress, unsigned char ucData)

/* 以前のEEPROMプログラミング完了まで待機 */

while (EECR & (1<<EPE));

EECR = (0 << EEPM1) | (0 << EEPM0);

/* 対応プログラミング種別設定 */

EEAR = ucAddress;

/* EEPROMアドレス設定*/

EEDR = ucData;

/* EEPROM書き込み値を設定 */

EECR = (1 << EEMPE);

/* EEPROM主プログラム許可*/

EECR = (1 << EEPE);

/* EEPROMプログラミング開始*/

```

### **注**: 5頁の「**コート** 例」をご覧ください。

次のコート・例はアセンブリ言語とC言語でのEEPROM読み込み関数を示します。本例は割り込みが制御され、これらの関数実行中に割り込みが起きない前提です。

```

アセンブリ言語プログラム例

;EEPROMプログラミング、完了ならばスキップ

EEPROM RD:

SBIC

EECR, EEPE

;以前のEEPROMプログラミング完了まで待機

R.TMP

EEPROM RD

;EEPROMアドレス上位設定(訳注:無効)

OUT

EEARH, R18

OUT

EEARL, R17

;EEPROMアドレス下位設定

SBI

EECR, EERE

;EEPROM読み出し開始(読み込み許可ビット設定)

ΙN

R16, EEDR

;EEPROM読み出し値を取得

RET

;呼び出し元へ復帰

C言語プログラム例

unsigned char EEPROM_read(unsigned int ucAddress)

while (EECR & (1<<EPE));

/* 以前のEEPROMプログラミング完了まで待機 */

EEAR = ucAddress;

/* EEPROMアドレス設定 */

EECR \mid = (1 << EERE);

/* EEPROM読み出し開始 */

/* EEPROM読み出し値を取得,復帰 */

return EEDR;

注: 5頁の「コート・例」をご覧ください。

```

### 5.4. メモリ関係レジスタ

### 5.4.1. **EEARL - EEPROM7**トレス レジスタ (EEPROM Address Register)

| ピット         | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _     |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$21 (\$41) | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEARL |

| Read/Write  | R/W   |       |

| 初期値         | 不定    |       |

#### ● ビット7~0 - EEAR7~0: EEPROMアドレス (EEPROM Address)

EEPROMアドレスレジスタはアクセスされつつあるメモリ位置を示すのに読み/書き操作で必要とされます。

EEPROMデータ バイトはメモリ範囲全体(0~(256-1))に渡って直線的にアドレス指定されます。これらのビットの初期値は未定義で従ってEEPROMがアクセスされる前に正当な値がこのレジスタに書かれなければなりません。

256小一个またはそれ以下のEEPROMを持つデバイスは上位アドレスレジスタ(EEARH)が不要です。従ってこのようなデバイスで上位アドレスレジスタが省かれますが、互換性の問題のため、残りのレジスタは未だEEPROMアドレスレジスタの下位バイト(EEARL)として参照されます。

アトンス ハイト全体を満たさないデバイス、換言すると256に等しくないEEPROMの大きさを持つデバイスは未使用位置に読み込み専用ビットを実装します。未使用ビットはアトンス レジスタの上位側に置かれ、それらは常に0を読みます。

### 5.4.2. EEDR - EEPROMデータレジスタ (EEPROM Data Register)

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     | _    |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|------|

| \$20 (\$40) | (MSB) |     |     |     |     |     |     | (LSB) | EEDR |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |      |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |      |

#### ● ビット7~0 - EEDR7~0 : EEPROMデータ (EEPROM Data)

EEPROM書き込み操作に対してEEDRはEEPROMアドレス レジスタ(EEAR)で与えられたEEPROMアドレスへ書かれるべきデータを含みます。EEPROM読み込み操作に対してEEDRはEEARによって与えられたEEPROMアドレスから読み出したデータを含みます。

### 5.4.3. EECR - EEPROM制御レジスタ (EEPROM Control Register)

| ピット         | 7 | 6 | 5     | 4     | 3     | 2     | 1    | 0    | _    |

|-------------|---|---|-------|-------|-------|-------|------|------|------|

| \$1F (\$3F) | - | - | EEPM1 | EEPM0 | EERIE | EEMPE | EEPE | EERE | EECR |

| Read/Write  | R | R | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  |      |

| 初期値         | 0 | 0 | 不定    | 不定    | 0     | 0     | 不定   | 0    |      |

## ビット7,6 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0を読みます。

### ● ビット5,4 - EEPM1,0: EEPROMプログラミング種別 (EEPROM Programing Mode Bits)

EEPROMプログラミング種別ビットはEEPROMプログラム許可(EEPE)が書かれる時に起動される活動を定義します。データは新しいデータが書かれる前に前の値が自動的に消去される単一非分離操作で書くことでき、または消去と書き込みが2つの異なる操作に分けること

ができます。各種動作形態に対するプログラミング 時間が表5.で示されます。

EEPE設定(1)時、EEPMnへのどの書き込みも無視されます。

リセット中、EEPMnビットはEEPROMがプログラミング多忙を除いて'00'にリセットされます。

| 衣 5. 上上 | ROMA  | コン フミンツ | 悝別          |

|---------|-------|---------|-------------|

| EEDM4   | EEDM0 | つ°ロカ゛ニ: | <b>、 か </b> |

| EEPM1 | EEPM0 | ブログラミング時間 | 動作 動作               |

|-------|-------|-----------|---------------------|

| 0     | 0     | 3.4ms     | 1操作での非分離操作(消去と書き込み) |

| 0     | 1     | 1.8ms     | 消去のみ                |

| 1     | 0     | 1.8ms     | 書き込みのみ              |

| 1     | 1     | -         | (予約)                |

### ● ビット3 - EERIE: EEPROM操作可割り込み許可(EEPROM Ready Interrupt Enable)

このビットの1書き込みはステーータス レジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されているならば、EEPROM操作可割り込みを許可し、不揮発性メモリがプログラミング準備可の時にEEPROM操作可割り込みが起動されます。

このビットの0書き込みはEEPROM操作可割り込みを禁止します。

## • ビット2 - EEMPE: EEPROM主プログラム許可(EEPROM Master Program Enable)

EEMPEL'ットはEEPROMプログラム許可(EEPE)ヒットの1書き込みが有効か否かのどちらかを決めます。

EEMPEが設定(1)されて4クロック周期内にEEPE書かれる(1)と、選択したアドレスでEEPROMがプログラミングされます。4クロック周期後にハードウェアがEEMPEビットを0に解除します。

EEMPEが0なら、EEPEビットは無効です。

#### ● ビット1 - EEPE: EEPROMプログラム許可 (EEPROM Program Enable)

これはEEPROMのプログラミング許可信号です。EEPEが(1を)書かれる前にEEPROM主プログラム許可(EEMPE)ビットが設定(1)されなければならず、さもなければEEPROMはプログラミングされません。

EEPEが(1を)書かれると、EEPROMはEEPMnビット設定に従ってプログラミングされます。EEPEが設定(1)されてしまうと、CPUは次の命令が実行される前に2周期間停止されます。書き込み(プログラミング)アクセス時間経過後、EEPEビットはハードウェアによって解除(0)されます。 EEPROM書き込み操作がフラッシュ、ヒューズ ビット、施錠ビットの全てのソフトウェア プログラミングを妨げることに注意してください。

#### ● ビット0 - EERE: EEPROM読み込み許可 (EEPROM Read Enable)

これはEEPROMの読み込みストローブです。目的アトレスがEEPROMアトレスレン、スタ(EEAR)で構成設定されてしまうと、EEPROM読み込み操作を起動するためにEEREビットが1を書かれなければなりません。

EEPROM読み出しアクセスは(その)1命令かかり、要求したデータは直ちに利用可能です。EEPROMが読まれる時にCPUは次の命令が実行される前に4周期間停止されます。

使用者は読み込み操作を開始する前にEEPEビットをポーリングすべきです。書き込み(プログラミング)操作が進行中の場合、EEPROMを読むことやアドレス レジスタ(EEAR)を変更することは不可能です。

### 5.4.4. GPIOR2 - 汎用I/Oレジスタ2 (General Purpose I/O Register 2)

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |        |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$2B (\$4B) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR2 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

### 5.4.5. GPIOR1 - 汎用I/Oレジスタ1 (General Purpose I/O Register 1)

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     | _      |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$2A (\$4A) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR1 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

### 5.4.6. GPIORO - 汎用I/OレジスタO (General Purpose I/O Register 0)

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |        |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$1E (\$3E) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR0 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

## 6. クロック体系

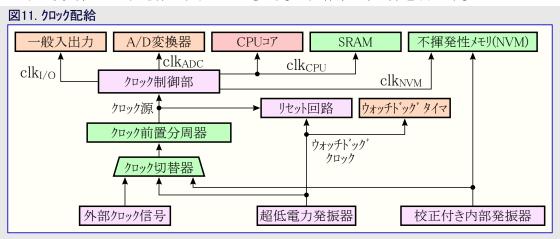

図11.はATtiny828での主要なクロック系統とそれらの配給を示します。全てのクロックが与えられた時間有効である必要はありません。消費電力低減のため、23頁の「電力管理と休止形態動作」で記述されるように、各種休止動作形態と電力削減レジスタ ビットを使うことによって、使われていない単位部へのクロックを停止することができます。クロック体系は下で詳述されます。

### 6.1. クロック副系統

クロック副系統が以下の項で詳述されます。

### 6.1.1. CPU クロック - clk<sub>CPU</sub>

CPUクロックはAVRコアの動作と関係する系統部分に配給されます。このような部分の例は汎用レジスタファイル、システムレジスタ、SRAMデータメモリです。CPUクロックの停止はコアが一般的な操作や計算を実行することを禁止します。

#### 6.1.2. I/O クロック - clk<sub>I/O</sub>

I/Oクロックはタイマ/カウンタのようなI/O部の大部分で使われます。I/Oクロックは外部割り込み部でも使われますが、いくつかの外部割り込みは例えI/Oクロックが停止されても検出されるのをこのような割り込みに許す非同期論理回路によって検出されることに注意してください。

### **6.1.3. NVMクロック** – clk<sub>NVM</sub>

NVMクロックは不揮発性メモリ制御部の動作を制御します。NVMクロックは常にCPUクロックと同時に活動します。

#### 6.1.4. A/D変換クロック - clk<sub>ADC</sub>

A/D変換器には専用のクロック範囲が提供されます。これはデジタル回路によって生成される雑音を低減するためにCPUとI/Oクロックの停止を許します。これはより正確なA/D変換結果を与えます。

#### 6.2. クロック元

このデバイスはシステムクロック用に以下のどれも使うことができます。

- 外部クロック信号(19頁をご覧ください。)

- 校正付き内部8MHz発振器 (19頁をご覧ください。)

- 内部32kHz超低電力(ULP)発振器 (19頁をご覧ください。)

クロック元は下の表6.で示されるようにCKSELヒューズを使って選ばれます。

| 表6. CKSELtュース | ゙゙゙゙゙゙゙゙゙゙゙゙゙゙゚゚゚゙゙゙゙゙゙゙゙゙゚゚゚゙゚゙゙゙゙゙゚゚゚゙゚゚゙゚゚゙゙゙゙ | 「イス クロック駆動任意選択                            |

|---------------|---------------------------------------------------|-------------------------------------------|

| CKSEL1,0 (注1) | 周波数                                               | デバイス クロック駆動任意選択                           |

| 0 x           | どれも                                               | 外部クロック信号(19頁をご覧ください。)                     |

| 1 0           | 8MHz                                              | 校正付き内部8MHz発振器 (19頁をご覧ください。) ( <b>注2</b> ) |

| 1 1           | 32kHz                                             | 内部32kHz超低電力(ULP)発振器 (19頁をご覧ください。)         |

**注1**: 全てのヒュース に対して"1"は非プログラム、"0"はプログラムを意味します。

注2: これが既定設定です。デバイスはこのヒューズの組み合わせで出荷されます。

CKSELヒュース<sup>\*</sup> ビットはファームウェアによって読むことができますが(153頁の「**ソフトウェアからの施錠、ヒューズ、識票データの読み出し**」をご覧ください)、ファームウェアはヒュース<sup>\*</sup> ビットを書くことができません。

デバイスがパワーダウンから起き上がる時に、命令実行開始前の安定な発振器動作を保証するために、始動時間に選択したクロック元が使われます。CPUがリセットから始まる時に、通常のデバイス動作が開始される前に安定な水準に達することを供給電圧に許す、付加遅延を生成するのに内部32kHz発振器が使われます。

システムクロック代替は以降の項で検討されます。

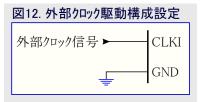

#### 6.2.1. 外部クロック信号

外部クロック元からデバイスを駆動するには、下の図12.で示されるようにCLKIが接続されるべきです。

このクロック元に対する始動時間は20頁の表7.で示されるように、SUTヒューズビットによって決められます。

外部クロック周波数での急な変化を避けるためにMCUの安定動作を保証することが必要とされます。或るクロック周期から次への2%よりも大きな周波数での変化は予測されない動きを引き起こし得ます。クロック周波数でのこのような変化中、MCUはリセットに保たれるのを保証することが必要とされます。

システム クロックでの大きな段階の変更に対する安定な操作はシステム クロック前置分周器を使う時に保証されます。「システム クロック前置分周器」をご覧ください。

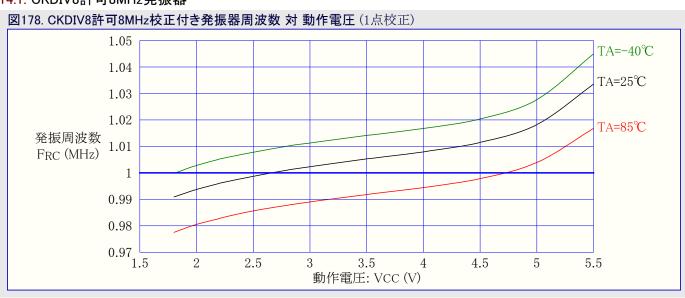

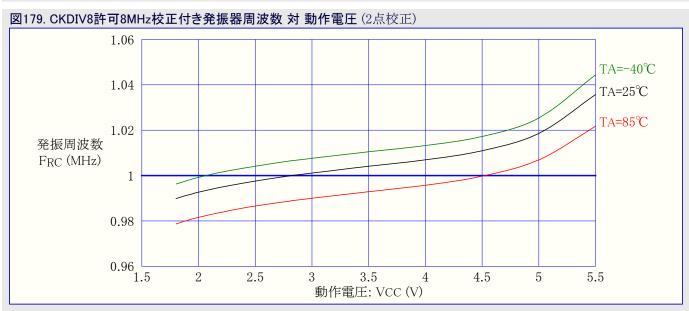

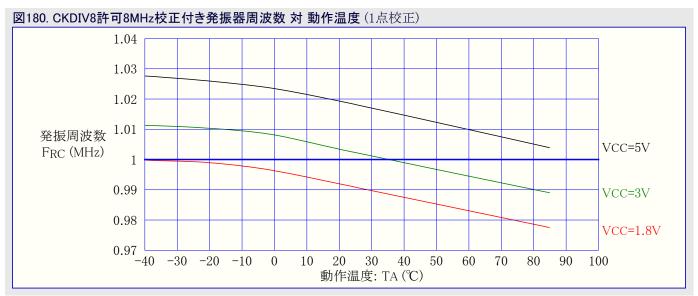

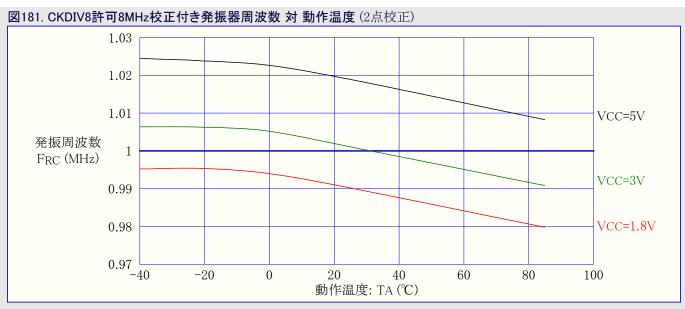

### 6.2.2. 校正付き内部8MHz発振器

内部8MHz発振器は外部部品なしで動作し、既定によって概ね8MHzの周波数を持つクロック元を提供します。電圧と温度に依存しますが、このクロックは使用者によって非常に正確に校正することができます。より多くの詳細については167頁の表104.と197頁の「内部発振器周波数」をご覧ください。

リセット中、ハート・ウェアが発振器校正の(OSCCAL0)レシ、スタ内に予めプログラムされた校正値を設定し、これによって発振器を自動的に校正します。この校正の精度は**表104**.で"工場校正"として参照されます。予めプログラムされた校正値の自動設定のより多くの情報については153頁の「校正パイト」項をご覧ください。

特に応用が狭い範囲の温度と電圧を許す時に、工場既定よりも高い精度に達することが可能です。ファームウェアは始動時や走行中の どちらでもOSCCAL0に校正データを再設定することができます。継続的な走行時校正法は電圧と温度の監視と検出したどの変化の 補償もファームウェアに許します。「OSCCALO - 発振器校正Oレジスタ」、138頁の「温度測定」、139頁の表76.をご覧ください。この校正の精 度は表104.で"使用者校正"として参照されます。

発振器温度校正レジスタ(OSCTCAL0AとOSCTCAL0B)は発振器周波数の一時的な温度校正に使うことができます。「OSCTCAL0A - 発振器温度校正レジスタA」と「OSCTCAL0B - 発振器温度校正レジスタB」をご覧ください。

このクロック元に対する始動時間は20頁の表7.で示されるように、SUTヒューズビットによって決められます。

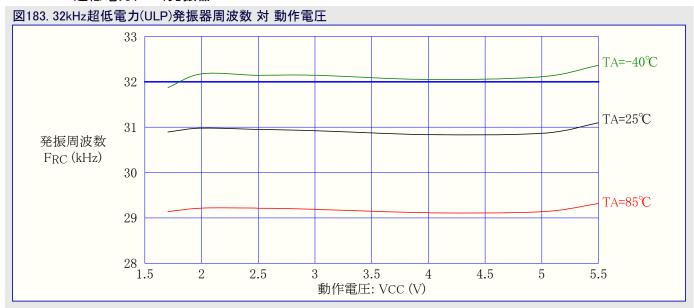

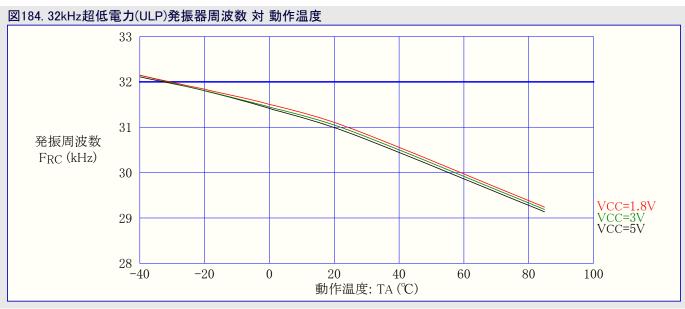

### 6.2.3. 内部32kHz超低電力(ULP)発振器

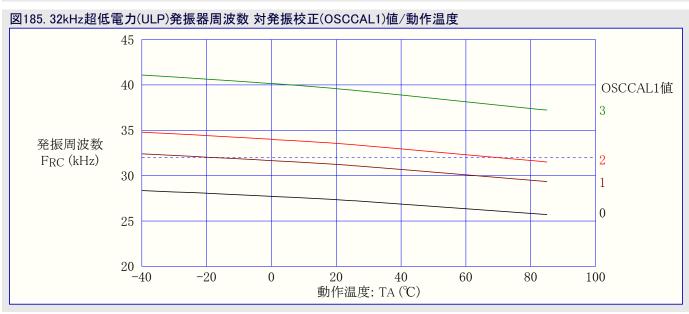

内部32kHz発振器は外部部品なしで動作する低電力発振器です。概ね32kHzの周波数を持つクロック元を提供します。周波数は供給電圧、温度と一群の変化に依存します。精度の詳細については167頁の表105.をご覧ください。

リセット中、ハート・ウェアが発振器校正1(OSCCAL1)レジスタ内に予めプログラムされた校正値を設定し、これによって発振器を自動的に校正します。この校正の精度は表105.で"工場校正"として参照されます。予めプログラムされた校正値の自動設定のより多くの情報については153頁の「校正バイト」項をご覧ください。

この発振器がチップ゚クロックとして使われる時に、未だウォッチドッグタイマとリセット時間超過に使われます。

このクロック元に対する始動時間は20頁の表7.で示されるように、SUTヒューズビットによって決められます。

#### 6.2.4. 既定クロック設定

このデバイスは以下のヒューズ設定で出荷されます。

- 校正付き内部8MHz発振器 (18頁の表6.でCKSELとュース」ビットをご覧ください。)

- 可能な最長始動時間(20頁の表7.でSUTヒューズ ビットをご覧ください。)

- システム クロック前置分周器を8に設定 (21頁のCKDIV8ヒュース ビットをご覧ください。)

既定設定は1MHzシステム クロックを与え、全ての使用者が実装または高電圧の書き込み器を使ってそれらを望むクロック元設定にすることができるのを保証します。

# 6.3. システム クロック前置分周器

ATtiny828のシステム クロックは「CLKPR - クロック前置分周レジスタ」の設定によって分周できます。この特徴(機能)は必要とされる処理能力が低い時の消費電力削減に使えます。これは全クロック種別で使え、CPUと全同期周辺機能のクロック周波数に影響を及ぼします。 clk<sub>CPU</sub>、clk<sub>NVM</sub>、clk<sub>I/O</sub>、clk<sub>ADC</sub>は21頁の表8.で示された値によって分周されます。

### 6.3.1. 切り替え時間

前置分周器設定間を切り替えるとき、システム クロック前置分周器は中間(経過途中)の周波数が直前の設定に対応するクロック周波数または新規設定に対応するクロック周波数のどちらよりも高くなく、クロック系で不具合が起きないことを保証します。

前置分周器として実行するリプルカウンタは分周されないクロック周波数で走行し、CPUのクロック周波数より速いかもしれません。従って例え(カウンタ値が)読めるとしても、前置分周器の状態を決めることはできず、1から他へのクロック分周値切り替えを行う正確な時間は必ずしも予測できません。

CLKPS値が書かれる時から新規クロック周波数が活性(有効)になる前にT1+T2~T1+2×T2間かかります。この間で2つの有効なクロック端が生成されます。ここでのT1は直前のクロック周期、T2は新規前置分周器設定に対応する周期です。

### 6.4. クロック出力緩衝部(外部クロック出力)

本デバイスはシステム クロックをCLKOピンに出力することができます。この出力を許可するには、CKOUTヒューズがプログラム(0)されなければなりません。

この動作はチップのクロックがシステム上の他の回路を駆動する時に適します。このヒュース、がプログラム(0)された時にI/Oピンの標準動作が無視され、このクロックがリセット間に出力されないことに注意してください。クロックがCLKOに出力される時は校正付き内部発振器を含むどのクロック元も選択できます。システム クロック前置分周器が使われると、出力されるのは分周されたシステム クロックです。

### 6.5. 始動時間

CKSELとSUTのヒュース、ビットは下の表7.で示されるように、デバイスの始動時間を定義します。

表7. CKSELとSUTのヒュース、ビット対デバイス始動時間

| CKSEL   | SUT               | クロック元      | パワーダウンから ( <u>注1,2</u> ) | リセットから (注3)               |

|---------|-------------------|------------|--------------------------|---------------------------|

|         | 0 0               |            |                          | 20×CK                     |

| 0 x     | 0 1               | 外部クロック信号   | 6×CK                     | $20 \times \text{CK+4ms}$ |

|         | 1 x               |            |                          | 20×CK+64ms                |

|         | 0 0               |            |                          | 20×CK ( <b>注5</b> )       |

| 10 (注4) | 0 1               | 内部8MHz発振器  |                          | $20 \times \text{CK+4ms}$ |

|         | 1 x ( <b>注4</b> ) |            | 6×CK ( <b>注5</b> )       | 20×CK+64ms                |

|         | 0 0               |            | 0 × CK (,±3)             | 20×CK ( <b>注5</b> )       |

| 1 1     | 0 1               | 内部32kHz発振器 |                          | 20×CK+4ms                 |

|         | 1 x               |            |                          | 20×CK+64ms                |

注1: パワーダウン休止動作形態からのデバイス始動時間。

**注2**: 低電圧検出器(BOD)がソフトウェアによって禁止されていると、MCUがコート・実行を続ける前にBODが正しく動作するのを保証するために、休止形態からの起き上がり時間は概ね60μsになります。

注3: リセット後のデバイス始動時間。

注4: デバイスはこの任意選択が選択されて出荷されます。

注5: リセットが禁止されている時に最小4ms。

### 6.6. クロック関係レジスタ

### 6.6.1. CLKPR - クロック前置分周レジスタ (Clock Prescale Register)

| ピット        | 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      |       |

|------------|---|---|---|---|--------|--------|--------|--------|-------|

| (\$61)     | _ | - | - | - | CLKPS3 | CLKPS2 | CLKPS1 | CLKPS0 | CLKPR |

| Read/Write | R | R | R | R | R/W    | R/W    | R/W    | R/W    |       |

| 初期値        | 0 | 0 | 0 | 0 | 内容参照   | 内容参照   | 内容参照   | 内容参照   |       |

#### ビット7~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0を読みます。

#### ● ビット3~0 - CLKPS3~0: クロック分周値選択 (Clock Prescaler Select Bits 3~0)

これらのビットは選択したクロック元と内部システム クロック間の分周係数を定義します。これらのビットは応用の必要条件に合わせてクロック周波数を変えるために走行時に書くことができます。前置分周器はMCUへの主クロック入力を分周するため、これによって全ての同期周辺機能の速度が減じられます。分周係数は表8.で与えられます。

前置分周器設定変更時、書き込み手続きが割り込まれないことを保証するため、割り込みは禁止されなければなりません。

| 表8. クロック前置分周 | 器選択                | 5       |   |                    |    |    |    |     |     |      |   |   |     |   |   |   |

|--------------|--------------------|---------|---|--------------------|----|----|----|-----|-----|------|---|---|-----|---|---|---|

| CLKPS3       |                    | 0 1     |   |                    |    |    |    |     |     |      |   |   |     |   |   |   |

| CLKPS2       |                    | 0 1 0 1 |   |                    |    |    |    |     |     |      |   |   |     |   |   |   |

| CLKPS1       | (                  | )       |   | 1                  | (  | )  |    | L   | (   | 0 1  |   |   | 0 1 |   |   | 1 |

| CLKPS0       | 0                  | 1       | 0 | 1                  | 0  | 1  | 0  | 1   | 0   | 1    | 0 | 1 | 0   | 1 | 0 | 1 |

| 分周値(数)       | 1<br>( <b>注1</b> ) | 2       | 4 | 8<br>( <b>注2</b> ) | 16 | 32 | 64 | 128 | 256 | (予約) |   |   |     |   |   |   |

注1: これはCKDIV8ヒュースが非プログラム(1)にされた時の初期値です。

注2: これはCKDIV8ヒュース、がプログラム(0)された時の初期値です。テブバイスはCKDIV8ヒュース、がプログラム(0)されて出荷されます。

クロック前置分周ビットの初期値はCKDIV8ヒュース。によって決められます(152頁の**表91**.をご覧ください)。 CKDIV8が非プログラム(1)にされる時にシステム クロック前置分周器は1に、プログラム(0)される時に8に設定されます。 どの値もCKDIV8ヒュース゛ビット設定に拘らずCLKPSビットに書くことができます。

CKDIV8がプログラム(0)される時にCLKPSビットの値は始動での8分周クロック係数を与えます。これは選択したクロック元が現在の動作条件下で許されるよりも高い周波数を持つ時に有用です。167頁の「速度」をご覧ください。

予期せぬクロック周波数の変更を防ぐため、CLKPSビットの変更するには保護された変更手順に従わなければなりません。

- 1. 保護されたI/Oレシ、スタの変更許可用の識票を構成設定変更保護(CCP)レシ、スタに書いてください。

- 2.4命令周期内に望む値でCLKPSビットを書いてください。

### 6.6.2. OSCCALO - 発振器校正レジスタ (Oscillator Calibration Register)

| ビット               | 7     | 6     | 5     | 4             | 3            | 2     | 1     | 0     | OSCCALO |

|-------------------|-------|-------|-------|---------------|--------------|-------|-------|-------|---------|

| (\$66)            | CAL07 | CAL06 | CAL05 | CAL04         | CAL03        | CAL02 | CAL01 | CAL00 |         |

| Read/Write<br>初期値 | R/W   | R/W   | R/W   | R/W<br>デバイス固有 | R/W<br>有の校正値 | R/W   | R/W   | R/W   |         |

### ● ビット7~0 - CAL07~0:発振器校正値 (Oscillator Calibration Value)

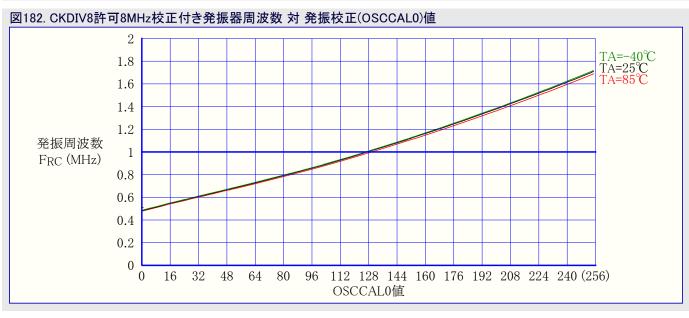

発振器校正レジスタは内部8MHz発振器の調整と発振器周波数からの変化除去処理に使われます。チップのリセット中に167頁の表104. で指定される工場校正された周波数を与える予めプログラムされた校正値が自動的にこのレジスタに書かれます。

応用ソフトウェアは発振器周波数を変更するために、このレジスタを書くことができます。この発振器は**表104**.で指定される周波数に校正することができます。この範囲外への校正は保証されません。

最低発振器周波数はこれらのビットを0に設定することによって達成されます。レジスタ値の増加は発振器周波数を増加します。代表的な周波数応答曲線が198頁の図182.で示されます。

この発振器がEEPROMとフラッシュ メモリの書き込みアクセスに使われ、それによって書き込み時間が影響を及ぼされますことに注意してください。EEPROMやフラッシュ メモリが書かれる場合、8.8MHz以上に校正しないでださい。さもなければ、EEPROMやフラッシュ メモリの書き込みが失敗するかもしれません。

MCUの安定な動作を保証するため、校正値は小さな間隔で変更されるべきです。或る周回から次へ2%以上の周波数での段階変更は予測不能な動きを引き起こし得ます。また、連続する2つのレジスタ値の差は\$20を超えるべきではありません。これらの限度を超える場合、MCUはクロック周波数変更の間にリセットを保たれなければなりません。

### 6.6.3. OSCTCALOA - 発振器温度校正レジスタA (Oscillator Temperature Calibration Register A)

| ピット        | 7   | 6   | 5   | 4      | 3      | 2   | 1   | 0   |           |

|------------|-----|-----|-----|--------|--------|-----|-----|-----|-----------|

| (\$F0)     |     |     |     | 発振器温度  | を校正データ |     |     |     | OSCTCAL0A |

| Read/Write | R/W | R/W | R/W | R/W    | R/W    | R/W | R/W | R/W |           |

| 初期値        |     |     |     | デバイス固有 | すの校正値  |     |     |     |           |

#### ● ビット7~0 - 発振器温度校正値 (Oscillator Temperature Calibration Value)

温度校正値は校正付き8MHz発振器を調節して発振器周波数から温度変動を取り去るのに使うことができます。

### 6.6.4. OSCTCALOB - 発振器温度校正レジスタB (Oscillator Temperature Calibration Register B)

| ピット        | 7   | 6   | 5   | 4      | 3      | 2   | 1   | 0   |           |

|------------|-----|-----|-----|--------|--------|-----|-----|-----|-----------|

| (\$F1)     |     |     |     | 発振器温度  | 度校正データ | ,   |     |     | OSCTCAL0B |

| Read/Write | R/W | R/W | R/W | R/W    | R/W    | R/W | R/W | R/W |           |

| 初期値        |     |     |     | デバイス固ィ | 有の校正値  |     |     |     |           |

#### ● ビット7~0 - 発振器温度校正値 (Oscillator Temperature Calibration Value)

温度校正値は校正付き8MHz発振器を調節して発振器周波数から温度変動を取り去るのに使うことができます。

### 6.6.5. OSCCAL1 - 発振器校正レジスタ (Oscillator Calibration Register)

| ピット        | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0     |         |

|------------|---|---|---|---|---|---|--------|-------|---------|

| (\$67)     | - | - | - | - | - | - | CAL11  | CAL10 | OSCCAL1 |

| Read/Write | R | R | R | R | R | R | R/W    | R/W   |         |

| 初期値        | 0 | 0 | 0 | 0 | 0 | 0 | デバイス固る | 有の校正値 |         |

#### ビット7~2 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0を読みます。

#### ● ビット1,0 - CAL11~0:発振器校正値 (Oscillator Calibration Value)

この発振器校正レジスタは内部32kHz発振器の調整と発振器周波数からの変化除去処理に使われます。チップのリセット中に167頁の表 105.で指定される工場校正された周波数を与える予めプログラムされた校正値が自動的にこのレジスタに書かれます。

応用ソフトウェアは発振器周波数を変更するために、このレシブスタを書くことができます。この発振器は**表105**で指定される周波数に校正することができます。この範囲外への校正は保証されません。

最低発振器周波数はこれらのビットを0に設定することによって達成されます。レジスタ値の増加は発振器周波数を増加します。代表的な周波数応答曲線が199頁の図185.で示されます。

MCUの安定な動作を保証するため、校正値は小さな間隔で変更されるべきです。或る周回から次へ2%以上の周波数での段階変更は予測不能な動きを引き起こし得ます。また、連続する2つのレジスタ値の差は\$20を超えるべきではありません。これらの限度を超える場合、MCUはクロック周波数変更の間にリセットを保たれなければなりません。(訳注:原書での本節(前4行)は単純複写のために不適切な記述になっており、基本的に削除されるべきです。)

## 7. 電力管理と休止形態動作

高機能と産業的に先行するコード効率は低電力の応用に対してAVRマイクロ コントローラを理想的に選択させます。加えて休止形態動作は応用でMCU内の未使用部を一時停止することを可能にし、それによって節電します。AVRは応用で必要な消費電力に仕立てることを使用者に許す様々な休止形態動作を提供します。

### 7.1. 休止形態動作種別

18頁の図11.はATtiny828の各種クロック系統とその配給を示します。この図は適切な休止形態動作選択の助けになります。表9.は異なる休止形態動作と起き上がりに使える起動元を示します。

#### 表9. 各休止形態動作に於ける動作クロック範囲と復帰起動要因

| ſ |                                    | 発振器動作                 | Ī          | 動作クロッ      | ク範囲 | ]          |               |              | 復帰起   | 記動要因       | (割り込み)      |                       |            |

|---|------------------------------------|-----------------------|------------|------------|-----|------------|---------------|--------------|-------|------------|-------------|-----------------------|------------|

|   | 休止形態種別                             | 許可された<br>主クロック<br>供給元 | clk<br>CPU | clk<br>NVM | clk | clk<br>ADC | ウォッチ<br>ト゛ック゛ | INTn<br>ピン変化 | USART | 従装置<br>TWI | A/D変換<br>完了 | SPM/<br>EEPROM<br>準備可 | その他<br>I/O |

| I | アイドル                               | 0                     |            |            | 0   | 0          | 0             | 0            | 2     | 0          | 0           | 0                     | 0          |

|   | A/D変換雑音低減                          | 0                     |            |            |     | 0          | 0             | 1            | 2     | 3          | 0           | 0                     |            |

| I | ハ <sup>°</sup> ワータ <sup>*</sup> ウン |                       |            |            |     |            | 0             | 1            | 2     | 3          |             |                       |            |

- ①: INTn(n=0,1)についてはレベル割り込みのみです。

- ②: フレーム開始検出のみです。

- ③: アドレス一致割り込みのみです。

休止形態動作へ移行するには休止形態制御レジスタ(SMCR)の休止許可(SE)ビットが設定(1)され、SLEEP命令が実行されなければなりません。SMCRの休止形態種別選択(SMn)ビットは<math>SLEEP命令によって活性(有効)にされる休止形態のどれかを選びます。一覧については表10.をご覧ください。

MCUが休止形態動作中に許可した割り込みが起こると、MCUは起動します。その時にMCUは起動時間に加えて4周期停止され、割り込みルーチンを実行し、そしてSLEEP命令の次の命令から実行を再開します。デバイスが休止状態から起動するとき、レジスタファイルとSRAMの内容は変えられません。休止形態動作中にリセットが起こると、MCUは起動し、リセット ベクタから実行します。

レベルで起動した割り込みが起動復帰に使われる場合、MCUを起動(とMCUがその割り込み処理ルーチンへ移行)するには、変更したレベルが一定時間保持されなければならないことに注意してください。詳細については35頁の「外部割り込み」を参照してください。

#### 7.1.1. アイドル動作

この休止形態は基本的にclkCPUとclkvNMを停止する一方、他のクロックに走行を許します。アイドル動作ではCPUが停止されますが、以下の周辺機能は動作を続けます。

- ウォッチト、ック、と割り込み機構

- アナログ比較器とA/D変換器

- USART、TWI、タイマ/カウンタ

アイドル動作はMCUにタイマ溢れなどの内部割り込みだけでなく、外部で起動された割り込みからの起き上がりも許します。アナロゲ比較器割り込みからの起き上がりが必要とされないなら、アナロゲ比較器はACSRAのアナロゲ比較器禁止(ACD)ビットを設定(1)することによって電源断にすることができます。130頁の「ACSRA - アナロゲ比較器制御/状態レジスタA」をご覧ください。これはアイドル動作での消費電力を削減します。

A/D変換が許可されているなら、この動作に移行すると自動的に変換が始まります。

### 7.1.2. A/D変換雑音低減動作

この休止形態は基本的に $clk_{I/O}$ ,  $clk_{CPU}$ ,  $clk_{NVM}$ を停止する一方、他のprotonを許します。A/D変換雑音低減動作ではCPUが停止されますが、以下の周辺機能は動作を続けます。

- (許可されていれば)ウォッチト、ック、と外部割り込み

- A/D変換器

- USARTフレーム開始検出部とTWI

これはA/D変換に対する雑音環境を改善し、より高い分解能の測定を許します。A/D変換器が許可されている場合、この動作に移行すると、変換が自動的に始まります。

以下の事象がMCUを起き上がらせ得ます。

- ウォッチドッグ リセット、外部リセット、低電圧検出(BOD)リセット

- INT0とINT1の外部レベル割り込み、ピン変化割り込み

- A/D変換完了割り込み、SPM/EEPROM操作可割り込み

- USARTフレーム開始検出、TWI従装置アトレス一致

#### 7.1.3. パワーダウン動作

この休止形態は生成した全てのクロックを停止し、非同期部の動作だけを許します。パワーダウン動作では発振器が停止される一方で以下の周辺機能は動作を続けます。

• (許可されていれば)ウォッチドック、、外部割り込み

以下の事象がMCUを起き上がらせることができます。

- ウォッチドッグ リセット、外部リセット、低電圧検出(BOD)リセット

- INT0とINT1の外部レベル割り込み、ピン変化割り込み

- USARTフレーム開始検出、TWI従装置アドレス一致

### 7.2. 電力削減レジスタ

電力削減レジスタ(26頁の「PRR - 電力削減レジスタ」参照)は個別周辺機能へのクロックを停止することにより、消費電力を削減方法を提供します。周辺機能へのクロックが停止されると、以下のようになります。

- 周辺機能の現在の状態が固定化されます。

- 関連するレシ、スタは読み書きすることができません。

- 周辺機能によって使われる資源は専有されたままに留まります。

周辺機能は殆どの場合に於いてクロックを停止する前に禁止されるべきです。電力削減レジスタ(PRR)のビットを解除(0)することが周辺機能部を起し、停止前と同じ状態にします。

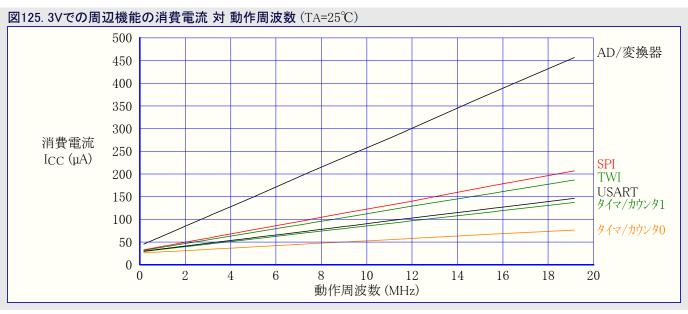

周辺機能停止は全体に亘る重要な消費電力の削減のために活動動作とアイドル動作で使えます。例については179頁の「**周辺機能部消費電流**」をご覧ください。その他の休止形態動作ではクロックが予め停止されます。

### 7.3. 消費電力の最小化

これらはAVRが制御するシステムで消費電力の最小化を試みる時に考慮するためのそれぞれの検討点です。一般的に休止形態動作は可能な限り多く使われるべきで、休止形態種別は動作するデバイスの機能が可能な限り少なくなるように選択されるべきです。必要とされない全ての機能は禁止されるべきです。特に次の機能部は最低可能消費電力の達成を試みるとき、特別な考慮を必要とするでしょう。

### 7.3.1. A/D変換器 (ADC)

許可したなら、A/D変換器は全ての休止形態動作で許可されます。節電するため、休止形態動作の何れかへ移行する前にA/D変換器は禁止されるべきです。A/D変換器がOFFそして再びONに切り替えられると、次の(最初の)変換は延長された(初回)変換になります。A/D変換器操作の詳細については133頁の「A/D変換器」をご覧ください。

#### 7.3.2. アナログ比較器

ア介・ル動作移行時に未使用ならばアナログ比較器は禁止されるべきです。A/D変換雑音削減動作移行時にアナログ・比較器は禁止されるべきです。その他の休止形態動作ではアナログ・比較器が自動的に禁止されます。けれども、アナログ・比較器が入力として内部基準電圧を使うように構成設定される場合、アナログ・比較器は全ての休止動作形態で禁止されるべきです。さもなければ、休止動作形態と無関係に内部基準電圧が許可されます。アナログ・比較器の構成設定方法の詳細については130頁の「アナログ・比較器」をご覧ください。

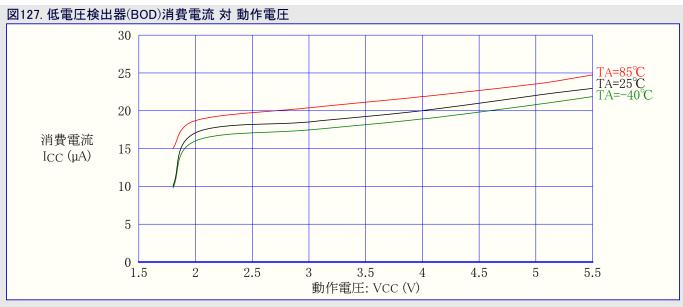

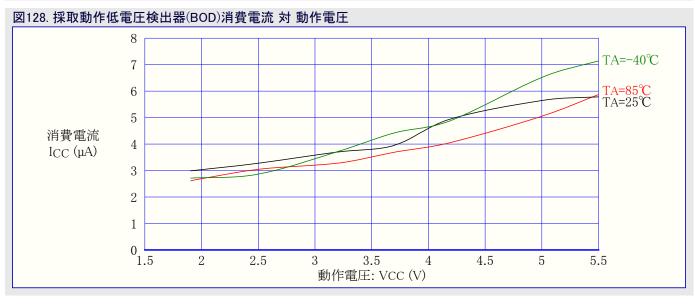

#### 7.3.3. 低電圧検出器 (BOD)

低電圧検出器(BOD)が応用で必要とされないなら、この単位部はOFFにされるべきです。低電圧検出器がBODPDヒューズによって許可されていると全休止形態動作で許可され、故に常時電力を消費します。これはより深い休止形態動作での総消費電流にとって重要な一因になります。応用に於いて低電圧検出器が必要とされる場合、この単位部は節電のために採取BOD動作形態に設定することもできます。低電圧検出器(BOD)設定法の詳細については28頁の「低電圧検出(BOD)」をご覧ください。

### 7.3.4. 内部基準電圧

内部基準電圧は低電圧検出器(BOD)、アナログ比較器、またはA/D変換器によって必要とされる時に許可されます。これらの単位部が上の項で記述されるように禁止されるなら、内部基準電圧は禁止され、電力を消費しません。再びONに切り替わる時に、この出力が使われる前に使用者はこの基準電圧に始動を許さなければなりません。基準電圧が休止動作形態でONを維持されるなら、この出力は直ちに使うことができます。始動時間の詳細については168頁の表107.内の内部バンバギャップ。基準をご覧ください。

#### 7.3.5. ウォッチト・ック・タイマ

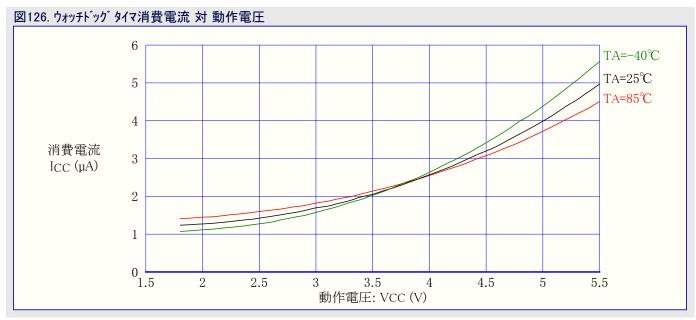

ウォッチト、ッグ タイマが応用で必要とされないなら、この単位部はOFFされるべきです。ウォッチト、ッグ タイマが許可されていると全休止形態動作で許可され、故に常時電力を消費します。これはより深い休止形態動作での総消費電流にとって重要な一因になります。ウォッチト、ッグ タイマ設定法の詳細については29頁の「ウォッチト、ッグ タイマ」をご覧ください。

### 7.3.6. ホート ピン

休止形態動作へ移行するとき、全てのポート ピンは最小電力使用に設定されるべきです。最も重要なことはその時にピンが抵抗性負荷を駆動しないのを保証することです。I/Oクロック(clk<sub>I/O</sub>)とA/D変換器クロック(clk<sub>ADC</sub>)の両方が停止される休止形態動作ではデバイスの入力緩衝部が禁止されます。これは必要とされない時に入力論理回路によって電力が消費されないことを保証します。いくつかの場合で入力論理回路は起動条件を検出するために必要とされ、その時は許可されます。どのピンが許可されるかの詳細については42頁の「デンタル入力許可と休止形態動作」をご覧ください。入力緩衝部が許可され、入力信号が浮いている状態のままか、またはアナロク信号電圧がVCC/2付近の場合、入力緩衝部は過大な電力を消費するでしょう。

アナログ、入力ピンに対するデジタル入力緩衝部は常に禁止されるべきです。入力ピンでのVCC/2付近のアナログ信号入力は活動動作でも重要な電流を引き起こし得ます。デジタル入力緩衝部はデジタル入力禁止レジスタ(DIDR0~3)の書き込みによって禁止できます。詳細については132頁と141頁の「DIDR0-デジタル入力禁止レジスタ0」をご覧ください。

### 7.4. 電力管理用レジスタ

### 7.4.1. SMCR - 休止形態制御レジスタ (Sleep Mode Control Register)

この休止形態制御レジスタは電力管理用の制御ビットを含みます。

| ピット         | 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0   |      |

|-------------|---|---|---|---|---|-----|-----|-----|------|

| \$33 (\$53) | - | _ | - | - | - | SM1 | SM0 | SE  | SMCR |

| Read/Write  | R | R | R | R | R | R/W | R/W | R/W |      |

| 初期値         | 0 | 0 | 0 | 0 | 0 | 0   | 0   | 0   |      |

ビット7~3 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0を読みます。

● ビット2,1 - SM1,0:休止形態種別選択(Sleep Mode Select Bit 1 and 0)

これらのビットは表10.で示されるように、休止形態動作を選択します。

| 表10. 休 | 表10. 休止形態動作種別選択 |             |  |  |  |  |  |  |

|--------|-----------------|-------------|--|--|--|--|--|--|

| SM1    | SM0             | 休止形態動作種別    |  |  |  |  |  |  |

| 0      | 0               | アイドル動作      |  |  |  |  |  |  |

| 0      | 1               | A/D変換雑音低減動作 |  |  |  |  |  |  |

| 1      | 0               | パプーダウン動作    |  |  |  |  |  |  |

| 1      | 1               | (予約)        |  |  |  |  |  |  |

#### ● ビット0 - SE:休止許可(Sleep Enable)

SLEEP命令が実行される時にMCUを休止形態動作へ移行させるには、休止許可(SE)ビットが論理1を書かれなければなりません。 MCUの予期せぬ休止形態動作移行を避けるため、SLEEP命令実行直前に休止許可(SE)ビットを設定(1)し、起動後直ちに解除(0)することが推奨されます。

### 7.4.2. PRR - 電力削減レジスタ (Power Reduction Register)

電力削減レシ、スタは周辺機能クロック信号が禁止されることを許すことによって電力消費を減らす方法を提供します。

| ピット        | 7     | 6 | 5      | 4 | 3      | 2     | 1        | 0     |     |

|------------|-------|---|--------|---|--------|-------|----------|-------|-----|

| (\$64)     | PRTWI | - | PRTIM0 | - | PRTIM1 | PRSPI | PRUSART0 | PRADC | PRF |

| Read/Write | R/W   | R | R/W    | R | R/W    | R/W   | R/W      | R/W   |     |

| 初期値        | 0     | 0 | 0      | 0 | 0      | 0     | 0        | 0     |     |

● ビット7 - PRTWI: TWI電力削減 (Power Reduction Two-Wire Interface)

このビットへの1書き込みは2線インターフェース(TWI)部を停止します。

ビット6.4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0を読みます。

ヒット5 - PRTIMO: タイマ/カウンタ0電力削減 (Power Reduction Timer/Counter0)

このビットへの1書き込みはタイマ/カウンタ0部を停止します。タイマ/カウンタ0が許可されると、停止前と同様に動作は継続します。

● ビット3 - PRTIM1: タイマ/カウンタ1電力削減 (Power Reduction Timer/Counter1)

このビットへの1書き込みはタイマ/カウンタ1部を停止します。タイマ/カウンタ1が許可されると、停止前と同様に動作は継続します。

● ビット2 - PRSPI: SPI電力削減 (Power Reduction SPI)

このビットへの1書き込みはこの単位部へクロックを停止することによって直列周辺インターフェース(SPI)部を停止します。再びSPIを起き上がらせる時に正しい動作を保証するためにSPIは再初期化されるべきです。

● ビット1 - PRUSART0: USART0電力削減 (Power Reduction USART0)

このビットへの1書き込みはこの単位部へクロックを停止することによってUSART部を停止します。USARTが許可されると、停止前と同様に動作は継続します。

● ビット0 - PRADC : A/D変換器電力削減 (Power Reduction ADC)

このビットへの1書き込みはA/D変換器(ADC)を停止します。A/D変換器は停止前に禁止されなければなりません。A/D変換器停止時、アナログ比較器はADC入力切替器を使えません。

## 8. システム制御とリセット

#### 8.1. AVRのリセット

リセット中、全てのI/Oレシ、スタはそれらの初期値に設定され、プログラムはリセット、クタから実行を開始します。リセット、クタに配置される命令は、きっとリセット処理ルーチンへのRJMP(相対分岐)命令でしょう。プログラムが決して割り込み元を許可しないなら、割り込みへ、クタは使われず、これらの位置に通常のプログラムコートを配置することができます。これはリセット、クタが応用領域の一方、割り込みへ、クタがブート領域の場合やその逆も同様です

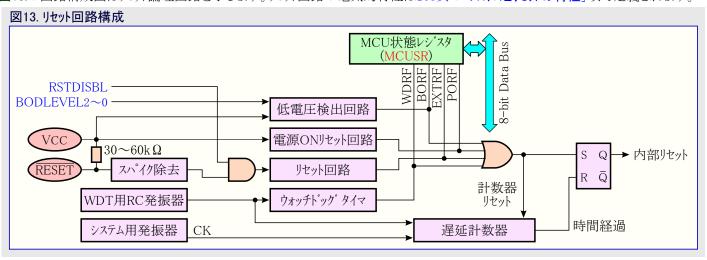

図13.の回路構成図はリセット論理回路を示します。リセット回路の電気的特性は168頁の「システムとリセットの特性」項で定義されます。

AVRのI/Oポートはリセット元が有効になると直ちにそれらの初期状態にリセットされます。これはどのクロック元の走行も必要ありません。 全てのリセット元が無効にされてしまった後、遅延計数器(タイマ)が始動され、内部リセットを引き伸ばします。これは通常動作開始前に安定電圧へ達することを電源に許します。

### 8.2. リセット元

ATtiny828には次の4つのリセット元があります。

- 電源ONJセット・・・・・ 供給電圧が電源ONJセット閾値電圧(VPOA)以下でMCUがJセットされます。

- 外部リセット・・・・・・・ RESET機能許可時にRESETとシンが最小ハールス幅以上Lowレー・ルに保たれると、MCUがリセットされます。

- ウォッチト、ッグ リセット・・・ ウォッチト、ック リセット動作が許可され、ウォッチト、ック タイマが終了すると、MCUがリセットされます。

- 低電圧リセット・・・・・ 低電圧検出器(BOD)が許可され、供給電圧(VCC)が低電圧検出電圧(VBOT)以下でMCUがリセットされます。

#### 8.2.1. 電源ONリセット

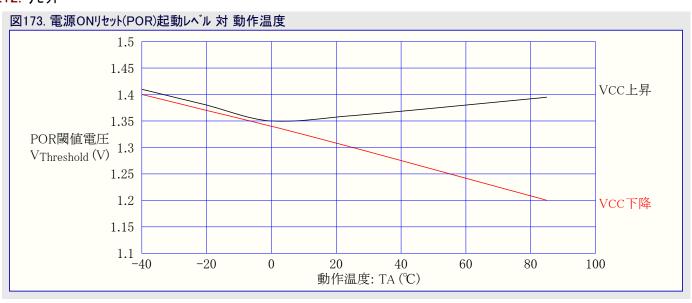

電源ONJセット(POR)パルスはチップ。上の検出回路により、生成されます。検出電圧は168頁の「システムとリセットの特性」項で定義されます。POR信号はVCCが検出電圧以下の時は必ず活性(有効)にされます。POR回路は供給電圧異常検出は勿論、始動リセットの起動にも使えます。

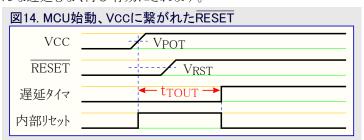

電源ONJセット回路はデバイスが電源投入でリセットされることを保証します。電源ONJセット閾値電圧(VPOR)への到達はVCCの上昇後にデバイスがどのくらいリセットを保つかを決める遅延計数器(タイマ)を起動します。VCCがこの検出電圧以下に低下すると、リセット信号はどんな遅延もなく再び有効にされます。

#### 8.2.2. 外部リセット

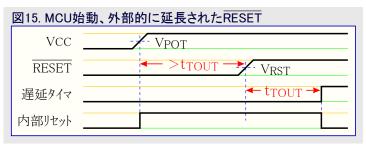

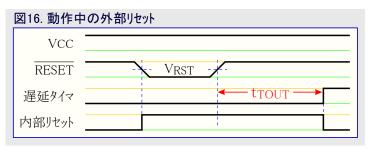

外部リセットはRESETt°ンのLowレヘルによって生成されます。クロックが動いていなくても、最小ハペルス幅(168頁の「システムとリセットの特性」項参照)以上のリセットハペルスはリセットを生成します。短すぎるハペルスはリセット生成が保証されません。印加された信号の上昇がリセット閾値電圧(VRST)に達すると(遅延タイマを起動し)、遅延タイマは遅延時間(trour)経過後にMCUを始動します。

### 8.2.3. ウォッチト・ック・リセット

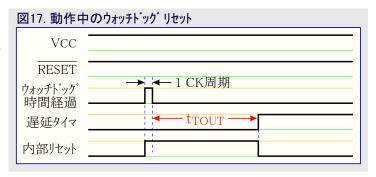

ウォッチト、ッグ・時間経過時に(内部で)短いリセット ハ゜ルスを生成します。 遅延タイマはこのハ゜ルスの下降端で遅延時間(t<sub>TOUT</sub>)の計時を始めます。ウォッチト、ッグ・タイマの操作の詳細については29頁をご覧ください。

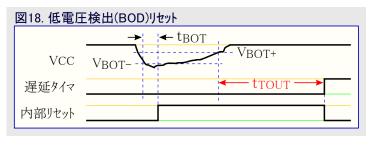

### 8.2.4. 低電圧(ブラウンアウト)検出リセット

低電圧検出(BOD)回路はVCC水準が構成設定可能な検出レヘル (VBOT)以上を維持することを監視します。BOD許可時、VCCが下降して検出時間の長さ(tBOD)の間、検出レヘル以下に留まる時にBODリセットが与えられます。このリセットはVCCが再び検出レヘル以上に上昇するまで活性を維持します。

BOD回路は電圧が検出時間(t<sub>BOD</sub>)の間、検出レベル以下に留まらなければ、VCCの降下を検出しません(168頁の「システムとリセットの特性」をご覧ください)。

BOD回路は以下のように3つの動作形態を持ちます。

- •禁止:この動作形態ではVCCが監視されず、従って供給電力が安定を維持する応用だけに推奨されます。

- 許可: この動作形態ではVCCレヘールが継続的に監視されます。VCCが最低tBOD間、VBOT以下へ降下した場合に低電圧(Brownout)リセットが生成されます。

- ・採取: この動作形態ではVCCが32kHz超低電力(ULP)発振器から配給される1kHzクロックの各負端で採取されます。各採取間でBODはOFFされます。この動作種別はBODが継続的に許可される動作形態に比べて消費電力を減らしますが、1kHzックロックの2つの正端間のVCCでの降下検出を怠ります。この動作形態で低電圧(Brown-out)が検出された場合、VCCがVBOT以上に上昇するまでデバイスがリセットを維持するのを保証するために、BOD回路が許可動作形態に設定されます。BODはリセットが開放されてヒュースが読み込まれた後で採取動作形態に戻ります。

BOD動作形態はBODACTとBODPDのヒュース、ビットを用いて選択されます。BODACTヒュース、ビットは**表11**.で示されるように、活動動作とアイトル動作でBODがどう動作するかを決めます。

| 表11. 活動とアイドルの動作でのBOD動作構成設定 |         |                  |  |  |  |  |  |

|----------------------------|---------|------------------|--|--|--|--|--|

| BODACT1                    | BODACT0 | 動作形態             |  |  |  |  |  |

| 0                          | 0       | (予約)             |  |  |  |  |  |

| 0                          | 1       | 採取動作: 採取動作でBOD許可 |  |  |  |  |  |

| 1                          | 0       | 許可動作: 継続的にBOD許可  |  |  |  |  |  |

| 1                          | 1       | 禁止動作: BOD禁止      |  |  |  |  |  |

BODPDヒュース ビットは表12.で示されるように、アイドル動作を除く全ての休止形態動作でBODがどう動作するかを決めます。

152頁の「**ヒュース´ ビット**」をご覧ください。

表12. アイル以外の休止形態でのBOD動作構成設定

| BODPD1 | BODPD0 | 動作形態             |

|--------|--------|------------------|

| 0      | 0      | (予約)             |

| 0      | 1      | 採取動作: 採取動作でBOD許可 |

| 1      | 0      | 許可動作: 継続的にBOD許可  |

| 1      | 1      | 禁止動作: BOD禁止      |

### 8.3. 内部基準電圧

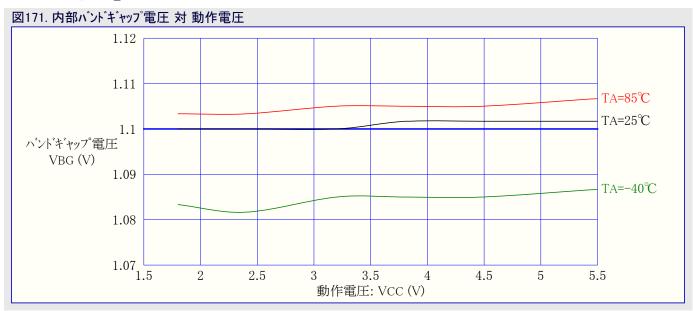

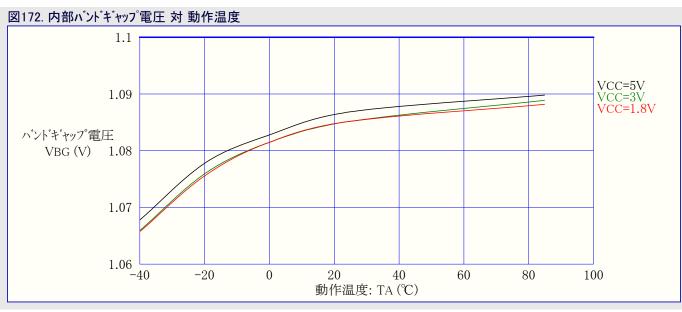

ATtiny828は内部基準電圧が特徴です。この基準電圧は低電圧検出(BOD)に使われ、A/D変換やアナログ比較器の入力としても使えます。 ハンドギャップ電圧は供給電圧と温度で変化します。

### 8.3.1. 基準電圧許可信号と起動時間

基準電圧には使われるべき方法に影響を及ぼすかもしれない起動時間があります。この起動時間は、168頁の「システムとリセットの特性」で与えられます。節電のために、この基準電圧は常にONではありません。この基準電圧は次の状態中ONです。

- 低電圧検出リセット許可時

- アナログ 比較器内部基準電圧接続時

- · A/D変換部動作許可時

従って低電圧検出(BOD)が許可されていないと、ACPMUXnの設定(=4)またはA/D変換部許可(ADEN=1)後、使用者はアナログ比較器またはA/D変換器出力が使われる前に基準電圧へ起動時間を与えなければなりません。ハプロタヴン動作での消費電力を減らすため、使用者はハプロタヴン動作へ移行する前に基準電圧がOFFされるのを保証することで上の3つの状態を避けられます。

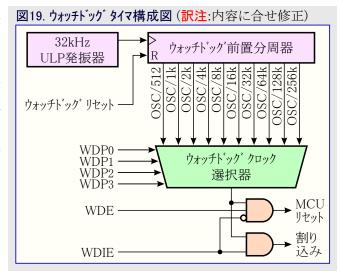

### 8.4. ウォッチトック タイマ

ウォッチト、ック、タイマは32kHz超低電力(ULP)発振器からクロック駆動されます(19頁をご覧ください)。ウォッチト、ック、タイマ前置分周器の制御によってウォッチト、ック、リセット間隔は31頁の表15.で示されるように調整できます。ウォッチト、ック、リセット(WDR)命令はウォッチト、ック、タイマをリセットします。ウォッチト、ック、タイマはそれが禁止される時とチッフ。リセットが起こる時もリセットされます。10種の異なるクロック周期時間がこのリセット周期を決めるために選択できます。別のウォッチト、ック、リセットなしにリセット周期が経過すると、ATtiny 828はリセットしてリセット、ベクタから実行します。

ウォッチドッグ タイマはリセットの代わりに割り込みを生成する設定にもできます。これはパワーダウン動作から起動するのにウォッチドッグを使う時に大変有用となり得ます。

予期せぬウォッチトック、禁止や予期せぬ計時終了周期変更を防ぐため、2つの異なる安全レベルが表13.で示されるWDTON構成設定ビットによって選択されます。詳細については次の「ウォッチト、ック、タイマ構成設定変更用手順」を参照してください。

| 表13    | WDTON構成設定ビットの設定によるウォッチドッグ機能                  | 設定 |

|--------|----------------------------------------------|----|

| AX IU. | VVDIONY母ルスロメ 佐し ノロソコメ 佐しらかる) ノイノノロ ノス 1皮 flt | :  |

| WDTON構成設定ビット | 安全レベル | WDT初期状態 | WDT禁止方法  | 計時完了時間変更方法 |

|--------------|-------|---------|----------|------------|

| 非プログラム(1)    | 1     | 禁止      | 時間制限変更手順 | なし(常時可)    |

| プ°ログラム(0)    | 2     | 許可      | なし(常時許可) | 時間制限変更手順   |

### 8.4.1. ウォッチト、ック、タイマ構成設定変更用時間制限手順

ウォッチドッグ構成設定変更手順は安全レベル間で僅かに異なります。各レベルに対して独立した手順が記述されます。

### • 安全レベル1

この動作種別ではウォッチドッグタイマが初めに禁止されますが、どんな制限もなくウォッチドッグ許可(WDE)ビットに1を書くことによって許可できます。許可したウォッチドッグタイマを禁止する時に時間制限手順が必要とされます。許可したウォッチドッグタイマを禁止するには次の手順に従わなければなりません。

- 1. 保護されたI/Oレジスタの変更許可用の識票を構成設定変更保護(CCP)レジスタに書いてください。

- 2. (次からの)4命令周期内に同じ操作(命令)で欲したWDEとウォッチト・ック・タイマ前置分周選択(WDP3~0)ビットを書いてください。

#### • 安全レベル2

この動作種別ではウォッチドッグ タイマが常に許可され、WDEビットは常に1として読めます。ウォッチドッグ計時完了周期を変更する時に時間制限された変更が必要とされます。ウォッチドッグ計時完了周期を変更するには次の手順に従わなければなりません。

- 1. 保護されたI/Oレジスタの変更許可用の識票を構成設定変更保護(CCP)レジスタに書いてください。

- 2. (次からの)4命令周期内に同じ操作(命令)でWDP2~0ビットを書いてください。WDEビットに書かれた値は無関係です。

#### 8.4.2. コート 例

次のコート・例はウォッチト、ック(WDT)をOFFに切り替える方法を示します。本例は(例えば全割り込み禁止によって)割り込みが制御され、 それ故この関数実行中に割り込みが起きない前提です。

| アセンブリ言語  | A A JA Di |                                                                         |                                |

|----------|-----------|-------------------------------------------------------------------------|--------------------------------|

| WDT_OFF: | WDR       |                                                                         | ;ウォッチドッグ タイマ リセット              |

|          | IN        | R16, MCUSR                                                              | ;現MCUSR値を取得                    |

|          | ANDI      | R16, ~ (1< <wdrf)< td=""><td>;WDRFビットのみ<mark>0</mark>値を取得</td></wdrf)<> | ;WDRFビットのみ <mark>0</mark> 値を取得 |

|          | OUT       | MCUSR, R16                                                              | ;MCUSRのWDRFを解除(0)              |

|          | LDI       | R16, \$D8                                                               | ;変更許可識票値を取得                    |

|          | OUT       | CCP, R16                                                                | ;構成設定変更許可手順開始                  |

|          | LDI       | R16, (0< <wde)< td=""><td>;WDE論理<mark>0</mark>値を取得</td></wde)<>         | ;WDE論理 <mark>0</mark> 値を取得     |

|          | OUT       | WDTCSR, R16                                                             | ;ウォッチドック゛禁止                    |

|          | RET       |                                                                         | ;呼び出し元へ復帰                      |

#### 注: 5頁の「コート・例」をご覧ください。

### 8.5. リセット関係レジスタ

#### 8.5.1. MCUSR - MCU状態レジスタ (MCU Status Register)

MCU状態レシブスタはどのリセット元がMCUリセットを起こしたかの情報を提供します。

| ピット         | 7 | 6 | 5 | 4 | 3    | 2    | 1     | 0    |       |

|-------------|---|---|---|---|------|------|-------|------|-------|

| \$35 (\$55) | _ | - | - | - | WDRF | BORF | EXTRF | PORF | MCUSR |

| Read/Write  | R | R | R | R | R/W  | R/W  | R/W   | R/W  |       |

| 初期値         | 0 | 0 | 0 | 0 | 内容参照 | 内容参照 | 内容参照  | 内容参照 |       |

#### ビット7~4 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0を読みます。

ヒット3 - WDRF: ウォッチトック・リセット フラク (Watchdog Reset Flag)

このビットはウォッチドッグ リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

● ビット2 - BORF: 低電圧リセット フラク (Brown-Out Reset Flag)

このビットは低電圧リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

● ビット1 - EXTRF:外部リセット フラク (External Reset Flag)

このビットは外部リセットが起こると設定(1)されます。このビットは電源ONリセットまたは、このフラグへの論理0書き込みによってリセット(0)されます。

● ビット0 - PORF: 電源ONリセット フラク (Power-on Reset Flag)

このビットは電源ONJセットが起こると設定(1)されます。このビットはこのフラグへの論理0書き込みによってのみリセット(0)されます。

リセット条件の確認にリセット フラグを使うため、使用者はプログラム内で可能な限り早くMCUSRを読み、そして解除(0)すべきです。別のリセットが起こる前にこのレジスタが解除(0)されると、そのリセット元はリセットフラグを調べることによって得られます。

### 8.5.2. WDTCSR - ウォッチドック タイマ制御/状態レジスタ (Watchdog Timer Control and Status Register)

| ピット        | 7    | 6    | 5    | 4 | 3   | 2    | 1    | 0    | _      |

|------------|------|------|------|---|-----|------|------|------|--------|

| (\$60)     | WDIF | WDIE | WDP3 | - | WDE | WDP2 | WDP1 | WDP0 | WDTCSR |

| Read/Write | R/W  | R/W  | R/W  | R | R/W | R/W  | R/W  | R/W  |        |

| 初期値        | 0    | 0    | 0    | 0 | 不定  | 0    | 0    | 0    |        |

### ● ビット7 - WDIF: ウォッチドッグ時間超過割り込み要求フラグ(Watchdog Timeout Interrupt Flag)

ウォッチト、ック、タイマが割り込みに設定され、ウォッチト、ック、タイマで計時完了が起こると、本ヒ、ットが設定(1)されます。対応する割り込み処理へ、クタを実行すると、WDIFはハート・ウェアによって解除(0)されます。代わりにWDIFはこのフラグへの論理1書き込みによっても解除(0)されます。ステータスレジ、スタ(SREG)の全体割り込み許可(I)ヒ、ットとウォッチト、ック、割り込みが実行されます。

### ● ビット6 - WDIE: ウォッチドッグ時間超過割り込み許可 (Watchdog Timeout Interrupt Enable)

このビットが1を書かれ、ウォッチドッグリセット許可(WDE)ビットが解除(0)され、ステータス レジスタ(SREG)の全体割り込み許可(I)ビットが設定(1)されると、ウォッチドッグ時間超過割り込みが許可されます。この動作形態ではウォッチドッグタイマで時間超過が起きた場合にリセットの代わりに対応する割り込みが実行されます。

WDEが設定(1)されると、時間経過発生時にハート・ウェアによってWDIE が自動的に解除(0)されます。これはウォッチト・ック・リセット保護を維持すると同時に割り込みを使うのに有用です。WDIEt・ット解除(0)後、次の時間経過がリセットを生成します。ウォッチト・ック・リセットを避けるには各割り込み後にWDIEが設定(1)されなければなりません。

| 表14. 🖠                          | <b>ウォッチト</b> ゙: | ッグタイマ構成設定 |      |  |  |  |  |  |  |

|---------------------------------|-----------------|-----------|------|--|--|--|--|--|--|

| WDE WDIE ウォッチドック、タイマの状態 時間超過での活 |                 |           |      |  |  |  |  |  |  |

| 0                               | 0               | 停止        | なし   |  |  |  |  |  |  |

| 0                               | 1               | 走行        | 割り込み |  |  |  |  |  |  |

| 1                               | 0               | 走行        | リセット |  |  |  |  |  |  |

| 1                               | 1               | 走行        | 割り込み |  |  |  |  |  |  |

#### ビット4 - Res: 予約 (Reserved)

このビットは予約されており、常に0を読みます。

### ビット3 - WDE: ウォッチト、ック、許可 (Watchdog Enable)

WDEが論理1を書かれると、ウォッチドッグ、タイマが許可され、WDEが論理0を書かれた場合にウォッチドッグ、タイマ機能が禁止されます。

安全レヘ・ル2では、例え上で記述した方法でもウォチト・ック・タイマを禁止することが不可能です。29頁の「ウォッチト・ック・タイマ構成設定変更用時間制限手順」をご覧ください。

安全レヘ・ル1では、WDEがMCUSRのウォッチト・ック・リセット フラグ (WDRF)によって無効化されます。WDRFの記述については30頁の「MCUSR - MCU状態レジスタ」をご覧ください。WDEを解除(0)するには、上で記述した手順でウィッチト・ック・を禁止する前に、WDRFが解除(0)されなければなりません。この特質は失敗が起こっている状況中の複数リセットと、失敗後の安全な始動を保証します。

ウォッチト、ック、タイマを応用で使わないつもりなら、デバイスの初期化でウォッチト、ック、禁止手順全体を行うことが重要です。例えばポインタ暴走や低電圧状況によってウォッチト、ッグが予期せず許可された場合、デバイスは順に新しいウォッチト、ック、リセットを引き起こす、リセットにされるでしょう。この状況を避けるため、応用ソフトウェアは初期化ルーチン内でWDRFとWDE制御ビットを常に解除(①)すべきです。

#### ビット5,2~0 - WDP3~0: ウォッチトック、タイマ前置分周選択 (Watchdog Timer Prescaler 3,2,1 and 0)

WDP3~0ビットはウォッチドッグタイマが許可される時のウォッチドッグタイマ前置分周を決めます。各種前置分周値と対応する計時完了周期は**表15**.で示されます。

表15. ウォッチト・ック・前置分周器選択

| 秋10. 7/17/11 77 HI    | 旦刀加  | 70.757.114 | •    |        |       |      |      |      |                     |      |                        |   |   |   |   |   |

|-----------------------|------|------------|------|--------|-------|------|------|------|---------------------|------|------------------------|---|---|---|---|---|

| WDP3                  |      |            |      | (      | )     |      |      |      | 1<br>0 1<br>0 1 0 1 |      |                        |   |   |   |   |   |

| WDP2                  |      | (          | )    |        | 1     |      |      |      | 0                   |      |                        |   | 1 |   |   |   |

| WDP1                  | (    | )          |      | 1      | (     | )    | ]    | [    | (                   | )    |                        | L | ( | ) |   | 1 |

| WDP0                  | 0    | 1          | 0    | 1      | 0     | 1    | 0    | 1    | 0                   | 1    | 0                      | 1 | 0 | 1 | 0 | 1 |

| WDT発振周期数              | 512  | 1k         | 2k   | 4k     | 8k    | 16k  | 32k  | 64k  | 128k                | 256k |                        |   |   |   |   |   |

| 代表的計時完了<br>周期(VCC=5V) | 16ms | 32ms       | 64ms | 0.125s | 0.25s | 0.5s | 1.0s | 2.0s | 4.0s                | 8.0s | (予約)( <mark>注</mark> ) |   |   |   |   |   |

注: 選択したなら、1010未満の有効設定の1つが使われます。

これらのビットの予期せぬ変更を避けるため、以下の手順に従わなければなりません。

- 1. 必要とされる識票を構成設定変更保護(CCP)レジスタに書いてください。10頁をご覧ください。

- 2. (次からの)4命令周期内に望むビット値を書いてください。

# 9. 割り込み

この章は割り込み操作の詳細を記述します。AVR割り込み操作の一般説明については8頁の「リセットと割り込みの扱い」をご覧ください。

### 9.1. 割り込みべかり

ATtiny828の割り込みベクタは下の表16.で記述されます。

表16. リセットと割り込みのベクタ

| ベクタ番号 | プ <sup>°</sup> ログラム アト゛レス ( <mark>注1</mark> ) | ラベル表記         | 割り込み元                  |  |  |  |  |

|-------|-----------------------------------------------|---------------|------------------------|--|--|--|--|

| 1     | \$0000 ( <b>注2</b> )                          | RESET         | 電源ON, WDT, BOD等の各種リセット |  |  |  |  |

| 2     | \$0001                                        | INT0          | 外部割り込み要求0              |  |  |  |  |

| 3     | \$0002                                        | INT1          | 外部割り込み要求1              |  |  |  |  |

| 4     | \$0003                                        | PCINTO (PCIO) | ピン変化0群割り込み要求           |  |  |  |  |

| 5     | \$0004                                        | PCINT1 (PCI1) | ピン変化1群割り込み要求           |  |  |  |  |

| 6     | \$0005                                        | PCINT2 (PCI2) | ピン変化2群割り込み要求           |  |  |  |  |

| 7     | \$0006                                        | PCINT3 (PCI3) | ピン変化3群割り込み要求           |  |  |  |  |

| 8     | \$0007                                        | WDT           | ウォッチドッグ計時完了            |  |  |  |  |

| 9     | \$0008                                        | TIM1_CAPT     | タイマ/カウンタ1捕獲発生          |  |  |  |  |

| 10    | \$009                                         | TIM1_COMPA    | タイマ/カウンタ1比較A一致         |  |  |  |  |

| 11    | \$000A                                        | TIM1_COMPB    | タイマ/カウンタ1比較B一致         |  |  |  |  |

| 12    | \$000B                                        | TIM1_OVF      | タイマ/カウンタ1溢れ            |  |  |  |  |

| 13    | \$000C                                        | TIM0_COMPA    | タイマ/カウンタ0比較A一致         |  |  |  |  |

| 14    | \$000D                                        | TIM0_COMPB    | タイマ/カウンタ0比較B一致         |  |  |  |  |

| 15    | \$000E                                        | TIM0_OVF      | タイマ/カウンタ0溢れ            |  |  |  |  |

| 16    | \$000F                                        | SPI           | SPI 転送完了               |  |  |  |  |

| 17    | \$0010                                        | USART0_RXS    | USART0受信開始             |  |  |  |  |

| 18    | \$0011                                        | USART0_RXC    | USART0受信完了             |  |  |  |  |

| 19    | \$0012                                        | USART0_DRE    | USART0データ レシブスタ空       |  |  |  |  |

| 20    | \$0013                                        | USART0_TXC    | USART0送信完了             |  |  |  |  |

| 21    | \$0014                                        | ADC_READY     | A/D変換完了                |  |  |  |  |

| 22    | \$0015                                        | EE_RDY        | EEPROM操作可              |  |  |  |  |

| 23    | \$0016                                        | ANA_COMP      | アナログ比較器出力遷移            |  |  |  |  |

| 24    | \$0017                                        | TWI           | 2線インターフェース             |  |  |  |  |

| 25    | \$0018                                        | SPM_RDY       | SPM命令操作可               |  |  |  |  |

| 26    | \$0019                                        | RESERVED      | (予約)                   |  |  |  |  |

注1: MCU制御レシ、スタ(MCUCR)の割り込みへ、クタ選択(IVSEL)ヒ、ットが設定(1)されると、割り込みへ、クタはブートフラッシュ領域先頭(部)へ移動されます。そして各割り込みへ、クタのアト・レスは、この表のアト・レスがブートフラッシュ領域の先頭アト・レスに加算されます。

**注2**: BOOTRSTヒュース・がプログラム(0)されると、デハイスはリセットでブートロータ・アトレスへ飛びます。145頁の「プートロータ・プログラムへの移行」をご覧ください。

プログラムが決して割り込み元を許可しない条件では、割り込みへ、クタは使われず、結果としてこれらの位置に通常のプログラム コードを置くことができます。これはリセット ヘンクタが応用領域の一方、割り込みヘンクタがブート領域、またはその逆の場合でも同様です。

ATtiny828での最も代表的且つ一般的なリセットと割り込みのヘブクタアドンス用設定は下のプログラム例で示されます。

| アト・レス  | ラヘ゛ル   | 命令    |                | 注釈               |

|--------|--------|-------|----------------|------------------|

|        |        | .org  | \$0000         | ;次命令行開始アドレス      |

| \$0000 |        | RJMP  | RESET          | ;各種リセット          |

| \$0001 |        | RJMP  | INTO_ISR       | ;外部割り込み要求0       |

| \$0002 |        | RJMP  | INT1_ISR       | ;外部割り込み要求1       |

| \$0003 |        | RJMP  | PCINTO_ISR     | ; 比少変化0群割9込み要求   |

| \$0004 |        | RJMP  | PCINT1_ISR     | ;比℃変化1群割9込み要求    |

| \$0005 |        | RJMP  | PCINT2_ISR     | ;ピン変化2群割り込み要求    |

| \$0006 |        | R.JMP | PCINT3 ISR     | ;ピン変化3群割り込み要求    |

| \$0007 |        | RJMP  | WDT_ISR        | ;ウォッチトック計時完了     |

| \$0008 |        | RJMР  | TIM1_CAPT_ISR  | ; タイマ/カウンタ1捕獲発生  |

| \$0009 |        | RJMР  | TIM1_COMPA_ISR | ;タイマ/カウンタ1比較A一致  |

| \$000A |        | RJMР  | TIM1 COMPB ISR | ;タイマ/カウンタ1比較B一致  |

| \$000B |        | RJMP  | TIM1_OVF_ISR   | ;タイマ/カウンタ1溢れ     |

| \$000C |        | RJMP  | TIMO_COMPA_ISR | ;タイマ/カウンタ0比較A一致  |

| \$000D |        | RJMP  | TIMO_COMPB_ISR | ;タイマ/カウンタ0比較B一致  |

| \$000E |        | RJMP  | TIMO_OVF_ISR   | ;タイマ/カウンタ0溢れ     |

| \$000F |        | RJMP  | SPI_ISR        | ;SPI転送完了         |

| \$0010 |        | RJMP  | USARTO_RXS_ISR | ;USART0受信開始      |

| \$0011 |        | RJMP  | USARTO_RXC_ISR | ;USART0受信完了      |

| \$0012 |        | RJMP  | USARTO_DRE_ISR | ;USARTOデータレシブスタ空 |

| \$0013 |        | RJMP  | USARTO_TXC_ISR | ;USART0送信完了      |

| \$0014 |        | RJMP  | ADC_ISR        | ;A/D変換完了         |

| \$0015 |        | RJMP  | EE_RDY_ISR     | ;EEPROM操作可       |

| \$0016 |        | RJMP  | ANA_COMP_ISR   | ;アナログ比較器出力遷移     |

| \$0017 |        | RJMP  | TWI_ISR        | ;2線インターフェース      |

| \$0018 |        | RJMP  | SPM_RDY_ISR    | ;SPM命令操作可        |

| \$0019 |        | RJMP  | RESERVED       | ;(予約)            |

| ;      |        |       |                |                  |

| \$001A | RESET: | 〈命令〉  |                | ;主プログラム開始        |

|        |        | >     |                | ;(以下命令)          |

<mark>注</mark>: 5頁の「**コード例**」をご覧ください。

表17.はBOOTRST(ヒュース)とIVSEL(割り込みへ)クタ 選択ヒット)の様々な組み合わせに対するリセットと割り込みのへ)クタ配置を示します。

## 表17. リセットと割り込みのベクタ配置

| BOOTRST                              | IVSEL | リセット ヘ・クタ アト・レス   | 割り込みベクタ先頭アドレス                     |  |  |  |

|--------------------------------------|-------|-------------------|-----------------------------------|--|--|--|

| ゴヒつ°ロカ'ラル(1)                         | 0     | \$0000            | \$0001                            |  |  |  |

| 非プログラム(1)                            | 1     | \$0000            | ブート リセット アトレス ( <b>注</b> )+\$0001 |  |  |  |

| プロガラル(0)                             | 0     | ブート リセット アドレス (注) | \$0001                            |  |  |  |

| プ <sup>°</sup> ロク <sup>*</sup> ラム(0) | 1     | ブート リセット アトレス (注) | ブート リセット アドレス (注)+\$0001          |  |  |  |

注: ブート リセット アドレスは145頁の表82.で示されます。

以下は次の場合に対するプログラム例です。

- BOOTRSTヒュース は非プログラム(1)

- ブート領域容量は2Kバイトに設定

- どの割り込みが許可されるのにも先立ってMCU制御レシ、スタ(MCUCR)の割り込みへ、クタ選択(IVSEL)ビットを設定(1)

| アト・レス            | ラヘ゛ル   | 命令                 |                         | 注釈                                   |

|------------------|--------|--------------------|-------------------------|--------------------------------------|

| \$0000           | RESET: | . ORG<br>〈命令〉<br>〈 | \$0000                  | ;アドレス \$0000<br>;主プログラム開始<br>;(以下命令) |

|                  |        | . ORG              | \$0C01                  | ;アドレス \$0C01                         |

| \$0C01<br>\$0C02 |        | RJMP<br>RJMP       | INTO_ISR<br>INT1_ISR    | ;外部割り込み要求0<br>;外部割り込み要求1             |

| \$0C18<br>\$0C19 |        | RJMP<br>RJMP       | SPM_RDY_ISR<br>RESERVED | ;SPM命令操作可<br>;(予約)                   |

注: 5頁の「**コード例**」をご覧ください。

以下は次の場合に対するプログラム例です。

- BOOTRSTヒュース ltプ ロク ラム(0)

- ブート領域容量は2Kバイトに設定

| アト・レス  | ラヘ゛ル   | 命令    |             | 注釈           |

|--------|--------|-------|-------------|--------------|

|        |        | . ORG | \$0001      | ;アドレス \$0001 |

| \$0001 |        | RJMP  | INTO_ISR    | ;外部割り込み要求0   |

| \$0002 |        | RJMP  | INT1_ISR    | ;外部割り込み要求1   |

|        |        | >     |             |              |

| \$0018 |        | RJMP  | SPM_RDY_ISR | ;SPM命令操作可    |

| \$0019 |        | RJMP  | RESERVED    | ;(予約)        |

|        |        | >     |             | ;以下、プログラムなど  |

|        |        | . ORG | \$0C00      | ;アトンス \$0C00 |

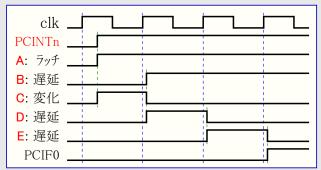

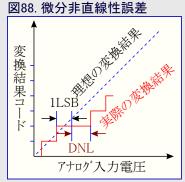

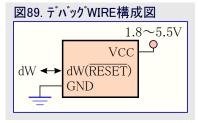

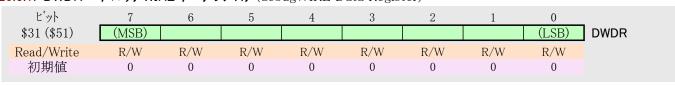

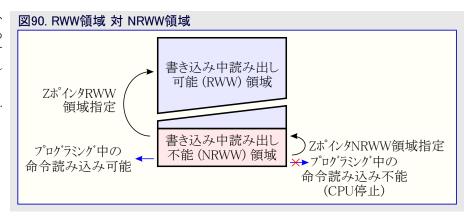

|        |        |       |             |              |