# ATtiny87/167

# tinyAVR® データシート

# 序説

ATtiny87/167はAVR®強化RISC構造に基づく低電力CMOS 8ビット マイクロ コントローラです。ATtiny87/167は8/16Kバイトのフラッシュ メモリ、512バイトのSRAM、512バイトのEEPROMを持つ20/32ピン デバイスです。単一クロック周期での強力な命令の実行により、デ゙バイスはMHz当たり1MIPS(100万命令/秒)近くの単位処理量を達成し、消費電力対処理速度に対するデ゙バイスの最適化をシステム設計者に許します。

本書は一般の方々の便宜のため有志により作成されたもので、Microchip社とは無関係であることを御承知ください。しおりの[はじめに]での内容にご注意ください。

© 2020 Microchip Technology Inc. 完全デーダント DS40002167A/J1 - 1頁

# 特徴

- 高性能、低消費AVR® 8ビットマイクロ コントローラ

- ・進化したRISC構造

- 強力な123命令(多くは1周期実行)

- 32個の1バイト長汎用レジスタ

- 完全なスタティック動作

- ・データメモリと不揮発性プログラムメモリ

- 実装書き換え可能な8K/16Kバイト(4K/8K語)フラッシュ メモリ内蔵

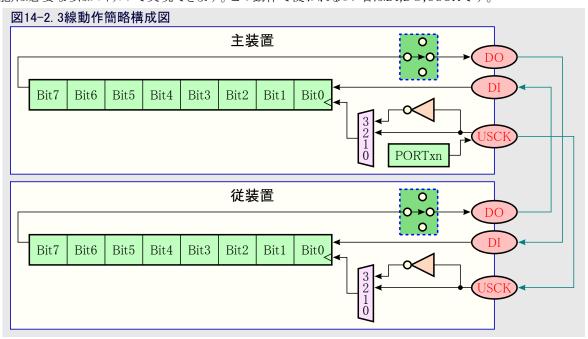

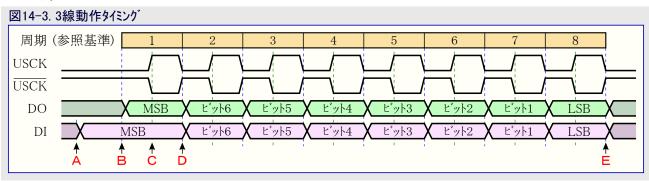

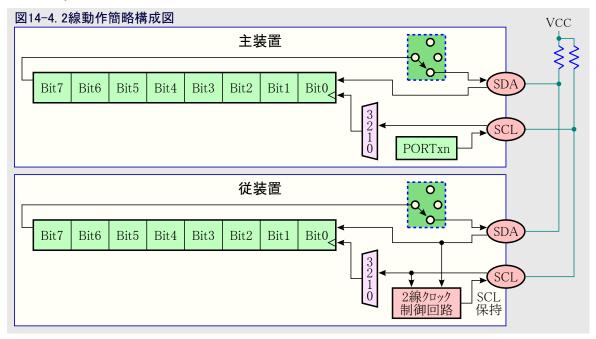

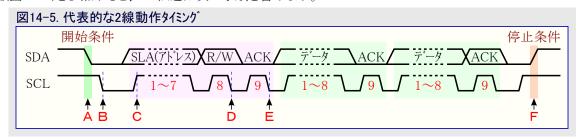

- ・10,000回の書き換えが可能

- 実装書き換え可能な512バイトのEEPROM

- ・100,000回の書き換えが可能

- 512 バ 小の内蔵SRAM

- データ保持力: 20年/85℃, 100年/25℃

- SPIポート経由の実装書き込み(ISP)

- 低容量LIN/UARTソフトウェア実装書き込み可能

- ソフトウェア保護用の設定可能な施錠機能

- · 内蔵周辺機能

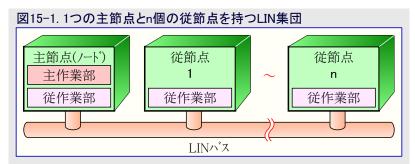

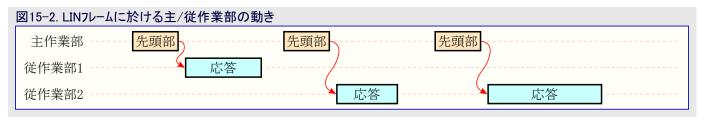

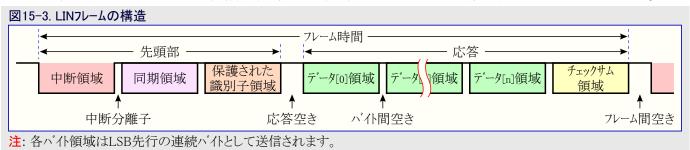

- LIN2.1と1.3の制御器または8ビットUART

- 1つの前置分周器付き8ビット非同期タイマ/カウンタ

- ・1つの比較または8ビットPWMチャネル

- 1つの前置分周器付き16ビット同期タイマ/カウンタ

- 外部事象計数器

- ・2つの比較または各々が最大4つの出力ピンを駆動するPWMチャネル

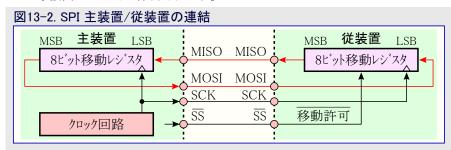

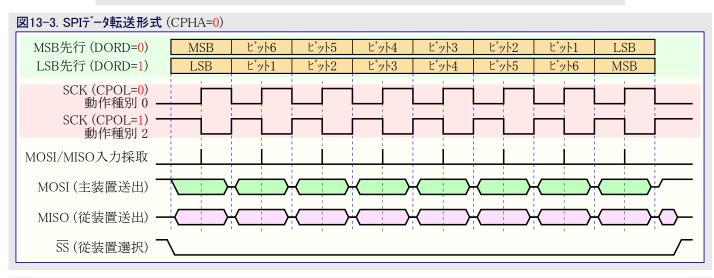

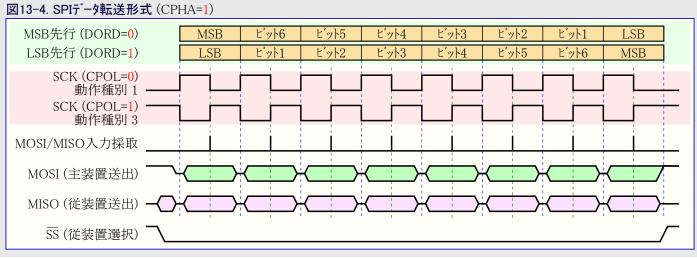

- 主装置/従装置動作SPI直列インターフェース

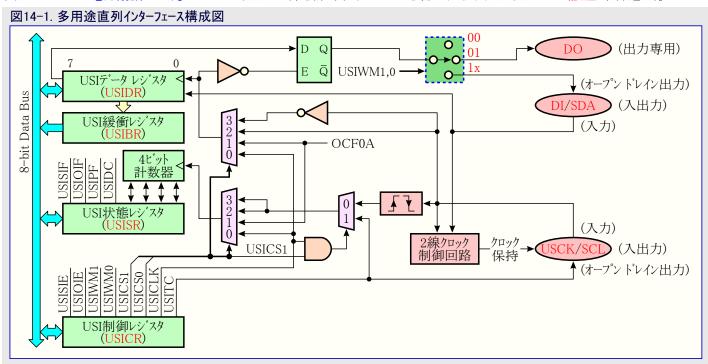

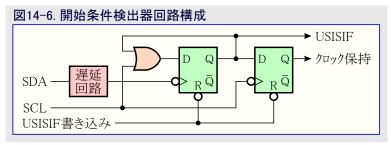

- 開始条件検出器付き多用途直列インターフェース(USI)

- 10ビット A/D変換器

- ・11本のシングル エント チャネル

- 設定可能な利得(×8,×20)付きの8つの差動ADCチャネル対

- 選択可能な基準電圧付きチップ。内蔵アナログ比較器

- LIN節(ノート)認証用100μA±10%電流源

- チップ上の温度感知器

- 独立した発振器付きの設定可能なウォッチドッグタイマ

- ・ 特殊マイクロ コントローラ機能

- 電力制御やEMC減少のためのソフトウェア制御クロック切り替え

- デバッグWIRE内蔵デバッグ システム

- 外部及び内部の割り込み

- アイドル、A/D変換雑音低減、パワーダウン、パワーセーブの4つの低消費動作

- 電源ONJセット回路と設定可能な低電圧検出器(BOD)

- 内蔵8MHz校正付き発振器

- 4~16MHzと32kHzのクリスタル発振子/セラミック振動子用の発振器

- ・I/Oと外囲器

- 16ビットの設定可能なI/O

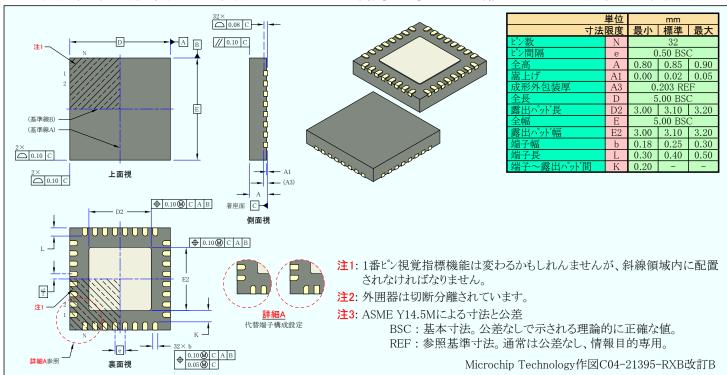

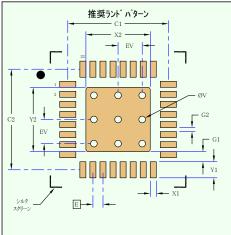

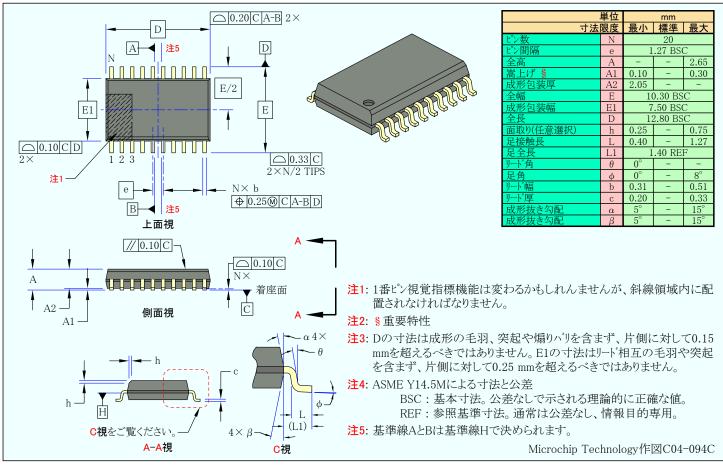

- 20"J-FSOIC, 20"J-FTSSOP, 20\nownbyFWQFN, 32\nownbyFVQFN

- 動作電圧

- 1.8~5.5V

- 動作温度

- --40∼85°C

- 動作速度

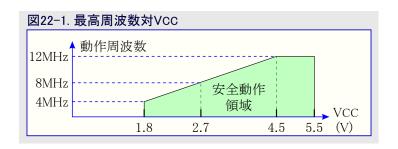

- $-0\sim4MHz/1.8\sim5.5V$

- $-0 \sim 8 MHz/2.7 \sim 5.5 V$

- $-0\sim16MHz/4.5\sim5.5V$

- 工業用温度範囲

# 目次

|    | 序説····································                                                                    |     | 03 🌣        | 換ポート機能 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                 | 5/           |

|----|-----------------------------------------------------------------------------------------------------------|-----|-------------|-----------------------------------------------------------------------------|--------------|

|    |                                                                                                           |     | 0.0.        | O ホ <sup>°</sup> ート用レシ <sup>*</sup> スタ ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 69           |

|    | 特徴                                                                                                        |     |             |                                                                             |              |

| 1. | <b>説明 ······</b> 5                                                                                        | 10. | 8E % !      | タイマ/カウンタ0と非同期動作・・・・・・                                                       | • 63         |

|    | 1.1. ATtiny87とATtiny167間の違い ・・・・・・ 5                                                                      |     | 10.1.       | 寺徴 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                     | •• 63        |

|    | 1.2. デバイス説明 ····································                                                          |     |             | 既要 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                     |              |

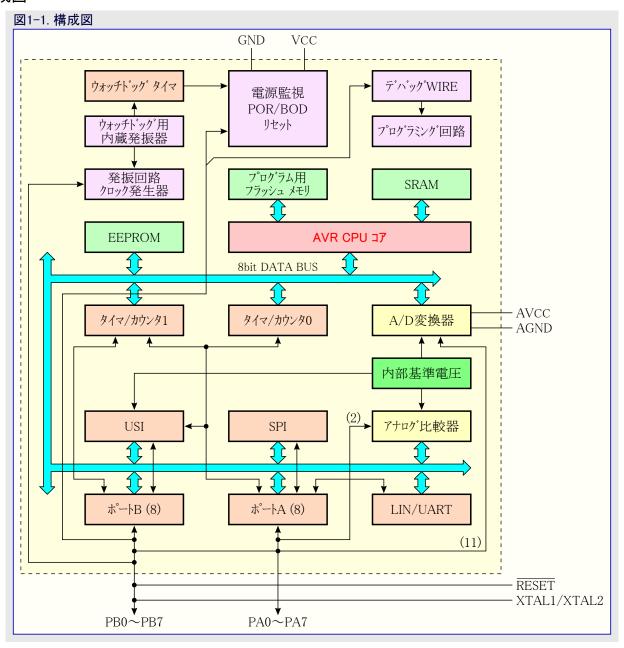

|    | 1.3. 構成図 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                              |     | 10.3.       | マイマ/カウンタのクロック ・・・・・・・・・                                                     | • • 64       |

|    |                                                                                                           |     |             | 計数器部 ••••••                                                                 |              |

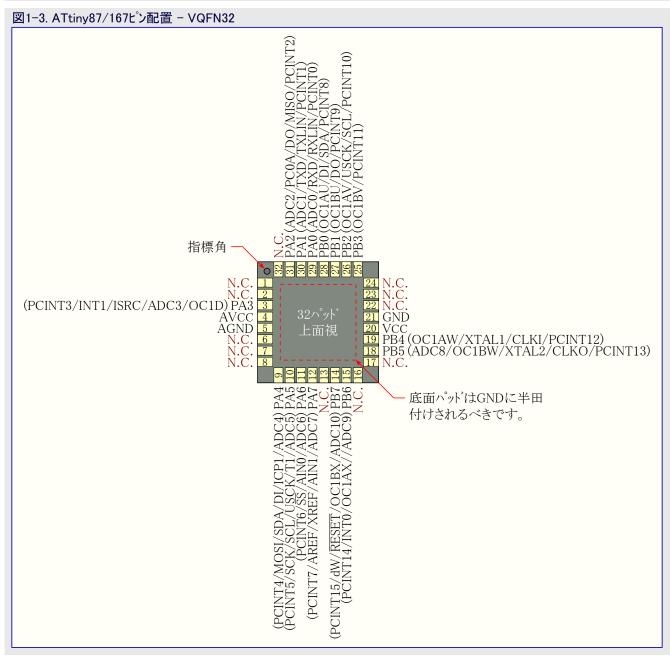

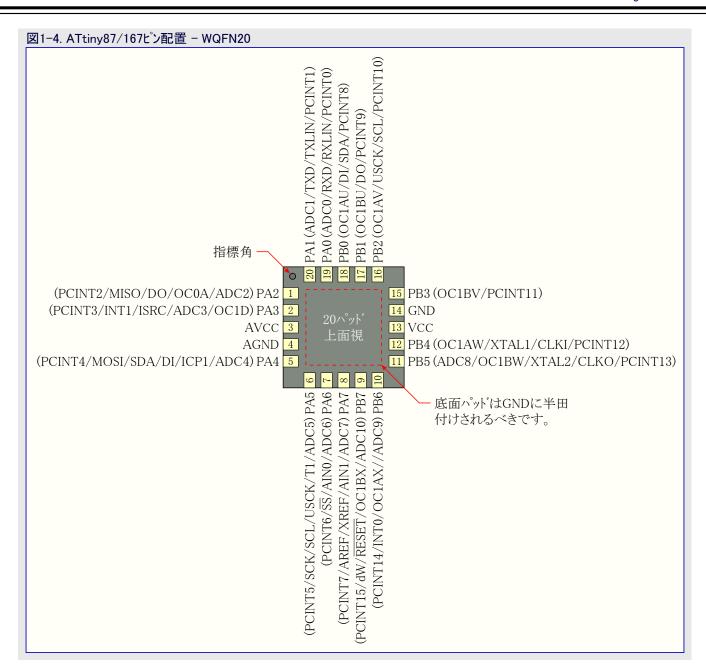

|    | <b>1.4.</b> ピン配置 · · · · · · · · · · · · 7                                                                |     |             | 比較出力部 ······                                                                |              |

|    | <b>1.5. ピン説明 ・・・・・・・・・・・・・・・</b> 9                                                                        |     |             | 七較山刃部 ····································                                  |              |

|    | 1.6. 資料 ・・・・・・・・・・・・・・・・・・・・9                                                                             |     |             |                                                                             |              |

|    | <b>1.7. コード例について ・・・・・・・・・・・</b> 9                                                                        |     | 10./.       | 動作種別 · · · · · · · · · · · · · · · · · · ·                                  | • • 67       |

|    | <b>1.8.</b> データ保持力 ・・・・・・・・・・・・・ 9                                                                        |     | 10.8.       | 1イマ/カウンタのタイミング・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                          | •• 70        |

|    | 1.9. お断り・・・・・・・・・・・・・・・・・・9                                                                               |     | 10.9.       | イイマ/カウンタ0の非同期動作 ・・・・・・・・・・                                                  | • 71         |

| ^  |                                                                                                           |     | 10.10. 5    | イイマ/カウンタ0の前置分周器 ・・・・・・・・・・                                                  | - 72         |

| 2. | AVR CPU 37 · · · · · 10                                                                                   |     | 10.11. 8    | ヒビット タイマ/カウンタ0用レジスタ ・・・・・・・・・                                               | · · 73       |

|    | <b>2.1</b> . 概要 ················· 10                                                                      | 11  |             | ウンタ1の前置分周器・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                              |              |

|    | 2.2. ALU (Arithmetic Logic Unit) · · · · · · 10                                                           | 11. |             |                                                                             |              |

|    | 2.3. ステータス レジスタ・・・・・・・・・・・・・11                                                                            |     | 11.1.       | 既要 •••••                                                                    | 77           |

|    | 2.4. 汎用レジスタ ファイル・・・・・・・・・・・ 12                                                                            |     | 11.2.       | イイマ/カウンタ前置分周器制御用レジスタ ・・・・・                                                  | · · 78       |

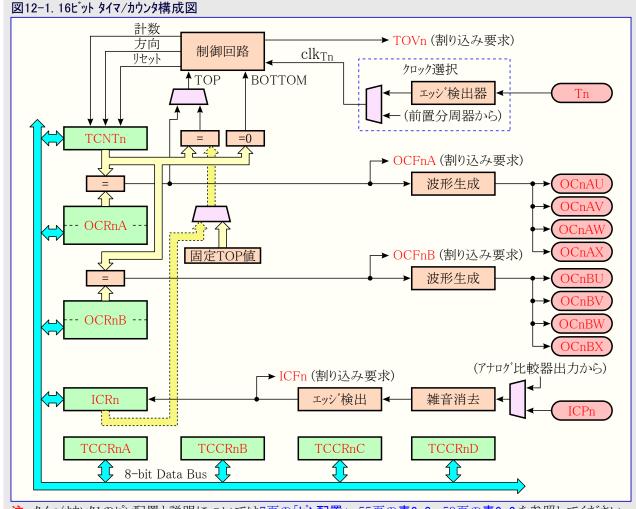

|    | <b>2.5.</b> スタック ホ°インタ ・・・・・・・・・ 12                                                                       | 12. | 16ピット       | タイマ/カウンタ1 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                              | <b>-</b> 79  |

|    | <b>2.6.</b> 命令実行タイミング・・・・・・・・・・ 13                                                                        |     |             | <del>す</del> 徴 ····································                         |              |

|    | 2.0. 叩刀夫1) パミング 13                                                                                        |     |             | ਾ।<br>既要 ••••••                                                             |              |

|    | 2.7. リセットと割り込みの扱い ・・・・・・・・ 13                                                                             |     |             |                                                                             |              |

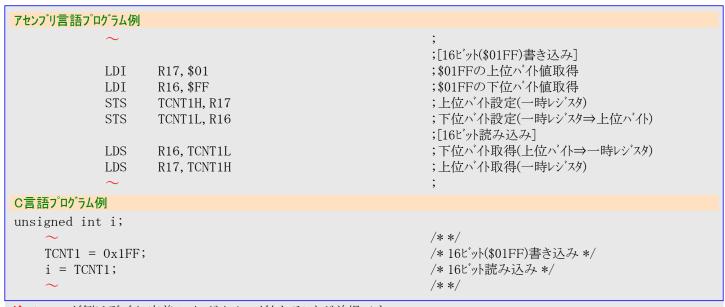

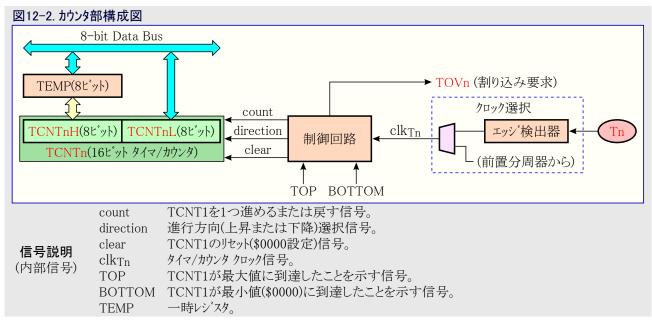

| 3. | AVRのメモリ · · · · · · · · 15                                                                                |     |             | 6ビット レジスタのアクセス · · · · · · · · · · · · · · · · · · ·                        |              |

|    | 3.1. 実装書き換え可能なプログラム用フラッシュ メモリ ・・・ 15                                                                      |     |             | パイマ/カウンタのクロック ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                           |              |

|    | <b>3.2.</b> データ用SRAMメモリ・・・・・・・・・・16                                                                       |     |             | <b>計数器部 •••••••</b>                                                         |              |

|    | 3.3. データ用EEPROMメモリ · · · · · · · · · · · · · · · · · · ·                                                  |     | 12.6.       | 甫獲入力部 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                  | • 84         |

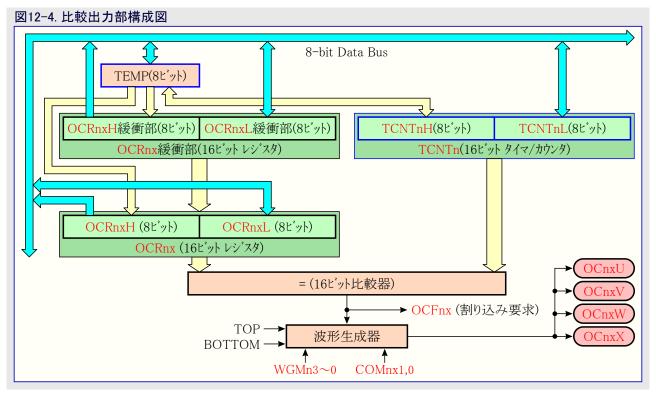

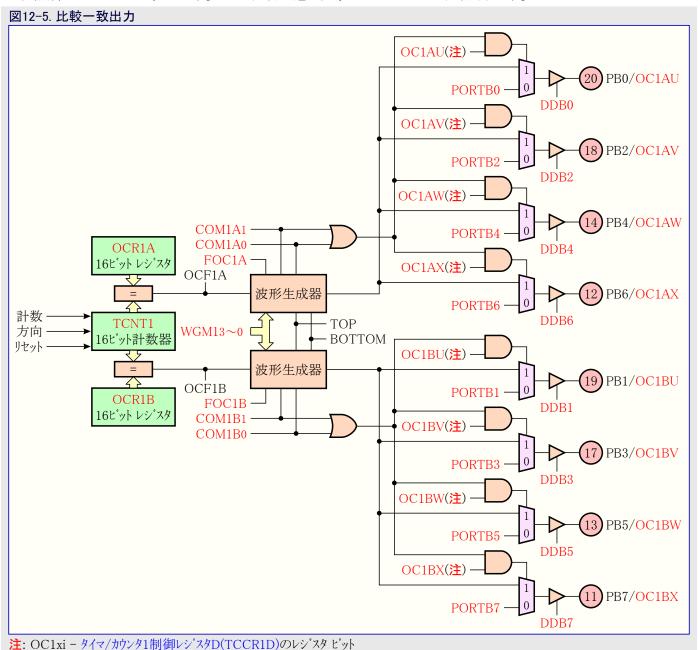

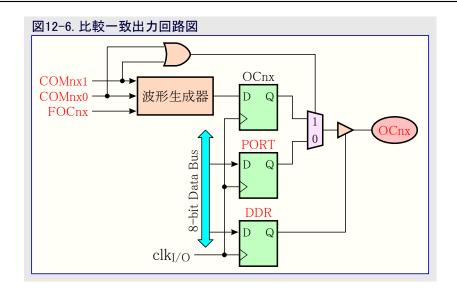

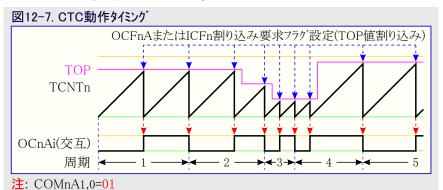

|    | 3.4. I/Oメモリ (レジスタ) · · · · · · 19                                                                         |     | 12.7.       | 七較出力部 ••••••                                                                | - 85         |

|    | 3.4. I/O>t/) (D/ X/)                                                                                      |     |             | - K - C - C - C - C - C - C - C - C - C                                     |              |

|    | 3.5. メモリ関係レシ、スタ・・・・・・・・・19                                                                                |     |             | 動作種別 ••••••                                                                 |              |

| 4. | システム クロックとクロック任意選択 ・・・・・・・ 21                                                                             |     |             | 97 F Y 全 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7                                |              |

|    | <b>4.1</b> . クロック系統とその配給・・・・・・・・・・・ 21                                                                    |     |             |                                                                             |              |

|    | <b>4.2.</b> クロック元 · · · · · · · · · · · · · · · · 22                                                      |     |             | 6ビット タイマ/カウンタ1 用レシ スタ ・・・・・・・・・                                             |              |

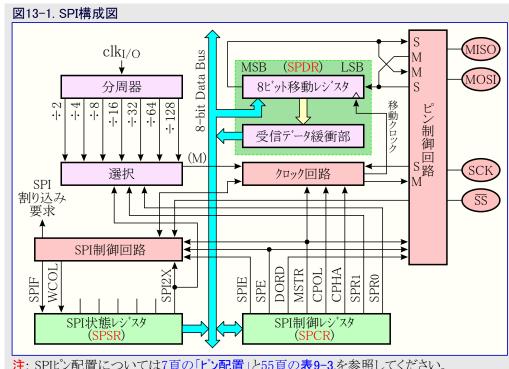

|    | 4.3. 動的クロック切り替え ······· 26                                                                                | 13. | 直列周         | 辺インターフェース (SPI) ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                        | • 99         |

|    | 4.4. システム クロック前置分周器 ・・・・・・・30                                                                             |     | 13.1.       | 寺徴                                                                          | 99           |

|    |                                                                                                           |     |             | ェート<br>SSピンの機能 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                         |              |

|    | 4.5. クロック関係レジスタ・・・・・・31                                                                                   |     |             | ···一夕転送形式 ······                                                            |              |

| 5. | 電力管理と休止形態 ・・・・・・ 34                                                                                       |     |             |                                                                             |              |

|    | 5.1. 休止形態種別                                                                                               | 14. | 多用远         | 直列インターフェース (USI) ・・・・・・・・・・                                                 | 104          |

|    | 5.2. 低電圧検出器(BOD)禁止 ····· 34                                                                               |     |             | 寺徴 •••••                                                                    |              |

|    | 5.3. <b>7</b> 仆 <b>* * * * * * * * * *</b>                                                                |     | 14.2.       | 既要 ••••••                                                                   | <b>•</b> 104 |

|    | 5.4. A/D変換雜音低減動作 ······· 35                                                                               |     | 14.3.       | 幾能説明 ••••••                                                                 | <b>1</b> 05  |

|    | 3.4. A/U変換維百低減期作 3.5.                                                                                     |     |             | JSIでの代替使用 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                              |              |

|    | <b>5.5</b> . パワーダウン動作 ・・・・・・・・・35                                                                         |     |             | JSI用レジスタ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                |              |

|    | <b>5.6.</b> パ <sup>°</sup> ワーセーフ <sup>*</sup> 動作 ・・・・・・・・・・35                                             |     |             |                                                                             |              |

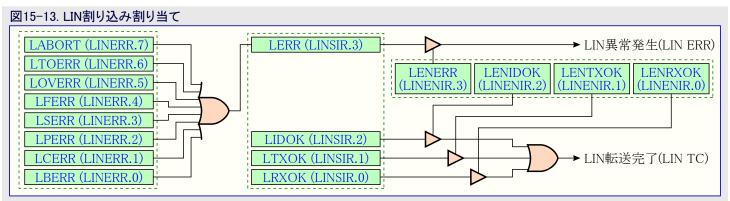

|    | 5.7. 電力削減 (レジスタ) ・・・・・・・・・・・ 35                                                                           | 15. |             | ART · · · · · · · · · · · · · · · · · · ·                                   |              |

|    | 5.8. 消費電力の最小化 ・・・・・・・・・ 36                                                                                |     |             | JN特徴 ·····                                                                  |              |

|    | 5.9. 電力管理用レジスタ・・・・・・・・37                                                                                  |     | 15.2. L     | JART特徴 ······                                                               | • 112        |

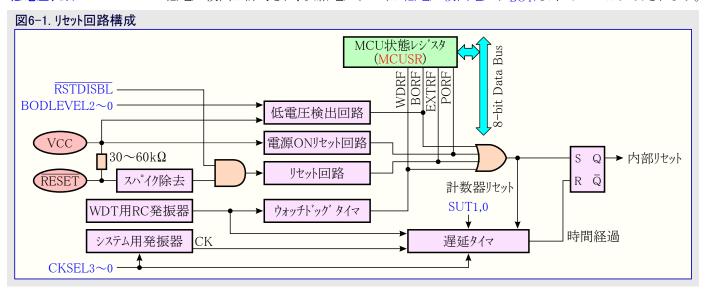

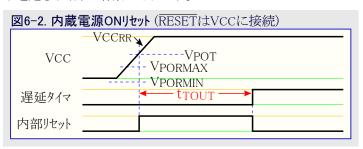

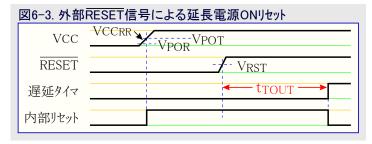

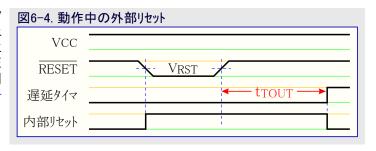

| 6  | システム制御とリセット・・・・・・・・・・・39                                                                                  |     | 15.3. L     | _IN規約 ······                                                                | • 112        |

| Ο. | <b>2人/ 4 前 加 こ グ ビッド</b> ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                             |     |             | IN/UART制御器 ······                                                           |              |

|    | <b>6.1.</b> リセット                                                                                          |     |             | IN/UART説明 ·······                                                           |              |

|    | 6.2. 内部基準電圧41                                                                                             |     |             | IN/UART用レジスタ ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                           |              |

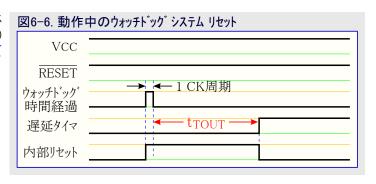

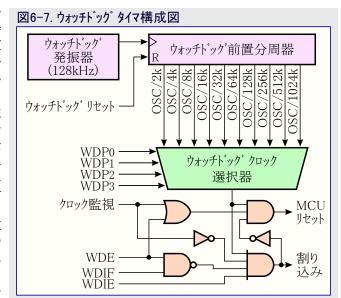

|    | <b>6.3</b> . ウォッチトック タイマ ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                              |     |             |                                                                             |              |

| 7  | <b>割り込み ・・・・・・・・・・・・・・・・</b> 45                                                                           | 16. | 電流源         | (ISRC) · · · · · · · · · · · · · · · · · · ·                                | 129          |

| ٠. | 7.1. ATtiny87/167の割り込みベクタ ・・・・・・・・・・・45                                                                   |     | 16.1.       | 寺徴                                                                          | • 129        |

|    | 7.1. ATTINY87/107の計り込みへが 13 14 15 15 15 14 15 15 15 14 15 15 15 16 17 17 17 17 17 17 17 17 17 17 17 17 17 |     | 16.2.       | ····<br>弋表的な応用 ······                                                       | 129          |

|    | <b>7.2.</b> ATtiny87でのプログラム構成設定 ······ 46                                                                 |     |             | <b>電流源用レジスタ ・・・・・・・・・・・・・・・・・・・・</b>                                        |              |

|    | 7.3. ATtiny167でのプログラム構成設定 ・・・・・・・・・・ 46                                                                   | 4-  |             |                                                                             |              |

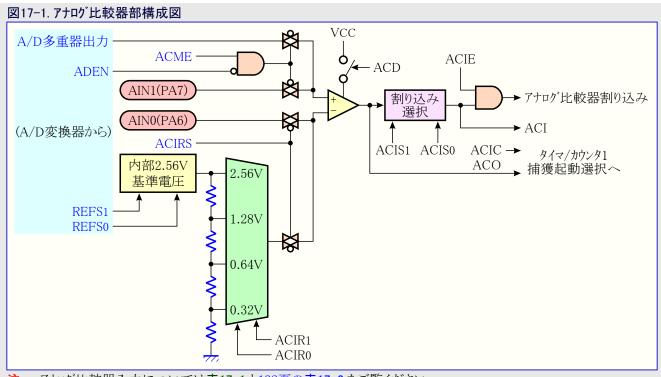

| 8. | <b>外部割り込み ・・・・・・・・・・・・・・・・</b> 47                                                                         | 1/. | <b>アナロク</b> | 比較器 (AC) · · · · · · · · · · · · · · · · · · ·                              | 131          |

|    | 8.1. 概要                                                                                                   |     |             | アナログ比較器入力・・・・・・・・・・・・・・・・・・                                                 |              |

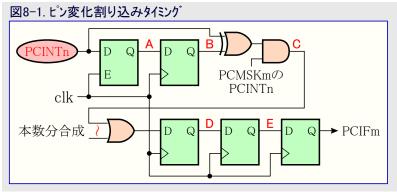

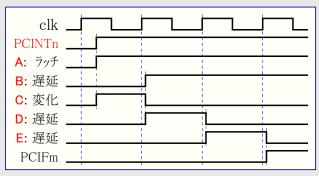

|    | 8.2. ピン変化割り込みタイミング・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                    |     | 17.2.       | ?ナログ比較器用レジスタ ・・・・・・・・・・・・・・                                                 | • 132        |

|    | 8.3. 外部割り込み用レジスタ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                      | 10  |             | 換器 (ADC) ······                                                             |              |

|    |                                                                                                           | 10. | ハ/レタ        | <del>                                      </del>                           | 104<br>104   |

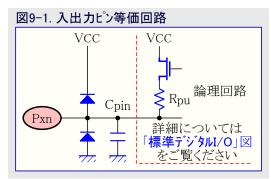

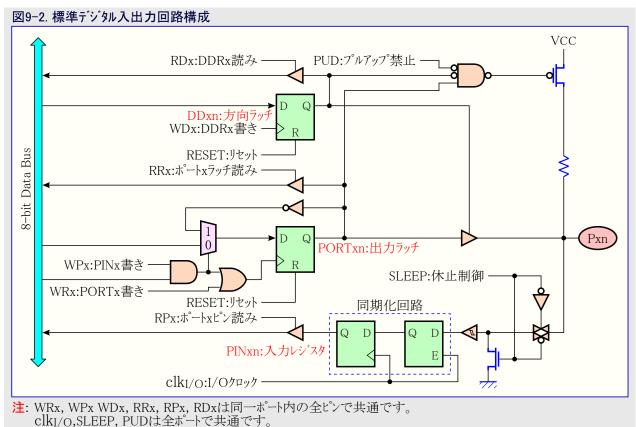

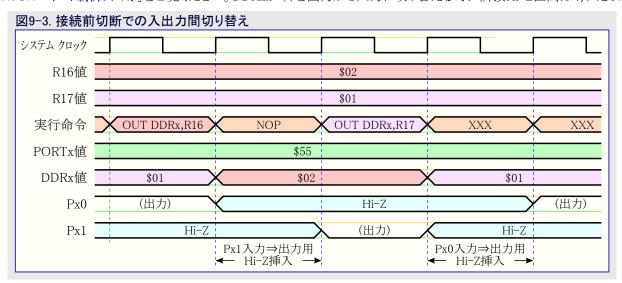

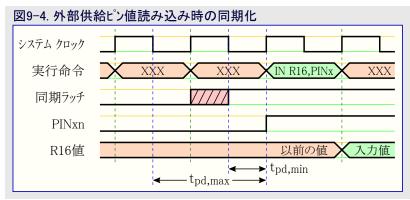

| 9. | 入出力ポート ······ 50                                                                                          |     |             |                                                                             |              |

|    | 9.1. 序説 ・・・・・・・・・・・ 50                                                                                    |     | 18.2.       | 既要 ·····                                                                    | • 134        |

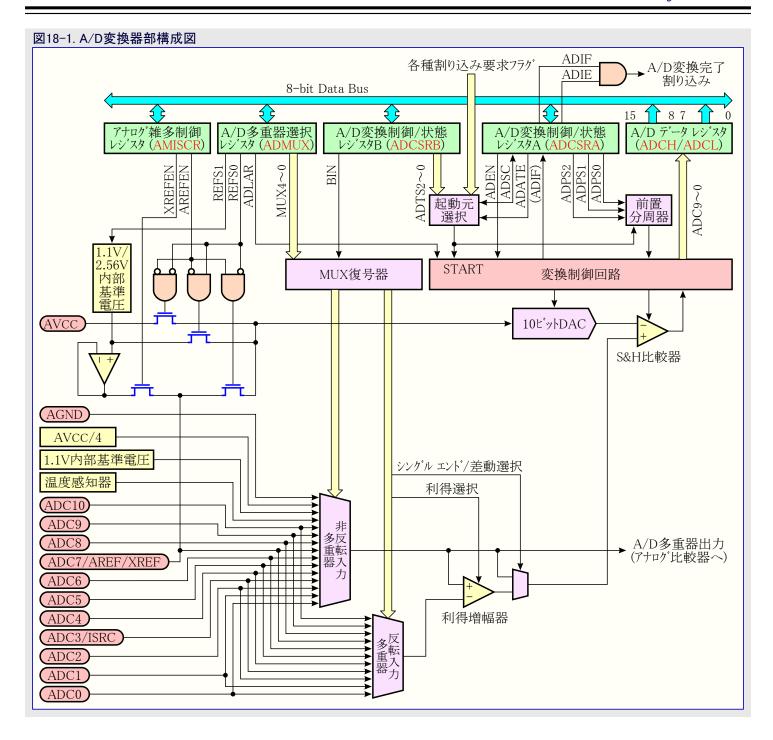

|    | 9.2. 標準デジタル入出力としてのポート ・・・・・・ 50                                                                           |     | 18.3.       | 操作 •••••                                                                    | • 136        |

|    |                                                                                                           |     |             |                                                                             |              |

|     | 18.4.          | 変換の開始・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                   | ••• 136            |

|-----|----------------|---------------------------------------------------------------------------------------------|--------------------|

|     | 18.5.          | 前置分周と変換タイミング・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                            | ••• 137            |

|     | 18.6.          | チャネル変更と基準電圧選択・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                           | ••• 138            |

|     | 18.7.          | 雑音低減機能                                                                                      | ••• 139            |

|     | 18.8.          | A/D変換の結果・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                | • • • 140          |

|     | 18.9.          | 温度測定                                                                                        | ••• 141            |

|     | 18.10.         | 内部基準電圧出力 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                               | ••• 141            |

|     | 18.11.         | A/D変換用レジスタ ····································                                             | ••• 142            |

| 19. |                | グWIRE内蔵デバッグ機能 ・・・・・・・                                                                       | •• 146             |

|     | 19.1.          | 特徴 · · · · · · · · · · · · · · · · · · ·                                                    | ••• 146            |

|     | 19.2.          | 概要 ••••••                                                                                   | • • • 146          |

|     | 19.3.          | 物理インターフェース・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                               | ••• 146            |

|     | 19.4.          | ソフトウェア中断点・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                               | ••• 146            |

|     | 19.5.          | テ゛ハ、゚ッグWIREの制限 · · · · · · · · · · · · · · · · · · ·                                        | ••• 146            |

|     | 19.6.          | テ <sup>・</sup> ハ・ック WIRE用レシ・スタ · · · · · · · · · · · · · · · · · · ·                        |                    |

| 20. |                | ュ メモリのフ <sup>°</sup> ロク <sup>*</sup> ラミンク <sup>*</sup> ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |                    |

|     | 20.1.          | フラッシュメモリの自己プログラミング・・・・・・・・                                                                  |                    |

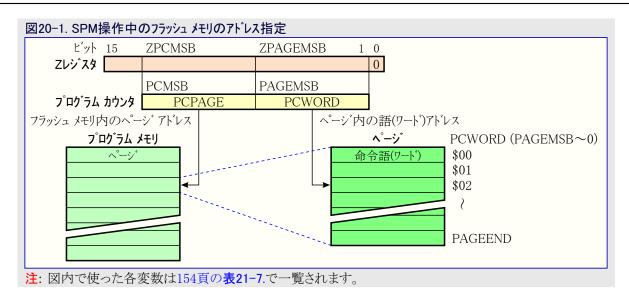

|     | 20.2.          | 自己プログラミングでのフラッシュアトレス指定・・                                                                    | ••• 147            |

| 21. |                | <sup>パ</sup> ロク゛ラミンク゛・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                   |                    |

|     | 21.1.          | プログラム メモリとデータ メモリ用施錠ビット・・・・                                                                 | ••• 152            |

|     | 21.2.          | ヒュース ビット ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                | ••• 153            |

|     | 21.3.          | <b>識祟バイ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・</b>                                             | ••• 154            |

|     | 21.4.          | 校正小仆                                                                                        | ••• 154            |

|     | 21.5.          | ページ <sup>*</sup> 容量・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                     | ••• 154            |

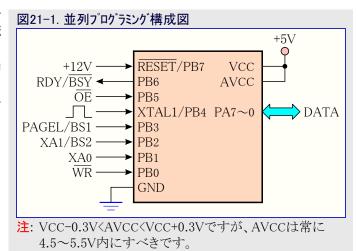

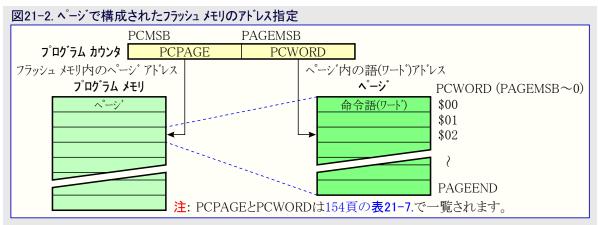

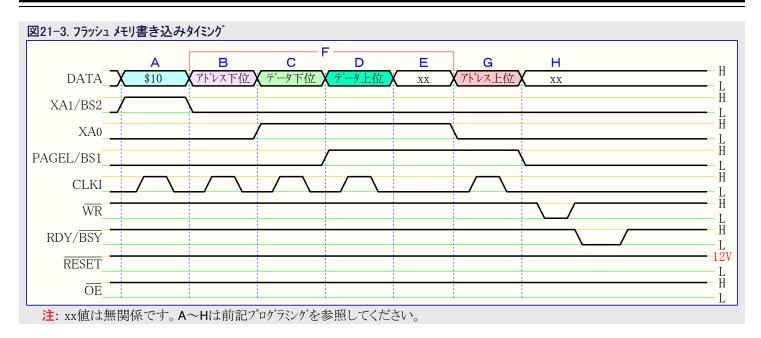

|     | 21.6.          | 並列プログラミング・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                               | 155                |

|     | 21.7.<br>21.8. | 並列プログラミング手順 ・・・・・・・・・・・・・・・・・<br>直列プログラミング ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・             | ••• 150            |

| 00  |                | 的特性・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                     | 101                |

| 22. |                | 例 行任 • • • • • • • • • • • • • • • • • •                                                    | • • 164            |

|     | 22.1.          | <b>DC特性・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・</b>                                             | ••• 164<br>164     |

|     | 22.2.<br>22.3. | 速度                                                                                          | ••• 164<br>••• 165 |

|     | 22.3.<br>22.4. | プロック特性 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                 | • • • 105          |

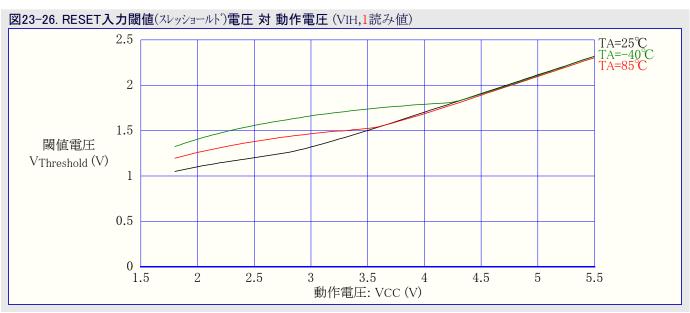

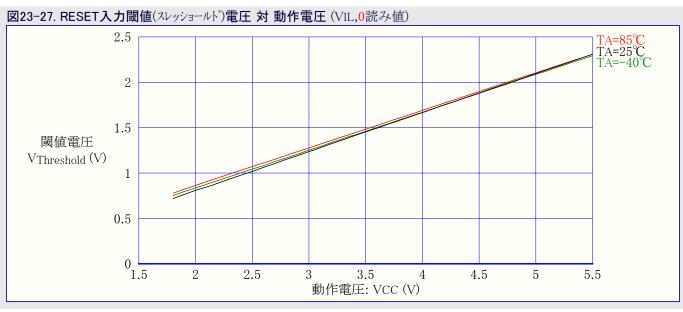

|     | 22.5.          | リセット特性 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                 | • • • 166          |

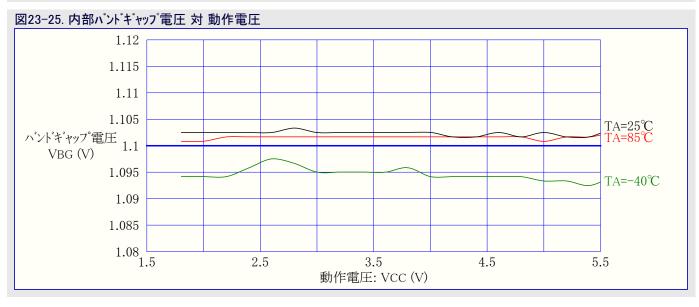

|     | 22.6.          | 内部基準電圧特性 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                               | • • • 166          |

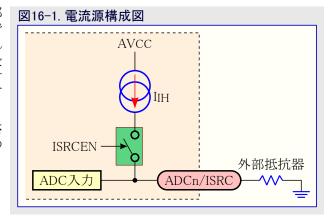

|     | 22.7.          | 電流源特性 ••••••                                                                                | 166                |

|     | 22.8.          | A/D変換器特性 · · · · · · · · · · · · · · · · · · ·                                              |                    |

|     |                |                                                                                             |                    |

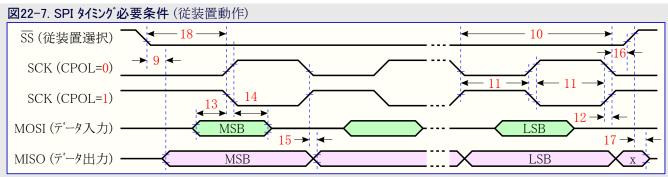

|     | 22.10.         | SPI タイミング 特性 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                            | ••• 170            |

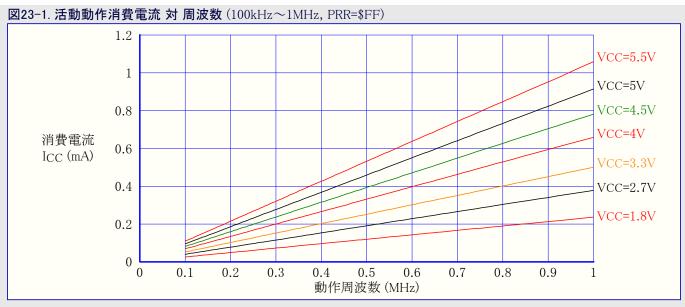

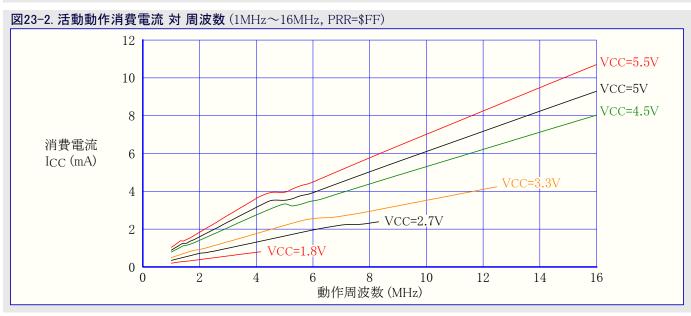

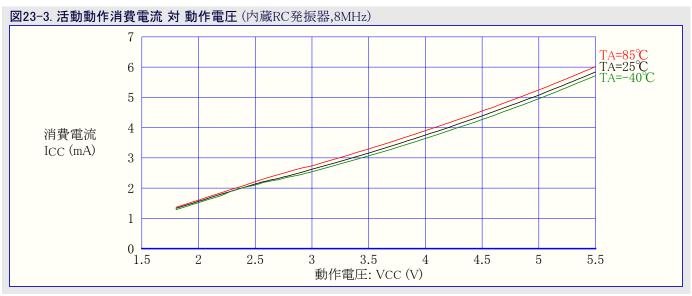

| 23. | 代表组            | 並列プログラミング特性 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                            | • • 171            |

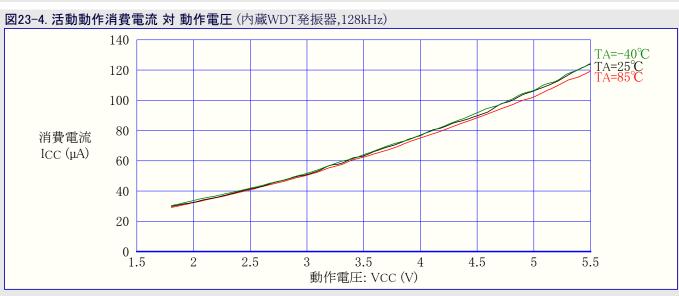

| 20. | 23.1.          | 活動動作消費電流                                                                                    | 171                |

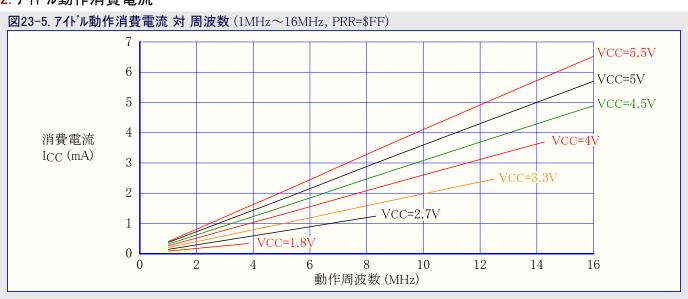

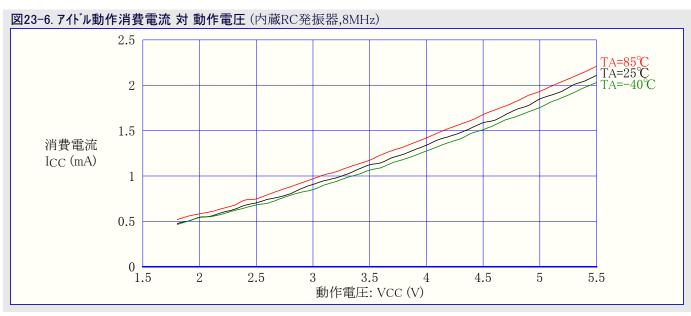

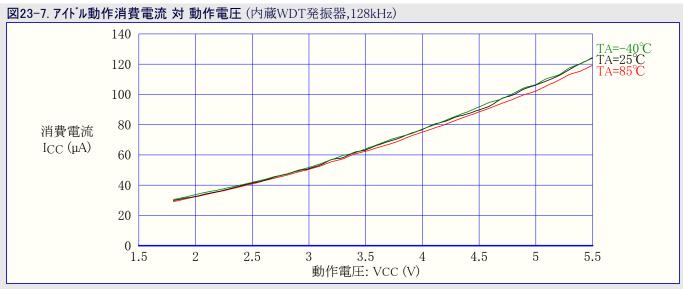

|     | 23.2.          | アイドル動作消費電流・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                              | ••• 172            |

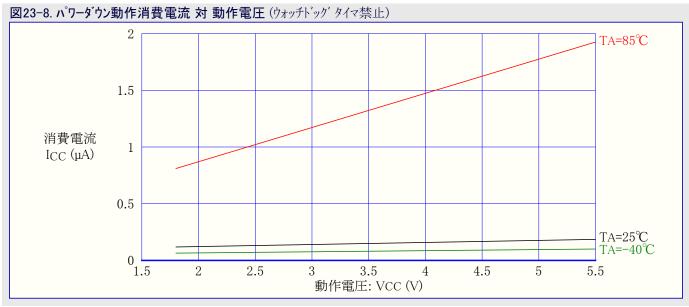

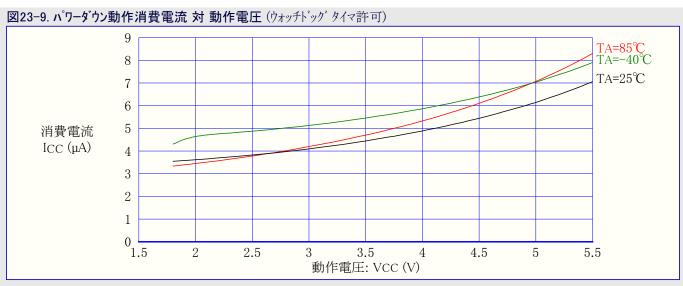

|     | 23.3.          | 入中五畄位却の消费(供給)重法                                                                             | 179                |

|     | 23.4.          | パロガギ 世帯の                                                                                    | • • • 174          |

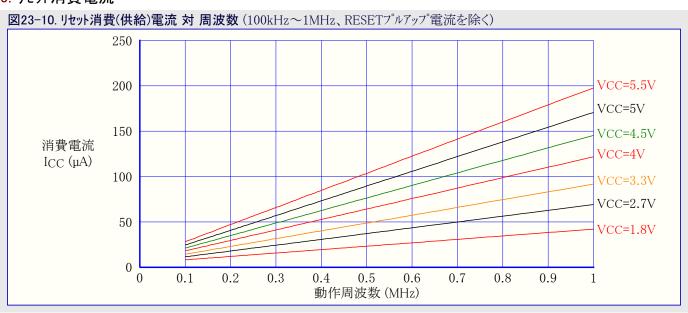

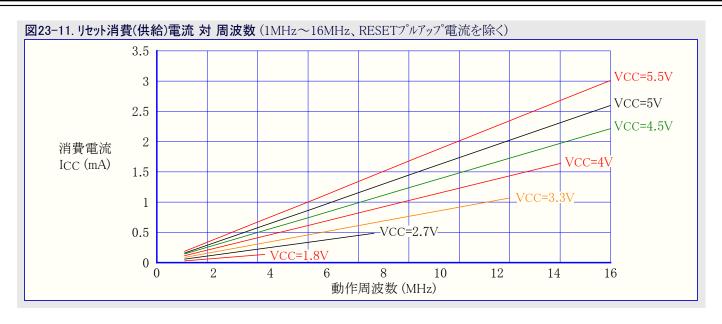

|     | 23.5.          | リセット消費電流・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                | ••• 174            |

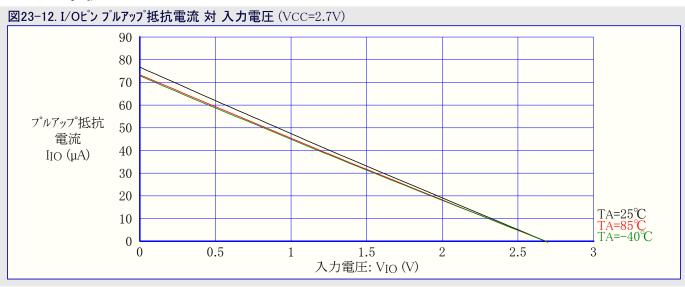

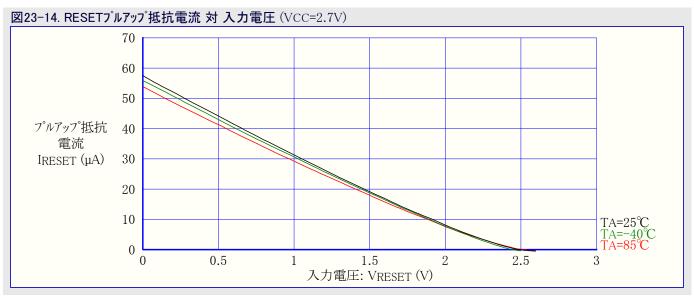

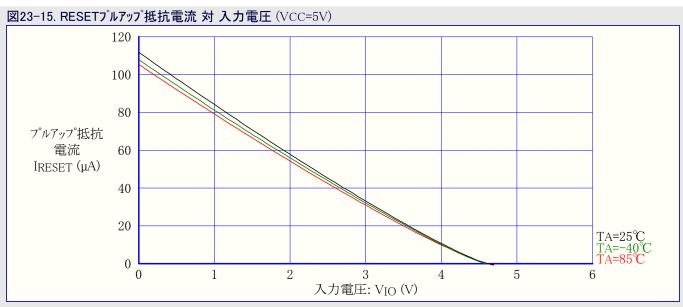

|     | 23.6.          | プルアップ 抵抗 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                | ••• 175            |

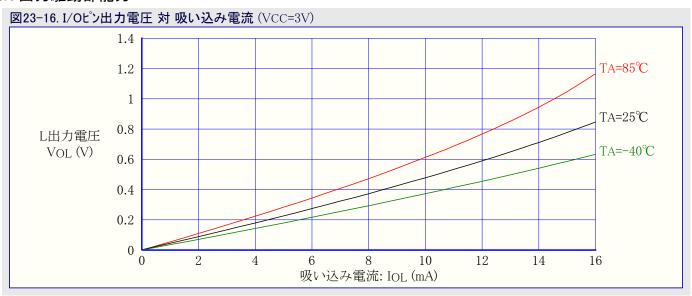

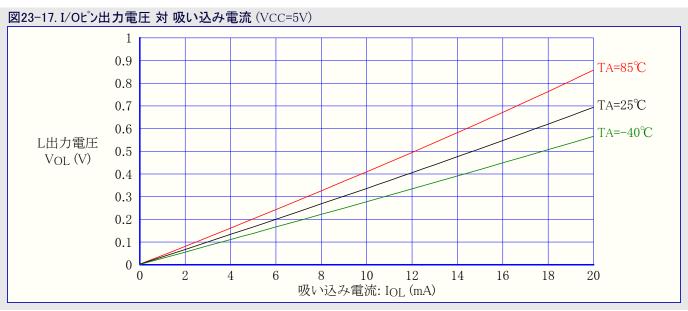

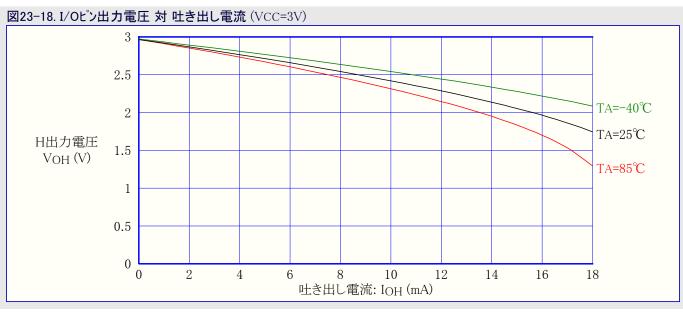

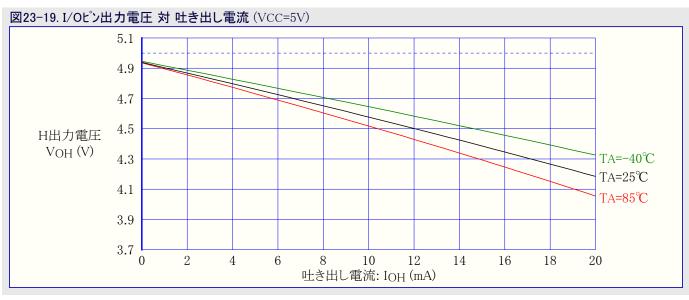

|     | 23.7.          | 出力駆動部能力                                                                                     | ••• 176            |

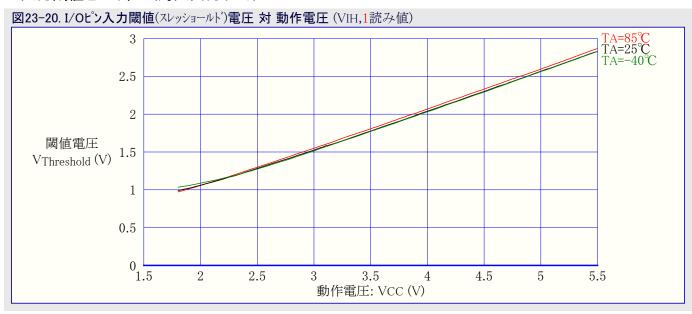

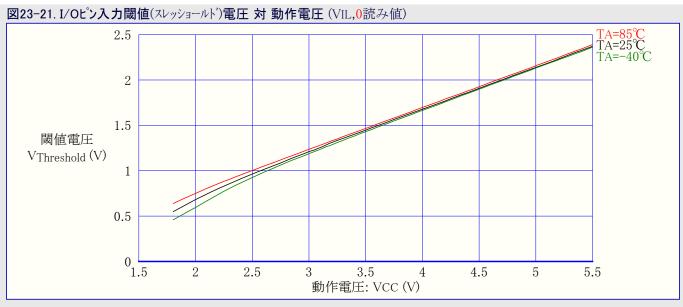

|     | 23.8.          | 入力閾値とヒステリシス(対入出力ポート)・・・・                                                                    | • • • 178          |

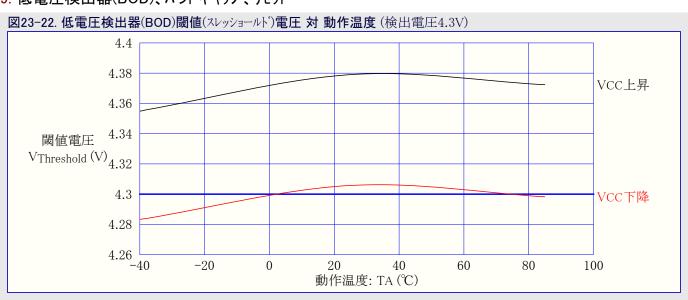

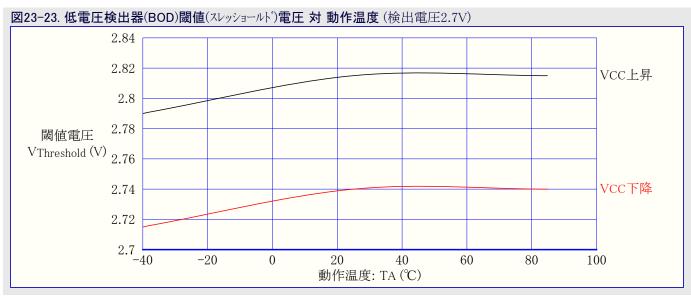

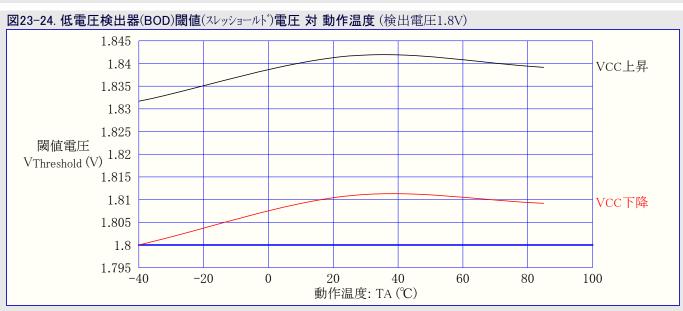

|     | 23.9.          | 低電圧検出器(BOD)、バンドギャップ、リセット                                                                    |                    |

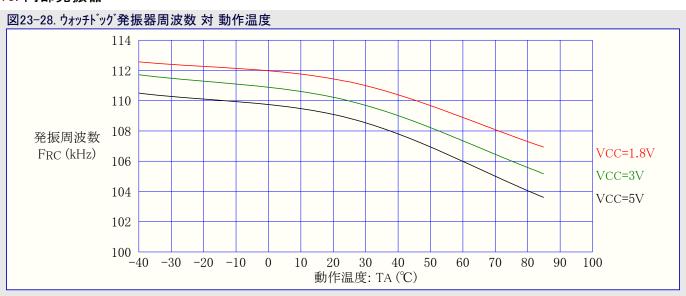

|     | 23.10.         | 内部発振器 ************************************                                                  | ••• 180            |

| 24. | レジスタ           | 7要約・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                                     | •• 182             |

| 25. | 命令             | - 女小。<br>要約 · · · · · · · · · · · · · · · · · · ·                                           | •• 186             |

| 26. | 注文性            | <br>書報                                                                                      | • 188              |

| 27. | 八四5            | <sub>骨報</sub><br>器情報 · · · · · · · · · · · · · · · · · · ·                                  | · · 189            |

|     | が四代            | 呀IP +以<br>書記・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                            | •• 193             |

| 28. | は こった          | <sup>育</sup> 報 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                         | 193                |

| 29. | ナーダン           | /ト以引復歴 ************************************                                                 | •• 194             |

# 1. 説明

# 1.1. ATtiny87とATtiny167間の違い

ATtiny87とATtiny168はハートウェアとソフトウェア互換です。それらは表1-1.で示されるようにメモリ容量だけが異なります。

| 表1-1. メモリ容量要約 |           |        |        |             |

|---------------|-----------|--------|--------|-------------|

| デバイス名         | フラッシュ メモリ | EEPROM | SRAM   | 割り込みベクタの大きさ |

| ATtiny87      | 8Kバイト     | 512バイト | 512バイト | 1命令語/ベクタ    |

| ATtiny167     | 16Kバイト    | 512バイト | 512バイト | 2命令語/ベクタ    |

# 1.2. デバイス説明

ATtiny87/167はAVR強化RISC構造に基づく低消費CMOS 8ビット マイクロ コントローラです。1周期で実行する強力な命令によって、ATtiny87/167は電力消費対処理速度の最適化をシステム設計者に許す、MHzあたり1MIPSに達する単位処理量を成し遂げます。

AVRコアは32個の汎用作業レジスタと豊富な命令群を兼ね備えています。32個の全レジスタはALU(Arithmetic Logic Unit)に直結され、レシ、スタ間命令は1クロック周期で実行されます。AVR構造は現状のCISC型マイクロコントローラに対して10倍以上の単位処理量向上効果があります。

ATtiny87/167は次の特徴、8/16Kハ・什の実装書き換え可能なフラッシュメモリと512ハ・イトのEEPROM、512ハ・イトのSRAM、16本の汎用入出力線、32個の汎用レジスタ、比較動作やPWMを含む柔軟性のある1つ8ビット タイマ/カウンタと1つの16ビット タイマ/カウンタ、多用途直列インターフェース(USI)、LIN制御器、内部及び外部の割り込み、11チャネルの10ビットA/D変換器、設定変更可能な内部発振器付きウォッチドッグタイマ、ソフトウェアで選択できる4つの低消費動作機能を提供します。アイドル動作では動作を停止しますが、SRAM、タイマ/カウンタ、A/D変換器、アナログ・比較器、割り込み機能は有効で動作を継続します。パワーダウン動作ではレジスタの内容は保護されますが、以降のハート・ウェアリセットか外部割り込みまで他の全機能を禁止(無効)にします。A/D変換雑音低減動作はA/D変換中の切り替え雑音を最小とために、A/D変換器を除く周辺機能とCPUを停止します。

本デ、バイスはMicrochipの高密度不揮発性メモリ技術を使って製造されています。内蔵の実装書き換え(ISP)可能なプログラム用フラッシュメモリは規定の不揮発性メモリ書き込み器、SPI直列インターフェース経由、AVRコア上ブートプログラムの実行によって再書き込みができます。 ブートプログラムはフラッシュメモリ内の応用プログラムの読み込みにどのインターフェースでも使えます。モノリシックチップ上の自己実装書き換え可能なフラッシュメモリと、8ビットRISC型CPUの組み合わせによるMicrochip ATtiny87/167は多くの組み込み制御の応用に対して高度な柔軟性と対費用効果をもたらす強力なマイクロコントローラです。

ATtiny87/167 AVRはCコンパイラ、マクロ アセンフ゛ラ、プロク゛ラム テ゛ハ゛ッカ゛/シミュレータ、インサーキット エミュレータ、評価キットを含む専用のプロク゛ラム及びシステム開発ツールで支援されます。

# 1.3. 構成図

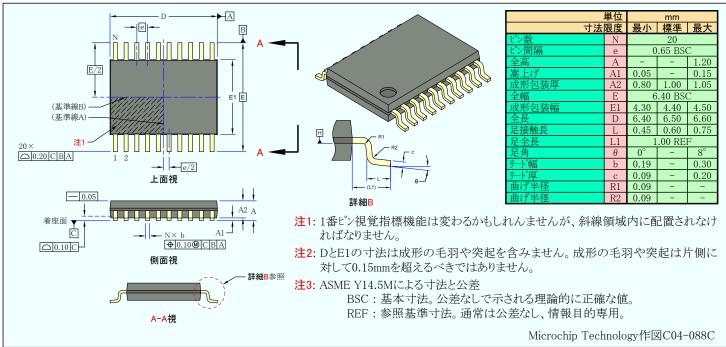

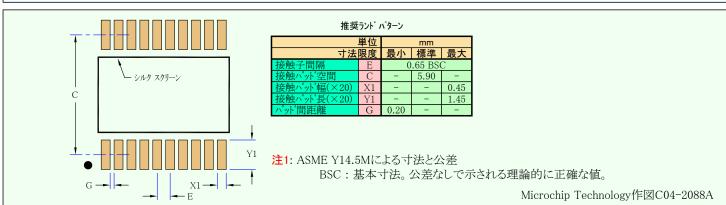

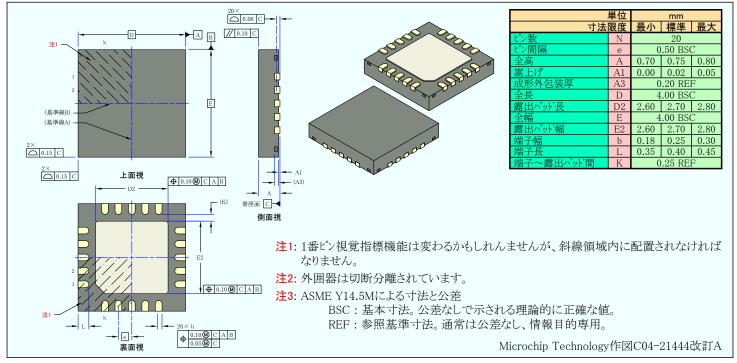

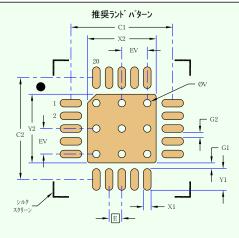

# 1.4. ピン配置

#

#### 1.5. ピン説明

#### 1.5.1. VCC

電源ピン。

#### 1.5.2. GND

接地ピン。

#### 1.5.3. AVCC

アナログ電源ピン。

#### 1.5.4. AGND

アナログ接地ピン。

#### 1.5.5. PA7~PA0 (ポートA)

ポートAは(ビット単位で選択される)内蔵プルアップ抵抗付きの8ビット双方向入出力ポートです。ポートA出力緩衝部は共に高い吐き出し/吸い込み能力の対称駆動特性です。入力の時にプルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートAピンには吐き出し電流が流れます。 リセット条件が有効になると、クロックが走行していなくても、ポートAピンはHi-Zにされます。

ポートAは55頁の「9.3.3. ポートAの交換機能」で一覧されるようにATtiny87/167の様々な特殊機能も扱います。

#### 1.5.6. PB7~PB0 (ホ°ートB)

ポートBは(ビット単位で選択される)内蔵プルアップ抵抗付きの8ビット双方向入出力ポートです。ポートB出力緩衝部は共に高い吐き出し/吸い込み能力の対称駆動特性です。入力の時にプルアップ抵抗が有効の場合、外部的にLowへ引き込まれたポートBピンには吐き出し電流が流れます。 リセット条件が有効になると、クロックが走行していなくても、ポートBピンはHi-Zにされます。

ポートBは59頁の「9.3.4. ポートBの交換機能」で一覧されるようにATtiny87/167の様々な特殊機能も扱います。

#### 1.6. 資料

包括的なデータシート、応用記述、開発ツール群はhttps://www.microchip.comでのダウンロートで利用可能です。

#### 1.7. コード例について

この資料はデバイスの様々な部分の使用法を手短に示す簡単なコート・例を含みます。これらのコート・例はアセンブルまたはコンパイルに先立ってデバイス定義へッタ・ファイルがインクルートされると仮定します。全てのCコンパイラ製造業者がヘッタ・ファイル内にビット定義を含めるとは限らず、またCでの割り込みの扱いがコンパイラに依存することに注意してください。より多くの詳細についてはCコンパイラの資料で確認してください。

# 1.8. データ保持力

信頼性証明結果はデータ保持誤り率の反映を示し、20年以上/85℃または100年以上/25℃で1PPMよりずっと小さな値です。

#### 1.9. お断り

本データシート内で示された代表値はシミュレーションと同じ製法技術で製造された他のAVRマイクロコントローラの特性に基いています。最小と最大の値はデバイスの特性が記載された後に利用可能になります。

#### 2. AVR CPU J7

#### 2.1. 概要

ここでは一般的なAVRコア構造について説明します。このCPUコアの主な機能は正しいプログラム実行を保証することです。従ってCPU はメモリ アクセス、計算実行、周辺制御、割り込み操作ができなければなりません。

最大効率と平行処理のため、AVRはプログラムとデータに対してメモリとバスを分離するハーバード構造を使います。プログラムメモリ内の命令は単一段のパイプラインで実行されます。1命令の実行中に次の命令がプログラムメモリから事前取得されます。この概念は全部のクロック周期で命令実行を可能にします。プログラムメモリは実装書き換え可能なフラッシュメモリです。高速レジスタファイルは1クロック周期アクセスの32個の8ビット長汎用レジスタを含みます。これは1クロック周期ALU(Arithmetic Logic Unit)操作を許します。代表的なALU操作では2つのオペランドがレジスタファイルからの出力で、1クロック周期内でその操作が実行され、その結果がレジスタファイルに書き戻されます。

32個中の6つのレシ、スタは効率的なアトンス計算ができるデータ空間アトンス指定用に3つの16ビット長間接アトンスポインタ用レシ、スタとして使われます。これらアトンスポインタの1つはプログラム用フラッシュメモリ内の定数表参照用アトンスポインタとしても使えます。これら16ビット長付加機能レシ、スタはX,Y,Zレシ、スタで、本項内で後述されます。

ALUはレジスタ間またはレジスタと定数間の算術及び論理操作を支援します。単一レジスタ操作もALUで実行できます。算術演算操作後、操作結果についての情報を反映するためにステータスレジスタ(SREG)が更新されます。

プログラムの流れは条件/無条件分岐や呼び出し命令によって提供され、全アドレス空間を直接アドレス指定できます。 殆どのAVR命令は16ビット語(ワード)形式です。全てのプログラム メモリのアドレスは(<mark>訳注</mark>:定数のみを除き)16または32ビット長命令を含みます。

図2-1. AVR構造構成図 8-bit Data Bus プログラム 状態/制御 割り込み部 カウンタ ウォッチト゛ック プログラム用  $32\times8$ フラッシュ メモリ 間 汎用レジスタ A/D変換器 命令レジスタ ALU 比較器 ノドレス指 直 接(Dir 命令復号器 ◆ 周辺機能部 1 データ用 SRAM → 周辺機能部 2 制御信号線 **EEPROM** 汎用入出力部 ◆ 周辺機能部 n

割り込みやサブルーチン呼び出し中、戻りアトレスを示すプログラム カウンタ(PC)はスタックに保存されます。スタックは一般的なデータ用SRAM上に実際には割り当てられ、従ってスタック容量は全SRAM容量とSRAM使用量でのみ制限されます。全ての使用者プログラムはリセット処理ルーチンで(サブルーチン呼び出しや割り込みが実行される前に)、スタック ホーインタ(SP)を初期化しなければなりません。SPはI/O空間で読み書きアクセスが可能です。データ用SRAMはAVR構造で支援される5つの異なるアトレス指定種別を通して容易にアクセスできます。

AVR構造に於けるメモリ空間は全て直線的な普通のメモリ配置です。

柔軟な割り込み部にはI/O空間の各制御レシ、スタとステータスレシ、スタ(SREG)の特別な全割り込み許可(I)ビットがあります。全ての割り込みは割り込みへ、クタ表に個別の割り込みへ、クタを持ちます。割り込みには割り込みへ、クタ表の位置に従う優先順があります。下位側割り込みへ、クタアドレスが高い優先順位です。

I/Oメモリ空間は制御レジスタ、SPI、他のI/O機能としてCPU周辺機能用の64アドレスを含みます。I/Oメモリは直接またはレジスタ ファイルの次のデータ空間位置\$20~\$5Fとしてアクセスできます。加えてATtiny87/167にはST/STS/STDとLD/LDS/LDD命令だけ使えるSRAM内の\$60~\$FFに拡張I/O空間があります(訳注:共通性から本行追加)。

#### **2.2. ALU** (Arithmetic Logic Unit)

高性能なAVRのALUは32個の全汎用レジスタとの直結で動作します。汎用レジスタ間または汎用レジスタと即値間の演算操作は単一クロック周期内で実行されます。ALU操作は算術演算、論理演算、ビット操作の3つの主な種類に大別されます。符号付きと符号なし両方の乗算と固定小数点形式を支援する乗算器(乗算命令)も提供する構造の実装(製品)もあります。詳細記述については「命令要約」章をご覧ください。

#### 2.3. ステータス レジスタ

ステータス レジスタは最も直前に実行した演算命令の結果についての情報を含みます。この情報は条件処理を行うためのプログラムの流れ変更に使えます。ステータス レジスタは「命令一式参考書」で詳述したように、全てのALU操作後、更新されることに注目してください。これは多くの場合でそれ用の比較命令使用の必要をなくし、高速でより少ないコードに帰着します。

ステータス レジスタは割り込み処理ルーチン移行時の保存と割り込みからの復帰時の回復(復帰)が自動的に行われません。これはソフトウェアによって扱われなければなりません。

#### 2.3.1. SREG - ステータス レシ スタ (Status Register)

AVRのステータス レジスタ(SREG)は次のように定義されます。

| ピット         | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _    |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| \$3F (\$5F) | I   | Т   | Н   | S   | V   | N   | Z   | С   | SREG |

| Read/Write  | R/W |      |

| 初期値         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

#### ● ビット7 - I: 全割り込み許可 (Global Interrupt Enable)

全割り込み許可ビットは割り込みが許可されるために設定(1)されなければなりません。その時に個別割り込み許可制御は独立した制御レジスタで行われます。全割り込み許可ビットが解除(0)されると、個別割り込み許可設定に拘らず、どの割り込みも許可されません。I ビットは割り込みが起こった後にハードウェアによって解除(0)され、後続の割り込みを許可するために、RETI命令によって設定(1)されます。Iビットは「命令一式参考書」で記述されるようにSEIやCLI命令で応用(プログラム)によって設定(1)や解除(0)もできます。

#### ビット6 - T:ビット変数 (Bit Copy Storage)

ビット複写命令、BLD(Bit LoaD)とBST(Bit STore)は操作したビットの転送元または転送先として、このTビットを使います。レジスタ ファイルのレジスタからのビットはBST命令によってTに複写でき、TのビットはBLD命令によってレジスタ ファイルのレジスタ内のビットに複写できます。

#### • ビット5 - H: ハーフキャリー フラク (Half Carry Flag)

ハーフキャリー(H)フラグはいくつかの算術操作でのハーフキャリーを示します。ハーフキャリーはBCD演算に有用です。詳細情報については「命令要約」記述をご覧ください。

#### ● ビット4 - S: 符号 (Sign Bit, S= N Ex-OR V)

Sフラグは常に負(N)フラグと2の補数溢れ(V)フラグの排他的論理和です。詳細情報については「命令要約」記述をご覧ください。

#### ビット3 - V: 2の補数溢れフラク (2's Complement Overflow Flag)

2の補数溢れ(V)フラグは2の補数算術演算を支援します。詳細情報については「命令要約」記述をご覧ください。

#### ヒット2 - N: 負フラク (Negative Flag)

負(N)フラグは算術及び論理操作での負の結果(MSB=1)を示します。詳細情報については「命令要約」記述をご覧ください。

#### ビット1 - Z: セロフラク (Zero Flag)

ゼロ(Z)フラグは算術及び論理操作でのゼロ(0)の結果を示します。詳細情報については「命令要約」記述をご覧ください。

#### ヒット0 − C : キャリー フラク (Carry Flag)

キャリー(C)フラク゛は算術及び論理操作でのキャリー(またはボロー)を示します。詳細情報については「**命令要約**」記述をご覧ください。

# 2.4. 汎用レジスタファイル

このレジスタファイルはAVRの増強したRISC命令群用に最適化されています。必要な効率と柔軟性を達成するために、次の入出力機構がレジスタファイルによって支援されます。

- ・1つの8ビット出力オペラントと1つの8ビットの結果入力

- ・2つの8ビット出力オペランドと1つの8ビットの結果入力

- ・2つの8ビット出力オペラントと1つの16ビットの結果入力

- ・1つの16ビット出力オペラントと1つの16ビットの結果入力

図2-2.はCPU内の32個の汎用作業レジスタの構造を示します。

レジスタファイルを操作する殆どの命令は全てのレジスタに直接アクセスし、 それらの殆どは単一周期命令です。

図2-2.で示されるように各レジスタは使用者データ空間の最初の32位置へ直接配置することで、それらはデータメモリアドレスも割り当てられます。例え物理的にSRAM位置として実装されていなくても、X,Y,Zレジスタ(ポインタ)がレジスタファイル内のどのレジスタの指示にも設定できるように、このメモリ構成は非常に柔軟なレジスタのアクセスを提供します。

| 図2-2. AVR CPU 汎用レシ、スタ構成図 |        |                        |  |  |  |  |  |  |

|--------------------------|--------|------------------------|--|--|--|--|--|--|

| 7                        | 0 アドレス | 特殊機能                   |  |  |  |  |  |  |

| R0                       | \$00   |                        |  |  |  |  |  |  |

| R1                       | \$01   |                        |  |  |  |  |  |  |

| R2                       | \$02   |                        |  |  |  |  |  |  |

| }                        |        |                        |  |  |  |  |  |  |

| R13                      | \$0D   |                        |  |  |  |  |  |  |

| R14                      | \$0E   |                        |  |  |  |  |  |  |

| R15                      | \$0F   |                        |  |  |  |  |  |  |

| R16                      | \$10   |                        |  |  |  |  |  |  |

| R17                      | \$11   |                        |  |  |  |  |  |  |

| ?                        |        |                        |  |  |  |  |  |  |

| R26                      | \$1A   | VI 3/74 下位バイ           |  |  |  |  |  |  |

| R27                      | \$1B   | Xレジスタ - 下位バイ・<br>上位バイト |  |  |  |  |  |  |

| R28                      | \$1C   | Yレジスター 下位バイト           |  |  |  |  |  |  |

| R29                      | \$1D   | 上位ハイト                  |  |  |  |  |  |  |

| R30                      | \$1E   | フレジスタ 下位バイト            |  |  |  |  |  |  |

| R31                      | \$1F   | 上位バイト                  |  |  |  |  |  |  |

# 2.4.1. XV9 A9. YV9 A9. ZV9 A9.

R26~R31レシ、スタには通常用途の使用にいくつかの追加機能があります。これらのレシ、スタはデータ空間の間接アト、レス指定用の16ビットアト、レスポインタです。3つのX,Y,Z間接アト、レスレシ、スタは**図2-3**.で記載したように定義されます。

種々のアドレス指定種別で、これらのアドレス レジスタは固定変位、自動増加、自動減少としての機能を持ちます(詳細については「命令ー式参考書」をご覧ください)。

| 図2-3. X,Y,Zレジスタ構成図   |    |            |     |            |   |  |  |  |

|----------------------|----|------------|-----|------------|---|--|--|--|

|                      | 15 | XH (上位)    |     | XL (下位)    | 0 |  |  |  |

| X レジスタ               | 7  | R27 (\$1B) | 0 7 | R26 (\$1A) | 0 |  |  |  |

|                      | 15 | YH (上位)    |     | YL (下位)    | 0 |  |  |  |

| Y レジスタ               | 7  | R29 (\$1D) | 0 7 | R28 (\$1C) | 0 |  |  |  |

|                      | 15 | ZH (上位)    |     | ZL (下位)    | 0 |  |  |  |

| Z レシ <sup>*</sup> スタ | 7  | R31 (\$1F) | 0 7 | R30 (\$1E) | 0 |  |  |  |

|                      |    |            |     |            |   |  |  |  |

#### 2.5. スタック ホ<sup>°</sup>インタ

スタックは主に一時データの保存、局所変数の保存、割り込みとサブルーチン呼び出し後の戻りアトレスの保存に使われます。スタック ポインタ レジスタは常にこのスタックの先頭(<mark>訳注</mark>:次に使われるべき位置)を指し示します。スタックが高位メモリから低位メモリへ伸長するように実行されることに注意してください。これはスタックへのPUSH命令はスタック ポインタを減少するという意味です。

スタック ポインタはサブルーチンや割り込みのスタックが配置されるデータSRAMのスタック領域を指し示します。データSRAM内のスタック空間はサブルーチン呼び出しの実行や割り込みの許可の何れにも先立って、プログラムによって定義されなければなりません。スタック ポインタは \$60以上を指示するように設定しなければなりません。スタック ポインタは PUSH命令でデータがスタックに格納されると-1され、サブルーチン呼び出しや割り込みで戻りアトレスがスタックに格納されると-2されます。スタック ポインタは POP命令でデータがスタックから引き出されると+1され、サブルーチンからの復帰(RET)命令や割り込みからの復帰(RETI)命令でアトレスがスタックから引き出されると+2されます。

AVRのスタック ポインタはI/O空間内の2つの8ビット レジスタとして実装されます。実際に使われるビット数は(そのデ゙バイス)実装に依存します。SPLだけが必要とされる程に小さいAVR構造の実装(デ゙バイス)のデータ空間もあることに注意してください。その場合、SPHレジスタは存在しません。

## 2.5.1. SPH,SPL (SP) - スタック ポインタ (Stack Pointer)

(**訳補**) 内蔵SRAMは512パイト(\$0100~\$02FF)ですので、ISRAM endは\$02FF(0000 0010 1111 1111)です。

# 2.6. 命令実行タイミング

本項は命令実行の一般的なアクセスタイミングの概念を記述します。AVR CPUはチップ(デバイス)用に選択したクロック元から直接的に生成したCPUクロック(clkCPU)によって駆動されます。内部クロック分周は使われません。

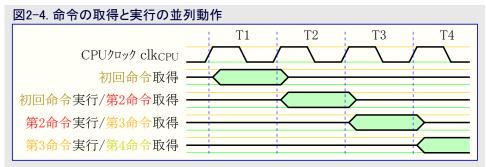

図2-4.はハーハート、構造と高速アクセスレジスタファイルの概念によって可能とされる並列の命令取得と命令実行を示します。これは機能対費用、機能対クロック、機能対電源部に関する好結果と対応するMHzあたり1MIPSを達成するための基本的なパイプ・ラインの概念です。

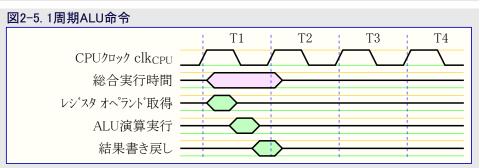

図2-5.はレジスタファイルに対する内部タイシングの概念を示します。単一クロック周期で2つのレジスタオペラントを使うALU操作が実行され、その結果が転送先レジスタへ書き戻されます。

# 2.7. リセットと割り込みの扱い

AVRは多くの異なる割り込み元を提供します。これらの割り込みと独立したリセット ベクタ各々はプログラム メモリ空間内に独立したプログラム ベクタを持ちます。全ての割り込みは割り込みを許可するために、ステータス レジスタ(SREG)の全割り込み許可(I)ビットと共に論理1が書かれなければならない個別の許可ビットを割り当てられます。

既定でのプログラム メモリ空間の最下位アトレスはリセットと割り込みへクタとして定義されます。 へクタの完全な一覧は45頁の「7. 割り込み」章で示されます。 この一覧は各種割り込みの優先順位も決めます。 下位側アトレスがより高い優先順位です。 リセットが最高優先順位で次が外部割り込み要求の(INTO)です。

#### 2.7.1. 割り込みの動き

割り込みが起こると全割り込み許可(I)ビットが解除(0)され、全ての割り込みは禁止されます。使用者ソフトウェアは多重割り込みを許可するため、全割り込み許可(I)ビットへ論理1を書けます。その後全ての許可した割り込みが現在の割り込みルーチンで割り込めます。全割り込み許可(I)ビットは割り込みからの復帰(RETI)命令が実行されると、自動的に設定1)されます。

根本的に2つの割り込み形式があります。1つ目の形式は割り込み要求フラグを設定(I)する事象によって起動されます。これらの割り込みでは割り込み処理ルーチンを実行するために、プログラム カウンタは対応する現実の割り込みへ、クタを指示し、ハートウェアが対応する割り込み要求フラグを解除(0)します。割り込み要求フラグは解除(0)されるべきフラグのビット位置へ論理1を書くことによっても解除(0)できます。対応する割り込み許可ビットが解除(0)されている間に割り込み条件が起こると、割り込み要求フラグが設定(1)され、割り込みが許可されるか、またはこのフラグがソフトウェアによって解除(0)されるまで記憶(保持)されます。同様に、全割り込み許可(I)ビットが解除(0)されている間に1つまたはより多くの割り込み条件が起こると、対応する割り込み要求フラグが設定(1)されて全割り込み許可(I)ビットが設定(1)されるまで記憶され、その(I=1)後で優先順に従って実行されます。

2つ目の割り込み形式は割り込み条件が存在する限り起動し(続け)ます。これらの割り込みは必ずしも割り込み要求フラグを持っているとは限りません。割り込みが許可される前に割り込み条件が消滅すると、この割り込みは起動されません。

AVRが割り込みから抜け出すと常に主プログラムへ戻り、何れかの保留割り込みが扱われる前に1つ以上の命令を実行します。

ステータス レジスタ(SREG)は割り込みルーチンへ移行時の保存も、復帰時の再設定も自動的に行われないことに注意してください。これはソフトウェアによって扱われなければなりません。

割り込みを禁止するためにCLI命令を使うと、割り込みは直ちに禁止されます。CLI命令と同時に割り込みが起こっても、CLI命令後に割り込みは実行されません。次例は時間制限EEPROM書き込み手順中に割り込みを無効とするために、これがどう使えるかを示します。

```

アセンブリ言語プログラム例

R16, SREG

;ステータス レシ スタを保存

ΙN

;EEPROM書き込み手順中割り込み禁止

CLI

SBI

EECR, EEMPE

;EEPROM主書き込み許可

SBI

EECR, EEPE

;EEPROM書き込み開始

OUT

SREG, R16

;ステータスレジスタを復帰

C言語プログラム例

/* ステータス レシ スタ保存変数定義 */

char cSREG;

/* ステータス レシ スタを保存 */

cSREG = SREG;

/* EEPROM書き込み手順中割り込み禁止 */

_disable_interrupt();

EECR = (1 < EEMPE);

/* EEPROM主書き込み許可 */

EECR \mid = (1 << EEPE);

/* EEPROM書き込み開始 */

SREG = cSREG:

/* ステータス レシ スタを復帰 */

```

割り込みを許可するためにSEI命令を使うと、次例で示されるようにどの保留割り込みにも先立ってSEI命令の次の命令が実行されます。

注: SLEEP命令までは割り込み禁止、保留割り込み実行前に休止形態へ移行します。

# 2.7.2. 割り込み応答時間

許可した全てのAVR割り込みに対する割り込み実行応答は最小4クロック周期です。4クロック周期後、実際の割り込み処理ルーチンに対するプログラム ヘブタ アトレスが実行されます。この4クロック周期時間中にプログラム カウンタ(PC)がスタック上に保存(プッシュ)されます。このヘブタは標準的に割り込み処理ルーチンへの無条件分岐で、この分岐は2/3クロック周期(**訳注**:原文は3(JMP命令=3)を想定、RJMP命令の場合は2)要します。複数周期命令実行中に割り込みが起こると、その割り込みが扱われる前に、この命令が完了されます。MCUが休止形態の時に割り込みが起こると、割り込み実行応答時間は4クロック周期増やされます。この増加は選択した休止形態からの起動時間に加えてです。

割り込み処理ルーチンからの復帰は4クロック周期要します。これらの4クロック周期中、プログラム カウンタ(PC:2バイト)がスタックから取り戻され(ポップ)、スタック ポープンタは増加され(+2)、ステータス レジ、スタ(SREG)の全割り込み許可(I)ビットが設定(1)されます。

# 3. AVRのメモリ

この項はATtiny87/167の各種メモリを記述します。AVR構造にはプログラム メモリ空間とデータ メモリ空間の2つの主なメモリ空間があります。加えてこれらのデバイスはデータ保存用EEPROMメモリが特徴です。3つのメモリ空間全ては一般的な直線的アドレスです。

表3-1. メモリ割付

| メモリ種        | 別      | ニーモニック      | ATtiny87                                            | ATtiny167                                           |  |  |

|-------------|--------|-------------|-----------------------------------------------------|-----------------------------------------------------|--|--|

|             | 容量     | Flash size  | 8Kハ*イト                                              | 16Kハブト                                              |  |  |

| フラッシュ メモリ   | 開始アドレス | -           | \$00000                                             |                                                     |  |  |

|             | 終了アドレス | Flash end   | \$1FFF( <mark>注1</mark> ),\$0FFF( <mark>注2</mark> ) | \$3FFF( <mark>注1</mark> ),\$1FFF( <mark>注2</mark> ) |  |  |

|             | 容量     | -           | 32^                                                 | 小                                                   |  |  |

| 汎用レジスタ      | 開始アドレス | ı           | \$00                                                | 000                                                 |  |  |

|             | 終了アドレス | 1           | \$00                                                | 01F                                                 |  |  |

|             | 容量     | -           | 64^                                                 | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\              |  |  |

| (標準)I/Oレジスタ | 開始アドレス | 1           | \$0020                                              |                                                     |  |  |

|             | 終了アドレス | ı           | \$005F                                              |                                                     |  |  |

|             | 容量     | -           | 160パイト                                              |                                                     |  |  |

| 拡張I/Oレジスタ   | 開始アドレス | 1           | \$00                                                | 060                                                 |  |  |

|             | 終了アドレス | 1           | \$00                                                | FF                                                  |  |  |

|             | 容量     | ISRAM size  | 512/                                                | ペイト                                                 |  |  |

| 内蔵SRAM      | 開始アドレス | ISRAM start | \$01                                                | 100                                                 |  |  |

|             | 終了アドレス | ISRAM end   | \$02                                                | FF                                                  |  |  |

|             | 容量     | E2 size     | 512/                                                | ヾ゚゚゙゙゙゙゙゙゚゚゙゙゙゙゙゚゚゙ヽ                                |  |  |

| 内蔵EEPROM    | 開始アドレス | ı           | \$00                                                | 000                                                 |  |  |

|             | 終了アドレス | E2 end      | \$01                                                | FF                                                  |  |  |

注1: バイトアドレスです。

注2: 語(ワート = 16 ビット)アトレスです。

# 3.1. 実装書き換え可能なプログラム用フラッシュ メモリ

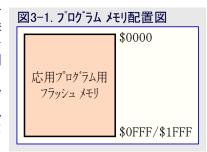

ATtiny87/167はプログラム保存用に実装書き換え可能な8/16Kハイトのフラッシュメモリをチップ上に含みます。全てのAVR命令が16または32ビット幅のため、このフラッシュメモリは4/8K×16ピットとして構成されます。ATtiny87/167は独立したブートプログラム領域と応用プログラム領域を持たず、SPM命令はフラッシュメモリ全体で実行できます。より多くの詳細については148頁の「20.2.1. SPM命令制御/状態レジスタ」項のSPM操作許可(SPMEN)の記述をご覧ください。

フラッシュ メモリは最低10,000回の消去/書き込み回数の耐久性があります。ATtiny87/167のプログラム カウンタ(PC)は12/13ビット幅で、従って4/8Kプログラム メモリ位置のアドレス指定です。<math>152 頁の「21. メモリプログラミング」章はSPIまたは並列プログラミング動作でのフラッシュ メモリ プログラミングの詳細な記述を含みます。

定数表は全てのプログラム メモリ アトレス空間に配置できます。(LPMとSPM命令記述参照) 命令の取得と実行のタイミング図は13頁の「2.6. 命令実行タイミング」項で示されます。

R0

アドレス

\$0000

#### 3.2. データ用SRAM メモリ

図3-2.はATtiny87/167のSRAMメモリ構成方法を示します。

ATtiny87/167はINやOUT命令で予約した64位置で支援されるより多くの周辺機能部を持つ複合マイクロコントローラです。SRAM(データ空間)内\$60~\$FFの拡張I/O空間に対してLD/LDS/LDDとST/STS/STD命令だけが使えます。

下位768データメモリ位置はレシ、スタファイル、I/Oメモリ、拡張I/Oメモリ、データ用内蔵SRAMに充てます。先頭の32位置はレシ、スタファイル、次の64位置は標準I/Oメモリ、その次の160位置は拡張I/Oメモリ、そして次の512位置はデータ用内蔵SRAMに充てます(15頁の表3-1.で"ISRAM size"をご覧ください)。

直接、間接、変位付き間接、事前減少付き間接、事後増加付き間接の5つの異なるアトレス指定種別でデータ メモリ(空間)を網羅します。レジスタファイル内のレジスタR26~R31は間接アトレス指定ホーインタ用レジスタが特徴です。

直接アドレス指定はデータ空間全体に届きます。

変位付き間接動作はYまたはZレジスタで与えられる基準アドレスからの63アドレス位置に (本: 赤子はI/O/ 届きます。

| $(32\times8)$    | R31       | \$001F      |

|------------------|-----------|-------------|

| I/Oレジスタ          | \$00      | \$0020      |

| $(64\times8)$    | °<br>\$3F | °<br>\$005F |

| 拡張I/Oレジスタ        | \$0060    | \$0060      |

| $(160 \times 8)$ | \$00FF    | \$00FF      |

| 内蔵SRAM           | \$0100    | \$0100      |

| $(512\times8)$   | \$0xFF    | \$02FF      |

| 注・表字は1/07じょ      |           | '           |

図3-2. データ メモリ配置図

レシブスタ ファイル

自動の事前減少付きと事後増加付きのレジスタ間接アトンス指定動作を使う時に(使われる)X,Y,Zアトンスレジスタは減少(-1)または増加(+1)されます。

ATtiny87/167の32個の汎用レジスタ、64個のI/Oレジスタ、160個の拡張I/Oレジスタ、512バイトのデータ用内蔵SRAMはこれら全てのアドレス指定種別を通して全部アクセスできます。レジスタファイルは12頁の「汎用レジスタファイル」で記述されます。

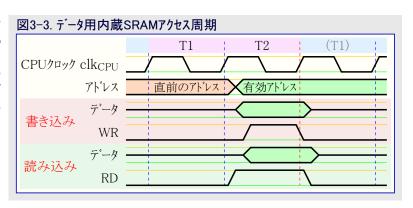

# 3.2.1. データ メモリ アクセス タイミング

本節は内部メモリ アクセスに対する一般的なアクセス タイミングの概念を記述します。 データ用内蔵SRAMアクセスは図3-3.で記載されるように2clkCPU周期で実行されます。

(訳注) 内蔵SRAMのアクセスを含む代表的な命令はT1,T2の 2周期で実行され、T1で対象アトレスを取得/(算出)/ 確定し、T2で実際のアクセスが行われます。後続する (T1)は次の命令のT1です。

#### 3.3. データ用EEPROMメモリ

ATtiny87/167は64バイトのデータ用EEPROMを含みます(15頁の**表3-1**.で"E2 size"をご覧ください)。それは単一バイトが読み書きできる分離したデータ空間として構成されます。EEPROMは最低100,000回の消去/書き込み回数の耐久性があります。CPUとEEPROM間のアクセスは以降のEEPROMアドレス レジスタ、EEPROMデータ レジスタ、EEPROM制御レジスタで詳細に記述されます。

152頁の「21. メモリ プログラミング」章はSPIまたは並列プログラミングの詳細な記述を含みます。

#### 3.3.1. EEPROMアクセス

EEPROMアクセスレジスタはI/O空間でアクセス可能です。

EEPROMの消去/書き込み(<mark>訳注</mark>:原文はアクセス)時間は表3-2.で与えられます。(書き込みは)自己タイシケ機能ですが、使用者ソフトウェアは次ハートが書ける時を検知してください。使用者コートがEEPROMに書く命令を含む場合、いくつかの予防処置が取られねばなりません。厳重に濾波した電源では電源投入/切断でVCCが緩やかに上昇または下降しそうです。これはデハーイスが何周期かの時間、使われるクロック周波数に於いて最小として示されるより低い電圧で走行する原因になります。これらの状態で問題を避ける方法の詳細については以下の「EEPROMデータ化けの防止」をご覧ください。

予期せぬEEPROM書き込みを防止するため特別な書き込み手順に従わなければなりません。この詳細については次の「非分離バイト書き込み」と「分離バイ書き込み」を参照してください。

EEPROMが読まれると、CPUは次の命令が実行される前に4クロック周期停止されます。EEPROMが書かれると、CPUは次の命令が実行される前に2クロック周期停止されます。

# 3.3.2. 非分離バイト プログラミング

非分離バイプログラミングの使用は最も簡単な形態です。EEPROMにバイトを書くとき、使用者はEEARにアドレス、EEDRにデータを書かなければなりません。EEPMnt'ットが'00'ならば、(EEMPEが1を書かれる後の4周期内の)EEPEの1書き込みは消去/書き込み動作を起動します。消去と書き込みの両周期は1操作で行われ、総プログラミング時間は表3-2.で与えられます。EEPEt'ットは消去と書き込み動作が完了されるまで設定(1)に留まります。デバイスがプログラミング動作中、他のどのEEPROM操作の実行も不可能です。

#### 3.3.3. 分離バイト プログラミング

2つの異なる操作として消去と書き込みの周期を分離することが可能です。これは或る時間制限(代表的には電源電圧不足)に対して システムが短いアクセス時間を必要とする場合に有用かもしれません。この方法の優位性を得るため、書かれるべき位置が書き込み操作 前に消去されてしまっていることが必要とされます。しかし、消去と書き込みが分離されるため、時間が重大な操作の実行をシステムが 許す時(代表的には電源投入後)に消去操作を行うことが可能です。

#### 3.3.4. 消去

ハーイトを消去するにはアトーレスがEEARに書かれなければなりません。EEPMntーットが、O1、なら、(EEMPEが1を書かれた後の4周期内の) EEPEの1書き込みは消去動作だけを起動します(プログラミング・時間は表3-2、で与えられます)。EEPEtーットは消去動作が完了されるまで設定(1)に留まります。デーバイスがプログラミング動作中、他のどのEEPROM操作の実行も不可能です。

#### 3.3.5. 書き込み

(特定)位置を書くため、使用者はEEARにアトンス、EEDRにデータを書かなければなりません。EEPMnt゙ットが'10'なら、(EEMPEが1を書かれる後の4周期内の)EEPEの1書き込みは書き込み動作だけを起動します(プログラミング時間は表3-2.で与えられます)。EEPEt゙ットは書き込み動作が完了されるまで設定(1)に留まります。書かれるべき位置が書き込み前に消去されてしまっていなければ、元の格納データは失ったとみなされなければなりません。デバイスがプログラミング動作中、他のどのEEPROM操作の実行も不可能です。

EEPROMアクセスの時間に校正済み内蔵発振器が使われます。発振器周波数が31頁の「OSCCAL - 発振校正レジスタ」で記述した必要条件内であることを確かめてください。

次のコート・例はアセンブリ言語とC言語でのEEPROM消去、書き込み、または非分離書き込み関数を示します。本例は(例えば全割り込み禁止によって)割り込みが制御され、これらの関数実行中に割り込みが起きない前提です。(訳注:共通性から以下の例は補足修正しています。)

```

アセンブリ言語プログラム例

EEPROM_WR:

;EEPROMプログラミング完了ならばスキップ

SBIC

EECR, EEPE

EEPROM_WR

;以前のEEPROMプログラミング完了まで待機

R.TMP

R19, (0<<EEPM1) | (0<<EEPM0)

LDI

;プログラミング種別値取得(本例は非分離)

;対応プログラミング種別設定

OUT

EECR, R19

;EEPROMアトレス上位ハイ・沿定

EEARH, R18

OUT

EEARL, R17

;EEPROMアドレス下位バイト設定

OUT

OUT

EEDR, R16

;EEPROM書き込み値を設定

EECR, EEMPE

;EEPROM主プログラム許可ビット設定

SBI

EECR, EEPE

;EEPROMプログラミング開始(プログラム許可ビット設定)

SBI

RET

;呼び出し元へ復帰

C言語プログラム例

void EEPROM write (unsigned int uiAddress, unsigned char ucData)

while (EECR & (1<<EPE));

/* 以前のEEPROMプログラミング完了まで待機 */

EECR = (0 < EEPM1) | (0 < EEPM0);

/* 対応プログラミング種別設定 */

EEAR = uiAddress;

/* EEPROMアドレス設定*/

EEDR = ucData;

/* EEPROM書き込み値を設定 */

EECR \mid = (1 << EEMPE);

/* EEPROM主プログラム許可*/

EECR = (1 \le EEPE);

/* EEPROMプログラミング開始*/

```

次のコート・例はアセンブリ言語とC言語でのEEPROM読み込み関数を示します。本例は割り込みが制御され、これらの関数実行中に割り込みが起きない前提です。

```

アセンブリ言語プログラム例

EEPROM RD:

SBIC

EECR, EEPE

;EEPROMプログラミング完了ならばスキップ

;以前のEEPROMプログラミング完了まで待機

R.TMP

EEPROM RD

;EEPROMアドレス上位バイト設定

OUT

EEARH, R18

;EEPROMアドレス下位バイト設定

OUT

EEARL, R17

EECR, EERE

;EEPROM読み出し開始(読み込み許可ビット設定)

SBI

;EEPROM読み出し値を取得

R16, EEDR

ΙN

RET

;呼び出し元へ復帰

C言語プログラム例

unsigned char EEPROM read(unsigned int uiAddress)

while (EECR & (1<<EPE));

/* 以前のEEPROMプログラミング完了まで待機 */

EEAR = uiAddress;

/* EEPROMアドレス設定 */

EECR |= (1<<EERE);

/* EEPROM読み出し開始 */

/* EEPROM読み出し値を取得,復帰 */

return EEDR;

}

```

#### 3.3.6. EEPROMデータ化けの防止

低VCCの期間中、正しく動作するための供給電圧がCPUとEEPROMに対して低すぎるためにEEPROMデータが化け得ます。これらの問題はEEPROMを使う基板段階の装置と同じで、同じ設計上の解決策が適用されるべきです。

EEPROMデータ化けは電圧が低すぎる時の2つの状態によって起こされ得ます。1つ目として、EEPROMへの通常の書き込み手順は正しく動作するための最低電圧が必要です。2つ目として、供給電圧が低すぎると、CPU自身が命令を間違って実行し得ます。

EEPROMデータ化けは次の推奨設計によって容易に避けられます。

不充分な供給電源電圧の期間中、AVRのRESETを活性(Low)に保ってください。これは内蔵低電圧検出器(BOD)を許可することによって行えます。内蔵BODの検出電圧が必要とした検出電圧と一致しない場合、外部低VCCリセット保護回路が使えます。書き込み動作実行中にリセットが起こると、この書き込み操作は供給電源電圧が充分ならば(継続)完了されます。

# 3.4. I/O メモリ (レシ スタ)

ATtiny87/167のI/O空間定義は182頁の「24. レジスタ要約」章で示されます。

ATtiny87/167の全てのI/Oと周辺機能はI/O空間に配置されます。全てのI/O位置はI/O空間と32個の汎用作業レジスタ間のデータ転送を行うLD/LDS/LDD命令とST/STS/STD命令によってアクセスされます。アドレス範囲 $\$00 \sim \$1$ F内のI/OレジスタはSBI命令とCBI命令の使用で直接的にビット アクセス可能です。これらのレジスタではSBISとSBIC命令の使用によって単一ビット値が検査できます。より多くの詳細については「命令要約」章を参照してください。I/O指定命令INとOUTを使う時はI/Oアドレス $\$00 \sim \$3$ Fが使われなければなりません。LD命令とST命令を使い、データ空間としてI/Oレジスタをアクセスする時はこれらのアドレスに\$20が加算されなければなりません。ATtin y87/167はINやOUT命令で予約した64位置で支援されるよりも多くの周辺機能部を持つ複合マイクロコントローラです。SRAM(データ空間)内 $\$60 \sim \$$ FFの拡張I/O領域に対してはLD/LDS/LDDとST/STS/STD命令だけが使えます。

将来のデバイスとの共通性を保つため、アクセスされる場合、予約ビットはのが書かれるべきです。予約済みI/Oメモリ アドレスは決して書かれるべきではありません。

状態フラグのいくつかはそれらへ論理1を書くことによって解除(0)されます。CBIとSBI命令は指定ビットだけを操作し、従って状態フラグのようなものを含むレジスタに使えることに注意してください。CBIとSBI命令は(I/Oアドレス)\$00~\$1Fのレジスタでのみ動作します。 I/Oと周辺制御レジスタは以降の項で説明されます。

# 3.4.1. 汎用I/Oレジスタ

ATtiny87/167は3つの汎用I/Oレジスタを含みます。これらのレジスタはどの情報の格納にも使え、特に全体変数や状態フラグの格納に有用です。(I/O)アドレス範囲\$00~\$1Fの汎用I/OレジスタはSBI,CBI,SBIS,SBIC命令の使用で直接ビット アクセスが可能です。

# 3.5. メモリ関係レジスタ

# 3.5.1. EEARH,EEARL (EEAR) - EEPROMアドレス レジスタ (EEPROM Address Register)

| ピット         | 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     | _     |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$22 (\$42) | -     | -     | -     | -     | -     | -     | -     | EEAR8 | EEARH |

| Read/Write  | R     | R     | R     | R     | R     | R     | R     | R/W   |       |

| 初期値         | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 不定    |       |

| ピット         | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |       |

| \$21 (\$41) | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEARL |

| Read/Write  | R/W   |       |

| 初期値         | 不定    |       |

|             |       |       |       |       |       |       |       |       |       |

#### ビット15~9 - Res: 予約 (Reserved)

これらのビットは予約されており、常に0として読まれます。

# ● ビット8~0 - EEAR8~0: EEPROMアドレス (EEPROM Address)

EEPROMアドレスレジスタ(EEARHとEEARL)は256小イトEEPROM空間(15頁の表3-1.の"E2 size"参照)のEEPROMアドレスを指定します。 EEPROMデータ ハイトは0~255間で直線的に配されます。EEARの初期値は不定です。EEPROMがアクセスされるであろう前に適切な値が書かれねばなりません。

# 3.5.2. EEDR - EEPROMデータレジスタ (EEPROM Data Register)

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |      |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|------|

| \$20 (\$40) | (MSB) |     |     |     |     |     |     | (LSB) | EEDR |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |      |

| 初期値         |       |     |     |     |     |     |     |       |      |

## ● ビット7~0 - EEDR7~0: EEPROMデータ (EEPROM Data)

EEPROM書き込み操作に対してEEDRはEEPROMアドレスレジスタ(EEAR)で与えたアドレスのEEPROMへ書かれるべきデータを含みます。 EEPROM読み込み操作に対してEEDRはEEARで与えたアドレスのEEPROMから読み出したデータを含みます。

#### 3.5.3. EECR - EEPROM制御レジスタ (EEPROM Control Register)

| ピット         | 7 | 6 | 5     | 4     | 3     | 2     | 1    | 0    |      |

|-------------|---|---|-------|-------|-------|-------|------|------|------|

| \$1F (\$3F) | - | - | EEPM1 | EEPM0 | EERIE | EEMPE | EEPE | EERE | EECR |

| Read/Write  | R | R | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  |      |

| 初期値         | 0 | 0 | 不定    | 不定    | 0     | 0     | 不定   | 0    |      |

#### ヒット7.6 - Res: 予約 (Reserved)

これらのビットは将来の使用に予約されており、常に0として読まれます。読み込み後、これらのビットを遮蔽してください。将来のAVRデバイスとの互換性のため、常にこれらのビットに0を書いてください。

#### ヒット5.4 - EEPM1.0: EEPROMプログラミング種別 (EEPROM Programing Mode Bits)

EEPROMプログラミング種別ビット設定はEEPROMプログラミング許可(EEPE)書き込み時にどのプログラミング動作が起動されるかを定義します。1つの非分離操作(旧値消去と新値書き込み)、または2つの異なる操作として消去と書き込み操作を分離してデータをプログラムする(書く)ことが可能です。各動作に対するプログラミング時間は表3-2.で示されます。EEPEが設定(1)されている間はEEPMnへのどの書き込

| 表3-2. E | 表3-2. EEPROMプログラミング種別 |           |                     |  |  |  |  |  |  |

|---------|-----------------------|-----------|---------------------|--|--|--|--|--|--|

| EEPM1   | EEPM0                 | プログラミング時間 | 動作                  |  |  |  |  |  |  |

| 0       | 0                     | 3.4ms     | 1操作での消去と書き込み(非分離操作) |  |  |  |  |  |  |

| 0       | 1                     | 1.8ms     | 消去のみ                |  |  |  |  |  |  |

| 1       | 0                     | 1.8ms     | 書き込みのみ              |  |  |  |  |  |  |

| 1       | 1                     | - 1       | 将来使用に予約             |  |  |  |  |  |  |

みも無視されます。リセット中、EEPMnt'ットはEEPROMがプログラミング作業中を除いて'00'にリセットされます。

#### ● ビット3 - EERIE: EEPROM操作可割り込み許可(EEPROM Ready Interrupt Enable)

EERIEの1書き込みはステータスレジスタ(SREG)の全割り込み許可(I)ビットが設定(1)されているなら、EEPROM操作可割り込みを許可します。EERIEの0書き込みは、この割り込みを禁止します。EEPROM操作可割り込みは不揮発性メモリ(フラッシュメモリとEEPROM)がプログラミングの準備可ならば継続する割り込みを発生します。EEPROM書き込みとSPM命令の間、本割り込みは生成されません。

#### • ビット2 - EEMPE: EEPROM主プログラム許可(EEPROM Master Program Enable)

EEMPEL'ットはEEPROMプログラム許可(EEPE)ヒットの1書き込みが有効か無効かどちらかを決めます。

EEMPEが設定(1)されると、4クロック周期内のEEPE設定(1)は選択したアトレスのEEPROMをプログラムします。EEMPEが0なら、EEPE設定(1)は無効です。EEMPEがソフトウェアによって設定(1)されてしまうと、4クロック周期後にハートウェアがこのビットを0に解除します。

#### • ビット1 - EEPE: EEPROMプログラム許可(EEPROM Program Enable)

EEPROMプログラム許可信号(EEPE)はEEPROMへのプログラミング許可信号です。EEPEが(1を)書かれると、EEPROMはEEPMnビット設定に従ってプログラムされます。論理1がEEPEへ書かれる前にEEPROM主プログラム許可(EEMPE)ビットは1を書かれなければならず、さもなければEEPROM書き込み(消去)は行われません。書き込み(プログラミング)アクセス時間が経過されると、EEPROMプログラム許可(EEPE)ビットはハートヴェアによって解除(0)されます。EEPEが設定(1)されてしまうと、次の命令が実行される前にCPUは2周期停止されます。

#### ● ビット0 - EERE : EEPROM読み込み許可 (EEPROM Read Enable)

EEPROM読み込み許可信号(EERE)はEEPROMへの読み込みストローブです。EEARに正しいアトレスが設定されると、EEPROM読み出しを起動するためにEEREビットは1を書かれなければなりません。EEPROM読み出しアクセスは(その)1命令で行われ、要求したデータは直ちに利用できます。EEPROMが読まれるとき、次の命令が実行される前にCPUは4周期停止されます。使用者は読み込み操作を始める前にEEPEビットをポーリングすべきです。書き込み(プログラム)操作実行中の場合、EEPROMアトレスレジスタ(EEAR)の変更もEEPROM読み込みもできません。

# 3.5.4. GPIOR2 - 汎用I/Oレジスタ2 (General Purpose I/O Register 2)

| \$2B (\$4B) (MSB) (LSB)                | CDIODA |

|----------------------------------------|--------|

|                                        | GPIOR2 |

| Read/Write R/W R/W R/W R/W R/W R/W R/W |        |

| 初期値 0 0 0 0 0 0 0                      |        |

このレジスタはどんな種類のデータの格納にも自由に使えるかもしれません。

#### 3.5.5. GPIOR1 - 汎用I/Oレジスタ1 (General Purpose I/O Register 1)

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |        |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$2A (\$4A) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR1 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

このレジスタはどんな種類のデータの格納にも自由に使えるかもしれません。

#### 3.5.6. GPIORO - 汎用I/OレジスタO (General Purpose I/O Register 0)

| ピット         | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |        |

|-------------|-------|-----|-----|-----|-----|-----|-----|-------|--------|

| \$1E (\$3E) | (MSB) |     |     |     |     |     |     | (LSB) | GPIOR0 |

| Read/Write  | R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W   |        |

| 初期値         | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |        |

# 4. システム クロックとクロック選択

ATtiny87/167は多数のクロック元を提供します。それらは内部と外部の2つの種類に分けることができます。いくつかの外部クロック元は非同期タイマ/カウンタと共用され得ます。リセット後、クロック元はCKSELヒューズによって決められます。一旦デバイスが走行すると、ソフトウェアクロック切り替えは他のどのクロック元にもできます。

クロック切り替え管理のためにハードウェア制御が提供されますが、いくつかの特別な手続きを遵守しなければなりません。クロック切り替えはデバイスが不正な構成設定を持つ結果となり得るいくつかの設定に注意して実行されるべきです。

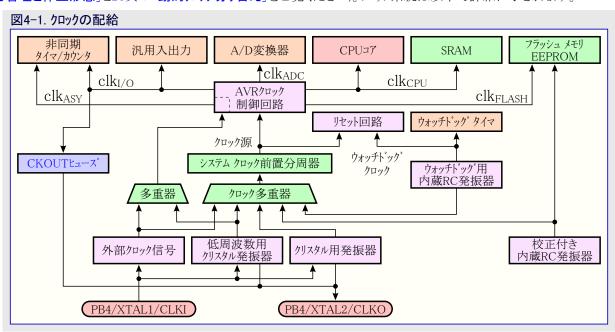

# 4.1. クロック系統とその配給

図4-1.はAVR内の主要なクロック系統とその配給を示します。全てのクロックが与えられた時間有効である必要はありません。消費電力低減のため、各種休止形態の使用または動的クロック切り替え回路の使用によって使われない部分のクロックを停止することができます(34頁の「電力管理と休止形態」と26頁の「動的クロック切り替え」をご覧ください)。クロック系統は以下で詳細に示されます。

#### **4.1.1. CPU クロック** – clk<sub>CPU</sub>

CPUクロックはAVRコアの動作と関係する系統の部分に配給されます。このような部分の例は汎用レジスタ ファイル、ステータス レジスタ、スタック ポインタを保持するデータ メモリです。CPUクロックの停止はコアが一般的な操作や計算を実行することを禁止します。

#### **4.1.2. I/O クロック** - clk<sub>I/O</sub>

I/Oクロックは同期タイマ/カウンタのようなI/O部の大部分で使われます。I/Oクロックは外部割り込み部でも使われますが、いくつかの外部割り込みは例えI/Oクロックが停止されても検出されることをこのような割り込みに許す非同期論理回路によって検出されることに注意してください。

#### **4.1.3**. フラッシュ クロック - clk<sub>FLASH</sub>

フラッシュ クロックはフラッシュ メモリ インターフェースの動作を制御します。このフラッシュ クロックは常にCPUクロックと同時に活動します。

# 4.1.4. 非同期タイマ クロック - clk<sub>ASY</sub>

非同期タイマ クロックは外部クロックまたは外部低周波数クリスタルから直接的にクロック駆動されることを非同期タイマ/カウンタに許します。この専用クロック範囲はデバイスが休止形態の時でも、このタイマ/カウンタの実時間計数器としての使用を許します。

#### 4.1.5. A/D変換クロック - clk<sub>ADC</sub>

A/D変換器には専用のクロック範囲が提供されます。これはデジタル回路によって生成される雑音を低減するためにCPUとI/Oクロックの停止を許します。これはより正確なA/D変換結果を与えます。

# 4.2. クロック元

このデバイスは下で示されるように、フラッシュ ヒュース ビット(既定)、または(動的クロック切り替え回路)クロック選択レジスタ(CLKSELR)によって 選択可能な以下のクロック元選択を持ちます。選択したクロック元からのクロックはAVRクロック発生器への入力で、適切な単位部へ配給されます。

表4-1. デバイス クロック任意選択(注1)、PB4とPB5の機能

| クロック種別                                  | CKSEL3~0 (注2)<br>CSEL3~0 (注3) | PB4   | PB5      |

|-----------------------------------------|-------------------------------|-------|----------|

| 外部クロック信号                                | 0 0 0 0                       | CLKI  | CLKO•I/O |

| (予約)                                    | 0 0 0 1                       | 1     | _        |

| 校正付き8MHz内部RC発振器                         | 0 0 1 0                       | I/O   | CLKO•I/O |

| 128kHz内部RC発振器(ウォッチドッケ <sup>*</sup> 発振器) | 0 0 1 1                       | I/O   | CLKO•I/O |

| 外部低周波数クリスタル/セラミック用発振器                   | 0 1 x x                       | XTAL1 | XTAL2    |

| 外部クリスタル/セラミック用発振器(0.4~0.9MHz)           | 1 0 0 x                       | XTAL1 | XTAL2    |

| 外部クリスタル/セラミック用発振器(0.9~3.0MHz)           | 1 0 1 x                       | XTAL1 | XTAL2    |

| 外部クリスタル/セラミック用発振器(3.0~8.0MHz)           | 1 1 0 x                       | XTAL1 | XTAL2    |

| 外部クリスタル/セラミック用発振器(8.0~16.0MHz)          | 1 1 1 x                       | XTAL1 | XTAL2    |

注1:全てのヒュース は1=非プログラム、0=プログラムです。

注2: フラッシュのヒュース ビットです。

注3: クロック選択レシ、スタ(CLKSELR)のビットです。

各クロック選択に対する各種選択は以降の項で得られます。

CPUがパワーダウンまたはパワーセーブから起きる時か、または動的クロック切り替え回路によって新しいクロック元が許可される時に、選択したクロック元が始動時間に使われ、命令実行開始前に安定な発振器動作を保証します。

CPUがリセットから始まる時は通常動作開始前に安定電圧へ達することを電源に許す付加遅延があります。ウォッチト、ック・発振器はこの起動時間の実時間部のタイミングに使われます。各計時完了に使われるウォッチト、ック(WDT)発振器の周期数は、表4-2.で示されます。

| 表4-2. ウォッチト・ック・発振器周期数 |          |           |  |  |  |

|-----------------------|----------|-----------|--|--|--|

| VCC=3.0V              | VCC=5.0V | 周期数       |  |  |  |

| 4.3ms                 | 4.1ms    | 512       |  |  |  |

| 69ms                  | 65ms     | 8K (8192) |  |  |  |

# 4.2.1. 既定のクロック元

リセットに於いてCKSELヒュース'とSUTヒュース'がクロック選択レシ`スタ(CLKSELR)に複写されます。そしてデバイスはCLKSELRレシ`スタ(クロック元選択(CSEL3~0)とクロック始動時間(CSUT1,0))によって定義されたクロック元と始動タイミンク'を使います。

本デバイスはCKSELヒューズ=0010, SUTヒューズ=10, CKDIV8ヒューズ=プログラム(0)で出荷されます。従って既定のクロック元設定は最長起動時間、8.0MHzで走行する内蔵RC発振器で、8分周の初期システム クロックです。この既定設定は全ての使用者が実装または高電圧書き込み器を使い、それらを希望したクロック元設定にできることを保証します。この構成設定はISPツール使用時に注意しなければなりません。

#### 4.2.2. 校正付き内蔵RC発振器

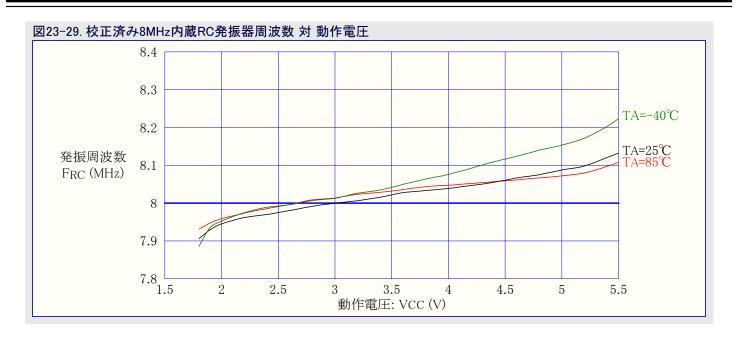

既定による内蔵RC発振器は概ね8.0MHzまたは1MHzのクロックを提供します。電圧と温度に依存しますが、このクロックは使用者によっ て高精度な校正ができます。より多くの詳細については165頁の**表22-1**.と180頁の「**23.10. 内部発振器**」項をご覧ください。

選択したなら、外部部品なしで動作します。リセット中、ハートウェアが発振校正(OSCCAL)レジブスタに校正値バイトを設定し、これによってRC 発振器を自動的に構成設定(校正)します。この校正の精度は161頁の表22-1.で工場校正として示されます。

ソフトウェアからOSCCALレジスタを変更することによって(発振校正レジスタ(OSCCAL)参照)、工場校正を使うよりも高い精度を得ることがで きます。この校正の精度は表22-1.で使用者校正として示されます。

この発振器がチップ(システム)クロックとして使われるとき、ウォッチドック.発振器は未だウォッチドック.タイマとリセット付加遅延タイマに使われます。予 め設定された校正値のより多くの情報については154頁の「校正n'仆」項をご覧ください。

この発振器が選択されると、起動時間は**表4-4**.で示されるようにSUTヒューズまたはクロック始動時間(CSUT)領域によって決定されます。

| 24 N-11-11-11-11-11-11-11-11-11-11-11-11-11 | 4 20 3/24 HH 2/3 11   ± /3 3 (1 = -7 |

|---------------------------------------------|--------------------------------------|

| CKSEL3~0 (注3,4)                             | 周波数範囲(注2)                            |

| CSEL3~0 (注5)                                | (MHz)                                |

| 0 0 1 0                                     | 7.6~8.4                              |

表4-3. 校正付き内蔵RC発振器動作種別(注1) 注1: この8MHz周波数がデバイス仕様(VCCに依存)を越える場合、内部周波数 を8分周するためにCKDIV8ヒューズをプログラム(0)にできます。

注2: この周波数範囲は指針値です。

注3: デバイスはこのCKSEL3~0='0010'で出荷されます。

注4: フラッシュのヒュース ビットです。

注5: クロック選択レシ、スタ(CLKSELR)のビットです。

#### 表4-4. 校正付き内蔵RC発振器用起動遅延時間選択表

|   | SUT1,0 ( <mark>注1</mark> )<br>CSUT1,0 ( <mark>注2</mark> ) | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法            |

|---|-----------------------------------------------------------|---------------------|------------------------------|------------------|

| I | 0 0 (注3)                                                  | 6×CK                | 14×CK                        | 低電圧検出リセット(BOD)許可 |

| I | 0 1                                                       | 6×CK                | 14×CK+4ms                    | 高速上昇電源           |

|   | 10 (注4)                                                   | 6×CK                | 14×CK+64ms                   | 低速上昇電源           |

|   | 1 1                                                       | (予約)                |                              |                  |

注1: フラッシュのヒュース ビットです。

注2: クロック選択レシブスタ(CLKSELR)のビットです。

注3: この設定はRSTDISBLEヒュースが設定されていない場合にだけ利用可能です。

注4: デバイスはこの選択で出荷されます。

# 4.2.3. 128kHz内部発振器

128kHz内部発振器は128kHzのクロックを供給する低電力発振器です。この周波数は3V,25℃での公称値です。このクロックは**表4-1**.で 示されるようにCKSELヒューズまたはクロック元選択(CSEL)領域のプログラミング(設定)によってシステム クロックとして選択できます。

このクロック元が選択されると、起動時間は表4-5.で示されるようにSUTヒューズまたはクロック始動時間(CSUT)領域によって決定されます。

# 表4-5 128kHz内部登振哭田起動遅延時間選択表

| SUT1,0 (注1)<br>CSUT1,0 (注2) | パワーダウンからの<br>起動遅延時間 | リセットからの<br>付加遅延時間 | 推奨使用法            |

|-----------------------------|---------------------|-------------------|------------------|

| 00 (注3)                     | 6×CK                | 14×CK             | 低電圧検出(BOD)リセット許可 |

| 0 1                         | 6×CK                | 14×CK+4ms         | 高速上昇電源           |

| 1 0                         | 6×CK                | 14×CK+64ms        | 低速上昇電源           |

| 1 1                         | (予約)                |                   |                  |

注1: フラッシュのヒューズ ビットです。

注2: クロック選択レシ、スタ(CLKSELR)のビットです。

注3: この設定はRSTDISBLEヒュースが設定されていない場合にだけ利用可能です。

#### 4.2.4. クリスタル用発振器

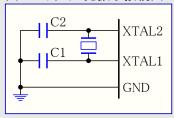

XTAL1とXTAL2は**図4-2**.で示されるように、チップ上の発振器としての使用に設定できる反転増幅器の各々、入力と出力です。クリスタル発振子またはセラミック振動子のどちらでも使えます。

C1とC2はクリスタル発振子とセラミック振動子の両方について常に等しくすべきです。このコンデンサの最適値は使うクリスタル発振子やセラミック振動子、浮遊容量の量、その環境の電磁雑音に依存します。クリスタル発振子使用に対するコンデンサ選択について初期の指針のいくつかは表4-6.で与えられます。セラミック振動子については製造業者によって与えられたコンデンサ値が使われるべきです。

低電力発振器は示された周波数範囲で各々最適化された3つの異なる種別で動作できます。この動作種別は表4-6.で示されるようにCKSEL3~1ヒューズまたはクロック元選択(CSEL3~1)領域によって選択されます。

CKSEL0ヒューズはSUT1,0ヒューズと、またはクロック元選択(CSEL0)領域はクロック始動時間(CSUT)領域と共に表4-7.で示されるように起動時間を選択します。

図4-2. クリスタル発振子接続図

| 表4-6. クリスタル用発振器動作種別           |                       |          |  |  |  |

|-------------------------------|-----------------------|----------|--|--|--|

| CKSEL3~1 (注1)<br>CSEL3~1 (注2) | 周波数範囲                 | 推奨C1,2容量 |  |  |  |

|                               |                       |          |  |  |  |

| 100 (注)                       | 0.4~0.9MHz            | -        |  |  |  |

| 101                           | 0.9~3.0MHz            | 12∼22pF  |  |  |  |

| 110                           | 3.0~8.0MHz            | 12∼22pF  |  |  |  |

| 111                           | 8.0~16MH <sub>7</sub> | 12∼22nF  |  |  |  |

注1: フラッシュのヒューズ ビットです。

注2: クロック選択レシブスタ(CLKSELR)のビットです。

注3: この選択はクリスタル発振子ではなく、セラミック振動子でのみ使われるべきです。

表4-7. クリスタル発振子/セラミック振動子用発振器起動遅延時間選択表

| CKSEL0 (注1)<br>CSEL0 (注2) | SUT1,0 (注1)<br>CSUT1,0 (注2) | パワーダウンからの<br>起動遅延時間  | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法                           |

|---------------------------|-----------------------------|----------------------|------------------------------|---------------------------------|

|                           | 0 0                         | 258×CK ( <b>注3</b> ) | $14 \times \text{CK+4ms}$    | 外部セラミック振動子、高速上昇電源               |

|                           | 0 1                         | 258×CK ( <b>注3</b> ) | $14 \times \text{CK+64ms}$   | 外部セラミック振動子、低速上昇電源               |

| 0                         | 10(注5)                      | 1K×CK ( <b>注4</b> )  | 14×CK                        | 外部セラミック振動子、<br>低電圧検出(BOD)リセット許可 |

|                           | 1 1                         | 1K×CK ( <b>注4</b> )  | $14 \times \text{CK+4ms}$    | 外部セラミック振動子、高速上昇電源               |

|                           | 0 0                         | 1K×CK ( <b>注4</b> )  | $14 \times \text{CK+64ms}$   | 外部セラミック振動子、低速上昇電源               |

| 1                         | 0 1 (注5)                    | 16K×CK               | 14×CK                        | 外部クリスタル発振子、<br>低電圧検出(BOD)リセット許可 |

|                           | 1 0                         | 16K×CK               | $14 \times \text{CK+4ms}$    | 外部クリスタル発振子、高速上昇電源               |

|                           | 1 1                         | 16K×CK               | $14 \times \text{CK+64ms}$   | 外部クリスタル発振子、低速上昇電源               |

注1: フラッシュのヒュース ビットです。

注2: クロック選択レシ、スタ(CLKSELR)のビットです。

**注3**: これらの選択はデバイスの最高周波数付近での動作でないとき、応用にとって起動での周波数安定性が重要でない場合だけ使われるべきです。これらの選択はクリスタル発振子用ではありません。

**注4**: これらの選択はセラミック振動子での使用を意図され、起動での周波数安定性を保証します。デバイスの最高周波数付近での動作でないとき、応用にとって起動での周波数安定性が重要でない場合はクリスタル発振子も使えます。

注5: この設定はRSTDISBLEヒューズが設定されていない場合にだけ利用可能です。

#### 4.2.5. 低周波数クリスタル用発振器

デバイスに対するクロック元として時計用32.768kHzクリスタルを使うには、表4-1.で示されるようにCKS ELヒュース、またはクロック元選択(CSEL)領域の設定によって低周波数クリスタル発振器が選択されなければなりません。クリスタルは図4-3.で示されるように接続されるべきです。32.768kHzクリスタル用の適当な負荷容量を探すには製造業者のデータシートを調べてください(訳注:整合性から本業修正)。

時計用32.768kHzクリスタル用発振器は(高周波数)クリスタル用発振器が走行していない、または外部クロックが許可されていない場合に非同期タイマ/カウンタによって使うことができます(27頁の「クロック元許可/禁止」をご覧ください)。非同期タイマ/カウンタはそれ自身でこの低周波数クリスタル用発振器を開始できます。

この発振器が選択されると、起動遅延時間は表4-8.で示されるようにSUTヒューズまたはクロック始動時間(CSUT)領域によって決定されます。

# 図4-3. クリスタル発振子接続図 C2=12~22pF XTAL2 32.768kHz XTAL1 C1=12~22pF GND

寄生インピーダンス(パッド,線,基板) が非常に低い場合に12~22pF の容量が必要かもしれません。

#### 表4-8. 低周波数クリスタル発振器起動遅延時間選択表

|   | SUT1,0 (注1)<br>CSUT1,0 (注2) | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法                     |  |

|---|-----------------------------|---------------------|------------------------------|---------------------------|--|

| I | 0 0                         | 1K×CK ( <b>注3</b> ) | 4ms                          | 高速上昇電源または低電圧検出(BOD)リセット許可 |  |

|   | 0 1                         | 1K×CK ( <b>注3</b> ) | 64ms                         | 低速上昇電源                    |  |

| I | 1 0                         | 32K×CK              | 64ms                         | 起動時の周波数安定                 |  |

|   | 1 1                         | (予約)                |                              |                           |  |

注1: フラッシュのヒューズ ビットです。

注2: クロック選択レシ、スタ(CLKSELR)のビットです。

注3: これらの選択は起動での周波数安定性が重要でない場合に使われるべきです。

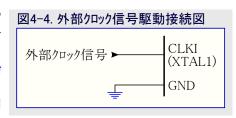

#### 4.2.6. 外部クロック信号

この外部クロック元からデバイスを駆動するには、CLKIが**図4-4**.で示されるように駆動されるべきです。外部クロックでデバイスを走行するには、**表4-1**.で示されるようにCKSELヒュース、またはクロック元選択(CSEL)領域がプログラム(設定)されなければなりません。

このクロック元が選択されると、起動時間は**表4-9**.で示されるようにSUTヒューズまたはクロック始動時間(CSUT)領域によって決定されます。

この外部クロックは高周波数または低周波数クリスタル用発振器が走行していない場合に非同期タイマ/カウンタによって使うことができます(27頁の「**クロック元許可/禁止**」をご覧ください)。 そして非同期タイマ/カウンタはこの入力を許可することができます。

#### 表4-9. 外部クロック信号駆動用起動遅延時間選択表

|   | SUT1,0 ( <u>注1)</u><br>CSUT1,0 ( <mark>注2</mark> ) | パワーダウンからの<br>起動遅延時間 | リセットからの付加遅延<br>時間 (VCC=5.0V) | 推奨使用法            |

|---|----------------------------------------------------|---------------------|------------------------------|------------------|

| I | 0 0                                                | 6×CK                | 14×CK(+4ms) ( <b>注3</b> )    | 低電圧検出(BOD)リセット許可 |

| I | 0 1                                                | 6×CK                | 14×CK+4ms                    | 高速上昇電源           |

| I | 1 0                                                | 6×CK                | 14×CK+64ms                   | 低速上昇電源           |

| ı | 1 1                                                |                     |                              | (予約)             |

注1: フラッシュのヒュース ビットです。

注2: クロック選択レシ、スタ(CLKSELR)のビットです。

注3: RSTDISBLEヒュースが設定されている場合は付加遅延(+4ms)が有効になります。

今までどおりの安定な動作を保証するのと同時に内部クロック周波数の走行時変更を実装するのにシステム クロック前置分周器を使うことができることを覚えておいてください。詳細については「システム クロック前置分周器」を参照してください。

#### 4.2.7. クロック出力緩衝部(外部クロック出力)

クリスタル用発振器を使わない場合、デバイスはCLKOピンにシステム クロックを出力することができます。出力を許可するには、CKOUTヒュース またはクロック選択レジスタ(CLKSELR)のクロック出力(COUT)ビットがプログラム(設定)されなければなりません。この形態はデバイスのクロックがシステム上の他の回路を駆動するのを必要とされる時に有用です。リセット中にクロックが出力されないのと、ヒューズがプログラム(の)されている時に入出力ピンの標準動作が無効にされることに注意してください。システム クロック前置分周器が使われると、分周されたシステム クロックが出力されます。

# 4.3. 動的クロック切り替え

# 4.3.1. 特徴

ATtinv87/167は進行中にデバイスのクロックのON/OFF切り替えを使用者に許す強力な動的クロック切り替えを提供します。組み込み整 合回路がクロックに非同期での許可と禁止を許します。これは簡単且つ素早い実装のための効率的な電力管理の仕組みを許します。 安全な応用では、動的クロック切り替え回路が外部クロックの継続監視を許し、クロック異常の場合に代替切り替えを実行します。

動的クロック切り替え回路の制御はソフトウェアによって管理されなければなりません。この操作は以下の特徴によって容易にされます。

- 安全な命令: 予期せぬ命令を避けるため、CLKCSRレシブスタのビットを変更するには特別な手続きに従わなければなりません(32頁 の「CLKCSR - クロック制御/状態レジスタ」をご覧ください)

- 排他的な活動: 活動はCLKCSRレジスタに書かれる復号(命令)表によって制御されます。これは1つの命令操作だけが同時に発行 され得ることを保証します。復号表の主な活動は次のとおりです。

- 'クロック元禁止'

- 'クロック元許可'

- 'クロック有効性要求'

- 'クロック元切り替え'

- 'システム クロック元回復'

- '自動再設定形態でのウォッチト'ック'許可'

- 命令状況返し: 'クロック有効性要求'命令はCLKCSRレジスタのクロック準備可(CLKRDY)ビット経由で状態を返します。'システム クロック元 回復'命令はクロック選択レジスタ(CLKSELR)で現在のクロック元の符号を返します。この情報は27頁の「クロック切り替 え」で示されるように管理ソフトウェアルーチンで使われます。

#### 4.3.2. クロック選択レシ、スタ (CLKSELR)

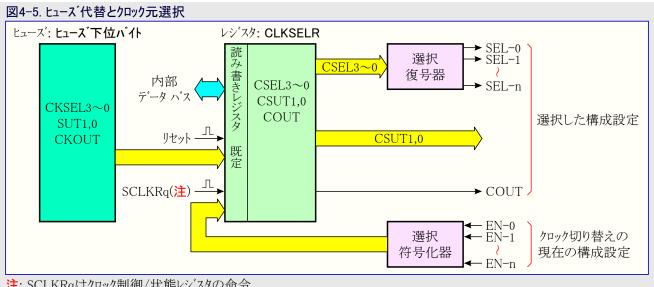

#### 4.3.2.1. ヒュース 代替

リセット中、ヒュース、下位ハイトのビットがクロック選択レシ、スタ(CLKSELR)に複写されます。その後、このレシ、スタの内容はヒュース、下位ハイトからの 既定値を上書きするように使用者変更することができます。図4-5.で示されるようにCKSEL3~0、SUT1,0、CKOUTのヒューズは各々 CLKSELRレシ、スタのクロック元選択(CSEL3~0)、クロック始動時間(CSUT1,0)、クロック出力(COUT)に対応します。

#### 4.3.2.2. クロック元選択

利用可能なクロック元の符号は22頁の表4-1.で与えられます。

注: SCLKRgはクロック制御/状態レシブスタの命令

CLKSELRレシ、スタは、クロック元許可/禁止、、クロック有効性要求、または、クロック元切り替え、の命令によって使われるクロック元選択(CSEL3~ 0)、クロック始動時間(CSUT1,0)、クロック出力(COUT)の値を含みます。

#### 4.3.2.3. クロック元回復

'システム クロック元回復'命令はCLKSELRレシ'スタのCKSEL領域を更新します(次頁の「システム クロック元回復」をご覧ください)。

#### 4.3.3. クロック元許可/禁止

'クロック元許可'命令はクロック選択(CLKSELR)レジスタの設定によって構成設定されたクロック元を選択して許可します。(丁度CKSELとSUT のヒューズ ビットが行うように)クロック元選択(CSEL3~0)がクロック元を選び、クロック始動時間(CSUT1,0)が始動時間を選びます。クロック元が動いていることを保証するために、'クロック元許可'命令の後で'クロック有効性要求'命令が実行されなければなりません。これは有効なクロックが操作可能で利用可能なことをクロック制御/状態レジスタ(CLKCSR)のクロック準備可(CLKRDY)ビット経由で示します。

'クロック元禁止'命令はCLKSELRレジスタ(CSEL3~0のみ)の設定によって示されるクロック元を禁止します。そのクロック元がシステム クロックを駆動するのに使われていたものなら、その命令は実行されません。

選択した構成設定がクロック供給元レヘ・ルでラッチされるため、与えられた時間で多くのクロック元を許可することが可能です(例:システム クロック用内蔵RC発振器+外部クリスタル用発振器)。使用者(コート・)にはこの管理の責任があります。

# 4.3.4. COUT命令

'CKOUT'命令はCLKOt'ンの駆動を許します。使用については25頁の「**4.2.7. クロック出力緩衝部 (外部クロック出力**)」を参照してください。

#### 4.3.5. クロック有効性

'クロック有効性要求'命令は選択したクロック元(CSEL3~0)によって駆動されるハードウェア発振周期計数器を許可します。計数限界値は CSUT1,0の設定によって決められます。クロックは計数限界値に達した時に準備可(クロック準備可(CLKRDY)=1)を宣言されます。CLKR DYフラグは計数開始時にリセットされます。一旦設定されると、このフラグは新しい計数が指示されるまで無変化に留まります。この検査を実行するために、CSELとCSUTの領域は操作が動作中の間、変更すべきではありません。

以下のように2つの使い方が可能です。

一旦新しいクロック元が選択される('クロック元許可'命令)と、計数手順が自動的に開始されることに注意してください。使用者(コート)は新しく選択するクロックを使う前にクロック制御/状態レジスタ(CLKCSR)のCLKRDYフラグの設定(1)を待つべきです。

何時でも、使用者(コード)はクロック元の有効性を問うことができます。使用者(コード)はCLKCSRレジスタに'クロック有効性要求'命令を書くことによってそれを要求することができます。従ってクロック元の状態の完全なポーリングを行うことができます。

# 4.3.6. システム クロック元回復

'システム クロック元回復'命令は**表4-1**.に対するようにシステム クロックを駆動するのに用いる現在のクロック元を返します。その後にクロック選択 (CLKSELR)レシ、スタのクロック元選択(CSEL3~0)領域がこの返された値で更新されます。使われるSUTの情報やCKOUTの状態はありません。

# 4.3.7. クロック切り替え

システム クロックを駆動するために、使用者は現在のクロック元から以下の他のどの1つ(それらの1つが現在のクロック元です)にも切り替えることができます。

- 1. 8.0MHz校正付き内蔵RC発振器

- 2. ウォッチト、ック、用128kHz内部発振器

- 3. 外部クロック信号

- 4. 外部低周波数クリスタル発振子

- 5. 外部クリスタル発振子/セラミック振動子

クロック切り替えは命令の流れで実行されます。最初に、使用者(コード)は新しいクロック元が動作中であることを保証しなければなりません。その後に'クロック元切り替え'命令を発行することができます。'システム クロック元回復'命令を用いて一旦この命令が成功裏に完了されると、使用者(コード)は直前のクロック元を停止することができます。

一旦割り込みが禁止されている場合にだけ、この手順を動かすことが強く推奨されます。使用者(コード)にはこのクロック切り替え手順の正しい実行の責任があります。

これはこのような命令の手順を記述する"軽い"C言語コートです。

```

C言語プログラム例

void ClockSwiching (unsigned char clk_number, unsigned char sut) {

#define CLOCK RECOVER

0x05

#define CLOCK_ENABLE

0x02

#define CLOCK_SWITCH

0x04

#define CLOCK_DISABLE

0x01

unsigned char previous_clk, temp;

// 全割り込み禁止

asm ("cli"); temp = SREG;

// 現在のシステム クロック元保存

CLKCSR = 1 << CLKCCE;

CLKCSR = CLOCK RECOVER;

previous clk = CLKSELR & 0x0F;

// "クロック元許可"命令

CLKSELR = ((sut \ll 4) \& 0x30) | (c1k_number \& 0x0F);

CLKCSR = 1 << CLKCCE;

CLKCSR = CLOCK_ENABLE;

// クロック有効性待ち

while ((CLKCSR & (1 << CLKRDY)) == 0);

// "クロック元切り替え"命令

CLKCSR = 1 << CLKCCE;

CLKCSR = CLOCK SWITCH;

// 切り替え効果待ち

while (1) {

CLKCSR = 1 << CLKCCE;

CLKCSR = CLOCK_RECOVER;

if ((CLKSELR \& 0x0F) == (c1k_number \& 0x0F)) break;

// "クロック元禁止"命令

CLKSELR = previous_clk;

CLKCSR = 1 << CLKCCE;

CLKCSR = CLOCK_DISABLE;

// 全割り込み再許可

SREG = temp; asm ("sei");

```

#### 警告:

ATtiny87/167では、3つの外部クロック元の内の1つだけが与えられた時に許可することができます。また、外部クロックと外部低周波数発振器の許可は非同期タイマ/カウンタと共用されます。

#### 4.3.8. クロック監視

安全なシステムはそのクロック元を監視する必要があります。以下の2つの領域が監視を必要とします。

- ・ 周辺機能用クロック元

- ・システム クロック生成用クロック元

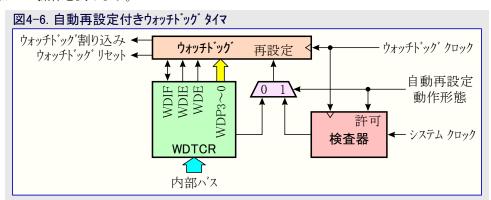

最初の領域で、使用者(コート)はクロックの有効性を容易に検査することができます(27頁の「COUT命令」をご覧ください)。 2つ目の領域で、クロックなしはコート・走行なしに帰着します。故に、システム クロックの存在はハート・ウェアによって監視されることが必要です。 チップ・上のウォッチト・ック・の使用がこの監視を許します。通常、ウォッチト・ック・の再設定はコート・が或る特定のラヘ・ルに達する場合にだけ実行され、これらのラヘ・ルへの到達はシステム クロックが走行していることを証明します。 さもなければ、ウォッチト・ック・リセットが許可されます。この動きはクロック監視と見做すことができます。

標準的なウォッチドッグ機能が求められないなら、ATtiny87/167のウォッチドッグは完全なソフトウェア ウォッチドッグ処理部の複雑さに頼らずに、 監視されることをシステム クロックに許します。ATtiny87/167で提案される解決策は作業の先頭に於いて1つの命令だけでウォッチドッグ再 設定を自動化することです。 故に、システム クロックを監視するため、使用者は以下の2つの任意選択を持ちます。

- 1. 標準的なウォッチト、ック、機能の使用(ソフトウェア再設定)

- 2. または、自動的な再設定(ハート・ウェア再設定)

この2つの任意選択は排他的です。

注: 警告: これら2つの任意選択はリセットでのクロック元が内部供給元の場合にだけ意味を成します。 ヒューズ設定がこの操作を決めます。

'自動再設定形態でウォッチト`ック`許可'命令は標準のウォッチト`ック`許可を超える優先権を持ちます。この動作形態ではウォッチト`ック`のリセット機能だけが許可されます(もはやウォッチト`ック`割り込みはありません)。ウォッチト`ック`制御レシ、スタ(WDTCR)のウォッチト`ック`タイマ前置分周選択(WDP3~0)ビットが常にウォッチト`ック`タイマの前置分周を決めます。

'自動再設定形態でウォッチト'ック'許可'命令を実行する前にウォッチト'ック'が活性でないとき、外部クロック元へ切り替える前にこの命令を活性にすることが推奨されます(上の警告をご覧ください)。

- 注:・(ウォッチドック゛リセットを含む)リセットだけがこの機能を禁止します。ウォッチドック゛システム リセット フラク(MCU状態レジスタ(MCUSR)のWDRF) はリセット発生を監視することができます。

- (ウォッチドック<sup>\*</sup> クロック周波数×4)と等しい、またはより大きなクロック周波数だけを監視することができます。

これは自動クロック監視を用いるクロック切り替え関数の"軽い"C言語コードです。

```

C言語プログラム例

void ClockSwiching (unsigned char clk_number, unsigned char sut) {

#define CLOCK RECOVER

0x05

#define CLOCK_ENABLE

0x02

#define CLOCK_SWITCH

0x04

#define CLOCK_DISABLE

0x01

#define WD_ARL_ENABLE

0x06

#define WD_2048CYCLES

0x07

unsigned char previous_clk, temp;

// 割り込み禁止

temp = SREG; asm ("cli");

// 現在のシステム クロック元保存

CLKCSR = 1 << CLKCCE;

CLKCSR = CLOCK_RECOVER;

previous_clk = CLKSELR & 0x0F;

// 新しいクロック元許可

CLKSELR = ((sut \ll 4) \& 0x30) | (c1k_number \& 0x0F);

CLKCSR = 1 << CLKCCE;

CLKCSR = CLOCK ENABLE;

// クロック有効待機

while ((CLKCSR & (1 << CLKRDY)) == 0);

// 自動再設定動作形態でウォッチドッグ許可

WDTCSR = (1 \ll WDCE) \mid (1 \ll WDE);

WDTCSR = (1 \ll WDE) \mid WD_2048CYCLES;

CLKCSR = 1 << CLKCCE;

CLKCSR = WD_ARL_ENABLE;

// クロック元切り替え

CLKCSR = 1 << CLKCCE;

CLKCSR = CLOCK_SWITCH;

// 切り替え有効待機

while (1) {

CLKCSR = 1 << CLKCCE;

CLKCSR = CLOCK RECOVER;

if ((CLKSELR \& 0x0F) == (c1k_number \& 0x0F)) break;

// 不要クロック元停止

if (previous_clk != (clk_number & 0x0F)) {

CLKSELR = previous_clk;

CLKCSR = 1 << CLKCCE;

CLKCSR = CLOCK DISABLE;

// 割り込み再許可

SREG = temp;

```

# 4.4. システム クロック前置分周器

#### 4.4.1. 特徴

ATtiny87/167のシステム クロックはクロック前置分周レジスタ(CLKPR)の設定によって分周することができます。この特徴(機能)は必要とされる処理能力が低い時の消費電力削減に使えます。これは全クロック種別で使え、CPUと全同期周辺機能のクロック周波数に影響を及ぼします。clk<sub>CPU</sub>、clk<sub>FLASH</sub>、clk<sub>I/O</sub>、clk<sub>ADC</sub>は表4-10.で示された係数によって分周されます。

#### 4.4.2. 切り替え時間

前置分周器設定間を切り替えるとき、システム クロック前置分周器は中間(経過途中)の周波数が直前の設定に対応するクロック周波数または新規設定に対応するクロック周波数のどちらよりも高くなく、クロック系で不整合が起きないことを保証します。前置分周器として実行するリプル計数器は分周されないクロック周波数で走行し、CPUのクロック周波数よりも速いかもしれません。従って例え(計数器値が)読めるとしても、前置分周器の状態を決めることはできず、1から他へのクロック分周値切り替えを行う正確な時間は必ずしも予測できません。CLKPS値が書かれる時から新規クロック周波数が活性(有効)になる前にT1+T2~T1+2×T2間かかります。この間で2つの有効なクロック端が生成されます。ここでのT1は直前のクロック周期、T2は新規前置分周器設定に対応する周期です。

# 4.5. クロック関係レジスタ

#### 4.5.1. OSCCAL - 発振校正レジスタ (Oscillator Calibration Register)

| ピット        | 7    | 6          | 5    | 4    | 3    | 2    | 1    | 0    |        |  |  |  |

|------------|------|------------|------|------|------|------|------|------|--------|--|--|--|

| (\$66)     | CAL7 | CAL6       | CAL5 | CAL4 | CAL3 | CAL2 | CAL1 | CAL0 | OSCCAL |  |  |  |

| Read/Write | R/W  | R/W        | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |        |  |  |  |

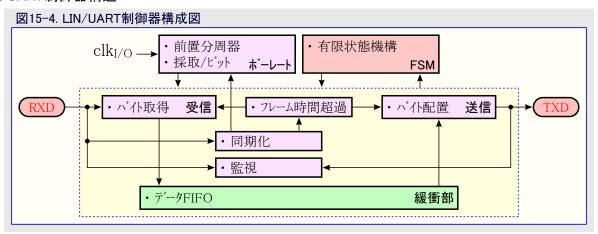

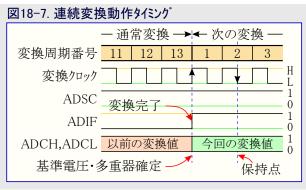

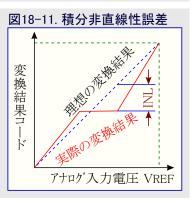

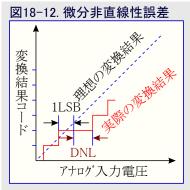

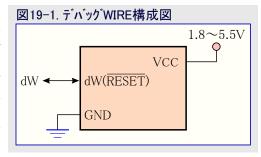

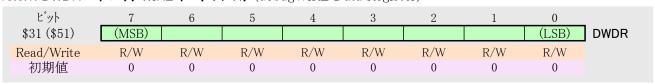

| 初期値        |      | デバイス固有の校正値 |      |      |      |      |      |      |        |  |  |  |