# ATxmega128A1U/64A1U

# XMEGA® A1U データシート

# 序説

AVR® XMEGA® AUはAVR強化RISC構造に基づく低電力、高性能、周辺機能が豊富な8/16ビット マイクロ コントローラの系統です。XMEGA A1Uは4K~8KバイトのSRAM、2KバイトのEEPROM、8Kバイトまでのブート領域を持つ64Kバイトから128Kバイトまでのフラッシュ メモリの100ピン デバイスです。ATxmegaA1Uデバイスは32MHzの最大周波数で動作します。単一クロック周期で命令を実行することにより、デバイスはMHz当たり1 MIPS(100万命令/秒)近くの単位処理量を達成し、電力消費対処理速度の最適化をシステム設計者に許します。

本書は一般の方々の便宜のため有志により作成されたもので、Microchip社とは無関係であることを御承知ください。しおりの[はじめに]での内容にご注意ください。

© 2018 Microchip Technology Inc. 完全データシート DS40002058A/J4 - 1頁

# 特徴

- 高性能、低消費AVR® XMEGA® 8/16ビット マイクロ コントローラ

- データ メモリと不揮発性プログラム メモリ

- 実装自己書き換え(ISP)可能な64~128Kバイト(32~64K語)フラッシュメモリ

- 4~8Kハイト(2~4K語)ブートコート、領域

- 2KハイトのEEPROM

- 4~8Kバイトの内部SRAM

- 最大16MバイトまでのSRAM用外部バス インターフェース

- 最大128MビットまでのSDRAM用外部バス インターフェース

- 内蔵周辺機能

- 4チャネルのDMA制御器

- 8チャネルの事象システム

- 8つの16ビットタイマ/カウンタ

- 4つの比較チャネルまたは捕獲チャネルを持つ、4つのタイマ/カウンタ

- 2つの比較チャネルまたは捕獲チャネルを持つ、4つのタイマ/カウンタ

- 全てのタイマ/カウンタでの高分解能拡張

- 2つのタイマ/カウンタでの新波形拡張

- 1つのUSB装置インターフェース

- USB2.0全速(Full-Speed,12Mbps)と低速(Low-speed,1.5Mbps)装置適合

- 完全な構成設定柔軟性を持つ32個のエンド、オペント

- 1つのUSARTに対するIrDA(赤外線通信)支援を持つ、8つのUSART

- 2重アドレス一致を持つ、4つの2線インターフェース (I<sup>2</sup>CとSMBus適合)

- 4つの直列周辺インターフェース(SPI:Serial Peripheral Interface)周辺機能

- AESとDESの暗号エンジン

- CRC-16(CRC-CCITT)とCRC-32(IEEE 802.3)生成器

- ●独立した発振器を持つ、16ビット実時間計数器

- 16チャネル、12ビット、2M採取/秒の2つのA/D変換器

- 2チャネル、12ビット、1M採取/秒の2つのD/A変換器

- 窓比較機能と電流源を持つ、4つのアナログ比較器

- 全ての汎用I/Oピンでの外部割り込み

- チップ 上の独立した超低電力発振器付きの設定可能なウォッチト、ック タイマ

- QTouch® ライフ ラリ支援

- 容量性接触釦、滑動部、輪

- 特殊マイクロ コントローラ機能

- 電源ONリセットと設定可能な低電圧検出(BOD)

- PLLと前置分周器を持つ、内部及び外部のクロック任意選択

- 設定可能な多段割り込み制御器

- 5つの休止形態動作

- プログラミングとディッグ用インターフェース

- ・境界走査を含むJTAG(IEEE 1149.1適合)インターフェース

- PDI(Program and Debug Interface)

- I/Oと外囲器

- 設定可能な78本のI/O線

- 100リート TQFP、100球BGA、100球VFBGA

- 動作電圧

- 1.6∼3.6V

- 速度性能

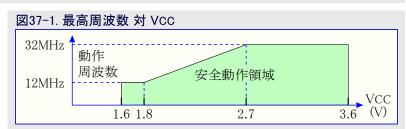

- 0~12MHz/1.6~V

- 0~32MHz/2.7~V

# 目次

|      | 序説 ・・・・・・・・・ 1                                                             |     | 14.1. 要点 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                          |            |

|------|----------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------|------------|

|      | 特徴2                                                                        |     | 14.2. 概要 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                          |            |

| 1.   | <b>注文情報 · · · · · · · · · · · · · · · · · · ·</b>                          |     | 14.3. 割り込みベクタ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                     |            |

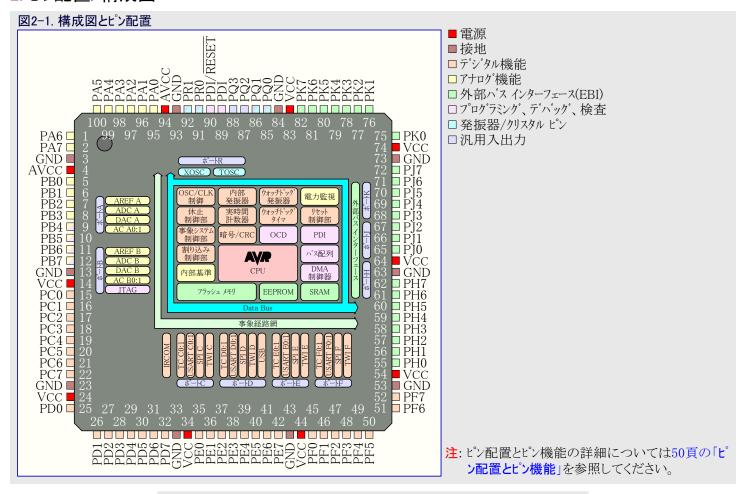

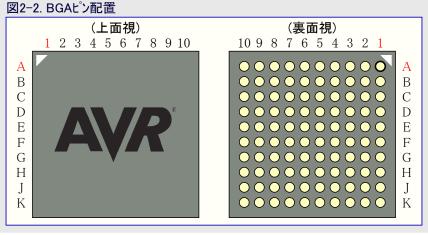

| 2.   | ピン配置/構成図 ・・・・・・・・・・・ 6                                                     | 15. | 入出力ポート・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                            | 27         |

|      | 概要 ••••• 7                                                                 |     | 15.1. 要点                                                                              | 27         |

| ٥.   | 3.1. 構成図                                                                   |     | 15.2. 概要                                                                              | 27         |

| 4    | 資料                                                                         |     | 15.3. 出力駆動部 ····································                                      |            |

|      | 4.1. 推奨読み物 ····································                            |     | 15.5. 交換术一ト機能 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                    |            |

| 5    | 容量性接触感知・・・・・・・・・・・・・・・・・9                                                  | 16  | TCO/1 - 16ビット タイマ/カウンタ0型と1型・・・・・・                                                     |            |

|      | AVR CPU 10                                                                 | 10. | 16.1. 要点・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                          |            |

| Ο.   | 6.1. 要点····································                                |     | 16.2. 概要 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                          |            |

|      | 6.2. 概要・・・・・・・・・・・10                                                       | 17  | TC2 - タイマ/カウンタ2型 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                 |            |

|      | 6.3. 構造概要・・・・・・・・・・・10                                                     | 17. | 17.1. 要点・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                          | ა⊿<br>. ვე |

|      | 6.4. 算術論理演算器 (ALU) · · · · · · · · · · · · · · · · · · ·                   |     | 17.2. 概要 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                          |            |

|      | 6.5. プログラムの流れ・・・・・・・・・・11                                                  | 18  | AWeX - 新波形拡張                                                                          |            |

|      | 6.6. ステータス レジスタ ・・・・・・・・・・・11                                              | 10. | 18.1. 要点                                                                              |            |

|      | <b>6.7.</b> スタックとスタック ポインタ ・・・・・・・・・・ 11                                   |     | 18.2. 概要 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                          |            |

|      | 6.8. レジスタファイル・・・・・・12                                                      | 19  | Hi-Res - 高分解能拡張 · · · · · · · · · · · · · · · · · · ·                                 |            |

| 7.   | <b>メモリ</b>                                                                 |     | 19.1. 要点 ·······                                                                      |            |

|      | 7.1. 要点                                                                    |     | 19.2. 概要 ••••••                                                                       |            |

|      | <b>7.2.</b> 概要 ・・・・・・・・・・・ 13 <b>7.3.</b> フラッシュ プログラム メモリ ・・・・・・・・・ 13     | 20. | RTC - 16ビット実時間計数器 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                | 35         |

|      | 7.3. フラッシュ ブログラム メモリ・・・・・・・・・・・・ 13<br>7.4. ヒュース と施錠ビット・・・・・・・・・・・・・・・・ 14 |     | 20.1. 要点                                                                              | 35         |

|      | 7.4. こユース と他 蜒 に ツト・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                     |     | 20.2. 概要                                                                              |            |

|      | 7.6. EEPROM · · · · · · · · · · · · · · · · · · ·                          | 21. | USB - 万能直列バス インターフェース ・・・・・・・・                                                        | 36         |

|      | 7.7. I/Oメモリ · · · · · · · · · · · · · · · · · · ·                          |     | 21.1. 要点                                                                              | 36         |

|      | <b>7.8.</b> 外部メモリ・・・・・・・・・・・・・・・15                                         |     | 21.2. 概要                                                                              |            |

|      | 7.9. データ メモリとバス調停 ・・・・・・・・・・15                                             | 22. | TWI - 2線インターフェース ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                 |            |

|      | 7.10. メモリ タイミング・・・・・・・・・・・15                                               |     | 22.1. 要点                                                                              |            |

|      | 7.11. デバイスIDと改訂 ····· 15                                                   |     | 22.2. 概要 ••••••                                                                       |            |

|      | 7.12. I/Oメモリ保護 ・・・・・・・・・・・15                                               | 23. | SPI - 直列周辺インターフェース ・・・・・・・・・・・・・・・・・                                                  |            |

|      | 7.13. JTAG禁止・・・・・・・・・・・ 16<br>7.14. フラッシュ メモリとEEPROMのヘ゜ーシ・容量・・・・・・・ 16     |     | 23.1. 要点                                                                              |            |

| 0    | DMAC - 直接メモリ入出力制御器 ・・・・・・・ 17                                              |     | 23.2. 概要                                                                              |            |

| ο.   | 8.1. 要点 ············· 17                                                   | 24. | USART                                                                                 |            |

|      | 8.2. 概要                                                                    |     | 24.1. 要点     24.2. 概要                                                                 | 39         |

| a    | 事象システム・・・・・・・・18                                                           | 0.5 | · · · · · · · · · · · · · · · · · · ·                                                 |            |

| J.   | 9.1. 要点 ···································                                | 25. | IRCOM - 赤外線通信単位部 · · · · · · · · · · · · 25.1. 要点 · · · · · · · · · · · · · · · · · · | 40         |

|      | 9.2. 概要 ・・・・・・・・・・・ 18                                                     |     | 25.2. 概要 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                          | 40         |

| 10.  | システム クロックとクロック選択 ・・・・・・・・・ 19                                              | 26  | AESとDESの暗号エンジン・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                     |            |

|      | 10.1. 要点                                                                   | 20. | 26.1. 要点 ···································                                          | 41         |

|      | 10.2. 概要 ・・・・・・・・・・19                                                      |     | 26.2. 概要                                                                              | 41         |

|      | <b>10.3</b> . <b>クロック元</b> ・・・・・・・・・・・・・20                                 | 27  | CRC - 巡回冗長検査生成器 ·······                                                               |            |

| 11.  | 電力管理と休止形態動作 ・・・・・・・・ 21                                                    | 27. | 27.1. 要点                                                                              | 42         |

|      | 11.1. 要点 ・・・・・・・・・・・・・・・ 21                                                |     | 27.1. 要点       27.2. 概要                                                               | 42         |

|      | 11.2. 概要                                                                   | 28. | EBI - 外部バス インターフェース ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                              | 43         |

|      | 11.3. 休止形態動作                                                               |     | 28.1. 要点                                                                              |            |

| 12.  | システム制御とリセット ・・・・・・ 22                                                      |     | 28.2. 概要                                                                              |            |

|      | 12.1. 要点                                                                   | 29. | ADC - 12ビット A/D変換器 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                               | 44         |

|      | <b>12.2</b> . 概要 ・・・・・・・・・・・・ 22<br><b>12.3</b> . リセットの流れ ・・・・・・・・・・ 22    |     | 29.1. 要点 ***********************************                                          | 44         |

|      | 12.3. リセットの流れ ・・・・・・・・・・・・・ 22<br>12.4. リセット元 ・・・・・・・・・・ 22                |     | 29.2. 概要                                                                              |            |

| 12   | WDT - ウォッチトック タイマ · · · · · · · · · · · · · · · · · · ·                    | 30. | DAC - 12ビット D/A変換器 ・・・・・・・・・・・・                                                       | 46         |

| ıδ.  | 13.1. 要点 ···································                               |     | 30.1. 要点 ***********************************                                          | 46         |

|      | 13.2. 概要                                                                   |     | 30.2. 概要                                                                              |            |

| 14   | 割り込みと設定可能な多段割り込み制御器・・25                                                    | 31. | AC - アナログ比較器 · · · · · · · · · · · · · · · · · · ·                                    | 47         |

| . 7. | ロップニップ CIRX にも BEの タイスロップニップ 中国 PP 国 20                                    |     | 31.1. 要点 · · · · · · · · · · · · · · · · · ·                                          | 47         |

|      |                                                                            |     |                                                                                       |            |

|     |                | 概要 ••••••                                               |           |

|-----|----------------|---------------------------------------------------------|-----------|

| 32. | PDI -          | プログラミングとテブバッグ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・       | 49        |

|     | 32.1.          | 要点                                                      | 49        |

|     | 32.2.          | 概要 ••••••                                               | 49        |

| 33. | ピン配            | 置とピン機能 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・             | 50        |

|     | 33.1.          | 交換ピン機能の種類・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・           | 50        |

|     | 33.2.          | 交換ピン機能・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・              | 51        |

| 34. | 周辺村            | 幾能単位部アドレス割り当て・・・・・・・                                    | ••• 55    |

| 35. | 命令-            | - 式要約 · · · · · · · · · · · · · · · · · · ·             | 56        |

| 36. | 外囲             | 器情報 ••••••                                              | 59        |

|     | 36.1.          | 100'J-F, TQFP                                           | 59        |

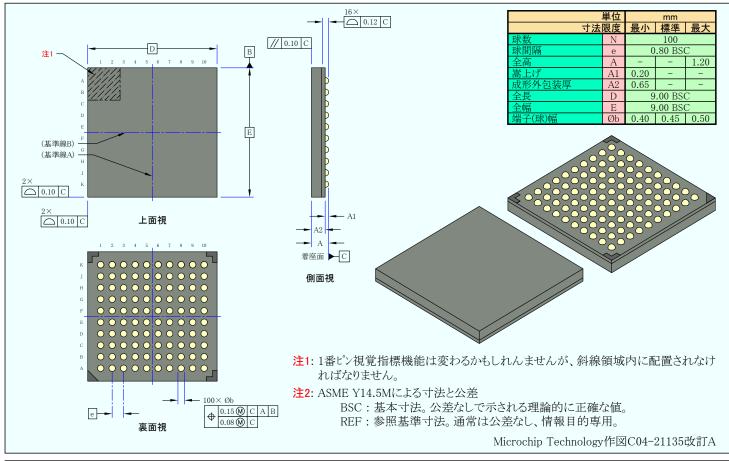

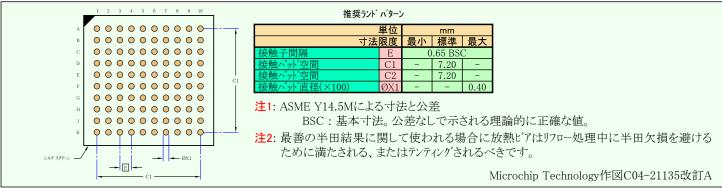

|     | 36.2.          | 100球TFGBA ······                                        | 60        |

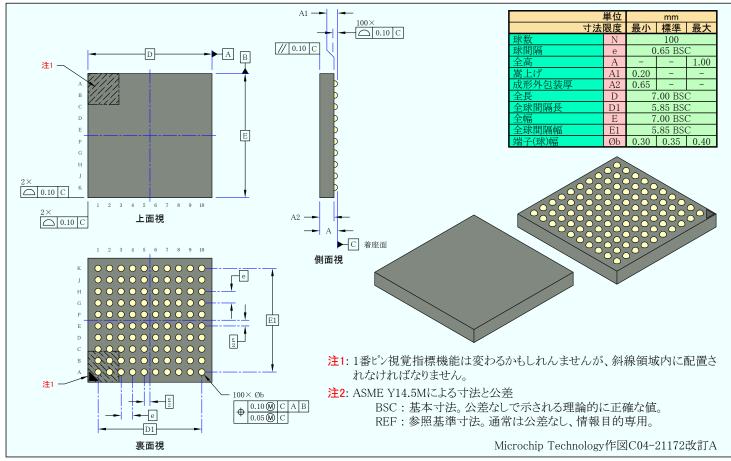

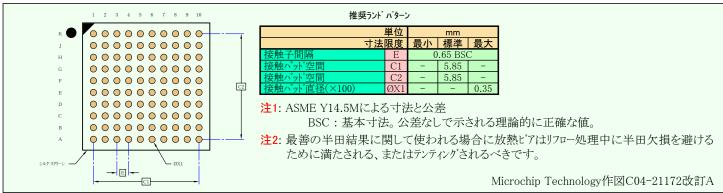

|     | 36.3.          | 100球VFGBA ······                                        |           |

| 37. | 電気             | 的特性•••••                                                | 62        |

|     | 37.1.          | ATxmega64A1U · · · · · · · · · · · · · · · · · · ·      | 62        |

|     | 37.2.          | ATxmega128A1U · · · · · · · · · · · · · · · · · · ·     | 77        |

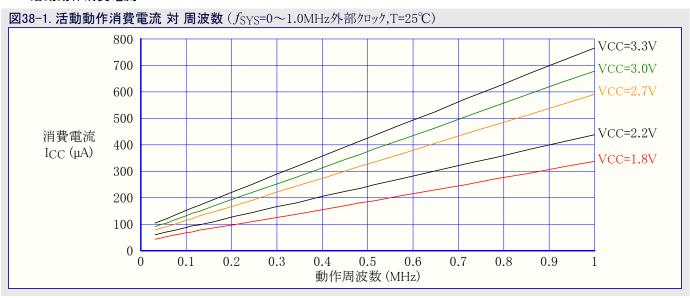

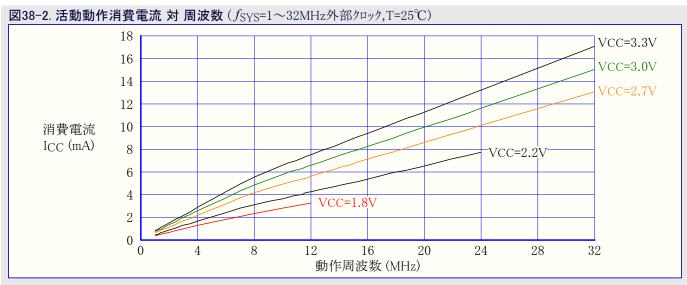

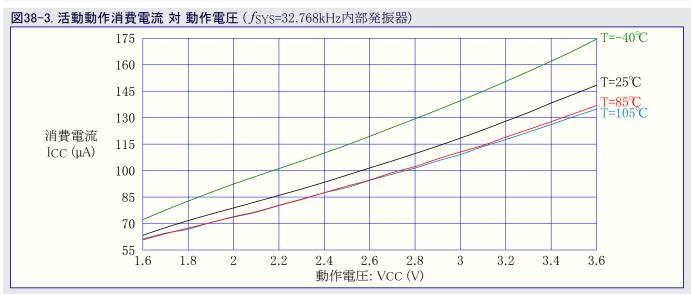

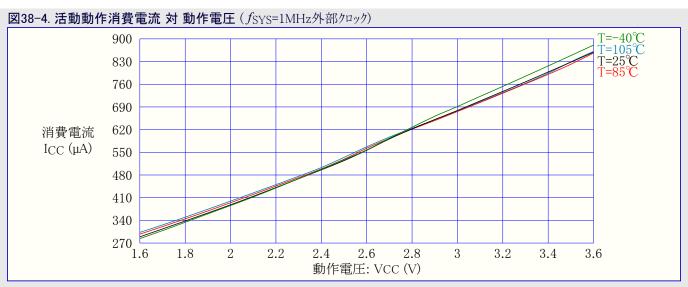

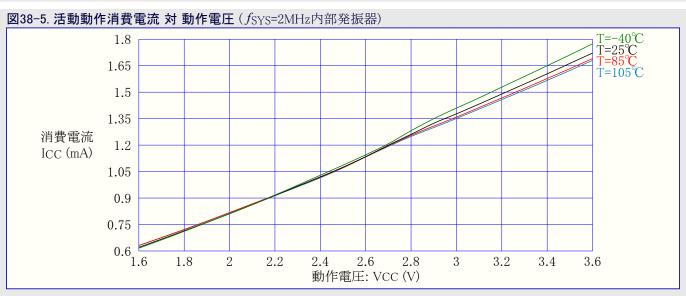

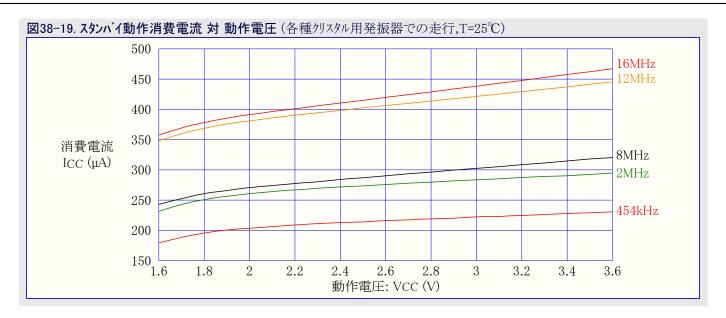

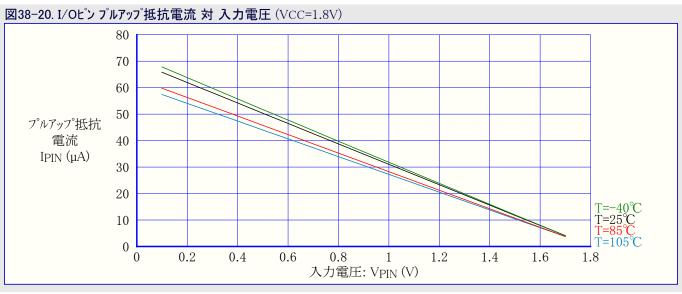

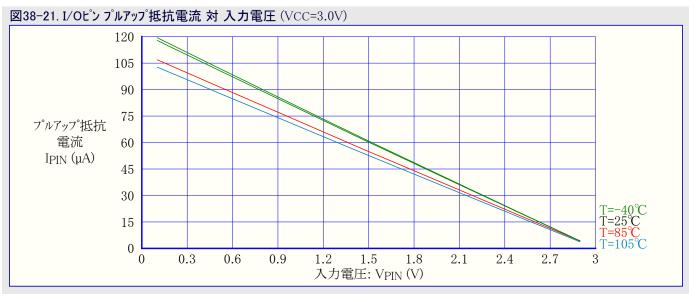

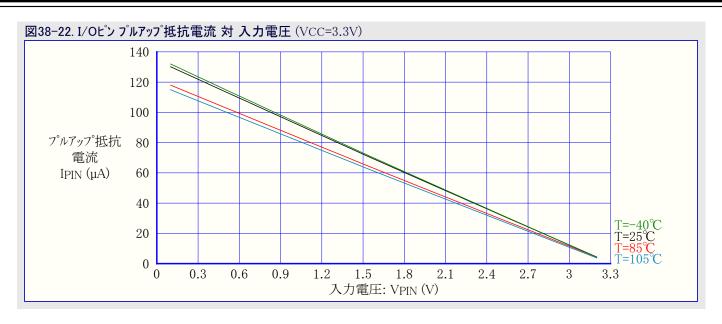

| 38. | 代表特            | 寺性 · · · · · · · · · · · · · · · · · · ·                | • • • 92  |

|     | 38.1.          | ATxmega64A1                                             | 92        |

|     | 38.2.          | ATxmega128A1U · · · · · · · · · · · · · · · · · · ·     | ••• 120   |

| 39. | 障害性            | 青報                                                      | • 148     |

|     | 39.1.          | <br>シリコン問題要約 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・       | ••• 148   |

|     | 39.2.          | デバイス・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                |           |

|     | 39.3.          | システム クロックとクロック選択 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・   | ••• 149   |

|     | 39.4.          | AWeX - 新波形生成拡張 ······                                   | 149       |

|     | 39.5.          | RTC - 16ビット実時間計数器 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・  | 150       |

|     | 39.6.          | USB - 万能直列バス インターフェース ・・・・・・・                           | ••• 150   |

|     | 39.7.          | TWI - 2線インターフェース・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・     |           |

|     | 39.8.          | USART - 万能同期/非同期送受信器・・・                                 | 151       |

|     | 39.9.          | ADC - 12ピットA/D変換器 · · · · · · · · · · · · · · · · · · · | · • • 151 |

| 40  | 39.10.         | /                                                       | 152       |

| 40. |                | /一ト改訂復歴 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・            |           |

|     | 40.1.<br>40.2. | 8385B - 2011年11月 · · · · · · · · · · · · · · · · · ·    | 153       |

|     | 40.2.<br>40.3. | 8385C - 2012年7月 · · · · · · · · · · · · · · · · · · ·   | 150       |

|     | 40.3.<br>40.4. | 8385D - 2012年7月 · · · · · · · · · · · · · · · · · · ·   | 150       |

|     | 40.4.          | 8385E - 2012年11月 · · · · · · · · · · · · · · · · · ·    | 159       |

|     | 40.6.          | 8385F - 2012年12月 ····································   |           |

|     | 40.7.          | 8385G - 2013年11月 · · · · · · · · · · · · · · · · · ·    | 153       |

|     | 40.8.          | 8385H - 2014年4月 · · · · · · · · · · · · · · · · · · ·   | ••• 153   |

|     | 40.9.          | 8385I - 2014年9月                                         |           |

|     | 40 10          | 改訂A - 2018年8目 ······                                    |           |

# 1. 注文情報

| 注文符号                             | フラッシュ       | EEPROM | SRAM | 外囲器 (注1,2,3)             | 速度(MHz) | 電源電圧      | 温度          |

|----------------------------------|-------------|--------|------|--------------------------|---------|-----------|-------------|

| ATxmega64A1U-AU                  | 64KB+4KB    | 2KB    | 4KB  |                          |         |           |             |

| ATxmega64A1U-AUR ( <b>注4</b> )   | O4IVD+4IVD  | 2110   | HIVD | 100A                     |         |           |             |

| ATxmega128A1U-AU                 | 128KB+8KB   | 2KB    | 8KB  | 100/4                    |         |           |             |

| ATxmega128A1U-AUR ( <b>注4</b> )  | 120KD+0KD   | ZIXD   | OIXD |                          |         |           |             |

| ATxmega64A1U-CU                  | 64KB+4KB    | 2KB    | 4KB  |                          |         |           |             |

| ATxmega64A1U-CUR ( <b>注4</b> )   | O4IVD+4IVD  | 2110   | 417D | 100C1 ( <b>注5</b> )      | 32      | 1.6~3.6V  | -40°C∼85°C  |

| ATxmega128A1U-CU                 | 128KB+8KB   | 2KB    | 8KB  | 100C1 ( <del>/±</del> 3) | 32      | 1.0 -5.00 | 40 C -00 C  |

| ATxmega128A1U-CUR ( <b>注4</b> )  | 120101010   | ZIND   | OIXD |                          |         |           |             |

| ATxmega64A1U-C7U                 | 64KB+4KB    | 2KB    | 4KB  |                          |         |           |             |

| ATxmega64A1U-C7UR ( <b>注4</b> )  | OTITO TIND  | 2110   | TIND | 100C2                    |         |           |             |

| ATxmega128A1U-C7U                | 128KB+8KB   | 2KB    | 8KB  | 10002                    |         |           |             |

| ATxmega128A1U-C7UR ( <b>注4</b> ) | 120KD+0KD   | 2110   | OIXD |                          |         |           |             |

| ATxmega128A1U-AN                 |             |        |      | 100A                     |         |           |             |

| ATxmega128A1U-ANR ( <b>注4</b> )  | 128KB+8KB   | 2KB    | 8KB  | 100/1                    | 32      | 1.6~3.6V  | -40°C∼105°C |

| ATxmega128A1U-CN                 | 120100 0100 | 2110   | OIND | 100C1 ( <b>注5</b> )      | 32      | 1.0 5.00  | 40 C 100 C  |

| ATxmega128A1U-CNR ( <b>注4</b> )  |             |        |      | 10001 (710)              |         |           |             |

注1: このデバイスはウェハー(チップ単体)形状でも供給できます。詳細な注文情報については最寄のMicrochip営業所へお問い合わせください。

注2: 有害物質使用制限に関する欧州指令(RoHS指令)適合の鉛フリー製品。またハロケン化合物フリーで完全に安全です。

注3: 外囲器情報については59頁の「外囲器情報」をご覧ください。

**注4**: テープ とリール。

注5: この外囲器はもはや利用できません。

- より多くの情報については生産終了(EOL)を参照してください。: www.microchip.com/product-changenotifications/#/1912 9/ASER-31SUSF550

|       | 外囲器形式                                                      |  |  |  |  |  |  |

|-------|------------------------------------------------------------|--|--|--|--|--|--|

| 100A  | 100A 100リート、14×14×1.0mm厚 0.5mmピッチ 薄型プラスティック4方向平板外囲器 (TQFP) |  |  |  |  |  |  |

| 100C1 | 100C1 100球、薄細密球格子配列外囲器(B2B) - 9×9×1.2mm本体 (TFBGA)          |  |  |  |  |  |  |

| 100C2 | 100C2 100球 7×7×1.0mm本体 0.65mmピッチ 極薄細密球格子配列外囲器 (VFBGA)      |  |  |  |  |  |  |

# 代表的な応用

| ・工業制御    | ・環境制御 | ・低電力電池応用              |

|----------|-------|-----------------------|

| III I II | N     | . <del></del> , , , , |

・工場自動化

・RFとZigBee<sup>®</sup>

・電力ツール

・建築制御

・USB接続性

・室内環境制御(HVAC)

・基板制御・感知器制御・実用計器・白物家電・光学・医療応用

# 2. ピン配置/構成図

| 表2- | 表2-1. BGA ピン配列 |     |               |          |     |     |     |     |     |     |

|-----|----------------|-----|---------------|----------|-----|-----|-----|-----|-----|-----|

|     | 1              | 2   | 3             | 4        | 5   | 6   | 7   | 8   | 9   | 10  |

| Α   | PK0            | VCC | GND           | PJ3      | VCC | GND | PH1 | GND | VCC | PF7 |

| В   | PK3            | PK2 | PK1           | PJ4      | PH7 | PH4 | PH2 | PH0 | PF6 | PF5 |

| С   | VCC            | PK5 | PK4           | PJ5      | PJ0 | PH5 | PH3 | PF2 | PF3 | VCC |

| D   | GND            | PK6 | PK7           | PJ6      | PJ1 | PH6 | PF0 | PF1 | PF4 | GND |

| Е   | PQ0            | PQ1 | PQ2           | PJ7      | PJ2 | PE7 | PE6 | PE5 | PE4 | PE3 |

| F   | PR1            | PR0 | RESET/PDI_CLK | PDI_DATA | PQ3 | PC2 | PE2 | PE1 | PE0 | VCC |

| G   | GND            | PA1 | PA4           | PB3      | PB4 | PC1 | PC6 | PD7 | PD6 | GND |

| Н   | AVCC           | PA2 | PA5           | PB2      | PB5 | PC0 | PC5 | PD5 | PD4 | PD3 |

| J   | PA0            | PA3 | PB0           | PB1      | PB6 | PC3 | PC4 | PC7 | PD2 | PD1 |

| K   | PA6            | PA7 | GND           | AVCC     | PB7 | VCC | GND | VCC | GND | PD0 |

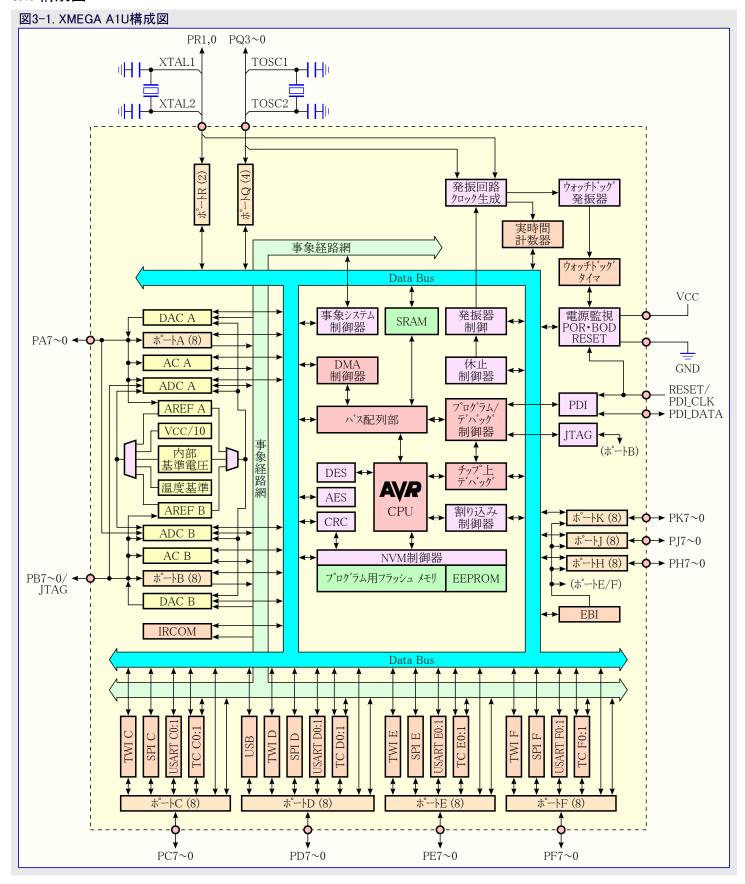

# 3. 概要

AVR XMEGAはAVR強化型RISC構造に基いた、低電力、高性能、豊富な周辺機能の8/16ビットマイクロコントローラ系列です。単一クロック 周期で実行する命令によって、AVR XMEGAデバイスはシステム設計者に対して電力消費対処理速度の最適化を可能とするMHz当た り100万命令に達するCPU単位時間処理能力を達成します。

AVR CPUは32個の汎用作業レジスタを豊富な命令一式に結合します。32個全てのレジスタが算術論理演算器(ALU)へ直接接続され、単一命令でのアクセスを2つの独立したレジスタに許し、単一クロック周期で実行されます。この構造はより大きなコート、効率と同時に伝統的な単一累積器やCISCに基くマイクロコントローラよりも何倍も速い単位時間処理能力達成に帰着します。

AVR XMEGA A1Uデバイスは次の機能、実装書き込み可能な書き中の読み(Read-While-Write)能力を持つフラッシュメモリ、内部のEE PROMとSRAM、4チャネルのDMA制御器、8チャネルの事象システム、設定可能な多段割り込み制御器、78本の汎用入出力線、16ビット実時間計数器(RTC)、比較動作とPWM付きの8つの柔軟な16ビットタイマ/カウンタ、1つのUSB2.0全速(Full-speed)装置インターフェース、8つのUSART、4つの2線直列インターフェース(TWI)、4つの直列周辺インターフェース(SPI)、AESとDESの暗号エンジン、CRC-16(CRC-CCITT)とCRC-32(IEEE 802.3)生成器、設定可能な利得を持つ2つの16チャネル12ビットA/D変換器、2つの2チャネル12ビットD/A変換器、窓動作を持つ4つのアナログ比較器(AC)、独立した内部発振器を持つ設定可能なウォッチドッグ、タイマ、PLLと前置分周器付きの正確な内部発振器、設定可能な低電圧検出(Brown-Out Detection)を提供します。

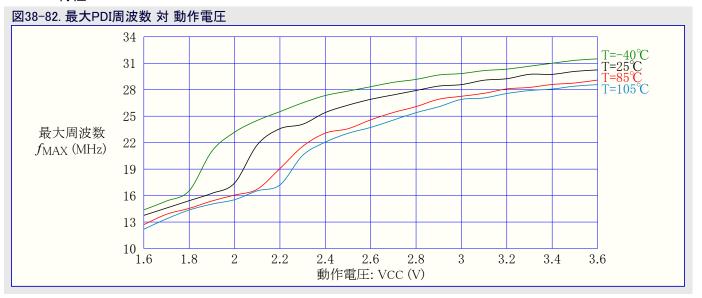

プログラミングとデブッグが用の高速2ピンインターフェースのプログラミングとデブッグインターフェース(PDI)が利用可能です。デブイスはIEEE規格1149.1 適合JTAGインターフェースも持ち、これは境界走査、チップ・上デブッグとプログラミングにも使うことができます。

XMEGA A1Uデバイスはソフトウェアで選択可能な5つの節電動作を持ちます。アイドル動作はCPUを停止する一方、SRAM、DMA制御器、事象システム、割り込み制御器と全ての周辺機能に機能の継続を許します。パワーダウン動作はSRAMとレジスタの内容を保存しますが、発振器を停止し、次のTWI、USB再開(resume)またはピン変化の割り込み、またはリセットまで他の全ての機能を禁止します。パワーセーブ動作では非同期実時間計数器が走行を続けて時間の維持を応用に許す一方、デバイスの残りは休止します。スタンバイ動作ではクリスタル発振子/セラミック振動子用発振器が走行を保つ一方、デバイスの残りは休止します。これは低電力消費と組み合わせた外部クリスタルからの非常に速い始動を可能にします。拡張スタンバイ動作では主発振器と非同期計時器の両方が走行を続けます。更なる消費電力低減のため、各個別周辺機能への周辺機能クロックは活動動作とアイドル動作に於いて任意で停止することができます。

MicrochipはAVRマイクロコントローラへ容量性接触釦、滑動部、輪を組み込むためのQTouchライブラリを提供します。

デバイスはMicrochipの高密度不揮発性メモリ技術を使って製造されています。プログラム用フラッシュメモリはPDIまたはJTAGインターフェースを通して実装書き換えをすることができます。デバイス内で走行するプートローダはフラッシュメモリに応用プログラムを取得格納するのにどのインターフェースをも用いることができます。プートフラッシュ領域内のプートローダ、ソフトウェアは応用フラッシュ領域が更新されている間も走行を続ける、真の「書き中の読み(Read-While-Write)」動作を提供します。実装自己書き換え可能なフラッシュと8/16ビットRISC CPUの結合によって、AVR XMEGAは多くの組み込み応用に対して高い柔軟性と費用効率の解決策を提供する強力なマイクロコントローラ系列です。

全てのAVR XMEGAデバイスはCコンパイラ、マクロ アセンブラ、プログラム デバッカブシミュレータ、書き込み器、評価キットを含む、プログラムとシステム開発ツールの完全な揃えで支援されます。

# 3.1. 構成図

# 4. 資料

開発ツール、応用記述、データシートの包括的な1式はwww.microchip.comでのダウンロートに関して利用可能です。

# 4.1. 推奨読物

- · AVR XMEGA AU手引書

- ・XMEGA応用記述

このデバイス データシートは各単位部と周辺機能の短い記述と共にデバイス固有情報だけを含みます。 XMEGA AU手引書は単位部と周辺機能を広く深く記述します。 XMEGA応用記述はコート 例を含み、単位部と周辺機能を適用する使い方を示します。

全ての資料はwww.microchip.comから利用可能です。

# 5. 容量性接触感知

QTouchライブラリは殆どのAVRマイクロコントローラ上の接触感知インターフェース実現の解決策を使うための単一物を提供します。特許権を持つ充電転移信号採取は強力な感知を提供し、接触キーの完全な反発運動報告を含み、そしてキー事象の明白な検出のための隣接キー抑制™(AKS™)技術を含みます。QTouchライブラリはQTouchとQMatrix採取法に関する支援を含みます。

接触感知はAVRマイクロ コントローラ用の適切なQTouchライブラリをリンクすることによってどの応用にも追加することができます。これは接触 チャネルと感知器を定義するために簡単なAPIの組を用いて行われ、そしてチャネル情報を取得して接触感知器の状態を決めるために接触感知APIを呼び出します。

QTouchライブラリは無料で以下の場所のMicrochipのウェブサイト、www.microchip.comからダウンロードすることができます。実装の詳細とその他の情報についてはMicrochipのウェブサイトからも入手可能な「QTouchライブラリ使用者の手引き」を参照してください。

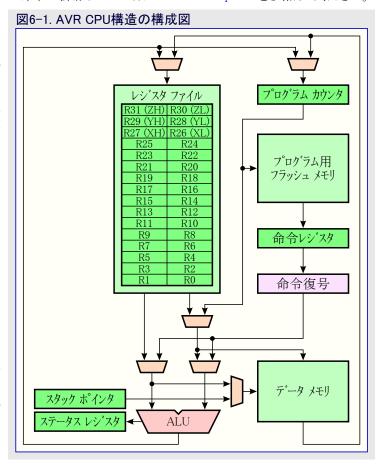

## 6. AVR CPU

# 6.1. 要点

- 8/16ビット高性能AVR RISC CPU

- 142命令

- ハート・ウェア乗算器

- ALUに直結された32個の8ビット レジスタ

- SRAM内のスタック

- I/Oメモリ空間内でアクセス可能なスタック ポインタ

- 16Mバイトまでのプログラムと16Mバイトのデータのメモリを直接アドレス指定

- 16/24ビット レシブスタへの真の16/24ビット入出力

- 8、16、32演算に対する効率的な支援

- システム重要特性の構成設定変更保護

# 6.2. 概要

全てのAVR XMEGAデバイスは8/16ビットAVR CPUを使います。CPUの主な機能は、コードを実行して全ての計算を実行することです。 CPUはメモリ入出力、計算実行、周辺制御、そしてフラッシュメモリ内のプログラムを実行することができます。割り込みの扱いは独立した章で記述され、25頁の「割り込みと設定可能な多段割り込み制御器」を参照してください。

# 6.3. 構造概要

最大性能と並列化のためにAVR CPUはプログラムとデータに対して独立したメモリとハスを持つハーハー・構造を使います。プログラム メモリ内の命令は単一段のパイプラインで実行されます。1つの命令が実行されつつあると同時に、次の命令がプログラム メモリから予め取得されます。これは毎クロック周期で実行される命令を可能にします。全AVR命令の詳細についてはwww.microchip.comを参照してください。

算術論理演算部(ALU:Arithmetic Logic Unit)はレジスタ間または定数とレジスタ間の算術と論理の操作を支援します。単一レジスタ操作をALUで実行することもできます。算術操作後、操作の結果についての情報を反映するためにステータスレジスタが更新されます。

ALUは高速入出力レジスタファイルに直接的に接続されます。32×8ビット汎用作業レジスタの全てがレジスタ間またはレジスタと即値間での単一周期算術論理部(ALU)操作を許す単一クロック周期アクセス時間を持ちます。32個中の6つのレジスタは効率的なアドレス計算を許す、プログラムとデータの空間をアドレス指定するための3つの16ビット アドレスポインタとして使うことができます。

メモリ空間は直線状です。データ メモリ空間とプログラム メモリ空間は2つの異なるメモリ空間です。

データ メモリ空間はI/Oレジスタ、SRAM、外部RAMに分けられます。 加えて、データ メモリ内にEEPROMをメモリ割り当てすることができます。

全てのI/Oの状態と制御のレシ、スタはデータメモリの最下位4Kバイのアト・レスに属します。これはI/Oメモリ空間として参照されます。最下位60アト・レスは直接、または\$00~\$3Fのデータ空間位置としてアクセスすることができます。残りは\$0040~\$0FFFに連なる拡張I/Oメモリ区間です。ここのI/Oレシ、スタは取得(LD/LDS/LDD)と格納(ST/STS/STD)の命令を用いてデータ空間位置としてアクセスされなければなりません。

SRAMはデータを保持します。SRAMからのコード実行は支援されません。SRAMはAVR構造で支援される5つの異なるアドレス指定形態を通して容易にアクセスすることができます。

\$1000~\$1FFFのデータアトレスはメモリ割り当てEEPROM用に予約されています。

プログラム メモリは応用プログラム領域とブート プログラム領域の2つの領域に分けられます。両領域は書き込みと読み書きの保護のための専用の施錠ビットを持ちます。応用フラッシュ メモリの自己プログラミングに使われるSPM命令はブート プログラム領域に属さなければなりません。応用領域は書き込みと読み書きの保護のための独立した施錠ビットを持つ応用表領域を含みます。応用表領域はプログラム メモリ内での不揮発性データの格納を減らすのに使うことができます。

# 6.4. 算術論理演算器 (ALU)

算術論理演算器(ALU)はレシ、スタ間またはレシ、スタと定数間の演算と論理操作を支援します。単一レシ、スタ操作の実行もできます。ALU は32個の汎用レシ、スタ全てとの直接接続で動作します。単一クロック周期内で、汎用レシ、スタ間、またはレシ、スタと即値間の算術操作が実行されて結果がレシ、スタファイルに書き戻されます。算術または論理の操作後、操作結果についての情報を反映するためにステータスレシ、スタが更新されます。

ALU操作は、演算、論理、ビット操作の、3つの主な分野に分けられます。8ビットと16ビットの両方の算術演算が支援され、命令一式は 効率的な32ビット演算の実装を可能にします。ハードウェア乗算器は符号付きと符号なしの両方と固定小数点形式を支援します。

#### 6.4.1. ハート・ウェア乗算器

乗算器は2つの8ビット数値を16ビットの結果に乗算する能力です。ハードウェア乗算器は符号付と符号なしの整数と固定小数点数の種々の変種を支援します。

- 符号なし整数の乗算

- ・ 符号付き整数の乗算

- ・符号付き整数と符号なし整数の乗算

- 符号なし固定小数点数の乗算

- ・ 符号付き固定小数点数の乗算

- ・符号付き固定小数点数と符号なし固定小数点数の乗算

乗算は2 CPUクロック周期かかります。

# 6.5. プログラムの流れ

リセット後、CPUはプログラム用フラッシュ メモリ内の最下位アトレス'\$000000'から命令の実行を始めます。プログラム カウンタ(PC)は取得されるべき次の命令を指示します。

プログラムの流れはアドレス空間全体を直接位置指定できる条件付きと条件なしの分岐(Jump)と呼び出し(Call)命令によって提供されます。殆どのAVR命令は16ビット語形式を用い、一方限られた若干が32ビット形式を使います。

割り込みとサブルーチン呼び出しの間、復帰アドレスのPC(値)がスタックに格納されます。スタックは一般的なデータ用SRAM内に割り当てられ、結果としてスタック容量は総SRAM容量とSRAMの使い方だけによって制限されます。リセット後のスタック ポインタ(SP)は内部SRAM内の最上位アドレスを指し示します。SPはI/Oメモリ空間で読み書きアクセスが可能で、スタックまたはスタック領域の容易な複数実装を可能にします。データ用SRAMはAVR CPUで支援される5つの異なる位置指定種別を通して容易にアクセスすることができます。

#### 6.6. ステータス レシ<sup>\*</sup>スタ

ステータス レジスタ(SREG)は最も直前に実行した演算または論理命令の結果についての情報を含みます。この情報は条件付き操作を実行するためにプログラムの流れを変えるのに使えます。ステータス レジスタは「命令一式手引書」で詳述されるように、全てのALU操作後に更新されることに注目してください。これは多くの場合でそれ用の比較命令使用の必要をなくし、高速でより簡潔なコート、に帰着します。

ステータス レジスタは割り込み処理ルーチン移行時の保存と割り込みからの復帰時の回復が自動的に行われません。これはソフトウェアによって扱われなければなりません。

ステータス レシ、スタはI/Oメモリ空間でアクセスできます。

## 6.7. スタックとスタック ホ°インタ

スタックは割り込みとサブルーチン呼び出し後の復帰アトンスの格納に使われます。一時データの格納にも使えます。スタック ポインタ(SP)レジスタ は常にスタックの先頭(訳注:次に使われるべき位置)を指し示します。これはI/Oメモリ空間でアクセス可能な2つの8ビットレジスタとして実装されます。データはPUSH命令とPOP命令を使ってスタックへ格納とスタックから取得されます。スタックは上位メモリ位置から下位メモリ位置へ増えます。これはスタックへのデータ格納がSPを減らし、スタックからのデータ取得がSPを増すことを意味します。SPはリセット後に自動的に設定され、その初期値は内部SRAMの最上位アトンスです。SPが変更されるなら、それは\$2000番地以上を指し示すように設定されなければならず、そして何れかのサブルーチン呼び出しが実行される前、または割り込みが許可される前に定義されなければなりません。

割り込みまたはサブルーチン呼び出しの間、自動的に復帰アトンスがスタックへ格納されます。復帰アトンスはデバイスのプログラム メモリ量に依存して2または3バイトで有り得ます。128Kバイト以下のプログラム メモリを持つデバイスについては復帰アトンスが2バイトで、故にスタック ポインタは +2/-2されます。128Kバイトを越えるプログラム メモリを持つデバイスについては復帰アトンスが3バイトで、故にSPは+3/-3されます。復帰アトンスはRETI命令を使って割り込みから、またはRET命令を使ってサブルーチン呼び出しから戻る時にスタックから取得されます。

データがPUSH命令でスタックに格納される時にSPは-1され、POP命令を使ってスタックからデータを取得する時に+1されます。

ソフトウェアからのスタック ポーインタ更新時の改変を防ぐため、SPL書き込みは4命令までに対して、または次のI/Oメモリ書き込みまで割り込みを自動的に禁止します。

リセット後、スタック ポインタはSRAMの最高アトレスに初期化されます。15頁の図7-2.をご覧ください。

# 6.8. レジスタ ファイル

レシ、スタ ファイルは単一クロック周期アクセス時間を持つ32個の8ビット汎用作業レシ、スタから成ります。レシ、スタ ファイルは以下の入出力機構を支援します。

- ・1つの8ビット出力オペランドと1つの8ビットの結果入力

- ・2つの8ビット出力オペラントと1つの8ビットの結果入力

- ・2つの8ビット出力オペラントと1つの16ビットの結果入力

- ・1つの16ビット出力オペランドと1つの16ビットの結果入力

32個のレジスタの6つはデータ空間のアトレス指定用の3つの16ビット アトレス レジスタ ポインタとして用いることができ、効率的なアトレス計算を許します。3つのアトレス ポインタの1つはプログラム用フラッシュ メモリ内の参照表用のアトレス ポインタとしても用いることができます。

# 7. メモリ

# 7.1. 要点

- フラッシュ プログラム メモリ

- 1つの直線的なアドレス空間

- 実装書き換え可能(In-System Reprogrammable)

- 自己プログラミングとブートローダ支援

- 応用コート 用応用領域

- 応用コート゛またはテ゛ータ記憶用応用表領域

- 応用コート、またはフートロータ、コート、用フートロータ、領域

- 全領域に対する独立した読み/書き保護施錠ビット

- 選択可能なフラッシュプログラム メモリ領域の組み込み高速CRC検査

- データ メモリ

- 1つの直線的なアドレス空間

- CPUからの単一周期アクセス

- SRAM

- EEPROM

- バイトまたはページでのアクセスが可能

- 直接取得/格納に対する任意のメモリ配置割り当て

- I/Oメモリ

- 全ての単位部と周辺機能に対する構成設定と状態のレジスタ

- 全体変数またはフラグ用にビットアクセス可能な16個の汎用I/Oレジスタ

- 外部メモリ支援

- SRAM

- SDRAM

- メモリ割り当て外部ハードウェア

- バス調停

- CPU、DMA制御器、他のバス所有者間の決定論的な優先順処理

- SRAM、EPROM、I/Oメモリ、外部メモリのアクセスに対する独立バス

- CPUとDMA制御器の同時バスアクセス

- 工場書き込みデータ用製品識票列メモリ

- 各マイクロ コートローラに対するID

- 各デバイスに対する通番

- 工場較正された周辺機能用の較正バイト

- 使用者識票列

- 1つのフラッシュ ページ 容量

- ソフトウェアから読み書き可能

- チップ消去後も内容保持

## 7.2. 概要

AVR構造はプログラム メモリとデータ メモリの主な2つのメモリ空間を持ちます。実行可能コードはプログラム用メモリにだけ属し、一方データはプログラム用メモリとデータ用メモリに格納することができます。データ用メモリはSRAMと不揮発性データ記憶用のEEPROMを含みます。全てのメモリ空間は直線状でメモリ バンク切り換えを必要としません。不揮発性メモリ(NVM:Non-Volatile Memory)空間は更なる書き込みと読み書きの操作に対して施錠することができます。これは応用ソフトウェアの無制限なアクセスを防ぎます。

独立したメモリ領域がヒューズバイトを含みます。これらは重要なシステム機能の構成設定に使われ、外部書き込み器によってのみ書くことができます。

利用可能なメモリ容量形態は5頁の「**注文情報**」で示されます。加えて、各デバイスは校正データ、デバイス識別、通番などに関するフラッシュ メモリ識票列を持っています。

# 7.3. フラッシュ プログラム メモリ

AVR XMEGAディー・イスはチップ・上にプログラム記憶用の実装書き換え可能なフラッシュ メモリを含みます。フラッシュ メモリはPDIを通す外部書き込み器またはディー・イスで走行する応用ソフトウェアから読み書きアクセスができます。

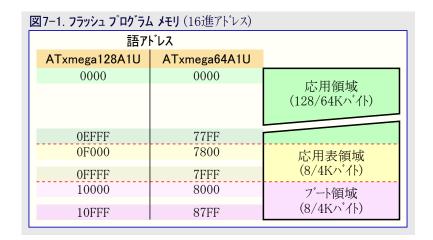

全てのAVR CPU命令は16または32ビット幅、フラッシュの各アドレス位置は16ビットです。フラッシュメモリは応用領域とブート ローダ領域の2つの主な領域で構成されます。各領域の容量は固定ですが、デバイス依存です。これら2つの領域は独立した施錠ビットを持ち、異なる保護段階を持てます。応用ソフトウェアからフラッシュを書くのに使われるSPM(Store Program Memory)命令はブート ローダ領域から実行される時にだけ動作します。

応用領域は独立した施錠設定を持つ応用表領域を含みます。これはプログラム メモリ内の不揮発性データの安全な記憶を許します。 応用表領域とブート領域は一般的な応用ソフトウェアにも使うことができます。

#### 7.3.1. 応用領域 (Application Section)

応用領域は実行可能な応用コートを格納するのに使われるフラッシュの領域です。応用領域に対する保護段階はこの領域用のブート施錠ビット(ブート施錠ビットA)によって選べます。SPM命令は応用領域から実行することができないので、応用領域はどんなブートローダコートも格納できません。

## **7.3.2.** 応用表領域 (Application Table Section)

応用表領域はデータの格納に使えるフラッシュの応用領域の一部です。容量はブートローダ領域と同じです。応用表に対する保護段階はこの領域用のブート施錠ビット(ブート施錠ビット(ブート施錠ビットT)によって選べます。応用領域と応用表領域で異なる保護段階にできることはプログラム メモリの安全なパラメータ記憶を可能にします。この領域がデータ用に使われないなら、ここに応用コートが存在できます。

#### 7.3.3. ブートローダ領域 (Boot Loader Section)

応用領域が応用コート・の格納に使われる一方、SPM命令がこの領域から実行する時にだけプログラミングを始められるので、ブートローダ、ソフトウェアはブートローダ、領域に配置されなければなりません。SPM命令はブートローダ、領域それ自身を含むフラッシュ全体をアクセスできます。フートローダ、領域に対する保護段階はブートローダ、施錠ビット(ブート施錠ビットB)によって選べます。この領域がブートローダ、ソフトウェア用に使われないなら、ここに応用コート・を格納することができます。

# 7.3.4. 製品識票列 (Production Signature Row)

製品識票列は工場書き込みデータ用の独立したメモリ領域です。これは発振器やアナログ部のような機能用の構成データを含みます。いくつかの校正値はリセット中に対応する単位部または周辺機能部へ自動的に格納されます。その他の値はソフトウェアで識票列から取得されて対応する周辺機能レジスタに書かれなければなりません。校正条件の詳細については62頁の「電気的特性」を参照してください。

製品識票列は消去や書き込みができませんが、応用ソフトウェアと外部書き込み器から読むことができます。

| 表7-1. XMEGA A1Uf n イス用f n イスIDn イト |       |       |       |  |  |

|------------------------------------|-------|-------|-------|--|--|

| テンバイス                              | 内容    |       |       |  |  |

| 7717                               | 第1バイト | 第2バイト | 第3バイト |  |  |

| ATxmega64A1U                       | 1E    | 96    | 4E    |  |  |

| ATxmega128A1U                      | 1E    | 97    | 4C    |  |  |

# 7.3.5. 使用者識票列 (User Signature Row)

使用者識票列は応用ソフトウェアと外部の書き込み器から完全にアクセス(読み書き)可能な独立したメモリ領域です。これは1つのフラッシュ へーシ 容量で、校正データ、独自の通番や識別番号、乱数の種(素)などのような静的な使用者パラメータ記憶を予定されています。この領域はフラッシュ メモリを消去するチップ 消去指令によって消去されず、専用の消去指令を必要とします。これは多数回の消去/書き込み操作とチップ 上デバッグ 作業中のパラメータ記憶を保証します。

#### 7.4. ヒュース と施錠(Lock)ビット

ヒュース、は重要なシステム機能を構成設定するのに使われ、外部プログラミンク、インターフェースから書くことができます。応用ソフトウェアはヒュース、を読むことができます。ヒュース、は低電圧検出器(BOD:Brown-out Detector)やウォッチト、ック、のようなリセット元構成設定や、始動構成設定、JTAG許可とJTAG使用者IDに使われます。

施錠ビットは各種フラッシュ領域の保護段階設定に使われます(換言すると、読み(と/または)書きのアクセスが防止されるべき場合に)。施錠ビットは外部書き込み器と応用ソフトュアから書けますが、より厳しい保護へだけです。チップ消去が施錠ビットを消去する唯一の方法です。例えチップ消去中でもフラッシュ内容が保護されることを保証するため、施錠ビットはフラッシュメモリの残りの部分が(完全に)消去された後に消去されます。

非プログラムにされたヒュースと施錠のビットは値1を持ち、一方プログラムにされたヒュースと施錠のビットは値0を持ちます。 ヒュースと施錠ビットの両方はプログラム用フラッシュメモリのように書き換え可能です。

# 7.5. データ メモリ

データメモリはI/Oメモリ、内部SRAM、任意選択のメモリ配置割り当てEEPROMを含みます。データメモリは1つの続いたメモリ領域として構成されます。図7-2をご覧ください。開発を簡単化するため、全てのAVR XMEGAデバイスでI/Oメモリ、EEPROMとSRAMは常に同じ開始アドレスを持ちます。外部メモリ用のアトレス空間は常に内部SRAMの終り(の次)で始まり、アトレス\$FFFFFFで終わります。

|              | アト゛レス        | バイトフ          |  |

|--------------|--------------|---------------|--|

|              | ATxmega64A1U | ATxmega128A1U |  |

| I/Oメモリ       | 0000         | 0000          |  |

| (4/4Kバイト)    | 0FFF         | 0FFF          |  |

| EEPROM       | 1000         | 1000          |  |

| (2/2Kバイト)    | 17FF         | 17FF          |  |

| (予約)         |              |               |  |

| 内部SRAM       | 2000         | 2000          |  |

| (8/4Kバイト)    | 2FFF         | 3FFF          |  |

| 外部メモリ        | 3000         | 4000          |  |

| (0~16Mハイト)   |              |               |  |

| (0 101/1 /// | FFFFFF       | FFFFFF        |  |

#### 7.6. EEPROM

全てのデバイスは不揮発性データ記憶用にEEPROMを持っています。それは独立したデータ空間(既定)でのアドレス指定、または通常のデータ空間にメモリ配置割り当てしてアクセスする、のどちらかにできます。EEPROMはバイトとページの両アクセスを支援します。メモリ配置割り当てEEPROMは高い効率のEEPROM読み込みとEEPROM緩衝部格納を許します。これを行うと、EEPROMは取得と格納の命令を使ってアクセスできます。メモリ配置割り当てEEPROMは常に16進アドレス\$1000で始まります。

#### 7.7. I/Oメモリ

CPUを含む単位部と周辺機能に関する状態と構成設定のレシ、スタはI/Oメモリ位置を通してアドレス指定できます。全てのI/O位置は取得 (LD/LDD/LDS)と格納(ST/STD/STS)命令によってアクセスでき、そしてそれはレシ、スタファイル内の32個のレシ、スタとI/Oメモリ間でデータを転送するのに使われます。IN命令とOUT命令は\$0000~\$003F範囲のI/Oメモリ位置を直接アドレス指定できます。アドレス範囲\$0000~\$001Fでは個別ビットの操作と検査の命令が利用できます。

XMEGA A1Uでの全ての周辺機能と単位部に対するI/Oメモリ アドレスは55頁の「周辺機能単位部アドレス割り当て」で示されます。

#### 7.7.1. 汎用I/Oレジスタ

最下位16個のI/Oメモリ アドレスは汎用I/Oレジスタ用に予約されています。これらのレジスタは、それらがSBI,CBI,SBIS,SBIC命令を使って直接ビット アクセスが可能なため、全体変数とフラグの格納に使うことができます。

# 7.8. 外部メモリ

外部のSRAMやSDRAMとLCD表示器のようなメモリ割り当て周辺装置を支援する外部メモリ用に4つのポートを使うことができます。43頁の「EBI - 外部パスインターフェース」を参照してください。外部メモリアドレス空間は常に内部SRAMの終り(の次)で始まります。

# 7.9. データ メモリとバス調停

データ メモリが4つの独立したメモリの組として構成されるため、異なるバス主権部(CPU、DMA制御器読み、DMA制御器書き、など)が同時に異なるメモリをアクセスし得ます。

# 7.10. メモリ タイミング

I/Oメモリへの読み書きアクセスは1 CPUクロック周期かかります。SRAMへの書き込みは1周期かかり、SRAMからの読み込みは2周期かかります。(DMA)集中読み込みについては新しいデータが毎周期で利用可能です。EEPROMページ設定(書き込み)は1周期かかり、読み込みに対して3周期が必要です。集中読み込みについては新しいデータが毎2周期で利用可能です。外部メモリは複数周期読み込みと書き込みを持ちます。その周期数はメモリ形式と外部バス インターフェースの構成設定に依存します。命令と命令タイミングのより多くの詳細については命令要約を参照してください。

# 7.11. デバイスIDと改訂

各々のデバイスは3バイトのデバイスIDを持ちます。このIDはデバイスの製造業者とデバイス型式を明らかにします。独立した改訂版ID (REVID)レジスタはデバイスの改訂版番号を含みます。

#### 7.12. I/Oメモリ保護

デバイス内のいくつかの機能はいくつかの応用での安全性に大いに関係します。このため、クロック系、事象システム、新波形拡張に関連するI/Oレジスタの施錠が可能です。施錠が許可されている限り、全ての関連I/Oレジスタが施錠され、それらは応用ソフトウェアから書くことができません。それら自身の施錠レジスタは構成設定変更保護機構によって保護されます。

# 7.13. JTAG禁止

応用ソフトウェアからJTAGインターフェースを禁止することができます。これは次のデバイスリセットまたはJTAGが応用ソフトウェアから再び許可されるまで、デバイスへの全ての外部JTAGアクセスを防ぎます。JTAGが禁止されている限り、JTAGで必要とされるI/Oピンとは標準I/Oピンとして使えます。

# 7.14. フラッシュ メモリとEEPROMのペーシ 容量

プログラム用フラッシュ メモリとデータ用EEPROMはヘージで構成されています。ヘージはフラッシュ メモリに対して語アクセス可能で、EEPROMに対してバイトアクセス可能です。

表7-2.はプログラム用フラッシュメモリ構成とプログラム カウンタ(PC)の大きさを示します。フラッシュの消去と書きこみの操作は1~゚ーシ´毎に実行され、一方フラッシュ読み込みは1バイト毎に行われます。フラッシュアクセスに関してはアドレス指定にZポインタ(Zn~0)が使われます。アドレスの上位側(FPAGE)がペーシ`番号を与え、下位側アドレス ビット(FWORD)がページ内の語(位置)を与えます。

| 表7-2. フラッシュ メモリ内のページ数と語数 |         |       |       |       |       |      |     |      |       |

|--------------------------|---------|-------|-------|-------|-------|------|-----|------|-------|

| テ゛ハ゛イス                   | フラッシュ容量 | ページ容量 | FPAGE | FWORD | 応用    | 領域   | ブート | 領域   | PC大きさ |

|                          | (バイト)   | (語)   |       |       | 容量    | ページ数 | 容量  | ページ数 | (ビット) |

| ATxmega64A1U             | 64K+4K  | 128   | Z16~8 | Z7~1  | 64KB  | 256  | 4KB | 16   | 16    |

| ATxmega128A1U            | 128K+8K | 256   | Z17~9 | Z8~1  | 128KB | 256  | 8KB | 16   | 17    |

表7-3.はXMEGA A1Uデバイスに対するEEPROM構成を示します。EEPROMの消去と書きこみの操作は1ページまたは1バイト毎に実行され、一方EEPROM読み込みは1バイト毎に行われます。EEPROMアクセスに関してはアドレス指定にNVMアドレスレジスタ(ADDRn~0)が使われます。アドレスの上位側(E2PAGE)がページ番号を与え、下位側アドレス ビット(E2BYTE)がページ内のバイト(位置)を与えます。

| 表7-3. EEPROM内のページ数とバイト数 |          |       |          |         |      |  |

|-------------------------|----------|-------|----------|---------|------|--|

| テ゛バ゛イス                  | EEPROM容量 | ページ容量 | E2PAGE   | E2BYTE  | ページ数 |  |

|                         | (バイト)    | (バイト) |          |         |      |  |

| ATxmega64A1U            | 2K       | 32    | ADDR10∼5 | ADDR4∼0 | 64   |  |

| ATxmega128A1U           | 2K       | 32    | ADDR10∼5 | ADDR4~0 | 64   |  |

(<mark>訳補</mark>) フラッシュ メモリは応用領域とブート領域が\$000000番地から連続的に配置されています。このため、例えば応用領域が64KBの場合の領域内に於けるZポインタのMSBはZ15ですが、ブート領域分まで含めた全領域に対してはZ16になります。またSPM命令ではフラッシュ メモリをヘ゜ーシ 単位で扱い、ヘ゜ーシ 内は語単位で扱います。このため、ZポインタのLSB(Z0)は常に無視されます。(E)LPM命令はハ・イト単位で扱うのでLSB(Z0)も使われます。表7-2.のFPAGE及びFWORDのZポインタはSPM命令に対するものです。

© 2018 Microchip Technology Inc. 完全データシート DS40002058A - 16頁

# 8. DMAC - 直接メモリ入出力制御器 (Direct Memory Access Controller)

# 8.1. 要点

- 最小CPU介在での高速転送を許容

- データ メモリからデータ メモリへ

- データ メモリから周辺機能へ

- 周辺機能からデータ メモリへ

- 周辺機能から周辺機能へ

- 独立した4つのDMAチャネル

- 転送起動元

- 割り込みへづクタ

- アドレス指示種別

- 設定可能なチャネル優先順

- 単一転送処理で1バイトから16Mバイトまでのデータ

- 複数のアドレス指示種別

- 静止

- 増加

- 減少

- 各終了での転送元と転送先の再設定任意選択

- 集中

- 塊

- 単位処理

- 転送終了での割り込み任意選択

- DMAデータ上のCRCに対するCRC発生器への接続任意選択

# 8.2. 概要

4チャネル直接メモリ入出力(DMA)制御器はメモリと周辺機能間でデータを転送することができ、従ってCPUからそれらの作業の負担を取り除きます。それは最小CPU介在での高いデータ転送速度を許し、CPU時間を自由にします。4つのDMAチャネルは4つまでの独立した平行転送を許します。

DMA制御器はSRAMと周辺機能間、SRAM位置間、周辺機能レシ、スタ間のデータを直接移動することができます。全ての周辺機能へのアクセスとで、DMA制御器は通信単位部との自動的なデータ転送を扱うことができます。DMA制御器はメモリ配置割り当てEEPROMから読むこともできます。

データ転送は1,2,4,8バイトの継続集中で行われます。それらは1バイトから64Kバイトまでの構成設定可能な量の塊転送を構築します。繰り返し計数器は単一転送処理に対して最大16Mバイトまで各塊転送を繰り返すのに使うことができます。転送元と転送先のアドレス指示は静止、増加、減少にすることができます。転送元と/または転送先のアドレスの自動再設定は、各集中転送または塊転送後、転送完了時に行うことができます。応用ソフトウェア、周辺機能と事象がDMA転送を起動することができます。

4つのDMAチャネルは個別の構成設定と制御設定を持ちます。これには転送元、転送先、転送起動元、転送単位処理量を含みます。 それらは個別の割り込み設定を持ちます。割り込み要求は転送単位処理完了時、またはDMA制御器がDMAチャネルで異常を検出した時に生成することができます。

継続的な転送を許すため、1つ目が終了された時に2つ目が転送を引き継ぐ、それとその逆のように2つのチャネルを内部接続することができます。

# 9. 事象システム

## 9.1. 要点

- 周辺機能から周辺機能への直接的な通信と合図のためのシステム

- 周辺機能は周辺機能事象へ直接的に送る、受ける、反応が可能

- CPUとDMAの個別動作

- 100%予測可能な信号タイミング

- 短く保証された応答時間

- CPUとDMAの個別動作

- •8つまでの異なる平行信号経路と構成設定の8つの事象チャネル

- 事象は殆どの周辺機能、クロック系、ソフトウェアによって送出、そして/または使うことが可能

- 以下の付加機能

- 直交復号

- 入出力ピン変化のデジタル濾波

- 活動動作とアイドル動作で作動

# 9.2. 概要

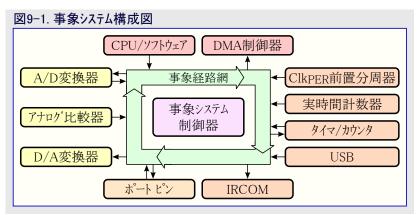

事象システムは周辺機能から周辺機能への直接的な通信と合図のためのシステムです。それは或る周辺機能の変化に別の周辺機能の自動起動活動を許します。これは周辺機能間の短くて予測可能な応答時間のために予測可能な系を提供するように設計されています。それは割り込み、CPU、またはDMA制御器の資源なしで自律の周辺機能制御と相互作用を許し、従って応用コードの複雑さ、大きさ、実行時間を減らすための強力なツールです。それはまた、多数の周辺機能単位部での同期した活動タイシングを許します。

周辺機能の状態変化は事象として参照され、通常、周辺機能に対する割り込み条件に対応します。事象は事象経路網と呼ばれる専用の配線網を用いて他の周辺機能へ直接渡すことができます。周辺機能によって事象がどう配線され、どう使われるかはソフトウェアで構成設定されます。

図9-1.は接続された全ての周辺機能の基本構成図を示します。事象システムはA/D変換器、アナログ比較器、入出力ポートピン、実時間計数器、タイマ/カウンタ、IR通信単位部(IRCOM)、USBインターフェースを共に直接的に接続することができます。これは単位転送処理起動(DMA制御器)に使うこともできます。事象はソフトウェアと周辺機能クロックからも生成することができます。

事象配線網は事象がどう配線され、どう使われるかを制御する、ソフトウェアで構成設定可能な8つの多重器から成ります。これらは事象チャネルと呼ばれ、8つまでの並列事象配線構成設定を許します。最大配線遅れは2周辺機能クロック周期です。事象システムは活動動作とアイト、ル休止動作の両形態で動きます。

# 10. システム クロックとクロック選択

# 10.1. 要点

- 高速な始動時間

- 安全な走行時クロック切り替え

- 内部発振器:

- 32MHz走行時校正付き調整可能な発振器

- 2MHz走行時校正付き発振器

- 32.768kHz校正付き発振器

- 1kHz出力を持つ32kHz超低電力(ULP)発振器

- 外部クロック任意選択

- 0.4~16MHzクリスタル用発振器

- 32.768kHzクリスタル用発振器

- 外部クロック信号

- 20~128MHz出力周波数を持つPLL

- 内部及び外部クロック任意選択と1~31逓倍

- 固定化検出器

- 1~2048分周のクロック前置分周器

- CPUクロック周波数の2倍と4倍で走行する高速周辺機能クロック

- 内部発振器の走行時自動校正

- 任意選択遮蔽不可割り込みを持つ、外部発振器とPLL固定化失敗検出

# 10.2. 概要

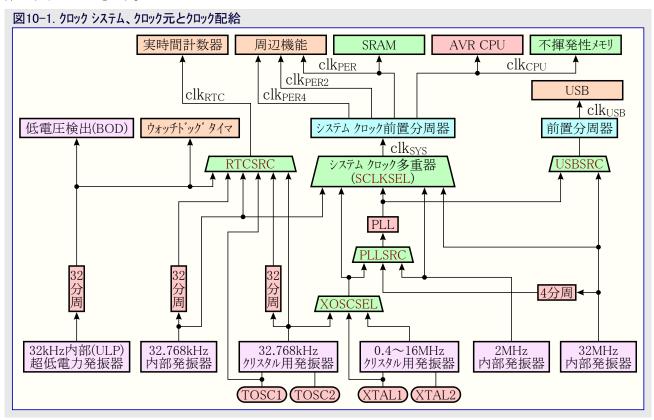

AVR XMEGAデバイスは多数のクロック元を支援する柔軟なクロック システムを持ちます。これは正確な内部発振器と外部のクリスタル発振子と セラミック振動子の支援の両方を結合します。高周波数の位相固定閉路(PLL:Phase Locked Loop)とクロック前置分周器が広い範囲のク ロック周波数生成に使えます。校正機能(DFLL)が利用可能で、電圧と温度に渡る周波数変動を取り去るための内部発振器の走行時自動校正に使えます。クリスタル用発振器停止監視器は外部発振器やPLLが停止した場合に遮蔽不可割り込みの発行と内部発振器の切り替えを許可することができます。

リセット発生時、32kHz超低電力を除く全ての発振器が禁止されます。リセット後、デバイスは常に2MHz内部発振器からの走行で始動します。標準動作の間はシステム クロック元と前置分周器はソフトウェアによって何時でも変更することができます。

図10-1.はXMEGA A1U系デバイスの原則的なクロック システムを表します。クロックの全てが与えられた時間での活動を必要とする訳ではありません。CPUと周辺機能用のクロックは21頁の「電力管理と休止形態動作」で記述されるように、休止形態動作と電力削減レジスタを使って停止することができます。

## 10.3. クロック元

クロック元は2つの主な群、内部発振器と外部クロック元に分けられます。クロック元の殆どはソフトウェアから直接的に許可と禁止ができ、一方その他は周辺機能設定に依存して自動的に許可または禁止されます。リセット後にデバイスは2MHz内部発振器からの走行で始動します。既定での他のクロック元、DFLL、PLLはOFFされます。

内部発振器は動作のためにどんな外部部品も必要としません。内部発振器の特性と精度の詳細についてはデバイスのデータシートを参照してください。

#### 10.3.1. 32kHz超低電力発振器

この発振器は概ね32kHzのクロックを提供します。32kHz超低電力(ULP)内部発振器は非常に低い電力のクロック元で、高い精度用には設計されていません。この発振器は1KHz出力を提供する組み込み前置分周器を使います。この発振器はデバイスのどれかの部分に対してクロック元として使われる時に自動的に許可/禁止が行われます。この発振器は実時間計数器(RTC)に対するクロック元として選ぶことができます。

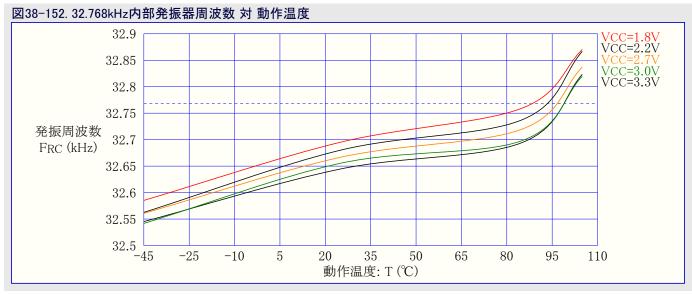

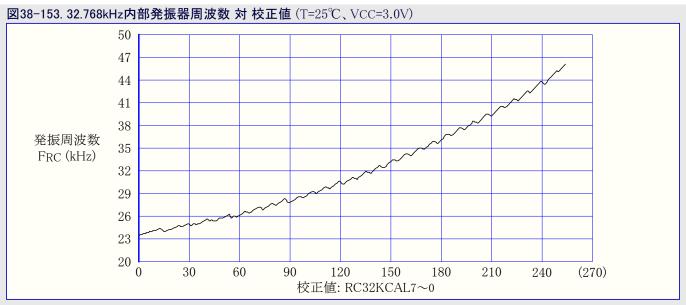

# 10.3.2. 32.768kHz校正付き内部発振器

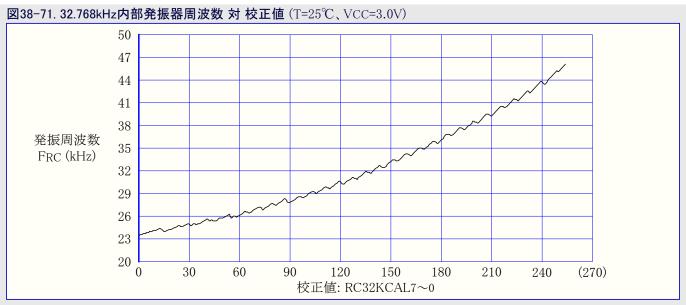

この発振器は概ね32.768kHzのクロックを提供します。これは公称周波数に近い既定周波数を提供するため、製造中に較正されます。32.768kHz発振器校正(RC32KCAL)レジスタは発振器周波数の走行時校正のためにソフトウェアからも書けます。発振器は32.768kHz出力と1.024kHz出力の両方を提供する組み込み前置分周器を使います。この発振器はシステム クロック、RTC、DFLL基準クロックに対するクロック元として使うことができます。

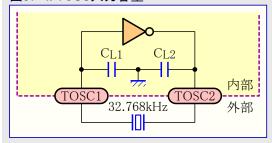

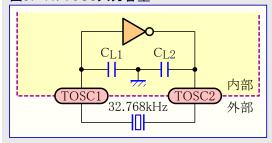

#### 10.3.3. 32.768kHzクリスタル用発振器

32.768kHzクリスタル用発振器はTOSC1とTOSC2のピン間に接続することができ、専用の低周波数発振器入力回路を許します。TOSC2での低減された電圧振れ幅を持つ低電力動作形態が利用可能です。この発振器はシステム クロック、RTC、DFLL基準クロックに対するク ロック元として使うことができます。

#### 10.3.4. 0.4~16MHzクリスタル用発振器

この発振器は0.4~16MHz内全てを含む各周波数範囲に最適化された4つの異なる動作で働けます。

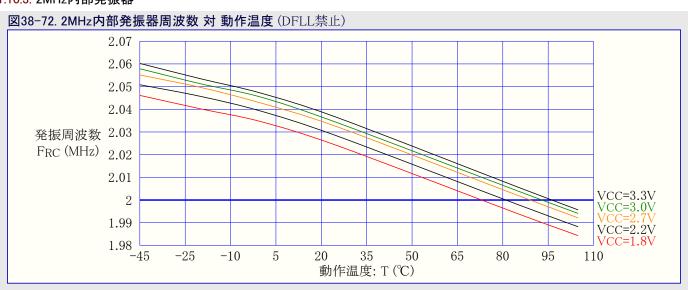

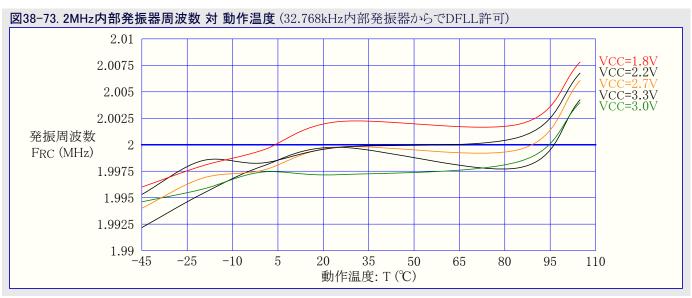

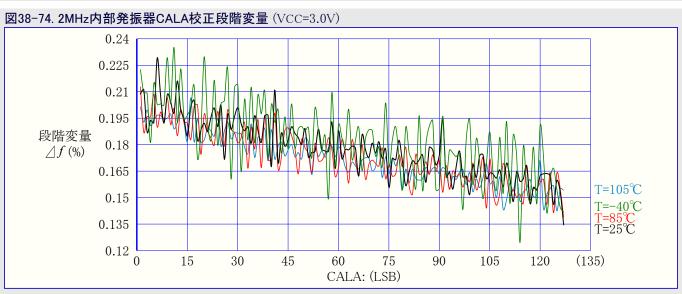

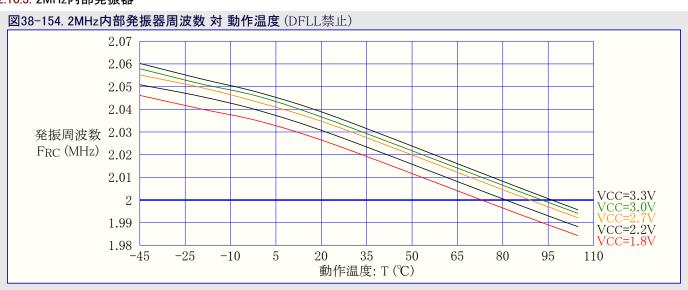

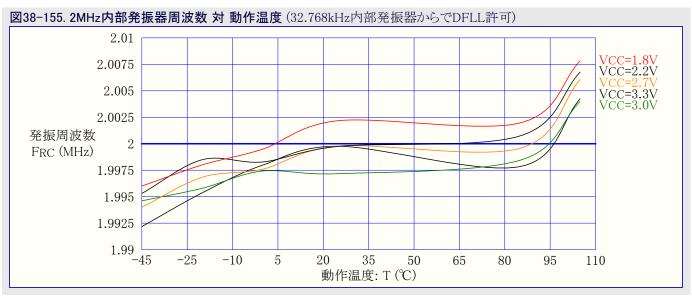

# 10.3.5. 2MHz走行時校正付き内部発振器

2MHz走行時校正付き内部発振器はリセット後の既定システム クロック元です。これは公称周波数に近い既定周波数を提供するため、製造中に校正されます。温度と電圧の変動に対する補償と発振器精度最適化のため、走行時自動校正にデジタル周波数固定化閉路 (DFLL:Digital Frequency Locked Loop)を許可することができます。

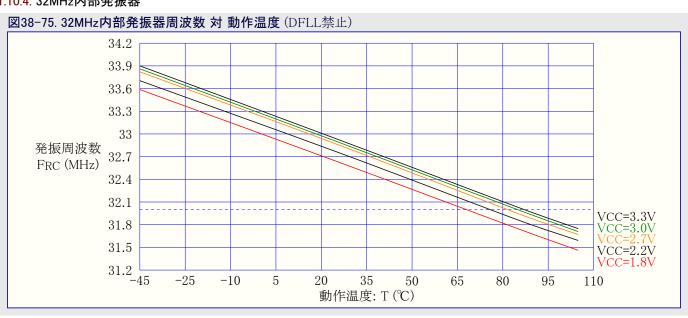

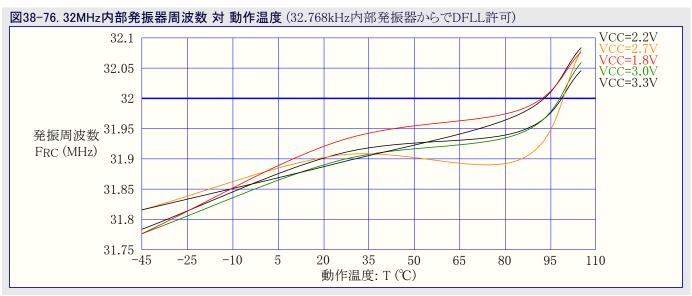

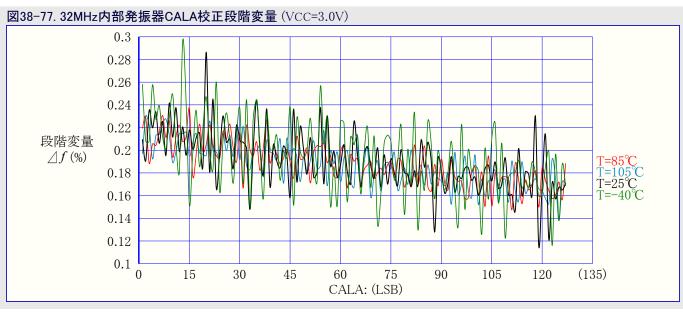

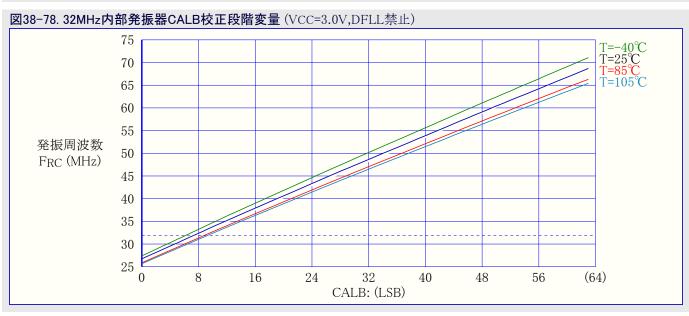

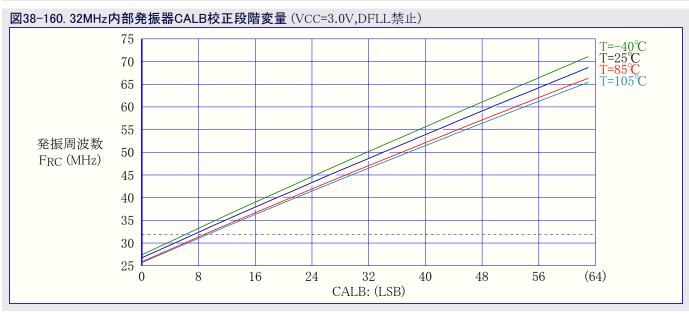

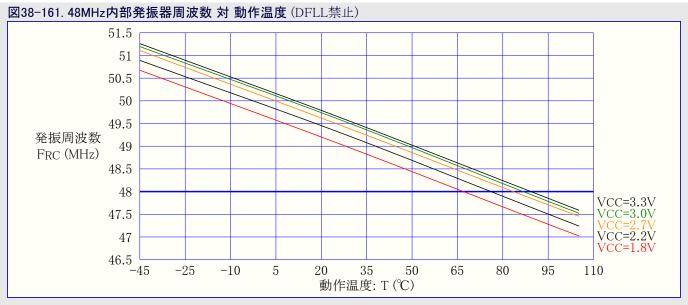

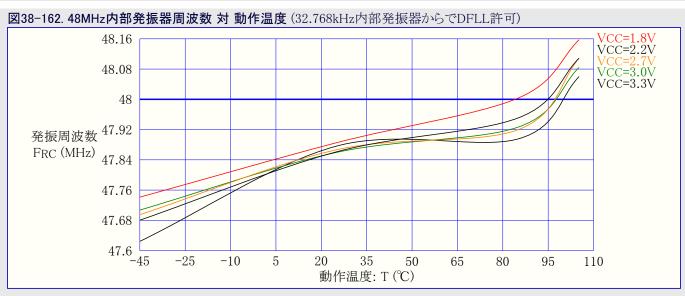

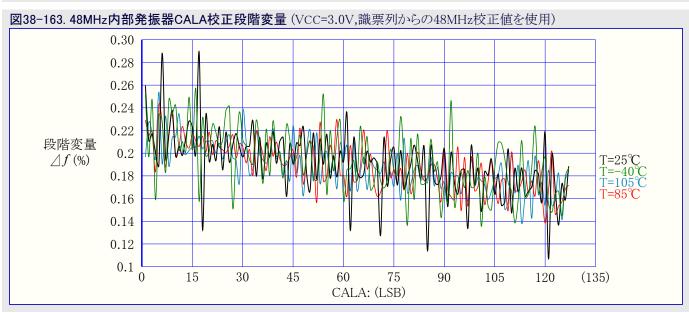

## 10.3.6. 32MHz走行時校正付き内部発振器

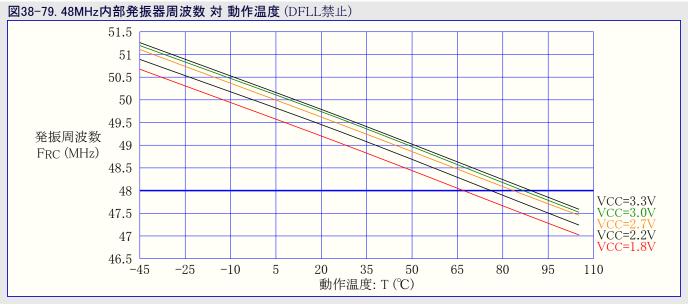

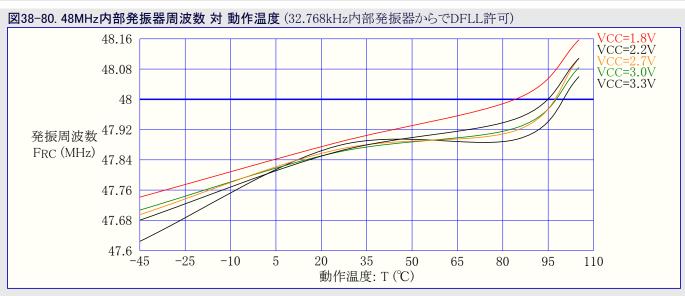

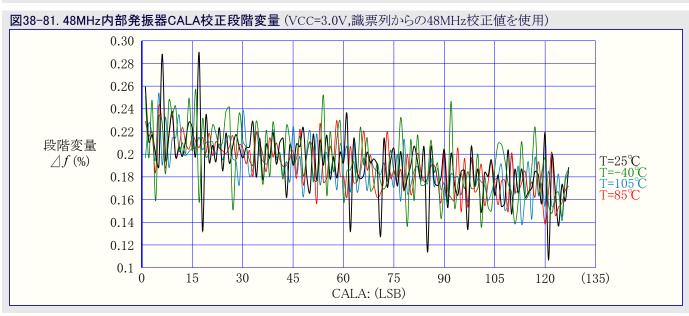

32MHz走行時校正付き内部発振器は高周波数発振器です。これは公称周波数に近い既定周波数を提供するため、製造中に校正されます。発振器精度の最適化のための温度と電圧の変動に対する補償のため、走行時自動校正にDFLLを許可することができます。この発振器は30~55MHz間のどの周波数にも調整、校正することができます。製品識票列は発振器が全速(Full-speed)USBクロック元に使われる時に使用を意図される48MHz校正値を含みます。

#### 10.3.7. 外部クロック入力

XTAL1とXTAL2ピンは水晶クリスタルまたはセラミック振動子のどちらに対しても、外部発振器を駆動するのに使えます。XTAL1は外部クロック信号に対する入力としても使えます。TOSC1とTOSC2ピンは32.768kHzクリスタル用発振器駆動専用です。

## 10.3.8. 1~31の倍率を持つPLL

組み込み位相固定化閉路(PLL)は高周波数システム クロックを生成するのに使うことができます。PLLは使用者選択可能な1~31の倍率を持ちます。前置分周器との組み合わせで、これは全てのクロック元から広範囲の出力周波数を与えます。

# 11. 電力管理と休止形態動作

# 11.1. 要点

- 消費電力と機能を調節するための電力管理

- •5つの休止形態動作種別

- アイドル

- パワータ゛ウン

- ハ°ワーセーブ

- スタンバイ

- 拡張スタンバイ

- 活性とアイト・ルの動作形態でクロックを禁止して未使用周辺機能をOFFにするための電力削減レジスタ

# 11.2. 概要

電力消費を応用の必要条件に仕立てるために様々な休止形態動作とクロック開閉が提供されます。これは節電のための未使用単位部の停止をAVR XMEGAマイクロコントローラに許します。

全ての休止形態が利用可能で、活動動作から移行することができます。活動動作ではCPUが応用コートを実行します。デバイスが休止 形態動作に移行すると、プログラム実行が停止され、再びデバイスを起動するのに割り込みまたはリセットが使われます。応用コートは何 時、どの休止動作形態へ移行するかを決めます。許可された周辺機能からの割り込みと許可された全てのリセット元がマイクロコントローラ を休止から活動動作に回復することができます。

加えて、電力削減レジスタはソフトウェアから個別周辺機能へのクロックを停止する方法を提供します。これが行われると、周辺機能の現在の状態は凍結され、その周辺機能からの電力消費はありません。これは活動動作とアイデル動作での消費電力を減らし、休止形態動作だけよりも遥かに細かく調整された電力管理を可能にします。

# 11.3. 休止形態動作

休止形態動作は節電のためにマイクロコントローラ内の単位部とクロック範囲を停止するのに使われます。XMEGAマイクロコントローラは応用実行中の代表的な機能段に合うように調整された5つの異なる休止形態動作を持ちます。休止形態へ移行するための専用休止命令(SLEEP)が利用できます。休止からデバイスを起動するのに割り込みが使われ、利用可能な割り込み起動元は構成設定された休止形態種別に依存します。許可された割り込みが起こると、デバイスは起動し、SLEEP命令の後の最初の命令から通常のプログラム実行を継続する前に、割り込み処理ルーチンを実行します。起動が起きた時により高い優先権の他の割り込みが保留中の場合、起動割り込みに対する割り込み処理ルーチンが実行される前に、それらの割り込み処理ルーチンがそれらの優先権に従って実行されます。起動後、CPUは実行を開始する前に4クロック周期停止します。

レジスタファイル、SRAM、I/Oレジスタの内容は休止中も維持されます。休止の間にリセットが起きた場合、デバイスはリセットし、リセット ベクタから 始動して実行します。

# 11.3.1. アイドル動作

アイドル動作ではCPUと不揮発性メモリが停止されますが(進行中のどのプログラミングも完了されることに注意)、割り込み制御器、事象システムとDMA制御器を含む全ての周辺機能は動作を維持されます。許可されたどの割り込みもデバイスを起動します。

#### 11.3.2. パワーダウン動作

ハプワーダウン動作では実時間計数器クロック元を含む全てのクロック元が停止されます。これは走行しているクロックを必要としない非同期単位部だけの動作を許します。MCUを起動できる割り込みは2線インターフェースアトレス一致割り込み、非同期ポート割り込み、USB再開割り込みだけです。

## 11.3.3. パワーセーブ動作

パワーセーブ動作は1つの例外(以下)を除いてパワーダウン動作と同じです。実時間計数器が許可されているなら、それは休止中も動作を維持され、デバイスはRTCの上昇溢れまたは比較一致の割り込みのどちらからでも起動することできます。

# 11.3.4. スタンバイ動作

スタンハーイ動作は許可されているシステム クロック元が動作を維持され、一方CPU、周辺機能、RTCのクロックが停止される例外を除いてハータータウン動作と同じです。これは起動時間を減らします。

# 11.3.5. 拡張スタンバイ動作

拡張スタンハーイ動作は許可されているシステムクロック元が動作を維持され、一方CPUと周辺機能のクロックが停止される例外を除いてパーヤーブ動作と同じです。これは起動時間を減らします。

# 12. システム制御とリセット

# 12.1. 要点

- リセット元が活性になる時にマイクロ コントローラをリセットして初期状態に設定

- 各種状況を網羅する多数のリセット元

- 電源ONリセット

- 外部リセット

- ウォッチト、ック、リセット

- 低電圧(Brown-out)リセット

- PDIリセット

- ソフトウェア リセット

- 非同期動作

- リセットにデバイス内のシステム クロックの走行が全く不要

- 応用コート、からリセット元を読み取るためのリセット状態レシ、スタ

# 12.2. 概要

リセット システムはマイクロ コントローラ リセットを発行してデバイスをその初期状態に設定します。これはマイクロ コントローラがそれの電源定格以下で動作するような時に動作が開始または継続しない状況のためです。リセット元が活性(有効)になった場合、デバイスは全てのリセット元がそれらのリセットを開放するまでリセットに移行して保持されます。I/Oピンは直ちにHi-Zにされます。プログラム カウンタはリセット ベクタ位置に設定され、全てのI/Oレジスタがそれらの初期値に設定されます。SRAM内容は保持されます。けれども、リセット発生時にデバイスがSRAMをアクセスする場合、アクセスされた位置の内容を保証することはできません。

リセットが全てのリセット元から開放された後、デバイスがリセット ベクタ アドレスから走行を始める前に、既定発振器が始動され、そして校正されます。 既定により、これは最低プログラム アドレス(0)ですが、リセット ベクタをブート領域の最低アドレスへ移動することが可能です。

リセット機能は非同期で、故にデバイスをリセットするのにシステム クロックの走行が全く必要とされません。ソフトウェア リセット機能は使用者ソフトウェアからの制御されたシステム リセットの発行を可能にします。

リセット状態(STATUS)レシ、スタは各リセット元に対する個別の状態フラク、を持ちます。これは電源ONリセットで解除(0)され、最後の電源ONからどのリセット元がリセットを発行したかを示します。

# 12.3. リセットの流れ

何れかのリセット元からのリセット要求は直ちにデバイスをリセットし、その要求が活性(有効)である限り、リセットを維持します。全てのリセット要求が開放されると、再びデバイスが走行を始める前にデバイスは3つの段階を通って行きます。

- ・ リセット 計数器遅延

- 発振器始動

- 発振器校正

この処理中に別のリセット要求が起きると、リセットの流れは最初から始まります。

# 12.4. リセット元

#### 12.4.1. 電源ONリセット

電源ONJセット(POR)はチップ上の検出回路によって生成されます。PORはVCCが上昇してPOR閾値電圧(VPOT)に達した時に活性にされ、リセット手順を開始します。

PORはVCCが下降してVPOT基準以下に落ちた時にデバイスの電力を正しく落とすのにも活性にされます。

VPOT基準はVCC上昇の方がVCC下降よりも高くなります。

## 12.4.2. 低電圧検出(Brown-Out)リセット

チップとの低電圧検出(BOD)回路はBODLEVELヒュースによって選ばれる設定可能な基準の固定値と比較することにより、動作中の VCC水準を監視します。禁止されると、BODはチップ消去中とPDIが許可されている時に最低基準を強制されます。

#### 12.4.3. 外部リセット

外部リセット回路は外部RESETピンに接続されています。RESETピンが最小パルス時間textより長くRESETピン閾値電圧VRST未満に駆動された時に外部リセットが起動されます。リセットはピンがLowに保たれる限り保持されます。リセット ピンは内部プルアップ。抵抗を内包します。

#### 12.4.4. ウォッチト・ック・リセット

ウォッチト・ック・タイマ(WDT)は正しいプログラム動作を監視するためのシステム機能です。WDTが設定された時間経過周期内にソフトウェアからリセットされない場合、ウォッチト・ック・リセットが起されます。ウォッチト・ック・リセットは2MHz内部発振器で1~2クロック周期の間、活性(有効)です。より多くの詳細については24頁の「WDT - ウォッチト・ック・タイマ」をご覧ください。

## 12.4.5. ソフトウェア リセット

ソフトウェア リセットはリセット制御(CTRL)レシ、スタのソフトウェア リセット(SWRST)ビットへの書き込みによってソフトウェアからシステム リセットを発行することを可能にします。 リセットはそのビット書き込み後、2 CPUクロック周期内で発行されます。 ソフトウェア リセットが要求される時からそれが発行されるまではどの命令も実行できません。

# 12.4.6. プログラミングとデブッグ用インターフェース リセット

プログラミングとデバッグ用インターフェースリセットは外部のプログラミングとデバッグの間中のデバイスリセットに使われる独立したリセット元を含みます。このリセット元はデバッガと書き込み器からだけアクセス可能です。

# 13. WDT - ウォッチト ック タイマ

## 13.1. 要点

- 計時経過時間前に計時器がリセットされない場合にデバイス リセットを発行

- 専用発振器からの非同期動作

- 32kHz超低電力発振器の1kHz出力

- 8msから8sまで11種の選択可能な時間経過周期

- 2つの動作種別

- 標準動作

- 窓動作

- 望まれない変更を防ぐための構成設定施錠

# 13.2. 概要

ウォッチト、ック、タイマ(WDT)は正しいプログラム動作を監視するシステム機能です。暴走や停滞コート、のような異常状況からの回復を可能にします。WDTはタイマで、予め定義された時間経過周期に構成設定され、許可された時に定常的に走行します。WDTが時間経過周期内にリセットされない場合、WDTはマイクロコントローラリセットを発行します。WDTは応用コート、からのWDR(Watchdog Timer Reset)命令を実行することによってリセットされます。

窓動作はWDTがリセットされなければならない総時間経過期間内の時間幅または窓の定義を可能にします。WDTが速すぎまたは遅すぎでこの窓の外側でリセットされると、システム リセットが発行されます。標準動作に比べ、これはコート、異常が一定のWDR実行を引き起こす状況を捕らえることもできます。

許可されていれば、WDTは活動動作と全ての電力(休止形態)動作で作動します。これは非同期で、CPUと無関係なクロック元で動作し、例え主クロックが停止したとしても、システム リセットを発行するための動作を継続します。

構成設定変更保護機構はWDT設定が事故によって変更され得ないことを保証します。安全性を増すため、WDT設定を固定化するためのヒュースも利用可能です。

# 14. 割り込みと設定可能な多段割り込み制御器

# 14.1. 要点

- 短くて予想可能な割り込み応答時間

- 各割り込みに対して独立した構成設定と独立した割り込みへうタ

- 設定可能な多段割り込み制御器

- 段位と割り込みへ、クタアト・レスに従った割り込み優先順化

- 全ての割り込みに対して選択可能な3つの割り込み段位:下位、中位、上位

- 低位割り込み内での選択可能なラウント、ロビン優先権の仕組み

- 重大な機能用の遮蔽不可割り込み

- 応用領域またはブートローダ領域に任意選択で配置される割り込みへりタ

# 14.2. 概要

割り込みは周辺機能の状態変化を合図し、これはプログラム実行の切り換えに使えます。周辺機能は1つ以上の割り込みを持つことができ、その全てが個別に許可され、構成設定されます。割り込みが構成設定されて許可される時に割り込み条件が存在すると、割り込み要求を生成します。設定可能な多段割り込み制御器(PMIC)は割り込み要求の処理と優先順化を制御します。割り込み要求がPMICによって応答されると、プログラム カウンタが割り込みへ、クタを指示するように設定され、割り込み処理ルーチンを実行できます。

全ての周辺機能はそれらの割り込みに対して、低、中、高の3つの異なる優先レベルを選べます。割り込みはそれらの段位とそれらのベクタアドレスに従って優先順化されます。中位割り込みは低位割り込み処理に割り込みます。高位割り込みは中位と低位の両方の割り込み処理に割り込みます。各レベル内では割り込み優先権が割り込みベクタアドレスから決められ、それは最下位割り込みベクタアドレスが最高割り込み優先権を持ちます。全ての割り込みが或る一定時間内に処理されるのを保証するために、低位割り込みは任意選択のラウンドロビン計画機構を持ちます。

遮蔽不可割り込み(NMI)も支援され、システムの重大な機能に使うことができます。

# 14.3. 割り込みべりタ

割り込みへ、クタは周辺機能の基準割り込みアト・レスと各周辺機能内の特定割り込みに対する変位アト・レスの合計です。AVR XMEGA A1 Uデバイスに関する基準アト・レスは表14-1.で示されます。周辺機能で利用可能な各割り込みに対する変位アト・レスはXMEGA AU手引書内で各周辺機能に対して記述されます。割り込みを1つだけ持つ周辺機能または単位部については表14-1.で割り込みへ、クタが示されます。プログラムアト・レスは語アト・レスです。

| 表14-1    | リセットと割り辺  | しみのべりな            |

|----------|-----------|-------------------|

| 1X IT I. | ノじノーにロリンと | <u>^</u> ひかひかヽ カか |

| プ <sup>ロ</sup> ク・ラム アト・レス<br>(基準アト・レス) | 供給元              | 割り込み内容                          |

|----------------------------------------|------------------|---------------------------------|

| \$000000                               | RESET            |                                 |

| \$000002                               | OSCF_INT_vect    | クリスタル用発振器停止割り込みベクタ (NMI)        |

| \$000004                               | PORTC_INT_base   | ポートC割り込み基準                      |

| \$000008                               | PORTR_INT_base   | ポートR割り込み基準                      |

| \$00000C                               | DMA_INT_base     | DMA制御器割り込み基準                    |

| \$000014                               | RTC_INT_base     | 実時間計数器割り込み基準                    |

| \$000018                               | TWIC_INT_base    | ポートC上の2線インターフェース割り込み基準          |

| \$00001C                               | TCC0_INT_base    | ポートC上のタイマ/カウンタ0割り込み基準           |

| \$000028                               | TCC1_INT_base    | ポートC上のタイマ/カウンタ1割り込み基準           |

| \$000030                               | SPIC_INT_vect    | ポートC上の直列周辺インターフェース(SPI)割り込みベクタ  |

| \$000032                               | USARTC0_INT_base | ポートC上のUSART0割り込み基準              |

| \$000038                               | USARTC1_INT_base | ポートC上のUSART1割り込み基準              |

| \$00003E                               | AES_INT_vect     | AES割り込みベクタ                      |

| \$000040                               | NVM_INT_base     | 不揮発性メモリ割り込み基準                   |

| \$000044                               | PORTB_INT_base   | ポートB割り込み基準                      |

| \$000048                               | ACB_INT_base     | ポートB上のアナログ比較器割り込み基準             |

| \$00004E                               | ADCB_INT_base    | ポートB上のA/D変換器割り込み基準              |

| \$000056                               | PORTE_INT_base   | ポートE割り込み基準                      |

| \$00005A                               | TWIE_INT_base    | ポートE上の2線インターフェース割り込み基準          |

| \$00005E                               | TCE0_INT_base    | ポートE上のタイマ/カウンタ0割り込み基準           |

| \$00006A                               | TCE1_INT_base    | ポートE上のタイマ/カウンタ1割り込み基準           |

| \$000072                               | SPIE_INT_vect    | ポートE上の直列周辺インターフェース(SPI)割り込みへ、クタ |

| \$000074                               | USARTE0_INT_base | ポートE上のUSARTO割り込み基準              |

| \$00007A                               | USARTE1_INT_base | ポートE上のUSART1割り込み基準              |

| \$000080                               | PORTD_INT_base   | ポートD割り込み基準                      |

| \$000084                               | PORTA_INT_base   | ポートA割り込み基準                      |

| \$000088                               | ACA_INT_base     | ポートA上のアナログ比較器割り込み基準             |

| \$00008E                               | ADCA_INT_base    | ポートA上のA/D変換器割り込み基準              |

| \$000096                               | TWID_INT_base    | ポートD上の2線インターフェース割り込み基準          |

| \$00009A                               | TCD0_INT_base    | ポートD上のタイマ/カウンタ0割り込み基準           |

| \$0000A6                               | TCD1_INT_base    | ポートD上のタイマ/カウンタ1割り込み基準           |

| \$0000AE                               | SPID_INT_vect    | ポートD上の直列周辺インターフェース(SPI)割り込みへ、クタ |

| \$0000B0                               | USARTD0_INT_base | ポートD上のUSARTO割り込み基準              |

| \$0000B6                               | USARTD1_INT_base | ポートD上のUSART1割り込み基準              |

| \$0000BC                               | PORTQ_INT_base   | ポートQ割り込み基準                      |

| \$0000C0                               | PORTH_INT_base   | ポートH割り込み基準                      |

| \$0000C4                               | PORTJ_INT_base   | ポート「割り込み基準                      |

| \$0000C1                               | PORTK_INT_base   | ポートK割り込み基準                      |

| \$0000D0                               | PORTF_INT_base   | ポートF割り込み基準                      |

| \$0000D0                               | TWIF_INT_base    | ポートF上の2線インターフェース割り込み基準          |

| \$0000D4<br>\$0000D8                   | TCF0_INT_base    | ポートF上のタイマ/カウンタ0割り込み基準           |

| \$0000E4                               | TCF1_INT_base    | ポートF上のタイマ/カウンタ1割り込み基準           |

| \$0000EC                               | SPIF_INT_vect    | ポートF上の直列周辺インターフェース(SPI)割り込みへ、クタ |

| \$0000EE                               | USARTF0_INT_base | ポートF上のUSARTO割り込み基準              |

| \$0000EL                               | USARTF1_INT_base | ポートF上のUSART1割り込み基準              |

| \$0000F4                               | USB_INT_base     | ポートD上のUSB割り込み基準                 |

# 15. 入出力ポート

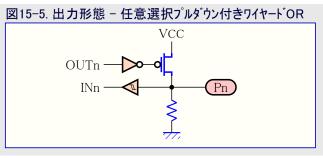

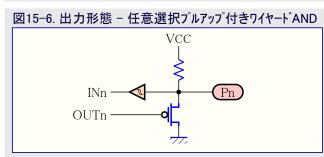

# 15.1. 要点

- 個別構成設定を持つ78本の汎用入出力ピン

- 構成設定可能な駆動部と引き込み設定を持つ出力駆動部

- コンプリメンタリ

- ワイヤードAND

- ワイヤート OR

- ●バス保持

- 反転入出力

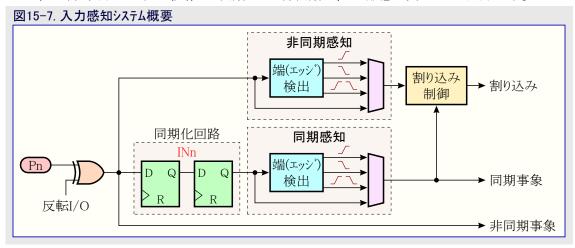

- 割り込みと事象を持つ同期と/または非同期の感知付き入力

- 両端感知

- 上昇端感知

- 下降端感知

- Lowレヘール感知

- 入力とワイヤート˙OR/AND構成設定での任意選択のプルアップとプルダウンの抵抗

- 任意選択のスリューレート制御

- 全休止形態からデバイスを起動できる非同期ピン変化感知

- 入出力ポート毎でピン遮蔽を持つ2つのポート割り込み

- ホートピンへの効率的で安全なアクセス

- 専用の切り換え、解除(0)、設定(1)用レシブスタ通すハードウェア読み−変更−書き

- 単一操作で複数ピンの構成設定

- ビット アクセス可能なI/Oメモリ空間へポート レジスタの割り当て

- ポート ピンでの周辺機能クロック出力

- ・ポートピンでの実時間計数器クロック出力

- 事象チャネルがポート ピンで出力可能

- デジタル周辺機能ピンの再割り当て

- 選択可能なUSART、SPI、タイマ/カウンタの入出力ピン位置

# 15.2. 概要

1つのポートはピン0~7で最大8つのポートピンから成ります。各ポートピンは構成設定可能な駆動部と引き込み設定を持つ入力または出力として構成設定することができます。それらは選択可能なピン変化条件用の割り込みと事象を持つ同期と非同期の入力感知も実装します。非同期ピン変化感知はクロックが全く動かない形態を含む全ての休止形態からピン変化がデバイスを起こせることを意味します。

全ての機能はピン毎に個別で構成設定可能ですが、単一操作で多数のピンを構成設定することができます。ピンは駆動値と/または引き込み抵抗の構成設定の安全で正しい変更のためのハードウェア読みー変更-書き(RMW)機能を持ちます。1つのポート ピンの方向は他のどのピンの方向をも予期せず変更することなく変えることができます。

ポート ピン構成設定は他のデバイス機能の入出力選択も制御します。それはポート ピンへの周辺機能クロックと実時間クロックの両出力を持つことが可能で、それは外部使用に利用可能です。同じことが外部機能の同期と制御に使える、事象システムからの事象に適用されます。応用の必要性に対するピン配置の最適化のため、USART、SPI、タイマ/カウンタのような他のデジタル周辺機能は選択可能なピン位置に再割り当てすることができます。

ポートの表記は、PORTA、PORTB、PORTC、PORTD、PORTE、PORTF、PORTH、PORTJ、PORTK、PORTQ、PORTRです。

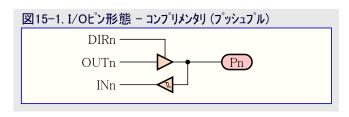

#### 15.3. 出力駆動部

全てのポート ピン(Pn)は設定可能な出力構成設定を持ちます。電磁放射を減らすため、ポート ピンは構成設定可能なスリューレート制限も持ちます。

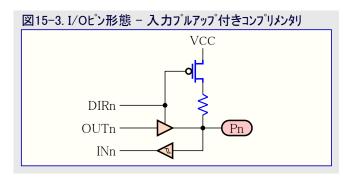

#### 15.3.1. コンプリメンタリ (プッシュプル)

# 15.3.2. プ<sup>°</sup>ルダ<sup>°</sup>ウン

# 図15-2. I/Oピン形態 - 入力プルダウン付きコンプリメンタリ DIRn OUTn INn

# 15.3.3. フ<sup>°</sup>ルアッフ<sup>°</sup>

# 15.3.4. バス保持

ハス保持の弱い出力は最後の出力値と同じ論理値を生成します。最後の値が1だったならプルアップとして、最後の値が0だったなら、プルダウンとして働きます。

# 図15-4. I/Oピン形態 - バス保持付きコンプリメンタリ DIRn OUTn INn

# 15.3.5. その他

# 15.4. 入力感知

入力感知はポートに対して許可されたクロックに依存して同期または非同期で、この形態は図15-7.で示されます。

ピンが反転I/Oで構成設定されると、ピン値は入力感知前に反転されます。

# 15.5. 交換ポート機能

殆どのポート ピンは汎用I/Oピンであることに加えて交換ピン機能を持ちます。機能交換が許可されると、それは通常ポート ピン機能またはピン値を無効にするかもしれません。これは他の周辺機能で必要とするピンが許可または使用ピンに構成設定される時に起きます。周辺機能がどう無効にして、ピンをどう使うかはその周辺機能に関する章で記述されます。50頁の「ピン配置とピン機能」は周辺機能でどの単位部がピンでの交換機能を許可するのかと、どの交換機能がピンで利用可能かを示します。

# 16. TC0/1 - 16ビットタイマ/カウンタ0型と1型

# 16.1. 要点

- 8つの16ビットタイマ/カウンタ

- 4つの0型タイマ/カウンタ

- 4つの1型タイマ/カウンタ

- 各0型タイマ/カウンタから2つの8ビットタイマ/カウンタを許す分割動作形態

- 2つのタイマ/カウンタの縦列接続によって支援される32ビットタイマ/カウンタ

- 4つまでの組み合わせた比較と捕獲(CC)チャネル

- 0型のタイマ/カウンタに対して4つのCCチャネル

- 1型のタイマ/カウンタに対して2つのCCチャネル

- 2重緩衝されたタイマ定期間設定

- 2重緩衝された比較と捕獲のチャネル

- 波形生成:

- 周波数生成

- 単一傾斜パルス幅変調

- 2傾斜パルス幅変調

- 捕獲:

- 雑音消去付き捕獲入力

- 周波数捕獲

- パルス幅捕獲

- 32ビット捕獲入力

- タイマ経過溢れとタイマ異常の割り込み/事象

- CCチャネル当たり1つの比較一致または捕獲の割り込み/事象

- 事象システムと共に以下が使用可能:

- 直交復号

- 計数と方向の制御

- 捕獲

- DMAと共にDMA転送単位処理起動に使用可能

- Hi-Res 高分解能拡張

- 周波数と波形の分解能を2ビット(×4)または3ビット(×8)増加

- AWeX 新波形拡張

- 設定可能な沈黙時間挿入(DTI)を持つLow側とHigh側の出力

- 外部駆動部の安全な禁止のための事象制御された障害保護

# 16.2. 概要

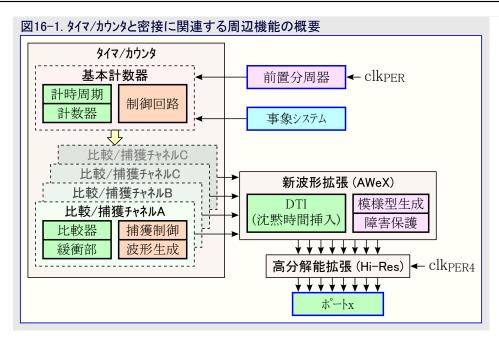

AVR XMEGA A1Uデバイスは8つの柔軟な16ビット タイマ/カウンタ(TC)の組を持ちます。それらの能力には正確なプログラム実行タイミング、周波数と波形の生成、事象管理、デジタル信号の時間と周波数の測定付きの捕獲入力を含みます。2つのタイマ/カウンタは任意選択の32ビット捕獲を持つ32ビット タイマ/カウンタを作成するために縦列接続することができます。

タイマ/カウンタは基本計数器と比較または捕獲(CC)チャネルの組から成ります。基本計数器はクロック周期または事象を計数するのに使えます。これは方向制御とタイミングに使うことができる定期設定を持ちます。CCチャネルは基本計数器と共に、比較一致制御、周波数生成、パプルス幅波形変調は勿論、様々な入力捕獲動作を行うのにも使うことができます。タイマ/カウンタは比較または捕獲のどちらの機能にも構成設定できますが、同時に両方を実行することはできません。

タイマ/カウンタは任意選択の前置分周付きの周辺機能クロックまたは事象システムからクロック駆動と計時を行うことができます。 事象システムは 方向制御と捕獲起動、または動作の同期にも使うことができます。

タイマ/カウンタの0型と1型間には2つの違いがあります。タイマ/カウンタ0は4つのCCチャネルを持ち、タイマ/カウンタ1は2つのCCチャネルを持ちます。CCチャネルCとCCチャネルDに関連する全ての情報はタイマ/カウンタ0に対してだけ有効です。タイマ/カウンタ0だけが各々4つの比較チャネルを持つ2つ8ビット タイマ/カウンタに分割する分割動作機能を持ちます。

いくつかのタイマ/カウンタはもっと特殊化された波形と周波数の生成を許すための拡張を持ちます。新波形拡張(AWeX)は電動機制御や他の電力制御応用を意図されています。それは沈黙時間挿入付きのLow側とHigh側の出力は勿論、禁止用の障害保護や外部駆動部切断も許します。ポート ピンの向こう側への同期したビット様式を生成することもできます。

新波形拡張はタイマ/カウンタに対して追加のもっと進化した機能の提供を許します。これはタイマ/カウンタ0でだけ利用可能です。より多くの詳細については33頁の「AWeX - 新波形拡張」をご覧ください。

高分解能(Hi-Res)拡張は周辺機能クロックよりも最大4倍速く走行する内部クロック元を使うことによって、波形出力分解能を4または8倍に増すのに使うことができます。より多くの詳細については34頁の「Hi-Res - 高分解能拡張」をご覧ください。

ポートC、ポートD、ポートE、ポートFは各々、1つのタイマ/カウンタ0と1つのタイマ/カウンタ1を持ちます。これらの表記は各々、TCC0(タイマ/カウンタC0)、TCC1、TCD0、TCD1、TCE0、TCE1、TCF0、TCF1です。

# 17. TC2 - タイマ/カウンタ2型

## 17.1. 要点

- 8つの8ビットタイマ/カウンタ

- 4つの下位バイト タイマ/カウンタ

- 4つの上位バイト タイマ/カウンタ

- 各タイマ/カウンタ2で最大8つの比較チャネル

- 下位バイトタイマ/カウンタ用の4つの比較チャネル

- 上位バイトタイマ/カウンタ用の4つの比較チャネル

- 波形生成

- 単一傾斜パルス幅変調

- 計時器漏れ(アンダーフロー)割り込み/事象

- 下位バイト タイマ/カウンタ用の比較チャネル当たり1つの比較一致割り込み/事象

- 計数制御に対して事象システムとで使用可

- DMA転送単位処理起動に使用可

# 17.2. 概要

3つのタイマ/カウンタ2があります。これらはタイマ/カウンタ0が分割動作に設定される時に実現されます。これは各々4つの比較チャネルを持つ2つの8ビット タイマ/カウンタのシステムです。これは個別に制御されるデューティサイクルを持つ8つの構成設定可能なパルス幅変調(PWM:Pulse Width Modulation)を与え、多くのPWMチャネルが必要な応用に意図されています。

2つの8ビット タイマ/カウンタはこのシステムに於いて各々、下位バイトタイマ/カウンタと上位バイトタイマ/カウンタとして参照されます。それらの違いは下位バイト タイマ/カウンタだけが比較一致割り込み、事象、DMA起動を生成するのに使えることです。2つの8ビット タイマ/カウンタは共用されるクロック元と、独立した定期と比較の設定を持ちます。それらは任意選択の前置分周を周辺機能クロックから、または事象システムからクロック駆動と計時をすることができます。計数器は常に下降計数です。

ポートC、ポートD、ポートE、ポートFは各々1つのタイマ/カウンタ2を持ちます。

これらの表記は各々、TCC2(タイマ/カウンタC2)、TCD2、TCE2、TCF2です。

# 18. AWeX - 新波形生成拡張

# 18.1. 要点

- 各比較チャネルからの補完出力を持つ波形出力

- 4つの沈黙時間挿入(DTI)部

- 8ビット分解能

- 独立したHigh側とLow側の沈黙時間設定

- 2重緩衝された沈黙時間

- 任意選択の沈黙時間中の停止計時器

- ポート ピンに渡って同期したビット様式を生成する模様型生成部

- 2重緩衝された模様型生成

- 任意選択のポート ピンに渡る1つの比較チャネル出力の分配

- 瞬時と予め予測可能な障害起動に対する事象制御された障害保護

#### 18.2. 概要

新波形拡張(AWeX)は波形生成(WG)動作でのタイマ/カウンタに追加の機能を提供します。これは主として各種形式の電動機や他の電力制御応用での使用が意図されています。これは外部駆動部の禁止と停止に対して沈黙時間挿入と障害保護を持つLow側とHigh側の出力を許します。ポート ピンに渡る同期されたビット模様を生成することもできます。

タイマ/カウンタのからの波形生成器出力の各々は何れかのAWeX機能が許可される時に出力の補完対に分けられます。これらの出力対はLow側(LS)とHigh側(HS)切り換え間の沈黙時間挿入を持つ、WG出力の非反転LSと反転HSを生成する沈黙時間挿入(DTI)部を通って行きます。DTI出力はポート無効化設定に従って標準ポート値を無効にします。

模様型生成部はそれが接続されたポートで同期したビット模様の生成に使うことができます。加えて、比較チャネルAからのWG出力は全てのポート ピンを無効にして、(そこへ)配給することができます。模様型生成器部が許可されている時はDTI部が迂回されます。

障害保護部は事象システムに接続され、AWeX出力を禁止する障害条件を起動するのをどの事象でも可能にします。事象システムは予測可能で即時の障害反応を保証し、障害起動の選択に於ける素晴らしい柔軟性を与えます。

AWeXはTCC0とTCE0に対して利用可能です。これの表記はAWEXCとAWEXEです。

# 19. Hi-Res - 高分解能拡張

# 19.1. 要点

- 波形生成器分解能を最大8倍(3ビット)増加

- 周波数、単一傾斜PWM、2傾斜PWMの生成を支援

- これが同じタイマ/カウンタに使われる時にAWeXを支援

# 19.2. 概要

高分解能(Hi-Res)拡張はタイマ/カウンタからの波形生成出力の分解能を4または8倍に増やすのに使うことができます。これはタイマ/カウンタに対して周波数、単一傾斜PWM、2傾斜PWMの生成を行うのに使うことができます。これが同じタイマ/カウンタに使われる場合、AWeXと共に使うこともできます。

Hi-Res拡張は4倍周辺機能クロック(clkper4)を使います。システム クロック前置分周器はHi-Res拡張が許可される時に4倍周辺機能クロックがCPUと周辺機能のクロック周波数よりも4倍高くなるように構成設定されなければなりません。

ポートC、ポートD、ポートE、ポートFの各タイマ/カウンタ対に対して各々が許可することができる4つのHi-Res拡張があります。これらの周辺機能の表記は各々、HIRESC、HIRESD、HIRESE、HIRESFです。

# 20. RTC - 16ビット実時間計数器

# 20.1. 要点

- 16ビット分解能

- 選択可能なクロック元

- 32.768kHz外部クリスタル

- 外部クロック信号

- 32.768kHz内部発振器

- 32kHz内部ULP発振器

- 設定可能な前置分周器

- 1つの比較レシブスタ

- 1つの定期レジスタ

- 定期上昇溢れでの計数器解除

- 任意選択の上昇溢れと比較一致での割り込み/事象

#### 20.2. 概要

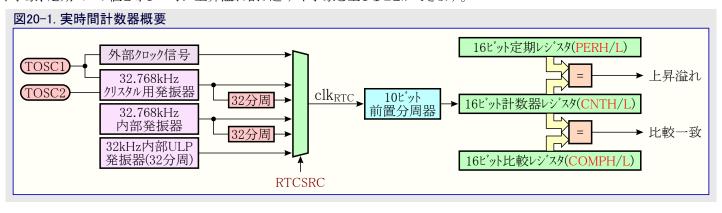

16ビット実時間計数器(RTC)は時間の経緯を保つために、低電力休止形態を含み、代表的に継続して走行する計数器です。これは規則的な間隔で休止形態からデバイスを起こしたり、デバイスに割り込むことができます。

基準クロックは代表的に32.768kHzの高精度クリスタルからの1.024kHzで、これは殆ど低電力消費用に最適化された構成設定です。RTC が1msよりも高い分解能を必要とするなら、より速い32.768kHz出力を選ぶことができます。RTCは外部クロック信号、32.768kHz内部発振器、または32kHz内部ULP発振器からもクロック駆動することができます。

RTCは計数器へ至る前に基準クロックを下げることができる設定可能な10ビットの前置分周器を含みます。広範囲の分解能と時間経過期間を構成設定することができます。32.768kHzのクロック元とで、最大分解能は30.5μs、時間経過期間は2000秒までにできます。1秒の分解能とで、最大時間経過期間は18時間よりも多くなります(65536秒)。RTCは計数器が比較レジスタ値と等しい時に比較割り込みや事象、定期レジスタ値と等しい時に上昇溢れ割り込みや事象を生じることができます。

# 21. USB - 万能直列バス インターフェース

# 21.1. 要点

- 1つのUSB2.0全速(Full-speed:12Mbps)と低速(Low-speed:1.5Mbps)装置適合インターフェース

- 統合されたチップ LUSB送受信部、外部部品不要

- 31までのエント゛ポイントに対する完全なエント゛ポイント柔軟性を持つ16のエント゛ポイントアト・レス

- エント・オペント当たり1つの入力エント・オペノント

- エント、ポイント当たり1つの出力エント、ポイント

- 選択可能なエント゛ポイントアト・レス転送形式

- 制御(Control)転送

- 割り込み(Interrupt)転送

- 大量(Bulk)転送

- 等時(Isochronous)転送

- 設定可能なエント、ポイント当たりのデータ本体量、最大1023小イト

- 内部SRAM内に配置されたエント、ポイント構成設定とデータ緩衝部

- エント゛ポイント構成設定データに対する構成設定可能な位置

- 各エント゛ポイントのテ゛ータ緩衝部に対する構成設定可能な位置

- 以下のための内部SRAMとの組み込み直接メモリ入出力(DMA)

- エント゛ぉ゚イント構成設定

- エント゛ポーイント データ読み書き

- より高い単位処理量のためのピンポン動作と2重緩衝動作

- 単一方向で使われる入力と出力のエント、ポイント データ緩衝部

- 転送中にCPU/DMA制御器がデータ緩衝部を更新可

- 割り込み負荷とソフトウェア介在を減らすための複数パケット転送

- 1つの継続する転送で転送される最大パケット量を超えるデータ本体

- パケット転送段階での割り込みまたはソフトウェアの相互作用なし

- 複数エント゛ポイント使用時の作業の流れ用の転送単位処理完了FIFO

- 到着先行、処理作業待ち行列先行での完了された全ての転送単位処理の経緯

- システム クロック元と選択に無関係なクロック選択

- 低速USB動作に必要とされる最小1.5MHzのCPUクロック

- 全速動作に必要とされる最小12MHzのCPUクロック

- 事象システムへの接続

- USB転送単位処理中のチップ上デバッグの可能性

#### 21.2. 概要

USBインターフェースはUSB2.0全速(Full speed:12Mbps)と低速(Low-speed:1.5Mbps)の装置の適合インターフェースです。

これは16のエント、ポイントアトンスを支援します。全てのエント、ポイントアトンスは1つの入力と1つの出力のエント、ポイント、計32のエント、ポイントを持ちます。各エント、ポイトアトンスは完全に構成設定可能で、制御(Control)、割り込み(Interrupt)、大量(Bulk)、等時(Iso-chronous)の4つの転送形式のどれにも構成設定することができます。データ本体量も選択可能で、1023パイトまでのデータ本体を支援します。

専用メモリはUSB単位部に全く配置または含まれません。各エント、ポイントアトレスに対する構成設定を保つのと、各エント、ポイント用のデータ 緩衝部に内部SRAMが使われます。エント、ポイント構成設定とデータ緩衝部に使われるメモリ位置は完全に構成設定可能です。割り当てられたメモリの量は使うエント、ポイントの数とそれらの構成設定に応じて完全に動的です。USB単位部は組み込み直接メモリ入出力(DMA)を持ちUSB転送単位処理が起こる時にSRAMとデータを読み書きします。

最大単位処理量のため、エント・ポイントアト・レスはピンーポン動作に構成設定することができます。これが行われると、入力と出力のエント・ポイントが両方共同じ方向で使われます。そしてCPUやDMA制御器が1つのデータ緩衝部を読み/書きすると同時にUSB単位部が他方を読み/書きすることができ、その逆もです。これは2重緩衝通信を与えます。

低電力動作のため、USB単位部はUSBバスがアイドルで休止条件が与えられた時にマイクロ コントローラをどれかの休止形態に置くことができます。バス再開で、USB単位部はどの休止形態からもマイクロ コントローラを起こすことができます。

ポートDは1つのUSBを持ちます。これの表記はUSBです。

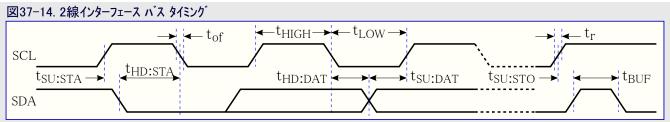

### 22. TWI - 2線インターフェース

#### 22.1. 要点

- 4つの同様のTWI周辺機能

- 双方向2線インターフェース

- Phillips社I2C適合

- システム管理バス(SMBus)適合

- バス権利者(主装置)と従装置を支援

- 従装置動作

- 単一バス権利者(主装置)動作

- 複数バス権利者(主装置)環境でのバス権利者(主装置)

- 複数バス権利者(主装置)調停

- 柔軟な従装置アドレス一致機能

- ハート・ウェアでの7ビットと一斉呼び出しのアトレス認証

- 10ビットアトレス指定支援

- 2重アトレス一致またはアトレス範囲遮蔽用のアトレス遮蔽レシ、スタ

- 無制限のアドレス数のための任意選択ソフトウェア アドレス認証

- パワーダウン動作を含む全休止形態動作で動作可能な従装置動作

- パワーダウン動作を含む全休止形態からデバイスを起こすことができる従装置アドレス一致

- 100kHzと400kHzのバス周波数支援

- スリューレート制限された出力駆動部

- バスの雑音とスパイクを消去するための入力濾波器

- 開始条件/再送開始条件とデータ ビット間の調停を支援(SMBus)

- アドレス解決規約(ARP)に対する支援を許す従装置調停(SMBus)

#### 22.2. 概要

2線インターフェース(TWI)は双方向2線インターフェースです。これはI<sup>2</sup>Cとシステム管理バス(SMBus)適合です。バス実装に必要な外部ハードウェアは各バス線上の1つのプルアップ抵抗だけです。

ハスに接続されたデバイスは主装置または従装置として動作しなければなりません。主装置はバス上の従装置をアドレス指定することによってデータ転送処理を始め、データの送信または受信のどちらを望むかを知らせます。1つのバスは多くの従装置と、バスの制御を取ることができる1つまたは多数の主装置を持つことができます。調停手順は1つよりも多い主装置が同時に送信を試みる場合の優先権を取り扱います。バス衝突を解決するための手法は本質的に規約です。

TWI単位部は主装置と従装置の機能を支援します。主装置と従装置の機能はお互いに分離されており、個別に許可と構成設定ができます。主装置単位部は複数主装置バス動作と調停を支援します。それはボーレート発生器を含みます。100kHzと400kHzの両バス周波数が支援されます。自動起動操作のために迅速指令と簡便動作を許可することができ、ソフトウェアの複雑さを低減します。

従装置単位部はハート・ウェアでの7ビット アドレス一致と一斉アドレス呼び出しを実装します。10ビット アドレスも支援されます。専用のアドレス遮蔽レジスタは第2のアドレス一致レジスタまたはアドレス範囲遮蔽用のレジスタとして働くことができます。従装置はパワーダウン動作を含む全ての休止形態動作で動作を継続します。これはTWIアドレス一致での全休止形態からのデバイス起動を従装置に許します。代わりにソフトウェアでこれを扱うために、アドレス一致を禁止することが可能です。

TWI単位部は開始条件、停止条件、バス衝突、バス異常を検出します。バス上の協調損失、異常、衝突、クロック保持も検出され、主装置と従装置の両動作で利用可能な独立した状態フラグで示されます。

デバイスの内部TWI駆動部を禁止して、外部TWIバス駆動部接続に対する4線インターフェースを許可することが可能です。これはデバイスがTWIバスによって使われるのと違うVCC電圧で動作する応用に使うことができます。

ポートC、ポートD、ポートE、ポートFは各々1つのTWIを持ちます。これらの周辺機能の表記はTWIC、TWID、TWIE、TWIFです。

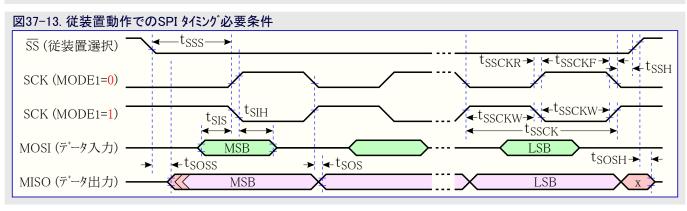

# 23. SPI - 直列周辺インターフェース

#### 23.1. 要点

- 4つの同様なSPI周辺機能

- 全二重、3線同期データ転送

- 主装置または従装置の動作

- LSB先行またはMSB先行のデータ転送

- 設定可能な7つのビット速度

- 送信終了での割り込み要求フラグ

- データ衝突を示すための上書き発生フラグ

- アイドル休止動作からの起動

- 倍速主装置動作

### 23.2. 概要

直列周辺インターフェース(SPI)は3線または4線を使う高速同期データ転送インターフェースです。それはAVR XMEGAデバイスと周辺装置間、または多数のマイクロ コントローラ間での高速通信を許します。SPIは全二重通信を支援します。

バスに接続する装置は主装置または従装置として動作しなければなりません。主装置が全てのデータ転送処理を始め、そして制御します。

ポートC、ポートD、ポートE、ポートFは各々1つのSPIを持ちます。これらの周辺機能の表記はSPIC、SPID、SPIE、SPIFです。

#### 24. USART

#### 24.1. 要点

- 8つの同様なUSART周辺機能

- 全二重動作

- 非同期と同期での動作

- デバイス クロック周波数の1/2までの同期クロック速度

- デバイス クロック周波数の1/8までの非同期クロック速度

- 5、6、7、8、9データ ビットと1、2停止ビットの直列フレーム支援

- 分数ボーレート発生器

- どのシステム クロック周波数からも望むボーレートを生成可

- 一定の周波数で外部発振器不要

- 組み込みの誤り検出と修正の仕組み

- 奇数/偶数パリティ生成器とパリティ検査

- データ オーハーランとフレーミング 異常の検出

- 不正開始ビット検出とデジタル低域通過濾波器を含む雑音濾波

- 以下の独立した割り込み

- 送信完了

- 送信データ レジスタ空

- 受信完了

- 複数プロセッサ通信動作

- 複数デバイスのバス上で特定デバイスをアドレス指定するためのアドレス指定の仕組み

- アドレス指定されないデバイスで全てのフレームを自動的に無視することが可

- 主装置SPI動作

- 2重緩衝された動作

- 構成設定可能なデータ順

- 周辺機能クロック周波数の1/2までの動作

- IrDA適合パルス変調/復調用赤外線通信(IRCOM)単位部

#### 24.2. 概要

USART(Universal Synchronous and Asynchronuos serial Receiver and Transmitter)は高速で柔軟な直列通信単位部です。USART は非同期と同期の動作と全二重通信を支援します。USARTはSPI主装置での動作形態に構成設定してSPI通信に使うことができます。

通信はフレームに基き、その構造形式は広範囲の規格を支援するように独自設定することができます。USARTは両方向於いて緩衝され、フレーム間のどんな遅延もなしに継続するデータ送信を可能にします。受信と送信の完了に対する独立した割り込みは完全な割り込み駆動通信を許します。フレーミング異常と緩衝部溢れはハートヴェアで検知され、独立した状態フラグで示されます。奇数または偶数のパリティ生成とパリティ検査も許可することができます。

クロック生成部はどのシステム クロック周波数からでも広範囲のUSARTボーレートを発生できる分数ボーレート発生器を含みます。これは必要とされるボーレートを達成するために特定周波数を持つ外部クリスタル発振器を使うことの必要を取り去ります。これは同期従装置動作での外部クロック入力も支援します。

USARTが主装置SPI動作に設定されると、全てのUSART特有論理回路は禁止され、送受信緩衝部、移動レジスタ、ボーレート発生器を許可のままにします。 ピン制御と割り込み生成は両動作で同じです。 レジスタは両動作で使われますが、いくつかの制御設定について機能が異なります。

赤外線通信(IRCOM)単位部は115.2kbpsまでのボーレートに対してIrDA 1.4物理適合パルスの変調と復調の支援を1つのUSARTに対して許可することができます。

ポートC、ポートD、ポートE、ポートFは各々、2つのUSARTを持ちます。これらの周辺機能の表記は各々、USARTC1、USART D0、USARTD1、USARTE1、USARTF1です。

# 25. IRCOM - 赤外線通信単位部

### 25.1. 要点

- 赤外線通信用パルス変調/復調

- 115.2kbpsまでのボーレートに対してIrDA適合

- ・選択可能なパルス変調方式

- 3/16ボーレート周期

- 固定パルス周期、設定可能な8ビット

- パルス変調禁止

- ・組み込み濾波

- 何れかのUSARTへ接続可能(USARTによる使用)

### 25.2. 概要

AVR XMEGAディーイスは115.2kbpsまでのボーレートに対してIrDA適合の赤外線通信単位部です。これはUSARTに対して赤外線パルスの符号化と復号を可能とするためにUSARTに接続することができます。

# 26. AESとDESの暗号エンシン

#### 26.1. 要点

- データ暗号化規格(DES)CPU命令

- 新暗号化規格(AES)暗号部

- DES命令

- 暗号化と解読

- DES支援

- 8バイトの塊当たり16 CPUクロック周期の暗号化/解読

- AES暗号部

- 暗号化と解読

- 128ビット鍵支援

- 状態メモリへのXORデータ設定支援

- 16バイトの塊当たり375クロック周期の暗号化/解読

#### 26.2. 概要

新暗号化規格(AES)とデータ暗号化規格(DES)は暗号化に使われる主な2つの規格です。これらはAES周辺単位部とDES CPU命令を通して支援され、通信インターフェースとCPUはこれらを高速で暗号化された通信と安全なデータ記憶に使うことができます。

DESはAVR CPUの命令によって支援されます。8バイトの鍵と8バイトのデータ塊がレジスタ ファイルに格納され、そしてそのデータ塊を暗号化/解読するためにDES命令が16回実行されなければなりません。

AES暗号単位部は128ビット鍵を使う128ビット データ塊の暗号化と解読を行います。鍵とデータは暗号化/解読が開始される前に単位部内の鍵と状態のメモリに格納されていなければなりません。暗号化/解読が行われる前に375周辺機能クロック周期かかります。その後に暗号化/解読されたデータが読み出すことができ、任意選択の割り込みを生成することができます。AES暗号単位部は暗号化/解読が行われた時の転送起動付きのDMA支援と、状態配列メモリが完全に設定された時の任意選択の暗号化/解読の自動開始も持ちます。

### 27. CRC - 巡回冗長検査(Cyclic Redundancy Check)生成器

#### 27.1. 要点

- 以下に対する巡回冗長検査(CRC)生成と検査

- 通信データ

- フラッシュ メモリ内のプログラムまたはデータ

- SRAMとI/Oメモリ空間内のデータ

- フラッシュ メモリ、DMA制御器、CPUとの統合

- DMAチャネルを通して行うデータでの継続的なCRC

- フラッシュ メモリの全体または選択可能な範囲の自動CRC

- CPUはI/Oインターフェースを通してデータをCRC生成器に設定可

- ・以下にソフトウェア選択可能なCRC生成多項式

- CRC-16 (CRC-CCITT)

- CRC-32 (IEEE 802.3)

- 0剰余検出

#### 27.2. 概要

巡回冗長検査(CRC)はデータ内の偶然の誤りを見つけるのに使われる誤り検出技術調査算法で、これは一般的にデータ送信の正しさを決めるのに使われ、データはデータとプログラムのメモリ内に存在します。CRCは入力としてデータの流れまたはデータの塊を取り、データに追加してチェックサムとして使うことができる16ビットまたは32ビットの出力を生成します。同じデータが後で受信される、または読まれる時に、デバイスまたは応用が計算を繰り返します。新しいCRCの結果が先に計算されたものと一致しなければ、その塊はデータ誤りを含みます。そして応用はこれを検知し、再び送るべきデータの要求または単純に不正なデータを不使用のように、調整的な活動を取るかもしれません。

代表的に、任意長のデータ塊に適用されるnビットCRCはnビットよりも長くないどんな単一の連続誤り(データのnビットよりも多くに及ばないどんな単一の改変)も検出し、より長い全ての連続誤り分の1-2<sup>-n</sup>を検出します。AVR XMEGAデバイスのCRC単位部は一般的に使われる2つのCRC生成多項式、CRC-16(CRC=CCITT)とCRC-32(IEEE 802.3)を支援します。

• CRC-16:

生成多項式: $X^{16}+X^{12}+X^{5}+1$

16進値 : \$1021

• CRC-32:

生成多項式: $X^{32}+X^{26}+X^{23}+X^{22}+X^{16}+X^{12}+X^{11}+X^{10}+X^{8}+X^{7}+X^{5}+X^{4}+X^{2}+X+1$

16進值 : \$04C11DB7

### 28. EBI - 外部バス インターフェース

#### 28.1. 要点

- ・以下までのSRAM支援

- 2または3ポートEBI構成設定使用で512Kバイト

- 3または4ポートEBI構成設定使用で16Mバイト

- 以下までのSDRAM支援

- 3または4ポートEBI構成設定使用で128Mビット

- 3ポートEBI構成設定での4ビット SDRAM

- 4ポートEBI構成設定での4または8ビット SDRAM

- ソフトウェアで構成設定可能な4つのチップ選択

- ソフトウェアで構成設定可能な待ち状態挿入

- 高速アクセスのために周辺機能クロック周波数×2で走行可

- 4ポートEBI構成設定でのSRAMとSDRAMの同時支援

#### 28.2. 概要

外部バス インターフェース(EBI)はデータ メモリ空間を通してアクセスする外部の周辺機能とメモリを接続するのに使われます。EBIが許可されると、内部SRAMに属さない(訳補:正確には内部で未定義の)データ アドレス空間が専用EBIピンを使って利用可能になります。

EBIは外部のSRAM、SDRAMや、LCD表示器、その他のメモリ割り当てデバイスのような周辺機能をインターフェースすることができます。

外部メモリ用のアドレス空間は256バイト(8ビット)~16Mバイト(24ビット)まで選択可能です。より多いまたはより少ないピンがEBIに対して利用可能な時に、ピンの最適使用のためにアドレス線とデータ線に関する多くの多重化動作種別を選べます。メモリ全体は内部SRAMの最後に続く1つの直線的なデータ アドレス空間に割り当てられます。これの詳細については15頁の「データ メモリ」を参照してください。

EBIは各々独立した構成設定の4つのチップ選択を持ちます。各々はSRAM、少ピン数(LPC)SRAM、またはSDRAM用に構成設定することができます。

EBIはCPUよりも最大2倍速く走行する高速周辺×2クロックからクロック駆動されます。

4ビットと8ビットのSDRAMが支援され、CAS遅延や再活性速度のようなSDRAM構成設定はソフトウェアで設定することができます。

### 29. ADC - 12t yh A/D変換器

#### 29.1. 要点

- 2つのA/D変換器

- 12ビット分解能

- 1秒当たり最大200万採取

- ADCと1倍利得段を使って同時に2つの入力を採取可

- 1.5µs内で4入力の採取可

- 8ビット分解能で最小2.5µsの変換時間

- 12ビット分解能で最小3.5usの変換時間

- 差動とシングルエントの入力

- 最大16のシングルエント・入力

- 16×4種の利得なし差動入力

- 8×4種の利得付き差動入力

- 組み込み差動利得段

- 1/2倍、1倍、2倍、4倍、8倍、16倍、32倍、64倍の利得任意選択

- 単発、連続、走査の変換任意選択

- 4つの内部入力

- 内部温度感知器

- D/A変換器(DAC)出力

- AVCCの1/10の電圧

- 1.1Vハントギャップ電圧

- 個別の入力制御と結果レジスタを持つ4つの変換チャネル

- 4つの並列構成設定と結果を許可

- 内部及び外部の基準電圧任意選択

- 使用者定義閾値の正確な監視用の比較機能

- 任意選択の正確なタイミング用事象起動変換

- 任意選択の変換結果DMA転送

- 任意選択の比較結果での割り込み/事象

#### 29.2. 概要

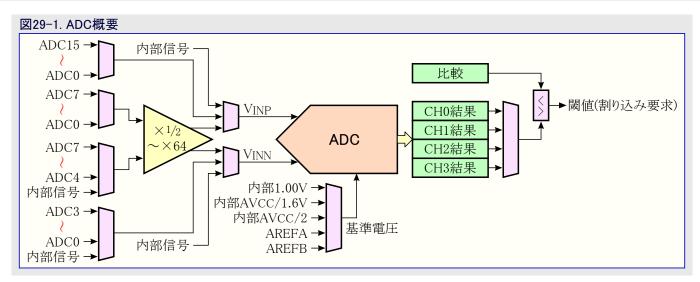

A/D変換器(ADC)はアナログ信号をデジタル値に変換します。同時、個別または同期して動作することができる2つのA/D変換器(ADC)があります。

ADCは12ビット分解能と秒当たり200万採取(Msps)までの変換能力を持ちます。入力選択は柔軟で、シンケルエント、と差動の両方の測定を実行することができます。差動測定に対しては動態範囲を拡大するために任意選択の利得段が利用可能です。加えて多数の内部信号入力が利用可能です。ADCは符号付と符号なしの結果を提供できます。

これは多くの連続段から成るパイプラインADCです。パイプライン設計は低いシステム クロック周波数での高い採取速度を許します。それは他のADC変換が未だ実行中と同時に新しい入力が採取され、新規のADC変換が始められることも意味します。これは採取速度と伝播遅延間の依存性を取り去ります。

ADC個別の入力選択、結果レジスタ、変換開始制御を持つ4つの変換チャネル(0~3)を持ちます。そしてADCは4つの並列構成設定と結果を維持して使うことができ、これは高いデータ単位処理能力またはADC依存性を用いる複数単位部での応用に対する使用を容易にします。変換が行われる時にADCの結果を直接、メモリまたは周辺機能へ移動するのにDMAを使うことが可能です。

内部と外部の両方の基準電圧が使えます。統合された温度感知器がADCとで利用可能です。D/A変換器、AVCC/10、バンドギャップ電圧からの出力もADCによって測定することができます。

ADCは必要とされる最小のソフトウェア介在で使用者定義された閾値の正確な監視のための比較機能を持ちます。

ADCと採取&保持回路を含む利得段の両方と利得段が1倍の利得を持つと時に2つの入力を同時に採取することができます。4つの入力は応用によるどんな介在もなしに1.5μs以内で採取することができます。

ADCは8または12ビットの結果に構成設定することができ、最小変換時間(伝播遅延)を12ビットに対する3.5μsから8ビットの結果に対する2.5μsに減らします。

ADCの変換結果は任意選択の'1'または'0'穴埋め付きの左または右揃えが提供されます。これは結果が符号付き整数(符号付き16 ビット数値)として表される時の計算が容易です。

ポートAとポートBの各々は1つのADCを持ちます。この周辺機能の表記は各々、ADCAとADCBです。

### 30. DAC - 12t yh D/A変換器

#### 30.1. 要点

- 2つの12ビット分解能D/A変換器

- 12ビット分解能

- DAC当たり2つの独立で継続駆動のチャネル

- DACチャネル当たり100万採取/秒までの変換速度

- ・以下を取り去る組み込み校正

- 変位(オフセット)誤差

- 利得誤差

- 複数の変換起動元

- 利用可能な新データで

- 事象システムからの事象

- 高い駆動能力と以下を支援

- 抵抗性負荷

- 容量性負荷

- 抵抗性と容量性の組み合わせ負荷

- 内部と外部の基準電圧任意選択

- アナログ比較器とA/D変換器(ADC)への入力として利用可能なDAC出力

- 低減された駆動力を持つ低電力動作形態

- 任意選択のDMAデータ転送

### 30.2. 概要

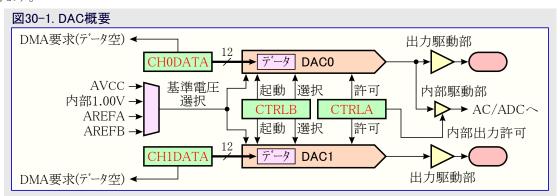

D/A変換器(DAC)はデジタル値を電圧に変換します。DACは各々が12ビット分解能を持つ2つのチャネルを持ち、各チャネルでの秒当たり100万採取(MSPS)の変換能力を持ちます。組み込み校正システムはソフトウェアで校正値を設定した時に変位(オフセット)と利得の誤差を取り去ることができます。

DAC変換は変換されるべき新しいデータが利用可能な時に自動的に開始されます。事象システムからの事象も変換を起動するのに使うことができ、これはタイマ/カウンタのような他の周辺機能とDAC間での時間を定めて同期した変換を許します。DMA制御器はDACへデータを転送するのに使うことができます。

DACは高い駆動力を持ち、抵抗性と容量性の両方だけでなくこれを組み合わせた負荷の駆動能力もあります。低電力動作が利用可能で、これは出力の駆動能力を減らします。

内部と外部の両方の基準電圧を使うことができます。DAC出力は内部的にアナログ比較器やA/D変換器(ADC)への入力としての使用にも利用可能です。

ポートAとポートBの各々は1つのDACを持ちます。この周辺機能の表記は各々、DACAとDACBです。

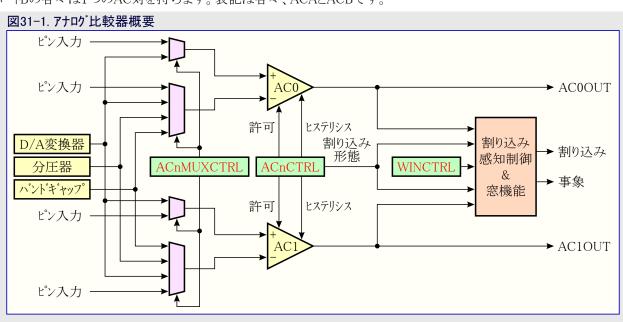

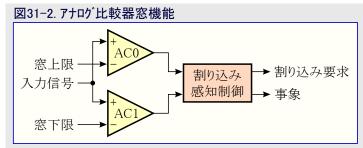

### 31. AC - アナログ比較器

#### 31.1. 要点

- 4つのアナログ比較器

- 選択可能な伝播遅延対消費電流

- 選択可能なヒステリシス

- ・なし

- /\

- 大

- ピンで利用可能なアナログ比較器出力

- 柔軟な入力選択

- ホート上の全ピン

- D/A変換器(DAC)からの出力

- バントギャップ 基準電圧

- 内部AVCC電圧の64段階に設定可能な分圧器

- 以下での割り込みと事象の生成

- 上昇端

- 下降端

- 切り替わり

- 以下での窓機能割り込みと事象の生成

- 窓以上の信号

- 窓内側の信号

- 窓以下の信号

- 構成設定可能な出力ピン選択を持つ定電流源

#### 31.2. 概要

アナログ・比較器(AC)は2つの入力の電圧水準を比較してその比較に基いたデジタル出力を与えます。アナログ・比較器は多数の異なる入力変化の組み合わせで割り込み要求や事象を生成するように構成設定できます。

アナログ比較器の動的な動きの2つの重要な特性はヒステリシスと伝播遅延です。これらのパラメータの両方は各応用に対して最適な動作を 達成するために調節することができます。

入力選択はアナログ ポート ピン、多数の内部信号、64段階の設定可能な分圧器を含みます。アナログ比較器出力の状態は外部デバイスによって使うためにピン上に出力することもできます。

定電流源を許可することができ、選択可能なピン上に出力することができます。これは例えば容量性接触感知応用でコンデンサを充電するのに使われる外部抵抗を置き換えるのに使うことができます。

アナログ比較器は常に各ポート上の対で分類されます。それらはアナログ比較器0(AC0)とアナログ比較器1(AC1)と呼ばれます。それらは同様の動きを持ちますが、独立した制御レジスタを持ちます。対として使うと、それらは電圧水準の代わりに電圧範囲と信号を比較するように窓動作で設定することができます。

ポートAとポートBの各々は1つのAC対を持ちます。表記は各々、ACAとACBです。

図31-2.で示されるように、窓機能は2つのアナログ比較器の外部入力を接続することによって実現されます。

### 32. PDI - プログラミングとデバッグ

#### 32.1. 要点

- プログラミング

- PDIまたはJTAGインターフェースを通す外部プログラミング

- 高速動作のための最小の規約付随負荷

- 確かな動作のための組み込みの異常検出と処理

- 何れかの通信インターフェースを通すプログラミング用のブート ローダ支援

- ・デバッグ

- 不干渉、実時間、チップ・上デバッグ・システム

- ピン接続を除き、デバイスから必要とされるソフトウェアまたはハードウェアなし

- ●プログラムの流れ制御

- 実行、停止、リセット、1行実行、内側実行、外側実行、カーソルまで実行

- 無制限数の使用者プログラム中断点(ブレークポーイント)

- 無制限数の使用者データ中断点、以下で中断

- ずータ位置読み、書き、または読み書き両方

- ずータ位置内容が値と等しいまたは等しくない

- ずータ位置内容が値よりも大きいまたは小さい

- ずータ位置内容が範囲の内側または外側

- デバイス クロック 周波数での制限なし

- プログラミングとデバッグ用インターフェース(PDI)

- 外部のプログラミングとデバッグ用の2ピンインターフェース

- リセット ピンと専用ピンを使用

- プログラミングまたはデバッグ中にI/Oピンの必要なし

- JTAGインターフェース

- プログラミングとデバッグ用の4ピン、IEEE規格1149.1適合インターフェース

- IEEE規格1149.1(JTAG)に従った境界走査(Boundary scan)能力

#### 322 概要

プログラミングとディバッグ用インターフェース(PDI)はディバイスの外部プログラミングとチップ上ディバッグ用の専有インターフェースです。

PDIはフラッシュ、EEPROM、ヒュース、施錠ビット、使用者識票列の不揮発性メモリ(NVM)の高速プログラミングを支援します。

デバック は不干渉、実時間のデバック を提供するチップ 上デバック システムを通して支援されます。これはデバイス ピン接続を除いてどんなソフトウェアまたはハートウェアも必要としません。Microchipのツール チェーン使用は完全なプログラムの流れ制御を提供し、プログラムと複雑なデータの無制限数の中断点(ブレークポイント)を支援します。応用デバッグ はアセンブラと逆アセンブラ レベルからだけでなく、Cまたは他の高位言語ソース コートのレベルからも行うことができます。

プログラミングとディッグは2つの物理インターフェースを通して行えます。基本は全てのディイスで利用可能なPDI物理層です。これはクロック入力用のリセット ピン(PDI\_CLK)とデータ入出力用の他の1つの専用検査ピン(PDI\_DATA)を使う2ピン インターフェースです。殆どのディイスでJTAGインターフェースも利用可能で、これは4ピンのJTAGインターフェースを通してプログラミングとディッグに使うことができます。JTAGインターフェースはIEEE規格1149.1適合で境界走査を支援します。何れかの外部書き込み器またはチップ上ディッガ/エミュレータがこれらインターフェースのどちらかへ直接的に接続することができます。他に言及がなければ、PDIへの全ての参照はPDI物理層を通すアクセスと仮定します。

# 33. ピン配置とピン機能

デバイスのピン配置は6頁の「ピン配置/構成図」で示されます。汎用I/O機能に加え、各ピンは様々な交換機能を持ち得ます。これはどの周辺機能が許可され、そして現実のピンに接続されるかに依存します。ピン機能は同時に1つだけを使うことができます。

### 33.1. 交換ピン機能の種類

下表は利用可能な全てのピン機能に対する表記とその機能の内容を示します。

### 33.1.1. 活動/電力供給

| VCC  | デジタル供給電圧 |

|------|----------|

| AVCC | アナログ供給電圧 |

| GND  | 接地       |

### 33.1.2. ホート割り込み機能

| SYNC  | 完全な同期と制限された非同期の割り込み機能を持つポートピン |

|-------|-------------------------------|

| ASYNC | 完全な同期と完全な非同期の割り込み機能を持つポートピン   |

#### 33.1.3. アナログ機能

| ACn    | アナログ比較器入力ピンn  |

|--------|---------------|

| ACnOUT | アナログ比較器n出力    |

| ADCn   | A/D変換器入力ピンn   |

| DACn   | D/A変換器出力ピンn   |

| AREF   | アナログ・基準電圧入力ピン |

#### 33.1.4. 外部バス インターフェース(EBI)機能

| An   | アドレス線n       |              |

|------|--------------|--------------|

| Dn   | データ線n        |              |

| CSn  | チップ。選択n      |              |

| ALEn | アトレスラッチ許可ピンn | (SRAM)       |

| RE   | 読み込み許可       | (SRAM)       |

| WE   | 外部データメモリ書き込み | (SRAM/SDRAM) |

| BAn  | バンク アトレスn    | (SDRAM)      |

| CAS  | 列アクセス ストローフ゛ | (SDRAM)      |

| CKE  | SDRAMクロック許可  | (SDRAM)      |

| CLK  | SDRAMクロック    | (SDRAM)      |

| DQM  | データ遮蔽信号/出力許可 | (SDRAM)      |

| RAS  | 行アクセス ストローフ゛ | (SDRAM)      |

#### 33.1.5. タイマ/カウンタとAWeX機能

|        | タイマ/カウンタn用比較チャネルx出力       |

|--------|---------------------------|

| OCnx   | タイマ/カウンタn用比較チャネルx反転出力     |

| OCnxLS | タイマ/カウンタn用比較チャネルx Low側出力  |

| OCnxHS | タイマ/カウンタn用比較チャネルx High側出力 |

#### 33.1.6. 通信機能

| SCL    | TWI用直列クロック                   |

|--------|------------------------------|

| SDA    | TWI用直列データ                    |

| SCLIN  | 外部駆動インターフェース許可時のTWI用直列クロック入力 |

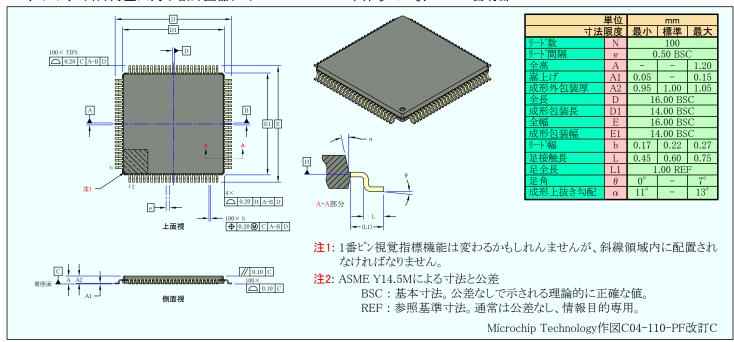

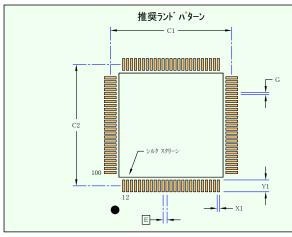

| SCLOUT | 外部駆動インターフェース許可時のTWI用直列クロック出力 |