# 8ビット Atmel XMEGA B マイクロ コントローラ XMEGA B 手引書

本文書はAtmel® AVR® XMEGA® Bマイクロコントローラ系列に含まれる全ての単位部の完全且つ詳細な記述を含みます。Atmel AVR XMEGA BはAVR強化型RISC構造に基いた低電力、高性能、豊富な周辺機能の8/16ビット マイクロコントローラ系列です。この手引書で記載されるAtmel AVR XM EGA B単位部は次のとおりです。

- Atmel AVR CPU

- ・メモリ

- DMAC 直接メモリ入出力制御器(Direct Memory Access Controller)

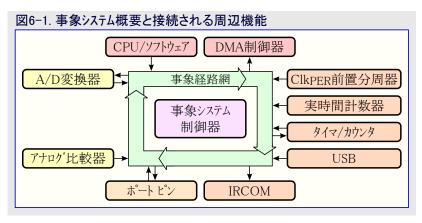

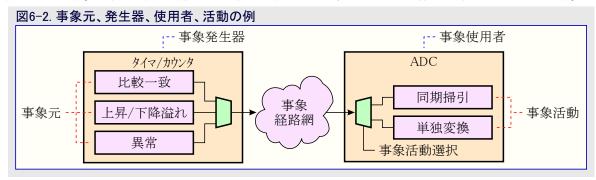

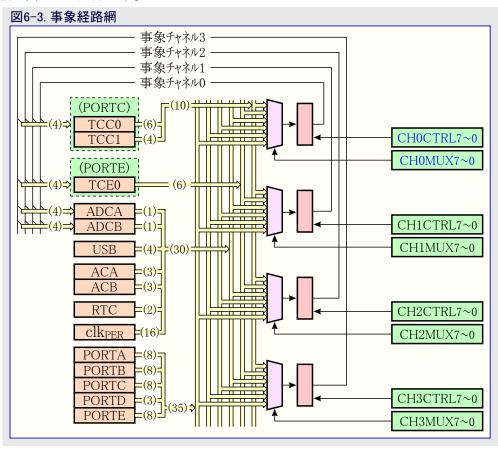

- 事象システム

- システム クロックとクロック選択

- 電力管理と休止形態動作

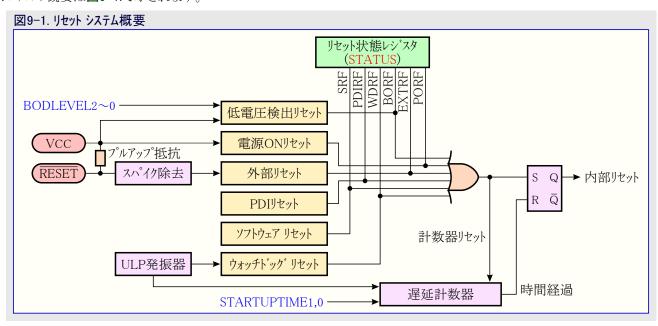

- システム制御とリセット

- WDT ウォッチトック タイマ(Watchdog Timer)

- 割り込みと設定可能な多段割り込み制御器

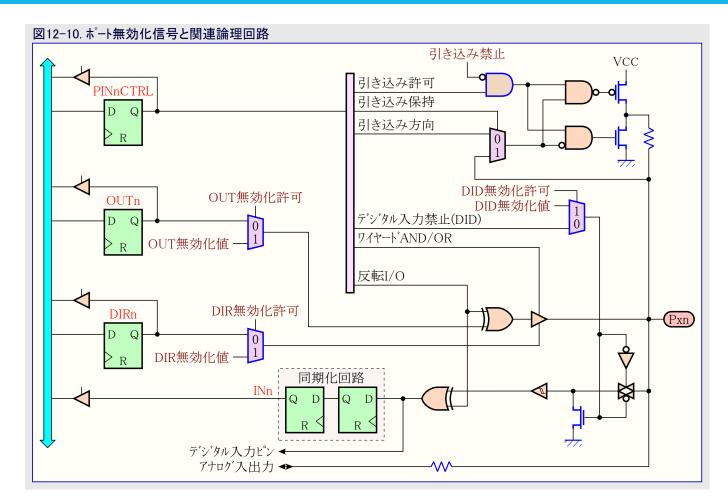

- PORT 入出力ポート

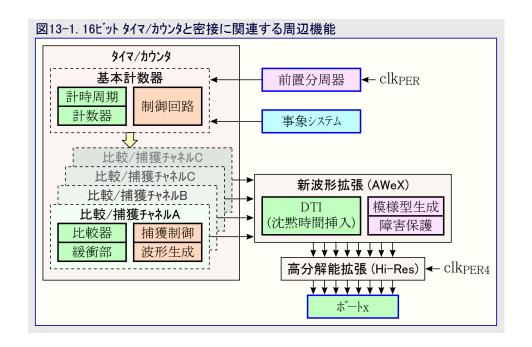

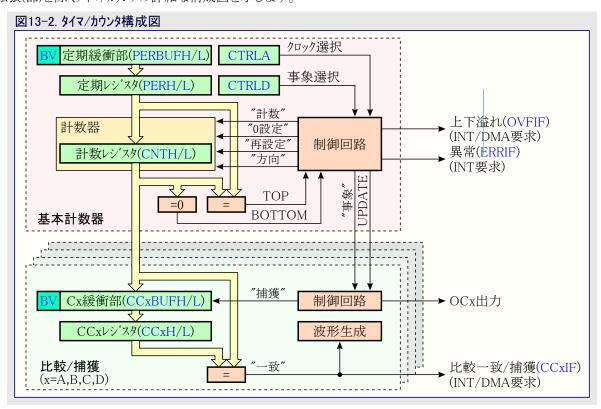

- TC 16ビット タイマ/カウンタ

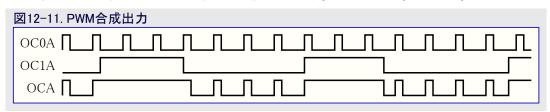

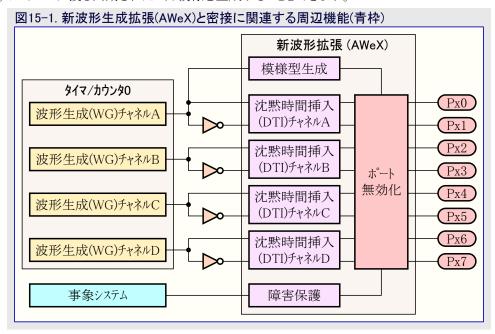

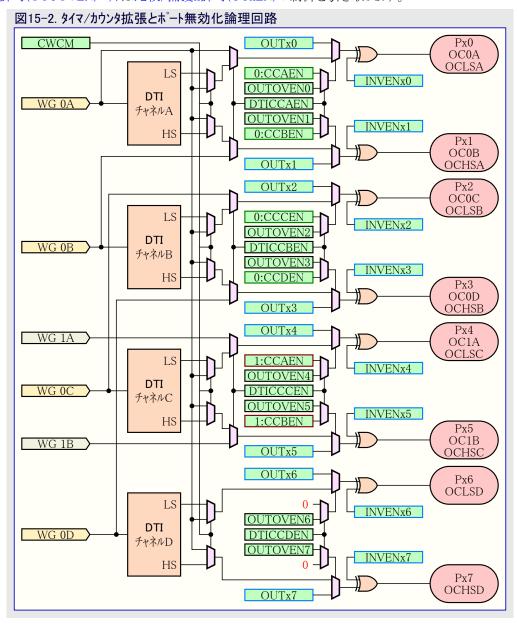

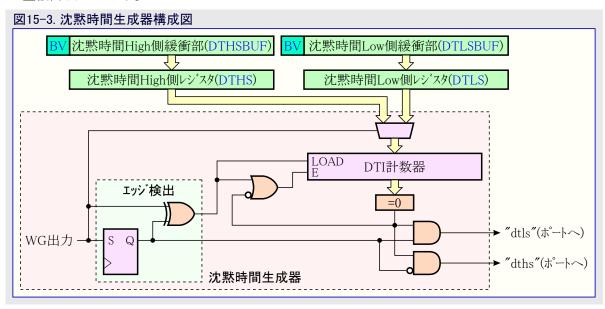

- AWeX 新波形生成拡張

- Hi-Res 高分解能拡張

- RTC 実時間計数器(Real Time Counter)

- USB 万能直列バス インターフェース(Universal serial bus interface)

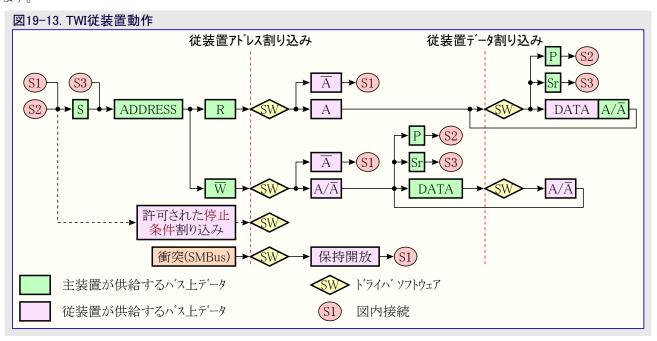

- TWI 2線直列インターフェース(Two Wire Serial Interface)

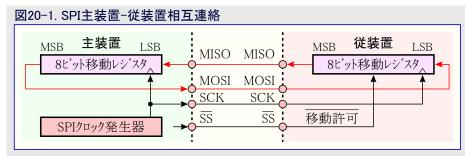

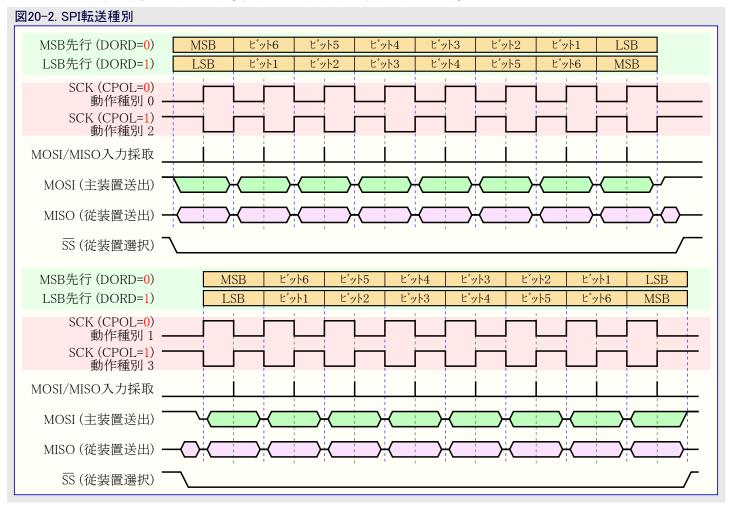

- SPI 設定可能な直列インターフェース(Serial Programmable Interface)

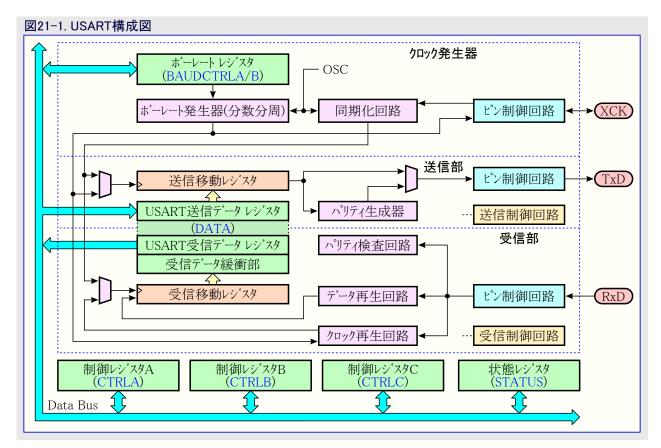

- USART 同期/非同期万能送受信機 (Universal Synchronous and Asynchronous Serial Receiver and Transmitter)

- IRCOM 赤外線通信部(IR Communication Module)

- AESとDESの暗号エンシン

- CRC 巡回冗長検査部(Cyclic redundancy check)

- LCD 液晶表示部(Liquid Crystal Display)

- ADC A/D変換器(Analog to Digital Converter)

- AC アナログ比較器(Analog Comparator)

- IEEE 1149.1 JTAGインターフェース

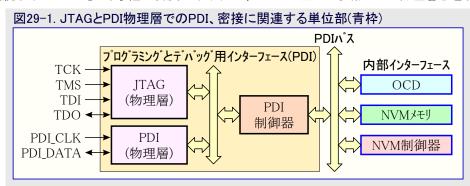

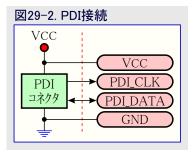

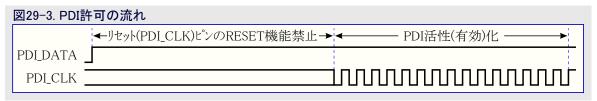

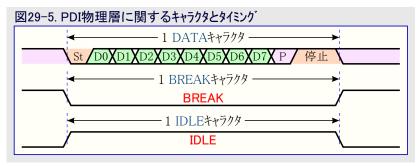

- PDI プログラミングとディッグ用インターフェース

- メモリ プログラミング

- 周辺機能アドレス割り当て

- レシブスタ要約

- 割り込みへ、クタ要約

- 命令一式要約

本書は一般の方々の便宜のため有志により作成されたもので、Atmel社とは無関係であることを御承知ください。しおりの[はじめに]での内容にご注意ください。

## 1. 手引書について

本文書はAtmel AVR XMEGA Bデバイス系列で利用可能な全単位部の徹底的な文書化を含みます。全ての特性は機能的段階で文書化され、一般的な意味で記述されています。この手引書で記述された全ての周辺機能や単位部が全てのAtmel AVR XMEGA B デバイスに存在しないかもしれません。

特性データ、メモリ容量、利用可能な周辺機能のようなデバイス特有情報の全てとそれらのメモリ絶対アドレスついてはデバイスのデータシートを参照してください。1つのデバイスに周辺機能が多数存在する場合、各部は一意の名前を持ちます。例えば各ポート単位部(PORT)はPORTAやPORTBなどのような一意の名前を持ちます。レジスタ名、ビット名はその単位部内で一意です。

周辺機能と単位部に対して用いられる使用とコート・例のより多くの詳細については、http://www.atmel.com/avrで利用可能なAtmel AVR XMEGA固有応用記述を参照してください。

## 1.1. 手引書の読み方

本手引書の主項目は様々な単位部と周辺機能を記述します。各項目は簡単な機能一覧と簡単な単位部概要記述を含みます。項の 残りは特性と機能をもっと詳細に記述します。

レシ、スタ記述項は全レシ、スタを一覧にし、それらの機能と共に各ビットとフラケを記述します。これは単位部の各種機能の設定と許可の方法の詳細を含みます。構成設定に複数ビットが必要な場合、それらはビット群で共に分類されます。可能なビット群構成設定はそれらが関連する群構成設定と簡単な記述と共に全てのビット群に関して一覧にされます。 群構成設定はAtmel AVR XMEGAで使われる定義済み構成設定名、アセンブラ ヘッダ・ファイル、応用記述ソース コートを参照してください。

レシ、スタ要約項は各単位部形式に対する内部レシ、スタ配置を一覧にします。

割り込みへ、クタ要約項は割り込みへ、クタと各単位部形式に対する差分アトレスを一覧にします。

#### 1.2. 資料

開発ツール、応用記述、データシートの包括的な1式はhttp://www.atmel.com/avrからのダウンロードで利用できます。

## 1.3. 推奨読物

- Atmel AVR XMEGA B デブイス データシート

- AVR XMEGA応用記述

本手引書は一般的な単位部と周辺機能記述を含みます。AVR XMEGA Bデバイスのデートシートはデバイス固有情報を含みます。 XMEGA応用記述とAtmelソフトウェア枠組み(ASF)はコートで例を含み、単位部と周辺機能を適用する使い方を示します。

新規の使用者は「AVR1000 - Atmel XMEGAIC対してCコードを書く前に」応用記述を読むことが推奨されます。

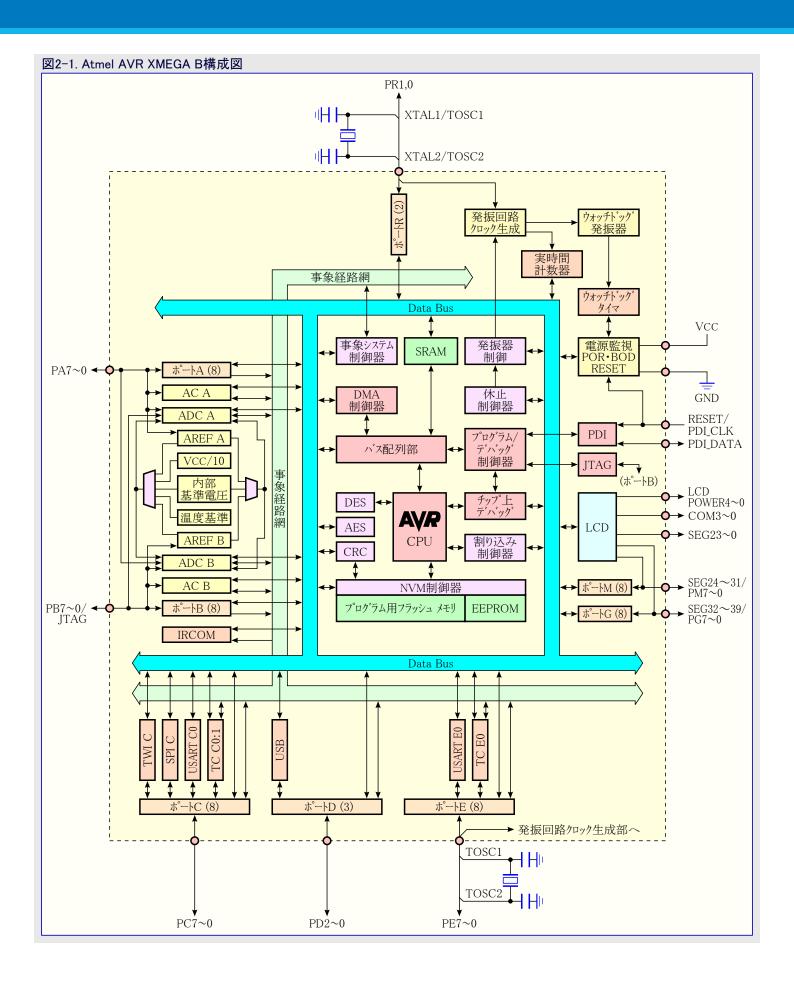

## 2. 概要

AVR XMEGA BはAVR強化型RISC構造に基いた低電力、高性能、豊富な周辺機能の8/16ビットマイクロコントローラ系列です。単一クロック周期で実行する強力な命令によって、Atmel AVR XMEGA Bデバイスはシステム設計者に対して電力消費対処理速度の最適化を可能にする、MHz当たり100万命令(MIPS:Million Instructions Per Second)に達する単位時間処理能力を達成します。

AVR CPUは32個の汎用作業レジスタを豊富な命令一式に結合します。32個全てのレジスタが算術論理演算器(ALU)へ直接接続され、単一命令でのアクセスを2つの独立したレジスタに許し、単一クロック周期で実行されます。この構造はより大きなコート、効率と同時に、伝統的な単一累積器やCISCに基くマイクロコントローラよりも何倍も速い単位時間処理能力達成に帰着します。

Atmel AVR XMEGA Bデバイスは次の機能、実装書き込み可能な書き中の読み(Read-While-Write)能力を持つフラッシュメモリ、内部のEEPROMとSRAM、2チャネルのDMA制御器、4チャネルの事象システム、設定可能な多段割り込み制御器、53本までの汎用入出力線、16 ビット実時間計数器(RTC)、比較動作とPWM付きの3つまでの柔軟な16ビット タイマ/カウンタ、2つまでのUSART、1つの $I^2$ CとSMBus適合の2線直列インターフェース(TWI)、1つの全速(Full-speed)USB2.0インターフェース、1つの直列周辺インターフェース(SPI)、4つまでの共通電極と最大40個のセグメント電極の表示能力を支援する1つのLCD制御器、CRC単位部、AESとDESの暗号エンジン、設定可能な利得付きの任意選択差動入力を持つ2組までの8チャネル 12ビットA/D変換器、窓動作を持つ4つまでのアナログ比較器、独立した内部発振器を持つ設定可能なウォッチドッグタイマ、PLLと前置分周器付きの正確な内部発振器、設定可能な低電圧検出(Brown-Out Detection)を提供します。

プログラミングとデバッグ用の高速2ピン インターフェースのプログラミングとデバッグ インターフェース(PDI)が利用可能です。選ばれたデバイスはIEEE std. 1149. 1適合JTAGインターフェースも持ち、これはチップ上デバッグとプログラミングにも使うことができます。

Atmel AVR XMEGAデバイスはソフトウェアで選択可能な5つの節電動作を持ちます。アイドル動作はCPUを停止する一方で、SRAM、DMA制御器、事象システム、割り込み制御器、全ての周辺機能に機能継続を許します。パワーダウン動作はSRAMとレジスタの内容を保存しますが、発振器を停止し、次のTWI、USB再開またはピン変化の割り込み、またはリセットまで他の全ての機能を禁止します。パワーセーブ動作では非同期実時間計数器が走行を続けて時間の維持を応用に許す一方、デバイスの残りは休止します。この動作形態ではLCD制御器がパネルへのデータ再活性を許されます。スタンバイ動作では外部クリスタル用発振器が走行を保つ一方、デバイスの残りは休止します。これは低電力消費と組み合わせた外部発振器からの非常に速い始動を可能にします。拡張スタンバイ動作では主発振器と非同期計時器の両方が走行を続けます。この動作形態ではLCD制御器がパネルへのデータ再活性を許されます。更なる消費電力低減のため、各個別周辺機能への周辺機能クロックは活動動作とアイドル動作に於いて任意で停止することができます。

デバイスはAtmelの高密度不揮発性メモリ技術を使って製造されています。プログラム用フラッシュメモリはPDIまたはJTAGインターフェースを通して実装書き換えすることができます。デバイス内で走行するブートローダはフラッシュメモリに応用プログラムを取得格納するのにどのインターフェースをも用いることができます。ブートフラッシュ領域内のブートローダ・ソフトウェアは応用フラッシュ領域が更新されている間も走行を続ける、真の「書き中の読み(Read-While-Write)」動作を提供します。実装自己書き換え可能なフラッシュと8/16ビットRISC CPUの結合により、Atmel AVR XMEGAは多くの組み込み応用に対して高い柔軟性と費用効率の解決策を提供する強力なマイクロコントローラ系列です。

Atmel AVR XMEGA BデバイスはCコンパイラ、マクロ アセンフ・ラ、プログラム デバッカ・/シミュレータ、書き込み器、評価キットを含む、プログラムとシステム開発ツールの完全な揃えで支援されます。

表2-1.に於いてXMEGA B系に関する機能要約が示され、各副系亜種に対して1つの機能要約列に分けます。各副系は同じ機能の 組を持ちますが、異なるメモリ選択を持ち、注文符号とメモリ選択についてはそれらのデバイスのデータシートを参照してください。

表2-1. XMEGA B機能要約概要

| 機能                                      | 詳細 副系               | B1          | B3                    |

|-----------------------------------------|---------------------|-------------|-----------------------|

|                                         | 合計                  | 100         | 64                    |

| ピン、I/O                                  | 設定可能なI/Oピン          | 53          | 36                    |

|                                         | プ゜ロク゛ラム メモリ (Kハ゛イト) | 64~128      | 64~128                |

|                                         | ブート メモリ (Κハ イト)     | 4~8         | 4~8                   |

| メモリ                                     | SRAM (Kバイト)         | 4~8         | 4~8                   |

|                                         | EEPROM (Kハ イト)      | 2           | 2~4                   |

|                                         | 汎用レジスタ              | 16          | 16                    |

|                                         | TQFP                | 100A        | 64A                   |

| 外囲器                                     | QFN/VQFN            | -           | 64M2                  |

|                                         | BGA                 | 100C1/100C2 | -                     |

| QTouch                                  | 感知チャネル              | 56          | 56                    |

| DMA制御器                                  | チャネル                | 2           | 2                     |

|                                         | チャネル                | 4           | 4                     |

| 事象システム                                  | QDEC                | 1           | 1                     |

|                                         | 0.4~16MHz XOSC      | 0           | $\cap$                |

| クリスタル用発振器                               | 32.768kHz TOSC      | Ô           | $\overline{\bigcirc}$ |

|                                         | 校正付き2MHz            | Ô           | 0                     |

|                                         | 校正付き32MHz           | Ô           | 0                     |

| 内部発振器                                   | 128MHz PLL          | 0           | 0                     |

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 校正付き32.768kHz       | 0           | $\overline{\bigcirc}$ |

|                                         | 32kHz ULP           | 0           | 0                     |

|                                         | TC0 - 16t yh,4CC    | 2           | 1                     |

|                                         | TC1 - 16t yh,2CC    | 1           | 1                     |

|                                         | TC2 - 8t y > 2      | 2           | 1                     |

| タイマ/カウンタ                                | Hi-Res              | 1           | 1                     |

|                                         | AWeX                | 1           | 1                     |

|                                         | RTC                 | 1           | 1                     |

|                                         | USB全速(Full-speed)装置 | 1           | 1                     |

|                                         | USART               | 2           | 1                     |

| 直列通信                                    | SPI                 | 1           | 1                     |

|                                         | TWI                 | 1           | 1                     |

|                                         | AES-128             | $\cap$      | $\cap$                |

|                                         | DES                 | O           | 0                     |

| 暗号/CRC                                  | CRC-16              | Ô           | O                     |

|                                         | CRC-32              | 0           | 0                     |

| 液晶表示制御器                                 | セグメント               | 40          | 25                    |

| (LCD)                                   | 共通電極                | 4           | 4                     |

| (===)                                   | ADC単位部数             | 2           | 1                     |

|                                         | 分解能(ビット)            | 12          | 12                    |

| A/D変換器 (ADC)                            | 採取速度 (kbps)         | 300         | 300                   |

|                                         | ADC当たりの入力チャネル       | 16          | 8                     |

|                                         | 変換チャネル              | 1           | 1                     |

| アナログ比較器 (AC)                            | -                   | 4           | 2                     |

|                                         | PDI                 | $\bigcirc$  | 0                     |

| プログラミングとデバッグ                            | JTAG                | Ö           | 0                     |

| 用インターフェース                               | 境界走査                | Ô           | O                     |

## 3. Atmel AVR CPU

### 3.1. 要点

- 8/16ビット高性能Atmel AVR RISC CPU

- 142命令

- ハート・ウェア乗算器

- ALUに直結された32個の8ビットレジスタ

- RAM内のスタック

- I/Oメモリ空間内でアクセス可能なスタック ポインタ

- 16Mハーイトまでのプログラムメモリと16Mハーイトのデータメモリを直接アトレス指定

- 16/24ビットレジスタへの真の16/24ビット入出力

- 8、16、32演算に対する効率的な支援

- システム重要特性の構成設定変更保護

#### 3.2. 概要

全てのAtmel AVR XMEGAデバイスは8/16ビットAVR CPUを使っています。CPUの主な機能はコードを実行して全ての計算を実行することです。CPUはメモリ入出力、計算実行、周辺制御、そしてフラッシュメモリ内のプログラムの実行が行えます。割り込みの扱いは独立した項、83頁の「割り込みと設定可能な多段割り込み制御器」で記述されます。

## 3.3. 構造概要

最大性能と並列化のためにAVR CPUはプログラムとデータに対して独立したメモリとハスを持つハーハード構造を使います。プログラムメモリ内の命令は単一段のパイプラインで実行されます。1つの命令が実行されつつあると同時に、次の命令がプログラムメモリから予め取得されます。これは毎クロック周期で実行される命令を可能にします。全AVR命令の要約については285頁の「命令一式要約」を参照してください。

全AVR命令の詳細については http://www.atmel.com/avr を参照してください。

論理演算部(ALU)はレジスタ間またはレジスタと定数間の演算と論理操作を支援します。単独レジスタ操作もALUで実行できます。 演算操作後、操作結果に関する情報を反映するためにステータスレジスタが更新されます。

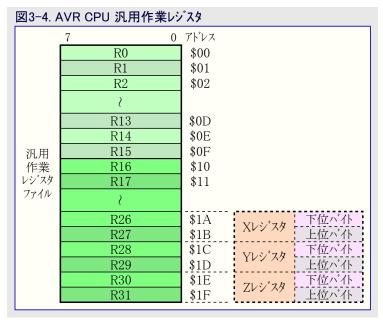

ALUは高速入出力レシ、スタファイルへ直結されます。32個の8ビット汎用作業レシ、スタの全てはレジ、スタ間またはレジ、スタと即値間での単一クロック論理演算操作を許す単一クロック周期アクセスです。32個のレジ、スタ内の6つはデータ空間に対して効率的なアドレス計算を可能とするアドレス指定用の3つの16ビットアドレスポインタとして使うことできます。これらのアドレスポインタ内の1つはプログラム用フラッシュメモリ内の表を調べるためのアドレスポインタとしても使うことができます。メモリ空間は直線的です。データメモリ空間とプログラムメモリ空間は2つの別なメモリ空間です。

データメモリ空間はI/Oレシ、スタ、SRAM、外部RAMに分けられます。 加えてEEPROMがデータメモリ内にメモリ割り当てされ得ます。

全I/Oの状態と制御のレジスタはデータ メモリの最下位4Kバイト位置に属します。これはI/Oメモリ空間として参照されます。最下位64位置は直接的、または\$0000~\$003Fのデータ空間位置としてアク

図3-1. AVR CPU構造の構成図 プログラム カウンタ レシブスタ ファイル R31 (ZH) R30 (ZL) R29 (YH) R28 (YL) R24 プログラム用 R21 R20 フラッシュ メモリ R19 R17 R16 R14 R13 R11 R9 R7 R5 R3 R12 R8 命令レジスタ R4 命令復号 データメモリ スタック ホ。インタ ステータス レシ・スタ ALU

セスできます。残りは\$0040~\$1FFFに連なる拡張I/Oメモリ空間です。I/Oレジスタはここで取得(LD/LDS/LDD)と格納(ST/STS/STD)命令を使ってデータ空間位置としてアクセスされなければなりません。

SRAMはデータを保持します。SRAMからのコード実行は支援されません。AVR構造で支援される5つの異なる位置指定種別を通してこれは容易にアクセスできます。SRAM先頭アドレスは\$2000です。

\$1000~\$1FFFのデータ位置はEEPROMのメモリ割り当て用に予約されています。

プログラム メモリは、応用プログラム領域とブートプログラム領域の2つの領域に分けられます。両領域は書き込みと読み書きの保護用の専用施錠ビットを持ちます。応用フラッシュ メモリの自己プログラミングに使われるSPM命令はブートプログラム領域に属さなければなりません。応用領域は書き込みと読み書きの保護用の独立した施錠ビットを持つ応用表領域を含みます。応用表領域はプログラム用メモリ内での不揮発性データ保存格納に使うことができます。

## 3.4. 算術論理演算器 (ALU)

算術論理演算器(ALU)はレシ、スタ間またはレシ、スタと定数間の演算と論理操作を支援します。単一レシ、スタ操作も実行できます。ALUは32個全ての汎用レシ、スタと直結で動作します。単一クロック周期で、汎用レシ、スタ間または、レシ、スタと即値間の演算操作が実行されて結果がレシ、スタファイルに格納されます。演算または論理操作後、ステータスレシ、スタが操作結果を反映するために更新されます。

ALU操作は、演算、論理、ビット操作の、3つの主な分野に分けられます。

8ビットと16ビットの両方の演算が支援され、命令一式は効率的な32ビット演算の実装を許します。ハードウェア乗算器は符号付と符号なしの乗算そして固定小数点形式を支援します。

## 3.4.1. ハート・ウェア乗算器

乗算器は2つの8ビット数値を16ビットの結果に乗算する能力です。ハードウェア乗算器は符号付と符号なしの整数と固定小数点数の種々の変種を支援します。

- 符号なし整数の乗算

- 符号付き整数の乗算

- 符号付きと符号なしの整数乗算

- 符号なし固定小数点数の乗算

- 符号付き固定小数点数の乗算

- 符号付きと符号なしの固定小数点数乗算

乗算は2CPUクロック周期かかります。

## 3.5. プログラムの流れ

リセット後、CPUはプログラム用フラッシュ メモリ内の最下位アドレス'0'から命令の実行を開始します。プログラム カウンタ(PC)は取得されるべき次の命令の位置を示します。

プログラムの流れはアドレス空間全体を直接位置指定できる条件付きと条件なしの分岐(Jump)と呼び出し(Call)命令によって提供されます。殆どの命令は16ビット語形式を用い、一方特別ないくつかは32ビット形式を用います。

割り込みとサブルーチン呼び出しの間、復帰アトンスのPC(値)がスタックに格納されます。スタックは一般的なデータ用SRAMに配置され、必然的にスタック容量は総SRAM容量とSRAMの使用法によってのみ制限されます。リセット後、スタック ポーインタ(SP)は内部SRAMの最上位アトンスを指し示します。SPはI/Oメモリ空間で読み書きアクセス可能で、多数のスタックまたはスタック領域の容易な実装を許します。データ用SRAMはAVR CPUで支援される5つの異なるアトンス指定形態を通して容易にアクセスすることができます。

## 3.6. 命令実行タイミング

AVR CPUはCPUクロック(clkCPU)によってクロック駆動されます。内部クロック分周は使われません。

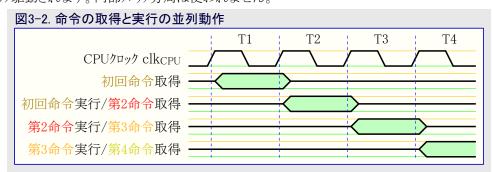

図3-2.はハーハート・構造と高速入出力レジスタファイルの概念によって可能にされる命令取得と命令実行の並列化を示します。これは高い電力効率と共にMHz当たり1MIPSの性能を得るのに使われる基本的なパイプラインの概念です。

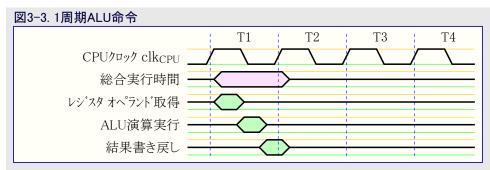

図3-3.はレシ、スタファイルに関する内部タイミングの概念を示します。単一クロック周期で2つのレシ、スタオペラントを使うALU操作が実行され、その結果が転送先レシ、スタへ書き戻されます。

## 3.7. ステータス レジスタ

ステータス レジ スタ(SREG)は最も直前に実行した演算または論理命令の結果についての情報を含みます。この情報は条件付き操作を実行するためにプログラムの流れを変えるのに使えます。ステータス レジスタは「命令一式手引書」で詳述されるように、全てのALU操作後に更新されることに注目してください。これは多くの場合でそれ用の比較命令使用の必要をなくし、高速でより簡潔なコートに帰着します。

ステータス レジスタは割り込み処理ルーチン移行時の保存と割り込みからの復帰時の回復が自動的に行われません。これはソフトウェアによって扱われなければなりません。

ステータス レシ、スタはI/Oメモリ空間でアクセスできます。

## 3.8. スタックとスタック ホ°インタ

スタックは割り込みとサブルーチン呼び出し後の復帰アトンスの格納に使われます。一時データの格納にも使えます。スタック ポインタ(SP)レシ、スタ は常にスタックの先頭(訳注:次に使われるべき位置)を指し示します。これはI/Oメモリ空間でアクセス可能な2つの8ビットレジ、スタとして実装されます。データはPUSH命令とPOP命令を使ってスタックへ格納とスタックから取得されます。スタックは上位メモリ位置から下位メモリ位置へ増えます。これはスタックへのデータ格納がSPを減らし、スタックからのデータ取得がSPを増すことを意味します。SPはリセット後に自動的に設定され、その初期値は内部SRAMの最上位アトンスです。SPが変更されるなら、それは\$2000番地以上を指し示すように設定されなければならず、そして何れかのサブルーチン呼び出しが実行される前、または割り込みが許可される前に定義されなければなりません。

割り込みまたはサブルーチン呼び出しの間、自動的に復帰アドレスがスタックへ格納されています。復帰アドレスはデバイスのプログラム メモリ量に依存して2または3バイトで有り得ます。128Kバイト以下のプログラム メモリを持つデバイスについては復帰アドレスが2バイトで、故にスタック ポインタは+2/-2されます。128Kバイトを越えるプログラム メモリを持つデバイスについては復帰アドレスが3バイトで、故にSPは+3/-3されます。復帰アドレスはRETI命令を使って割り込みから、またはRET命令を使ってサブルーチン呼び出しから戻る時にスタックから取得されます。

データがPUSH命令でスタックに格納される時にSPは-1され、POP命令を使ってスタックからデータを取得する時に+1されます。

ソフトウェアからのスタック ポインタ更新時の改変を防ぐため、SPL書き込みは4命令までに対して、または次のI/Oメモリ書き込みまで割り込みを自動的に禁止します。

#### 3.9. レジスタ ファイル

レジスタファイルは単一クロック周期アクセス時間を持つ32個の8ビット汎用レジスタから成ります。レジスタファイルは以下の入出力機構を支援します。

- 1つの8ビット出力オペラントと1つの8ビットの結果入力

- 2つの8ビット出力オペラントと1つの8ビットの結果入力

- 2つの8ビット出力オペランドと1つの16ビットの結果入力

- 1つの16ビット出力オペランドと1つの16ビットの結果入力

32個のレジスタの6つはデータ空間のアトンス指定用の3つの16ビットアトンスレジスタ ポインタとして用いることができ、効率的なアトンス計算を許します。3つのアトンスポインタの1つはプログラム用フラッシュメモリ内の参照表用のアトンスポインタとしても用いることができます。レジスタファイルは独立したアトンス空間に配置され、故にレジスタはデータメモリとしてアクセスできません。

## 3.9.1. X,Y,Z レジスタ

R26~R31レジスタにはそれらの汎用使用に属する付加機能があります。

これらのレジスタはデータ メモリ位置指示用の16ビットアトレスポインタ形式にできます。これら3つのアトレスレジスタはX,Y,Zレジスタと呼ばれます。Zレジスタはプログラム用フラッシュメモリ、識票列、ヒューズと施錠ビットに対する読み書きのためのアトレスポインタとしても使えます。

下位側レジスタのアトレスは最下位バイト(LSB)を保持し、上位側レジスタのアトレスは最上位バイト(MSB)を保持します。様々な位置指

| 図3-5. X,Y,Z | レジスタ | 2          |     |            |    |

|-------------|------|------------|-----|------------|----|

|             | 15   | XH (上位)    |     | XL (下位)    | 0_ |

| X レジスタ      | 7    | R27 (\$1B) | 0 7 | R26 (\$1A) | 0  |

|             | 15   | YH (上位)    |     | YL (下位)    | 0_ |

| Y レジスタ      | 7    | R29 (\$1D) | 0 7 | R28 (\$1C) | 0  |

|             | 15   | ZH (上位)    |     | ZL (下位)    | 0_ |

| Z レジスタ      | 7    | R31 (\$1F) | 0 7 | R30 (\$1E) | 0  |

|             |      |            |     |            |    |

示種別で、これらのアドレス レジスタは固定変位、自動増加、自動減少としての機能を持ちます(詳細については「**命令一式手引書**」をご覧ください)。

## 3.10. RAMPと間接拡張レジスタ

64Kバイトを越えるプログラム メモリやデータ メモリをアクセスするために、アドレス ポインタは16ビットより多くなければなりません。これはX,Y,または Zレジスタの1つに1つのレジスタを連結することによって行われます。そのレジスタは24ビットのアドレスまたはアドレス ポインタ内の最上位バイト (MSB)を保持します。

これらのレジスタは外部バスインターフェースまたは64Kバイトを越えるプログラムかデータのメモリ空間を持つデバイスでだけ利用できます。これらのデバイスついてはデバイス内のプログラムとデータのメモリ空間全体をアドレス指定するのに必要なビット数だけがレジスタ内に実装されます。

#### 3.10.1. RAMPX,RAMPY,RAMPZ レシ スタ

RAMPX,RAMPY,RAMPZレシ、スタは64Kハ、イトを越え16Mハ、イトまでのデータ メモリ空間全体の間接位置指示を可能とするために各々X,Y,Zレシ、スタと連結されます。

| 図3-6. RAMPX+X,RAM | MPY+Y,RAMPZ | Z+Zレジスタの | 組み合わせ |     |    |   |

|-------------------|-------------|----------|-------|-----|----|---|

| 23                |             | 16 15    |       | 8 7 |    | 0 |

| Xホ°インタ 7          | RAMPX       | 0 7      | XH    | 0 7 | XL | 0 |

| 23                |             | 16 15    |       | 8 7 |    | 0 |

| Yポペンタ 7           | RAMPY       | 0 7      | ΥH    | 0 7 | YL | 0 |

| 23                |             | 16 15    |       | 8 7 |    | 0 |

| Zポペンタ 7           | RAMPZ       | 0 7      | ZH    | 0 7 | ZL | 0 |

|                   |             |          |       |     |    |   |

プログラム メモリの最初の128Kバイトを越えるプログラム メモリ位置の読み込み(ELPM)と書き込み(SPM)時、RAMPZは24ビット アドレス形式のためにZレジスタと連結されます。LPMはRAMPZ設定によって影響を及ぼされません。

#### 3.10.2. RAMPD レジスタ

このレシ、スタは64Kハ、イトを越えるデータ メモリ空間全体の直接位置指示を可能とするためにオペラント、と連結されます。RAMPDとオペラントと 共に24ビット アト、レス形式になるでしょう。

| 図3-7. RAMPD+ | kの組み | 合わせ   |       |     |   |

|--------------|------|-------|-------|-----|---|

|              | 23   |       | 16 15 | 8 7 | 0 |

| 直接位置指示       | 7    | RAMPD | 0 15  | k   | 0 |

#### 3.10.3. EIND レジスタ

EINDはプログラム メモリの最初の128Kバイト(64K語)を越える位置に対して間接の分岐や呼び出しを可能とするためにZポインタと連結されます。

| 図3-8. EIND+Zレ | ジスタの糸 | 且み合わせ |       |    |     |    |   |

|---------------|-------|-------|-------|----|-----|----|---|

|               | 23    |       | 16 15 |    | 8 7 |    | 0 |

| 間接位置指示        | 7     | EIND  | 0 7   | ZH | 0 7 | ZL | 0 |

## 3.11. 16ビット レシ スタのアクセス

AVRのデータ バスは8ビット幅で、故に16ビット レジスタのアクセスは非分断(atomic)操作が必要です。これらのレジスタは2つの読みまたは書き操作を用いてバイト入出力されなければなりません。16ビット レジスタは8ビット バスと16ビット バスを使う一時レジスタに接続されています。

書き込み操作については上位バイトの前に16ビット レジスタの下位バイトが書かれなければなりません。そして下位バイトは一時レジスタに書かれます。16ビット レジスタの上位バイトが書かれる時に、同じクロック周期で一時レジスタが16ビット レジスタの下位バイトに複写されます。

読み込み操作については上位バイトの前に16ビット レジスタの下位バイトが読まれなければなりません。下位バイト レジスタがCPUによって 読まれるとき、下位バイトが読まれるのと同じクロック周期で16ビット レジスタの上位バイトが一時レジスタに複写されます。上位バイトが読まれると、それは一時レジスタから読まれます。

これはレジスタの読み書き時に16ビット レシ、スタの上位バイトと下位バイトがいつも同時にアクセスされることを保証します。

非分断16ビット読み/書き操作間に割り込みが起動されて同じ16ビット レジスタのアクセスを試みる場合、割り込みは時間手順を不正にし得ます。これを防ぐために、16ビット レジスタの読み書き時に割り込みを禁止できます。

一時レジスタは使用者ソフトウェアから直接読み書きできます。

#### 3.11.1. 24及び32ビットレジスタのアクセス

24と32ビットのレジスタに対する読み書きアクセスは、24ビットレジスタについては2つ、32ビットレジスタについては3つの一時レジスタがあるのを除いて、16ビットレジスタに関して記述されたのと同じ方法で行われます。最下位バイトは書き込みを行う時に先に書かれ、読み込みを行う時に先に読まれなければなりません。

## 3.12. 構成設定変更保護

システムの重要なI/Oレシ、スタ設定は予期せぬ変更から保護されます。SPM命令が予期せぬ実行から保護され、LPM命令はヒュースと識票列読み込み時に保護されます。これは構成設定変更保護(CCP)レシ、スタによって全体的に取り扱われます。保護されたI/Oレシ、スタまたはビットへの変更や、保護された命令の実行は、CPUがCCPレシ、スタへ識票を書いた後でだけ可能です。各識票はレシ、スタ説明で記述されます。

I/Oレシ、スタ保護に対する1つとLPM/SPM命令保護に対する2つの動作種別があります。

## 3.12.1. 保護されたI/Oレジスタへの書き込み操作手順

- 1. 応用コートはCCPレジスタに保護されたI/Oレジスタの変更許可用識票を書きます。

- 2. 4命令周期内に応用コートは保護されたレジスタへ適切なデータを書かなければなりません。殆どの保護されたレジスタは書き込み許可/変更許可のビットも含みます。このビットはデータが書かれるのと同じ操作内で1を書かれなければなりません。保護された変更はCPUがI/Oレジスタまたはデータメモリに書き込み操作を実行する場合、またはSPM,LPM.SLEEP命令が実行される場合、直ちに禁止されます。

## 3.12.2. 保護されたLPM/SPMの実行手順

- 1. 応用コードはCCPレジスタに保護されたLPM/SPMの実行用識票を書きます。

- 2. 4命令周期内に応用ュートは適切な命令を実行しなければなりません。保護された変更はCPUがデータメモリに書き込み操作を実行する場合、またはSLEEP命令が実行される場合、直ちに禁止されます。

CPUによって一旦正しい識票が書かれると、割り込みは構成設定変更許可期間中について無視されるでしょう。CCP期間の間の(遮蔽不可割り込みを含む)どんな割り込み要求も通常様に対応する割り込み要求フラグを設定(1)し、そしてその要求は保留を維持されるでしょう。CCP期間完了後に何れかの保留割り込みがそれらのレベルと優先権に従って実行されます。DMA要求が未だ取り扱われていますが、保護された構成設定変更許可期間に影響しません。DMAによって書かれた識票は無視されます。

## 3.13. 施錠ヒューズ

システムで重要ないくつかの機能について関連するI/O制御レジスタ内の全ての変更を禁止するためのヒューズをプログラム(0)にできます。これが行われた場合、使用者ソフトウェアからレジスタを変更することが不可能になり、このヒューズは外部書き込み器を使う書き換えだけができます。これの詳細はこの機能が利用可能な単位部のデーターシートで記述されます。

## 3.14. レジスタ説明

## 3.14.1. CCP - 構成設定変更保護レジスタ (Configuration Change Protection register)

| ピット        | 7 | 6 | 5 | 4   | 3    | 2 | 1   | 0   |     |

|------------|---|---|---|-----|------|---|-----|-----|-----|

| +\$04      |   |   |   | CCF | P7~0 |   |     |     | CCP |

| Read/Write | W | W | W | W   | W    | W | R/W | R/W |     |

| 初期値        | 0 | 0 | 0 | 0   | 0    | 0 | 0   | 0   |     |

#### ● ビット7~0 - CCP7~0:構成設定変更保護 (Configuration Change Protection)

CCPレジスタは保護されたI/Oレジスタの変更または保護された命令の実行を許可するための正しい識票を最大4CPU命令周期内に書かれなければなりません。これらの周期の間は全ての割り込みが無視されます。これらの周期後に割り込みはCPUによって自動的に再び取り扱われて、どの保留割り込みもそれらのレベルと優先権に従って実行されるでしょう。保護されたI/Oレジスタの識票が書かれると、CCP0は保護機能が許可されている限り1として読めます。同様に保護されたLPM/SPMの識票が書かれると、CCP1は保護機能が許可されている限り1として読めます。でCP7~2は常に0として読めます。表3-1.は各種別用の識票を示します。

| 表3-1. CPI | J変更保護種別 |              |

|-----------|---------|--------------|

| 識票        | 構成群種別   | 内容           |

| \$9D      | SPM     | 保護されたLPM/SPM |

| \$D8      | IOREG   | 保護されたI/Oレジスタ |

## 3.14.2. RAMPD - 直接位置指示拡張レジスタ (Extended Direct Addressing register)

64Kバイトを越えるデータ メモリを持つデ゙バイスでデータ メモリ空間全体の直接位置指示(LDS/STS)のために、このレジスタはオペランドと連結されます。外部メモリを含むデータ メモリが64Kバイト以下の場合、このレジスタは利用できません。

| ピット        | 7   | 6   | 5   | 4    | 3     | 2   | 1   | 0   |       |

|------------|-----|-----|-----|------|-------|-----|-----|-----|-------|

| +\$08      |     |     |     | RAMI | PD7~0 |     |     |     | RAMPD |

| Read/Write | R/W | R/W | R/W | R/W  | R/W   | R/W | R/W | R/W |       |

| 初期値        | 0   | 0   | 0   | 0    | 0     | 0   | 0   | 0   |       |

## ● ビット7~0 - RAMPD7~0: 直接位置指示拡張ビット (Extended Direct Addressing bits)

これらのビットはRAMPDと16ビット オペランドによって生成された24ビット アドレスのMSB(最上位バイト)を保持します。各デバイスについては利用可能なデータ メモリのアドレスが必要とするビット数だけが実装されます。未使用ビットは常に0として読めます。

#### 3.14.3. RAMPX - Xポインタ拡張レジスタ (Extended X-Pointer register)

64Kハ・イトを越えるデータ メモリを持つデハ・イスでデータ メモリ空間全体の間接位置指示(LD/LDD/ST/STD)のために、このレジスタはXレジスタと連結されます。外部メモリを含むデータ メモリが64Kバイト以下の場合、このレジスタは利用できません。

| ピット        | 7   | 6   | 5   | 4    | 3     | 2   | 1   | 0   |       |

|------------|-----|-----|-----|------|-------|-----|-----|-----|-------|

| +\$09      |     |     |     | RAMI | PX7∼0 |     |     |     | RAMPX |

| Read/Write | R/W | R/W | R/W | R/W  | R/W   | R/W | R/W | R/W |       |

| 初期値        | 0   | 0   | 0   | 0    | 0     | 0   | 0   | 0   |       |

## ● ビット7~0 - RAMPX7~0: Xポインタ拡張アドレス ビット (Extended X-pointer Address bits)

これらのビットはRAMPXと16ビット Xレジスタによって生成された24ビット アドレスのMSB(最上位バイト)を保持します。各デバイスについては利用可能なデータ メモリのアドレスが必要とするビット数だけが実装されます。未使用ビットは常に0として読めます。

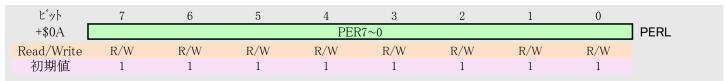

## 3.14.4. RAMPY - Yポインタ拡張レジスタ (Extended Y-Pointer register)

64Kバイトを越えるデータ メモリを持つデバイスでデータ メモリ空間全体の間接位置指示(LD/LDD/ST/STD)のために、このレジスタはYレジスタと連結されます。外部メモリを含むデータ メモリが64Kバイト以下の場合、このレジスタは利用できません。

| ピット _      | 7   | 6   | 5   | 4    | 3     | 2   | 1   | 0   | _     |

|------------|-----|-----|-----|------|-------|-----|-----|-----|-------|

| +\$0A      |     |     |     | RAMI | PY7∼0 |     |     |     | RAMPY |

| Read/Write | R/W | R/W | R/W | R/W  | R/W   | R/W | R/W | R/W |       |

| 初期値        | 0   | 0   | 0   | 0    | 0     | 0   | 0   | 0   |       |

## ● ビット7~0 - RAMPY7~0: Yポインタ拡張アドレス ビット (Extended Y-pointer Address bits)

これらのビットはRAMPYと16ビット Yレジスタによって生成された24ビット アドレスのMSB(最上位バイト)を保持します。各デバイスについては利用可能なデータ メモリのアドレスが必要とするビット数だけが実装されます。未使用ビットは常に0として読めます。

## 3.14.5. RAMPZ - Zポインタ拡張レジスタ (Extended Z-Pointer register)

64Kバイトを越えるデータ メモリを持つデバイスでデータ メモリ空間全体の間接位置指示(LD/LDD/ST/STD)のために、このレジスタはYレジスタと連結されます。先頭の64Kバイトを越えるプログラム メモリ位置を読む(ELPM)時と、先頭の128Kバイトを越えるプログラム メモリ位置に書く(SPM)時に、RAMPZはZレジスタと連結されます。

外部メモリを含むデータ メモリが64Kバイト以下と、デバイス内のプログラム メモリが64Kバイト以下の場合、このレジスタは利用できません。

| ピット        | 7   | 6   | 5   | 4    | 3     | 2   | 1   | 0   |       |

|------------|-----|-----|-----|------|-------|-----|-----|-----|-------|

| +\$0B      |     |     |     | RAMI | PZ7~0 |     |     |     | RAMPZ |

| Read/Write | R/W | R/W | R/W | R/W  | R/W   | R/W | R/W | R/W |       |

| 初期値        | 0   | 0   | 0   | 0    | 0     | 0   | 0   | 0   |       |

## ● ビット7~0 - RAMPZ7~0: Zポインタ拡張アドレス ビット (Extended Z-pointer Address bits)

これらのビットはRAMPZと16ビット Zレジスタによって生成された24ビット アドレスのMSB(最上位バイト)を保持します。各デバイスについては利用可能なデータとプログラムのメモリのアドレスが必要とするビット数だけが実装されます。未使用ビットは常に0として読めます。

## 3.14.6. EIND - 間接拡張レジスタ (Extended Indirect register)

128Kハ・イトを越えるプログラム メモリを持つデハ・イスでプログラム メモリ空間全体の拡張間接の分岐(EIJMP)と呼び出し(EICALL)のために、このレジスタはZレジスタと連結されます。128Kハ・イト以下のアト・レスへの分岐に対してEICALL/EIJMPが使われる場合、このレジスタが使われるべきで、ICALLとIJMP命令が使われる場合にそれは使われません。128Kハ・イト以下のアト・レスへの分岐と呼び出しに関しては、このレジスタが使われません。デハ・イス内のプログラム メモリが128Kハ・イト以下の場合、このレジスタは利用できません。

|                                    | ピット _      | 7   | 6   | 5   | 4    | 3    | 2   | 1   | 0   | _    |

|------------------------------------|------------|-----|-----|-----|------|------|-----|-----|-----|------|

| Read/Write R/W R/W R/W R/W R/W R/W | +\$0C      |     |     |     | EINI | O7~0 |     |     |     | EIND |

| 1000, 11110 1, 11                  | Read/Write | R/W | R/W | R/W | R/W  | R/W  | R/W | R/W | R/W |      |

| 初期値 0 0 0 0 0 0 0 0                | 初期値        | 0   | 0   | 0   | 0    | 0    | 0   | 0   | 0   |      |

#### ● ビット7~0 - EIND7~0:間接拡張アドレス ビット (Extended Indirect Address bits)

これらのビットはEINDと16ビット Zレン゙スタによって生成された24ビット アドレスのMSB(最上位バイト)を保持します。各デバイスについては利用可能なプログラム メモリのアドレスが必要とするビット数だけが実装されます。未使用ビットは常に0として読めます。

### 3.14.7. SPL - スタック ポインタ レシ スタ下位 (Stack Pointer register Low)

SPHとSPLレジスタ対は16ビット値SPを表します。SPはスタックの先頭を指示するスタック ポインタを保持します。リセット後、スタック ポインタは内部 SRAM最高アドレスを指示します。ソフトウェアからスタック ポインタを更新する時の不正(化け)を防ぐため、SPLへの書き込みは次の4命令間、または次のI/Oメモリ書き込みまで割り込みを自動的に禁止します。

各デバイスについては外部メモリを含み64Kバイトまでで利用可能なデータメモリのアドレスが必要とするビット数だけが実装されます。未使用ビットは常に0として読めます。

| ピット _      | 7   | 6   | 5   | 4   | 3            | 2   | 1   | 0   |     |

|------------|-----|-----|-----|-----|--------------|-----|-----|-----|-----|

| +\$0D      |     |     |     | SP' | 7 <b>~</b> 0 |     |     |     | SPL |

| Read/Write | R/W | R/W | R/W | R/W | R/W          | R/W | R/W | R/W |     |

| 初期値        | 0/1 | 0/1 | 0/1 | 0/1 | 0/1          | 0/1 | 0/1 | 0/1 |     |

注: 正確な初期値については固有デバイスのデータシートを参照してください。

ビット7~0 - SP7~0: スタック ポインタ下位ビット (Stack Pointer register Low byte)

これらのビットは16ビットスタック ポインタ(SP)のLSB(最下位バイト)を保持します。

## 3.14.8. SPH - スタック ホーインタ レシ スタ上位 (Stack Pointer Register High)

| ピット _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |     |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| +\$0E      |     |     |     | SP1 | 5~8 |     |     |     | SPH |

| Read/Write | R/W |     |

| 初期値        | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |     |

**注**: 正確な初期値については固有デバイスのデータシートを参照してください。

● ビット7~0 - SP15~8: スタック ポインタ上位ビット (Stack Pointer Register High byte)

これらのビットは16ビットスタック ポインタ(SP)のMSB(最上位バイト)を保持します。

## 3.14.9. SREG - ステータス レジスタ (Status register)

ステータス レシ、スタ(SREG)は最も直前に実行された演算または論理命令の結果についての情報を含みます。

| F. wh      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _    |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| +\$0F      | I   | T   | Н   | S   | V   | N   | Z   | С   | SREG |

| Read/Write | R/W |      |

| 初期値        | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |      |

## ● ビット7 - I: 全体割り込み許可 (Global Interrupt Enable)

全体割り込み許可ビットは許可されるべき割り込みに関して設定(1)されなければなりません。全体割り込み許可ビットが解除(0)された場合、個別割り込み許可設定に拘らず、どの割り込みも許可されません。このビットは割り込みが起きた後でハードウェアによって解除(0)されません。このビットは「命令一式手引書」で記述されるようにSEIとCLI命令で応用(1°ログラム)によって設定(1)と解除(0)ができます。 I/Oレジスタを通したIビットの変更はそのアクセスでの1周期の待ち状態に帰着します。

#### ● ビット6 - T: ビット複写変数 (Bit Copy Storage)

ビット複写命令、ビット取得(BLD:Bit LoaD)とビット格納(BST:Bit STore)は操作するビットの転送元または転送先として、このビットを使います。レジスタ ファイルのレジスタからのビットがBST命令によってこのビットに複写でき、このビットはBLD命令によってレジスタ ファイルのレジスタ内のビットに複写できます。

#### ビット5 - H: ハーフキャリー フラク゛(Half Carry Flag)

ハーフキャリー(H)フラグはいくつかの算術操作でのハーフキャリーを示します。ハーフキャリーはBCD演算に有用です。詳細情報については「命令ー式手引書」をご覧ください。

## ● ビット4 - S: 符号 (Sign Bit, S= N Ex-OR V)

Sフラグは常に負(N)フラグと2の補数溢れ(V)フラグ間の排他的論理和です。詳細情報については「命令一式手引書」をご覧ください。

#### ● ビット3 - V: 2の補数溢れフラグ(2's Complement Overflow Flag)

2の補数溢れ(V)フラグは2の補数算術演算を支援します。詳細情報については「命令一式手引書」をご覧ください。

#### ビット2 - N: 負フラク (Negative Flag)

負(N)フラグは算術及び論理操作での負の結果(MSB=1)を示します。詳細情報については「命令一式手引書」をご覧ください。

#### ヒット1 - Z:セロフラク (Zero Flag)

ゼロ(Z)フラグは算術及び論理操作でのゼロ(0)の結果を示します。詳細情報については「命令一式手引書」をご覧ください。

#### ● ビット0 – C: キャリー フラク (Carry Flag)

キャリー(C)フラグは算術及び論理操作でのキャリー(またはボロー)を示します。詳細情報については「命令一式手引書」をご覧ください。

# 3.15. レジスタ要約

| アト・レス | 略称    | ピット7 | ピット6 | ピット5 | ピット4 | ピット3 | ピット2 | ピット1 | ピット0 | 頁  |

|-------|-------|------|------|------|------|------|------|------|------|----|

| +\$0F | SREG  | I    | Т    | Н    | S    | V    | N    | Z    | С    | 13 |

| +\$0E | SPH   |      | 1    | 1    | SP1  | 5~8  | 1    |      | 1    | 13 |

| +\$0D | SPL   |      |      |      | SP   | 7~0  | 1    |      | 1    | 12 |

| +\$0C | EIND  |      |      |      | EINI | 07~0 | 1    |      | 1    | 12 |

| +\$0B | RAMPZ |      |      |      | RAMI | 27∼0 | 1    |      | 1    | 12 |

| +\$0A | RAMPY |      |      |      | RAMI | Y7~0 | 1    |      | 1    | 12 |

| +\$09 | RAMPX |      |      |      | RAMI | X7~0 | 1    |      | 1    | 11 |

| +\$08 | RAMPD |      |      |      | RAME | D7~0 | 1    |      | 1    | 11 |

| +\$07 | 予約    | -    | _    | -    | -    | -    | -    | -    | -    |    |

| +\$06 | 予約    | -    | _    | -    | -    | -    | -    | -    | _    |    |

| +\$05 | 予約    | -    | _    | -    | -    | -    | -    | -    | _    |    |

| +\$04 | CCP   |      |      |      | CCF  | 7~0  |      |      |      | 11 |

| +\$03 | 予約    | -    | -    | _    | -    | -    | -    | -    | _    |    |

| +\$02 | 予約    | -    | _    | _    | -    | _    | -    | -    | _    |    |

| +\$01 | 予約    | -    | _    | _    | -    | -    | _    | -    | _    |    |

| +\$00 | 予約    |      | -    | -    | -    | -    | -    |      | _    |    |

## 4. メモリ

## 4.1. 要点

- フラッシュ プログラム メモリ

- 1つの直線的なアドレス空間

- 実装書き換え可能(In-System Programmable)

- 自己プログラミングとブートローダ 支援

- 応用コート・用応用領域

- 応用コート またはデータ記憶用応用表領域

- 応用コート、またはブートロータ、コート、用ブート領域

- 全領域に対する独立した施錠ビット

- 選択可能なプログラム用フラッシュ メモリ領域の組み込み高速CRC検査

- データ メモリ

- 1つの直線的なアドレス空間

- CPUからの単一周期アクセス

- SRAM

- EEPROM

- ハブイトとへ。一ジでのアクセスが可能

- 直接の取得と格納に対する任意のメモリ配置割り当て

- I/Oメモリ

- 全ての単位部と周辺機能に対する構成設定と状態のレジスタ

- 全体変数またはフラグ用のビットアクセス可能な16個の汎用I/Oレジスタ

- バス調停

- CPU、DMA制御器、他のバス所有者間の優先順を扱う安全な決定法

- SRAM、EPROM、I/Oメモリのアクセスに関する独立バス

- CPUとDMA制御器に対する同時アクセス

- 工場書き込みデータ用製品識票列メモリ

- 各マイクロ コントローラ型式に対するID

- 各デバイスに対する通番

- 工場較正された周辺機能用の較正バイト

- 使用者識票列

- 1つのフラッシュ ページ 容量

- ソフトウェアから読み書き可能

- チップ消去後の内容保持

#### 4.2. 概要

本項は各種メモリ領域を記述します。AVRの構造はプログラム メモリとデータ メモリの主な2つのメモリ空間を持ちます。実行可能なコードはプログラム メモリにだけ属せ、一方データはプログラム メモリとデータ メモリの両方に格納できます。データ メモリは内部SRAMだけでなく、不揮発性データ記憶用のEEPROMも含みます。全てのメモリ空間は直線状でメモリ バンク切り替えを必要としません。不揮発性メモリ(NVM:Non-Vola tile Memory)空間は更なる書き込みまたは読み書きの操作に対して施錠できます。これは応用ソフトウェアの無制限なアクセスを防ぎます。

独立したメモリ領域はヒューズビットを含みます。これらは重要なシステム機能の構成設定に使われ、外部書き込み器によってだけ書き込むことができます。

#### 4.3. フラッシュ プログラム メモリ

全てのXMEGAデバイスはチップ上にプログラム記憶用の実装書き換え可能なフラッシュ メモリを含みます。フラッシュ メモリはPDIを通す外部書き込み器またはデバイスで走行する応用ソフトウェアから読み書きアクセスができます。

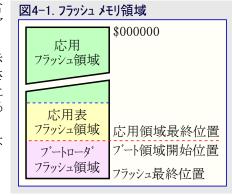

全てのAVR CPU命令は16または32ビット幅、フラッシュの各位置は16ビット幅です。**図4-1**.で示されるようにXMEGAのフラッシュ メモリは応用領域とブートローダ領域の2つの主な領域で構成されています。各領域の容量は固定ですが、デバイス依存です。これら2つの領域は独立した施錠ビットを持ち、異なる保護段階を持てます。応用ソフトウェアからフラッシュを書くのに使われるSPM(Store Program Memory)命令は、ブートローダ領域から実行される時にだけ動作します。

応用領域は独立した施錠設定を持つ応用表領域を含みます。これはプログラム メモリ内の不揮発性データの安全な記憶に使えます。

#### **4.3.1**. 応用領域 (Application Section)

応用領域は実行可能な応用コート・を格納するのに使われるフラッシュの領域です。応用領域に対する保護段階はこの領域用のブート施錠ビット(ブート施錠ビットA)によって選択できます。SPM命令は応用領域から実行することができないので、応用領域はどんなブートロータ・コート・も格納できません。

## 4.3.2. 応用表領域 (Application Table Section)

応用表領域はデータの格納に使えるフラッシュの応用領域の一部です。容量はブートロータ、領域と同じです。応用表に対する保護段階はこの領域用のブート施錠ビット(ブート施錠ビットT)によって選択できます。応用領域と応用表領域で異なる保護段階にできることはプログラムメモリの安全なパラメータ記憶を可能にします。この領域がデータ用に使われないなら、ここに応用コートが存在できます。

#### 4.3.3. ブートローダ領域 (Boot Loader Section)

応用領域が応用コート・の格納に使われる一方、SPM命令がこの領域から実行する時にだけプログラミングを始められるので、ブートローダ、ソフトウェアはブートローダ、領域に配置されなければなりません。SPM命令はブートローダ、領域とれ自身を含むフラッシュ全体をアクセスできます。ブートローダ、領域に対する保護段階はブートローダ、施錠ビット(フート施錠ビットB)によって選択できます。この領域がブートローダ、ソフトウェア用に使われないなら、ここに応用コート・を格納することができます。

## 4.3.4. 製品識票列 (Production Signature Row)

製品識票列は工場書き込みデータ用の独立したメモリ領域です。これは発振器やアナログ部のような機能用の構成データを含みます。いくつかの校正値はリセット中に対応する単位部または周辺機能部へ自動的に格納されます。その他の値はソフトウェアで識票列から取得されて対応する周辺機能レジスタに書かれなければなりません。温度、基準電圧などのような校正条件の詳細についてはデバイスのデータシートを参照してください。

製品識票列は各マイクロコントローラ型式を識別するIDと製造された各デバイスに対する通番も含みます。通番はそのデバイスに対する製品ロット番号、ウェハー番号、ウェハー座標から成ります。

製品識票列は消去や書き込みができませんが、応用ソフトウェアと外部書き込み器から読むことができます。

製品識票列のアクセスについては273頁の「NVMフラッシュ指令」を参照してください。

#### **4.3.5.** 使用者識票列 (User Signature Row)

使用者識票列は応用ソフトウェアと外部の書き込み器から完全にアクセス(読み書き)可能な独立したメモリ領域です。これは1つのフラッシュ へージ 容量で、校正データ、独自の通番や識別番号、乱数の種(素)などのような静的な使用者パラメータ記憶を予定されています。この領域はフラッシュ メモリを消去するチップ 消去指令によって消去されず、専用の消去指令を必要とします。これは多数回の消去/書き込み操作とチップ 上デバッグ 作業中のパラメータ記憶を保証します。

## 4.4. ヒュース と施錠(Lock)ビット

ヒュース、は重要なシステム機能を構成設定するのに使われ、外部プログラミンク、インターフェースから書くことができます。応用ソフトウェアはヒュース、を読むことができます。ヒュース、は低電圧検出器(BOD:Brown-out Detector)やウォッチト、ック、のようなリセット元構成設定や、始動構成設定、JTAG許可とJTAG使用者IDに使われます。

施錠ビットは各種フラッシュ領域の保護段階設定に使われます(換言すると、読み(と/または)書きのアクセスが防止されるべき場合に)。施錠ビットは外部書き込み器と応用ソフトュアから書けますが、より厳しい保護へだけです。チップ消去が施錠ビットを消去する唯一の方法です。例えチップ消去中でもフラッシュ内容が保護されることを保証するため、施錠ビットはフラッシュメモリの残りの部分が(完全に)消去された後に消去されます。

非プログラムにされたヒュース」と施錠のビットは値1を持ち、一方プログラムにされたヒュース」と施錠のビットは値0を持ちます。

ヒュース」と施錠ビットの両方はプログラム用フラッシュメモリのように書き換え可能です。

いくつかのヒュース、バイトに対して、それらを非プログラム(\$FF)のままにすることが不正な設定に帰着します。使用者はヒュース、バイトが有効な設定を与える値にプログラミングされることを確実にしなければなりません。更なる情報については個別ヒュース、バイトの詳細説明を参照してください。

## 4.5. データ メモリ

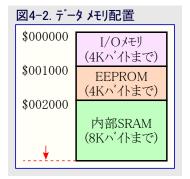

データ メモリはエ/Oメモリ、内部SRAM、任意選択のメモリ配置割り当てEEPROMを含みます。図4-2.で示されるように、データ メモリは1つの続いたメモリ領域として構成されます。

I/Oメモリ、EEPROM、SRAMは全てのXMEGAデバイスに関して常に同じ開始アドレスを持ちます。

## 4.6. 内部SRAM

内部SRAMは常に16進アドレス位置\$2000で始まります。SRAMは取得(LD/LDD/LDS)と格納(ST/STD/STS)命令を使うことでCPUによってアクセスされます。

#### 4.7. EEPROM

XMEGAデバイスは不揮発性データ記憶用にEEPROMを持っています。それは独立したデータ空間(既定)でアドレス指定可能か、または通常のデータ空間でメモリ配置割り当てされてアクセスされるかのどちらかです。EEPROMはバイトとページの両アクセスを支援します。メモリ配置割り当てEEPROMは高い効率のEEPROM読み込みとEEPROM緩衝部格納を許します。これを行うと、EEPROMは取得と格納の命令を使ってアクセスできます。メモリ配置割り当てEEPROMは常に16進アドレス\$1000で始まります。けれども、緩衝部破棄とページの消去と書き込みは未だI/O割り当てアクセスとしてNVM制御器を通して行われなければなりません。

#### 4.8. I/Oメモリ

CPUを含む単位部と周辺機能に関する状態と構成設定のレシ、スタはI/Oメモリ位置を通してアドレス指定できます。全てのI/O位置は取得 (LD/LDD/LDS)と格納(ST/STD/STS)命令によってアクセスでき、そしてそれはレシ、スタファイル内の32個のレシ、スタとI/Oメモリ間でデータを転送するのに使われます。IN命令とOUT命令は\$0000~\$003F範囲のI/Oメモリ位置を直接アドレス指定できます。アドレス範囲\$0000~\$001Fでは個別ビットの操作と検査の命令が利用できます。

#### 4.8.1. 汎用I/Oレジスタ

最下位4個のI/Oメモリ アドレスは汎用I/Oレジスタ用に予約されています。これらのレジスタは、それらがSBI,CBI, SBIS,SBIC命令を使って直接ビット アクセスが可能なため、全体変数とフラグの格納に使うことができます。

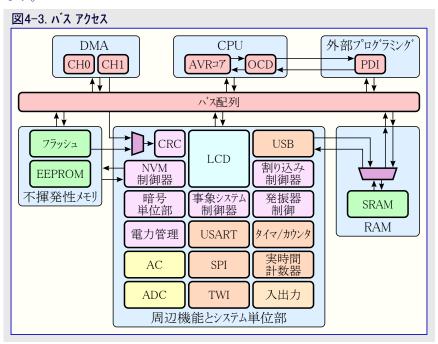

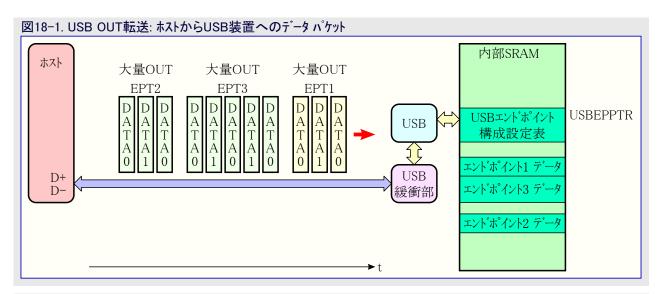

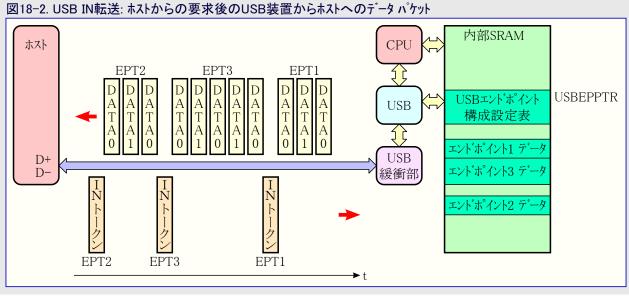

### 4.9. データ メモリとバス調停

データメモリが4つの独立したメモリの組として構成されるため、異なるハ、ス主権部(CPU、DMA制御器読み、DMA制御器書き、など)が同時に異なるメモリ領域をアクセスし得ます。図4-3.をご覧ください。CPUがEEPROMをアクセスできるのと同時にDMA制御器がデータを内部SRAMからI/Oメモリに転送します。USB単位部はハ、ス主権部として働き、擬似2ポート(PDP:Pseudo-DualPort)インターフェースを通して内部SRAMへ直接的に接続されます。

#### 4.9.1. バス優先権

多数の主権部が同じバスへのアクセスを要求するとき、バス優先権は以下の順です(高位から低位の優先順)。

- 1. アクセス実行中のバス主権部

- 2. 集中転送実行中のバス主権部

- 同じデータ メモリ領域アクセス時のDMA制御器読み込みとDMA制御器書き込みの切り換え

- 3. 集中転送アクセスを要求するバス主権部

- CPU優先

- 4. バスアクセスを要求するバス主権部

- CPU優先

## 4.10. メモリ タイミング

I/Oメモリへの読み書きアクセスは1CPUクロック周期かかります。SRAMへの書き込みは1周期かかり、SRAMからの読み込みは2周期かかります。(DMA)集中読み込みについては新しいデータが毎周期で利用可能です。EEPROMぺージ設定(書き込み)は1周期かかり、読み込みに対して3周期が必要です。集中読み込みについては新しいデータが毎2周期で利用可能です。命令と命令タイミングのより多くの詳細については命令要約を参照してください。

## 4.11. デバイスIDと改訂

各々のデバイスは3バイトのデバイスIDを持ちます。このIDはデバイスの製造業者としてのAtmelとデバイス型式を明らかにします。独立した改訂版ID(REVID)レジスタはデバイスの改訂版番号を含みます。

## 4.12. JTAG禁止

応用ソフトウェアからJTAGインターフェースを禁止することができます。これは次のデバイス リセットまたはJTAGが応用ソフトウェアから再び許可されるまで、デバイスへの全ての外部JTAGアクセスを防ぎます。JTAGが禁止されている限り、JTAGで必要とされるI/Oピンとは標準I/Oピンとして使えます。

## 4.13. I/Oメモリ保護

デバイス内のいくつかの機能はいくつかの応用での安全性に大いに関係します。このため、クロック系、事象システム、新波形拡張に関連するI/Oレジスタの施錠が可能です。施錠が許可されている限り、全ての関連I/Oレジスタが施錠され、それらは応用ソフトウェアから書くことができません。それら自身の施錠レジスタは構成設定変更保護機構によって保護されます。詳細については10頁の「構成設定変更保護」を参照してください。

## 4.14. レジスタ説明 - 不揮発性メモリ(NVM)制御器

## **4.14.1. ADDR0 - アドレス レジスタ0** (Address register 0)

ADDR2,ADDR1,ADDR0レジスタは24ビット値ADDRを表します。これは全てのNVM領域の読み、書き、CRC操作のアドレス指定に使われます。

| ピット        | 7   | 6   | 5   | 4   | 3    | 2   | 1   | 0   |       |

|------------|-----|-----|-----|-----|------|-----|-----|-----|-------|

| +\$00      |     |     |     | ADD | R7∼0 |     |     |     | ADDR0 |

| Read/Write | R/W | R/W | R/W | R/W | R/W  | R/W | R/W | R/W |       |

| 初期値        | 0   | 0   | 0   | 0   | 0    | 0   | 0   | 0   |       |

## ヒット7~0 - ADDR7~0: アトレス下位パイト (Address Byte 0)

このレジスタはNVM位置をアクセスする時のアドレス下位バイトを与えます。

## **4.14.2. ADDR1 - アドレス レシ スタ1** (Address register 1)

| ピット        | 7   | 6   | 5   | 4    | 3     | 2   | 1   | 0   |       |

|------------|-----|-----|-----|------|-------|-----|-----|-----|-------|

| +\$01      |     |     |     | ADDI | R15~8 |     |     |     | ADDR1 |

| Read/Write | R/W | R/W | R/W | R/W  | R/W   | R/W | R/W | R/W |       |

| 初期値        | 0   | 0   | 0   | 0    | 0     | 0   | 0   | 0   |       |

#### ヒット7~0 - ADDR15~8: アト・レス上位バイト (Address Byte 1)

このレジスタはNVM位置をアクセスする時のアドレス上位バイトを与えます。

## **4.14.3**. **ADDR2** - **アト**レス レシ スタ2 (Address register 2)

| ピット        | 7   | 6   | 5   | 4    | 3     | 2   | 1   | 0   | _     |

|------------|-----|-----|-----|------|-------|-----|-----|-----|-------|

| +\$02      |     |     |     | ADDF | 23~16 |     |     |     | ADDR2 |

| Read/Write | R/W | R/W | R/W | R/W  | R/W   | R/W | R/W | R/W |       |

| 初期値        | 0   | 0   | 0   | 0    | 0     | 0   | 0   | 0   |       |

#### ビット7~0 - ADDR23~16: アト・レス拡張バイト (Address Byte 2)

このレシ、スタはNVM位置をアクセスする時のアトレス拡張バイトを与えます。

## **4.14.4. DATA0** - データレジスタ0 (Data register 0)

DATA2,DATA1,DATA0レジスタは24ビット値DATAを表します。これはNVM読み、書き、CRCアクセス中のデータを保持します。

| ヒ"ット _     | 7   | 6   | 5   | 4   | 3    | 2   | 1   | 0   |       |

|------------|-----|-----|-----|-----|------|-----|-----|-----|-------|

| +\$04      |     |     |     | DAT | A7~0 |     |     |     | DATA0 |

| Read/Write | R/W | R/W | R/W | R/W | R/W  | R/W | R/W | R/W |       |

| 初期値        | 0   | 0   | 0   | 0   | 0    | 0   | 0   | 0   |       |

#### ビット7~0 - DATA7~0: データ下位バイト (Data Byte 0)

このレシ、スタはNVM位置をアクセスする時のデータ値第1バイトを与えます。

## **4.14.5. DATA1** - データレジスタ1 (Data register 1)

| ピット        | 7   | 6   | 5   | 4    | 3             | 2   | 1   | 0   |       |

|------------|-----|-----|-----|------|---------------|-----|-----|-----|-------|

| +\$05      |     |     |     | DATA | <b>\</b> 15∼8 |     |     |     | DATA1 |

| Read/Write | R/W | R/W | R/W | R/W  | R/W           | R/W | R/W | R/W |       |

| 初期値        | 0   | 0   | 0   | 0    | 0             | 0   | 0   | 0   |       |

|            |     |     |     |      |               |     |     |     |       |

## ● ビット7~0 - DATA15~8: デ-タ上位バイト (Data Byte 1)

このレシ、スタはNVM位置をアクセスする時のデータ値第2バイトを与えます。

#### **4.14.6. DATA2** - **テ**ータ レシ スタ2 (Data register 2)

| ピット        | 7   | 6   | 5   | 4    | 3      | 2   | 1   | 0   | _     |

|------------|-----|-----|-----|------|--------|-----|-----|-----|-------|

| +\$06      |     |     |     | DATA | ∆23~16 |     |     |     | DATA2 |

| Read/Write | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |       |

| 初期値        | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |       |

## ● ビット7~0 - DATA23~16: デ-タ第3バイト (Data Byte 2)

このレジスタはNVM位置をアクセスする時のデータ値第3小小を与えます。

## 4.14.7. CMD - 指令レジスタ (Command register)

| ピット        | 7 | 6 | 5   | 4   | 3      | 2   | 1   | 0   | _   |

|------------|---|---|-----|-----|--------|-----|-----|-----|-----|

| +\$0A      | - |   |     |     | CMD6~0 |     |     |     | CMD |

| Read/Write | R | R | R/W | R/W | R/W    | R/W | R/W | R/W |     |

| 初期値        | 0 | 0 | 0   | 0   | 0      | 0   | 0   | 0   |     |

#### ビット7 - 予約 (Reserved)

このビットは未使用で将来用に予約されています。将来のデバイスとの互換性のため、このレジスタが書かれる時に、このビットへ常に<mark>0</mark>を書いてください。

#### ● ビット6~0 - CMD6~0: 指令(Command)

これらのビットはフラッシュに対するプログラミング指令を定義します。ビット6は外部プログラミング指令に対してだけ設定(1)されます。プログラミング指令については268頁の「メモリ プログラミング」をご覧ください。

## 4.14.8. CTRLA - 制御レジスタA (Control register A)

| ピット        | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |       |

|------------|---|---|---|---|---|---|---|--------|-------|

| +\$0B      | - | - | - | - | - | _ | - | CMDEX  | CTRLA |

| Read/Write | R | R | R | R | R | R | R | R/W(S) |       |

| 初期値        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0      |       |

#### ビット7~1 - 予約 (Reserved)

これらのビットは未使用で将来用に予約されています。将来のデバイスとの互換性のため、このレジスタが書かれる時に、これらのビットへ常に0を書いてください。

## ● ビット0 - CMDEX: 指令実行(Command Execute)

このビットを設定(1)することが不揮発性メモリ指令(CMD)レジスタ内の指令を実行します。このビットは構成設定変更保護(CCP)機構によって保護されており、CCPの詳細については10頁の「構成設定変更保護」を参照してください。

#### 4.14.9. CTRLB - 制御レジスタB (Control register B)

| ピット _      | 7 | 6 | 5 | 4 | 3       | 2    | 1    | 0       |       |

|------------|---|---|---|---|---------|------|------|---------|-------|

| +\$0C      | - | - | - | - | EEMAPEN | FPRM | EPRM | SPMLOCK | CTRLB |

| Read/Write | R | R | R | R | R/W     | R/W  | R/W  | R/W     |       |

| 初期値        | 0 | 0 | 0 | 0 | 0       | 0    | 0    | 0       |       |

#### ビット7~4 - 予約 (Reserved)

これらのビットは未使用で将来用に予約されています。将来のデバイスとの互換性のため、このレジスタが書かれる時に、これらのビットへ常に0を書いてください。

#### ● ビット3 - EEMAPEN : EEPROMデータメモリ割り当て許可 (EEPROM Data Memory Mapping Enable)

このビットを設定(1)することがEEPROM領域のデータ メモリ配置割り当てを許可します。その後EEPROMは取得(LD/LDD/LDS)と格納 (ST/STD/STS)の命令を使ってアクセスできます。

#### ● ビット2 - FPRM: フラッシュ電力削減動作(Flash Power Reduction Mode)

このビットを設定(1)することがフラッシュ メモリに対する節電を許可します。コードが応用領域で走行している場合、ブートローダ領域がOFFされ、逆もまた同様です。OFFされている領域へのアクセスが必要とされる場合、CPUはアイドル休止形態動作からの起動時間と等しい時間停止されます。

#### ● ビット1 - EPRM: EEPROM電力削減動作(EEPROM Power Reduction Mode)

このビットを設定(1)することがEEPROMに対する節電を許可します。その後、EEPROMは休止形態動作移行に等しい規則でOFFにされます。アクセスが必要とされる場合、バス主権部はアイデル休止形態動作からの起動時間と等しい時間停止されます。

#### ● ビット0 - SPMLOCK: SPM施錠(SPM Locked)

このビットは更なる自己プログラミングを防止するために1を書くことができます。このビットはリセットで解除(0)され、ソフトウェアから解除(0)することはできません。このビットは構成設定変更保護(CCP)機構によって保護されており、CCPの詳細については10頁の「構成設定変更保護」を参照してください。

### 4.14.10. INTCTRL - 割り込み制御レジスタ (Interrupt Control register)

| ピット        | 7 | 6 | 5 | 4 | 3    | 2     | 1    | 0     | _       |

|------------|---|---|---|---|------|-------|------|-------|---------|

| +\$0D      | - | _ | - | _ | SPML | VL1,0 | EELV | VL1,0 | INTCTRL |

| Read/Write | R | R | R | R | R/W  | R/W   | R/W  | R/W   |         |

| 初期値        | 0 | 0 | 0 | 0 | 0    | 0     | 0    | 0     |         |

#### ビット7~4 - 予約 (Reserved)

これらのビットは未使用で将来用に予約されています。将来のデバイスとの互換性のため、このレジスタが書かれる時に、これらのビットへ常に0を書いてください。

#### • ビット3,2 - SPMLVL1,0 : SPM操作可割り込みレヘル (SPM Ready Interrupt Level)

これらのビットは割り込みを許可し、83頁の「割り込みと設定可能な多段割り込み制御器」で記述されるように割り込みレベルを選択します。これは状態(STATUS)レジスタの不揮発性メモリ多忙(NVMBUSY)フラグが0に設定される時にだけ起動されるレベル割り込みです。従って、NVM命令が起動される前にはNVMBUSYフラグが設定(1)されないので、この割り込みはNVM命令起動前に許可されるべきではありません。この割り込みは割り込み処理ルーチンで禁止されるべきです。

## ● ビット1,0 - EELVL1,0: EEPROM操作可割り込みレベル (EEPROM Ready Interrupt Level)

これらのビットはEEPROM操作可割り込みを許可し、83頁の「割り込みと設定可能な多段割り込み制御器」で記述されるように割り込みレヘブルを選択します。これは状態(STATUS)レシブスタの不揮発性メモリ多忙(NVMBUSY)フラケがのに設定される時にだけ起動されるレヘブル割り込みです。従って、NVM命令が起動される前にはNVMBUSYフラケブが設定(1)されないので、この割り込みはNVM命令起動前に許可されるべきではありません。この割り込みは割り込み処理ルーチンで禁止されるべきです。

#### 4.14.11. STATUS - 状態レジスタ (Status register)

| ピット        | 7       | 6     | 5 | 4 | 3 | 2 | 1      | 0     |        |

|------------|---------|-------|---|---|---|---|--------|-------|--------|

| +\$0F      | NVMBUSY | FBUSY | - | - | - | - | EELOAD | FLOAD | STATUS |

| Read/Write | R       | R     | R | R | R | R | R      | R     |        |

| 初期値        | 0       | 0     | 0 | 0 | 0 | 0 | 0      | 0     |        |

#### ● ビット7 - NVMBUSY: 不揮発性メモリ多忙フラグ(Non-Volatile Memory Busy)

NVMBUSYフラグはNVM(フラッシュ、EEPROM、施錠ビット)がプログラミングされつつあるかどうかを示します。一旦操作が開始されると、この フラグが設定(1)され、操作が完了されるまで設定(1)に留まります。NVMBUSYフラグは操作完了時に、自動的に解除(0)されます。

#### ビット6 - FBUSY: フラッシュ多忙フラク\*(Flash Busy)

FBUSYフラグはフラッシュのプログラミング動作が始められたかどうかを示します。一旦操作が開始されると、FBUSYフラグが設定(1)され、応用領域がアクセスできなくなります。FBUSYフラグは操作完了時、自動的に解除(0)されます。

#### ビット5~2 - 予約 (Reserved)

これらのビットは未使用で将来の使用に予約されており、常に0として読めます。将来のデバイスとの互換性のため、このレジスタが書かれる時に、これらのビットへ常に0を書いてください。

## ● ビット1 - EELOAD : EEPROMページ緩衝部設定中フラグ(EEPROM Page Buffer Active Loading)

EELOADフラグはEEPROMページ一時緩衝部が1バイト以上格納されていることを示します。これはEEPROMページ書き込みまたはペー ジ緩衝部解除操作が実行されるまで設定(1)に留まります。より多くの詳細については、270頁の「フラッシュ メモリとEEPROMのプログラミング 手順」をご覧ください。

## ● ビット0 - FLOAD : フラッシュ ページ緩衝部設定中フラグ(Flash Page Buffer Active Loading)

FLOADフラグはフラッシュ ペーシー 中緩衝部が1バイト以上格納されていることを示します。これは応用ペーシ 書き込み、ブート ペーシ 書き込み、またはペーシ 緩衝部解除操作が実行されるまで設定(1)に留まります。より多くの詳細については270頁の「フラッシュ メモリとEEPROM のプログラミング 手順」をご覧ください。

## 4.14.12. LOCKBITS - 施錠ビット レジスタ (Lock Bit register)

| ヒ゛ット _     | 7   | 6    | 5   | 4    | 3    | 2     | 1  | 0   |          |

|------------|-----|------|-----|------|------|-------|----|-----|----------|

| +\$10      | BLB | B1,0 | BLB | A1,0 | BLBA | AT1,0 | LB | 1,0 | LOCKBITS |

| Read/Write | R   | R    | R   | R    | R    | R     | R  | R   |          |

| 初期値        | 1   | 1    | 1   | 1    | 1    | 1     | 1  | 1   |          |

|            |     |      |     |      |      |       |    |     |          |

このレシ、スタはI/Oメモリ空間内へのNVM施錠ビット割り当てで、応用ソフトウェアからの直接読み込みアクセスを許します。記述については24頁の「LOCKBITS - 施錠ビット レジスタ」を参照してください。

## 4.15. レジスタ説明 - ヒュース、と施錠ビット

#### **4.15.1. FUSEBYTE0** - ヒュース・ハイト**0** (Fuse Byte 0)

| ピット          | 7  | 6   | 5   | 4       | 3            | 2   | 1   | 0   |           |

|--------------|----|-----|-----|---------|--------------|-----|-----|-----|-----------|

| +\$00        |    |     |     | JTAGUID | 7 <b>~</b> 0 |     |     |     | FUSEBYTE0 |

| Read/Write R | /W | R/W | R/W | R/W     | R/W          | R/W | R/W | R/W |           |

| 初期値          | 0  | 0   | 0   | 0       | 0            | 0   | 0   | 0   |           |

#### ● ビット7~0 - JTAGUID7~0: JTAG使用者ID (JTAG User ID)

これらのヒューズはデバイスに対する既定JTAG使用者ID(JTAG USER ID)を設定するのに使えます。リセットの間にJTAGUIDヒューズビットはMCU JTAG使用者IDレジスタ内に設定されます。

## **4.15.2. FUSEBYTE1** - ヒュース・ハイト1 (Fuse Byte 1)

| ピット _      | 7   | 6   | 5      | 4   | 3   | 2   | 1     | 0   |           |

|------------|-----|-----|--------|-----|-----|-----|-------|-----|-----------|

| +\$01      |     | WDW | PER3~0 |     |     | WDP | ER3~0 |     | FUSEBYTE1 |

| Read/Write | R/W | R/W | R/W    | R/W | R/W | R/W | R/W   | R/W |           |

| 初期値        | 0   | 0   | 0      | 0   | 0   | 0   | 0     | 0   |           |

#### ● ビット7~4 - WDWPER3~0:ウォッチトック、窓周期 (Watchdog Window Timeout Period)

これらのヒュース、ビットは窓動作でのウォッチト、ック、タイマに対する窓閉鎖初期値を設定するのに使われます。リセットの間にこれらのヒュース、ビットが自動的にウォッチト、ック、窓動作制御レシ、スタのウォッチト、ック、窓動作周期(WPER)ビットに書かれます。詳細については81頁の「WINCTR L - 窓動作制御レジ、スタ」を参照してください。

#### ● ビット3~0 - WDPER3~0: ウォッチドック 周期 (Watchdog Timeout Period)

これらのヒュース、ビットはウォッチト、ック、タイマ周期初期値を設定するために使われます。リセットの間にこれらのヒュース、ビットが自動的にウォッチト、ック、制御レジ、スタのウォッチト、ック、周期(PER)ビットに書かれます。詳細については81頁の「CTRL - 制御レジスタ」を参照してください。

#### **4.15.3. FUSEBYTE2** - ヒュース・ハイト2 (Fuse Byte 2)

| ヒ"ット       | 7   | 6       | 5       | 4   | 3   | 2   | 1   | 0     |           |

|------------|-----|---------|---------|-----|-----|-----|-----|-------|-----------|

| +\$02      | -   | BOOTRST | TOSCSEL | -   | _   | -   | BOD | PD1,0 | FUSEBYTE2 |

| Read/Write | R/W | R/W     | R/W     | R/W | R/W | R/W | R/W | R/W   |           |

| 初期値        | 1   | 1       | 1       | 1   | 1   | 1   | 1   | 1     |           |

## ● ビット7 - 予約 (Reserved)

これらのビットは未使用で将来用に予約されています。将来のデバイスとの互換性のため、このレジスタが書かれる時に、これらのビットへ常に1を書いてください。

#### ● ビット6 - BOOTRST: プートローダ領域リセット ペクタ (Boot Loader Section Reset Vector)

このヒュース゛はリセット ベクタがブートローダ フラッシュ領域の先頭アドレスを指示するようにプログラム(0)にできます。 デバイスはリセット後にブートローダ フラッシュ領域から実行を開始します。

| 表4-1. ブート リセット ヒュース゛ |  |  |  |  |  |  |

|----------------------|--|--|--|--|--|--|

| リセット ヘ゛クタ(アト゛レス)     |  |  |  |  |  |  |

| フ゛ートロータ゛リセット         |  |  |  |  |  |  |

| 応用リセット(\$000000)     |  |  |  |  |  |  |

|                      |  |  |  |  |  |  |

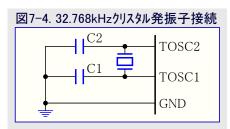

#### ● ビット5 - TOSCSEL: 32.768kHzタイマ発振器ピン選択(32.768kHz Timer Oscillator Pin Selection)

このヒュース'は32.768kHzタイマ発振器(TOSC)用のピン位置の 選択に使われます。このヒュース'は既定によってXTALとTOS Cのピンが共用されているデバイスだけで利用可能です。 **表4-2. TOSCSEL 工場 TOSCSEL 工場**

| 20      |              |                  |

|---------|--------------|------------------|

| TOSCSEL | 群構成設定        | 内容               |

| 0       | ALTERNATE(注) | 独立したピンでのTOSC1/2  |

| 1       | XTAL         | XTALと共用するTOSC1/2 |

注: 代替TOSC位置についてはデバイスのデータシートをご覧ください。

## ビット4~2 - 予約 (Reserved)

これらのビットは未使用で将来用に予約されています。将来のデバイスとの互換性のため、このレジスタが書かれる時に、これらのビットへ常に1を書いてください。

### ● ビット1.0 - BODPD1.0: 低電力保持動作でのBOD動作 (BOD operation in power-down mode)

これらのヒューズビットはデバイスがアイドル動作を除く全ての休止形態動作でのBOD動作種別を設定します。

BODとBOD動作種別の詳細については76頁の「低電圧検出(Brown-out Detection)」を参照してください。

| 表4-3. 休止形 | 表4-3. 休止形態動作でのBOD動作種別 |  |  |  |  |  |  |  |

|-----------|-----------------------|--|--|--|--|--|--|--|

| BODPD1,0  | 内容                    |  |  |  |  |  |  |  |

| 0 0       | (予約)                  |  |  |  |  |  |  |  |

| 0 1       | 採取動作でBOD許可            |  |  |  |  |  |  |  |

| 1 0       | 継続的にBOD許可             |  |  |  |  |  |  |  |

| 1 1       | BOD禁止                 |  |  |  |  |  |  |  |

## **4.15.4. FUSEBYTE4** - ヒュース・ハイト4 (Fuse Byte 4)

| <b>ビット</b> | 7   | 6   | 5   | 4        | 3      | 2        | 1      | 0      |           |

|------------|-----|-----|-----|----------|--------|----------|--------|--------|-----------|

| +\$04      | -   | _   | -   | RSTDISBL | STARTU | PTIME1,0 | WDLOCK | JTAGEN | FUSEBYTE4 |

| Read/Write | R/W | R/W | R/W | R/W      | R/W    | R/W      | R/W    | R/W    |           |

| 初期値        | 1   | 1   | 1   | 1        | 1      | 1        | 1      | 0      |           |

#### ビット7~5 - 予約 (Reserved)

これらのビットは未使用で将来用に予約されています。将来のデバイスとの互換性のため、このレジスタが書かれる時に、これらのビットへ常に1を書いてください。

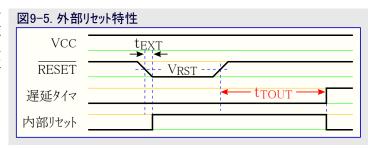

#### ● ビット4 - RSTDISBL:外部リセット禁止(External Reset Disable)

このヒューズは外部リセット ピン機能を禁止するためにプログラム(0)にできます。これが行われると、リセット ピンのLow引き込みは外部リセットを引き起こしません。このビットが変更された後でそれが正しく読めるのに先立ってリセットが必要とされます。

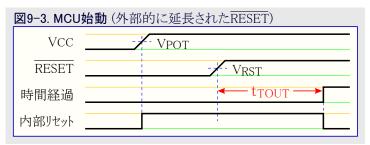

## ● ビット3,2 - STARTUPTIME1,0: 始動時間 (Start-up time)

これらのヒュース、ヒットは全てのリセット元が開放される時から内部リセットが遅延計数器から開放されるまでの設定可能な時間間隔を設定するのに使えます。これらのヒットが変更された後でそれらが正しく読めるのに先立ってリセットが必要とされます。

この遅延は超低電力(ULP)発振器の1kHz出力で計時されます。詳細については75頁の「リセットの流れ」を参照してください。

| 表4-4. 始動時間     |                |  |  |  |  |  |  |  |

|----------------|----------------|--|--|--|--|--|--|--|

| STARTUPTIME1,0 | 1kHz ULP発振器周期数 |  |  |  |  |  |  |  |

| 0 0            | 64             |  |  |  |  |  |  |  |

| 0 1            | 4              |  |  |  |  |  |  |  |

| 1 0            | (予約)           |  |  |  |  |  |  |  |

| 11             | 0              |  |  |  |  |  |  |  |

## ● ビット1 - WDLOCK: ウォッチドッグ タイマ施錠 (Watchdog Timer lock)

WDLOCKヒュース<sup>\*</sup>はウォッチト<sup>\*</sup>ック<sup>\*</sup> タイマ構成設定を施錠するためにプログラム(0)にすることができます。このヒュース<sup>\*</sup>がプログラム(0)されると、ウォッチト<sup>\*</sup>ック<sup>\*</sup> タイマ構成設定を変更できなくなり、リセットでウォッチト<sup>\*</sup>ック<sup>\*</sup> タイマ制御(CTRL)レシ<sup>\*</sup>スタのウォッチト<sup>\*</sup>ック<sup>\*</sup>許可(ENABLE)ヒ<sup>\*</sup>ットが自動的

に設定(1)され、応用ソフトウェアから解除(0)できなくなります。ウォッチト、ッケ、タイマ窓制御(WINCTRL)レシ、スタのウォッチト、ッケ、窓動作許可(WEN) ビットは自動的に設定(1)されず、ソフトウェアからの設定(1)を必要とします。このビットが変更された後でそれが正しく読めるのに先立ってリセットが必要とされます。

| WDLOCK | 内容                       |

|--------|--------------------------|

| 0      | ウォッチドッグタイマは変更に対して閉ざされます。 |

| 1      | ウォッチドッグタイマは施錠されません。      |

#### ● ビット0 - JTAGEN: JTAG許可 (JTAG Enable)

このヒューズはJTAGインターフェースが許可されるか否かを制御します。

JTAGインターフェースが禁止されると、JTAGを通す全てのアクセスが禁止され、デバイスはプログラミングとデバックが用インターフェース(PDI)を用いてだけアクセスすることができます。

JTAGENヒューズはJTAGインターフェースを持つデバイスでだけ利用可能です。このビットが変更された後でそれが正しく読めるのに先立ってリセットが必要とされます。

| 表4-6. JTAG許可 |           |  |  |  |  |  |  |  |  |

|--------------|-----------|--|--|--|--|--|--|--|--|

| JTAGEN       | JTAGEN 内容 |  |  |  |  |  |  |  |  |

| 0            | JTAG許可    |  |  |  |  |  |  |  |  |

| 1            | JTAG禁止    |  |  |  |  |  |  |  |  |

#### **4.15.5. FUSEBYTE5** – ヒュース・ハイト5 (Fuse Byte 5)

| <b>ビット</b> | 7 | 6 | 5    | 4      | 3      | 2   | 1         | 0   |           |

|------------|---|---|------|--------|--------|-----|-----------|-----|-----------|

| +\$05      | - | _ | BODA | ACT1,0 | EESAVE | В   | ODLEVEL2~ | ~0  | FUSEBYTE5 |

| Read/Write | R | R | R/W  | R/W    | R/W    | R/W | R/W       | R/W |           |

| 初期値        | 1 | 1 | -    | _      | -      | -   | -         | -   |           |

#### ビット7.6 - 予約 (Reserved)

これらのビットは未使用で将来用に予約されています。 将来のデバイスとの互換性のため、このレジスタが書かれる時に、これらのビットへ 常に1を書いてください。

#### ● ビット5,4 - BODACT1,0 : 活動中のBOD動作 (BOD operation in active mode)

これらのヒューズビットはデバイスが活動(標準)またはアイドル動作の時のBOD動作種別 を設定します。

BODとBOD動作種別の詳細については76頁の「低電圧検出(Brown-out Detectio n)」を参照してください。

| 表4-7. 活動とアイドル動作でのBOD動作種別 |              |     |  |  |  |  |  |

|--------------------------|--------------|-----|--|--|--|--|--|

| BODACT1,0                | BODACT1,0 内容 |     |  |  |  |  |  |

| 0 0                      | (予約)         |     |  |  |  |  |  |

| 0 1                      | 採取動作でBO      | D許可 |  |  |  |  |  |

| 1 0                      | 継続的にBOD      | 許可  |  |  |  |  |  |

| 1 1                      | BOD禁止        |     |  |  |  |  |  |

#### ● ビット3 - EESAVE: チップ消去からEEPROM保護 (EEPROM is preserved through the Chip Erase)

チップ消去命令は標準的にフラッシュ、EEPROM、内部SRAMを消去します。このヒューズがプログラム(0)されている場合、チップ消去の間に EEPROMは消去されません。これはEEPROMがソフトウェア改訂版に無関係なデータの格納に使われる場合に有用です。

EESAVEヒューズビット変更は書き込み時間経過後直ちに効力を発 表4-8 チップ消去を涌したFFPROM保護 揮します。従って、プログラミング動作の抜け出しと再移行なしにEES AVE更新とEESAVEの新しい設定に応じたチップ消去の実行が可能 です。

| 表4-8. ナップ | 泊去を囲したEEPROM保護 |

|-----------|----------------|

| FESAVE    | 内容             |

| EESAVE | 内容                     |

|--------|------------------------|

| 0      | EEPROMはチップ消去の間、保護されます。 |

| 1      | EEPROMはチップ消去の間に消去されます。 |

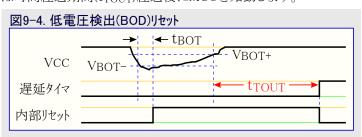

#### ● ビット2~0 - BODLEVEL2~0: 低電圧検出(BOD)電圧 (Brown-ut detection voltage level)

これらのヒューズビットはBOD電圧値を設定します。電源投入時、デバイスはVCCが設定されたBOD電圧に達するまでリセットを維持しま す。このため、BOD電圧は常にVCCよりも低く設定されることを保証してください。通常動作の間にBODが許可され且つ使われない 場合、詳細については76頁の「Jセット元」を参照してください。BOD電圧の公称値については76頁の表9-2.をご覧ください。

## 4.15.6. LOCKBITS - 施錠ビットレジスタ (Lock Bit register)

| Ľ'ット       | 7       | 6   | 5            | 4   | 3        | 2   | 1     | 0   | _        |

|------------|---------|-----|--------------|-----|----------|-----|-------|-----|----------|

| +\$07      | BLBB1,0 |     | B1,0 BLBA1,0 |     | BLBAT1,0 |     | LB1,0 |     | LOCKBITS |

| Read/Write | R/W     | R/W | R/W          | R/W | R/W      | R/W | R/W   | R/W |          |

| 初期値        | 1       | 1   | 1            | 1   | 1        | 1   | 1     | 1   |          |

## ● ビット7,6 - BLBB1,0:ブート領域ブート施錠ビット1,0 (Boot Lock Bit Boot Section)

これらの施錠ビットはブートローダ領域に対するソフトウェア保護レベルを制御します。BLBBビットはより厳しい施錠へだけ書くことができます。 BLBBビットのリセットはチップ消去命令の実行によって可能です。

表4-9 ブートローダ領域用ブート施錠ビット

| BLBB1,0 | 群構成設定  | 内容                                                                                                                                   |

|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------|

| 11      | NOLOCK | 施錠なし、ブートローダ、領域をアクセスするSPMと(E)LPM命令に制限はありません。                                                                                          |

| 1 0     | WLOCK  | 書き込み施錠、SPM命令はブートローダ領域書き込みを許されません。                                                                                                    |

| 0 1     | RLOCK  | 読み込み施錠、応用領域で実行する(E)LPM命令はブートローダ領域からの読み込みを許されません。<br>割り込みベクタが応用領域に配置されている場合、ブートローダ領域から実行されている間、割り込みが禁止されます。                           |

| 0 0     | RWLOCK | 読み書き施錠、SPM命令はブートローダ領域への書き込みを許されず、応用領域で実行する(E)LPM命令はブートローダ領域からの読み込みを許されません。<br>割り込みベクタが応用領域に配置されている場合、ブートローダ領域から実行されている間、割り込みが禁止されます。 |

## ● ビット5,4 - BLBA1,0:応用領域プート施錠ビット1,0 (Boot Lock Bit Application Section)

これらのビットは表4-10.に従って応用領域に対するソフトウェア保護レベルを制御します。BLBAビットはより厳しい施錠へだけ書くことができます。BLBAビットのリセットはチップ消去命令の実行によってのみ可能です。

表4-10. 応用領域用ブート施錠ビット

| BLBA1,0 | 群構成設定  | 内容                                                                                                                               |

|---------|--------|----------------------------------------------------------------------------------------------------------------------------------|

| 11      | NOLOCK | 施錠なし、応用領域をアクセスするSPMと(E)LPM命令に制限はありません。                                                                                           |

| 1 0     | WLOCK  | 書き込み施錠、SPM命令は応用領域書き込みを許されません。                                                                                                    |

| 0 1     | RLOCK  | 読み込み施錠、ブートロータ。領域で実行する(E)LPM命令は応用領域からの読み込みを許されません。<br>割り込みベクタがブートロータ。領域に配置されている場合、応用領域から実行されている間、割り込みが禁止されます。                     |

| 0 0     | RWLOCK | 読み書き施錠、SPM命令は応用領域への書き込みを許されず、ブートローダ領域で実行する(E)LPM命令は応用領域からの読み込みを許されません。<br>割り込みベクタがブートローダ領域に配置されている場合、応用領域から実行されている間、割り込みが禁止されます。 |

#### ● ビット3,2 - BLBAT1,0:応用表領域プート施錠ビット1,0 (Boot Lock Bit Application Table Section)

これらのビットはソフトウェア アクセスに関する応用表領域に対するソフトウェア保護レベルを制御します。BLBATビットはより厳しい施錠へだけ書くことができます。BLBATビットのリセットはチップ消去命令の実行によってのみ可能です。

表4-11. 応用表領域用ブート施錠ビット

| BLBAT1,0 | 群構成設定  | 内容                                                                                                                                  |

|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------|

| 11       | NOLOCK | 施錠なし、応用表領域をアクセスするSPMと(E)LPM命令に制限はありません。                                                                                             |

| 1 0      | WLOCK  | 書き込み施錠、SPM命令は応用表領域書き込みを許されません。                                                                                                      |

| 0 1      | RLOCK  | 読み込み施錠、ブートローダ領域で実行する(E)LPM命令は応用表領域からの読み込みを許されません。<br>割り込みベクタがブートローダ領域に配置されている場合、応用領域から実行されている間、割り込みが禁止されます。                         |

| 0 0      | RWLOCK | 読み書き施錠、SPM命令は応用表領域への書き込みを許されず、ブートローダ領域で実行する(E)LPM命令は応用表領域からの読み込みを許されません。<br>割り込みへ、カタがブートローダ領域に配置されている場合、応用領域から実行されている間、割り込みが禁止されます。 |

#### • ビット1,0 - LB1,0:施錠ビット1,0 (Lock Bit)

これらのビットは外部プログラミング中のフラッシュとEEPROMに対する保護レベルを制御します。これらのビットは外部プログラミング インターフェースを通してのみ書き込み可能です。施錠ビットのリセットはチップ消去命令の実行によってのみ可能です。TIFとOCDを使う他の全てのアクセスはこの施錠ビットの何れかがOに書かれる場合に防がれます。これらのビットはメモリへのどのソフトウェア アクセスも妨げません。

表4-12. プログラミング 用施錠ビット

| <b>双干 12. 7 円</b> | 7 17 7 7 18 18 18 18 18 18 18 18 18 18 18 18 18 |                                                                                                                            |

|-------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| LB1,0             | 群構成設定                                           | 内容                                                                                                                         |

| 1 1               | NOLOCK                                          | 施錠なし、メモリ施錠は許可されません。                                                                                                        |

| 1 0               | WLOCK                                           | 書き込み施錠、フラッシュ メモリとEEPROMのプログラミング(書き込み)はプログラミング インターフェースに対して禁止されます。ヒューズビットはプログラミング インターフェースからの書き込みに対して施錠されます。                |

| 0 0               |                                                 | 読み書き施錠、フラッシュ メモリとEEPROMのプログラミング(書き込み)と読み込み/検証はプログラミング インターフェースに対して禁止されます。施錠ビットとヒューズ ビットはプログラミング インターフェースからの読み書きに対して施錠されます。 |

注: 施錠ビットを設定する前にヒューズビットとブート施錠ビットを設定してください。

## 4.16. レジスタ説明 - 製品識票列

## 4.16.1. RCOSC2M - 2MHz内部発振器校正レジスタ (Internal 2MHz Oscillator Calibration register)

| ピット        | 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 |         |

|------------|---|---|---|-------|--------|---|---|---|---------|

| \$00       |   |   |   | RCOSC | C2M7~0 |   |   |   | RCOSC2M |

| Read/Write | R | R | R | R     | R      | R | R | R |         |

| 初期値        | X | X | X | X     | X      | X | X | X |         |

#### ● ビット7~0 - RCOSC2M7~0: 2MHz内部発振器校正値 (Internal 2MHz Oscillator Calibration Value)

このバイトは2MHz内部発振器用の発振器校正値を含みます。発振器の校正はデバイスの製造検査中に実行されます。リセット中にこの値が2MHz DFLL用の校正レジスタB内へ自動的に格納されます。より多くの詳細については67頁の「CALB - DFLL校正レジスタB」を参照してください。

#### 4.16.2. RCOSC2MA - 2MHz内部発振器校正レジスタA (Internal 2MHz Oscillator Calibration register)

| ピット<br>\$01 | 7 | 6 | 5 | 4<br>RCOSC | 3<br>2MA7~0 | 2 | 1 | 0 | RCOSC2MA |

|-------------|---|---|---|------------|-------------|---|---|---|----------|

| Read/Write  | R | R | R | R          | R           | R | R | R |          |

| 初期値         | x | x | x | x          | x           | x | x | x |          |

#### ● ビット7~0 - RCOSC2MA7~0: 2MHz内部発振器校正値 (Internal 2MHz Oscillator Calibration Value)

このバイトは2MHz内部発振器用の発振器校正値を含みます。発振器の校正はデバイスの製造検査中に実行されます。リセット中にこの値が2MHz DFLL用の校正レジスタA内へ自動的に格納されます。より多くの詳細については67頁の「CALA - DFLL校正レジスタA」を参照してください。

### 4.16.3. RCOSC32K - 32.768kHz内部発振器校正レジスタ (Internal 32.768kHz Oscillator Calibration register)

| ピット        | 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 |          |

|------------|---|---|---|-------|--------|---|---|---|----------|

| \$02       |   |   |   | RCOSC | 32K7~0 |   |   |   | RCOSC32K |

| Read/Write | R | R | R | R     | R      | R | R | R |          |

| 初期値        | X | X | X | X     | X      | X | X | X |          |

#### ● ビット7~0 - RCOSC32K7~0: 32.768kHz内部発振器校正値 (Internal 32.768kHz Oscillator Calibration Value)

このバイトは32.768kHz内部発振器用の発振器校正値を含みます。発振器の校正はデバイスの製造検査中に実行されます。リセット中にこの値が32kHz発振器用の校正レジスタ内へ自動的に格納されます。より多くの詳細については65頁の「RC32KCAL - 32kHz内部発振器校正レジスタ」を参照してください。

#### 4.16.4. RCOSC32M - 32MHz内部発振器校正レジスタ(Internal 32MHz Oscillator Calibration register)

| \$03 RCOSC32M7~0 RCO | DSC32M   |

|----------------------|----------|

|                      | 3000ZIII |

| Read/Write R R R R R |          |

| 初期値 x x x x x x x x  |          |

#### ● ビット7~0 - RCOSC32M7~0 : 32MHz内部発振器校正値 (Internal 32MHz Oscillator Calibration Value)

このバイトは32MHz内部発振器用の発振器校正値を含みます。発振器の校正はデバイスの製造検査中に実行されます。リセット中にこの値が32MHz DFLL用の校正レジスタB内へ自動的に格納されます。より多くの詳細については67頁の「CALB - DFLL校正レジスタB」を参照してください。

## 4.16.5. RCOSC32MA - 32MHz内部発振器校正レジスタA (Internal 32MHz Oscillator Calibration register)

| ピット        | 7 | 6 | 5 | 4      | 3       | 2 | 1 | 0 |           |

|------------|---|---|---|--------|---------|---|---|---|-----------|

| \$04       |   |   |   | RCOSC3 | 32MA7∼0 |   |   |   | RCOSC32MA |

| Read/Write | R | R | R | R      | R       | R | R | R |           |

| 初期値        | X | X | X | X      | X       | X | X | X |           |

#### ● ビット7~0 - RCOSC32MA7~0: 32MHz内部発振器校正値 (Internal 32MHz Oscillator Calibration Value)

このバイトは32MHz内部発振器用の発振器校正値を含みます。発振器の校正はデバイスの製造検査中に実行されます。リセット中にこの値が32MHz DFLL用の校正レジスタA内へ自動的に格納されます。より多くの詳細については67頁の「CALA - DFLL校正レジスタA」を参照してください。

## 4.16.6. LOTNUMO - ロット番号レジスタO (Lot Number register 0)

LOTNUM0,LOTNUM1,LOTNUM2,LOTNUM3,LOTNUM4,LOTNUM5は各々のデバイスに対するロット番号を含みます。ウェハー番号とウェハー座標と共に、これはデバイスに対する通番を与えます。

|                        | T      |

|------------------------|--------|

|                        | OMUNTC |

| Read/Write R R R R R R |        |

| 初期値 x x x x x x x x    |        |

• ビット7~0 - LOTNUM07~0 : ロット番号バイト0 (LOT Number Byte 0)

このバイトはデバイスに対するロット番号のバイト0を含みます。

## 4.16.7. LOTNUM1 - ロット番号レジスタ1 (Lot Number register 1)

| ピット        | 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 | _       |

|------------|---|---|---|-------|--------|---|---|---|---------|

| \$09       |   |   |   | LOTNU | JM17∼0 |   |   |   | LOTNUM1 |

| Read/Write | R | R | R | R     | R      | R | R | R |         |

| 初期値        | X | X | X | X     | X      | X | X | X |         |

|            |   |   |   |       |        |   |   |   |         |

● ビット7~0 - LOTNUM17~0: ロット番号バイト1 (LOT Number Byte 1)

このバイトはデバイスに対するロット番号のバイト1を含みます。

#### **4.16.8. LOTNUM2 - ロット番号レシ スタ2** (Lot Number register 2)

| ピット        | 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 |         |

|------------|---|---|---|-------|--------|---|---|---|---------|

| \$0A       |   |   |   | LOTNU | JM27∼0 |   |   |   | LOTNUM2 |

| Read/Write | R | R | R | R     | R      | R | R | R |         |

| 初期値        | X | X | X | X     | X      | X | X | X |         |

● ビット7~0 - LOTNUM27~0: ロット番号バイト2 (LOT Number Byte 2)

このバイトはデバイスに対するロット番号のバイト2を含みます。

#### 4.16.9. LOTNUM3 - ロット番号レシ、スタ3 (Lot Number register 3)

| \$0B LOTNUM37~0 LOTNUM3 Read/Write R R R R R R R R R N N N N N N N N N N | ピット  | 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 | _       |

|--------------------------------------------------------------------------|------|---|---|---|-------|--------|---|---|---|---------|

|                                                                          | \$0B |   |   |   | LOTNU | JM37∼0 |   |   |   | LOTNUM3 |

| 初期値 x x x x x x x x x x                                                  |      | R | R | R | R     | R      | R | R | R |         |

|                                                                          | 初期値  |   |   |   | X     | X      | X | X | X |         |

● ビット7~0 - LOTNUM37~0: ロット番号バイト3 (LOT Number Byte 3)

このバイトはデバイスに対するロット番号のバイト3を含みます。

## 4.16.10. LOTNUM4 - ロット番号レジスタ4 (Lot Number register 4)

| ピット        | 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 |         |

|------------|---|---|---|-------|--------|---|---|---|---------|

| \$0C       |   |   |   | LOTNU | JM47∼0 |   |   |   | LOTNUM4 |

| Read/Write | R | R | R | R     | R      | R | R | R |         |

| 初期値        | X | X | X | X     | X      | X | X | X |         |

|            |   |   |   |       |        |   |   |   |         |

● ビット**7~0 - LOTNUM47~0 : ロット番号バイト4** (LOT Number Byte 4)

このバイトはデバイスに対するロット番号のバイト4を含みます。

## 4.16.11. LOTNUM5 - ロット番号レジスタ5 (Lot Number register 5)

| ヒ'ット       | 7 | 6 | 5 | 4        | 3   | 2 | 1 | 0 |         |

|------------|---|---|---|----------|-----|---|---|---|---------|

| \$0D       |   |   |   | LOTNUM57 | ·~0 |   |   |   | LOTNUM5 |

| Read/Write | R | R | R | R        | R   | R | R | R |         |

| 初期値        | X | X | X | X        | X   | X | X | X |         |

● ビット7~0 - LOTNUM57~0: ロット番号バイト5 (LOT Number Byte 5)

このバイトはデバイスに対するロット番号のバイト5を含みます。

## 4.16.12. WAFNUM - ウェハー番号レジスタ (Wafer Number register)

| ピット        | 7 | 6 | 5 | 4    | 3     | 2 | 1 | 0 | _      |

|------------|---|---|---|------|-------|---|---|---|--------|

| \$10       |   |   |   | WAFN | UM7~0 |   |   |   | WAFNUM |

| Read/Write | R | R | R | R    | R     | R | R | R |        |

| 初期値        | 0 | 0 | 0 | X    | X     | X | X | X |        |

#### ● ビット7~0 - WAFNUM7~0: ウェハー番号 (Wafer Number)

このバイトは各々のデバイスに対するウェハー番号を含みます。 ロット番号とウェハー座標と共に、これはデバイスに対する通番を与えます。

## 4.16.13. COORDXO - ウェハーX座標レジスタO (Wafer Coordinate X register 0)

COORDX0,COORDX1,COORDY0,COORDY1は各々のデバイスに対するウェハーのX座標とY座標を含みます。ロット番号とウェハー番号と共に、これは各々のデバイスに対する通番を与えます。

| ヒット 7        | 6   | 5 | 4  | 3        | 2 | 1 | 0 |         |

|--------------|-----|---|----|----------|---|---|---|---------|

| \$12         |     |   | CO | ORDX07~0 |   |   |   | COORDX0 |

| Read/Write F | ' R | R | R  | R        | R | R | R |         |

| 初期値x         | X   | X | X  | X        | X | X | X |         |

### ● ビット7~0 - COORDX07~0: ウェハーX座標パイト0 (Wafer Coordinate X Byte 0)

このバイトはデバイスに対するウェハーX座標のバイト0を含みます。

## 4.16.14. COORDX1 - ウェハーX座標レジスタ1 (Wafer Coordinate X register 1)

| <b>ビット</b> | 7  | 6  | 5 | 4     | 3      | 2 | 1 | 0 | _       |

|------------|----|----|---|-------|--------|---|---|---|---------|

| \$13       |    |    |   | COORI | DX17∼0 |   |   |   | COORDX1 |

| Read/Write | R  | R  | R | R     | R      | R | R | R |         |

| 初期値        | ** | ** |   |       | **     |   |   |   |         |

### ● ビット7~0 - COORDX17~0: ウェハーX座標パイト1 (Wafer Coordinate X Byte 1)

このバイトはデバイスに対するウェハーX座標のバイト1を含みます。

## 4.16.15. COORDYO - ウェハーY座標レシ、スタO (Wafer Coordinate Y register 0)

| ヒ`ット _     | 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 |         |

|------------|---|---|---|-------|--------|---|---|---|---------|

| \$14       |   |   |   | COORI | OY07∼0 |   |   |   | COORDY0 |

| Read/Write | R | R | R | R     | R      | R | R | R |         |

| 初期値        | X | X | X | X     | X      | X | X | X |         |

#### ● ビット7~0 - COORDY07~0: ウェハーY座標バイト0 (Wafer Coordinate Y Byte 0)

このバイトはデバイスに対するウェハーY座標のバイト0を含みます。

#### 4.16.16. COORDY1 - ウェハーY座標レジスタ1 (Wafer Coordinate Y register 1)

| ピット _      | 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 | _       |

|------------|---|---|---|-------|--------|---|---|---|---------|

| \$15       |   |   |   | COORI | DY17~0 |   |   |   | COORDY1 |

| Read/Write | R | R | R | R     | R      | R | R | R |         |

| 初期値        | X | X | X | X     | X      | X | X | X |         |

## ● ビット7~0 - COORDY17~0: ウェハ-Y座標バイト1 (Wafer Coordinate Y Byte 1)

このバイトはデバイスに対するウェハーY座標のバイト1を含みます。

#### 4.16.17. USBCALO - USBパット校正レジスタの (USB Pad Calibration register 0)

USBCAL0とUSBCAL1はUSBピンに対する校正値を含みます。校正はデバイスに対してUSB線上での外部部品の必要なしでの動作を 許すために製造検査中に行われます。この校正バイトはUSB校正レジスタ内へ自動的に格納されず、故にソフトウェアで行われなければなりません。

| ピット        | 7 | 6 | 5 | 4     | 3     | 2 | 1 | 0 |         |

|------------|---|---|---|-------|-------|---|---|---|---------|

| \$1A       |   |   |   | USBCA | L07∼0 |   |   |   | USBCAL0 |

| Read/Write | R | R | R | R     | R     | R | R | R |         |

| 初期値        | X | X | X | X     | X     | X | X | X |         |

#### ● ビット7~0 - USBCAL07~0: USB校正バイト0 (USB Pad Calibration Byte 0)

このバイトはUSBピン校正データのバイト0を含み、これはUSBの校正下位(CALL)レジスタ内に格納されなければなりません。

## 4.16.18. USBCAL1 - USBパット 校正レジスタ1 (USB Pad Calibration register 1)

| ピット        | 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 | _       |

|------------|---|---|---|-------|--------|---|---|---|---------|

| \$1B       |   |   |   | USBCA | \L17~0 |   |   |   | USBCAL1 |

| Read/Write | R | R | R | R     | R      | R | R | R |         |

| 初期値        | X | X | X | X     | X      | X | X | X |         |

#### ● ビット7~0 - USBCAL17~0: USB校正バ仆1 (USB Pad Calibration Byte 1)

このバイトはUSBピン校正データのバイト1を含み、これはUSBの校正上位(CALH)レジスタ内に格納されなければなりません。

## 4.16.19. USBRCOSC - USB RCOSC校正レジスタ (USB RCOSC Calibration register)

| ピット        | 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 | _        |

|------------|---|---|---|-------|--------|---|---|---|----------|

| \$1C       |   |   |   | USBRC | OSC7~0 |   |   |   | USBRCOSC |

| Read/Write | R | R | R | R     | R      | R | R | R |          |

| 初期値        | X | X | X | X     | X      | X | X | X |          |

#### ● ビット7~0 - USBRCOSC7~0: 48MHz RCOSC校正バイト0 (48MHz RCOSC Calibration Byte)

このバイトは内部32MHz発振器に対する48MHz校正値を含みます。この校正値が32MHz DFLL用の校正レジスタB(CALB)に書かれると、内部発振器からの全速(Full-speed)USB動作を許すために発振器が48MHzに較正されます。

注: DFLL32M内部のCOMP2とCOMP1のレシブスタは\$B71Bに設定されなければなりません。

## 4.16.20. ADCACALO - ADCA校正レジスタO (ADCA Calibration register 0)

ADCACAL0とADCACAL1はA/D変換器A(ADCA)に対する校正値を含みます。校正はデバイスの製造検査中に行われます。この校正パイトはA/D変換器校正レジスタ内へ自動的に格納されず、故にソフトウェアで行われなければなりません。

| ヒ"ット       | 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 | -        |

|------------|---|---|---|-------|--------|---|---|---|----------|

| \$20       |   |   |   | ADCAC | AL07~0 |   |   |   | ADCACAL0 |

| Read/Write | R | R | R | R     | R      | R | R | R |          |

| 初期値        | X | X | X | X     | X      | X | X | X |          |

### ● ビット7~0 - ADCACAL07~0: A/D変換器A校正バイト0 (ADCA Calibration Byte 0)

このバイトはA/D変換器A校正データのバイト0を含み、これはADCAの校正下位(CALL)レジスタ内に格納されなければなりません。

#### 4.16.21. ADCACAL1 - ADCA校正レジスタ1 (ADCA Calibration register 1)

| ピット        | 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 |          |

|------------|---|---|---|-------|--------|---|---|---|----------|

| \$21       |   |   |   | ADCAC | AL17~0 |   |   |   | ADCACAL1 |

| Read/Write | R | R | R | R     | R      | R | R | R |          |

| 初期値        | X | X | X | X     | X      | X | X | X |          |

|            |   |   |   |       |        |   |   |   |          |

## ● ビット7~0 - ADCACAL17~0: A/D変換器A校正バイト1 (ADCA Calibration Byte 1)

このバイトはA/D変換器A校正データのバイト1を含み、これはADCAの校正上位(CALH)レン゙スタ内に格納されなければなりません。

#### 4.16.22. ADCBCALO - ADCB校正レジスタO (ADCB Calibration register 0)

ADCBCAL0とADCBCAL1はA/D変換器B(ADCB)に対する校正値を含みます。校正はデバイスの製造検査中に行われます。この校正バイトはA/D変換器校正レジスタ内へ自動的に格納されず、故にソフトウェアで行われなければなりません。

| ピット        | 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 |          |

|------------|---|---|---|-------|--------|---|---|---|----------|

| \$24       |   |   |   | ADCBC | AL07~0 |   |   |   | ADCBCAL0 |

| Read/Write | R | R | R | R     | R      | R | R | R |          |

| 初期値        | X | X | X | X     | X      | X | X | X |          |

|            |   |   |   |       |        |   |   |   |          |

#### ● ビット7~0 - ADCBCAL07~0: A/D変換器B校正バイト0 (ADCB Calibration Byte 0)

このバイトはA/D変換器B校正データのバイト0を含み、これはADCBの校正下位(CALL)レジスタ内に格納されなければなりません。

#### 4.16.23. ADCBCAL1 - ADCB校正レジスタ1 (ADCB Calibration register 1)

| ピット        | 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 |          |

|------------|---|---|---|-------|--------|---|---|---|----------|

| \$25       |   |   |   | ADCBC | AL17~0 |   |   |   | ADCBCAL1 |

| Read/Write | R | R | R | R     | R      | R | R | R |          |

| 初期値        | X | X | X | X     | X      | X | X | X |          |

|            |   |   |   |       |        |   |   |   |          |

## ● ビット7~0 - ADCBCAL17~0: A/D変換器B校正バイト1 (ADCB Calibration Byte 1)

このバイトはA/D変換器B校正データのバイト1を含み、これはADCBの校正上位(CALH)レジスタ内に格納されなければなりません。

## 4.16.24. TEMPSENSEO - 温度感知器校正レジスタO (Temperature Sensor Calibration register 0)

TEMPSENSE0とTEMPSENSE1は内部温度感知器で行われた温度測定からの12ビットADCA変換値を含みます。この測定は製造検査に於いて85℃で行われ、単点または多点温度感知器校正に使うことができます。

| <b>Ľ</b> ット | 7 | 6 | 5 | 4        | 3    | 2 | 1 | 0 |            |

|-------------|---|---|---|----------|------|---|---|---|------------|

| \$2E        |   |   | Т | EMPSENSE | 07~0 |   |   |   | TEMPSENSE0 |

| Read/Write  | R | R | R | R        | R    | R | R | R |            |

| 初期値         | X | X | X | X        | X    | X | X | X |            |

● ビット7~0 - TEMPSENSE07~0:温度感知器校正バイト0 (Temperature Sensor Calibration Byte 0)

このバイトは温度測定のバイト0(下位8ビット)を含みます。

## 4.16.25. TEMPSENSE1 - 温度感知器校正レジスタ1 (Temperature Sensor Calibration register 1)

| ヒ゛ット _     | 7 | 6 | 5 | 4      | 3       | 2 | 1 | 0 |            |

|------------|---|---|---|--------|---------|---|---|---|------------|

| \$2F       |   |   |   | TEMPSE | NSE17~0 |   |   |   | TEMPSENSE1 |

| Read/Write | R | R | R | R      | R       | R | R | R |            |

| 初期値        | 0 | 0 | 0 | 0      | X       | X | X | X |            |

● ビット7~0 - TEMPSENSE17~0: 温度感知器校正バイト1 (Temperature Sensor Calibration Byte 1)

このバイトは温度測定のバイト1を含みます。

## 4.17. レジスタ説明 - 汎用I/Oメモリ

## 4.17.1. GPIORn - 汎用I/Oレジスタn (General Purpose I/O register n)

| ピット        | 7         | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _ |  |

|------------|-----------|-----|-----|-----|-----|-----|-----|-----|---|--|

| +n         | GPIORn7~0 |     |     |     |     |     |     |     |   |  |

| Read/Write | R/W       | R/W | R/W | R/W | R/W | R/W | R/W | R/W |   |  |

| 初期値        | 0         | 0   | 0   | 0   | 0   | 0   | 0   | 0   |   |  |

これらはビット アクセス可能なI/Oメモリ空間でのフラグや全体変数のようなデータの格納に使える汎用レジスタです。

## 4.18. レジスタ説明 - MCU制御

## **4.18.1. DEVIDO - デバイスIDレシ スタO** (Device ID register 0)

DEVID0,DEVID1,DEVID2レジスタは各マイクロコントローラデバイス形式を識別するバイト識別を含みます。実際のIDの詳細についてはデバイスのデータシートを参照してください。

| ヒ゛ット       | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 | _ |  |  |

|------------|----------|---|---|---|---|---|---|---|---|--|--|

| +\$00      | DEVID7~0 |   |   |   |   |   |   |   |   |  |  |

| Read/Write | R        | R | R | R | R | R | R | R |   |  |  |

| 初期値        | 0        | 0 | 0 | 1 | 1 | 1 | 1 | 0 |   |  |  |

ビット7~0 - DEVID7~0: デバイスID第1バイト (Device ID Byte 0)

デバイスIDの第1バイト。このバイトは常に\$1Eとして読めます。これはAtmelによって製造されたことを示します。

## **4.18.2. DEVID1** – すいイスIDレシスタ1 (Device ID register 1)

| L            | 6     | 5   | 4   | 3       | 2   | 1   | 0   |        |

|--------------|-------|-----|-----|---------|-----|-----|-----|--------|

| +\$01        |       |     | DEV | VID15~8 |     |     |     | DEVID1 |

| Read/Write F | R R   | R   | R   | R       | R   | R   | R   |        |

| 初期値 1/       | 0 1/0 | 1/0 | 1/0 | 1/0     | 1/0 | 1/0 | 1/0 |        |

• ビット7~0 - DEVID15~8: デバイスID第2バイト (Device ID Byte 1)

デバイスIDの第2バイはデバイスのフラッシュ容量を示します。

#### **4.18.3. DEVID2 - デバイスIDレジスタ2** (Device ID register 2)

| ピット        | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|------------|------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| +\$02      | DEVID23~16 |     |     |     |     |     |     |     |  |  |

| Read/Write | R          | R   | R   | R   | R   | R   | R   | R   |  |  |

| 初期値        | 1/0        | 1/0 | 1/0 | 1/0 | 1/0 | 1/0 | 1/0 | 1/0 |  |  |

• ビット7~0 - DEVID23~16: デバイスID第3バイト (Device ID Byte 2)

デバイスIDの第3バイトはデバイス番号を示します。

#### 4.18.4. REVID - 改訂ID (Revision ID)

| ピット        | 7 | 6 | 5 | 4 | 3   | 2   | 1     | 0   |       |

|------------|---|---|---|---|-----|-----|-------|-----|-------|